Page 1

Rev 0; 4/09

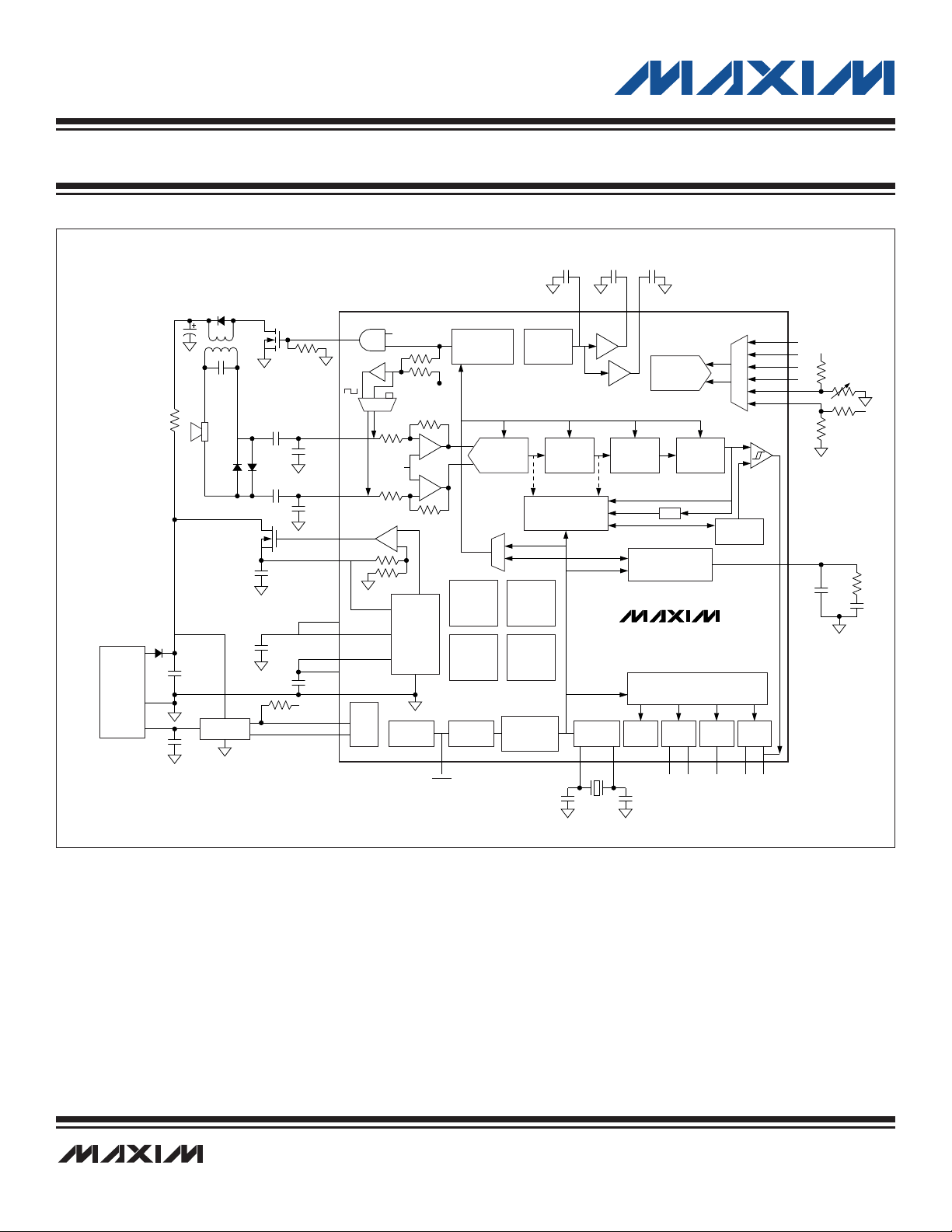

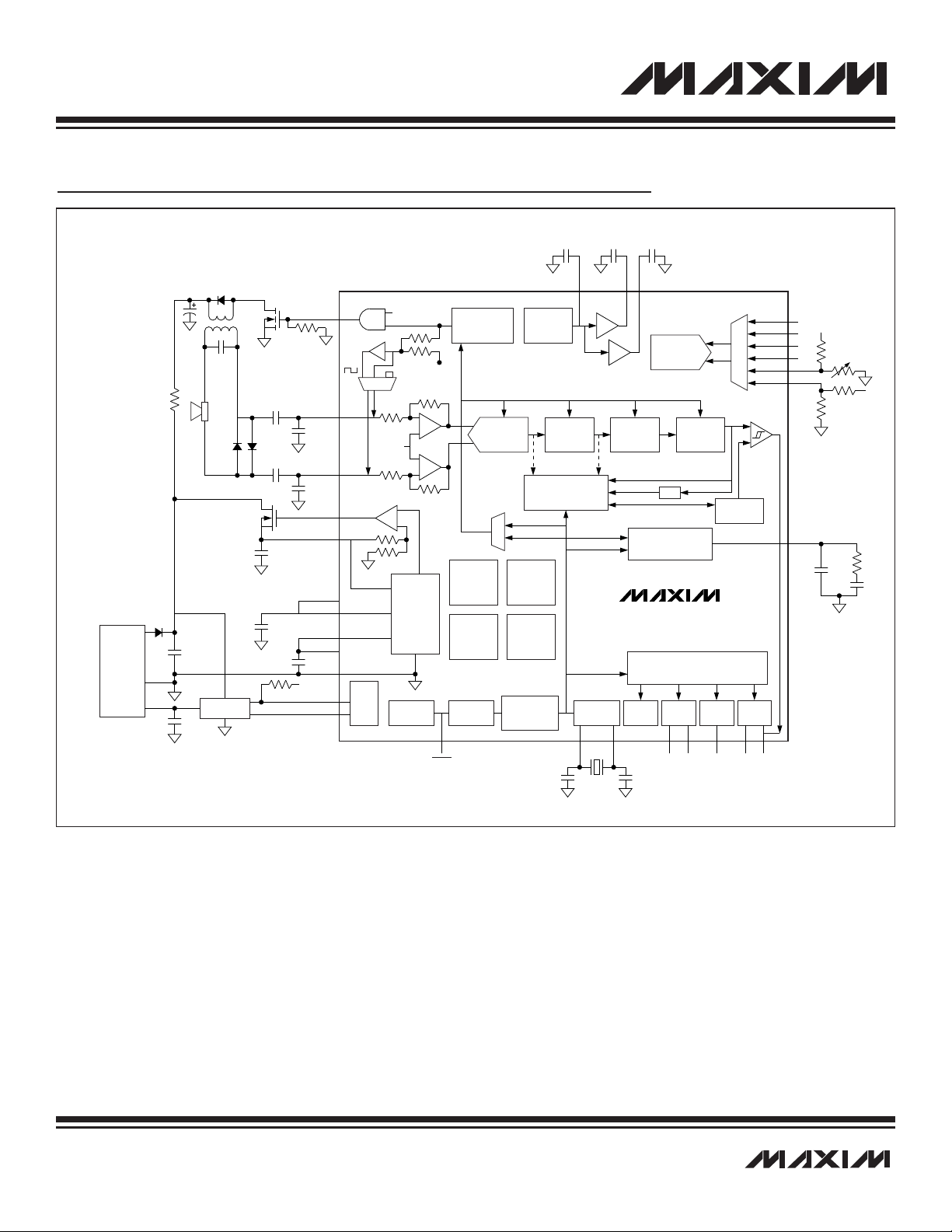

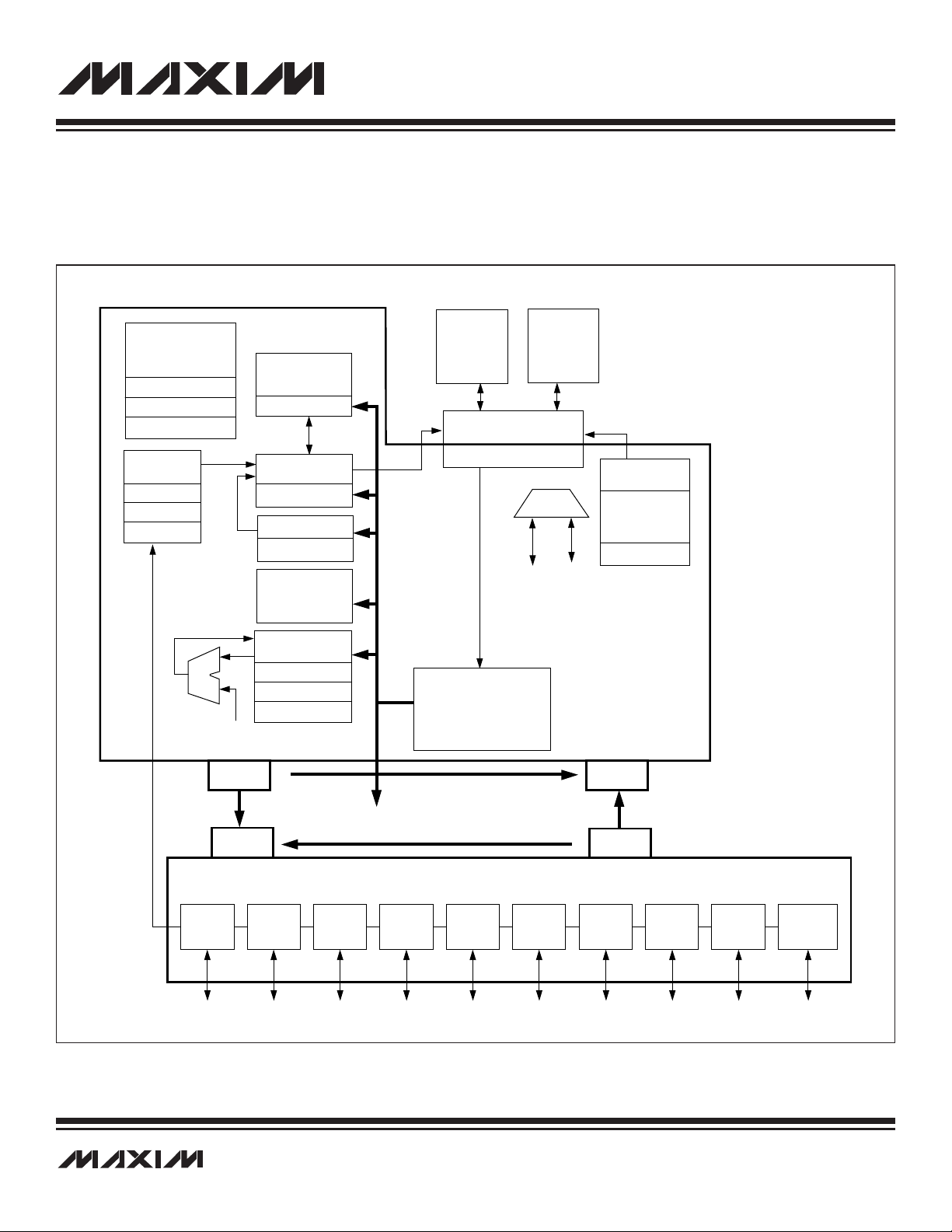

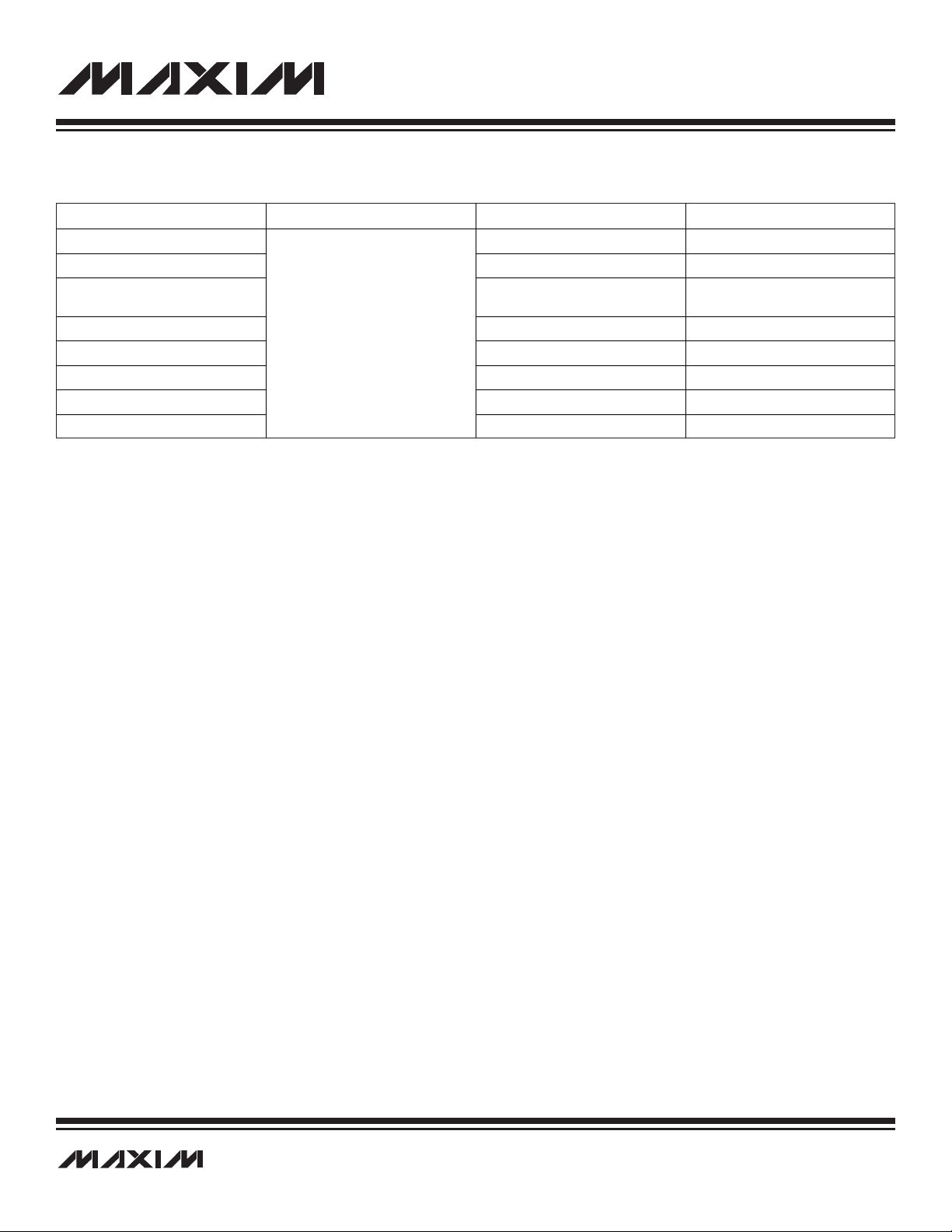

BURST ENABLE

AVDD/2

120kΩ

LNAAVDD/2

0mV

2mV

-1

MUX

BURST OUTPUT,

DUTY CYCLE, AND

PULSE COUNTER

SIGMA-DELTA

ADC

SIGMA-DELTA

ADC

DIGITAL

BANDPASS

FILTER

RAM

2K x 16

ROM

2K x 16

16 x 16

HW MULT

+ ACCUM

FLASH

8K x 16

OR

16K x 16

INTERNAL

REGULATORS

16-BIT 16-MIPS

MICROCONTROLLER

PROGRAMMABLE

PLL-BASED OSCILLATOR

VOLTAGE

REFERENCE

FULL WAVE

DETECTOR

THRESHOLD

ADJUST

SYSTEM

TIMER

TIMER 2

CRYSTAL

OSCILLATOR

16MHz (MAX)

INTERNAL

OSCILLATOR

WATCHDOG

POR/

BROWNOUT

UART

(LIN)

TIMER 1 TIMER 0

T0B_CMPOT0

DIGITAL

LOWPASS

FILTER

120kΩ

3kΩ

3kΩ

0.47µF

REFBG

0.47µF 0.47µF

REFSAR REFECHO

AIN0

BURST

ECHON

470pF

0.01µF

ECHOP

GATE5

AVDD

DVDD

GND

Rx

Tx

DVDDIO

REG3P3

REG2P5

+5.0V DVDDIO

BSP129

AVDD

330pF

THERMISTOR

BATTERY+

AIN1

AIN2

AIN3

AIN4

AIN5

FILT

T1T2

16MHz

20pF20pF

T2B

RESET

CLOCK PRESCALERS

DIVIDE BY 1 TO 128

FIFO

33nF

24kΩ

470pF

0.01µF

0.1µF

0.1µF

0.1µF

TRANSCEIVER

CONNECTOR

V+

GROUND

SIGNAL

+9V TO

+20V

MAXQ7667

MAXQ7667 USER’S GUIDE

______________________________________________________________________________________ Maxim Integrated Products i

Page 2

MAXQ7667 User’s Guide

TABLE OF CONTENTS

SECTION 1: Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .1-1

SECTION 2: Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-1

SECTION 3: Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-1

SECTION 4: Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .4-1

SECTION 5: General-Purpose I/O Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .5-1

SECTION 6: Type 2 Timer/Counter Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .6-1

SECTION 7: Schedule Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .7-1

SECTION 8: UART and LIN . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8-1

SECTION 9: Enhanced Serial Peripheral Interface (SPI) Module . . . . . . . . . . . . . . . . . . . . . . . . . . .9-1

SECTION 10: Hardware Multiplier Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10-1

SECTION 11: Test Access Port (TAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11-1

SECTION 12: In-Circuit Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .12-1

SECTION 13: In-System Programming/Bootloader . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13-1

SECTION 14: SAR ADC Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14-1

SECTION 15: Oscillator/Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15-1

SECTION 16: Power-Supply/Supervisory Monitoring . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .16-1

SECTION 17: Ultrasonic Distance Measurement Module—

Burst Transmission and Echo Reception . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .17-1

SECTION 18: Utility ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18-1

SECTION 19: Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19-1

_____________________________________________________________________________________________________________ ii

Page 3

MAXQ7667 User’s Guide

SECTION 1: OVERVIEW

The MAXQ7667 is a smart data-acquisition system based on the MAXQ®microcontroller (µC) with integrated peripheral functions for

ultrasonic, time-of-flight, distance measurement. The MAXQ processor is a high-performance reduced instruction set computing (RISC)

core µC designed for efficient peripheral multitasking applications. The MAXQ core contains a 16-bit Harvard Architecture RISC core

that executes instructions in a single clock cycle from instruction fetch to cycle completion. The MAXQ core works without the aid of

an instruction prefetch pipeline. This streamlines the entire instruction fetch, decode, and execute task, which dramatically improves

code density, memory access benchmarks, and multitasking interrupt-based latency. The MAXQ architecture was designed specifically for analog I/O and peripheral multitasking applications.

As a member of the MAXQ family of 16-bit RISC µCs, the MAXQ7667 is ideal for low-cost, low-power embedded applications such as

• Automotive Parking

• Vehicle Security

• Industrial Processing

• Automation

• Handheld Devices

The flexible, modular architecture design used in these µCs allows development of targeted products for specific applications with minimal effort.

The MAXQ7667 includes the following general-purpose peripherals: maximum 16MHz (factory default is 13.5MHz) RC oscillator, crystal oscillator support, watchdog timer, schedule timer, three general-purpose timer/counters, two 8-bit GPIO ports, SPI™ port, JTAG

port, LIN-capable UART, 12-bit ADC with five input channels, and a voltage reference. These modules are useful for communication,

diagnostics, and miscellaneous support.

Peripherals dedicated to ultrasonic measurement include a burst signal generator and echo signal processing for transducer frequencies from 25kHz to 100kHz. When triggered, the BURST output supplies the specified number of transducer excitation cycles at

the specified frequency and duty cycle. Echo signals are received and digitized by a low noise amplifier (LNA) and 16-bit sigma-delta

ADC that together provide a variable gain ranging from 38dB to 60dB. Following the ADC is a digital bandpass filter, demodulator, and

digital lowpass filter with a 16-bit output. Supporting both the burst generator and echo reception is a programmable, PLL frequency

synthesizer that supplies both the burst frequency and the clock for the digital filters. Using the PLL for both burst transmission and

echo reception ensures that the bandpass filter always tracks the transducer excitation. Both the digital filtering and the clock synthesis are done without CPU intervention. All the CPU power is available for other tasks.

MAXQ7667 Features

• 16-Bit Single-Cycle RISC Core Processor

• Simultaneous Instruction/Data Harvard Memory Architecture

• 32KB Flash Memory

• 4KB Data RAM

• Utility ROM

• Burst-Pulse Generation Using Fractional N Frequency Synthesis

• Low-Noise, Variable Gain, Echo Receive Amplifier

16-Bit Sigma-Delta ADC for Digitizing the Echo

Digital Bandpass Filter that Tracks the Burst Frequency

Digital Demodulator and Lowpass Filter to Create an Echo Envelope with 16-Bit Resolution

FIFO Stores Up to 8 Readings from the Lowpass Filter

Digital Comparator Trips When Output of Lowpass Filter Reaches the Programmed Value

• 12-Bit, 5-Channel SAR ADC

• 2.5V Reference

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

SPI is a trademark of Motorola, Inc.

___________________________________________________________________________________ Maxim Integrated Products 1-1

Page 4

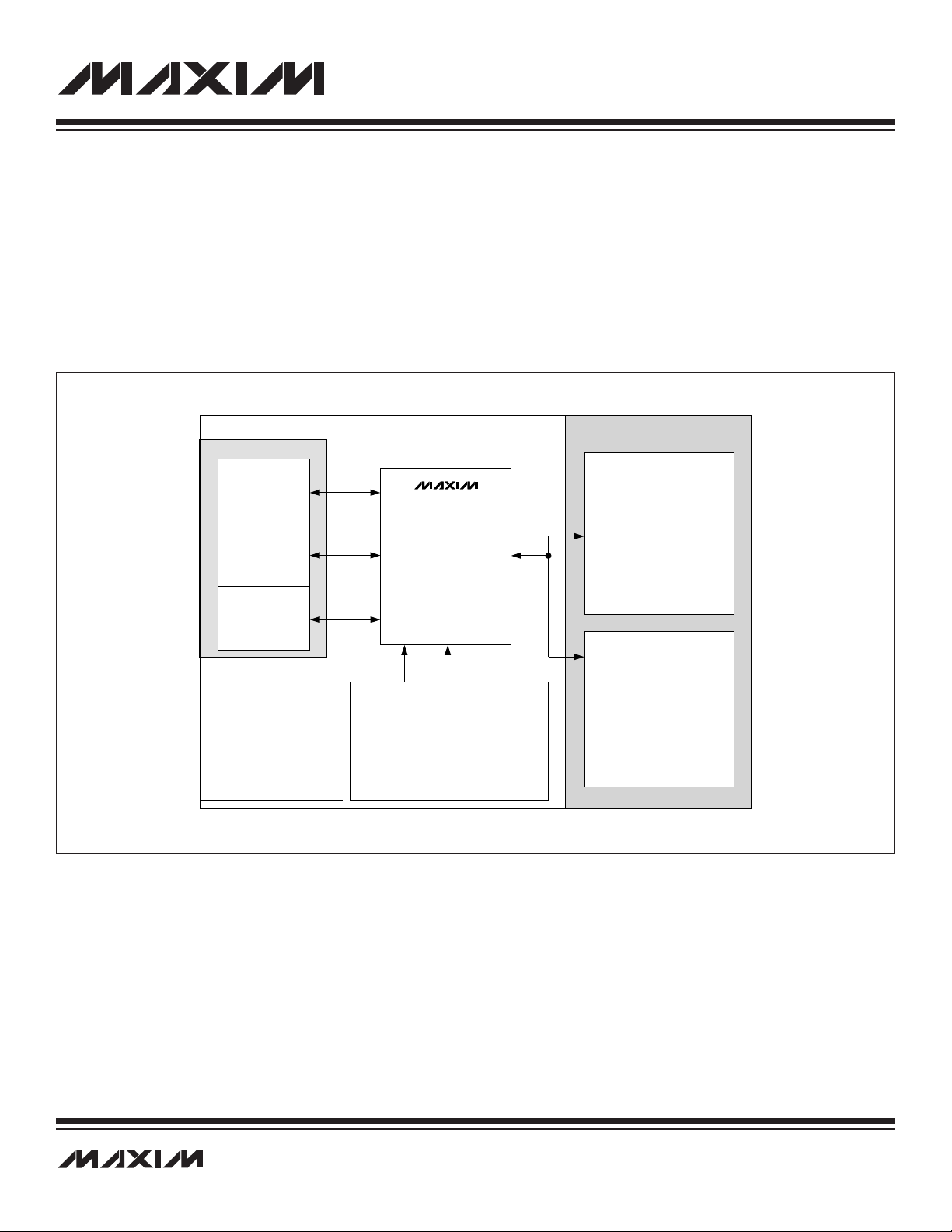

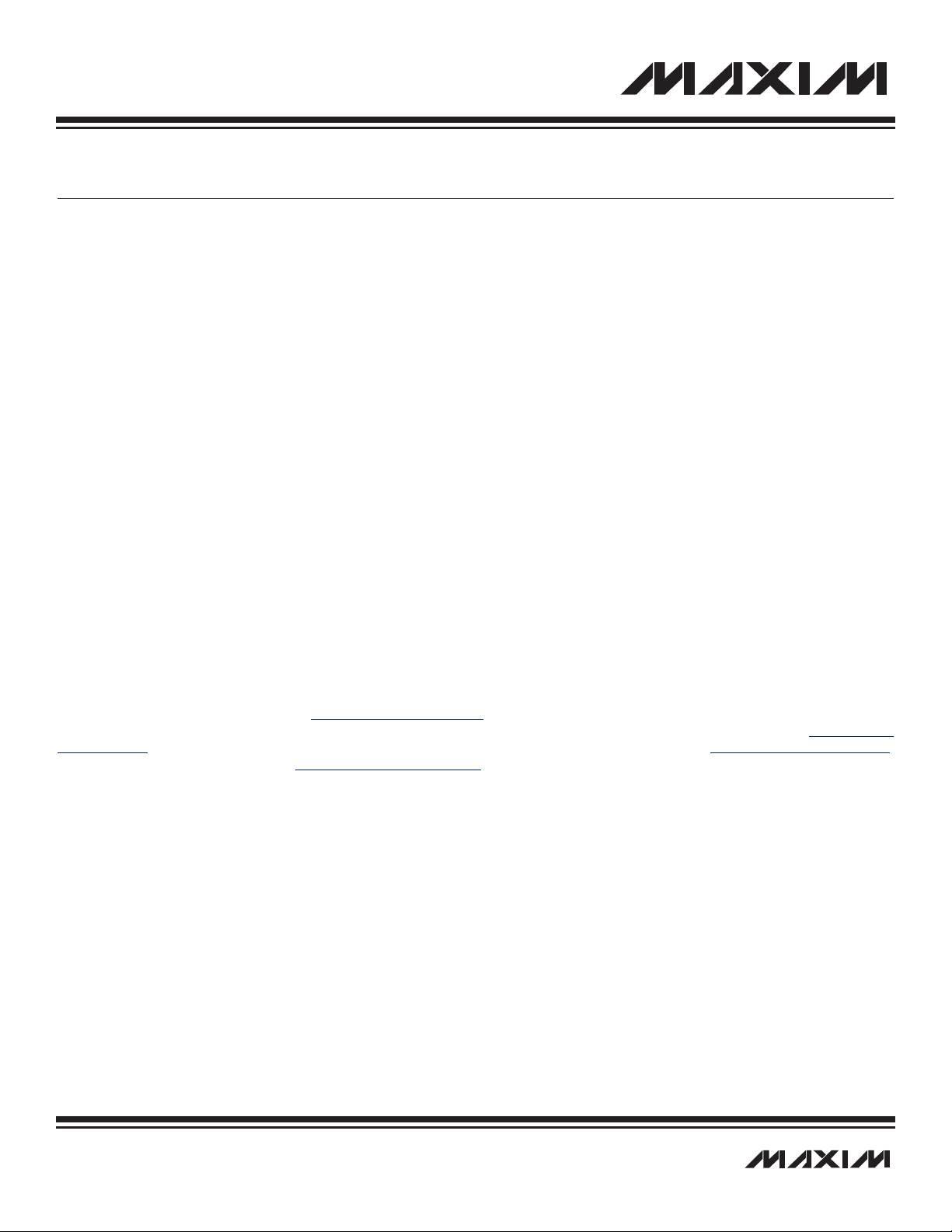

• One Schedule Timer

16-BIT HARVARD

MAXQ RISC CPU

•

16 ALU REGISTERS

•

MMU

•

HW MULTPLY/ACCUM

•

INTERRUPT CONTROL

•

16-WORD HW STACK

•

HARVARD ARCHITECTURE

MEMORY MODULE

CORE MODULES

CLOCK/CRYSTAL/

TIMER MODULE

•

INTERNAL 16MHz (MAX)

OSCILLATOR

•

EXTERNAL XTAL OSC

•

WATCHDOG TIMER

•

SCHEDULE TIMER

POWER MANAGEMENT

MODULE

•

+5V I/O REGULATOR

•

+3.3V ANALOG REGULATOR

•

+2.5V CORE REGULATOR

•

POWER-ON RESET

•

SUPPLY BROWNOUT DETECTORS

PERIPHERAL MODULES

GENERAL-PURPOSE

PERIPHERALS

•

3 16-BIT TIMER/PWMs

•

2 8-BIT I/O PORTS

•

UART WITH LIN 2.0 H/W

•

SPI INTERFACE

•

JTAG INTERFACE

•

12-BIT, 5-CHANNEL ADC

•

VOLTAGE REFERENCE

MAXQ7667

APPLICATION-SPECIFIC

PERIPHERALS

•

VARIABLE GAIN LNA

•

16-BIT SIGMA-DELTA ADC

•

DIGITAL BANDPASS FILTER

•

DIGITAL LOWPASS FILTER

•

LP FILTER FIFO

•

PLL FREQUENCY GENERATOR

•

BURST GENERATOR

UTILITY ROM

DATA RAM

4KB

(2KWORD)

FLASH ROM

32KB

(16KWORD)

• Three General-Purpose Timers

• LIN-Compatible UART

• SPI Port

• JTAG Port

• Watchdog Timer

• Voltage Monitors

MAXQ7667 User’s Guide

MAXQ7667 Module Functions

___________________________________________________________________________________________________________ 1-2

Page 5

MAXQ7667 User’s Guide

BURST ENABLE

AVDD/2

120kΩ

LNAAVDD/2

0mV

2mV

-1

MUX

BURST OUTPUT,

DUTY CYCLE, AND

PULSE COUNTER

SIGMA-DELTA

ADC

SIGMA-DELTA

ADC

DIGITAL

BANDPASS

FILTER

RAM

2K x 16

ROM

2K x 16

16 x 16

HW MULT

+ ACCUM

FLASH

8K x 16

OR

16K x 16

INTERNAL

REGULATORS

16-BIT 16-MIPS

MICROCONTROLLER

PROGRAMMABLE

PLL-BASED OSCILLATOR

VOLTAGE

REFERENCE

FULL WAVE

DETECTOR

THRESHOLD

ADJUST

SYSTEM

TIMER

TIMER 2

CRYSTAL

OSCILLATOR

16MHz (MAX)

INTERNAL

OSCILLATOR

WATCHDOG

POR/

BROWNOUT

UART

(LIN)

TIMER 1 TIMER 0

T0B_CMPOT0

DIGITAL

LOWPASS

FILTER

120kΩ

3kΩ

3kΩ

0.47µF

REFBG

0.47µF 0.47µF

REFSAR REFECHO

AIN0

BURST

ECHON

470pF

0.01µF

ECHOP

GATE5

AVDD

DVDD

GND

Rx

Tx

DVDDIO

REG3P3

REG2P5

+5.0V DVDDIO

BSP129

AVDD

330pF

THERMISTOR

BATTERY+

AIN1

AIN2

AIN3

AIN4

AIN5

FILT

T1T2

16MHz

20pF20pF

T2B

RESET

CLOCK PRESCALERS

DIVIDE BY 1 TO 128

FIFO

33nF

24kΩ

470pF

0.01µF

0.1µF

0.1µF

0.1µF

TRANSCEIVER

CONNECTOR

V+

GROUND

SIGNAL

+9V TO

+20V

MAXQ7667

Typical Application Circuit

1-3 ___________________________________________________________________________________________________________

Page 6

MAXQ7667 User’s Guide

SECTION 2: ARCHITECTURE

This section contains the following information:

2.1 Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.1 References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.1.2 Instruction Set . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.1.3 Harvard Memory Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.1.4 Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.2 Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.2.1 Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

2.2.2 Register Space . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.2.3 Memory Organization . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.3.1 Program Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.2.3.2 Utility ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.3.3 Data Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.2.3.4 Stack Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.2.3.5 Pseudo-Von Neumann Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.2.3.6 Pseudo-Von Neumann Memory Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.2.3.7 Data Alignment . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.2.3.8 Memory Management Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-15

2.2.4 Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18

2.2.4.1 Servicing Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18

2.2.4.2 Interrupt System Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-18

2.2.4.3 Synchronous vs. Asynchronous Interrupt Sources . . . . . . . . . . . . . . . . . . . . . .2-19

2.2.4.4 Interrupt Prioritization by Software . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19

2.2.4.5 Interrupt Exception Window . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19

2.2.4.6 MAXQ7667 Interrupt Sources . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-19

___________________________________________________________________________________ Maxim Integrated Products 2-1

Page 7

MAXQ7667 User’s Guide

LIST OF FIGURES

Figure 2-1. MAXQ7667 Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Figure 2-2. MAXQ7667 Transport-Triggered Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

Figure 2-3. Instruction Word Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

Figure 2-4. Pseudo-Von Neumann Memory Map (MAXQ7667 Default) . . . . . . . . . . . . . . . . . . . .2-13

Figure 2-5. Word Access Mode in MAXQ7667 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-16

Figure 2-6. Byte Access Mode in MAXQ7667 . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-17

Figure 2-7. MAXQ7667 Interrupt Source Hierarchy Example . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-20

LIST OF TABLES

Table 2-1. Register-to-Register Transfer Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

Table 2-2. MAXQ7667 Register Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

Table 2-3. MAXQ7667 Interrupt Sources and Control Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-21

___________________________________________________________________________________________________________ 2-2

Page 8

MAXQ7667 User’s Guide

SECTION 2: ARCHITECTURE

2.1 Overview

The MAXQ7667 is a low-power, high-performance, 16-bit RISC microcontroller based on the MAXQ architecture. It includes support

for integrated, in-system-programmable flash memory and a wide range of peripherals supporting ultrasonic measurement, schedule

timer, general-purpose timer/counters, GPIO, SPI, JTAG port, LIN-capable UART, 12-bit SAR ADC with five input channels, and a voltage reference.

The MAXQ7667 key features include:

• 16-Bit Single-Cycle RISC Core Processor

• Simultaneous instruction/Data Harvard Memory Architecture

• 32KB Flash Memory

• 4KB Data RAM

• Utility ROM

• Burst Generation and Echo Reception for Ultrasonic Measurement

• 12-Bit, 5-Channel SAR ADC

• One Schedule Timer

• Three General-Purpose Timers

• LIN-Compatible UART

• SPI Port

• JTAG Port

• Watchdog Timer

• Voltage Monitors

2.1.1 References

The online MAXQ7667 QuickView page contains information and data sheet links for all parts in the MAXQ7667 family. Errata sheets

for the MAXQ products are available at

ment hardware and software, frequently asked questions and software examples, visit the MAXQ home page at

ic.com/MAXQ. For general questions and discussion of the MAXQ platform, visit our discussion board at http://discuss.dalsemi.com.

Technical Support is also available at www.maxim-ic.com/support.

www.maxim-ic.com/errata. For more information on other MAXQ microcontrollers, develop-

www.maxim-

2-3 ___________________________________________________________________________________________________________

Page 9

MAXQ7667 User’s Guide

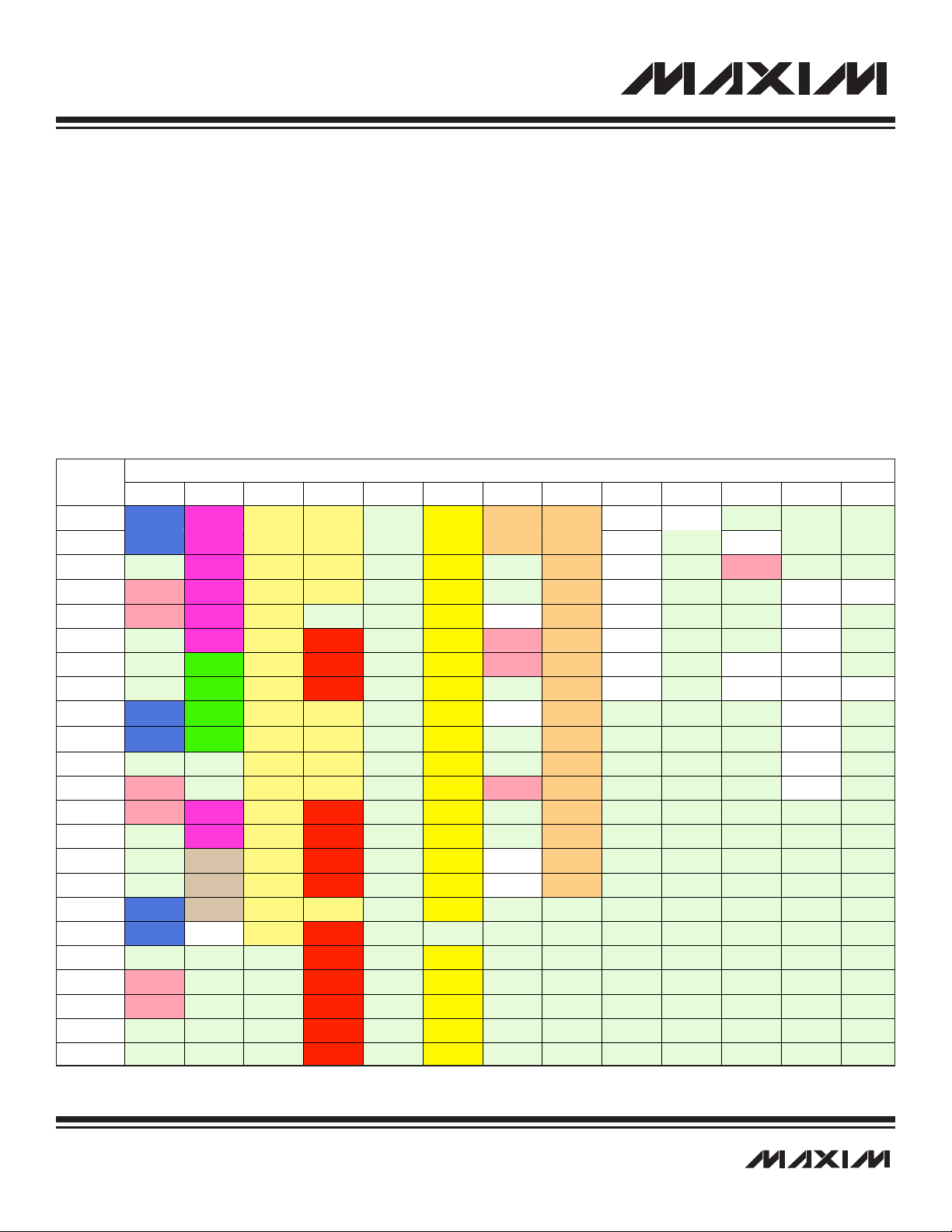

16-BIT HARVARD

MAXQ RISC CPU

•

16 ALU REGISTERS

•

MMU

•

HW MULTPLY/ACCUM

•

INTERRUPT CONTROL

•

16-WORD HW STACK

•

HARVARD ARCHITECTURE

MEMORY MODULE

CORE MODULES

CLOCK/CRYSTAL/

TIMER MODULE

•

INTERNAL 16MHz (MAX)

OSCILLATOR

•

EXTERNAL XTAL OSC

•

WATCHDOG TIMER

•

SCHEDULE TIMER

POWER MANAGEMENT

MODULE

•

+5V I/O REGULATOR

•

+3.3V ANALOG REGULATOR

•

+2.5V CORE REGULATOR

•

POWER-ON RESET

•

SUPPLY BROWNOUT DETECTORS

PERIPHERAL MODULES

GENERAL-PURPOSE

PERIPHERALS

•

3 16-BIT TIMER/PWMs

•

2 8-BIT I/O PORTS

•

UART WITH LIN 2.0 H/W

•

SPI INTERFACE

•

JTAG INTERFACE

•

12-BIT, 5-CHANNEL ADC

•

VOLTAGE REFERENCE

MAXQ7667

APPLICATION-SPECIFIC

PERIPHERALS

•

VARIABLE GAIN LNA

•

16-BIT SIGMA-DELTA ADC

•

DIGITAL BANDPASS FILTER

•

DIGITAL LOWPASS FILTER

•

LP FILTER FIFO

•

PLL FREQUENCY GENERATOR

•

BURST GENERATOR

UTILITY ROM

DATA RAM

4KB

(2KWORD)

FLASH ROM

32KB

(16KWORD)

Figure 2-1. MAXQ7667 Block Diagram

2.1.2 Instruction Set

As part of the MAXQ family, the MAXQ7667 uses the standard 16-bit MAXQ20 instruction set, with all instructions a fixed 16 bits in

length. A register-based, transport-triggered architecture allows all instructions to be coded as simple transfer operations. All instructions reduce to either writing an immediate value to a destination register or memory location or moving data between registers and/or

memory locations.

This simple top-level instruction decoding allows all instructions to be executed in a single cycle. Since all CPU operations are performed on registers only, any new functionality can be added by simply adding new register modules. The simple instruction set also

provides maximum flexibility for code optimization by a compiler.

___________________________________________________________________________________________________________ 2-4

Page 10

MAXQ7667 User’s Guide

2.1.3 Harvard Memory Architecture

As part of the MAXQ family, the MAXQ7667 core architecture is based on the MAXQ20 design, which implements a 16-bit internal databus and ALU. Program memory, data memory, and register space on the MAXQ7667 follow the Harvard architecture model. Each type

of memory is kept separate and is accessed by a separate bus, allowing different word lengths for different types of memory. Registers

may be either 8 or 16 bits in width. Program memory is 16 bits in width to accommodate the standard MAXQ 16-bit instruction set. Data

memory is also 16 bits in width but can be accessed in 8-bit or 16-bit modes for maximum flexibility.

The MAXQ7667 includes a flexible memory management unit (MMU), which allows code to be executed from either the program flash,

the utility ROM, or the internal data SRAM. Any of these three memory spaces may also be accessed in data space at any time, with

the single restriction that whichever physical memory area is currently being used as program space cannot be read from in data

space.

2.1.4 Register Space

Since all functions in the MAXQ family are accessed through registers, common functionality is provided through a common register

set. Many of these registers provide the equivalent of higher level op codes by directly accessing the arithmetic logic unit (ALU), the

loop counter registers, and the data pointer registers. Others, such as the interrupt registers, provide common control and configuration functions that are equivalent across all MAXQ microcontrollers.

The common register set, also known as the System Registers, includes the following:

• ALU access and control registers, including working accumulator registers and the processor status flags

• Two Data Pointers and a Frame Pointer for data memory access

• Autodecrementing Loop Counters for fast, compact looping

• Instruction Pointer and other branching control access points

• Stack Pointer and an access point to the 16-bit-wide dedicated hardware stack

• Interrupt vector, identification, and masking registers

The MAXQ7667 peripheral register space (modules 0 to 5) contains registers that access the following peripherals:

• Two general-purpose, 8-bit, I/O ports (P0, P1)

• LIN-compatible UART

• Serial peripheral interface (SPI)

• Hardware multiplier

• JTAG debug engine

• Three programmable Type 2 timer/counters

• Analog module

• Schedule timer

• Burst generator

• Echo receiver path

2-5 ___________________________________________________________________________________________________________

Page 11

MAXQ7667 User’s Guide

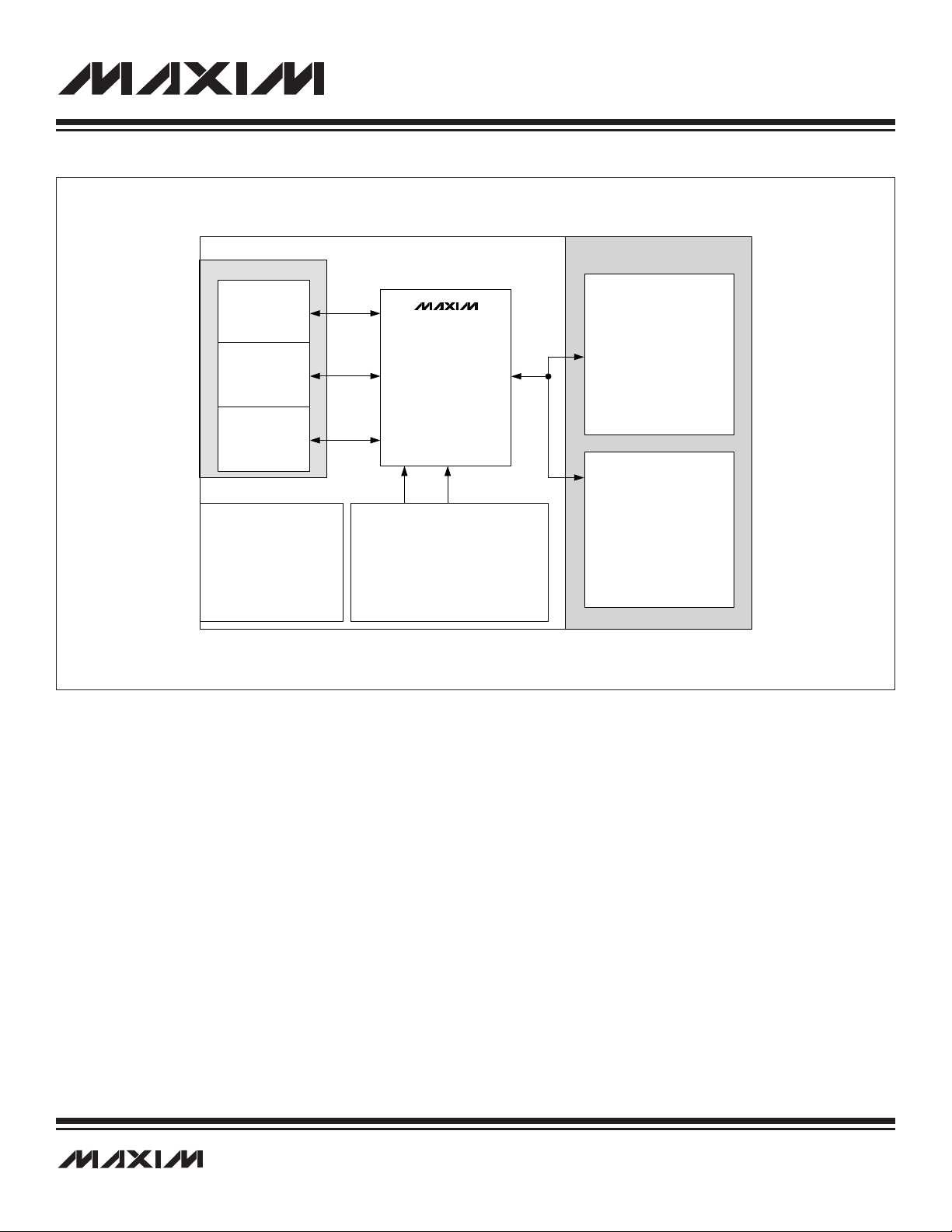

SYSTEM MODULES/

REGISTERS

PERIPHERAL MODULES/REGISTERS

DATA

MEMORY

dst

STACK

MEMORY

CKCN

WDCN

IC

ADDRESS

GENERATION

IP

SP

IC

LOOP COUNTERS

LC[η]

IIR

IMR

INTERRUPT

LOGIC

CLOCK CONTROL,

WATCHDOG TIMER

AND POWER MONITOR

BOOLEAN

VARIABLE

MANIPULATION

ACCUMULATORS

(16)

AP

APC

PSF

INSTRUCTION

DECODE

(SRC, DST TRANSPORT

DETERMINATION)

MUX

DATA POINTERS

DP[0], DP[1]

FP =

(BP + OFFS)

DPC

SC

MEMORY MANAGEMENT

UNIT (MMU)

PROGRAM

MEMORY

src

dst

src

GENERAL-

PURPOSE

I/O

TIMERS/

COUNTERS

UART

(LIN)

SPI

ANALOG

HARDWARE

MULTIPLIER

JTAG

DEBUG

ENGINE

SCHEDULE

TIMER

CLOCK

ULTRASONIC

SOUND

MEASUREMENT

2.2 Architecture

The MAXQ7667 architecture is designed to be modular and expandable. Top-level instruction decoding is extremely simple and based

on transfers to and from registers. The registers are organized into functional modules, which are in turn divided into the system register and peripheral register groups. Figure 2-2 illustrates the modular architecture.

Figure 2-2. MAXQ7667 Transport-Triggered Architecture

___________________________________________________________________________________________________________ 2-6

Page 12

MAXQ7667 User’s Guide

FORMAT DESTINATION SOURCE

f

dddddddssssssss

Memory access from the MAXQ7667 is based on a Harvard architecture with separate address spaces for program and data memory. The simple instruction set and transport-triggered architecture allow the MAXQ7667 to run in a nonpipelined execution mode where

each instruction can be fetched from memory, decoded, and executed in a single clock cycle. Data memory is accessed through one

of three data pointer registers. Two of these data pointers, DP[0] and DP[1], are stand-alone 16-bit pointers. The third data pointer, FP,

is composed of a 16-bit base pointer (BP) and an 8-bit offset register (OFFS). All three pointers support postincrement/decrement functionality for read operations and preincrement/decrement for write operations. For the Frame Pointer (FP = BP[OFFS]), the increment/decrement operation is executed on the OFFS register and does not affect the base pointer (BP). Stack functionality is provided

by dedicated memory with a 16-bit width and depth of 16. An on-chip memory management unit (MMU) is accessible through system

registers to allow logical remapping of physical program and data spaces, and thus facilitates in-system programming and fast access

to data tables, arrays, and constants physically located in program memory.

2.2.1 Instruction Decoding

Every MAXQ7667 instruction is encoded as a single 16-bit word according to the format in Figure 2-3.

Figure 2-3. Instruction Word Format

Bit 15 (f) indicates the format for the source field of the instruction as follows:

• If f equals 0, the instruction is an immediate source instruction, and the source field represents an immediate 8-bit value.

• If f equals 1, the instruction is a register source instruction, and the source field represents the register that the source value will be

read from.

Bits 0 to 7 (ssssssss) represent the source for the transfer. Depending on the value of the format field, this can either be an immediate

value or a source register. If this field represents a register, the lower four bits contain the module specifier and the upper four bits contain the register index in that module.

Bits 8 to 14 (ddddddd) represent the destination for the transfer. This value always represents a destination register, with the lower four

bits containing the module specifier and the upper three bits containing the register subindex within that module.

Since the source field is 8 bits wide and 4 bits are required to specify the module, any one of 16 registers in that module may be specified as a source. However, the destination field has one less bit, which means that only eight registers in a module can be specified

as a destination in a single-cycle instruction.

While the asymmetry between source and destination fields of the op code may initially be considered a limitation, this space can be

used effectively. Firstly, since read-only registers will never be specified as destinations, they can be placed in the second eight locations in a module to give single-cycle read access. Secondly, there are often critical control or configuration bits associated with system and certain peripheral modules where limited write access is beneficial (e.g., watchdog-timer enable and reset bits). By placing

such bits in one of the upper 24 registers of a module, this write protection is added in a way that is virtually transparent to the assembly source code. Anytime that it is necessary to directly select one of the upper 24 registers as a destination, the prefix register PFX is

used to supply the extra destination bits. This prefix register write is inserted automatically by the assembler and requires one additional execution cycle.

The MAXQ7667 architecture is transport-triggered. This means that writing to or reading from certain register locations will also cause

side effects to occur. These side effects form the basis for the higher level op codes defined by the assembler, such as ADDC, OR,

JUMP, and so on. While these op codes are actually implemented as MOVE instructions between certain register locations, the encoding is handled by the assembler and need not be a concern to the programmer. The registers defined in the System Register and

Peripheral Register maps operate as described in the documentation; the unused "empty" locations are the ones used for these special cases.

The MAXQ7667 instruction set is designed to be highly orthogonal. All arithmetic and logical operations that use two registers can use

any register along with the accumulator. Data can be transferred between any two registers in a single instruction.

2-7 ___________________________________________________________________________________________________________

Page 13

MAXQ7667 User’s Guide

DESTINATION SET TO VALUE

SOURCE REGISTER SIZE

(BITS)

DESTINATION REGISTER

SIZE (BITS)

PREFIX SET?

HIGH 8 BITS LOW 8 BITS

88— Source [7:0]

8 16 No 00h Source [7:0]

8 16 Yes Prefix [7:0] Source [7:0]

16 8 — Source [7:0]

16 16 No Source [15:8] Source [7:0]

2.2.2 Register Space

The MAXQ7667 architecture provides a total of 16 register modules. Each of these modules contains 32 registers. Of these possible

16 register modules, only 13 are used on the MAXQ7667—seven for system registers and six for peripheral registers. The first eight

registers in each module may be read from or written to in a single cycle; the second eight registers may be read from in a single cycle

and written to in two cycles (by using the prefix register PFX); the last 16 registers may be read or written in two cycles (always requiring use of the prefix register PFX).

Registers may be either 8 or 16 bits in length. Within a register, any number of bits can be implemented; bits not implemented are fixed

at zero. Data transfers between registers of different sizes are handled as shown in Table 2-1.

• If the source and destination registers are both 8 bits wide, data is transferred bit to bit accordingly.

• If the source register is 8 bits wide and the destination register is 16 bits wide, the data from the source register is transferred

into the lower 8 bits of the destination register. The upper 8 bits of the destination register are set to the current value of the prefix register; this value is normally zero, but it can be set to a different value by the previous instruction if needed. The prefix register reverts back to zero after one cycle, so this must be done by the instruction immediately before the one that will be using

the value.

• If the source register is 16 bits wide and the destination register is 8 bits wide, the lower 8 bits of the source are transferred to

the destination register.

• If both registers are 16 bits wide, data is copied bit to bit.

Table 2-1. Register-to-Register Transfer Operations

The above rules apply to all data movements between defined registers. Data transfer to/from undefined register locations has the following behavior:

• If the destination is an undefined register, the MOVE is a dummy operation but may trigger an underlying operation according

to the source register (e.g., @DP[n]--).

• If the destination is a defined register and the source is undefined, the source data for the transfer will depend upon the source module width. If the source is from a module containing 8-bit or 8-bit and 16-bit source registers, the source data will be equal to the prefix data concatenated with 00h. If the source is from a module containing only 16-bit source registers, 0000h source data is used for

the transfer.

The 16 available register modules are broken up into two different groups. The low six modules (specifiers 0h through 5h) are known

as the Peripheral Register modules, while the high 10 modules (specifiers 6h to Fh) are known as the System Register modules. These

groupings are descriptive only, as there is no difference between accessing the two register groups from a programming perspective.

The System Registers define basic functionality that remains the same across all products based on the MAXQ architecture. This

includes all register locations that are used to implement higher-level op codes as well as the following common system features.

• ALU (MAXQ20: 16 bits) and associated status flags (zero, equals, carry, sign, overflow)

• Eight working accumulator registers (MAXQ20: 16-bit width), along with associated control registers

• Instruction pointer

• Registers for interrupt control, handling, and identification

• Autodecrementing loop counters for fast, compact looping

• Two data pointer registers and a frame pointer for data memory access

___________________________________________________________________________________________________________ 2-8

Page 14

MAXQ7667 User’s Guide

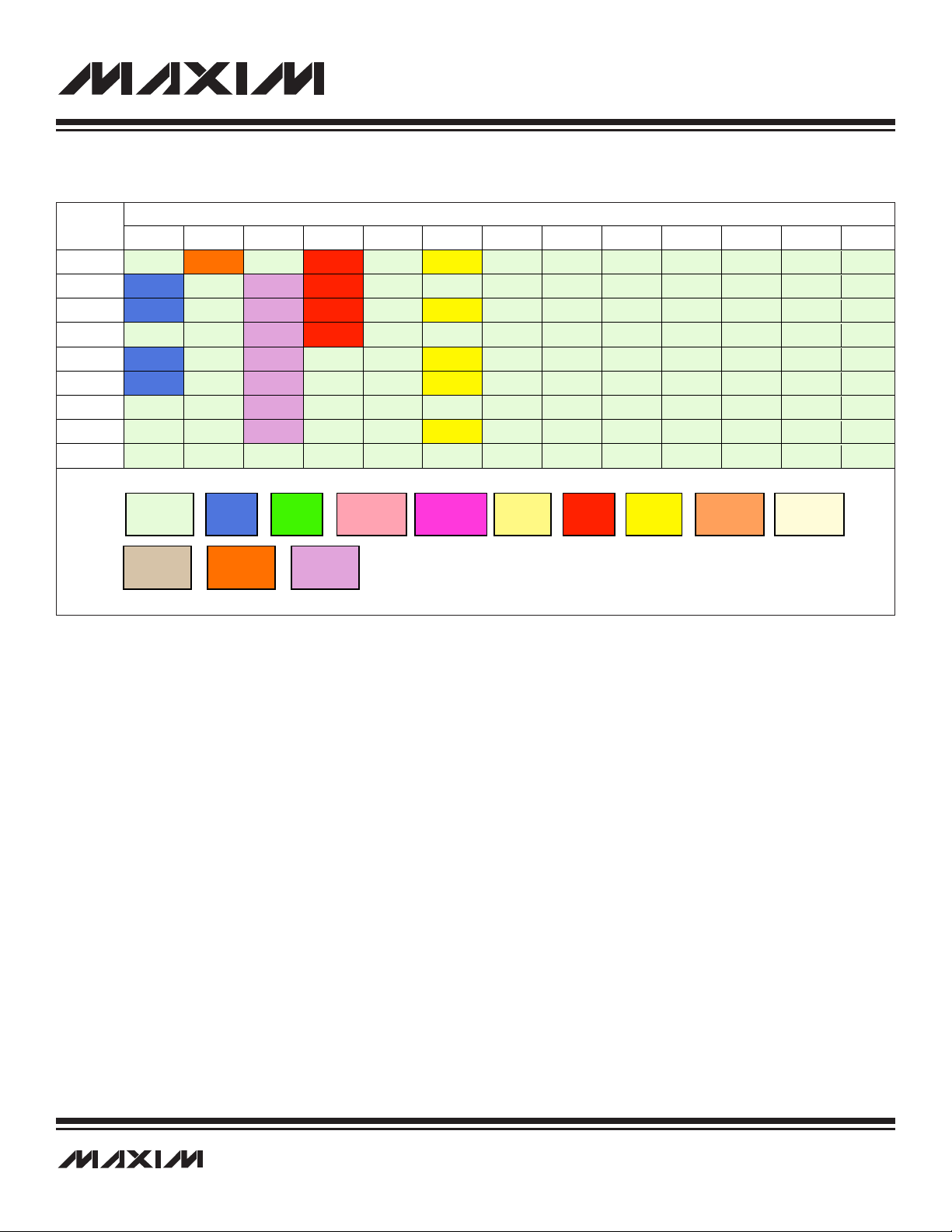

MODULE NAME (BASE SPECIF IER)

REGISTER

INDEX

M0 M1 M2 M3 M4 M5 M8 M9 M11 M12 M13 M14 M15

00h PO0 MCNT T2CNA0 T2CNA2 BPH AP A[0] PFX[0] IP

01h PO1 MA T2H0 T2H2 BTRN APC A[1] PFX[1] SP

02h MB T2RH 0 T2RH2 SARC A[2] PFX[2] IV

03h EIF0 MC2 T2CH0 T2CH2 RCVC A[3] PFX[ 3] OFFS DP0

04h EIF1 MC1 T2CNA1 PLLF PSF A[4] PFX[4] DPC

05h MC0 T2H1 C NT1 AIE IC A[5] PFX[5] GR

06h SPIB T2RH1 SCON CMPC IMR A[6] PFX[6] LC0 GRL

07h SPICN T2CH 1 SBUF CMPT A[7] PFX[7] LC1 BP DP1

08h PI0 SPIC F T2CNB0 T2CNB2 ASR SC A[8] GRS

09h PI1 SPICK T2V0 T2V2 SARD A[9] GRH

0Ah T2R0 T2R2 LPFC A[10] GRXL

0Bh EIE0 T2C0 T2C2 OSCC IIR A[11] FP

0Ch EIE1 MC1R T2CNB1 FSTAT BPFI A[12]

0Dh MC0R T2V1 ERRR BPFO A[13]

0Eh SCNT T2R1 CHKSUM LPFD CKCN A[14]

0Fh STIM T2C1 ISVEC LPFF WDCN A[15]

10h PD0 SALM T2CFG0 T2CFG2 APE

11h PD1 FPC TL T2CFG1 STA 0

12h SMD FGAIN

13h EIES0 FCON B1COEF

14h EIES1 CNT0 B2COEF

15h CNT2 B3COEF

16h IDFB A2A

The MAXQ7667 peripheral register space (modules 0 to 5) contains registers that access the following peripherals:

• Two general-purpose, 8-bit, I/O ports (P0, P1)

• External interrupts (up to 16)

• Three programmable Type 2 timer/counters

• LIN-compatible UART interface

• SPI

• Analog module (SAR ADC and ultrasonic measurement)

• Hardware multiplier

• JTAG debug engine

• Schedule timer

The lower 8 bits of all registers in modules 0 to 5 (as well as the AP module M8) are bit addressable.

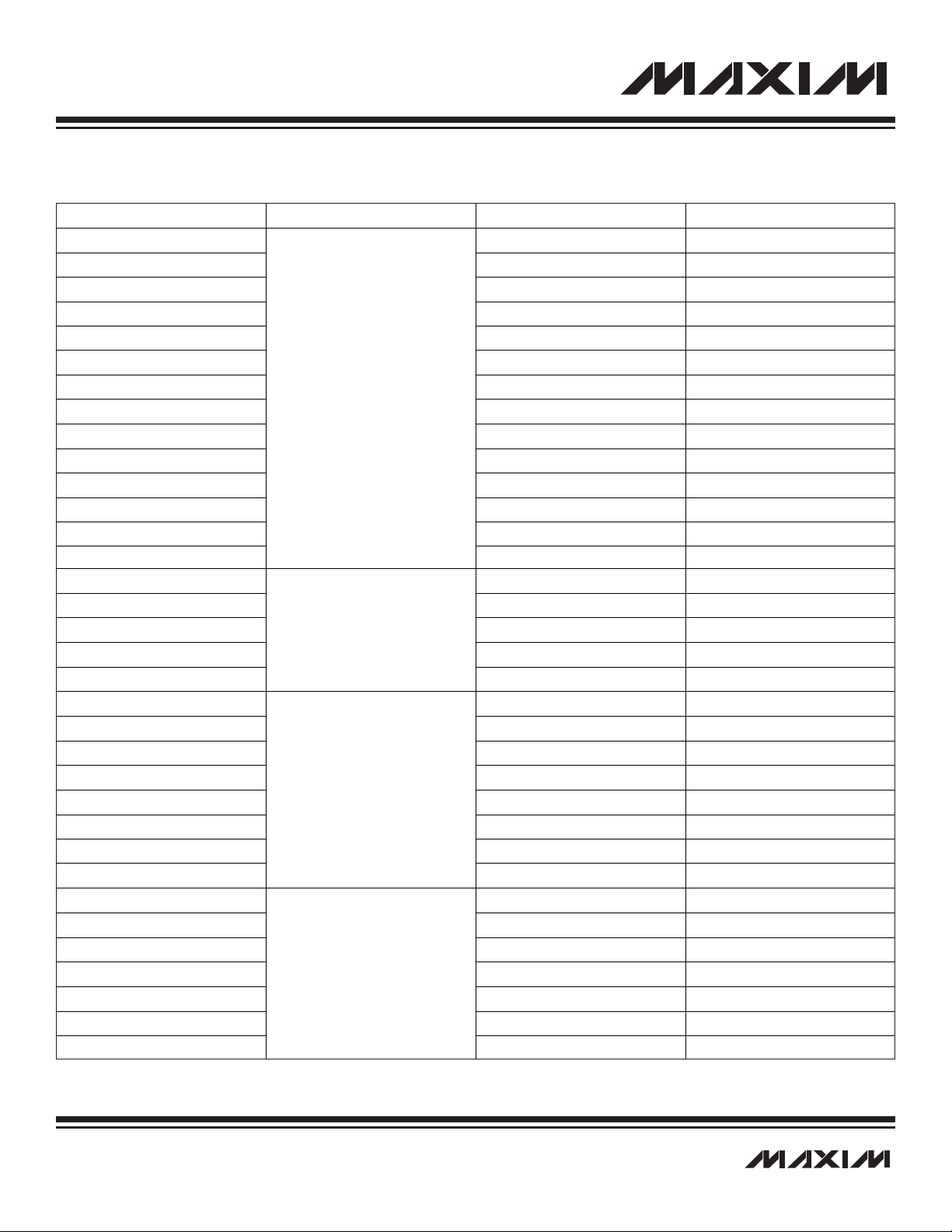

Table 2-2. MAXQ7667 Register Modules

2-9 ___________________________________________________________________________________________________________

Page 15

MODULE NAME (BASE SPECIF IER)

REGISTER

INDEX

M0 M1 M2 M3 M4 M5 M8 M9 M11 M12 M13 M14 M15

17h RCTRM† SADDR A2B

18h PS0 ICDT0 SADEN

19h PS1 ICDT1 BT A2D

1Ah ICDC T MR

1Bh PR0 ICDF A3A

1Ch PR1 ID0 ICDB A3B

1Dh ID1 ICDA

1Eh ICDD A3D

1Fh

RESERVE D

OR

OPCOD E

PORT

PINS

(GPIO)

SPI

INTERR U PT

CONTRO L

HARDWA RE

MULTIP LIE R

TIMERS

UART

(LIN)

ANALOG

I/O

ACC

ARRAY,

CONTRO L

OTHER

FUNCTIO N S

SCHED UL E

TIMER

TRIM

REGIST E R

JTAG

DEBUG

Table 2-2. MAXQ7667 Register Modules (continued)

MAXQ7667 User’s Guide

†The RCTRM register is a read/write register, but on power-up flash restores the factory-trimmed voltage. (Contact Maxim for write capability.)

2.2.3 Memory Organization

Beyond the internal register space, memory on the MAXQ7667 microcontroller is organized according to a Harvard architecture, with

a separate address space and bus for program memory and data memory. Stack memory is also separate and is accessed through

a dedicated register set.

To provide additional memory map flexibility, an MMU allows data memory space to be mapped into a predefined program memory segment, thus affording the possibility of code execution from data memory. Additionally, program memory space can be made accessible

as data space, allowing access to constant data stored in program memory. All memory is internal, and physical memory segments

(other than the stack and register memories) can be accessed as either program memory or as data memory, but not both at once.

2.2.3.1 Program Memory

The MAXQ7667 contains up to 16K x 16 (32KB) of flash memory, which normally serves as program memory. When executing from the

data SRAM or utility ROM, this memory is mapped to data space and can be used for lookup tables and similar functions. Flash memory mapped into data space can be read from directly, like any other type of data memory. However, writing to flash memory must be

done by calling the in-application functions provided by the utility ROM. The utility ROM provides routines to carry out the necessary

operations (erase, write) on flash memory.

Program memory begins at address 0000h and is contiguous through the internal program memory. The actual size of the on-chip program memory available for user application is product dependent. Given a 16-bit program address bus, the maximum program space

is 64KWords. Since the codewords are 16 bits, the program memory is therefore a 64K x 16 linear space.

Program memory is accessed directly by the program fetching unit and is addressed by the Instruction Pointer register. From an implementation perspective, system interrupts and branching instructions simply change the contents of the Instruction Pointer and force

the op code fetch from a new program location. The Instruction Pointer is direct read/write accessible by the user software; write access

to the Instruction Pointer will force program flow to the new address on the next cycle following the write. The contents of the Instruction

Pointer will be incremented by 1 automatically after each fetch operation. The Instruction Pointer defaults to 8000h, which is the start-

__________________________________________________________________________________________________________ 2-10

Page 16

MAXQ7667 User’s Guide

ing address of the utility ROM. The default IP setting of 8000h is assigned to allow initial in-system programming to be accomplished

with utility ROM code assistance. The utility ROM code interrogates a specific register bit in order to decide whether to execute in-system programming or jump immediately to user code starting at 0000h. The user code reset vector should always be stored in the lowest bytes of the program memory.

2.2.3.2 Utility ROM

A utility ROM (4K x 16) is normally placed in the upper 32KWord program memory space starting at address 8000h. This utility ROM

potentially provides the following system utility functions:

• Reset vector

• Bootstrap function for system initialization

• In-application programming

• In-circuit debug

Following each reset, the processor automatically starts execution at address 8000h in the utility ROM, allowing ROM code to perform

any necessary system support functions.

After a reset, the MAXQ7667 instruction pointer jumps to the ROM bootloader (0x8000). At this point the password location gets

checked for a valid entry. If the password space (0x0010 to 0x001F) in flash is populated by all 0s or 1s (implying that no password

has been set), the PWL bit (in SC register) is set to 0, allowing access to all the bootloader functions. Otherwise, the PWL bit gets set

to 1, preventing access to the password-protected family of commands (more on this later) and eventually the user must provide the

password to clear PWL to access all the bootloader functions.

The processor then looks for a request from the JTAG port. The JTAG port is established as the programming port before the MAXQ7667

is released from reset. While the MAXQ7667 is in reset, the SPE bit is set to 1 via the JTAG/TAP port. If the request is valid (i.e., SPE =

1, PSS = 00), the processor establishes communication between the ROM bootloader and the JTAG port. Otherwise, the UART is monitored for an autobaud character: 0x0D (carriage return). If the autobaud character is detected, the UART is established as the bootloader communication port and the MAXQ7667 responds with 0x3E. 0x3E is the acknowledgement that a loader command has been

completed. After this, some or all of the bootloader functions are accessible through the UART, depending on password settings.

The processor jumps to the flash program space 0x0000 and starts executing application code when there is no JTAG request and a

valid password is found (PWL =1). The code execution also jumps to 0x0000 when the autobaud routine does not receive the 0x0D

character within the 5-second built-in wait.

It is still possible to load a new program through the UART or the JTAG, after the MAXQ7667 begins executing code in the flash program space. To load code through the JTAG would merely require resetting the device and holding the device in reset while the SPE

bit is set to 1 through the JTAG/TAP port, once the reset is released the device executes in the bootloader (SPE = 1, PSS = 00). To load

new code through the UART would require the application code to call the UARTloader function in the utility ROM, which eventually

passes control to the bootloader (more on this later).

If the MAXQ7667’s password-protection feature is being used, it is important to note that setting the PWL (password lock) bit to 0

makes the MAXQ7667 vulnerable to attacks. It is recommended that after a communication link is established between the host and

the MAXQ7667, the Password Match command (03h) be executed to access the password-protected family of commands.

2.2.3.3 Data Memory

The MAXQ7667 contains 2K x 16 (4096 bytes) of on-chip data SRAM that can be mapped into either program or data space. The contents of this SRAM are indeterminate after power-on reset, but are maintained during stop mode and across non-POR resets, as long

as the DVDD (CORE) supply stays within the acceptable range.

On-chip data memory begins at address x0000h and is contiguous through the internal data memory. Data memory is accessed via

indirect register addressing through a Data Pointer (@DP[n]) or Frame Pointer (@BP[OFFS]). The Data Pointer is used as one of the

operands in a MOVE instruction. If the Data Pointer is used as source, the core performs a Load operation that reads data from the

data memory location addressed by the Data Pointer. If the Data Pointer is used as destination, the core executes a Store operation

that writes data to the data memory location addressed by the Data Pointer. The Data Pointer can be directly accessed by the user

software.

The core incorporates two 16-bit Data Pointers (DP[0] and DP[1]) to support data memory accessing. All Data Pointers support indirect addressing mode and indirect addressing with autoincrement or autodecrement. Data Pointers DP[0] and DP[1] can be used as

post increment/decrement source pointers by a MOVE instruction or pre increment/decrement destination pointers by a MOVE instruc-

2-11 __________________________________________________________________________________________________________

Page 17

MAXQ7667 User’s Guide

tion. Using Data Pointer indirectly with "++" will automatically increase the content of the active Data Pointer by 1 immediately following the execution of read data transfer (@DP[n]++) or immediately preceding the execution of a write operation (@++DP[n]). Using

Data Pointer indirectly with "--" will decrease the content of the active Data Pointer by 1 immediately following the execution of read

data transfer (@DP[n]--) or immediately preceding the execution of a write operation (@--DP[n]).

The Frame Pointer (BP[OFFS]) is formed by 16-bit unsigned addition of Frame Pointer Base Register (BP) and Frame Pointer Offset

Register (OFFS). Frame Pointer can be used as a post increment/decrement source pointer by a MOVE instruction or as a pre increment/decrement destination pointer. Using Frame Pointer indirectly with "++" (@BP[++OFFS] for a write or @BP[OFFS++] for a read) will

automatically increase the content of the Frame Pointer Offset by 1 immediately before or after the execution of data transfer depending

upon whether it is used as a destination or source pointer respectively. Using Frame Pointer indirectly with "--" (@BP[--OFFS] for a write or

@BP[OFFS--] for a read) will decrease the content of the Frame Pointer Offset by 1 immediately before/after execution of data transfer

depending upon whether it is used as a destination or source pointer respectively. Note that the increment/decrement function affects the

content of the OFFS register only, while the contents of the BP register remain unaffected by the borrow/carry out from the OFFS register.

A data memory cycle contains only one system clock period to support fast internal execution. This allows read or write operations on

SRAM to be completed in one clock cycle. Data memory mapping and access control are handled by the MMU. Read/write access to

the data memory can be in word or in byte.

When using the in-circuit debugging features of the MAXQ7667, the top 32 bytes (bytes 0x7D0 to 0x7FF) of the SRAM must be reserved

for saved state storage and working space for the debugging routines in the utility ROM. If in-circuit debug will not be used, the entire

SRAM is available for application use.

2.2.3.4 Stack Memory

The MAXQ7667 provides a 16 x 16 hardware stack to support subroutine calls and system interrupts. A 16-bit wide on-chip stack is

provided by the MAXQ7667 for storage of program return addresses and general-purpose use. The stack is used automatically by the

processor when the CALL, RET, and RETI instructions are executed and when an interrupt is serviced; it can also be used explicitly to

store and retrieve data by using the @SP- - source, @++SP destination, or the PUSH, POP, and POPI instructions. The POPI instruction acts identically to the POP instruction except that it additionally clears the INS bit.

The width of the stack is 16 bits to accommodate the instruction pointer size. The stack depth is 16 for the MAXQ7667. As the stack

pointer register SP is used to hold the index of the top of the stack, the maximum size of the stack allowed is defined by the number

of bits defined in the SP register (e.g., 4 bits for stack depth of 16).

On reset, the stack pointer SP initializes to the top of the stack (e.g. 0Fh for a 16-word stack). The CALL, PUSH, and interrupt vectoring operations increment SP and then store a value at @SP. The RET, RETI, POP, and POPI operations retrieve the value at @SP and

then decrement SP.

As with the other RAM-based modules, the stack memory is initialized to indeterminate values upon reset or power-up. Stack memory

is dedicated for stack operations only and cannot be accessed through program or data address spaces.

When using the in-circuit debugging features of the MAXQ7667, one word of the stack must be reserved to store the return location

when execution branches into the debugging routines in the utility ROM. If in-circuit debug will not be used, the entire stack is available for application use.

__________________________________________________________________________________________________________ 2-12

Page 18

MAXQ7667 MEMORY MAP (DEFAULT CONDITION, UPA = 0)

0x0000

0x8000

0x9000

0x800

DATA MEMORY

0

15

LOGICAL SPACE

0xFFFF

PHYSICAL PROGRAM

(P0)

UTILITY ROM

LOGICAL SPACE

0x0000

0x8000

0x4000

0xA000

0xFFFF

0xA800

0x9000

PROGRAM MEMORY

15 0

LOGICAL SPACE

PHYSICAL DATA

MAXQ7667 User’s Guide

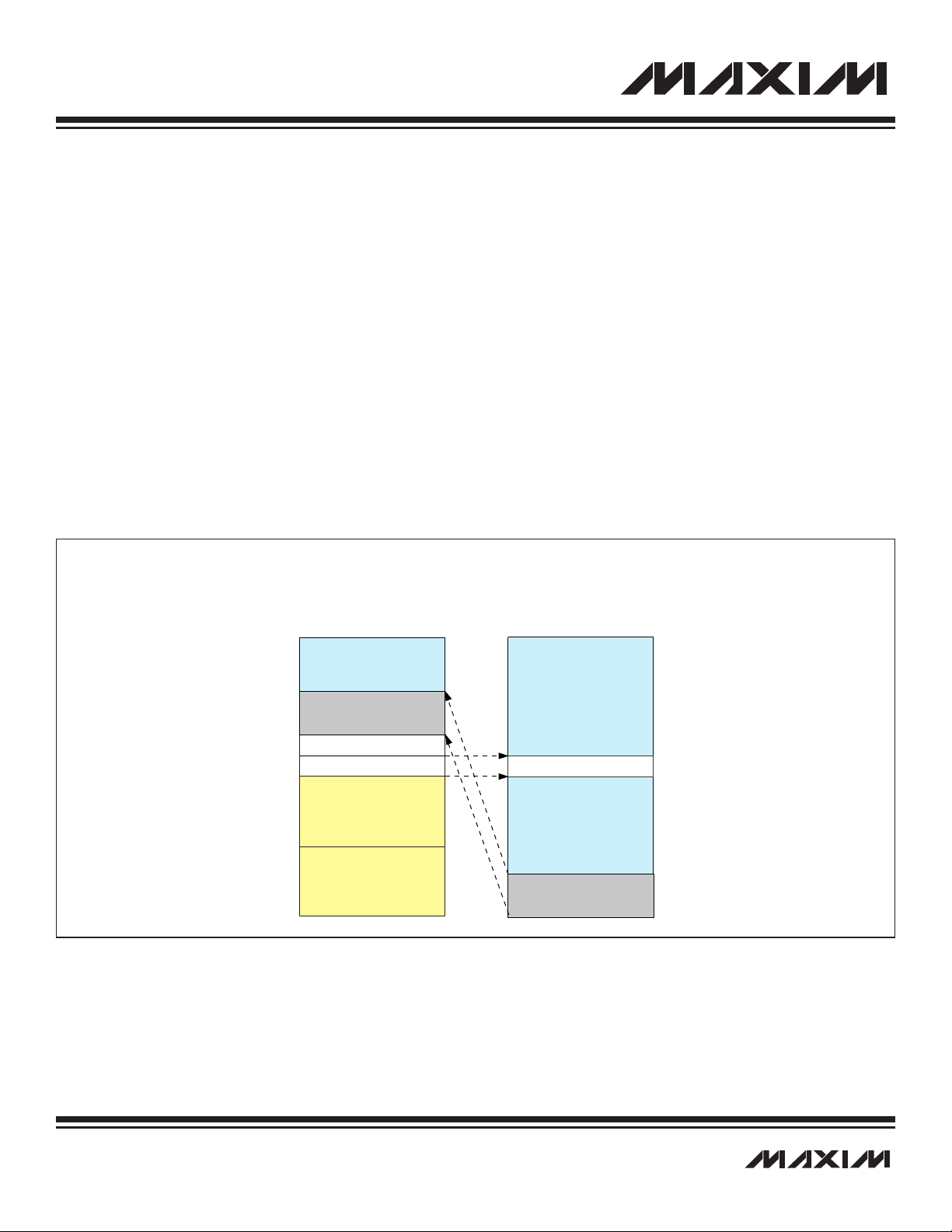

2.2.3.5 Pseudo-Von Neumann Memory Mapping

The MAXQ7667 supports a pseudo-Von Neumann memory structure that can merge program and data into a linear memory map. This

is accomplished by mapping the data memory into the program space or mapping program memory segment into the data space. In

all MAXQ processors the program memory ranges from x0000h to x7FFFh is the normal user code segment, followed by the utility ROM

segment. The uppermost part of the 64KWord memory is the logical area for data memory when accessed as a code segment.

The program memory is logically divided into four program pages, in all MAXQ processors:

• P0 contains the lower 16KWords (available in MAXQ7667),

• P1 contains the second 16KWords (not available in MAXQ7667),

• P2 contains the third 16KWords (not available in MAXQ7667), and

• P3 contains the fourth 16KWords (not available in MAXQ7667).

The MAXQ7667 only has 16K of P0 space and hence the focus will be on P0.

The logical mapping of physical program memory page(s) into data space depends upon two factors: physical memory currently in

use for program execution; and word/byte data memory access selection. If execution is from the utility ROM, physical program memory page (P0) can logically be mapped to the upper half of data memory space. If logical data memory is used for execution, physical program memory page can logically be mapped to the lower half of data memory space.

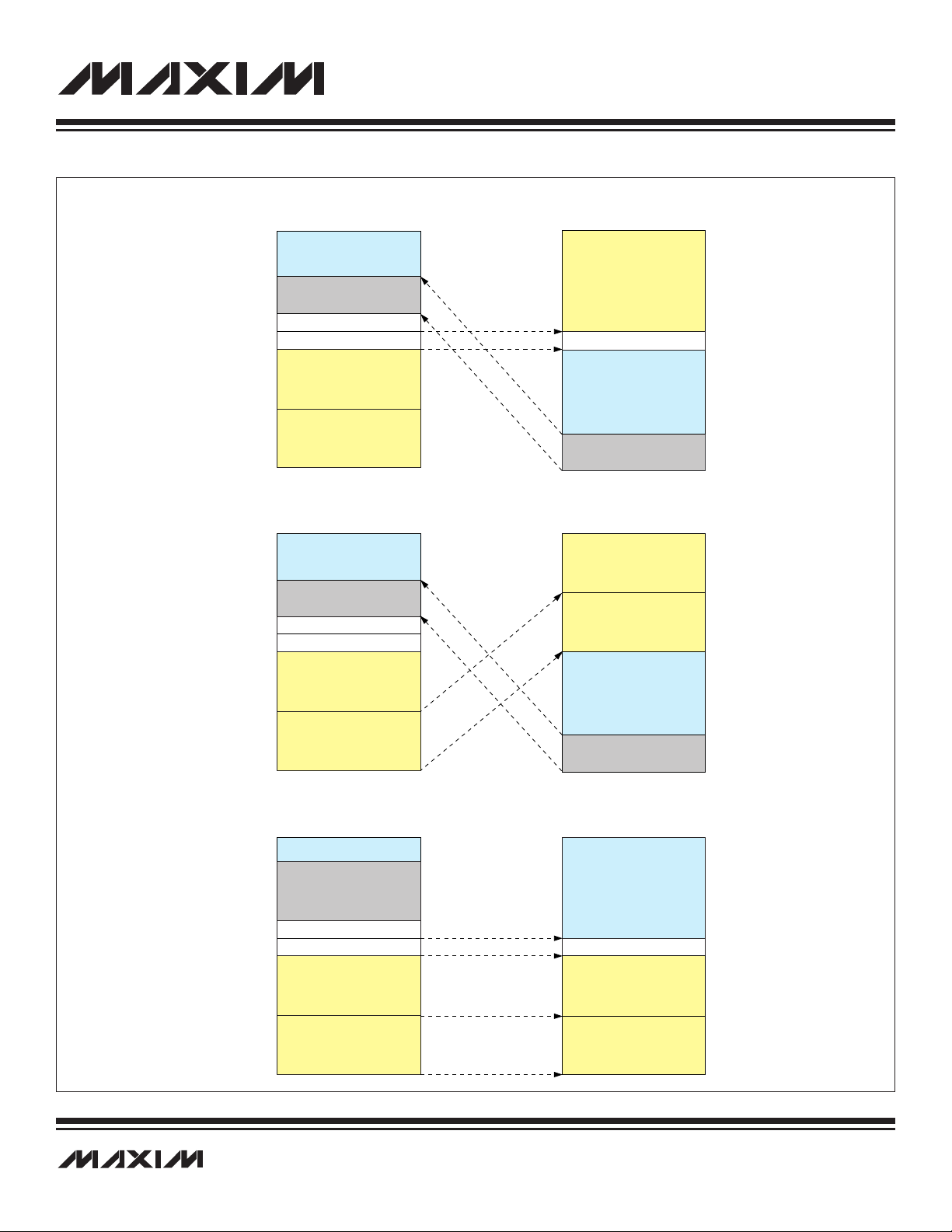

Figure 2-4 summarizes the default memory maps for this memory structure. The primary difference lies in the reset default settings for

the data pointer Word/Byte Mode Select (WBSn) bits. The WBSn bits of the MAXQ7667 default to word access mode (WBSn = 1).

Figure 2-4. Pseudo-Von Neumann Memory Map (MAXQ7667 Default)

2-13 __________________________________________________________________________________________________________

Page 19

MAXQ7667 User’s Guide

2.2.3.6 Pseudo-Von Neumann Memory Access

The pseudo-Von Neumann memory mapping is straightforward if there is no memory overlapping among the program, utility ROM, and

data memory segments. When accessing the program memory as data, the CDA bit can be used to select the program pages as needed. Full data memory access to the physical program memory pages is based on the assumption that the maximum physical data memory is in the range of 16K x 16. The other restriction for accessing the pseudo-Von Neumann map is that when program execution is in a

particular memory segment, the same memory segment cannot be simultaneously accessed as data.

When executing from the lower 16K program space (P0):

• The physical data memory is available for accessing as a code segment with offset at xA000h if the UPA bit is 0.

• Load and Store operations addressed to physical data memory are executed as normal.

• The utility ROM can be read as data, starting at x8000h of the data space.

When executing from the utility ROM:

• The lower 16K program space (P0) functions as normal program memory.

• The physical data memory is available for accessing as a code segment with offset at xA000h.

• Load and Store operations addressed to physical data memory are executed as normal.

• The 16K program space, P0, can be accessed as data, either in byte mode or word mode, with offset at 8000h.

When executing from the data memory:

• Program flows freely between the lower 16K user code (P0) and the utility ROM segment.

• The utility ROM can be accessed as data with offset at x8000h.

• The 16K program space, P0, can be accessed as data, either in byte mode or word mode, with offset at 0000h.

2.2.3.7 Data Alignment

To support merged program and data memory operation while maintaining efficiency on memory space usage, the data memory must

be able to support both byte-wide and word-wide accessing. Data is aligned in data memory as word, but the effective data address is

resolved to bytes. This data alignment allows direct program fetching in its native word size while maintaining accessibility at the byte

level. It is important to realize that this accessibility requires strict word alignment. All executable words must align to an even address

in byte mode. Care must be taken when updating the code segment in the unified data memory space as misalignment of words will

likely result in loss of program execution control. Worst yet, this situation may not be detected if the watchdog timer is also disabled.

Data memory is organized as two byte-wide memory banks with common word address decode but two 8-bit data buses. The data

memory will always be read as a complete word, independent of operation, whether program fetch or data access. The program

decoder always uses the full 16-bit word, whereas the data access can utilize a word or an individual byte.

In byte mode, data pointer hardware reads out the word containing the selected byte using the effective data word address pointer

(the least significant bit of the byte data pointer is not initially used). Then, the least significant data pointer bit functions as the byte

select that is used to place the target byte to the data path. For write access, data pointer hardware addresses a particular word using

the effective data word address while the least significant bit selects the corresponding data bank for write, leaving the contents of the

another memory bank unaffected.

__________________________________________________________________________________________________________ 2-14

Page 20

MAXQ7667 User’s Guide

2.2.3.8 Memory Management Unit

Memory allocation and accessing control for program and data memory can be managed by the memory management unit (MMU). A

single memory management unit option is discussed in this user’s guide, however the memory management unit implementation for

any given product depends upon the type and amount of memory addressable by the device. Users should consult the individual product data sheet(s) and/or user’s guide supplement(s) for detailed information.

Although supporting less than the maximum addressable program and data memory segments, the MMU implementation presented

provides a high degree of programming and access control flexibility. It supports the following:

• User program memory up to 32K x 16 (up to 64K x 16 with inclusion of UPA bit).

• Utility ROM up to 8K x 16.

• Data memory SRAM up to 16K x 16.

• In-system and in-application programming of embedded EEPROM, flash, or SRAM memories.

• Access to any of the three memory areas (SRAM, code memory, utility ROM) using the data memory pointers.

• Execution from any of the three memory areas (SRAM, code memory, factory written and tested utility-ROM routines).

Given these capabilities, the following rules apply to the memory map:

• A particular memory segment cannot be simultaneously accessed as both program and data.

• The offset address is xA000h when logically mapping data memory into the program space.

• The offset for logically mapping the utility ROM into the data memory space is x8000h.

• Program memory:

- The lower half of the program memory (P0 and P1) is always accessible, starting at x0000h. (

MAXQ7667.)

- The upper half of the program memory (P2 and P3) must be activated by setting the UPA bit to 1 when accessing for code

execution, starting at x8000h. (

- Setting the UPA bit to 1 disallows access to the utility ROM and logical data memory as program.

- Physical program memory pages (P0, P1, P2, P3) are logically mapped into data space based upon the memory segment

currently being used for execution, selection of byte/word access mode, and CDA1:0 bit settings (described in the

Von Neumann Memory Map

MAXQ7667 because it has only P0.)

• Data memory

- Access can be either word or byte.

- All 16 data pointer address bits are significant in either access mode (word or byte).

Note: P2 and P3 are not available in the MAXQ7667.)

and Pseudo-Von Neumann Memory Access sections). (Note: This does not apply to the

Note: P1 is not available in the

Pseudo-

2-15 __________________________________________________________________________________________________________

Page 21

x0000

x8000

x4000

DATA MEMORYPROGRAM MEMORY

0

15

LOGICAL SPACE

EXECUTING FROM LOGICAL DATA MEMORY (UPA = 0, ONLY P0 PRESENT)

LOGICAL UTILITY ROM

xFFFF

0x4000

PHYSICAL PROGRAM

(P0)

UTILITY ROM

CDA1 = 0

x0000

x8000

xA000

xFFFF

0xA800

15 0

LOGICAL SPACE

LOGICAL DATA MEMORY

x9000

LOGICAL SPACE

PHYSICAL DATA

x0000

x8000

xC000

0x800

DATA MEMORY

0

15

CDA1 = 0

EXECUTING FROM UTILITY ROM (UPA = 0, ONLY P0 PRESENT)

PHYSICAL PROGRAM

(P0)

UTILITY ROM

x0000

0x4000

x8000

xA000

x9000

xFFFF

0xA800

PROGRAM MEMORY

15 0

LOGICAL SPACE

LOGICAL DATA

MEMORY

LOGICAL SPACE

x0000

0x8000

0x9000

0x800

DATA MEMORYPROGRAM MEMORY

0

15

EXECUTING FROM PROGRAM SPACE (UPA = 0, ONLY P0 PRESENT)

UTILITY ROM

0xFFFF

0x4000

PHYSICAL PROGRAM

(P0)

PHYSICAL DATA

UTILITY ROM

0x0000

0x8000

0xA000

0xFFFF

0xA800

150

LOGICAL SPACE

LOGICAL DATA MEMORY

0x9000

LOGICAL SPACE

MAXQ7667 User’s Guide

Figure 2-5. Word Access Mode in MAXQ7667

__________________________________________________________________________________________________________ 2-16

Page 22

MAXQ7667 User’s Guide

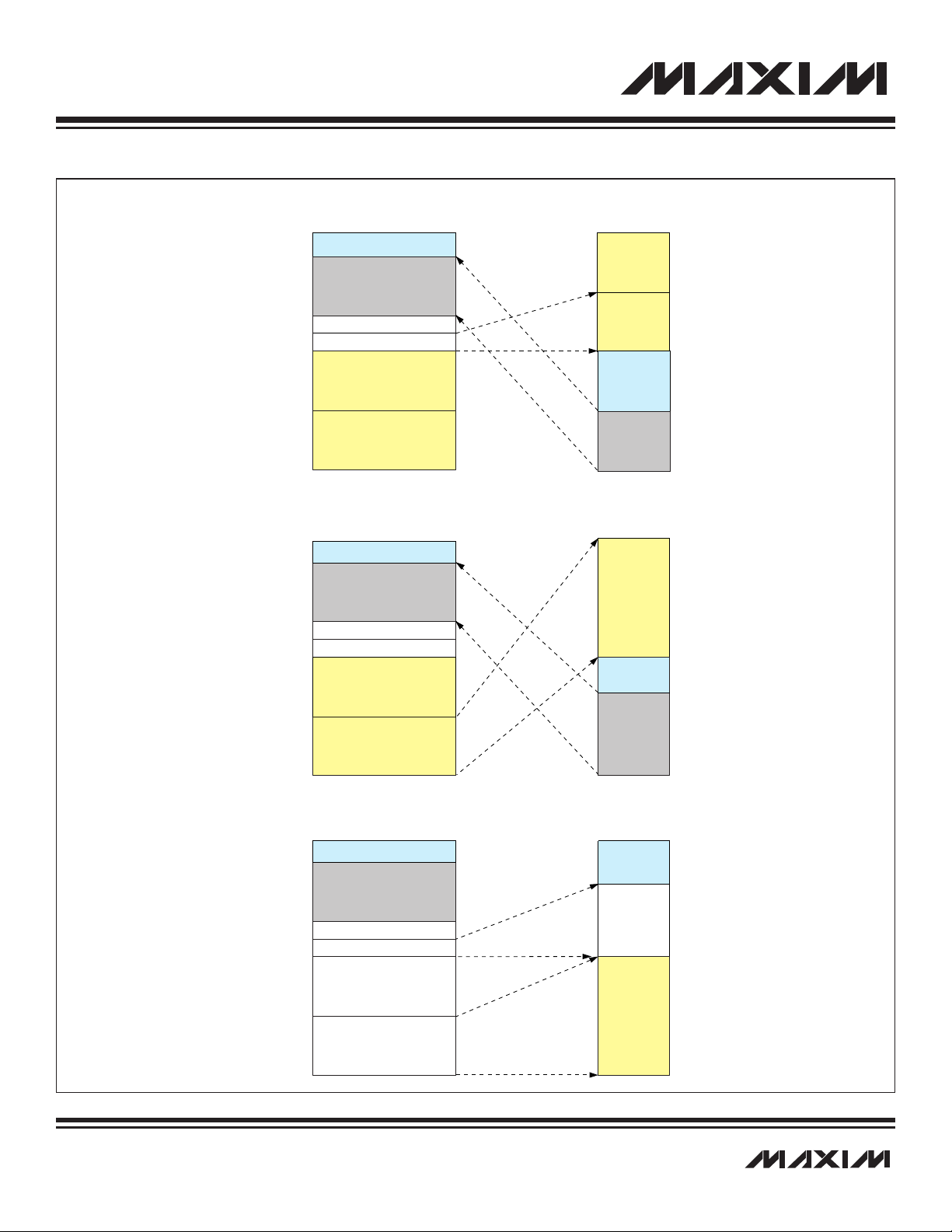

UTILITY ROM

PHYSICAL DATA

x0000

x8000

xA000

x9000

xFFFF

0xA800

0x4000

x0000

x8000

0x1000

xFFFF

DATA MEMORYPROGRAM MEMORY

150 07

CDA0 = 0

EXECUTING FROM UTILITY ROM (UPA = 0, ONLY P0 PRESENT)

LOGICAL SPACE

LOGICAL SPACE

LOGICAL SPACE

LOGICAL DATA

MEMORY

PHYSICAL PROGRAM

(P0)

0x4000

PHYSICAL PROGRAM

(P0)

UTILITY ROM

x0000

x8000

xA000

xFFFF

0xA800

x0000

x8000

xFFFF

xA000

DATA MEMORYPROGRAM MEMORY

15 0

07

CDA0 = 0

EXECUTING FROM LOGICAL DATA MEMORY (UPA = 0, ONLY P0 PRESENT)

LOGICAL SPACE

LOGICAL DATA

MEMORY

LOGICAL SPACE

x9000

LOGICAL SPACE

PHYSICAL DATA

0x0000

0x8000

0xA000

0x1000

DATA MEMORY

0

7

EXECUTING FROM PROGRAM SPACE (UPA = 0, ONLY P0 PRESENT)

PHYSICAL PROGRAM

(P0)

UTILITY ROM

0x0000

0x4000

0x8000

0xA000

0x9000

0xFFFF 0xFFFF

0xA800

PROGRAM MEMORY

150

LOGICAL SPACE

LOGICAL DATA

MEMORY

LOGICAL SPACE

Figure 2-6. Byte Access Mode in MAXQ7667

2-17 __________________________________________________________________________________________________________

Page 23

MAXQ7667 User’s Guide

2.2.4 Interrupts

The MAXQ7667 provides a single, programmable interrupt vector (IV) that can be used to handle internal and external interrupts.

Interrupts can be generated from system level sources (e.g., watchdog timer) or by sources associated with the peripheral modules

included in the specific MAXQ7667 microcontroller. Only one interrupt can be handled at a time, and all interrupts naturally have the

same priority. A programmable interrupt mask register allows software-controlled prioritization and nesting of high-priority interrupts.

2.2.4.1 Servicing Interrupts

For the MAXQ7667 to service an interrupt, interrupts must be enabled globally, modularly, and locally. The Interrupt Global Enable (IGE)

bit located in the Interrupt Control (IC) register acts as a global interrupt mask. This bit defaults to 0, and it must be set to 1 before any

interrupt takes place.

The local interrupt-enable bit for a particular source is in one of the peripheral registers associated with that peripheral module, or in a

system register for any system interrupt source. Between the global and local enables are intermediate per-module and system interrupt

mask bits. These mask bits reside in the Interrupt Mask system register. By implementing intermediate per-module masking capability in

a single register, interrupt sources spanning multiple modules can be selectively enabled/disabled in a single instruction. This promotes

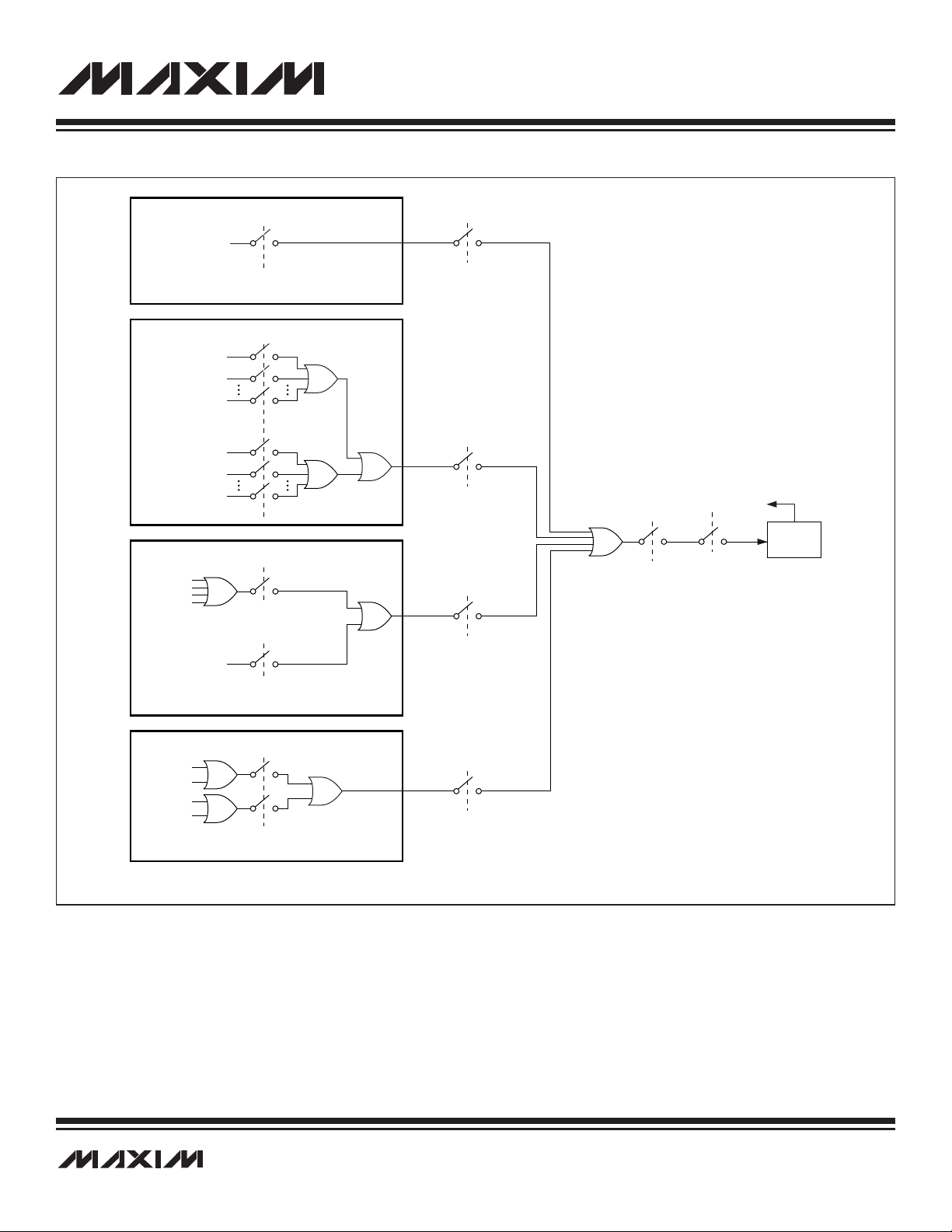

a simple, fast, and user-definable interrupt prioritization scheme. The interrupt source-enable hierarchy is illustrated in Figure 2-7.

When an interrupt condition occurs, its individual flag is set, even if the interrupt source is disabled at the local, module, or global level.

Interrupt flags must be cleared within the user interrupt routine to avoid repeated interrupts from the same source.

Since all interrupts vector to the address contained in the Interrupt Vector (IV) register, the Interrupt Identification Register (IIR) may be

used by the interrupt service routine to determine the module source of an interrupt. The IIR contains a bit flag for each peripheral module and one flag associated with all system interrupts; if the bit for a module is set, then an interrupt is pending that was initiated by

that module. If a module is capable of generating interrupts for different reasons, then peripheral register bits inside the module provide a means to differentiate among interrupt sources.

The Interrupt Vector (IV) register provides the location of the interrupt service routine. It may be set to any location within program memory. The IV register defaults to 0000h on reset or power-up, so if it is not changed to a different address, the user program must determine whether a jump to 0000h came from a reset or interrupt source. Note that the password starts at 0x0010, thus leaving 16 words

of programming space between the interrupt vector and the password, if 0000h is used as the IV value. (See Sections 12 and 13 for

details on password handling.)

2.2.4.2 Interrupt System Operation

The interrupt handler hardware responds to any interrupt event when it is enabled. An interrupt event occurs when an interrupt flag is

set. All interrupt requests are sampled at the rising edge of the clock and can be serviced by the processor one clock cycle later,

assuming the request does not hit the interrupt exception window. The one-cycle stall between detection and acknowledgement/servicing is due to the fact that the current instruction may also be accessing the stack. For this reason, the CPU must allow the current

instruction to complete before pushing the stack and vectoring to IV. If an interrupt exception window is generated by the currently executing instruction, the following instruction must be executed, so the interrupt service routine will be delayed an additional cycle.

Interrupt operation in the MAXQ7667 CPU is essentially a state machine generated long CALL instruction. When the interrupt handler

services an interrupt, it temporarily takes control of the CPU to perform the following sequence of actions:

1) The next instruction fetch from program memory is cancelled.

2) The return address is pushed on to the stack.

3) The INS bit is set to 1 to prevent recursive interrupt calls.

4) The instruction pointer is set to the location of the interrupt service routine (contained in the Interrupt Vector register).

5) The CPU begins executing the interrupt service routine.

Once the interrupt service routine completes, it should use the RETI instruction to return to the main program. Execution of RETI

involves the following sequence of actions:

1) The return address is popped off the stack.

2) The INS bit is cleared to 0 to re-enable interrupt handling.

3) The instruction pointer is set to the return address that was popped off the stack.

4) The CPU continues execution of the main program.

Pending interrupt requests will not interrupt an RETI instruction; a new interrupt will be serviced after first being acknowledged in the

execution cycle which follows the RETI instruction and then after the standard one stall cycle of interrupt latency. This means there will

be at least two cycles between back-to-back interrupts.

__________________________________________________________________________________________________________ 2-18

Page 24

MAXQ7667 User’s Guide

2.2.4.3 Synchronous vs. Asynchronous Interrupt Sources

Interrupt sources can be classified as either asynchronous or synchronous. All internal interrupts are synchronous interrupts. An internal

interrupt is directly routed to the interrupt handler that can be recognized in one cycle. All external interrupts are asynchronous interrupts

by nature. When the device is not in stop mode, asynchronous interrupt sources are passed through a 3-clock sampling/glitch filter circuit before being routed to the interrupt handler. The sampling/glitch filter circuit is running on the undivided source clock (i.e., before

PMME, CD[1:0]-controlled clock divide) such that the number of system clocks required to recognize an asynchronous interrupt request

depends upon the system clock divide ratio:

• if the system clock divide ratio is 1, the interrupt request is recognized after 3 system clock

• if the system clock divide ratio is 2, the interrupt request is recognized after 2 system clock (unavailable in MAXQ7667)

• if the system clock divide ratio is 4 or greater, the interrupt request is recognized after 1 system clock (unavailable in MAXQ7667)

An interrupt request with a pulse width less than three undivided clock cycles is not recognized. Note that the granularity of interrupt

source is at module level. Synchronous interrupts and sampled asynchronous interrupts assigned to the same module product a single interrupt to the interrupt handler.

External interrupts, when enabled, can be used as switchback sources from power management mode. There is no latency associated with the switchback because the circuit is being clocked by an undivided clock source versus the divide-by-256 system clock. For

the same reason, there is no latency for other switchback sources that do not qualify as interrupt sources.

2.2.4.4 Interrupt Prioritization by Software

All interrupt sources of the MAXQ7667 microcontroller naturally have the same priority. However, when CPU operation vectors to the programmed Interrupt Vector address, the order in which potential interrupt sources are interrogated is left entirely up to the user, as this

often depends upon the system design and application requirements. The Interrupt Mask system register provides the ability to knowingly block interrupts from modules considered to be of lesser priority and manually re-enable the interrupt servicing by the CPU (by setting INS = 0). Using this procedure, a given interrupt service routine can continue executing, only to be interrupted by higher priority

interrupts. An example demonstrating this software prioritization is provided in

Section 3.8: Handling Interrupts.

2.2.4.5 Interrupt Exception Window

An interrupt exception window is a noninterruptable execution cycle. During this cycle, the interrupt handler does not respond to any interrupt requests. All interrupts that would normally be serviced during an interrupt exception window are delayed until the next execution cycle.

Interrupt exception windows are used when two or more instructions must be executed consecutively without any delays in between.

Currently, there is a single condition in the MAXQ7667 microcontroller that causes an interrupt exception window: activation of the prefix (PFX) register.

When the prefix register is activated by writing a value to it, it retains that value only for the next clock cycle. For the prefix value to be

used properly by the next instruction, the instruction that sets the prefix value and the instruction that uses it must always be executed back to back. Therefore, writing to the PFX register causes an interrupt exception window on the next cycle. If an interrupt occurs

during an interrupt exception window, an additional latency of one cycle in the interrupt handling will be caused as the interrupt will

not be serviced until the next cycle.

2.2.4.6 MAXQ7667 Interrupt Sources

Table 2-2 lists all possible interrupt sources for the MAXQ7667, along with their corresponding module interrupt enable bits, local interrupt enable bits, and interrupt flags.

• Each module interrupt enable bit, when cleared to 0, will block interrupts originating in that module from being acknowledged.

When the module interrupt enable bit is set to 1, interrupts from that module are acknowledged (unless the interrupts have been

disabled globally).

• Each local interrupt enable bit, when cleared to 0, will disable the corresponding interrupt. When the local interrupt enable bit

is set to 1, the interrupt will be triggered whenever the interrupt flag is set to 1 (either by software or hardware).

• All interrupt flag bits cause the corresponding interrupt to trigger when the bit is set to 1. These bits are typically set by hardware and must be cleared by software (generally in the interrupt handler routine).

Note that for an interrupt to fire, the following five conditions must exist:

1) Interrupts must be enabled globally by setting IGE (IC.0) to 1.

2) The module interrupt enable bit for that interrupt source’s module must be set to 1.

2-19 __________________________________________________________________________________________________________

Page 25

MAXQ7667 User’s Guide

SYSTEM MODULES

MODULE 0

WDIF

(WATCHDOG)

EWDI

(LOCAL ENABLE)

IM1

(MODULE 1 ENABLE)

EIF0.0

EIE0.0–EIE0.5

(LOCAL ENABLES)

EIF0.1

EIF0.5

IM0

(MODULE 0 ENABLE)

IMS

(SYSTEM ENABLE)

MODULE 2

ET2L, ET2

(LOCAL ENABLES)

IM2

(MODULE 2 ENABLE)

IGE

(GLOBAL ENABLE)

NOTE: ONLY A FEW OF THE MANY POSSIBLE MAXQ PERIPHERAL MODULES ARE SHOWN IN THIS INTERRUPT HIERARCHY FIGURE.

INS

(INTERRUPT IN SERVICE)

INTERRUPT

VECTOR

EIF1.0

EIE1.0–EIE1.7

EIF1.1

EIF1.7

TC2L

TF2L

TCC2

TF2

MODULE 1

ESPII

(LOCAL ENABLE)

SPIC

SALIE

(LOCAL ENABLE)

SALMF

ROVR

WCOL

MODF

Figure 2-7. MAXQ7667 Interrupt Source Hierarchy Example

3) The local interrupt enable bit for that specific interrupt source must be set to 1.

4) The interrupt flag for that interrupt source must be set to 1. Typically, this is done by hardware when the condition that requires

interrupt service occurs.

5) The Interrupt In Service (INS) bit must be cleared to 0. This bit is set automatically upon vectoring to the interrupt handler

address and cleared automatically upon exit (RETI/POPI), so the only reason to clear this bit manually (inside the interrupt handler routine) is allow nested interrupt handling.

__________________________________________________________________________________________________________ 2-20

Page 26

MAXQ7667 User’s Guide

INTERRUPT MODU LE ENAB LE BIT LOC A L ENABLE BIT INTER R UPT FL AG

External Interrupt Port 0 0 EX0 (EIE0.0) IE0 (EIF0.0)

External Interrupt Port 0 1 EX1 (EIE0.1) IE1 (EIF0.1)

External Interrupt Port 0 2 EX2 (EIE0.2) IE2 (EIF0.2)

External Interrupt Port 0 3 EX3 (EIE0.3) IE3 (EIF0.3)

External Interrupt Port 0 4 EX4 (EIE0.4) IE4 (EIF0.4)

External Interrupt Port 0 5 EX5 (EIE0.5) IE5 (EIF0.5)

External Interrupt Port 1 0 EX0 (EIE1.0) IE0 (EIF1.0)

External Interrupt Port 1 1 EX1 (EIE1.1) IE1 (EIF1.1)

External Interrupt Port 1 2 EX2 (EIE1.2) IE2 (EIF1.2)

External Interrupt Port 1 3 EX3 (EIE1.3) IE3 (EIF1.3)

External Interrupt Port 1 4 EX4 (EIE1.4) IE4 (EIF1.4)

External Interrupt Port 1 5 EX5 (EIE1.5) IE5 (EIF1.5)

External Interrupt Port 1 6 EX6 (EIE1.6) IE6 (EIF1.6)

External Interrupt Port 1 7

IM0 (IMR.0)

EX7 (EIE1.7) IE7 (EIF1.7)

SPI Mode Fault ESPII (SPICF.7) MODF (SPICN.3)

SPI Write Coll is ion ESPII (SPICF.7) WCOL (SPI C N.4)

SPI Receive Overrun ESPII (SPICF.7) ROVR (SPICN .5)

SPI Transfer Complete ESPII (SPICF.7) SPIC (SPIC N .6)

Schedule Timer Alarm

IM1 (IMR.1)

SALIE (SC NT.7) SALMF (S C N T.6)

Timer 0—Low Compare ET2L (T2CNB0.7) T2CL (T2CNB0.0)

Timer 0—Low Overflow ET2L (T2CNB0.7) TF2L (T2CNB0.2)

Timer 0—Capture/Compare ET2 (T2NCA0.7) TCC2 (T2CNB0.1)

Timer 0—Overflow ET2 (T2NCA0.7) TF2 (T2CNB0.3)

Timer 1—Low Compare ET2L (T2CNB1.7) T2CL (T2CNB1.0)

Timer 1—Low Overflow ET2L (T2CNB1.7) TF2L (T2CNB1.2)

Timer 1—Capture/Compare ET2 (T2NCA1.7) TCC2 (T2CNB1.1)

Timer 1—Overflow

IM2 (IMR.2)

ET2 (T2NCA1.7) TF2 (T2CNB1.3)

Timer 2—Low Compare ET2L (T2CNB2.7) T2CL (T2CNB2.0)

Timer 2—Low Overflow ET2L (T2CNB2.7) TF2L (T2CNB2.2)

Timer 2—Capture/Compare ET2 (T2NCA2.7) TCC2 (T2CNB2.1)

Timer 2—Overflow ET2 (T2NCA2.7) TF2 (T2CNB2.3)

UART Mode Receive Interrupt IE ( S M D.2) RI (SCON0.0)

UART Mode Transm it Interrupt IE (SM D.2) TI (SCO N0.1)

LIN Mode Master or S lave Interrupt

IM3 (IMR.3)

INE (CNT0.4) INP (STA0.1)

Table 2-3. MAXQ7667 Interrupt Sources and Control Bits

2-21 __________________________________________________________________________________________________________

Page 27

MAXQ7667 User’s Guide

INTERRUPT MODU LE ENAB LE BIT LOC A L ENABLE BIT INTER R UPT FL AG

SAR ADC Data Ready SARIE (AIE.0) SARRDY (ASR.0)

Echo Envelope Lowpass Filter Output LPFIE (AIE.1) LPFRDY (ASR.1)

Echo Envelope Lowpass Filter FIFO

Full Interrupt

LFLIE (AIE.2) LPFFL (ASR.2)

Echo Envelope Comparator Interrupt CMPIE (AIE.3) CMPI (ASR.3)

AVDD Brownout Interrupt VABIE (AIE.4) VABI (ASR.4)

DVD D Brownout Interrupt VDBIE (AIE.5) VDBI (ASR.5)

DVD DIO Brownout Interrupt VIBIE (AIE.6) VIBI (ASR.6)

Crystal Oscillator Failure Interrupt

IM5 (IMR.5)

XTIE (AIE.7) XTI (ASR.7)

Table 2-3. MAXQ7667 Interrupt Sources and Control Bits (continued)

__________________________________________________________________________________________________________ 2-22

Page 28

MAXQ7667 User’s Guide

SECTION 3: PROGRAMMING

This section contains the following information:

3.1 Addressing Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.2 Prefixing Operations . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

3.3 Reading and Writing Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.3.1 Loading an 8-Bit Register with an Immediate Value . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.3.2 Loading a 16-Bit Register with a 16-Bit Immediate Value . . . . . . . . . . . . . . . . . . . . . .3-4

3.3.3 Moving Values Between Registers of the Same Size . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.3.4 Moving Values Between Registers of Different Sizes . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

3.3.4.1 8-Bit Destination

3.3.4.2 8-Bit Destination

3.3.4.3 16-Bit Destination

3.3.4.4 Low (16-Bit Destination)

3.3.4.5 High (16-Bit Destination)

3.4 Reading and Writing Register Bits . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.5 Using the Arithmetic and Logic Unit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.5.1 Selecting the Active Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.5.2 Enabling Autoincrement and Autodecrement . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.5.3 ALU Operations Using the Active Accumulator and a Source . . . . . . . . . . . . . . . . . . .3-9

3.5.4 ALU Operations Using Only the Active Accumulator . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.5.5 ALU Bit Operations Using Only the Active Accumulator . . . . . . . . . . . . . . . . . . . . . . .3-9