Page 1

19-5004; Rev 1; 6/10

EVALUATION KIT

AVAILABLE

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

General Description

The MAX97000 audio subsystem combines a mono

speaker amplifier with a stereo headphone amplifier and

an analog DPST switch. The headphone and speaker

amplifiers have independent volume control and on/off

control. The four inputs are configurable as two differential inputs or four single-ended inputs.

The entire subsystem is designed for maximum efficiency.

The high-efficiency 725mW Class D speaker amplifier

operates directly from the battery and consumes no more

than 1FA in shutdown mode. The Class H headphone

amplifier utilizes a dual-mode charge pump to maximize

efficiency while outputting a ground-referenced signal

that does not require output coupling capacitors.

The speaker amplifier incorporates a distortion limiter to

automatically reduce the volume level when excessive

clipping occurs. This allows high gain for low-level signals without compromising the quality of large signals.

All control is performed using the 2-wire, I2C interface.

The MAX97000 operates in the extended -40NC to +85NC

temperature range, and is available in the 2mm x 2mm,

25-bump WLP package (0.4mm pitch).

Applications

Cell Phones

Portable Multimedia Players

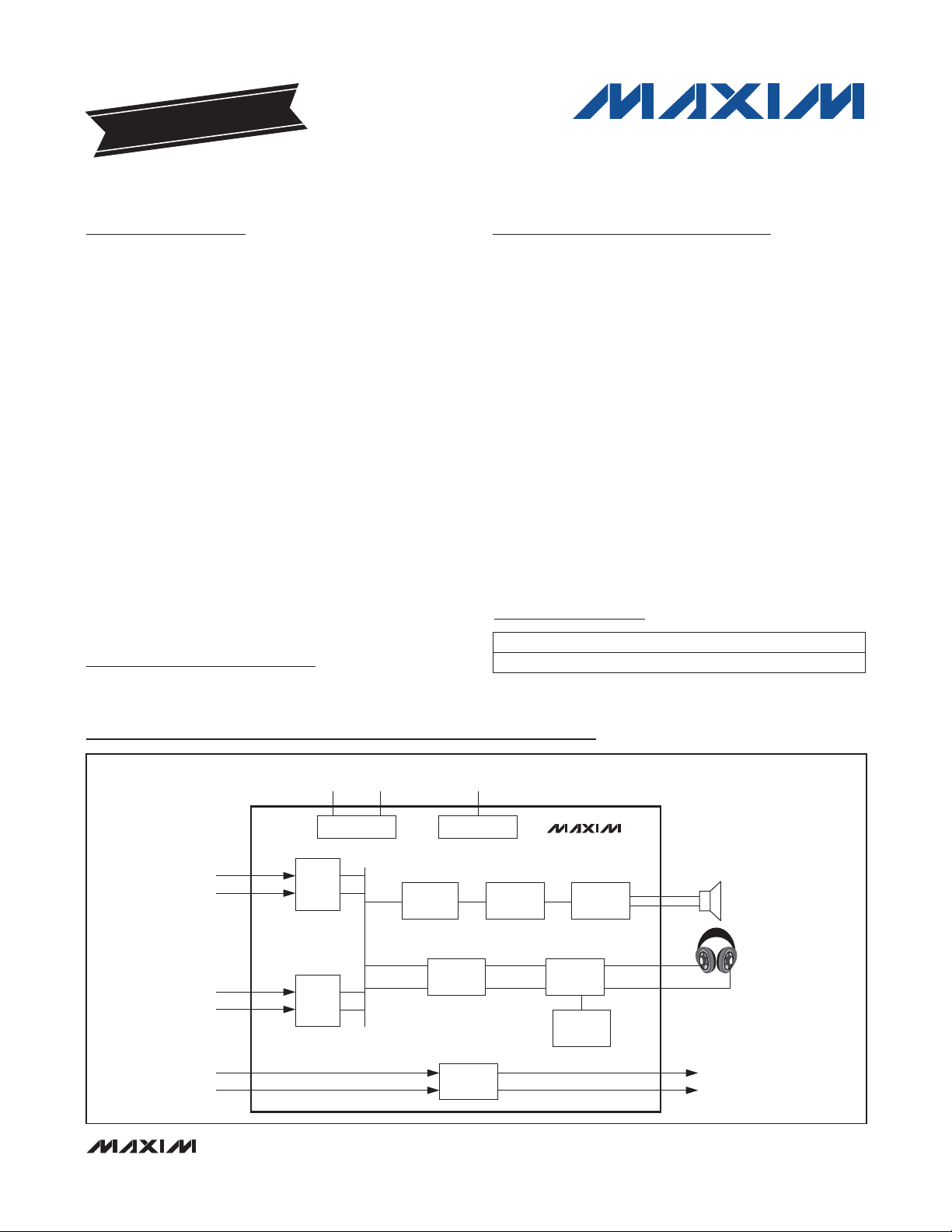

Simplified Block Diagram

Features

S 1.6V to 2.0V Headphone Supply Voltage

S 2.7V to 5.5V Speaker Supply Voltage

S Internal LDO Allows Single-Supply Operation

S 725mW Speaker Output (V

PVDD

= 3.7V, Z

SPK

= 8I

+ 68µH)

S 40mW/Channel Headphone Output (RHP = 16I)

S Low-Emission Class D Amplifier

S Efficient Class H Headphone Amplifier

S Ground-Referenced Headphone Outputs

S Two Stereo Single-Ended/Mono Differential Inputs

S Integrated Distortion Limiter (Speaker Outputs)

S Integrated DPST Analog Switch

S No Clicks and Pops

S TDMA Noise Free

S 2mm x 2mm, 25-Bump 0.4mm Pitch WLP Package

Ordering Information

PART TEMP RANGE PIN-PACKAGE

MAX97000EWA+

+Denotes a lead(Pb)-free/RoHS-compliant package.

-40NC to +85NC

25 WLP

MAX97000

BATTERY

2.7V TO 5.5V

1.8V

POWER SUPPLY

STEREO/

MONO

INPUT

STEREO/

MONO

INPUT

_______________________________________________________________ Maxim Integrated Products 1

LIMITER

CONTROL

VOLUME

SWITCH

I2C

VOLUME

MAX97000

CLASS D

AMPLIFIER

CLASS H

AMPLIFIER

CHARGE

PUMP

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Page 2

Audio Subsystem with Mono Class D Speaker

and Class H Headphone Amplifier

TABLE OF CONTENTS

General Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Simplified Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1

Table of Contents . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

MAX97000

Functional Diagram/Typical Application Circuit . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4

Absolute Maximum Ratings . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Electrical Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5

Digital I/O Characteristics. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

I2C Timing Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

Typical Operating Characteristics . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10

Pin Configuration . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Pin Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17

Detailed Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Signal Path . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18

Mixers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Class D Speaker Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19

Ultra-Low EMI Filterless Output Stage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Distortion Limiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Analog Switch . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Headphone Amplifier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

DirectDrive . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21

Charge Pump . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Class H Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

Low-Power Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

I2C Slave Address. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 22

I2C Registers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 23

2

Page 3

Audio Subsystem with Mono Class D Speaker

and Class H Headphone Amplifier

TABLE OF CONTENTS (CONTINUED)

Mixers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 24

Volume Control . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 25

Distortion Limiter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Power Management . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 27

Charge-Pump Control. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

I2C Serial Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Bit Transfer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

START and STOP Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Early STOP Conditions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Slave Address . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 28

Acknowledge . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Write Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 29

Read Data Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 30

Applications Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Filterless Class D Operation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

RF Susceptibility . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Component Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Optional Ferrite Bead Filter . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Input Capacitor. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 31

Charge-Pump Capacitor Selection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Charge-Pump Flying Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Charge-Pump Holding Capacitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Supply Bypassing, Layout, and Grounding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

WLP Applications Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 32

Package Information. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 33

Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 34

MAX97000

3

Page 4

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

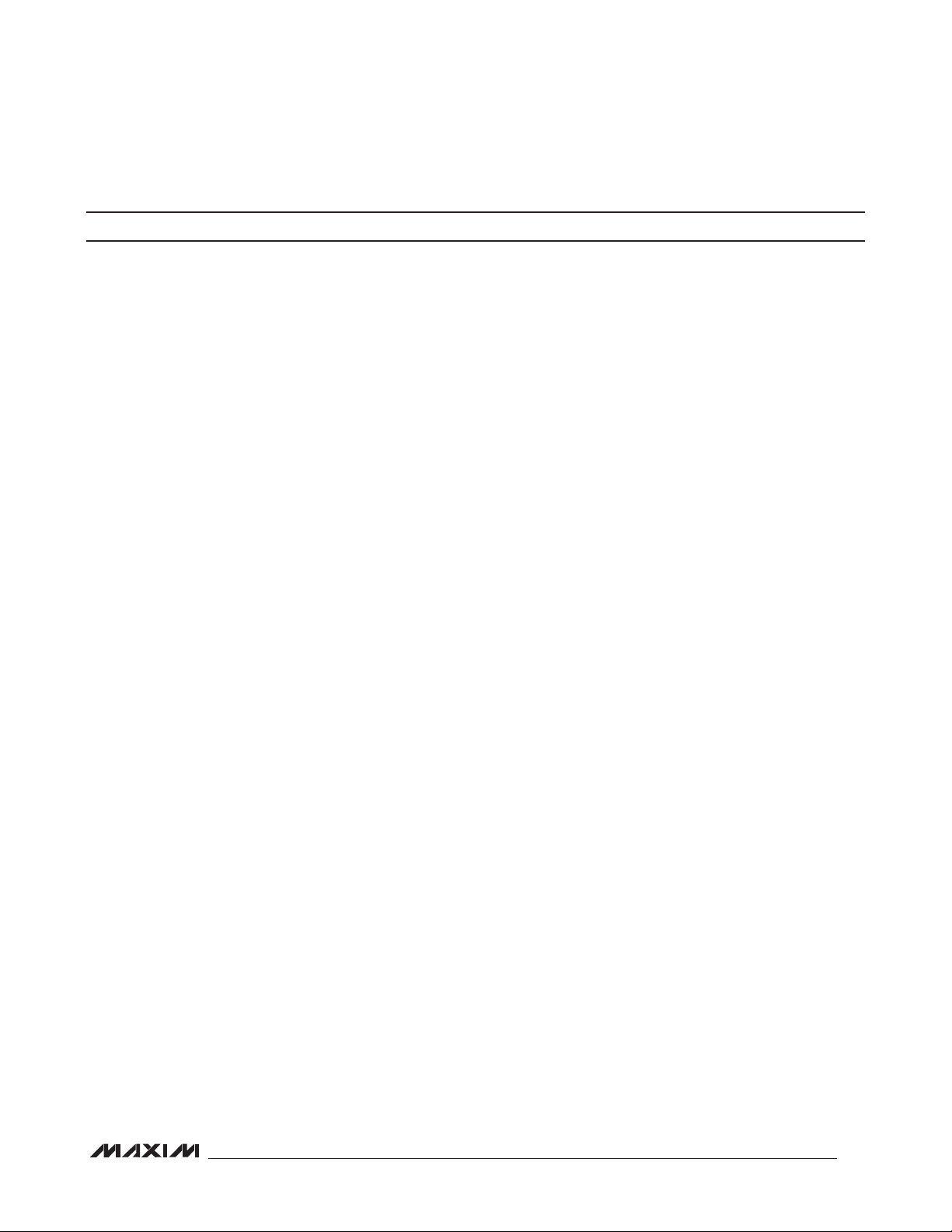

Functional Diagram/Typical Application Circuit

OPTIONAL

1.6V TO 2.0V

2.5V TO 5.5V

2.7V TO 5.5V

MAX97000

0.47µF

OPTIONAL

0.47µF

OPTIONAL

0.47µF

OPTIONAL

0.47µF

OPTIONAL

INA1

INA2

INB1 D4

INB2 D5

COM1 D2

10µF

PGAINA

-6dB TO +18dB

E4

PGAINA

-6dB TO +18dB

E5

+

PGAINB

-6dB TO +18dB

PGAINB

-6dB TO +18dB

+

1µF 1µF 1µF 10µF

LDOIN

B2

HPLVOL:

-64dB TO +6dB

HPRVOL:

-64dB TO +6dB

SPKVOL:

-30dB TO +20dB

PVDD

C1

CLASS D

PVDD

+12dB

PGND

HPVDD

CLASS H

0/3dB

HPVSS

HPVDD

CLASS H

0/3dB

HPVSS

SPKEN

BIAS

HPLEN

HPREN

THD LIMITER

THDCLP

INADIFF

INBDIFF

VDD

B1

LDO

M U X

LPMODE

M I X

HPLMIX

M I X

HPRMIX

M I X

SPKMIX

ANALOG SWITCHES

C5

BIAS

1µF

HPLB5

HPRA5

E1

OUTP

OUTN

D1

NC1E2

COM2 D3

SDA B3

SCL B4

SHDN

VDD

2

I

C

INTERFACE/

SHUTDOWN

C4

C3

GND

SWEN

MAX97000

C2

PGND

A1

C1P

1µF

VDD

CHARGE PUMP

A2

A3

HPVDD HPVSS

C1N

1µF 1µF

NC2E3

A4

4

Page 5

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

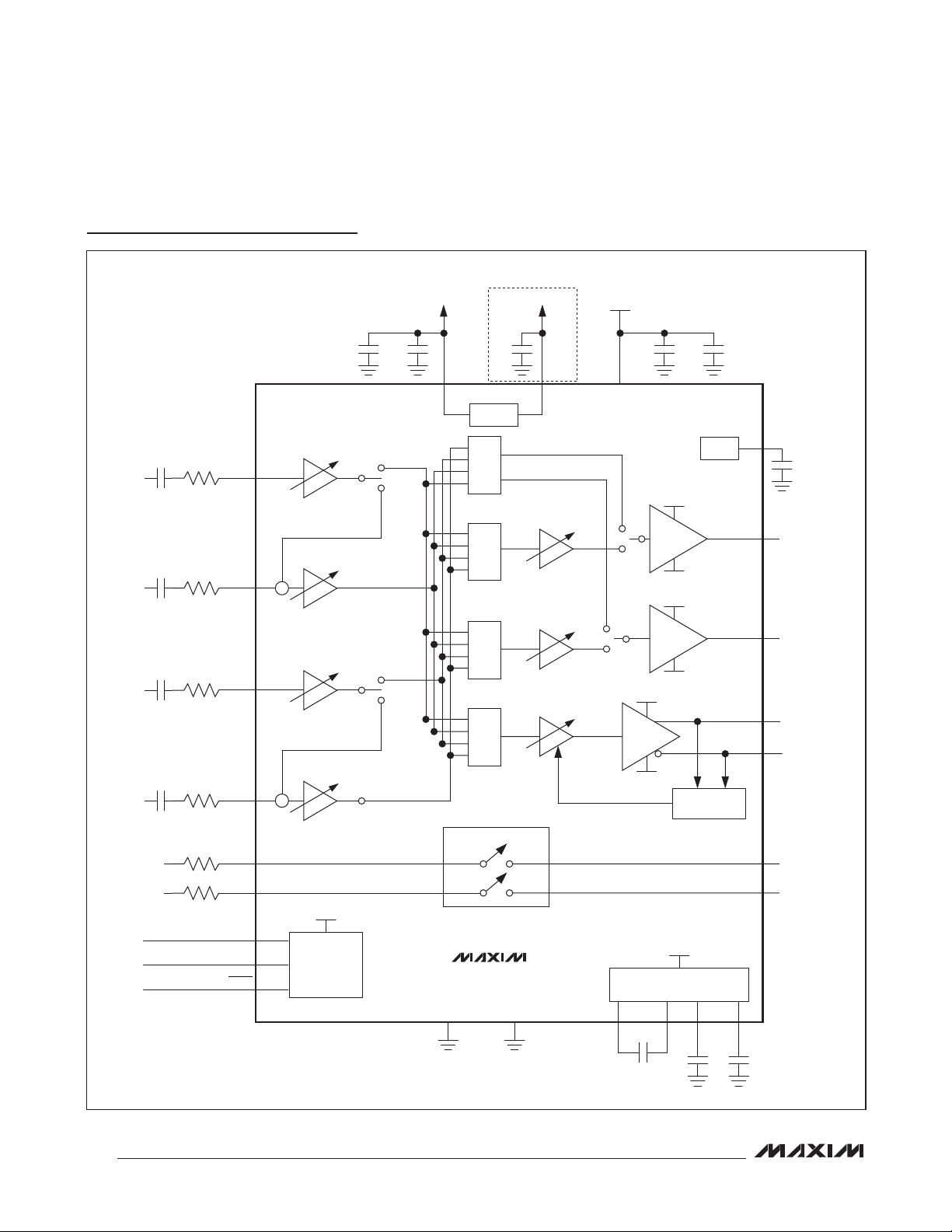

ABSOLUTE MAXIMUM RATINGS

(Voltages with respect to GND.)

VDD, HPVDD ........................................................-0.3V to +2.2V

PVDD, LDOIN .......................................................-0.3V to +6.0V

PGND ...................................................................-0.1V to +0.1V

HPVSS .................................................................-2.2V to + 0.3V

C1N .....................................(HPVSS - 0.3V) to (HPVDD + 0.3V)

C1P ..........................................................- 0.3V to (VDD + 0.3V)

HPL, HPR ............................. (HPVSS - 0.3V) to (HPVDD +0.3V)

INA1, INA2, INB1, INB2, BIAS ............................. -0.3V to +6.0V

SDA, SCL, SHDN .................................................-0.3V to +6.0V

COM1, COM2, NC1, NC2,

OUTP, OUTN ......................................-0.3V to (PVDD + 0.3V)

Continuous Current In/Out of PVDD, PGND, OUT_ ...... Q800mA

Continuous Current In/Out of HPR, HPL,

VDD, LDOIN .............................................................. Q140mA

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute

maximum rating conditions for extended periods may affect device reliability.

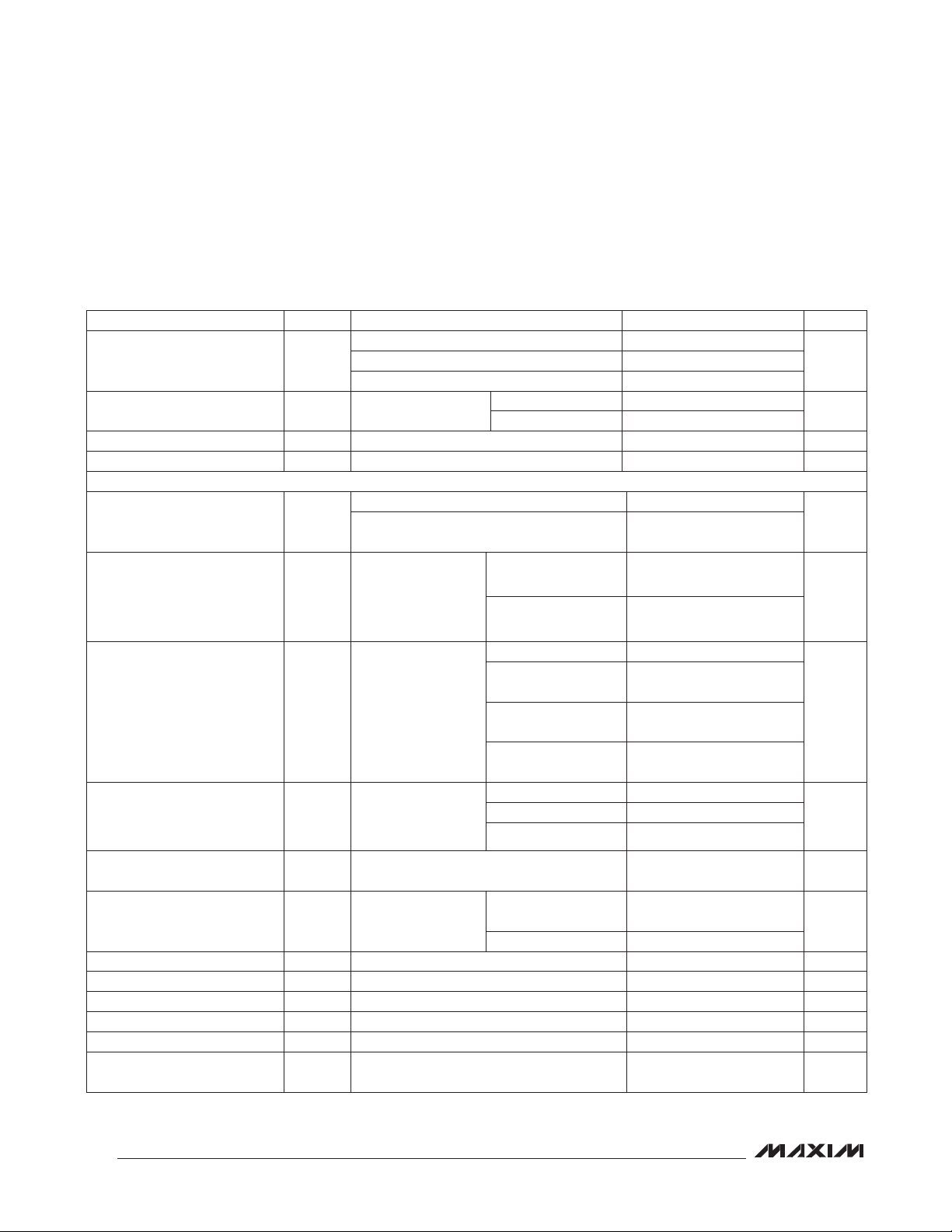

ELECTRICAL CHARACTERISTICS

(V

HPLVOL = HPRVOL = SPKVOL = 0dB, speaker loads (Z

nected from HPL or HPR to GND. SDA and SCL pullup voltage = 1.8V. Z

= 1FF. TA = T

LDOIN

= V

PVDD

MIN

= V

to T

= 3.7V, V

SHDN

, unless otherwise noted. Typical values are at TA = +25NC.) (Note 1)

MAX

GND

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Speaker Amplifier SupplyVoltage Range

Headphone Amplifier Supply

Voltage Range

LDO Input Supply-Voltage Range V

V

PVDD

VDD Guaranteed by PSRR test 1.6 2 V

LDOIN

Quiescent Supply Current

Shutdown Current I

SHDN

Turn-On Time t

Input Resistance R

Feedback Resistance R

= V

= 0V. Input signal applied at INA configured single-ended, preamp gain = 0dB,

PGND

SPK

Guaranteed by PSRR test 2.7 5.5 V

Guaranteed by PSRR test 2.5 5.5 V

Low-power mode, TA = +25NC,

LPMODE = 0x01

HP mode, TA = +25NC, stereo SE

input on INA, INB disabled

SPK mode, TA = +25NC mono

differential input on INB, INA disabled

SPK + HP mode, TA = +25NC stereo

SE input on INA, INB disabled

TA = +25NC, internal gain, software

TA = +25NC, internal gain, I

hardware

Time from power-on to full operation

ON

including soft-start

TA = +25NC,

IN

internal gain

TA = +25NC, external gain

F

Continuous Current In/Out of COM1,

COM2, NC1, NC2 ...................................................... Q150mA

Continuous Input Current (all other pins) ........................ Q20mA

Duration of OUT_ Short Circuit to GND

or PVDD ................................................................. Continuous

Duration of Short Circuit Between OUTP

and OUTN .............................................................Continuous

Duration of HP_ Short Circuit to GND or VDD ..........Continuous

Continuous Power Dissipation (TA = +70NC) Multilayer Board

25 WLP (derate 19.2mW/NC above +70NC) ................850mW

Junction Temperature .....................................................+150NC

Operating Temperature Range .......................... -40NC to +85NC

Storage Temperature Range ............................ -65NC to +150NC

Soldering Temperature (reflows) .....................................+260NC

) connected between OUTP and OUTN. Headphone loads (RHP) con-

= J, RHP = J. C

SPK

I

LDOIN

I

PVDD

I

LDOIN

I

PVDD

I

LDOIN

I

PVDD

I

LDOIN

I

PVDD

I

PVDD

I

LDOIN

+ I

PVDD

LDOIN

C1P-C1N

,

= C

HPVDD

1.45 2

0.4 0.7

1.45 2

0.79 1.2

0.42 0.75

1.38 2.2

1.45 2

1.8 2.7

90 175

60 110

= C

HPVSS

1

= C

mA

FA

BIAS

8 ms

Gain = -6dB, -3dB 41.2

Gain = 0dB to +9dB 16 20.6 27

kI

Gain = +18dB 5.5 7.2 9.5

19 20 21

kI

MAX97000

5

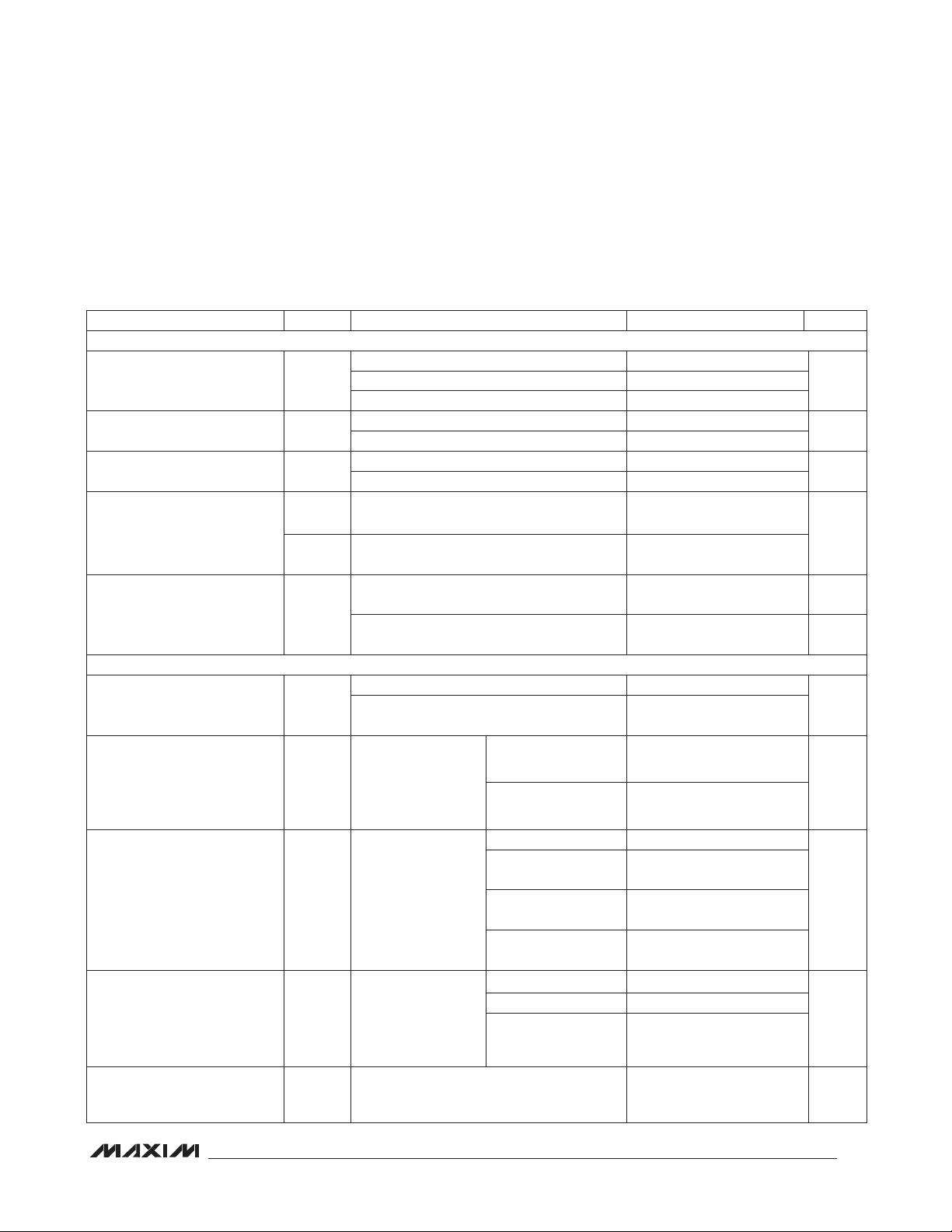

Page 6

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

ELECTRICAL CHARACTERISTICS (continued)

(V

HPLVOL = HPRVOL= SPKVOL = 0dB, speaker loads (Z

nected from HPL or HPR to GND. SDA and SCL pullup voltage = 1.8V. Z

= 1FF. TA = T

MAX97000

LDOIN

= V

PVDD

MIN

= V

to T

= 3.7V, V

SHDN

, unless otherwise noted. Typical values are at TA = +25NC.) (Note 1)

MAX

GND

= V

= 0V. Input signal applied at INA configured single-ended, preamp gain = 0dB,

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) con-

SPK

= J, RHP = J. C

SPK

C1P-C1N

= C

HPVDD

= C

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Preamp = 0dB 2.3

Maximum Input Signal Swing

Common-Mode Rejection Ratio CMRR

Preamp = +18dB 0.29

Preamp = external gain 2.3 x R

f = 1kHz (differential

input mode)

Gain = 0dB 55

Gain = +18dB 32

IN,EX/RF

Input DC Voltage IN__ inputs 1.125 1.2 1.275 V

Bias Voltage V

BIAS

1.13 1.2 1.27 V

SPEAKER AMPLIFIER

TA = +25NC, SPKM = 1 Q0.5 Q4

Output Offset Voltage V

Click-and-Pop Level K

Power-Supply Rejection Ratio

Output Power

Total Harmonic Distortion +

Noise

Signal-to-Noise Ratio SNR

Oscillator Frequency f

Spread-Spectrum Bandwidth

OS

CP

PSRR

THD+N

OSC

TA = +25NC, SPKVOL = 0dB, SPKMIX = 0x01,

IN_DIFF = 0V

Peak voltage, TA =

+25NC, A-weighted,

Into shutdown -70

32 samples per

second, volume at

mute (Note 2)

Out of shutdown -70

V

= 2.7V to 5.5V 50 75

PVDD

f = 217Hz,

TA = +25NC (Note 2)

V

f = 1kHz,

V

RIPPLR

RIPPLR

= 200mV

= 200mV

P-P

P-P

f = 20kHz,

THD+N P 1%,

f = 1kHz,

Z

= 8I + 68FH

SPK

(Note 3)

f = 1kHz, P

Z

= 8I + 68FH

SPK

= 360mW, TA = +25NC,

OUT

A-weighted, SPKMIX

= 0x03, referenced to

725mW

V

V

V

V

IN_DIFF = 0

(single-ended)

IN_DIFF = 1 (differential) 93

= 200mV

RIPPLR

= 4.2V 930

PVDD

= 3.7V 725

PVDD

= 3.3V 562

PVDD

P-P

Q1.5

65

65

59

0.05 0.6 %

93

250 kHz

Q20

Gain 11.5 12 12.5 dB

Current Limit 1.5 A

Efficiency

Output Noise

E P

= 725mW, f = 1kHz, Z

OUT

SPK

A-weighted, (SPKMIX = 0x01), IN_DIFF = 1,

SPKVOL = 0dB

= 8I + 68FH

87 %

50

HPVSS

= C

V

dB

mV

dBV

dB

mW

dB

kHz

FV

BIAS

P-P

RMS

6

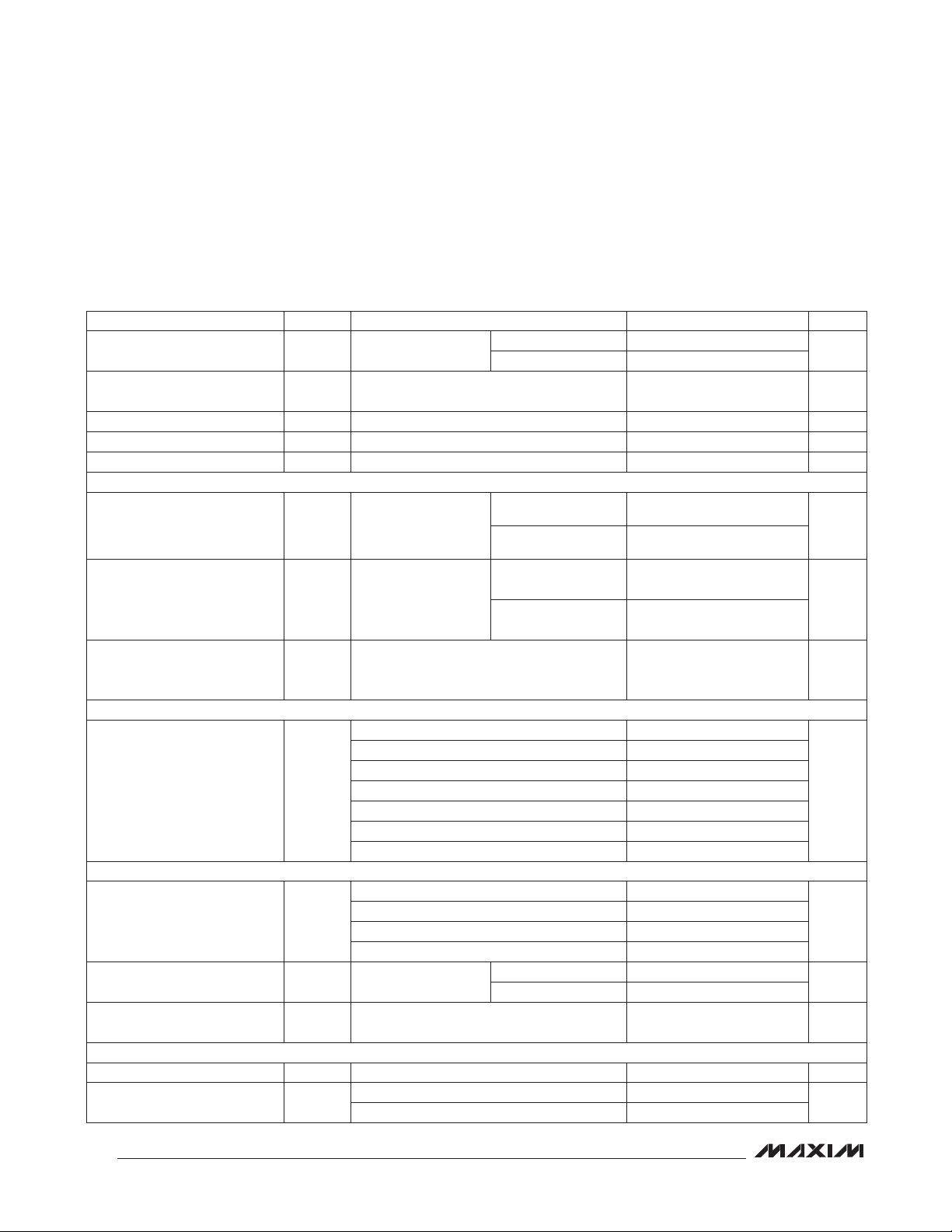

Page 7

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

ELECTRICAL CHARACTERISTICS (continued)

(V

LDOIN

= V

PVDD

HPLVOL = HPRVOL= SPKVOL = 0dB, speaker loads (Z

nected from HPL or HPR to GND. SDA and SCL pullup voltage = 1.8V. Z

= 1FF. TA = T

MIN

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

CHARGE PUMP

Charge-Pump Frequency

Positive Output Voltage V

Negative Output Voltage V

Headphone Output Voltage

Threshold

Mode Transition Timeouts

HEADPHONE AMPLIFIERS

Output Offset Voltage

Click-and-Pop Level

Power-Supply Rejection Ratio

Output Power P

Channel-to-Channel Gain

Tracking

= V

to T

= 3.7V, V

SHDN

, unless otherwise noted. Typical values are at TA = +25NC.) (Note 1)

MAX

GND

HPVDD

HPVSS

V

TH1

V

TH2

= V

= 0V. Input signal applied at INA configured single-ended, preamp gain = 0dB,

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) con-

SPK

V

V

V

V

V

V

HPL

HPL

HPL

HPL

HPL

HPL

HPL

= V

= V

= V

, V

, V

, V

, V

= 0V 80 83 85

HPR

= 0.2V 665

HPR

= 0.5V 500

HPR

> V

HPR

HPR

HPR

HPR

< V

> V

< V

TH

TH

TH

TH

Output voltage at which the charge pump

switches between fast and slow clock

Output voltage at which the charge pump

switches modes, V

rising or falling

OUT

Time it takes for the charge pump to

transition from invert to split mode

Time it takes for the charge pump to

transition from split to invert mode

TA = +25NC volume at mute Q0.15 Q0.6

V

OS

TA = +25NC, HP_VOL = 0dB, HP_MIX = 0x1,

IN_DIFF = 0

Peak voltage, TA =

+25NC, A-weighted, 32

K

samples per second,

CP

volume at mute

(Note 2)

Into shutdown -74

Out of shutdown -74

V

LDOIN

f = 217Hz,

V

RIPPLE

PSRR

TA = +25NC (Note 2)

f = 1kHz,

V

RIPPLE

f = 20kHz,

V

RIPPLE

RHP = 16I

RHP = 32I

RHP = 32I,

OUT

THD+N = 1%,

f = 1kHz

LPMODE = 1,

LP gain = 3dB

TA = +25NC, HPL to HPR, volume at

maximum, HPLMIX = 0x01, HPRMIX = 0x02,

IN_DIFF = 0

= J, RHP = J. C

SPK

C1P-C1N

0.1 0.16 0.21

0.40 0.46 0.52

= 2.5V to 5.5V 70 85

= 200mV

= 200mV

= 200mV

P-P

P-P

P-P

= C

HPVDD

= C

HPVSS

1.8

0.9

-1.8

-0.9

32 ms

20

Q0.5

84

80

62

40

23

34

Q0.3 Q2.5

= C

kHzV

mV

dBV

mW

V

V

V

Fs

dB

%

BIAS

MAX97000

7

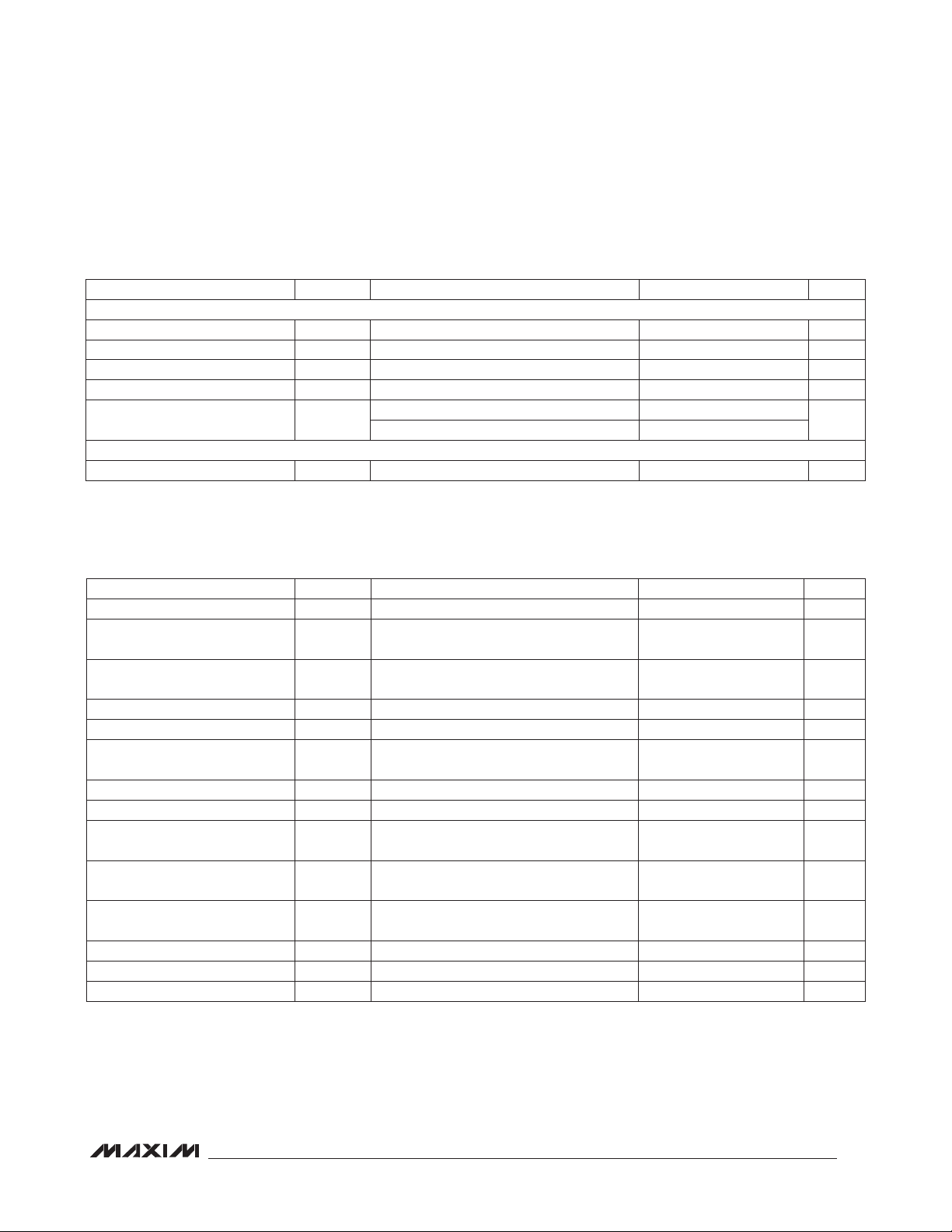

Page 8

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

ELECTRICAL CHARACTERISTICS (continued)

(V

HPLVOL = HPRVOL= SPKVOL = 0dB, speaker loads (Z

nected from HPL or HPR to GND. SDA and SCL pullup voltage = 1.8V. Z

= 1FF. TA = T

MAX97000

= V

LDOIN

Total Harmonic Distortion +

Noise

Signal-to-Noise Ratio SNR

Slew Rate SR 0.35

Capacitive Drive C

Crosstalk HPL to HPR, HPR to HPL, f = 20Hz to 20kHz 65 dB

ANALOG SWITCH

On-Resistance R

= V

PVDD

to T

MIN

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 3.7V, V

SHDN

, unless otherwise noted. Typical values are at TA = +25NC.) (Note 1)

MAX

GND

THD+N

L

ON

= V

= 0V. Input signal applied at INA configured single-ended, preamp gain = 0dB,

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) con-

SPK

= J, RHP = J. C

SPK

P

= 10mW,

OUT

f = 1kHz

A-weighted, RHP = 16I, HPLMIX = 0x01,

HPRMIX = 0x02, IN_DIFF = 0

I

= 20mA, V

NC_

= 0V and PVDD,

SWEN = 1

COM_

RHP = 32I

RHP = 16I

TA = +25NC

TA = T

MIN

to T

MAX

C1P-C1N

= C

0.02

0.03 0.1

100 dB

200 pF

1.6 4

HPVDD

= C

HPVSS

5.2

= C

V/Fs

%

I

BIAS

V

DIFCOM_

Total Harmonic Distortion +

Noise

Off-Isolation

PREAMPLIFIER

Gain

VOLUME CONTROL

Volume Level

Mute Attenuation f = 1kHz

Zero-Crossing Detection

Timeout

LIMITER

Attack Time 1 ms

Release Time Constant

V

CMCOM_

f = 1kHz, SWEN = 1,

Z

SPK

SWEN = 0, COM1 and COM2 to GND = 50I,

f = 10kHz, referred to signal applied to NC1

and NC2

PGAIN_ = 000 -6.5 -6 -5.5

PGAIN_ = 001 -3.5 -3 -2.5

PGAIN_ = 010 -0.5 0 0.5

PGAIN_ = 011 2.5 3 3.5

PGAIN_ = 100 5.5 6 6.5

PGAIN_ = 101 8.5 9 9.5

PGAIN_ = 110 17.5 18 18.5

HP_VOL = 0x1F 5.5 6 6.5

HP_VOL = 0x00 -68 -64 -60

SPKVOL = 0x3F 19 20 21

SPKVOL = 0x00 -31 -30 -29

THDT1 = 0 1.4

THDT1 = 1 2.8

= 2V

P-P

= PVDD/2,

= 8I + 68FH

10I in series with

,

each switch

No series resistors 0.3

Speaker 109

Headphone 101

0.05

%

105 dB

dB

dB

dB

100 ms

s

8

Page 9

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

DIGITAL I/O CHARACTERISTICS

(V

TA = +25NC.) (Note 1)

I2C TIMING CHARACTERISTICS

(V

TA = +25NC.) (Note 1)

Note 1: 100% production tested at TA = +25NC. Specifications overtemperature limits are guaranteed by design.

Note 2: Amplifier inputs are AC-coupled to GND.

Note 3: Class D amplifier testing performed with a resistive load in series with an inductor to simulate an actual speaker load.

Note 4: CB is in pF.

LDOIN

= V

PVDD

= V

SHDN

= 3.7V, V

GND

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

DIGITAL INPUTS (SDA, SCL, SHDN)

Input Voltage High V

Input Voltage Low V

Input Hysteresis V

Input Capacitance C

Input Leakage Current I

DIGITAL OUTPUTS (SDA Open Drain)

Output Low Voltage V

LDOIN

= V

PVDD

= V

SHDN

= 3.7V, V

GND

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Serial-Clock Frequency f

Bus Free Time Between STOP

and START Conditions

Hold Time (Repeated) START

Condition

SCL Pulse-Width Low t

SCL Pulse-Width High t

Setup Time for a Repeated

START Condition

Data Hold Time t

Data Setup Time t

t

t

HD,STA

LOW

HIGH

t

SU,STA

HD,DAT

SU,DAT

SDA and SCL Receiving

Rise Time

SDA and SCL Receiving Fall Time t

SDA Transmitting Fall Time t

Setup Time for STOP Condition t

SU,STO

Bus Capacitance C

Pulse Width of Suppressed Spike t

IH

IL

HYS

IN

IN

OL

SCL

BUF

t

R

F

F

SP

= V

= 0V. TA = T

PGND

MIN

to T

, unless otherwise noted. Typical values are at

MAX

1.3 V

TA = +25NC Q1.0

V

= 0, TA = +25NC Q1.0

LDOIN

I

= 3mA 0.4 V

SINK

= V

= 0V. TA = T

PGND

MIN

to T

, unless otherwise noted. Typical values are at

MAX

0 400 kHz

1.3

0.6

1.3

0.6

0.6

0 900 ns

100 ns

(Note 4)

(Note 4)

(Note 4)

20 +

0.1C

20 +

0.1C

20 +

0.1C

B

B

B

0.6

B

0 50 ns

0.5 V

200 mV

10 pF

300 ns

300 ns

300 ns

400 pF

MAX97000

FA

Fs

Fs

Fs

Fs

Fs

Fs

9

Page 10

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

SDA

t

BUF

t

LOW

t

SU,DAT

t

HD,DAT

t

SU,STA

t

HD,STA

t

SP

t

SU,STO

SCL

MAX97000

t

HD,STA

START CONDITION

t

HIGH

t

t

R

F

REPEATED START CONDITION

STOP

CONDITION

START

CONDITION

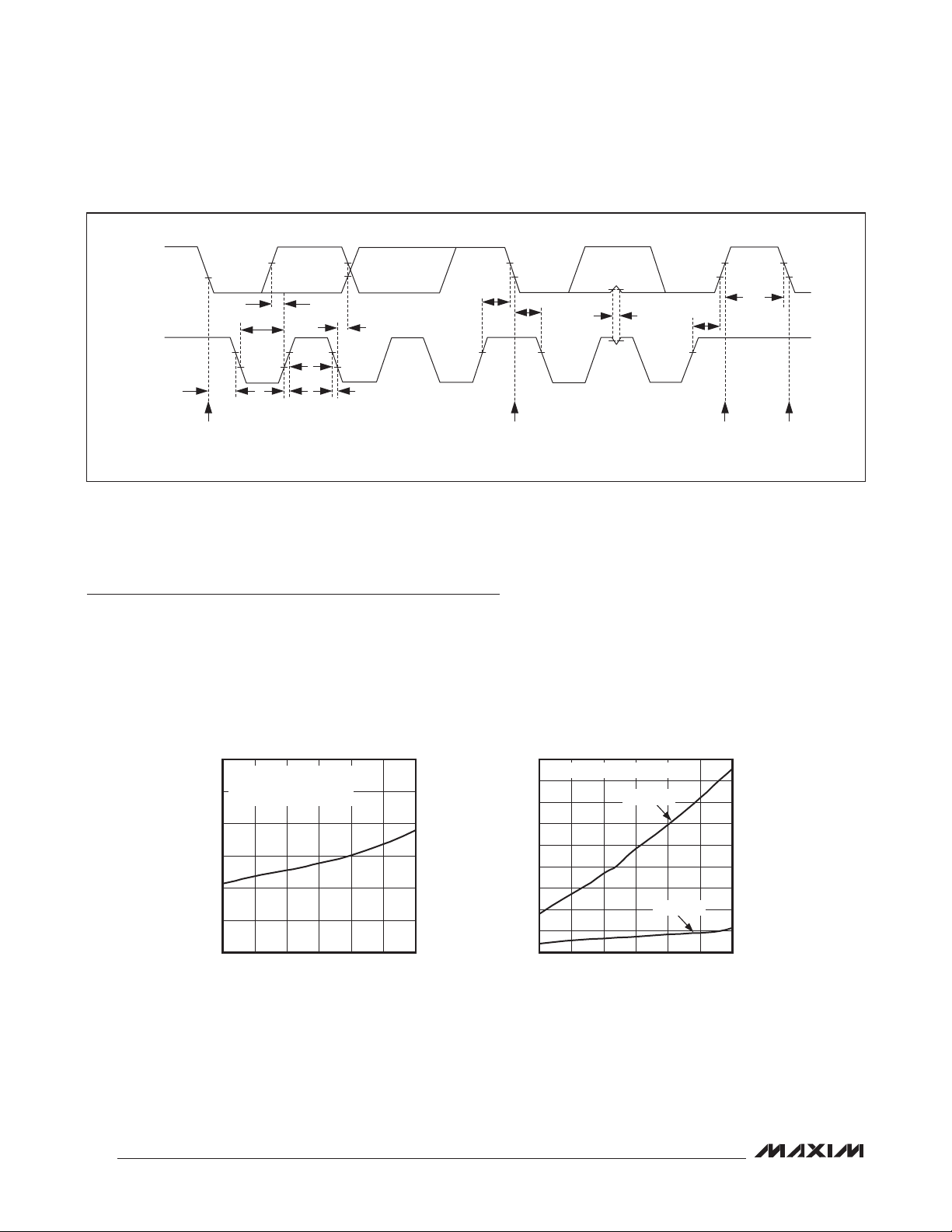

Figure 1. I2C Interface Timing Diagram

Typical Operating Characteristics

(V

loads (Z

C

LDOIN

C1P-C1N

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

= ∞, RHP = ∞.

SPK

GENERAL

SUPPLY CURRENT

vs. SUPPLY VOLTAGE

3.0

SPEAKER ONLY

INPUTS AC-COUPLED TO GND

2.5

INA CONNECTED TO OUTPUT

2.0

1.5

1.0

SUPPLY CURRENT (mA)

0.5

0

2.5 5.5

SUPPLY VOLTAGE (V)

4.5

4.0

MAX97000 toc01

5.04.54.03.53.0

3.5

3.0

2.5

2.0

1.5

SHUTDOWN CURRENT (µA)

1.0

0.5

0

2.5 5.5

SHUTDOWN CURRENT

vs. SUPPLY VOLTAGE

INPUTS AC-COUPLED TO GND

SOFTWARE

SUPPLY VOLTAGE (V)

MAX97000 toc02

HARDWARE

5.04.54.03.53.0

10

Page 11

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued)

(V

LDOIN

loads (Z

C

C1P-C1N

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

SPEAKER AMPLIFIER

= ∞, RHP = ∞.

SPK

MAX97000

10

V

= 3.7V

PVDD

Z

= 8I + 68µF

SPRK

1

P

= 500mW

OUT

0.1

THD+N (%)

P

= 200mW

0.01

0.001

0.01 100

FREQUENCY (kHz)

OUT

THD+N vs. OUTPUT POWER

100

V

= 5.0V

PVDD

Z

= 8I + 68µF

SPRK

10

THD+N vs. FREQUENCY

1

THD+N (%)

0.1

0.01

0.001

fIN = 6kHz

fIN = 1kHz

fIN = 100Hz

0 2.5

P

(mW)

OUT

10

V

= 3.7V

PVDD

Z

= 4I + 33µF

MAX97000 toc03

THD+N (%)

1010.1

SPRK

1

P

= 1000mW

OUT

0.1

P

= 200mW

0.01

0.001

0.01 100

FREQUENCY (kHz)

OUT

1010.1

MAX97000 toc04

10

1

0.1

THD+N (%)

0.01

0.001

0.01 100

THD+N vs. OUTPUT POWER

THD+N vs. FREQUENCY

100

V

= 5.0V

PVDD

Z

= 4I + 33µF

MAX97000 toc06

THD+N (%)

2.01.51.00.5

SPRK

10

1

0.1

0.01

0.001

fIN = 6kHz

fIN = 1kHz

fIN = 100Hz

0 4.0

P

(mW)

OUT

3.53.02.52.01.51.00.5

MAX97000 toc07

100

10

1

THD+N (%)

0.1

0.01

0.001

THD+N vs. FREQUENCY

V

= 3.7V

PVDD

Z

= 8I + 68µF

SPRK

SSM

FFM

1010.1

FREQUENCY (kHz)

THD+N vs. OUTPUT POWER

V

= 4.2V

PVDD

Z

= 8I + 68µF

SPRK

fIN = 6kHz

fIN = 1kHz

fIN = 100Hz

0 1.6

P

(mW)

OUT

1.41.21.00.80.60.40.2

MAX97000 toc05

MAX97000 toc08

100

10

1

THD+N (%)

0.1

0.01

0.001

THD+N vs. OUTPUT POWER

V

= 4.2V

PVDD

Z

= 4I + 33µF

SPRK

fIN = 6kHz

fIN = 1kHz

fIN = 100Hz

P

(mW)

OUT

2.52.01.51.00.50 3.0

MAX97000 toc09

100

10

1

THD+N (%)

0.1

0.01

0.001

THD+N vs. OUTPUT POWER

V

= 3.7V

PVDD

Z

= 8I + 68µF

SPRK

fIN = 6kHz

fIN = 1kHz

fIN = 100Hz

P

(mW)

OUT

1.21.00.80.60.40.20 1.4

MAX97000 toc10

100

THD+N vs. OUTPUT POWER

V

= 3.7V

PVDD

Z

= 4I + 33µF

SPRK

10

fIN = 6kHz

1

fIN = 1kHz

THD+N (%)

0.1

0.01

0.001

0 2.5

fIN = 100Hz

P

(mW)

OUT

MAX97000 toc11

2.01.51.00.5

11

Page 12

Audio Subsystem with Mono Class D

POWER-SUPPLY REJECTION RATIO

POWER-SUPPLY REJECTION RATIO

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued)

(V

LDOIN

loads (Z

C

C1P-C1N

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

= ∞, RHP = ∞.

SPK

EFFICIENCY vs. OUTPUT POWER

100

Z

= 8I + 68µF

SPRK

90

MAX97000

80

70

60

50

40

EFFICIENCY (%)

30

20

10

0

0 3.0

P

OUT

OUTPUT POWER vs. SUPPLY VOLTAGE

2.0

fIN = 1kHz

1.8

Z

= 8I + 68µF

SPRK

1.6

1.4

1.2

1.0

0.8

OUTPUT POWER (W)

0.6

0.4

0.2

0

2.5 5.5

THD+N = 10%

SUPPLY VOLTAGE (V)

Z

SPRK

(W)

THD+N = 1%

= 4I + 33µF

V

= 5.0V

PVDD

fIN = 1kHz

2.52.01.51.00.5

5.04.54.03.53.0

100

MAX97000 toc12

EFFICIENCY (%)

2.0

1.8

MAX97000 toc15

1.6

1.4

1.2

1.0

0.8

OUTPUT POWER (W)

0.6

0.4

0.2

EFFICIENCY vs. OUTPUT POWER

Z

= 8I + 68µF

SPRK

90

80

Z

= 4I + 33µF

70

60

50

40

30

20

10

0

SPRK

V

PVDD

fIN = 1kHz

P

(W)

OUT

OUTPUT POWER vs. LOAD RESISTANCE

V

= 3.7V

PVDD

f

= 1kHz

IN

Z

= LOAD + 68µF

SPRK

THD+N = 10%

THD+N = 1%

0

LOAD RESISTANCE (I)

100101 1000

= 3.7V

1.41.20.8 1.00.4 0.60.20 1.6

MAX97000 toc13

OUTPUT POWER (W)

MAX97000 toc16

PSRR (dB)

OUTPUT POWER vs. SUPPLY VOLTAGE

4.0

fIN = 1kHz

3.5

Z

= 4I + 33µF

SPRK

3.0

2.5

2.0

1.5

1.0

0.5

0

2.5 5.5

THD+N = 10%

THD+N = 1%

SUPPLY VOLTAGE (V)

vs. FREQUENCY

0

V

= 3.7V

PVDD

V

= 200mV

RIPPLE

-20

INPUTS AC-COUPLED GND

-40

-60

-80

-100

0.01 100

P-P

1010.1

FREQUENCY (kHz)

MAX97000 toc14

5.04.53.0 3.5 4.0

MAX97000 toc17

0

V

= 200mV

RIPPLE

fIN = 1kHz

-20

INPUTS AC-COUPLED GND

-40

PSRR (dB)

-60

-80

-100

2.5 5.5

P-P

SUPPLY VOLTAGE (V)

12

vs. SUPPLY VOLTAGE

IN-BAND OUTPUT SPECTRUM

0

SSM

-20

MAX97000 toc18

-40

-60

AMPLITUDE (dBV)

-80

-100

5.04.54.03.53.0

-120

= 1kHz

f

IN

0 20

FREQUENCY (kHz)

15105

MAX97000 toc19

AMPLITUDE (dBV)

-100

-120

IN-BAND OUTPUT SPECTRUM

0

FFM

-20

-40

-60

-80

= 1kHz

f

IN

0 20

FREQUENCY (kHz)

15105

MAX97000 toc20

Page 13

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued)

(V

loads (Z

C

LDOIN

C1P-C1N

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

= ∞, RHP = ∞.

SPK

MAX97000

WIDEBAND OUTPUT SPECTRUM

0

-20

-40

-60

-80

OUTPUT AMPLITUDE (dBV)

-100

-120

0.1 1000

FREQUENCY (MHz)

RBW = 100Hz

FFM

SPEAKER VOLUME GAIN

vs. SPKVOL CODE

30

20

10

0

-10

-20

SPEAKER VOLUME GAIN (dB)

-30

WIDEBAND OUTPUT SPECTRUM

0

-10

MAX97000 toc21

100101

-20

-30

-40

-50

-60

-70

OUTPUT AMPLITUDE (dBV)

-80

-90

-100

0.1 1000

FREQUENCY (MHz)

HARDWARE SHUTDOWN RESPONSE

MAX97000 toc23

RBW = 100Hz

SSM

100101

MAX97000 toc24

MAX97000 toc22

SHDN

2V/div

SPKR

OUTPUT

500mV/div

-40

0 70

SPKVOL CODE (NUMERIC)

SOFTWARE SHUTDOWN RESPONSE

400µs/div

605040302010

MAX97000 toc25

SDA

2V/div

SPKR

OUTPUT

1V/div

1ms/div

SOFTWARE TURN-ON RESPONSE

4ms/div

MAX97000 toc26

SDA

2V/div

SPKR

OUTPUT

1V/div

13

Page 14

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued)

(V

loads (Z

C

MAX97000

LDOIN

C1P-C1N

10

1

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

HEADPHONE AMPLIFIER

THD+N vs. FREQUENCY

R

= 32I

LOAD

MAX97000 toc27

10

R

= 16I

LOAD

1

10

MAX97000 toc28

THD+N vs. FREQUENCY

THD+N vs. OUTPUT POWER

R

= 32I

LOAD

1

= ∞, RHP = ∞.

SPK

MAX97000 toc29

0.1

THD+N (%)

0.01

0.001

P

= 25mW

OUT

P

= 5mW

OUT

0.01 100

FREQUENCY (kHz)

THD+N vs. OUTPUT POWER

10

R

= 16I

LOAD

1

fIN = 1kHz

0.1

THD+N (%)

0.01

0.001

fIN = 100Hz

0 80

OUTPUT POWER (mW)

fIN = 6kHz

OUTPUT POWER vs. LOAD RESISTANCE

70

fIN = 1kHz

THD+N = 1%

60

C

= 0.47µF

CHARGE_PUMP

C

CHARGE_PUMP

10010

50

40

30

OUTPUT POWER (mW)

20

C

CHARGE_PUMP

10

0

1 1000

LOAD RESISTANCE (I)

1010.1

70605040302010

= 2.2µF

= 1µF

0.1

THD+N (%)

0.01

0.001

0.01 100

180

160

MAX97000 toc30

140

120

100

80

60

POWER DISSIPATION (mW)

40

20

0

0 90

0

-20

MAX97000 toc33

-40

PSRR (dB)

-60

-80

-100

0.01 100

P

= 30mW

OUT

P

= 10mW

OUT

1010.1

FREQUENCY (kHz)

POWER DISSIPATION

vs. OUTPUT POWER

fIN = 1kHz

P

OUT

= P

HPL

+ P

HPR

R

= 32I

LOAD

OUTPUT POWER (mW)

R

LOAD

= 16I

POWER-SUPPLY REJECTION RATIO

vs. FREQUENCY

V

= 200mV

RIPPLE

INPUTS AC-COUPLED GND

P-P

1010.1

FREQUENCY (kHz)

0.1

THD+N (%)

0.01

0.001

fIN = 1kHz

fIN = 100Hz

0 60

OUTPUT POWER (mW)

fIN = 6kHz

5040302010

OUTPUT POWER vs. LOAD RESISTANCE

80

70

MAX97000 toc31

60

50

40

THD+N = 1%

30

OUTPUT POWER (mW)

20

10

807050 6020 30 4010

0

1 1000

LOAD RESISTANCE (I)

THD+N = 10%

= 1kHz

f

IN

MAX97000 toc32

10010

OUTPUT SPECTRUM

0

R

= 32I

LOAD

-20

f

= 1kHz

MAX97000 toc34

AMPLITUDE (dBV)

IN

-40

-60

-80

-100

-120

-140

-160

0 24

FREQUENCY (kHz)

MAX97000 toc35

20164 8 12

14

Page 15

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued)

(V

= V

LDOIN

loads (Z

C

SPK

C1P-C1N

0

-20

-40

-60

-80

-100

AMPLITUDE (dBV)

-120

-140

-160

0 24

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

COMMON-MODE REJECTION RATIO

OUTPUT SPECTRUM

R

= 16I

LOAD

f

= 1kHz

IN

FREQUENCY (kHz)

-20

MAX97000 toc36

-40

-60

CROSSTALK (dB)

-80

-100

20164 8 12

-120

CROSSTALK vs. FREQUENCY

0

R

= 32I

LOAD

HPL TO HPR

HPR TO HPL

0.01 100

FREQUENCY (kHz)

1010.1

MAX97000 toc37

0

R

= 16I

LOAD

-10

-20

-30

CMRR (dB)

-40

-50

-60

PREGAIN = +18dB

0.01 100

= ∞, RHP = ∞.

SPK

vs. FREQUENCY

PREGAIN = +9dB

FREQUENCY (kHz)

PREGAIN = 0dB

1010.1

MAX97000

MAX97000 toc38

HEADPHONE VOLUME GAIN

vs. HP_VOL CODE

10

RIGHT AND LEFT

0

-10

-20

-30

-40

-50

HEADPHONE VOLUME GAIN (dB)

-60

-70

0 35

HP_VOL CODE (NUMERIC)

SOFTWARE SHUTDOWN RESPONSE

30255 10 15 20

MAX97000 toc41

MAX97000 toc39

SDA

2V/div

HPL/HPR

500mV/div

HARDWARE SHUTDOWN RESPONSE

1ms/div

SOFTWARE TURN-ON RESPONSE

MAX97000 toc40

MAX97000 toc42

SHDN

2V/div

HPL/HPR

500mV/div

SDA

2V/div

HPL/HPR

500mV/div

1ms/div

4ms/div

15

Page 16

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Typical Operating Characteristics (continued

(V

LDOIN

loads (Z

C

C1P-C1N

= V

SPK

PVDD

= 3.7V, V

GND

= V

= 0V. Single-ended inputs, preamp gain = 0dB, HPLVOL = HPRVOL = SPKVOL = 0dB. Speaker

PGND

) connected between OUTP and OUTN. Headphone loads (RHP) connected from HPL or HPR to GND. Z

= C

HPVDD

= C

HPVSS

= C

= 1μF. TA = +25°C, unless otherwise noted.)

BIAS

ANALOG SWITCH

= ∞, RHP = ∞.

SPK

MAX97000

HPVDD

0V

HPVSS

0V

3.0

INC = 20mA

2.5

2.0

(I)

1.5

ON

R

1.0

0.5

CLASS H OPERATION

10ms/div

ON-RESISTANCE vs. V

V

= 2.7V

PVDD

V

PVDD

V

= 3.0V

PVDD

COM

= 3.7V

V

PVDD

MAX97000 toc43

= 5.0V

HPVDD

1V/div

HPL/HPR

200mV/div

HPVSS

1V/div

MAX97000 toc45

TOTAL HARMONIC DISTORTION

PLUS NOISE vs. OUTPUT POWER

10

1

0.1

THD+N (%)

0.01

0.001

0 30

I

R

= 32

LOAD

EXTERNAL CLASS AB CONNECTED

DIRECTLY TO COM1 AND COMR

f = 100kHz

f = 6kHz

f = 100kHz

OUTPUT POWER (mW)

BYPASS SWITCH OFF-ISOLATION

0

-20

-40

-60

-80

OFF ISOLATION (dB)

-100

-120

MAX97000 toc44

252015105

MAX97000 toc46

16

0

0 6

V

(V)

COM

54321

-140

0.01 100

FREQUENCY (kHz)

1010.1

Page 17

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Pin Configuration

TOP VIEW

(BUMP SIDE DOWN)

2 3 41

+

MAX97000

5

MAX97000

A

B

C

D

E

C1N HPVDD HPVSSC1P

LDOIN SDA SCLVDD

PGND GND

COM1 COM2 INB1 INB2OUTN

NC1 NC2 INA1

2.0mm x 2.0mm

SHDN

HPR

HPL

BIASPVDD

INA2OUTP

Pin Description

BUMP NAME FUNCTION

A1 C1P

A2 C1N

A3 HPVDD

A4 HPVSS

A5 HPR Headphone Amplifier Right Output

B1 VDD

B2 LDOIN

B3 SDA Serial Data Input/Output. Connect a pullup resistor from SDA to the I2C bus supply.

B4 SCL Serial-Clock Input. Connect a pullup resistor from SCL to the I2C bus supply.

B5 HPL Headphone Amplifier Left Output

C1 PVDD

C2 PGND Class D Power Ground and Charge Pump Ground

C3 GND Analog Ground.

C4

C5 BIAS

SHDN

Charge-Pump Flying Capacitor Positive Terminal. Connect a 1FF capacitor between C1P and

C1N.

Charge-Pump Flying Capacitor Negative Terminal. Connect a 1FF capacitor between C1P and

C1N.

Headphone Amplifier Positive Power Supply. Bypass with a 1FF capacitor to PGND.

Headphone Amplifier Negative Power Supply. Bypass with a 1FF capacitor to PGND.

LDO Output and Headphone Amplifier Supply. Bypass with a 1FF and a 10FF capacitor to

GND. Power VDD or LDOIN. When powering VDD, leave LDOIN unconnected.

LDO Input. Generates VDD if no 1.8V power supply is available. Leave unconnected to disable.

Do not power VDD when powering LDOIN.

Class D Power Supply. Bypass with a 1FF and a 10FF capacitor to PGND.

Active-Low Shutdown

Common-Mode Bias. Bypass to GND with a 1FF capacitor.

17

Page 18

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Pin Description (continued)

BUMP NAME FUNCTION

D1 OUTN Negative Speaker Output

D2 COM1 Analog Switch 1 Input

D3 COM2 Analog Switch 2 Input

D4 INB1 Input B1. Left or negative input.

D5 INB2 Input B2. Right or positive input.

MAX97000

E1 OUTP Positive Speaker Output

E2 NC1 Analog Switch 1 Output

E3 NC2 Analog Switch 2 Output

E4 INA1 Input A1. Left or negative input.

E5 INA2 Input A2. Right or positive input.

Detailed Description

The MAX97000 audio subsystem combines a mono

speaker amplifier with a stereo headphone amplifier

and an analog DPST switch. The high-efficiency 725mW

Class D speaker amplifier operates directly from the battery and consumes no more than 1FA when in shutdown

mode. The headphone amplifier utilizes a dual-mode

charge pump and a Class H output stage to maximize

efficiency while outputting a ground-referenced signal

that does not require output coupling capacitors. The

headphone and speaker amplifiers have independent

volume control and on/off control. The four inputs are

configurable as two differential inputs or four singleended inputs. All control is performed using the 2-wire,

I2C interface.

The speaker amplifier incorporates a distortion limiter to

automatically reduce the volume level when excessive

clipping occurs. This allows high gain for low-level signals without compromising the quality of large signals.

INA2

INA1

INPUT A

-6dB TO +18dB

Internal Linear Regulator

The MAX97000 includes an internal regulator (LDOIN) to

generate VDD in cases where no 1.8V supply is available.

Using the regulator allows single-supply operation directly

from a Li+ battery. To enable the internal regulator apply

a power supply to LDOIN and do not connect power to

VDD. When not using the internal regulator, leave LDOIN

unconnected and power VDD from a 1.8V supply.

Signal Path

The MAX97000 signal path consists of flexible inputs,

signal mixing, volume control, and output amplifiers

(Figure 2). The inputs can be configured for singleended or differential signals (Figure 3). The internal

preamplifiers feature programmable gain settings using

internal resistors and an external gain setting using a

trimmed internal feedback resistor. The external option

allows any desired gain to be selected. Following preamplification, the input signals are mixed, volume adjusted,

and routed to the headphone and speaker amplifiers

based on the desired configuration.

-64dB TO +6dB

0/3dB

Figure 2. Signal Path

18

INB2

INB1

INPUT B

-6dB TO +18dB

MIXER

AND

MUX

-64dB TO +6dB 0/3dB

-30dB TO +20dB +12dB

Page 19

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

STEREO SINGLE-ENDED

IN_2 (R)

R

TO MIXER

IN_1 (L)

L

DIFFERENTIAL

IN_2 (+)

MAX97000

IN_1 (-)

Figure 3. Differential and Stereo Single-Ended Input Configurations

Mixers

The MAX97000 features independent mixers for the left

headphone, right headphone, and speaker paths. Each

output can select any combination of any inputs. This

allows for mixing two audio signals together and routing independent signals to the headphone and speaker

amplifiers. If one of the inputs is not selected by either

mixer, it is automatically powered down to save power.

TO MIXER

Class D Speaker Amplifier

The MAX97000 Class D speaker amplifier utilizes active

emissions limiting and spread-spectrum modulation to

minimize the EMI radiated by the amplifier.

19

Page 20

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Ultra-Low EMI Filterless Output Stage

Traditional Class D amplifiers require the use of external

LC filters or shielding to meet EN55022B electromagnetic-interference (EMI) regulation standards. Maxim’s

active emissions limiting edge-rate control circuitry and

spread-spectrum modulation reduces EMI emissions,

while maintaining up to 87% efficiency. Maxim’s spreadspectrum modulation mode flattens wideband spectral

MAX97000

40

30

20

10

AMPLITUDE (dBµV/m)

0

-10

30 300

40

components, while proprietary techniques ensure that

the cycle-to-cycle variation of the switching period

does not degrade audio reproduction or efficiency.

The MAX97000’s spread-spectrum modulator randomly

varies the switching frequency by Q20kHz around the

center frequency (250kHz). Above 10MHz, the wideband spectrum looks like noise for EMI purposes (see

Figure 4).

2802602402202001801601401201008060

FREQUENCY (MHz)

30

20

10

AMPLITUDE (dBµV/m)

0

-10

300 350 1000

Figure 4. EMI with 15cm of Speaker Cable

950900850800750700650600550500450400

FREQUENCY (MHz)

20

Page 21

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Distortion Limiter

The MAX97000 speaker amplifiers integrate a limiter

to provide speaker protection and audio compression.

When enabled, the limiter monitors the audio signal at

the output of the Class D speaker amplifier and decreases the gain if the distortion exceeds the predefined

threshold. The limiter automatically tracks the battery

voltage to reduce the gain as the battery voltage drops.

Figure 5 shows the typical output vs. input curves with

and without the distortion limiter. The dotted line shows

the maximum gain for a given distortion limit without

the distortion limiter. The solid line shows how, with the

distortion limiter enabled, the gain can be increased

without exceeding the set distortion limit. When the

limiter is enabled, selecting a high gain level results in

peak signals being attenuated while low signals are left

unchanged. This increases the perceived loudness without the harshness of a clipped waveform.

Analog Switch

The MAX97000 integrates a DPST analog audio switch.

This switch can be used to disconnect an independent

audio signal, or drive the 8I speaker by connecting

NC1 and NC2 to OUTN and OUTP, respectively. Unlike

discrete solutions, the switch design reduces coupling

of Class D switching noise to the COM_ inputs. This

eliminates the need for a costly T-switch. Drive COM1

and COM2 with a low-impedance source to minimize

noise on the pins. In applications that do not require

the analog switch, leave COM1, COM2, NC1, and NC2

unconnected.

Headphone Amplifier

DirectDrive

Traditional single-supply headphone amplifiers have

outputs biased at a nominal DC voltage (typically half

the supply). Large coupling capacitors are needed to

block this DC bias from the headphone. Without these

capacitors, a significant amount of DC current flows to

the headphone, resulting in unnecessary power dissipation and possible damage to both headphone and

headphone amplifier.

Maxim’s DirectDrive® architecture uses a charge

pump to create an internal negative supply voltage.

This allows the headphone outputs of the MAX97000

to be biased at GND while operating from a single

supply (Figure 6). Without a DC component, there is

no need for the large DC-blocking capacitors. Instead

of two large (220FF, typ) capacitors, the MAX97000

charge pump requires three small ceramic capacitors,

V

DD

V

/ 2

DD

GND

CONVENTIONAL AMPLIFIER BIASING SCHEME

+V

DD

MAX97000

V

OUT

MAXIMUM THD+N

LEVEL

V

IN

Figure 5. Limiter Gain Curve

DirectDrive is a registered trademark of Maxim Integrated Products, Inc.

Figure 6. Traditional Amplifier Output vs. MAX97000

DirectDrive Output

DirectDrive AMPLIFIER BIASING SCHEME

SGND

-V

DD

21

Page 22

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

conserving board space, reducing cost, and improving

the frequency response of the headphone amplifier.

See the Output Power vs. Load Resistance graph in

the Typical Operating Characteristics for details of the

possible capacitor sizes. There is a low DC voltage on

the amplifier outputs due to amplifier offset. However,

the offset of the MAX97000 is typically Q0.15mV, which,

when combined with a 32I load, results in less than 5FA

of DC current flow to the headphones.

MAX97000

In addition to the cost and size disadvantages of

the DC-blocking capacitors required by conventional

headphone amplifiers, these capacitors limit the amplifier’s low-frequency response and can distort the audio

signal. Previous attempts at eliminating the output-coupling capacitors involved biasing the headphone return

(sleeve) to the DC bias voltage of the headphone amplifiers. This method raises some issues:

• The sleeve is typically grounded to the chassis.

Using the midrail biasing approach, the sleeve must

be isolated from system ground, complicating product design.

• During an ESD strike, the amplifier’s ESD structures

are the only path to system ground. Thus, the amplifier must be able to withstand the full energy from an

ESD strike.

• When using the headphone jack as a line out to

other equipment, the bias voltage on the sleeve may

conflict with the ground potential from other equipment, resulting in possible damage to the amplifiers.

Charge Pump

The MAX97000’s dual-mode charge pump generates

both the positive and negative power supply for the

headphone amplifier. To maximize efficiency, both the

charge pump’s switching frequency and output voltage

change based on signal level.

When the input signal level is less than 10% of VDD,

the switching frequency is reduced to a low rate. This

minimizes switching losses in the charge pump. When

the input signal exceeds 10% of VDD, the switching frequency increases to support the load current.

For input signals below 25% of VDD, the charge pump

generates Q(VDD/2) to minimize the voltage drop across

the amplifier’s power stage and thus improve efficiency.

Input signals that exceed 25% of VDD cause the charge

pump to output QVDD. The higher output voltage allows

for full output power from the headphone amplifier.

To prevent audible gliches when transitioning from the

Q(VDD/2) output mode to the QVDD output mode, the

charge pump transitions very quickly. This quick change

draws significant current from VDD for the duration of

the transition. The bypass capacitor on VDD supplies the

required current and prevents droop on VDD.

The charge pump’s dynamic switching mode can be

turned off through the I2C interface. The charge pump

can then be forced to output either Q(VDD/2) or QVDD

regardless of input signal level.

Class H Operation

A Class H amplifier uses a Class AB output stage with

power supplies that are modulated by the output signal.

In the case of the MAX97000, two nominal power-supply

differentials of 1.8V (+0.9V to -0.9V) and 3.6V (+1.8V

to -1.8V) are available from the charge pump. Figure 7

shows the operation of the output-voltage-dependent

power supply.

Low-Power Mode

To minimize power consumption when using the headphone amplifier, enable the low-power mode. In this

mode, the headphone mixers and volume control are

bypassed and shut down.

I2C Slave Address

The MAX97000 uses a slave address of 0x9A or

1001101RW. The address is defined as the 7 most

significant bits (MSBs) followed by the read/write bit.

Set the read/write bit to 1 to configure the MAX97000 to

read mode. Set the read/write bit to 0 to configure the

MAX97000 to write mode. The address is the first byte

of information sent to the MAX97000 after the START (S)

condition.

V

V

-0.9V

-1.8V

1.8V

0.9V

TH_H

TH_L

HPVDD

HPVSS

32ms

OUTPUT

VOLTAGE

32ms

22

Figure 7. Class H Operation

Page 23

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

I2C Registers

Nine internal registers program the MAX97000. Table

1 lists all the registers, their addresses, and power-onreset states. Register 0xFF indicates the device revision.

Table 1. Register Map

REGISTER B7 B6 B5 B4 B3 B2 B1 B0 ADDRESS DEFAULT R/W

STATUS

Input Gain INADIFF INBDIFF PGAINA PGAINB 0x00 0x00 R/W

Headphone

Mixers

Speaker Mixer 0 0 0 0 SPKMIX 0x02 0x00 R/W

Headphone

Left

Headphone

Right

Speaker FFM SPKM SPKVOL 0x05 0x00 R/W

Reserved 0 0 0 0 0 0 0 0 0x06 0x00 R/W

Limiter THDCLP 0 0 0 THDT1 0x07 0x00 R/W

Power

Management

Charge Pump 0 0 0 0 0 0 CPSEL FIXED 0x09 0x00 R/W

REVISION ID

Rev ID REV 0xFF 0x00 R

ZCD SLEW

LPGAIN 0 HPRM HPRVOL 0x04 0x00 R/W

SHDN

HPLMIX HPRMIX 0x01 0x00 R/W

HPLM HPLVOL 0x03 0x00 R/W

LPMODE SPKEN 0 HPLEN HPREN SWEN 0x08 0x01 R/W

Write zeros to all unused bits in the register table when

updating the register, unless otherwise noted. Tables 2

through 7 describe each bit.

MAX97000

Table 2. Input Register

REGISTER BIT NAME DESCRIPTION

Input A Differential Mode. Configures the input A channel as either a mono differential

signal (INA = INA2 - INA1) or as a stereo signal (INA1 = left, INA2 = right).

0 = Stereo single-ended

1 = Differential

Input B Differential Mode. Configures the input B channel as either a mono differential

signal (INB = INB2 - INB1) or as a stereo signal (INB1 = left, INB2 = right).

0 = Stereo single-ended

1 = Differential

Input A Preamp Gain. Set the input gain to maximize output signal level for a given input

signal range to improve the SNR of the system. PGAINA = 111 switches to a trimmed 20kI

feedback resistor for external gain setting.

VALUE

000

001

010

011

100

101

110

111

LEVEL (dB)

-6

-3

0

3

6

9

18

External

0x00

7 INADIFF

6 INBDIFF

5

4

PGAINA

3

23

Page 24

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Table 2. Input Register (continued)

REGISTER BIT NAME DESCRIPTION

Input B Preamp Gain. Set the input gain to maximize output signal level for a given input

2

1

PGAINB

MAX97000

0

Table 3. Mixer Registers

REGISTER BIT NAME DESCRIPTION

signal range to improve the SNR of the system. PGAINB = 111 switches to a trimmed 20kI

feedback resistor for external gain setting.

VALUE

000

001

010

011

100

101

110

111

LEVEL (dB)

-6

-3

0

3

6

9

18

External

Mixers

0x01

0x02

7

6

HPLMIX

5

4

3

2

HPRMIX

1

0

3

2

SPKMIX

1

0

Left Headphone Mixer. Selects which of the four inputs is routed to the left headphone output.

VALUE

0000

xxx1

xx1x

x1xx

1xxx

Right Headphone Mixer. Selects which of the four inputs is routed to the right headphone output.

VALUE

0000

xxx1

xx1x

x1xx

1xxx

Speaker Mixer. Selects which of the four inputs is routed to the speaker output.

VALUE

0000

xxx1

xx1x

x1xx

1xxx

INPUT

No input

INA1 (Disabled when INADIFF = 1)

INA2 (Select when INADIFF = 1)

INB1 (Disabled when INBDIFF = 1)

INB2 (Select when INBDIFF = 1)

INPUT

No input

INA1 (Disabled when INADIFF = 1)

INA2 (Select when INADIFF = 1)

INB1 (Disabled when INBDIFF = 1)

INB2 (Select when INBDIFF = 1)

INPUT

No input

INA1 (Disabled when INADIFF = 1)

INA2 (Select when INADIFF = 1)

INB1 (Disabled when INBDIFF = 1)

INB2 (Select when INBDIFF = 1)

24

Page 25

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Table 4. Volume Control Registers

REGISTER BIT NAME DESCRIPTION

Zero-Crossing Detection. Determines whether zero-crossing detection is used on all

volume control changes to reduce clicks and pops. Disabling zero-crossing detection

0x03

7

6

5 HPLM

4

ZCD

SLEW

allows volume changes to occur immediately.

0 = Enabled

1 = Disabled

Volume Slewing. Determines whether volume slewing is used on all volume control

changes to reduce clicks and pops. When enabled, volume changes cause the

MAX97000 to ramp through intermediate volume settings whenever a change to the

volume is made. If ZCD = 1, slewing occurs at a rate of 0.2ms per step. If ZCD = 0, slew

time depends on the input signal. Write a 1 to this bit to disable slewing and implement

volume changes immediately. This bit also activates soft-start at power-on and soft-stop

and power-off.

0 = Enabled

1 = Disabled

Left Headphone Mute

0 = Unmuted

1 = Muted

Left Headphone Volume

Volume Control

MAX97000

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

0x1E

0x1F

LEVEL (dB)

-12

-10

-8

-6

-4

-2

-1

0

1

2

3

4

4.5

5

5.5

6

VALUE

3

2

HPLVOL

1

0

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0A

0x0B

0x0C

0x0D

0x0E

0x0F

LEVEL (dB)

-64

-60

-56

-52

-48

-44

-40

-37

-34

-31

-28

-25

-22

-19

-16

-14

VALUE

0x1A

0x1B

0x1C

0x1D

25

Page 26

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Table 4. Volume Control Registers (continued)

REGISTER BIT NAME DESCRIPTION

Low-Power Mode Gain. Controls the headphone amplifier gain when LPMODE ≠ 0.

7 LPGAIN

5 HPRM

MAX97000

0x04

0x05

4

3

2

1

0

7 FFM

6 SPKM

5

4

3

2

1

0

HPRVOL

SPKVOL

0 = 0dB

1 = 3dB

Right Headphone Mute

0 = Unmuted

1 = Muted

Right Headphone Volume

0x10

0x11

0x12

0x13

0x14

0x15

0x16

0x17

0x18

0x19

VALUE

0x26

0x27

0x28

0x29

0x2A

0x2B

0x2C

0x2D

0x2E

0x2F

0x30

0x31

0x32

0x33

LEVEL (dB)

-12

-10

-8

-6

-4

-2

-1

0

1

2

3

4

4.5

5

5.5

6

LEVEL (dB)

3

4

5

6

7

8

9

10

11

12

12.5

13

13.5

14

VALUE

VALUE

0x0A

0x0B

0x0C

0x0D

0x0E

Fixed-Frequency Oscillation. Removes spread spectrum from the class D oscillator.

0 = Spread-spectrum mode

1 = Fixed-frequency mode

Speaker Mute

0 = Unmuted

1 = Mute

Speaker Volume

VALUE

0x00–0x18

0x00

0x01

0x02

0x03

0x04

0x05

0x06

0x07

0x08

0x09

0x0F

0x19

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x20

0x21

0x22

0x23

0x24

0x25

LEVEL (dB)

-64

-60

-56

-52

-48

-44

-40

-37

-34

-31

-28

-25

-22

-19

-16

-14

LEVEL (dB)

-30

-26

-22

-18

-14

-12

-10

-8

-6

-4

-2

0

1

2

VALUE

0x1A

0x1B

0x1C

0x1D

0x1E

0x1F

0x34

0x35

0x36

0x37

0x38

0x39

0x3A

0x3B

0x3C

0x3D

0x3E

0x3F

LEVEL (dB)

14.5

15

15.5

16

16.5

17

17.5

18

18.5

19

19.5

20

26

Page 27

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Table 5. Distortion Limiter Register

REGISTER BIT NAME DESCRIPTION

Distortion Limiter

MAX97000

Distortion Limit

VALUE

0001–1001

Distortion Release Time Constant

0 = 1.4s

1 = 2.8s

0000

1010

1011

1100

1101

1110

1111

THD LIMIT (%)

Disabled

P 4

P 5

P 6

P 8

P 11

P 12

P 15

0x07

7

6

THDCLP

5

4

0 THDT1

Table 6. Power Management Register

REGISTER BIT NAME DESCRIPTION

Software Shutdown

0 = Device disabled

1 = Device enabled

Low-Power Headphone Mode. Enables low-power headphone mode. When activated

this mode directly connects the selected channel to the headphone amplifiers,

bypassing the mixers and the volume control. Additionally, low-power mode disables the

speaker path.

VALUE

Speaker Amplifier Enable

0 = Disabled

1 = Enabled

Left Headphone Amplifier Enable

0 = Disabled

1 = Enabled

Right Headphone Amplifier Enable

0 = Disabled

1 = Enabled

Analog Switch

0 = Open

1 = Closed

INPUT

Disabled

00

INA (SE) Connected to the headphone output

01

INB (SE) Connected to the headphone output

10

INA (Diff) to HPL and INB (Diff) to HPR

11

0x08

7

6

5

4 SPKEN

2 HPLEN

1 HPREN

0 SWEN

SHDN

LPMODE

Power Management

27

Page 28

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Charge-Pump Control

Table 7. Charge-Pump Control Register

REGISTER BIT NAME DESCRIPTION

Charge-Pump Output Select. Works with the FIXED to set Q1.8V or Q0.9V outputs on

1 CPSEL

0x09

MAX97000

0 FIXED

HPVDD and HPVSS. Ignored when FIXED = 0.

0 = Q1.8V on HPVDD/HPVSS

1 = Q0.9V on HPVDD/HPVSS

Class H Mode. When enabled, this bit forces the charge pump to generate static power

rails for HPVDD and HPVSS, instead of dynamically adjusting them based on output

signal level.

0 = Class H mode

1 = Fixed-supply mode

I2C Serial Interface

The MAX97000 features an I2C/SMBusK-compatible,

2-wire serial interface consisting of a serial-data line

(SDA) and a serial-clock line (SCL). SDA and SCL

facilitate communication between the MAX97000 and the

master at clock rates up to 400kHz. Figure 1 shows the

2-wire interface timing diagram. The master generates

SCL and initiates data transfer on the bus. The master

device writes data to the MAX97000 by transmitting the

proper slave address followed by the register address

and then the data word. Each transmit sequence is

framed by a START (S) or REPEATED START (Sr) condition and a STOP (P) condition. Each word transmitted

to the MAX97000 is 8 bits long and is followed by an

acknowledge clock pulse. A master reading data from

the MAX97000 transmits the proper slave address followed by a series of nine SCL pulses. The MAX97000

transmits data on SDA in sync with the master-generated

SCL pulses. The master acknowledges receipt of each

byte of data. Each read sequence is framed by a START

or REPEATED START condition, a not acknowledge, and

a STOP condition. SDA operates as both an input and an

open-drain output. A pullup resistor, typically greater than

500I, is required on SDA. SCL operates only as an input.

A pullup resistor, typically greater than 500I, is required

on SCL if there are multiple masters on the bus, or if

the single master has an open-drain SCL output. Series

resistors in line with SDA and SCL are optional. Series

resistors protect the digital inputs of the MAX97000 from

high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

Bit Transfer

One data bit is transferred during each SCL cycle. The

data on SDA must remain stable during the high period of

the SCL pulse. Changes in SDA while SCL is high are control signals (see the START and STOP Conditions section).

S Sr P

SCL

SDA

Figure 8. START, STOP, and REPEATED START Conditions

START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A

master initiates communication by issuing a START condition. A START condition is a high-to-low transition on

SDA with SCL high. A STOP condition is a low-to-high

transition on SDA while SCL is high (Figure 8). A START

condition from the master signals the beginning of a

transmission to the MAX97000. The master terminates

transmission and frees the bus by issuing a STOP condition. The bus remains active if a REPEATED START

condition is generated instead of a STOP condition.

Early STOP Conditions

The MAX97000 recognizes a STOP condition at any point

during data transmission except if the STOP condition

occurs in the same high pulse as a START condition. For

proper operation, do not send a STOP condition during

the same SCL high pulse as the START condition.

Slave Address

The slave address is defined as the seven most significant bits (MSBs) followed by the read/write bit. For the

MAX97000 the seven most significant bits are 1001101.

Setting the read/write bit to 1 (slave address = 0x9B) configures the MAX97000 for read mode. Setting the read/write

bit to 0 (slave address = 0x9A) configures the MAX97000

for write mode. The address is the first byte of information

sent to the MAX97000 after the START condition.

SMBus is a trademark of Intel Corp.

28

Page 29

Audio Subsystem with Mono Class D

Speaker and Class H Headphone Amplifier

Acknowledge

The acknowledge bit (ACK) is a clocked 9th bit that

the MAX97000 uses to handshake receipt each byte

of data when in write mode (Figure 9). The MAX97000

pulls down SDA during the entire master-generated 9th

clock pulse if the previous byte is successfully received.

Monitoring ACK allows for detection of unsuccessful

data transfers. An unsuccessful data transfer occurs

if a receiving device is busy or if a system fault has