General Description

The MAX9420–MAX9423 are extremely fast, low-skew

quad LVECL-to-LVPECL translators designed for highspeed signal and clock driver applications. The

devices feature ultra-low propagation delay of 336ps

and channel-to-channel skew of 17ps.

The four channels can be operated synchronously with

an external clock, or in asynchronous mode, determined by the state of the SEL input. An enable input

provides the ability to force all the outputs to a differential low state.

These devices operate with a negative supply voltage

of -2.0V to -3.6V, compatible with LVECL input signals.

The positive supply range is 2.375V to 3.6V for differential LVPECL output signals.

A variety of input and output terminations are offered for

maximum design flexibility. The MAX9420 has open

inputs and open-emitter outputs. The MAX9421 has

open inputs and 50Ω series outputs. The MAX9422 has

100Ω differential input impedance and open-emitter

outputs. The MAX9423 has 100Ω differential input

impedance and 50Ω series outputs.

The MAX9420–MAX9423 are specified for operation

from -40°C to +85°C, and are offered in space-saving

32-pin 5mm ✕ 5mm TQFP and 32-lead 5mm ✕ 5mm

QFN packages.

Applications

Data and Clock Driver and Buffer

Central Office Backplane Clock Distribution

DSLAM Backplane

Base Station

ATE

Features

♦ >500mV Differential Output at 3.0GHz Clock

♦ 336ps (typ) Propagation Delay in Asynchronous

Mode

♦ 17ps (typ) Channel-to-Channel Skew

♦ Integrated 50Ω Outputs (MAX9421/MAX9423)

♦ Integrated 100Ω Inputs (MAX9422/MAX9423)

♦ Synchronous/Asynchronous Operation

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

________________________________________________________________ Maxim Integrated Products 1

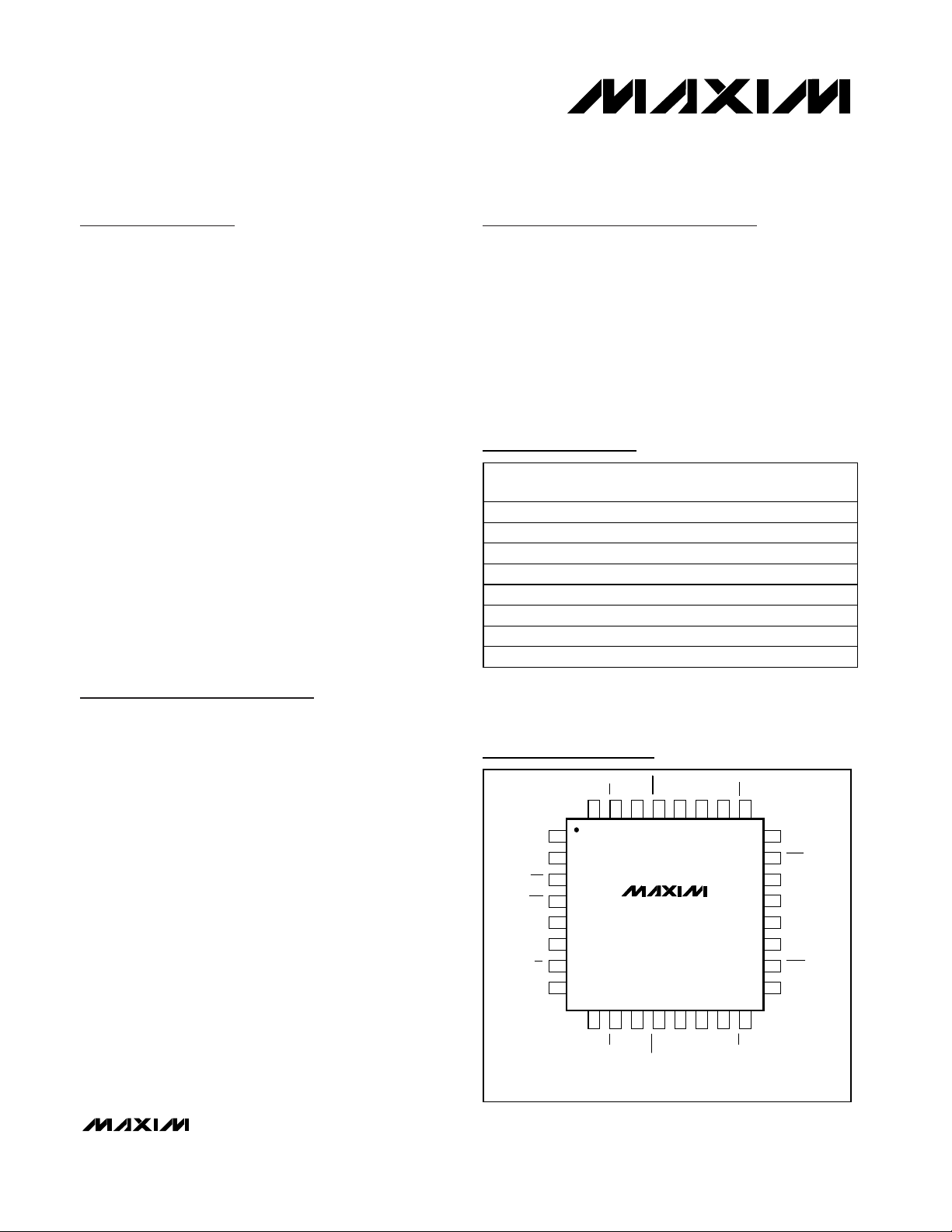

Ordering Information

TQFP (5mm x 5mm)

TOP VIEW

32 28

293031

25

26

27

IN0

VCCOUT0

OUT0

IN0

GND

IN1

IN1

10

13

15

14

1611 12

9

IN3

V

CC

IN3

OUT3

OUT3

IN2

GND

IN2

17

18

19

20

21

22

23

OUT1

24 V

CC

OUT1

GND

GND

OUT2

OUT2

V

CC

2

3

4

5

6

7

8V

EE

EN

EN

CLK

CLK

SEL

SEL

1V

EE

MAX9420

MAX9421

MAX9422

MAX9423

Pin Configurations

19-2285; Rev 0; 1/02

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at

1-888-629-4642, or visit Maxim’s website at www.maxim-ic.com.

Functional Diagram appears at end of data sheet.

Pin Configurations continued at end of data sheet.

*Future product—contact factory for availability.

PART

TEMP

RANGE

MAX9420EHJ -40°C to +85°C 32 TQFP Open Open

MAX9420EGJ* -40°C to +85°C 32 QFN Open Open

MAX9421EHJ -40°C to +85°C 32 TQFP Open 50Ω

MAX9421EGJ* -40°C to +85°C 32 QFN Open 50Ω

MAX9422EHJ -40°C to +85°C 32 TQFP 100Ω Open

MAX9422EGJ* -40°C to +85°C 32 QFN 100Ω Open

MAX9423EHJ -40°C to +85°C 32 TQFP 100Ω 50Ω

MAX9423EGJ* -40°C to +85°C 32 QFN 100Ω 50Ω

PIN-

PACKAGE

DATA

INPUT

OUTPUT

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

2 _______________________________________________________________________________________

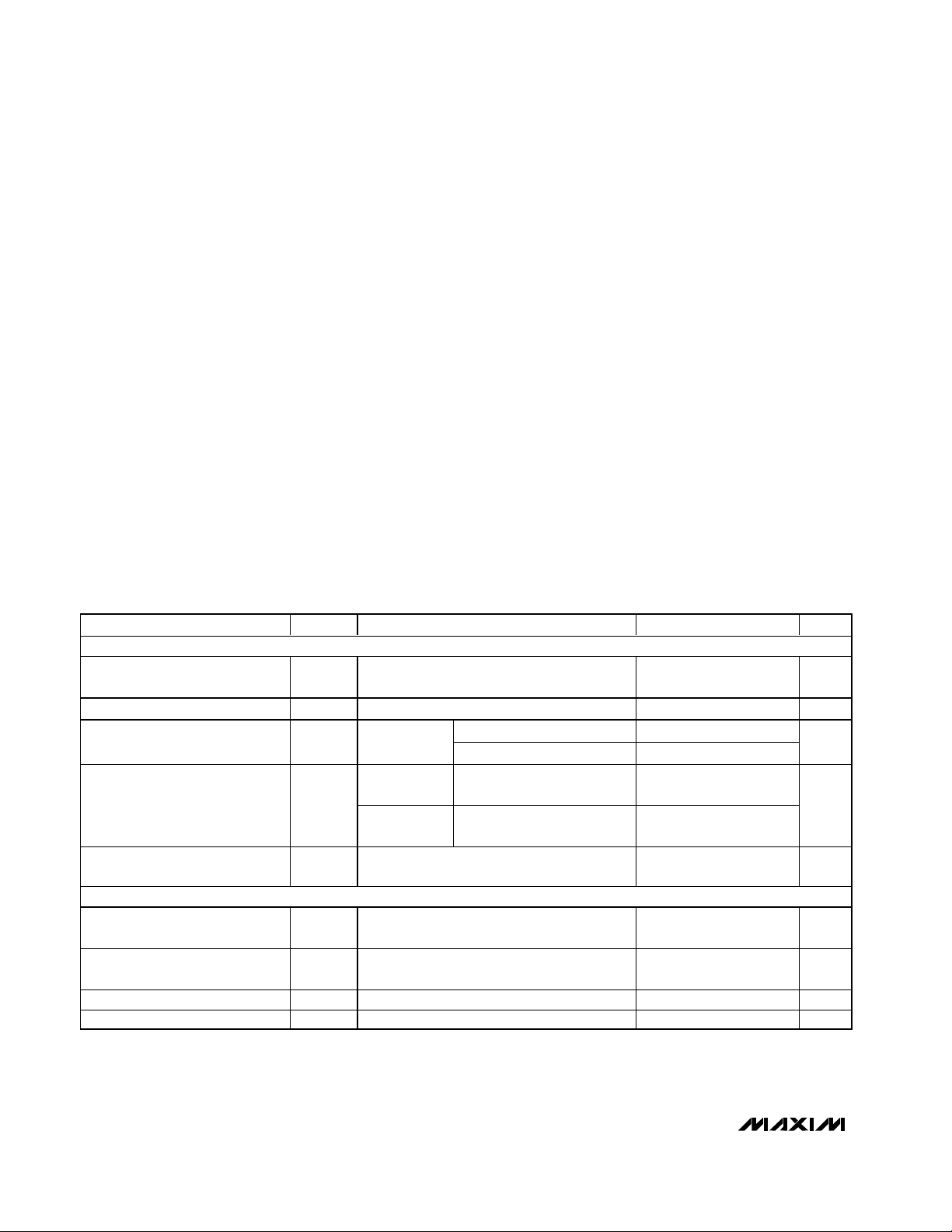

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(VEE= -2.0V to -3.6V, VCC= 2.375V to 3.6V, GND = 0, MAX9420/MAX9422 outputs terminated with 50Ω ±1% to VCC- 2.0V. Typical values are at V

EE

= -3.3V, VCC= 3.3V, TA= +25°C, V

IHD

= -0.9V, V

ILD

= -1.7V, unless otherwise noted.) (Notes 1, 2, and 3)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VCCto GND...........................................................-0.3V to +4.1V

V

EE

to GND............................................................-4.1V to +0.3V

Inputs to GND .............................................(V

EE

- 0.3V) to +0.3V

Differential Input Voltage .......................................................±3V

Continuous Output Current .................................................50mA

Surge Output Current........................................................100mA

Continuous Power Dissipation (T

A

= +70°C)

Single-Layer PC Board

32-Pin 5mm

✕ 5mm TQFP

(derate 9.5mW/°C above +70°C)................................761mW

32-Lead 5mm

✕ 5mm QFN

(derate 21.3mW/°C above +70°C).................................1.7W

Junction-to-Ambient Thermal Resistance in Still Air

32-Pin 5mm

✕ 5mm TQFP......................................+105°C/W

32-Lead 5mm

✕ 5mm QFN......................................+47°C/W

Junction-to-Ambient Thermal Resistance with 500

LFPM Airflow

32-Pin 5mm

✕ 5mm TQFP.........................................+73°C/W

Junction-to-Case Thermal Resistance

32-Pin 5mm

✕ 5mm TQFP.........................................+25°C/W

32-Lead 5mm

✕ 5mm QFN.........................................+2°C/W

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

ESD Protection

Human Body Model (IN_, IN_) ........................................500V

Others.............................................................................1.2kV

Lead Temperature (soldering, 10s) .................................+300°C

LVECL INPUTS (IN_, IN_, CLK, CLK, EN, EN, SEL, SEL)

Differential Input High Voltage V

Differential Input Low Voltage V

Differential Input Voltage V

Input Current IIH, I

Differential Input Resistance

(IN, IN)

LVPECL OUTPUTS (OUT_, OUT_)

Differential Output Voltage

Output Common-Mode Voltage V

Internal Current Source I

Output Impedance R

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

IHD

ILD

ID

Figure 1

Figure 1 V

Figure 1

MAX9420/

MAX9421

IL

MAX9422/

MAX9423

MAX9422/MAX9423 86 100 114 Ω

IN

Figure 1 600 660 mV

OL

Figure 1

MAX9421/MAX9423, Figure 2 6.5 8.2 10.0 mA

MAX9421/MAX9423, Figure 2 40 50 60 Ω

V

V

SINK

R

OH

OCM

OUT

V

+

EE

1.4

EE

VEE ≤ -3.0V 0.2 3.0

> -3.0V 0.2 V

V

EE

EN, EN, SEL, SEL , IN_, IN_,

CLK, or CLK = V

IHD

or V

ILD

EN, EN, SEL, SEL, CLK, or

CLK = V

IHD

or V

ILD

-10 25

-10 25

V

-

CC

1.5

VCC -

1.25

VCC -

0V

-0.2 V

EE

1.1

V

µA

V

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

_______________________________________________________________________________________ 3

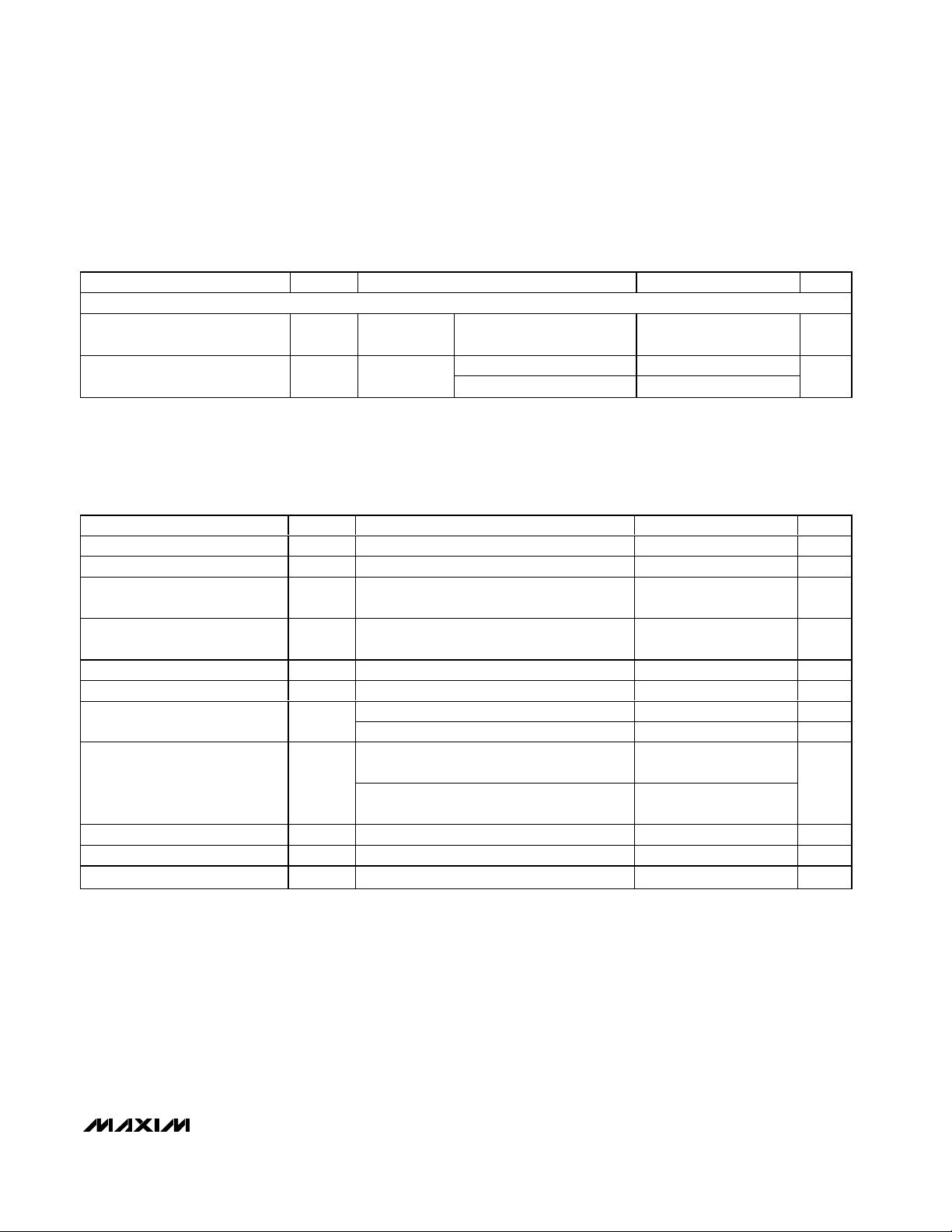

DC ELECTRICAL CHARACTERISTICS (continued)

(VEE= -2.0V to -3.6V, VCC= 2.375V to 3.6V, GND = 0, MAX9420/MAX9422 outputs terminated with 50Ω ±1% to VCC- 2.0V. Typical values are at V

EE

= -3.3V, VCC= 3.3V, TA= +25°C, V

IHD

= -0.9V, V

ILD

= -1.7V, unless otherwise noted.) (Notes 1, 2, and 3)

AC ELECTRICAL CHARACTERISTICS

(VEE= -2.0V to -3.6V, VCC= 2.375V to 3.6V, GND = 0, outputs terminated with 50Ω ±1% to VCC- 2.0V. For SEL = high, CLK = high

or low, f

IN

= 2.0GHz. For SEL = low, FIN= 1.5GHz, CLK = 3.0GHz, input transition time = 125ps (20% to 80%), V

IHD

= VEE+ 1.4V to

0, V

ILD

= VEEto -0.2V, V

IHD

- V

ILD

= 0.2V to the smaller of 3.0V or |VEE|. Typical values are at VEE= -3.3V, VCC= 3.3V, GND = 0, T

A

= +25°C, V

IHD

= -0.9V, V

ILD

= -1.7V, unless otherwise noted.) (Note 4)

)

)

(

)

(

)

(

)

POWER SUPPLY

Negative Supply Current I

Positive Supply Current I

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

EE

CC

OUT_, OUT_

open

OUT_, OUT_

open

MAX9421/MAX9422/

MAX9423

710mA

MAX9421/MAX9423 153 -180

MAX9420/MAX9422 87 105

mA

IN-to-OUT Differential

CLK-to-OUT Differential

IN-to-OUT Channel-to-Channel

Skew (Note 5)

CLK-to-OUT Channel-toChannel Skew (Note 5)

Maximum Clock Frequency f

Maximum Data Frequency f

Added Random Jitter (Note 6) t

Added Deterministic Jitter

(Note 6)

IN-to-CLK Setup Time t

CLK-to-IN Hold Time t

Output Rise Time t

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

t

P LH 1, tP H L 1

t

P LH 2, tP H L 2

t

SKD1

t

SKD2

CLK(MAX

IN(MAX

RJ

t

DJ

SEL = high, Figure 3 250 336 450 ps

SEL = low, Figure 4 350 506 575 ps

SEL = high 17 60 ps

SEL = low 17 55 ps

V

VOL ≥ 500mV, SEL = low 3.0 GHz

OH

-

V

VOL ≥ 400mV, SEL = high 2 GHz

OH

-

SEL = low, f

SEL = high, fIN = 2GHz 0.53 1.0 ps

SEL = low, f

23

- 1 PRBS pattern

2

SEL = high, IN_ = 3.0Gbps 223 - 1 PRBS

= 3.0GHz, fIN = 1.5GHz 0.65 1.0 ps

CLK

= 3.0GHz, IN_ = 3.0Gbps,

CLK

pattern

Figure 4 80 ps

S

H

Figure 4 80 ps

Figure 3 90 120 ps

R

28 45

23 45

RMS

RMS

ps

P-P

AC ELECTRICAL CHARACTERISTICS (continued)

(VEE= -2.0V to -3.6V, VCC= 2.375V to 3.6V, GND = 0, outputs terminated with 50Ω ±1% to VCC- 2.0V. For SEL = high, CLK = high

or low, f

IN

= 2.0GHz. For SEL = low, FIN= 1.5GHz, CLK = 3.0GHz, input transition time = 125ps (20% to 80%), V

IHD

= VEE+ 1.4V to

0, V

ILD

= VEEto -0.2V, V

IHD

- V

ILD

= 0.2V to the smaller of 3.0V or |VEE|. Typical values are at VEE= -3.3V, VCC= 3.3V, GND = 0, T

A

= +25°C, V

IHD

= -0.9V, V

ILD

= -1.7V, unless otherwise noted.) (Note 4)

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

4 _______________________________________________________________________________________

Typical Operating Characteristics

(VEE= -3.3V, VCC= 3.3V, GND = 0, MAX9420/MAX9422 outputs terminated with 50Ω ±1% to VCC- 2.0V, SEL = high, f

CLK

= 3.0GHz,

fIN= 1.5GHz, input transition time = 125ps (20% to 80%), V

IHD

= -0.9V, V

ILD

= -1.7V, TA= +25°C, unless otherwise noted.)

Note 1: Measurements are made with the device in thermal equilibrium.

Note 2: Current into a pin is defined as positive. Current out of a pin is defined as negative.

Note 3: DC parameters are production tested at +25°C. DC limits are guaranteed by design and characterization over the full oper-

ating temperature range.

Note 4: Guaranteed by design and characterization. Limits are set to ±6 sigma.

Note 5: Measured between outputs of the same part at the signal crossing points for a same-edge transition.

Note 6: Device jitter added to the input signal.

Output Fall Time t

Propagation Delay Temperature

Coefficient

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Figure 3 90 120 ps

F

∆tPD/

∆T

0.2 1 ps/°C

SUPPLY CURRENT (ICC)

vs. TEMPERATURE

100

MAX9420/MAX9422

SEL = HIGH

95

OUTPUTS NOT TERMINATED

90

85

80

SUPPLY CURRENT (mA)

75

70

-40 10-15 35 60 85

TEMPERATURE (°C)

9

MAX9420 toc01

8

7

6

OUTPUT AMPLITUDE (mV)

5

4

-40 10-15 35 60 85

OUTPUT RISE/FALL TIME

vs. TEMPERATURE

100

MAX9420/MAX9422

SEL = HIGH

95

t

90

85

OUTPUT RISE/FALL TIME (ps)

80

75

-40 10-15 35 60 85

TEMPERATURE (°C)

R

t

F

370

360

MAX9420 toc04

350

340

330

320

PROPAGATION DELAY (ps)

310

300

290

-40 10-15 35 60 85

SUPPLY CURRENT (IEE)

vs. TEMPERATURE

MAX9420/MAX9422

SEL = HIGH

OUTPUTS NOT TERMINATED

TEMPERATURE (°C)

IN-TO-OUT PROPAGATION DELAY

vs. TEMPERATURE

MAX9420/MAX9422

SEL = HIGH

t

PLH1

t

PHL1

TEMPERATURE (°C)

1000

MAX9420 toc02

800

600

400

OUTPUT AMPLITUDE (mV)

200

0

0 1000500 1500 2000 2500 3000 3500

600

575

MAX9420 toc05

550

525

500

475

PROPAGATION DELAY (ps)

450

425

-40 10-15 35 60 85

OUTPUT AMPLITUDE (VOH - VOL)

vs. FREQUENCY

MAX9420/MAX9422

SEL = HIGH

IN_ FREQUENCY (MHz)

CLK-TO-OUT PROPAGATION DELAY

vs. TEMPERATURE

MAX9420/MAX9422

SEL = LOW

TEMPERATURE (°C)

t

PLH2

t

PHL2

MAX9420 toc03

MAX9420 toc06

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

_______________________________________________________________________________________ 5

Pin Description

PIN NAME FUNCTION

1, 8 V

2 SEL

3 SEL Inverting Differential Select Input

4 CLK

5 CLK Noninverting Differential Clock Input

6EN

7 EN Inverting Differential Output Enable Input

9 IN3 Noninverting Differential Input 3

10 IN3 Inverting Differential Input 3

11, 17,

24, 30

12 OUT3 Inverting Differential Output 3

13 OUT3 Noninverting Differential Output 3

14, 20,

21, 27

15 IN2 Noninverting Differential Input 2

16 IN2 Inverting Differential Input 2

18 OUT2 Inverting Differential Output 2

19 OUT2 Noninverting Differential Output 2

22 OUT1 Noninverting Differential Output 1

23 OUT1 Inverting Differential Output 1

25 IN1 Inverting Differential Input 1

26 IN1 Noninverting Differential Input 1

28 OUT0 Noninverting Differential Output 0

29 OUT0 Inverting Differential Output 0

31 IN0 Inverting Differential Input 0

32 IN0 Noninverting Differential Input 0

— EP Exposed Paddle (MAX942_EGJ only). Connected to VEE internally. See package dimensions.

V

GND Ground

Negative Supply Voltage. Bypass VEE to GND with 0.1µF and 0.01µF ceramic capacitors. Place the

EE

capacitors as close to the device as possible with the smaller value capacitor closest to the device.

Noninverting Differential Select Input. Setting SEL = high and SEL = low (differential high) enables all four

channels to operate asynchronously. Setting SEL = low and SEL = high (differential low) enables all four

channels to operate in synchronous mode.

Inverting Differential Clock Input. A rising edge on CLK (and falling on CLK) transfers data from the inputs to

the outputs when SEL = differential low.

Noninverting Differential Output Enable Input. Setting EN = high and EN = low (differential high) enables the

outputs. Setting EN = low and EN = high (differential low) drives the output low.

Positive Supply Voltage. Bypass VCC to GND with 0.1µF and 0.01µF ceramic capacitors. Place the

CC

capacitors as close to the device as possible with the smaller value capacitor closest to the device.

MAX9420–MAX9423

Detailed Description

The MAX9420–MAX9423 are extremely fast, low-skew

quad LVECL-to-LVPECL translators designed for highspeed signal and clock driver applications. The

devices feature ultra-low propagation delay of 336ps

and channel-to-channel skew of 17ps.

The four channels can be operated synchronously with

an external clock, or in asynchronous mode, determined by the state of the SEL input. An enable input

provides the ability to force all the outputs to a differential low state.

These devices operate with a negative supply voltage

of -2.0V to -3.6V, compatible with LVECL input signals.

The positive supply range is 2.375V to 3.6V for differential LVPECL output signals.

A variety of input and output terminations are offered

for maximum design flexibility. The MAX9420 has open

inputs and open-emitter outputs. The MAX9421 has

open inputs and 50Ω series outputs. The MAX9422 has

100Ω differential input impedance and open-emitter

outputs. The MAX9423 has 100Ω differential input

impedance and 50Ω series outputs.

Supply Voltages

For interfacing to differential LVECL input levels, the

VEErange is -2.0V to -3.6V with GND = 0. The V

CC

range is from 2.375V to 3.6V, compatible with LVPECL

logic. Output levels are referenced to VCC.

Data Inputs

The MAX9420/MAX9421 have open inputs and require

external termination. The MAX9422/MAX9423 have integrated 100Ω differential input termination resistors from

IN_ to IN_, reducing external component count.

Outputs

The MAX9421/MAX9423 have internal 50Ω series output termination resistors and 8mA internal pulldown

current sources. Using integrated resistors reduces

external component count.

The MAX9420/MAX9422 have open-emitter outputs. An

external termination is required. See the Output

Termination section.

Enable

Setting EN = high and EN = low enables the device.

Setting EN = low and EN = high forces the outputs to a

differential low. All changes on CLK, SEL, and IN_ are

ignored.

Asynchronous Operation

Setting SEL = high and SEL = low enables the four

channels to operate independently as LVECL-toLVPECL translators. The CLK signal is ignored in this

mode. In asynchronous mode, the CLK signal should

be set to either logic low or high state to minimize noise

coupling.

Synchronous Operation

Setting SEL = low and SEL = high enables all four

channels to operate in synchronized mode. In this

mode, buffered inputs are clocked into flip-flops simultaneously on the rising edge of the differential clock

input (CLK and CLK).

Differential Signal Input Limit

The maximum signal magnitude of all the differential

inputs is 3.0V.

Quad Differential LVECL-to-LVPECL Translators

6 _______________________________________________________________________________________

Figure 1. Input and Output Voltage Definitions

GND

V

ID

V

ID

V

EE

INPUT VOLTAGE DEFINITION OUTPUT VOLTAGE DEFINITION

V

= 0

ID

V

= 0

ID

V

(MAX) V

IHD

V

(MAX)

ILD

V

- V

OH

OL

V

(MIN)

IHD

V

(MIN)

ILD

V

OCM

CC

V

OH

V

OL

GND

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

_______________________________________________________________________________________ 7

Figure 2. Input and Output Configurations

Figure 3. IN-to-OUT Propagation Delay Timing Diagram

IN_

IN_

MAX9420/MAX9421 MAX9422/MAX9423

MAX9420/MAX9422

V

CC

OUT_

OUT_

I

SINK

IN_

IN_

R

OUT

R

OUT

I

SINK

MAX9421/MAX9423

100kΩ

V

CC

OUT_

OUT_

V

EE

IN_

IN_

t

PLH1

OUT_

OUT_

20% 20%

OUT_ - OUT_

DIFFERENTIAL OUTPUT

WAVEFORM

V

- V

IHD

ILD

t

PHL1

VOH - V

OL

80%

t

R

VOH - V

VOH - V

OL

OL

80%

t

F

SEL = HIGH

EN = HIGH

Applications Information

Input Bias

Unused inputs should be biased or driven as shown in

Figure 5. This avoids noise coupling that might cause

toggling at the unused outputs.

Output Termination

Terminate open-emitter outputs (MAX9420/MAX9422)

through 50Ω to VCC- 2V or use an equivalent Thevenin

termination. Terminate outputs using identical termination on each for the lowest output-to-output skew. When

a single-ended signal is taken from a differential output,

terminate both outputs. For example, if OUT_ is used as

a single-ended output, terminate both OUT_ and OUT_.

Ensure that the output currents do not exceed the current limits as specified in the Absolute Maximum

Ratings table. Under all operating conditions, the

device’s total thermal limits should be observed.

Power-Supply Bypassing

Adequate power-supply bypassing is necessary to

maximize the performance and noise immunity. Bypass

VCCto GND and VEEto GND with high-frequency surface-mount ceramic 0.1µF and 0.01µF capacitors in

parallel as close to the device as possible, with the

0.01µF capacitor closest to the device pins. Use multi-

ple parallel vias for ground-plane connection to minimize inductance.

Circuit Board Traces

Input and output trace characteristics affect the performance of the MAX9420–MAX9423. Connect each of the

inputs and outputs to a 50Ω characteristic impedance

trace. Avoid discontinuities in differential impedance

and maximize common-mode noise immunity by maintaining the distance between differential traces and

avoid sharp corners. Minimize the number of vias to

prevent impedance discontinuities. Reduce the reflections by maintaining 50Ω characteristic impedance

through connectors and across cables. Minimize skew

by matching the electrical length of the traces.

Chip Information

TRANSISTOR COUNT: 927

PROCESS: Bipolar

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

8 _______________________________________________________________________________________

Figure 4. CLK-to-OUT Propagation Delay Timing Diagram

CLK

V

- V

IHD

ILD

CLK

t

H

IN_

IN_

t

PLH2

OUT_

OUT_

t

S

V

- V

IHD

ILD

VOH - V

t

H

t

PHL2

OL

SEL = LOW

EN = HIGH

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

_______________________________________________________________________________________ 9

Figure 5. Input Bias Circuits for Unused Inputs

IN3

32

31

30

29

28

27

26

IN0

IN0

V

CC

OUT0

OUT0

GND

IN1

IN1

25

9

10

11

12

13

14

15

IN3

V

CC

OUT3

OUT3

GND

IN2

16

IN2

17

18

19

20

21

22

23

V

CC

*EXPOSED PADDLE AND CORNER PINS ARE CONNECTED TO V

EE

LEAD UNDER PACKAGE.

**

**

OUT2

OUT2

GND

GND

OUT1

OUT1

8

7

6

5

4

3

2

V

EE

EN

EN

CLK

CLK

SEL

SEL

QFN-EP*

1V

EE

24 V

CC

TOP VIEW

MAX9420

MAX9421

MAX9422

MAX9423

Pin Configurations (continued)

V

IN_

IN_

IN_

IN_

100Ω

100Ω

GND

MAX9420

1kΩ

1kΩ

1/4

MAX9421

V

EE

V

CC

CC

IN_

OUT_

OUT_

OUT_

100Ω

OUT_

OUT_

IN_

MAX9422

1kΩ

1/4

MAX9423

V

EE

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

10 ______________________________________________________________________________________

Functional Diagram

IN0

IN0

1

DQ

D

IN1

IN1

DQ

D

IN2

IN2

DQ

D

IN3

IN3

DQ

D

Q

CK

CK

Q

CK

CK

Q

CK

CK

Q

CK

CK

0

1

0

1

0

1

0

OUT0

OUT0

OUT1

OUT1

OUT2

OUT2

OUT3

OUT3

CLK

CLK

SEL

SEL

EN

EN

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

______________________________________________________________________________________ 11

Package Information

32L TQFP, 5x5x01.0.EPS

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

12 ______________________________________________________________________________________

Package Information (continued)

MAX9420–MAX9423

Quad Differential LVECL-to-LVPECL Translators

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 13

© 2002 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Package Information (continued)

Loading...

Loading...