Page 1

General Description

The MAX9209/MAX9213 serialize 21 bits of LVTTL/

LVCMOS parallel input data to three LVDS outputs. A

parallel rate clock on a fourth LVDS output provides

timing for deserialization.

The MAX9209/MAX9213 feature programmable DC balance, which allows isolation between the serializer and

deserializer using AC-coupling. The DC balance circuits

on each channel code the data, limiting the imbalance

of transmitted ones and zeros to a defined range. The

companion MAX9210/MAX9214 deserializers decode

the data. When DC balance is not programmed, the

serializers are compatible with non-DC-balanced, 21-bit

serializers such as the DS90CR215 and DS90CR217.

Two frequency ranges and two DC-balance default

conditions are available for maximum replacement flexibility and compatibility with existing non-DC-balanced

serializers.

The MAX9209/MAX9213 are available in TSSOP and

space-saving TQFN packages.

Applications

Automotive Navigation Systems

Automotive DVD Entertainment Systems

Digital Copiers

Laser Printers

Features

o Programmable DC-Balanced or Non-DC-Balanced

Operation

o DC Balance Allows AC-Coupling for Ground-Shift

Tolerance

o As Low as 8MHz Operation

o Pin Compatible with DS90CR215 and DS90CR217

in Non-DC-Balanced Mode

o Integrated 110Ω (DC-Balanced) and 410Ω (Non-

DC-Balanced) Output Resistors

o 5V Tolerant LVTTL/LVCMOS Data Inputs

o PLL Requires No External Components

o Up to 1.785Gbps Throughput

o LVDS Outputs Meet IEC 61000-4-2 and ISO 10605

Requirements

o LVDS Outputs Conform to ANSI TIA/EIA-644

LVDS Standard

o Low-Profile 48-Lead TSSOP and Space-Saving

TQFN Packages

o -40°C to +85°C Operating Temperature Range

o +3.3V Supply

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

________________________________________________________________

Maxim Integrated Products

1

Ordering Information

19-2828; Rev 5; 3/12

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

+

Denotes a lead(Pb)-free/RoHS-compliant package.

/V denotes an automotive qualified part.

*EP = Exposed pad.

EVALUATION KIT

AVAILABLE

PART TEMP. RANGE PIN-PACKAGE

-40°C to +85°C 48 TSSOP

-40°C to +85°C 48 TSSOP

-40°C to +105°C 48 TSSOP

MAX9213ETM+ -40°C to +85°C 48 TQFN-EP*

MAX9213EUM+ -40°C to +85°C 48 TSSOP

Pin Configurations appear at end of data sheet.

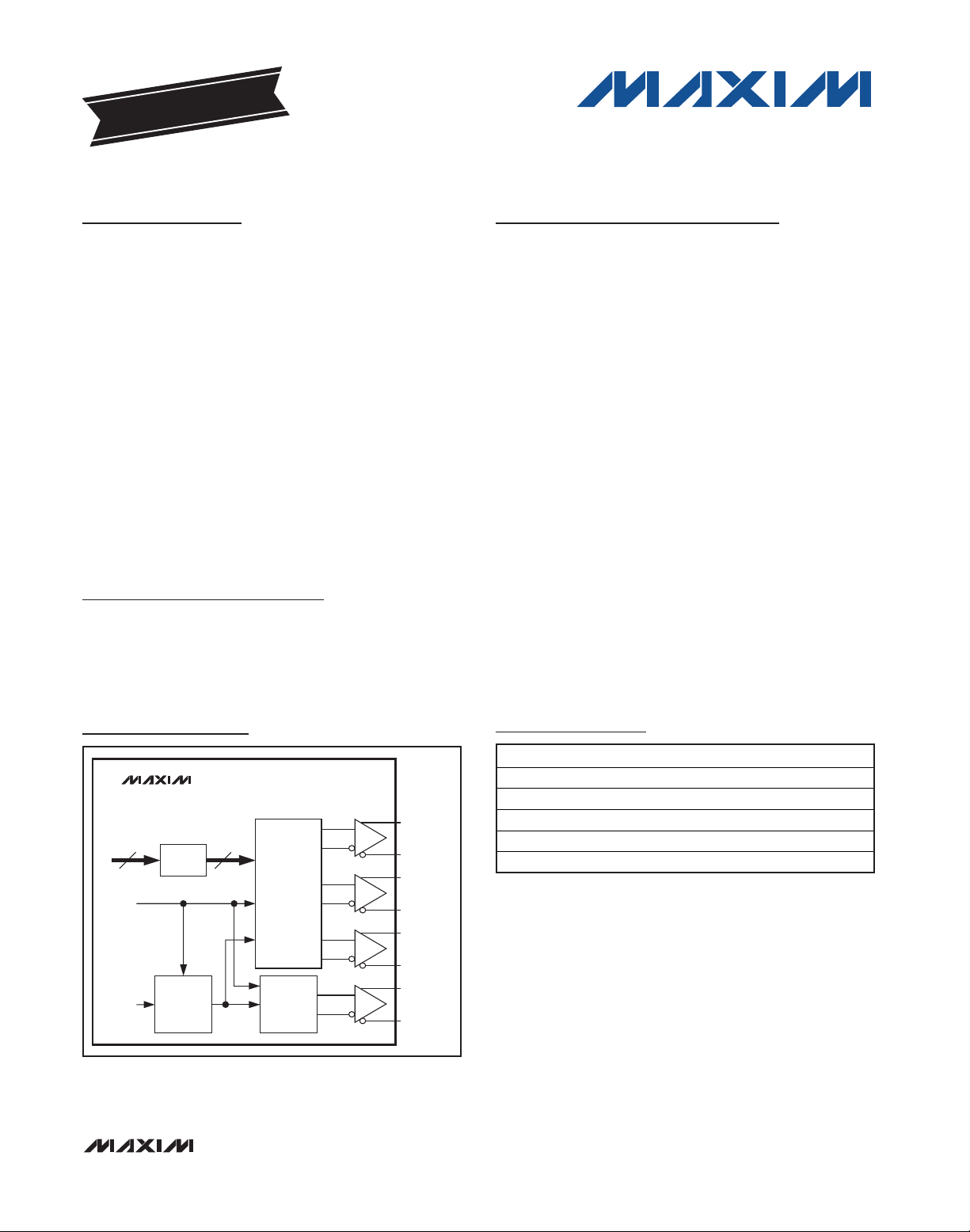

Functional Diagram

MAX9209

MAX9213

TxIN 0 - 20 21

DCB/NC

TxCLK IN

TIMING

CONTROL

PLL

7X OR 9X

PARALLEL-TO-

SERIAL

CONVERTER

DC-BALANCE

LOGIC

CLOCK

GENERATOR

LVDS DRIVER 0

LVDS DRIVER 1

AND

LVDS DRIVER 2

LVDS CLK

TxOUT0+

TxOUT0-

TxOUT1+

TxOUT1-

TxOUT2+

TxOUT2-

TxCLK OUT+

TxCLK OUT-

MAX9209EUM+

MAX9209EUM/V+

MAX9209GUM+

Page 2

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

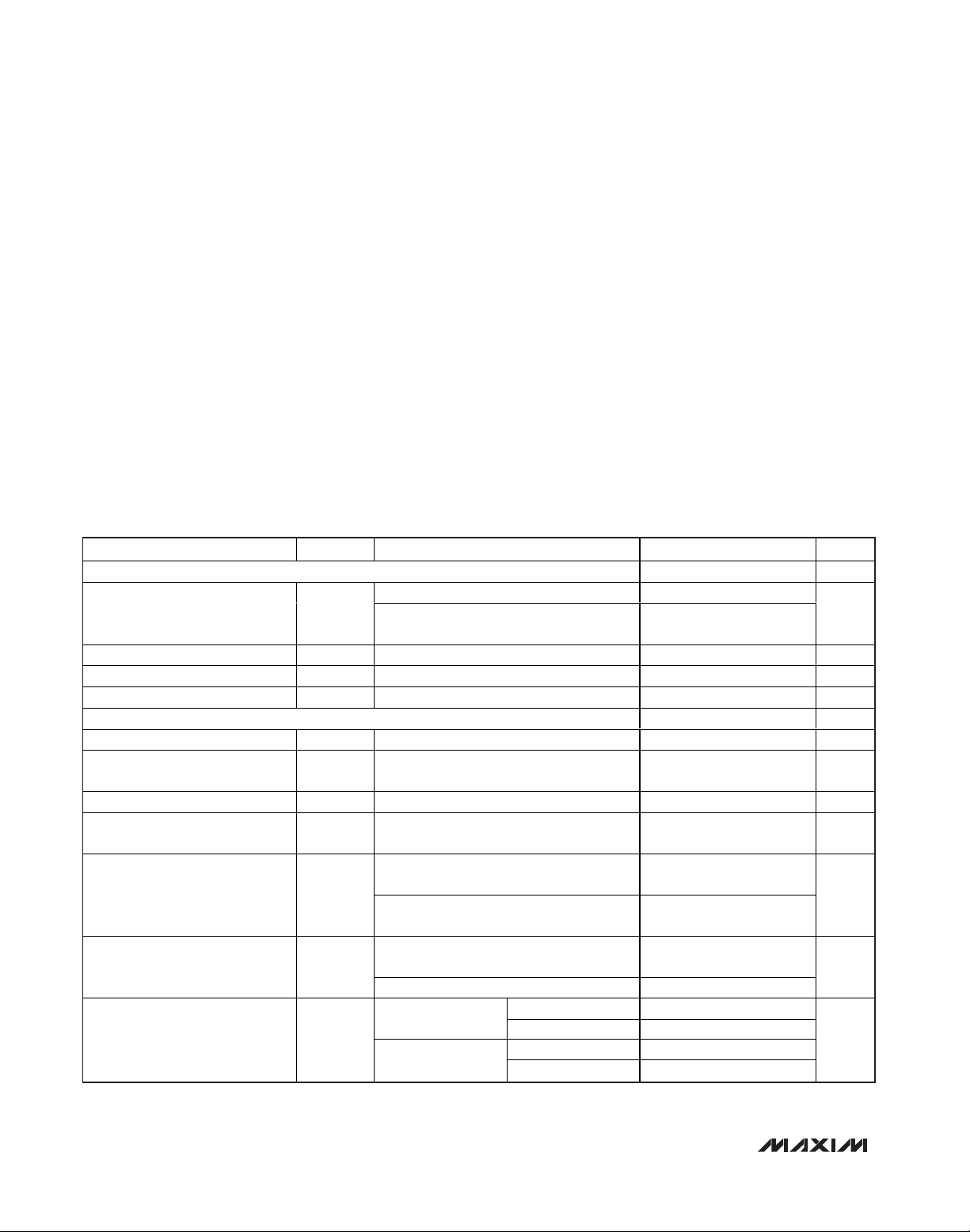

DC ELECTRICAL CHARACTERISTICS

(VCC= +3.0V to +3.6V, RL= 100Ω±1%, PWRDWN = high, DCB/NC = high or low, unless otherwise noted. Typical values are at V

CC

= +3.3V, TA= +25°C.) (Notes 1, 2)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VCCto GND...........................................................-0.5V to +4.0V

LVDS Outputs (TxOUT_, TxCLK OUT_) to GND ...-0.5V to +4.0V

5V Tolerant LVTTL/LVCMOS Inputs

(TxIN_, TxCLK IN, PWRDWN) to GND ..............-0.5V to +6.0V

(DCB/NC) to GND ......................................-0.5V to (V

CC

+ 0.5V)

LVDS Outputs (TxOUT_, TxCLK OUT_)

Short to GND and Differential Short .......................Continuous

Continuous Power Dissipation (multilayer board, T

A

= +70°C)

48-Pin TSSOP (derate 16mW/°C above +70°C) ....... 1282mW

48-Pin TQFN (derate 40mW/°C above +70°C) ..........3200mW

Storage Temperature Range .............................-65°C to +150°C

Junction Temperature......................................................+150°C

ESD Protection

Human Body Model (R

D

= 1.5kΩ, CS= 100pF)

All Pins to GND..............................................................±2kV

IEC 61000-4-2 (R

D

= 330Ω, CS= 150pF)

Contact Discharge (TxOUT_, TxCLK OUT_) to GND ....±8kV

Air Gap Discharge (TxOUT_, TxCLK OUT_) to GND ..±15kV

ISO 10605 (R

D

= 2kΩ, CS= 330pF)

Contact Discharge (TxOUT_, TxCLK OUT_) to GND ....±8kV

Air Gap Discharge (TxOUT_, TxCLK OUT_) to GND ..±25kV

Lead Temperature (soldering, 10s) .................................+300°C

Soldering Temperature (reflow) .......................................+260°C

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SINGLE-ENDED INPUTS (TxIN_, TxCLK IN, PWRDWN, DCB/NC)

TxIN_, TxCLK IN, PWRDWN 2.0 5.5

High-Level Input Voltage V

Low-Level Input Voltage V

Input Current I

Input Clamp Voltage V

LVDS OUTPUTS (TxOUT_, TxCLK OUT)

Differential Output Voltage V

Change in VOD Between

Complementary Output States

Output Offset Voltage V

Change in VOS Between

Complementary Output States

Output Short-Circuit Current I

Magnitude of Differential Output

Short-Circuit Current

Differential Output Resistance R

∆V

∆V

I

IH

IL

IN

CL

OD

OD

OS

OS

OS

OSD

O

DCB/NC 2.0

V

= hi g h or l ow , P WRDWN = hi g h or l ow -20 +20 µA

IN

ICL = -18mA -0.9 -1.5 V

Figure 1 250 350 450 mV

Figure 1 2 25 mV

Figure 1 1.125 1.25 1.375 V

Figure 1 10 30 mV

V

or V

OUT+

non-DC-balanced mode

V

OUT+

DC-balanced mode

V

OD

(Note 3)

V

OD

DC-balanced mode

Non-DC-balanced

mode

OUT-

or V

OUT-

= 0V, non-DC-balanced mode

= 0V, DC-balanced mode (Note 3) 8.2 15

= 0V or V

= 0V or VCC,

CC,

-40°C to +105°C 78 110 150

-40°C to +105°C 292 410 564

-0.3 +0.8 V

-10 ±5.7 +10

-15 ±8.2 +15

5.7 10

78 110 147

292 410 547

V

+

CC

0.3

V

mA

mA

Ω

Page 3

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

_______________________________________________________________________________________ 3

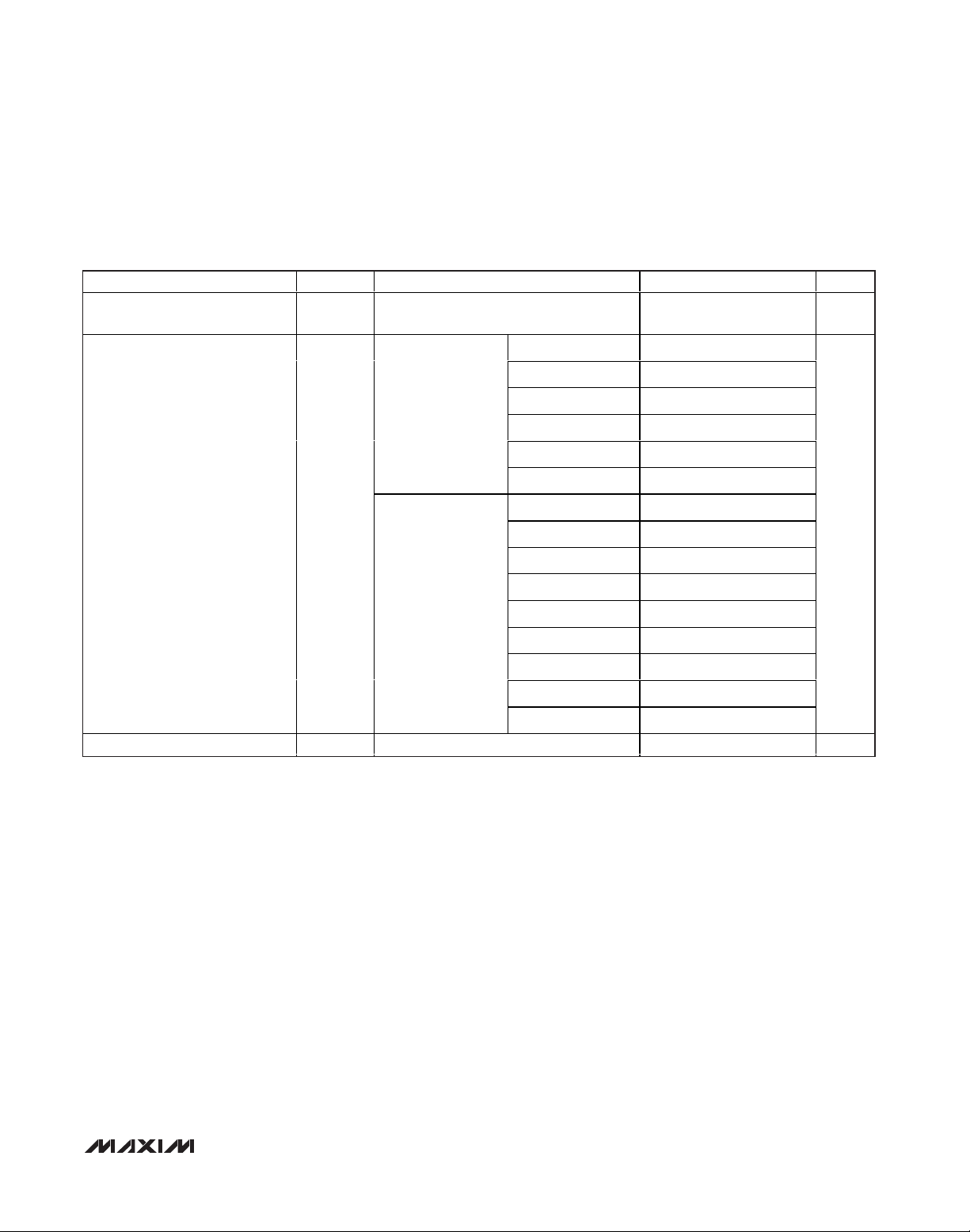

DC ELECTRICAL CHARACTERISTICS (continued)

(VCC= +3.0V to +3.6V, RL= 100Ω±1%, PWRDWN = high, DCB/NC = high or low, unless otherwise noted. Typical values are at V

CC

= +3.3V, TA= +25°C.) (Notes 1, 2)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Output High-Impedance Current I

Worst-Case Supply Current I

Power-Down Supply Current I

OZ

CCW

CCZ

PWRDWN = low or VCC = 0V,

V

= 0V or 3.6V, V

OUT+

DC-balanced mode,

worst-case pattern,

C

= 5pF, Figure 2

L

Non-DC-balanced

mode, worst-case

pattern, C

Figure 2

PWRDWN = low 17 50 µA

= 5pF,

L

= 0V or 3.6V

OUT-

8MHz MAX9209 40 54

16MHz MAX9209 48 68

34MHz MAX9209 71 90

16MHz MAX9213 46 64

34MHz MAX9213 59 87

66MHz MAX9213 94 108

10MHz MAX9209 30 39

20MHz MAX9209 37 53

33MHz MAX9209 49 70

40MHz MAX9209 56 75

20MHz MAX9213 36 49

33MHz MAX9213 45 62

40MHz MAX9213 49 70

66MHz MAX9213 68 89

85MHz MAX9213 83 100

-0.5 ±0.1 +0.5 µA

mA

Page 4

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

4 _______________________________________________________________________________________

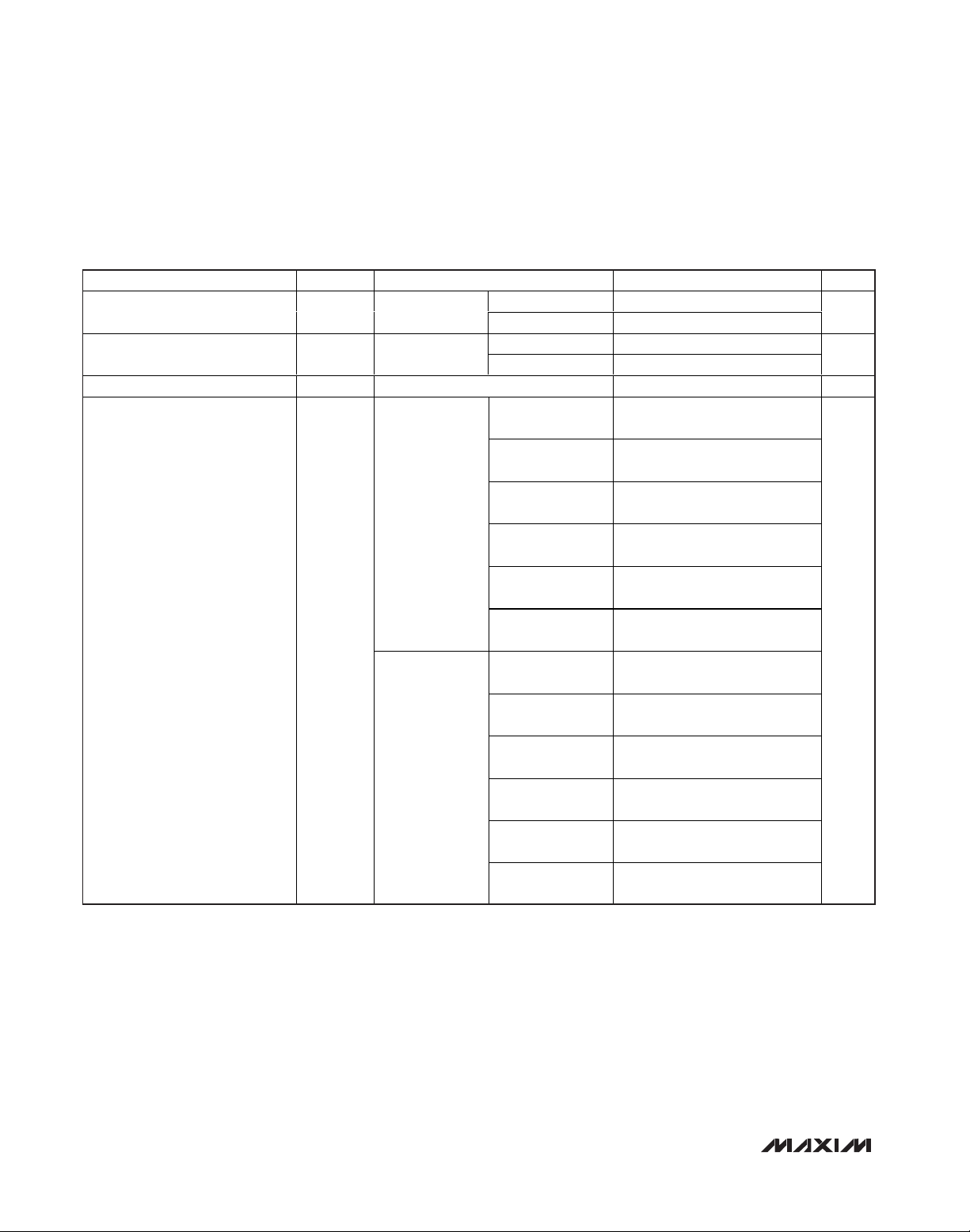

AC ELECTRICAL CHARACTERISTICS

(VCC= +3.0V to +3.6V, RL= 100Ω±1%, CL= 5pF, PWRDWN = high, DCB/NC = high or low, unless otherwise noted. Typical values

are at V

CC

= +3.3V, TA= +25°C.) (Notes 4, 5)

LVDS Low-to-High Transition

Time

LVDS High-to-Low Transition

Time

TxCLK IN Transition Time TCIT Figure 4 4 ns

Output Pulse Position TPPosN

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

LLHT Figure 3

LHLT Figure 3

N = 0, 1, 2, 3,

4, 5, 6

non-DCbalanced mode,

Figure 5 (Note 6)

N = 0, 1, 2, 3,

4, 5, 6, 7, 8

DC-balanced

mode, Figure 6

(Note 6)

MAX9209 150 280 400

MAX9213 150 260 350

MAX9209 150 280 400

MAX9213 150 260 350

10MHz MAX9209

20MHz MAX9209

40MHz MAX9209

20MHz MAX9213

40MHz MAX9213

85MHz MAX9213

8MHz MAX9209

16MHz MAX9209

34MHz MAX9209

16MHz MAX9213

34MHz MAX9213

66MHz MAX9213

N/7 x TCIP

- 0.25

N/7 x TCIP

- 0.15

N/7 x TCIP

- 0.1

N/7 x TCIP

- 0.25

N/7 x TCIP

- 0.15

N/7 x TCIP

- 0.1

N/9 x TCIP

- 0.25

N/9 x TCIP

- 0.15

N/9 x TCIP

- 0.1

N/9 x TCIP

- 0.25

N/9 x TCIP

- 0.15

N/9 x TCIP

- 0.1

N/7 x TCIP

N/7 x TCIP

N/7 x TCIP

N/7 x TCIP

N/7 x TCIP

N/7 x TCIP

N/9 x TCIP

N/9 x TCIP

N/9 x TCIP

N/9 x TCIP

N/9 x TCIP

N/9 x TCIP

N/7 x TCIP

+ 0.25

N/7 x TCIP

+ 0.15

N/7 x TCIP

+ 0.1

N/7 x TCIP

+ 0.25

N/7 x TCIP

+ 0.15

N/7 x TCIP

+ 0.1

N/9 x TCIP

+ 0.25

N/9 x TCIP

+ 0.15

N/9 x TCIP

+ 0.1

N/9 x TCIP

+ 0.25

N/9 x TCIP

+ 0.15

N/9 x TCIP

+ 0.1

ps

ps

ns

Page 5

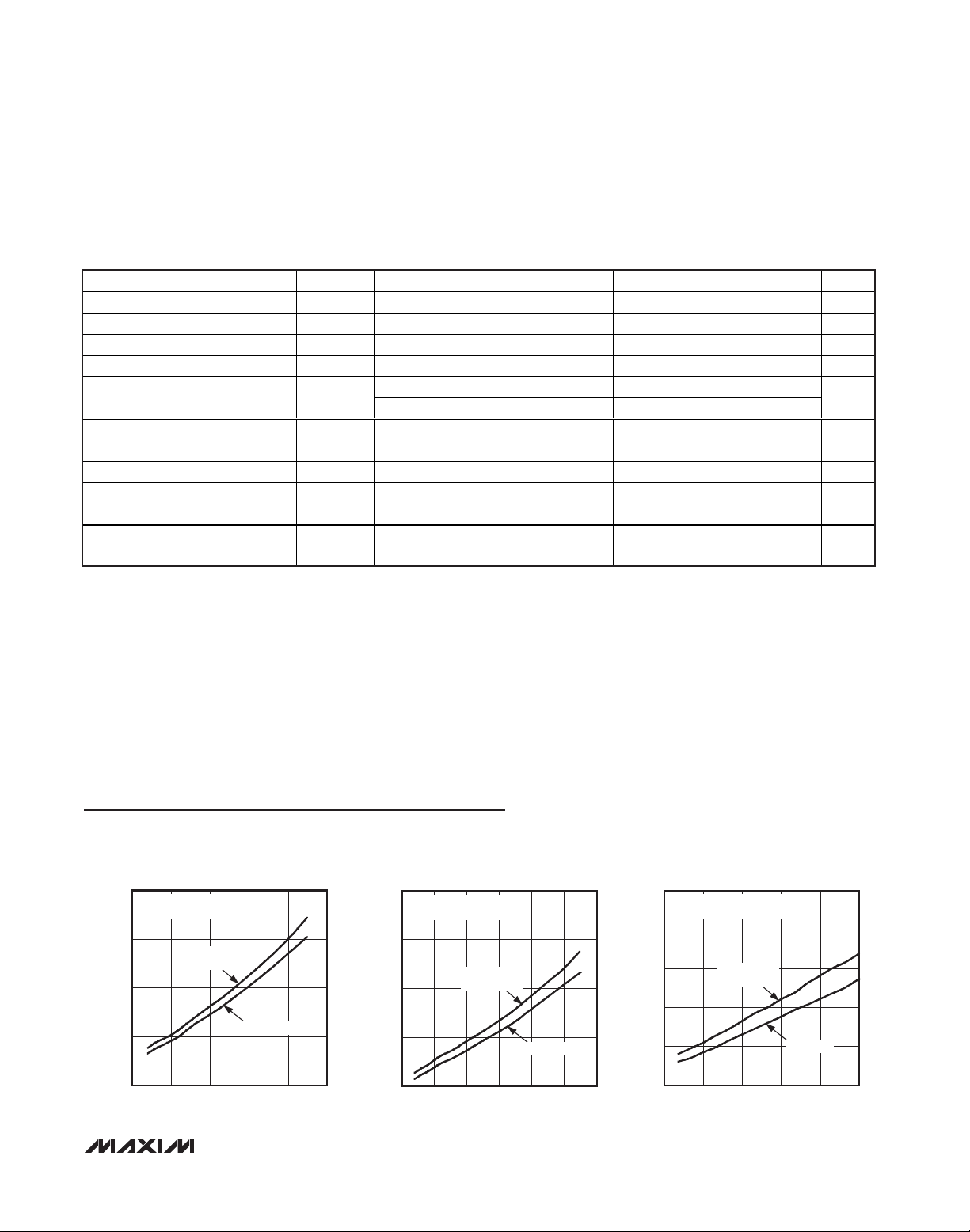

MAX9209/MAX9213

Typical Operating Characteristics

(VCC= +3.3V, RL= 100Ω±1%, CL= 5pF, PWRDWN = high, TA= +25°C, unless otherwise noted.)

AC ELECTRICAL CHARACTERISTICS (continued)

(VCC= +3.0V to +3.6V, RL= 100Ω±1%, CL= 5pF, PWRDWN = high, DCB/NC = high or low, unless otherwise noted. Typical values

are at V

CC

= +3.3V, TA= +25°C.) (Notes 4, 5)

Note 1: Current into a pin is defined as positive. Current out of a pin is defined as negative. All voltages are referenced to ground

except V

OD

, ∆VOD, and ∆VOS.

Note 2: Maximum and minimum limits over temperature are guaranteed by design and characterization. Devices are production

tested at T

A

= +25°C.

Note 3: Guaranteed by design.

Note 4: TCIP is the period of TxCLK IN.

Note 5: AC parameters are guaranteed by design and characterization, and are not production tested. Limits are set at ±6 sigma.

Note 6: Pulse position TPPosN is characterized using 2

7

- 1 PRBS data.

Programmable DC-Balanced

21-Bit Serializers

_______________________________________________________________________________________ 5

TxCLK IN High Time TCIH Figure 7 0.3 x TCIP 0.7 x TC IP ns

TxCLK IN Low Time TCIL Figure 7 0.3 x TCIP 0.7 x TC IP ns

TxIN to TxCLK IN Setup TSTC Figure 7 2.2 ns

TxIN to TxCLK IN Hold THTC Figure 7 0 ns

TxCLK IN to TxCLK OUT Delay TCCD

Serializer Phase-Locked Loop Set TPLLS Figure 9

Serializer Power-Down Delay TPDD Figure 10 14 50 ns

TxCLK IN Cycle-to-Cycle Jitter

(Input Clock Requirement)

Magnitude of Differential Output

Voltage

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Non-DC-balanced mode, Figure 8 3.5 4.5 6.0

DC-balanced mode, Figure 8 4.7 5.9 7.2

32800 x

TCIP

TJIT 2ns

595Mbps data rate, worst-case

pattern

250 mV

V

OD

ns

ns

WORST-CASE PATTERN AND PRBS

SUPPLY CURRENT vs. FREQUENCY

100

MAX9209

DC-BALANCED MODE

80

60

SUPPLY CURRENT (mA)

40

20

050

WORST-CASE

PATTERN

FREQUENCY (MHz)

27 - 1 PRBS

40302010

MAX9209 toc01

WORST-CASE PATTERN AND PRBS

SUPPLY CURRENT vs. FREQUENCY

100

MAX9209

NON-DC-BALANCED MODE

80

60

SUPPLY CURRENT (mA)

40

20

060

WORST-CASE

PATTERN

FREQUENCY (MHz)

MAX9209 toc02

27 - 1 PRBS

5040302010

WORST-CASE AND PRBS SUPPLY CURRENT

120

100

80

60

SUPPLY CURRENT (mA)

40

20

vs. FREQUENCY

MAX9213

NON-DC-BALANCED MODE

WORST-CASE

PATTERN

27 - 1 PRBS

15 90

FREQUENCY (MHz)

75604530

MAX9209 toc03

Page 6

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

6 _______________________________________________________________________________________

Typical Operating Characteristics (continued)

(VCC= +3.3V, RL= 100Ω±1%, CL= 5pF, PWRDWN = high, TA= +25°C, unless otherwise noted.)

WORST-CASE PATTERN AND PRBS

SUPPLY CURRENT vs. FREQUENCY

120

MAX9213

DC-BALANCED MODE

100

WORST-CASE

80

60

SUPPLY CURRENT (mA)

40

20

15 75

PATTERN

27 - 1 PRBS

604530

FREQUENCY (MHz)

MAX9209 toc04

100mV/div

MAX9213

EYE DIAGRAM—NON-DC-BALANCED MODE

100mV/div

TxCLK IN = 85MHz

DC-COUPLED

0V

DIFFERENTIAL

10m OF CAT-5

UTP CABLE

EYE DIAGRAM—NON-DC-BALANCED MODE

MAX9213

TxCLK IN = 85MHz

DC-COUPLED

ALL-CHANNELS

SWITCHING

300ps/div

2m OF CAT-5

UTP CABLE

0V

DIFFERENTIAL

27 - 1 PRBS PATTERN

100Ω TERMINATION

EYE DIAGRAM—DC-BALANCED MODE

TxCLK IN = 66MHz AC-COUPLED

USING 0.1µF CAPACITORS

MAX9209 TOC07

100mV/div

MAX9209 TOC05

100mV/div

EYE DIAGRAM—NON-DC-BALANCED MODE

MAX9213

TxCLK IN = 85MHz

DC-COUPLED

ALL-CHANNELS

SWITCHING

0V

DIFFERENTIAL

300ps/div

5m OF CAT-5

UTP CABLE

27 - 1 PRBS PATTERN

100Ω TERMINATION

MAX9213

2m OF CAT-5

UTP CABLE

MAX9209 TOC08

0V

DIFFERENTIAL

MAX9209 TOC06

27 - 1 PRBS PATTERN

100Ω TERMINATION

300ps/div

MAX9213

0V

DIFFERENTIAL

27 - 1 PRBS PATTERN

100Ω TERMINATION

300ps/div

5m OF CAT-5

UTP CABLE

MAX9209 TOC09

100mV/div

ALL-CHANNELS

SWITCHING

27 - 1 PRBS PATTERN

100Ω TERMINATION

300ps/div

MAX9213

EYE DIAGRAM—DC-BALANCED MODE

TxCLK IN = 66MHz AC-COUPLED

USING 0.1µF CAPACITORS

0V

DIFFERENTIAL

ALL-CHANNELS

SWITCHING

300ps/div

10m OF CAT-5

UTP CABLE

27 - 1 PRBS PATTERN

100Ω TERMINATION

100mV/div

ALL-CHANNELS

SWITCHING

EYE DIAGRAM—DC-BALANCED MODE

TxCLK IN = 66MHz AC-COUPLED

USING 0.1µF CAPACITORS

ALL-CHANNELS

SWITCHING

MAX9209 TOC10

Page 7

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

_______________________________________________________________________________________ 7

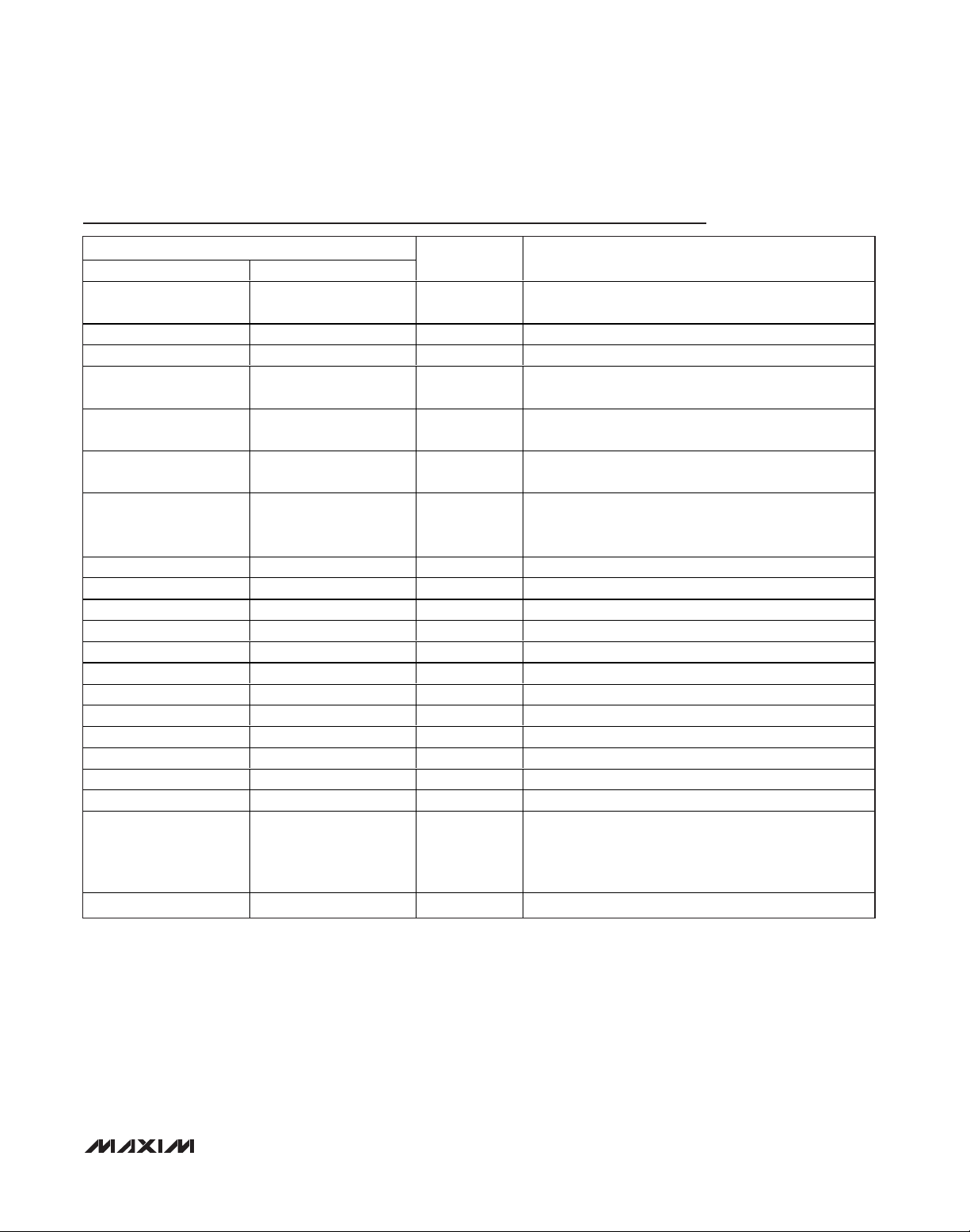

Pin Description

PIN

TSSOP TQFN

1, 3, 4, 44, 45, 47, 48, 38, 39, 41, 42, 43, 45, 46 TxIN0–TxIN6

2, 8, 14, 21 2, 8, 15, 44 V

5, 11, 17, 24, 46 5, 11, 18, 40, 47 GND Ground

6, 7, 9, 10, 12, 13, 15 1, 3, 4, 6, 7, 9, 48 TxIN7–TxIN13

16, 18, 19, 20, 22, 23, 25 10, 12, 13, 14, 16, 17, 19 TxIN14–TxIN20

26 20 TxCLK IN

27 21 PWRDWN

28, 30 22, 24 PLL GND PLL Ground

29 23 PLL V

31, 36, 42 25, 30, 36 LVDS GND LVDS Ground

32 26 TxCLK OUT+ Noninverting LVDS Parallel Rate Clock Output

33 27 TxCLK OUT- Inverting LVDS Parallel Rate Clock Output

34 28 TxOUT2+ Noninverting Channel 2 LVDS Serial Data Output

35 29 TxOUT2- Inverting Channel 2 LVDS Serial Data Output

37 31 LVDS V

38 32 TxOUT1+ Noninverting Channel 1 LVDS Serial Data Output

39 33 TxOUT1- Inverting Channel 1 LVDS Serial Data Output

40 34 TxOUT0+ Noninverting Channel 0 LVDS Serial Data Output

41 35 TxOUT0- Inverting Channel 0 LVDS Serial Data Output

43 37 DCB/NC

— — EP Exposed Paddle (TQFN Only). Solder to ground.

NAME FUNCTION

CC

CC

CC

5V Tolerant LVTTL/LVCMOS Channel 0 Data Inputs.

Internally pulled down to GND.

Digital Supply Voltage

5V Tolerant LVTTL/LVCMOS Channel 1 Data Inputs.

Internally pulled down to GND.

5V Tolerant LVTTL/LVCMOS Channel 2 Data Inputs.

Internally pulled down to GND.

5V Tolerant LVTTL/LVCMOS Parallel Rate Clock Input.

Internally pulled down to GND.

5V Tolerant LVTTL/LVCMOS Power-Down Input. Internally

pulled down to GND. Outputs are high impedance when

PWRDWN = low or open.

PLL Supply Voltage

LVDS Supply Voltage

LVTTL/LVCMOS DC-Balance Programming Input:

MAX9209: pulled up to V

MAX9213: pulled up to V

See Table 1.

CC

CC

Page 8

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

8 _______________________________________________________________________________________

Figure 2. Worst-Case Test Pattern

Figure 3. LVDS Output Load and Transition Times

Figure 1. LVDS Output DC Parameters

Figure 4. Clock Transition Time Waveform

TxOUT_- OR TxCLK OUT-

TxOUT_+ OR TxCLK OUT+

(TxOUT_+) - (TxOUT_-) OR

(TxCLK OUT+) - (TxCLK OUT-)

VOS(-) VOS(+) VOS(-)

∆VOS = |VOS(+) - VOS(-)|

VOD(-) VOD(-)

TxCLK IN

ODD TxIN

EVEN TxIN

VOD(+)

∆VOD = |VOD(+) - VOD(-)|

TCIP

0V

TxOUT_+ OR

TxOUT_- OR

TxCLK OUT-

TxCLK OUT+

C

L

R

L

C

(TxOUT_+) - (TxOUT_-) OR

L

(TxCLK OUT+) - (TxCLK OUT-)

80% 80%

20% 20%

LLHT LHLT

V

IH

TxCLK IN

90%

10%

90%

10%

V

IL

TCITTCIT

Page 9

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

_______________________________________________________________________________________ 9

Detailed Description

The MAX9209 operates at a parallel clock frequency of

8MHz to 34MHz in DC-balanced mode and 10MHz to

40MHz in non-DC-balanced mode. The MAX9213 operates at a parallel clock frequency of 16MHz to 66MHz

in DC-balanced mode and 20MHz to 85MHz in nonDC-balanced mode.

DC-balanced or non-DC-balanced operation is controlled by the DCB/NC pin (see Table 1). In non-DCbalanced mode, each channel serializes 7 bits every

cycle of the parallel clock. In DC-balanced mode, 9 bits

are serialized every clock cycle (7 data bits + 2 DC-balance bits). The highest data rate in DC-balanced mode

for the MAX9213 is 66MHz x 9 = 594Mbps. In non-DCbalanced mode, the maximum data rate is 85MHz x 7 =

595Mbps. A bit time is 1 divided by the data rate, for

example, 1 / 595Mbps = 1.68ns.

DC Balance

Through data coding, the DC-balance circuits limit the

imbalance of ones and zeros transmitted on each channel. If +1 is assigned to each binary one transmitted

and -1 is assigned to each binary zero transmitted, the

variation in the running sum of assigned values is

called the digital sum variation (DSV). The maximum

DSV for the MAX9209/MAX9213 data channels is 10. At

most, 10 more zeros than ones, or 10 more ones than

zeros, are transmitted. The maximum DSV for the clock

channel is 5. Limiting the DSV and choosing the correct

coupling capacitors maintain differential signal amplitude

and reduce jitter due to droop on AC-coupled links.

TxCLK OUT

Figure 5. Non-DC-Balanced Mode LVDS Output Pulse Position Measurement

Table 1. DC-Balance Programming

(DIFFERENTIAL)

CYCLE N - 1 CYCLE N

TxOUT2

(SINGLE ENDED)

TxOUT1

(SINGLE ENDED)

TxOUT0

(SINGLE ENDED)

TxIN15 TxIN14 TxIN20 TxIN19 TxIN18 TxIN17 TxIN16 TxIN15 TxIN14

TxIN8 TxIN7 TxIN13 TxIN12 TxIN11 TxIN10 TxIN9 TxIN8 TxIN7

TxIN1 TxIN0 TxIN6 TxIN5 TxIN4 TxIN3 TxIN2 TxIN1 TxIN0

TPPos0

TPPos1

TPPos2

TPPos3

TPPos4

TPPos5

TPPos6

DEVICE DCB/NC

MAX9209

MAX9213

OPERATING

MODE

High or open DC balanced 8 to 34

Low

High or open DC balanced 16 to 66

Low

Non-DC

balanced

Non-DC

balanced

OPERATING

FREQUENCY

(MHz)

10 to 40

20 to 85

Page 10

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

10 ______________________________________________________________________________________

Figure 6. DC-Balanced Mode LVDS Output Pulse Position Measurement

Figure 7. Setup and Hold, High and Low Times

Figure 8. Clock-In to Clock-Out Delay

TxCLK OUT

(DIFFERENTIAL)

CYCLE N - 1 CYCLE N

TxOUT2

(SINGLE ENDED)

TxOUT1

(SINGLE ENDED)

TxOUT0

(SINGLE ENDED)

DCA2 DCB2 TxIN20 TxIN19 TxIN18 TxIN17 TxIN16 TxIN15 TxIN14

DCA1 DCB1 TxIN13 TxIN12 TxIN11 TxIN10 TxIN9 TxIN8 TxIN7

DCA0 DCB0 TxIN6 TxIN5 TxIN4 TxIN3 TxIN2 TxIN1 TxIN0

TPPos0

TPPos1

TPPos2

TPPos3

TPPos4

TPPos5

TPPos6

TPPos7

TPPos8

DCA2 DCB2

DCA1 DCB1

DCA0 DCB0

TCIP

TxCLK IN

TxIN 0:20

TCIH TCIL

THTCTSTC

SETUP 1.5V1.5V HOLD

2.0V

1.5V

0.8V

TxCLK IN

TxCLK OUT+

TxCLK OUT-

1.5V

TCCD

DIFFERENTIAL 0

Page 11

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

______________________________________________________________________________________ 11

To obtain DC balance on the data channels, the parallel input data is inverted or not inverted, depending on

the sign of the digital sum at the word boundary. Two

complementary bits are appended to each group of 7

parallel input data bits to indicate to the MAX9210/

MAX9214 deserializers whether the data bits are inverted (Figure 11). The deserializer restores the original

state of the parallel data. The LVDS clock signal alternates duty cycles of 4/9 and 5/9, which maintains DC

balance. Figure 12 shows the non-DC-balanced mode

inputs mapped to LVDS outputs.

Figure 11. DC-Balanced Mode Inputs Mapped to LVDS Outputs

PWRDWN

Figure 9. PLL Set Time

Figure 10. Power-Down Delay

V

CC

TxCLK IN

TxOUT_, TxCLK OUT

2.0V

3.6V

HIGH-Z

3.0V

TPPLS

V

OD

= 0

DIFFERENTIAL 0

TxCLK OUT+

TxCLK OUT-

DCB2DCA2

TxOUT2

DCB1DCA1

TxOUT1

DCA0

DCB0

TxOUT0

PWRDWN

TxCLK IN

TxOUT_, TxCLK OUT

0.8V

TPDD

HIGH-Z

CYCLE N + 1CYCLE NCYCLE N - 1

TxIN14TxIN15TxIN16TxIN20 TxIN17TxIN18TxIN19

TxIN9TxIN13 TxIN10TxIN11TxIN12

TxIN2TxIN6 TxIN3TxIN4TxIN5

TxIN7TxIN8

TxIN0TxIN1

TxIN16TxIN17TxIN18DCA2 TxIN19TxIN20DCB2

TxIN15

TxIN14

TxIN9TxIN10TxIN11DCA1 TxIN12TxIN13DCB1

TxIN8

TxIN7

TxIN2TxIN3TxIN4DCA0 TxIN5TxIN6DCB0

TxIN1

TxIN0

Page 12

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

12 ______________________________________________________________________________________

AC-Coupling Benefits

Bit errors experienced with DC-coupling can be eliminated by increasing the receiver common-mode voltage range by AC-coupling. AC-coupling increases the

common-mode voltage range of an LVDS receiver to

nearly the voltage rating of the capacitor. The typical

LVDS driver output is 350mV centered on an offset volt-

age of 1.25V, making single-ended output voltages of

1.425V and 1.075V. An LVDS receiver accepts signals

from 0V to 2.4V, allowing approximately ±1V commonmode difference between the driver and receiver on a

DC-coupled link (2.4V - 1.425V = 0.975V and 1.075V 0V = 1.075V). Figure 13 shows the DC-coupled link,

non-DC-balanced mode.

Figure 12. Non-DC-Balanced Mode Inputs Mapped to LVDS Outputs

Figure 13. DC-Coupled Link, Non-DC-Balanced Mode

TxCLK OUT+

TxCLK OUT-

TxIN14TxIN15

TxOUT2

TxIN14TxIN15TxIN16TxIN20 TxIN17TxIN18TxIN19

CYCLE N + 1CYCLE NCYCLE N - 1

TxIN14TxIN15TxIN16TxIN20 TxIN17TxIN18TxIN19

TxOUT1

TxIN1

TxOUT0

TxIN7TxIN8

TxIN0

TxIN9TxIN13 TxIN10TxIN11TxIN12

TxIN2TxIN6 TxIN3TxIN4TxIN5

7

7

TxIN

7

MAX9209

MAX9213

TxOUT

7:1

7:1

7:1

R

O

R

O

R

O

TxIN7TxIN8

TxIN0TxIN1

TRANSMISSION LINE

100Ω

100Ω

100Ω

TxIN7TxIN8TxIN9TxIN13 TxIN10TxIN11TxIN12

TxIN0TxIN1TxIN2TxIN6 TxIN3TxIN4TxIN5

MAX9210

MAX9214

RxIN

=

R

T

=

R

T

R

=

T

1:7

1:7

1:7

7

7

RxOUT

7

PWRDWN

TxCLK IN

PLL

21:3 SERIALIZER 3:21 DESERIALIZER

R

O

TxCLK OUT

R

T

100Ω

RxCLK IN

=

PLL

PWRDWN

RxCLK OUT

Page 13

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

______________________________________________________________________________________ 13

Common-mode voltage differences may be due to

ground potential variation or common-mode noise. If

there is more than ±1V of difference, the receiver is not

guaranteed to read the input signal correctly and may

cause bit errors. AC-coupling filters low-frequency

ground shifts and common-mode noise and passes

high-frequency data. A common-mode voltage difference up to the voltage rating of the coupling capacitor

(minus half the differential swing) is tolerated. DC-balanced coding of the data is required to maintain the differential signal amplitude and limit jitter on an

AC-coupled link. A capacitor in series with each output

of the LVDS driver is sufficient for AC-coupling. However,

two capacitors—one at the serializer output and one at

the deserializer input—provide protection in case either

end of the cable is shorted to a high voltage.

5V Tolerant Inputs

All signal and control inputs except DCB/NC are 5V tolerant and are internally pulled down to GND. The

DCB/NC pin has a pullup on the MAX9209/MAX9213.

DCB/NC Pin Default Conditions

The MAX9209/MAX9213 have programmable DC balance/non-DC balance. See Table 1 for DCB/NC default

settings and operating modes.

MAX9209

Figure 14. Two Capacitors per Link, AC-Coupled, DC-Balanced Mode

MAX9213

HIGH-FREQUENCY CERAMIC

SURFACE-MOUNT CAPACITORS

CAN ALSO BE PLACED AT

SERIALIZER INSTEAD OF DESERIALIZER.

TxOUT

RxIN

MAX9210

MAX9214

TxIN

PWRDWN

TxCLK IN

7

(7 + 2):1

7

(7 + 2):1

7

(7 + 2):1

PLL

21:3 SERIALIZER 3:21 DESERIALIZER

R

O

R

O

R

O

R

O

TxCLK OUT

R

T

100Ω

R

T

100Ω

R

T

100Ω

R

T

100Ω

RxCLK IN

=

=

=

=

1:(9 - 2)

1:(9 - 2)

1:(9 - 2)

PLL

7

7

RxOUT

7

PWRDWN

RxCLK OUT

Page 14

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

14 ______________________________________________________________________________________

Applications Information

Selection of AC-Coupling Capacitors

Voltage droop and the DSV of transmitted symbols

cause signal transitions to start from different voltage

levels. Because the transition time is finite, starting the

signal transition from different voltage levels causes

timing jitter. The time constant for an AC-coupled link

needs to be chosen to reduce droop and jitter to an

acceptable level.

The RC network for an AC-coupled link consists of the

LVDS receiver termination resistor (R

T

), the LVDS driver

output resistor (RO), and the series AC-coupling capacitors (C). The RC time constant for two equal-value

series capacitors is (C x (RT + RO)) / 2 (Figure 14). The

RC time constant for four equal-value series capacitors

is (C x (RT + RO)) / 4 (Figure 15).

RTis required to match the transmission line impedance (usually 100Ω) and ROis determined by the LVDS

driver design, with a minimum value of 78Ω (see the

DC

Electrical Characteristics

table). This leaves the capaci-

tor selection to change the system time constant.

In the following example, the capacitor value for a

droop of 2% is calculated. Jitter due to this droop is

then calculated assuming a 1ns transition time:

C = -(2 x tBx DSV) / (ln (1 - D) x (RT+ RO)) (Eq 1)

where:

C = AC-coupling capacitor (F)

tB= bit time (s)

DSV = digital sum variation (integer)

ln = natural log

D = droop (% of signal amplitude)

RT= termination resistor (Ω)

Figure 15. Four Capacitors per Link, AC-Coupled, DC-Balanced Mode

HIGH-FREQUENCY CERAMIC

MAX9209

MAX9213

SURFACE-MOUNT CAPACITORS

TxOUT

RxIN

MAX9210

MAX9214

TxIN

7

(7 + 2):1

7

(7 + 2):1

R

O

R

O

7

(7 + 2):1

PWRDWN

PLL

TxCLK IN

21:3 SERIALIZER 3:21 DESERIALIZER

R

O

R

O

TxCLK OUT

=

R

T

100Ω

=

R

T

100Ω

=

R

T

100Ω

=

R

T

100Ω

RxCLK IN

1:(9 - 2)

1:(9 - 2)

1:(9 - 2)

PLL

7

7

RxOUT

7

PWRDWN

RxCLK OUT

Page 15

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

______________________________________________________________________________________ 15

RO= output resistance (Ω)

Equation 1 is for two series capacitors (Figure 14). The

bit time (t

B

) is the period of the parallel clock divided by

9. The DSV is 10. See equation 3 for four series capacitors (Figure 15).

The capacitor for 2% maximum droop at 8MHz parallel

rate clock is:

C = -(2 x tBx DSV) / (ln (1 - D) x (RT+ RO))

C = -(2 x 13.9ns x 10) / (ln (1 - .02) x (100Ω + 78Ω))

C = 0.0773µF

Jitter due to droop is proportional to the droop and

transition time:

tJ= tTx D (Eq 2)

where:

tJ= jitter (s)

tT= transition time (s) (0% to 100%)

D = droop (% of signal amplitude)

Jitter due to 2% droop and assumed 1ns transition time is:

tJ= 1ns x 0.02

tJ= 20ps

The transition time in a real system depends on the frequency response of the cable driven by the serializer.

The capacitor value decreases for a higher frequency

parallel clock and for higher levels of droop and jitter.

Use high-frequency, surface-mount ceramic capacitors.

Equation 1 altered for four series capacitors (Figure 15) is:

C = -(4 x tBx DSV) / (ln (1 - D) x (RT+ RO)) (Eq 3)

Integrated Termination

The MAX9209/MAX9213 have an integrated output termination resistor across each of the four LVDS outputs.

These resistors damp reflections from induced noise and

mismatches between the transmission line impedance

and termination resistor at the deserializer input. In DCbalanced mode, the differential output resistance is part

of the RC time constant. In non-DC-balanced mode, the

output termination is increased to 410Ω (typ) to reduce

power. In power-down mode (PWRDWN = low) or when

the power supply is off, the output resistor is switched

out and the LVDS outputs are high impedance.

PWRDWN

and Power-Off

Driving PWRDWN low stops the PLL, switches out the

integrated output termination resistors, puts the LVDS

outputs in high impedance, and reduces supply current

to 50µA or less. Driving PWRDWN high starts the PLL

lock to the input clock and switches in the output termination resistors. The LVDS outputs are not driven until

the PLL locks. The differential output resistance pulls

the outputs together and the LVDS outputs are high

impedance to ground. If the power supply is turned off,

the output resistors are switched out and the LVDS outputs are high impedance.

PLL Lock Time

The PLL lock time is set by an internal counter. The maximum time to lock is 32,800 clock periods. Power and

clock should be stable to meet the lock-time specification. When the PLL is locking, the LVDS outputs are not

active and have a differential output resistance of RO.

Power-Supply Bypassing

There are separate power domains for LVDS, PLL, and

digital circuits. Bypass each LVDS VCC, PLL VCC, and

VCCpin with high-frequency surface-mount ceramic

0.1µF and 0.001µF capacitors in parallel as close to the

device as possible, with the smallest value capacitor

closest to the supply pin.

LVDS Outputs

The LVDS outputs are current sources. The voltage

swing is proportional to the load impedance. The outputs are rated for a differential load of 100Ω±1%.

Cables and Connectors

Interconnect for LVDS typically has a differential impedance of 100Ω. Use cables and connectors that have

matched differential impedance to minimize impedance

discontinuities.

Twisted-pair and shielded twisted-pair cables offer

superior signal quality compared to ribbon cable and

tend to generate less EMI due to magnetic field canceling effects. Balanced cables pick up noise as common

mode, which is rejected by the LVDS receiver.

Board Layout

Keep the LVTTL/LVCMOS input and LVDS output signals separated to prevent crosstalk. A four-layer PCB

with separate layers for power, ground, LVDS outputs,

and digital signals is recommended.

Page 16

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

16 ______________________________________________________________________________________

ESD Protection

The MAX9209/MAX9213 ESD tolerance is rated for IEC

61000-4-2, Human Body Model and ISO 10605 standards. IEC 61000-4-2 and ISO 10605 specify ESD tolerance for electronic systems. The IEC 61000-4-2

discharge components are CS= 150pF and RD= 330Ω

(Figure 16). For IEC 61000-4-2, the LVDS outputs are

rated for ±8kV contact and ±15kV air discharge. The

Human Body Model discharge components are C

S

=

100pF and RD= 1.5kΩ (Figure 17). For the Human Body

Model, all pins are rated for ±2kV contact discharge. The

ISO 10605 discharge components are CS= 330pF and

RD= 2kΩ (Figure 18). For ISO 10605, the LVDS outputs

are rated for ±8kV contact and ±25kV air discharge.

Figure 16. IEC 61000-4-2 Contact Discharge ESD Test Circuit

Figure 17. Human Body ESD Test Circuit

Figure 18. ISO 10605 Contact Discharge ESD Test Circuit

R

D

HIGH-

VOLTAGE

DC

SOURCE

50Ω TO 100Ω

CHARGE-CURRENT-

LIMIT RESISTOR

C

150pF

S

330Ω

DISCHARGE

RESISTANCE

STORAGE

CAPACITOR

DEVICE

UNDER

TEST

R

D

50Ω TO 100Ω

2kΩ

R

D

S

1.5kΩ

DISCHARGE

RESISTANCE

STORAGE

CAPACITOR

DEVICE

UNDER

TEST

1MΩ

CHARGE-CURRENT-

DC

LIMIT RESISTOR

C

100pF

HIGH-

VOLTAGE

SOURCE

HIGH-

VOLTAGE

DC

SOURCE

CHARGE-CURRENT-

LIMIT RESISTOR

330pF

C

S

DISCHARGE

RESISTANCE

STORAGE

CAPACITOR

DEVICE

UNDER

TEST

Page 17

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

______________________________________________________________________________________ 17

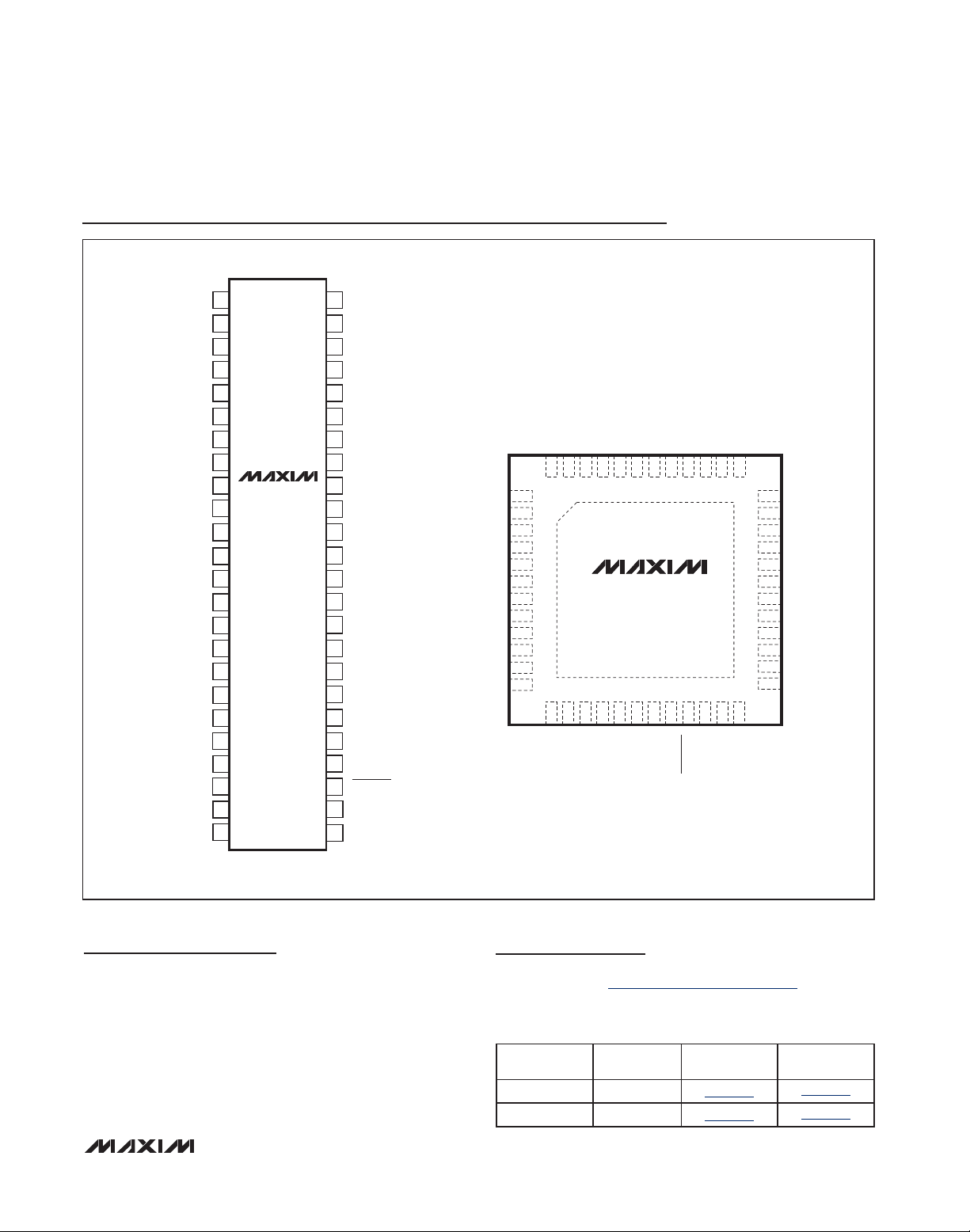

Pin Configurations

Chip Information

PROCESS: CMOS

Package Information

For the latest package outline information and land patterns

(footprints), go to www.maxim-ic.com/packages

. Note that a

“+”, “#”, or “-” in the package code indicates RoHS status only.

Package drawings may show a different suffix character, but

the drawing pertains to the package regardless of RoHS status.

PACKAGE

TYPE

PACKAGE

CODE

OUTLINE NO.

LAND

PATTERN NO.

48 TSSOP A48+1

21-0155

90-0124

48 TQFN T4877+6

21-0144

90-0132

TOP VIEW

TxIN4

V

TxIN5

GND

TxIN7

TxIN8

TxIN9

GND

TxIN11

TxIN12

V

TxIN13

TxIN14

GND

TxIN15

TxIN16

TxIN17

VCC

TxIN18

TxIN19

GND

+

1

2

CC

3

4

5

6

7

8

CC

9

MAX9209

MAX9213

10

11

12

13

14

CC

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

TxIN3

TxIN2

GND

TxIN1TxIN6

TxIN0

DCB/NC

LVDS GND

TxOUT0-V

TxOUT0+

TxOUT1-TxIN10

TxOUT1+

LVDS V

CC

LVDS GND

TxOUT2-

TxOUT2+

TxCLK OUT-

TxCLK OUT+

LVDS GND

PLL GND

PLL V

CC

PLL GND

PWRDWN

TxCLK IN

TxIN20

TxIN8

V

TxIN9

TxIN10

GND

TxIN11

TxIN12

V

TxIN13

TxIN14

GND

TxIN15

TxIN6

CC

V

TxIN5

TxIN18

CC

V

TxIN4

TxIN3

MAX9209

MAX9213

EXPOSED PAD

GND

TxIN19

TxIN20

TxIN2

GND

TxCLK IN

PWRDWN

TxIN1

TxIN0

CC

PLL V

PLL GND

DCB/NC

37

36

35

34

33

32

31

30

29

28

27

26

25

24

PLL GND

LVDS GND

TxOUT0TxOUT0+

TxOUT1TxOUT1+

LVDS V

CC

LVDS GND

TxOUT2-

TxOUT2+

TxCLK OUTTxCLK OUT+

LVDS GND

GND

TxIN7

4847464544434241403938

+

1

2

CC

3

4

5

6

7

8

CC

9

10

11

12

1314151617181920212223

TxIN17

TxIN16

TQFN

TSSOP

Page 18

MAX9209/MAX9213

Programmable DC-Balanced

21-Bit Serializers

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in

the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.

18

____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2012 Maxim Integrated Products Maxim is a registered trademark of Maxim Integrated Products, Inc.

Revision History

REVISION

NUMBER

3 6/07 —

4 10/07 Removed all references to MAX9211 and MAX9215. 1–20

5 3/12 Updated Ordering Information 1

REVISION

DATE

DESCRIPTION

PAGES

CHANGED

1–5, 9, 14, 15, 18,

19, 20

Loading...

Loading...