Page 1

19-3360; Rev 0; 8/04

用于

________________________________

MAX8707

型控制器,用于为

工作减少了输入电流纹波和输出电压波纹,同时简化了

元件选择和布局设计。

有源电压定位功能,降低了功耗和对大体积输出电容的

要求。

MAX8707

直接从电池降压或从

一次变换方案直接从高压电池降压,可达到尽可能高的

效率。另外一种方案,二次变换 (从

而不是从电池降压) 方案能够工作在更高的开关频率,可

获得最小的物理尺寸。

MAX8707

对检流输入,利用单个检流电阻可提供精确的电压定位

斜率和平均电流限流保护。

入,提供差分远端电压检测。

MAX8707

用于在

器降低了启动和关断期间的转换摆率,提供具有最小输

入浪涌电流的软启动,阻尼软关断功能保证没有负输出

下冲。

锁定过压和热过载保护——以及一个独立的电压调节器

电源好”(

“

MAX8707

300kHz或600kHz

引脚

40

请参考

是一款多相 (

AMD Hammer CPU

可以用于两种不同的笔记本

的每一相都有专门的差分检流输入,并包括第

具有一个设置挂起电压的模拟输入,以及一个

码或挂起电压之间转换的摆率控制器。控制

VID

MAX8707

6mmx6mm

MAX8702/MAX8703

集成了输出故障保护电路——欠压、非

)输出。

VROK

提供可选择的开关频率,每相可选择为

的工作频率。

相)、交错式、固定频率、降压

3/4

核供电。多相交错

MAX8707

+5V

的薄型

包含可调增益和偏移的

CPU

系统电源降压,产生核电压。

的系统电源降压

+5V

MAX8707

QFN

。

还有两个专用的输

MAX8707

封装。与其兼容的驱动器

AMD Hammer CPU

概述

核供电方案:

200kHz

采用低截面的

核电源的多相、

固定频率控制器

________________________________

相交错式、固定频率控制器

♦

3/4

在整个输入、负载和温度变化范围内保持

♦

精度

V

OUT

位内置数/模转换器

♦

5

可调挂起电压输入

♦

有源电压定位,具有可调增益和偏移

♦

精确、无损的电流均衡

♦

精确的下垂和电流限制

♦

远端输出和地检测

♦

输出摆率控制

♦

电源好”窗口比较器

♦

5

“

可选开关频率:

♦

输出过压和欠压保护

♦

热故障保护

♦

♦

2V ±0.7%

软启动和关断

♦

基准输出

____________________________

PART TEMP RANGE PIN-PACKAGE

、

MAX8707ETL -40°C to +85°C 40 Thin QFN 6mm x 6mm

________________________________

AMD Hammer

多相

电压定位降压型转换器

笔记本电脑/台式计算机

服务器

CPU

核电源

(DAC)— 0.80V至1.55V

200kHz/300kHz/600kHz

台式计算机

特性

±0.75%

的

定购信息

应用

MAX8707

________________________________________________________________ Maxim Integrated Products 1

本文是

翻译错误,如需确认任何词语的准确性,请参考

索取免费样品和最新版的数据资料,请访问

正式英文资料的译文,

Maxim

不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

Maxim

Maxim

Maxim

引脚配置在数据资料的最后部分给出。

提供的英文版资料。

的主页:

www.maxim-ic.com.cn

。

Page 2

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

ABSOLUTE MAXIMUM RATINGS

VCCto GND..............................................................-0.3V to +6V

D0–D4 to GND..........................................................-0.3V to +6V

SKIP, SUS, VROK, ILIM(AVE) to GND......................-0.3V to +6V

SUSV, OFS, OSC to GND.........................................-0.3V to +6V

CSP_, CSN_, CRSP, CRSN to GND .........................-0.3V to +6V

VPS, FBS, CCV, REF to GND .....................-0.3V to (V

ILIM(PK), TRC, TIME to GND .....................-0.3V to (V

PWM_, DRSKP to PGND ............................-0.3V to (V

PGND, GNDS to GND ...........................................-0.3V to +0.3V

MAX8707

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Note 1: SHDN can be forced to 12V for debugging prototype boards using the no-fault test mode, which disables fault protection.

CC

CC

CC

+ 0.3V)

+ 0.3V)

+ 0.3V)

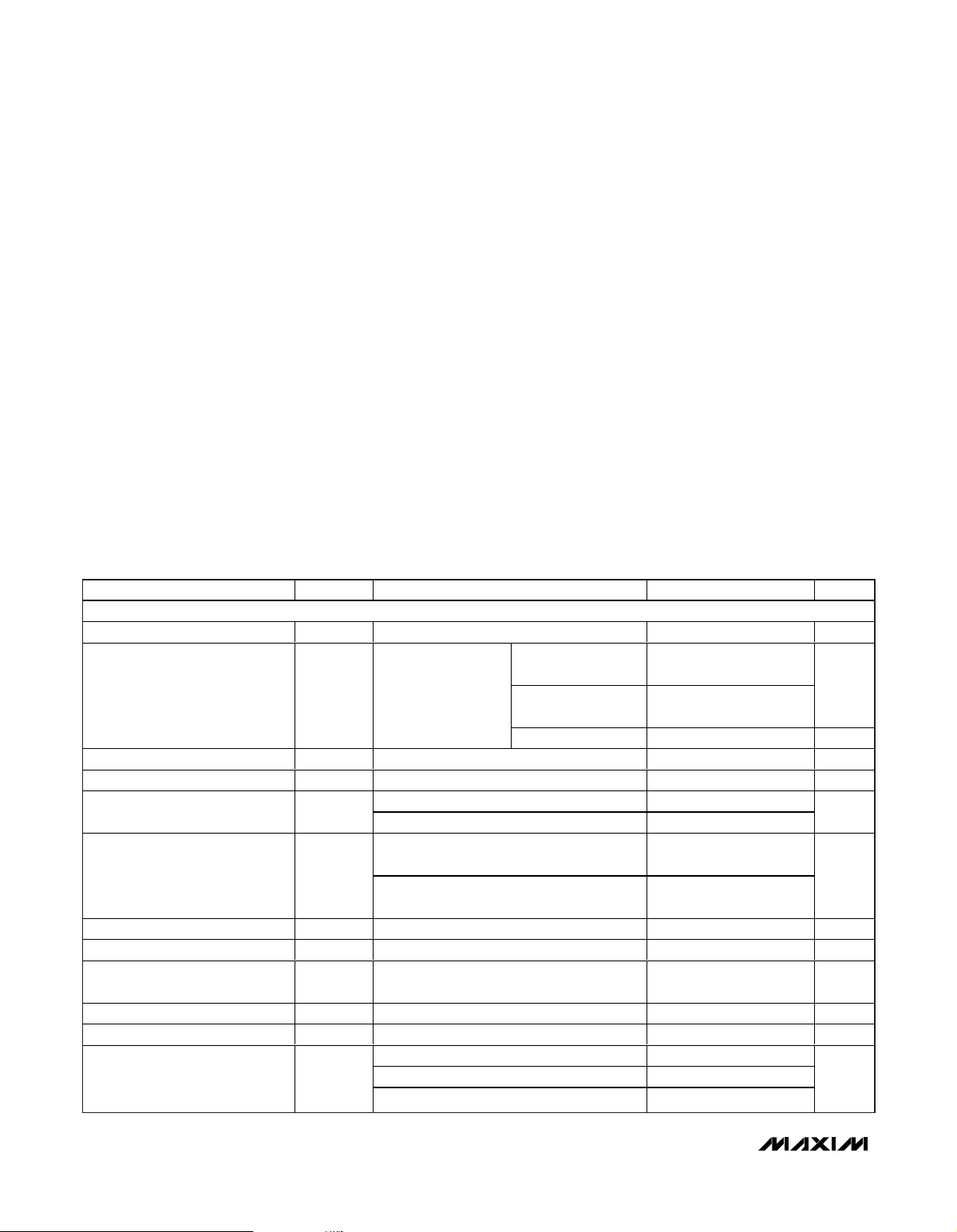

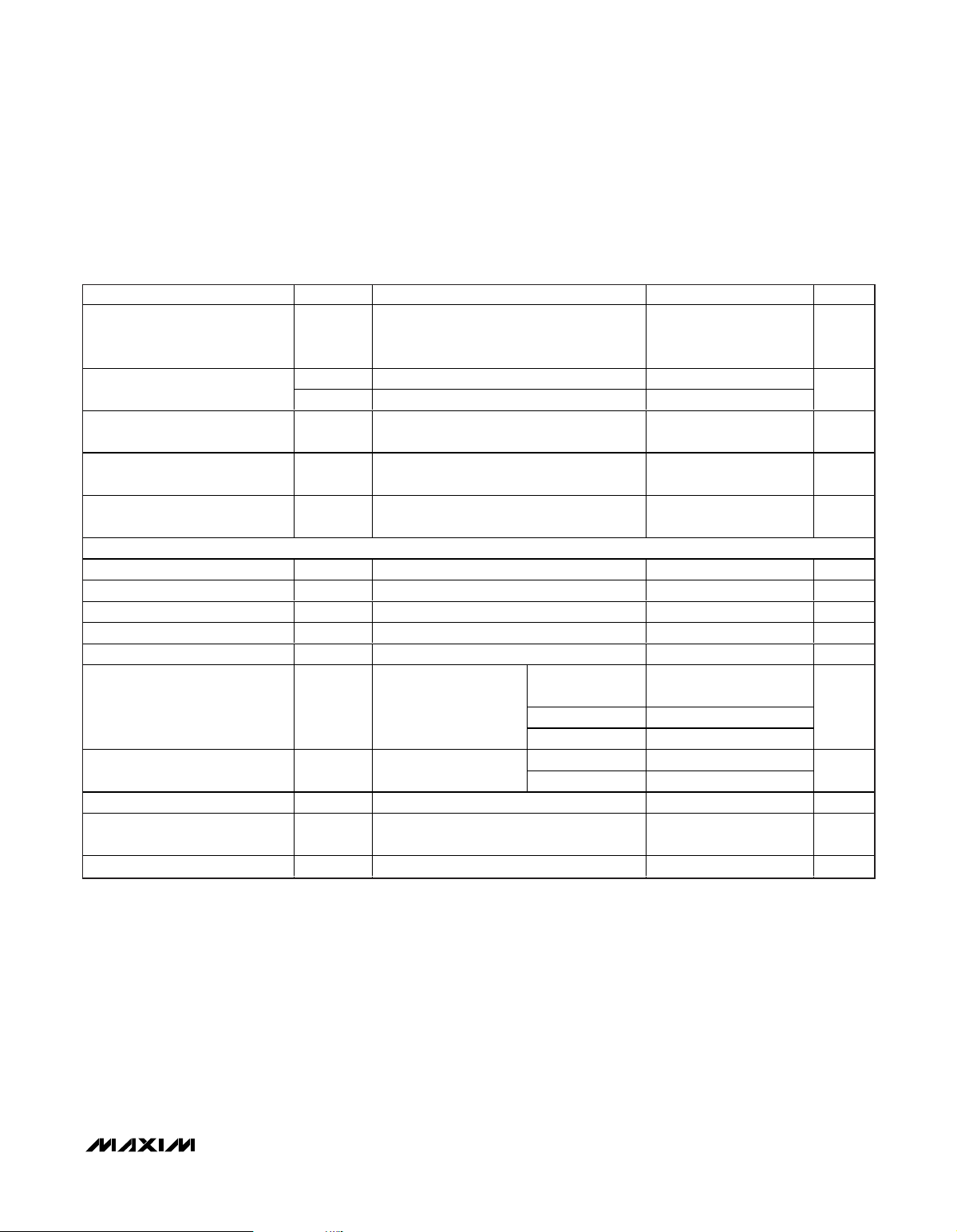

ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

are at T

PWM CONTROLLER

Input Voltage Range V

DC Output Voltage Accuracy V

SUSV Input Range V

SUSV Input-Bias Current I

OFS Input Range V

OFS GAIN A

OFS Input-Bias Current I

GNDS Input Range V

GNDS Gain A

GNDS Input-Bias Current I

FBS Input-Bias Current I

Switching Frequency Accuracy

(Per Phase)

= +25°C.)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, OSC = REF, V

SHDN

SUSV

SUSV

OFS

GNDS

GNDS

GNDS

FBS

f

CC

OUT

OFS

OFS

SW

= V

VPS

Includes loadregulation error

(VPS = FBS)

V

= 0.4V to 2V -0.1 +0.1 µA

SUSV

Negative offsets 0 0.8

Positive offsets 1.2 2.0

∆V

/ ∆V

OUT

V

OFS

∆V

OUT

V

OFS

V

OFS

∆V

OUT

-200mV ≤ V

CRSP = CRSN, CSP_ = CSN_ -10 +10 µA

OSC = GND 180 200 220

OSC = REF 270 300 330

OSC = V

OFS

= 0 to 0.8V

/ ∆V

OFS

= 1.2V to 2V

= 0 to 2V -0.1 +0.1 µA

/ ∆V

GNDS

GNDS

CC

SHDN to GND (Note 1)...........................................-0.3V to +14V

REF Short-Circuit Duration .........................................Continuous

Continuous Power Dissipation (T

40-Pin 6mm x 6mm Thin QFN

(derate 26.3mW/°C above +70°C)................................2.105W

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

= V

FBS

, ∆V

, ∆V

,

≤ +200mV

= V

CRSN

= 0°C to +85°C, unless otherwise specified. Typical values

A

DAC codes from

1.10V to 1.55V

DAC codes from

0.80V to 1.075V

SUS = V

= V

OFS

OFS

= V

OFS

OFS-VREF

CRSP

CC

,

= V

,

CSP_

= 1.20V, V

= +70°C)

A

= 0.8V, OFS = SUS =

SUSV

4.5 5.5 V

-0.75 +0.75

-2.0 +2.0

-20 +20 mV

0.4 2.0 V

-0.131 -0.125 -0.118

-0.131 -0.125 -0.118

-200 +200 mV

0.95 1.00 1.05 V/V

-2 +2 µA

540 600 660

%

V

V/V

kHz

2 _______________________________________________________________________________________

Page 3

用于

)

AMD Hammer CPU

核电源的多相、

固定频率控制器

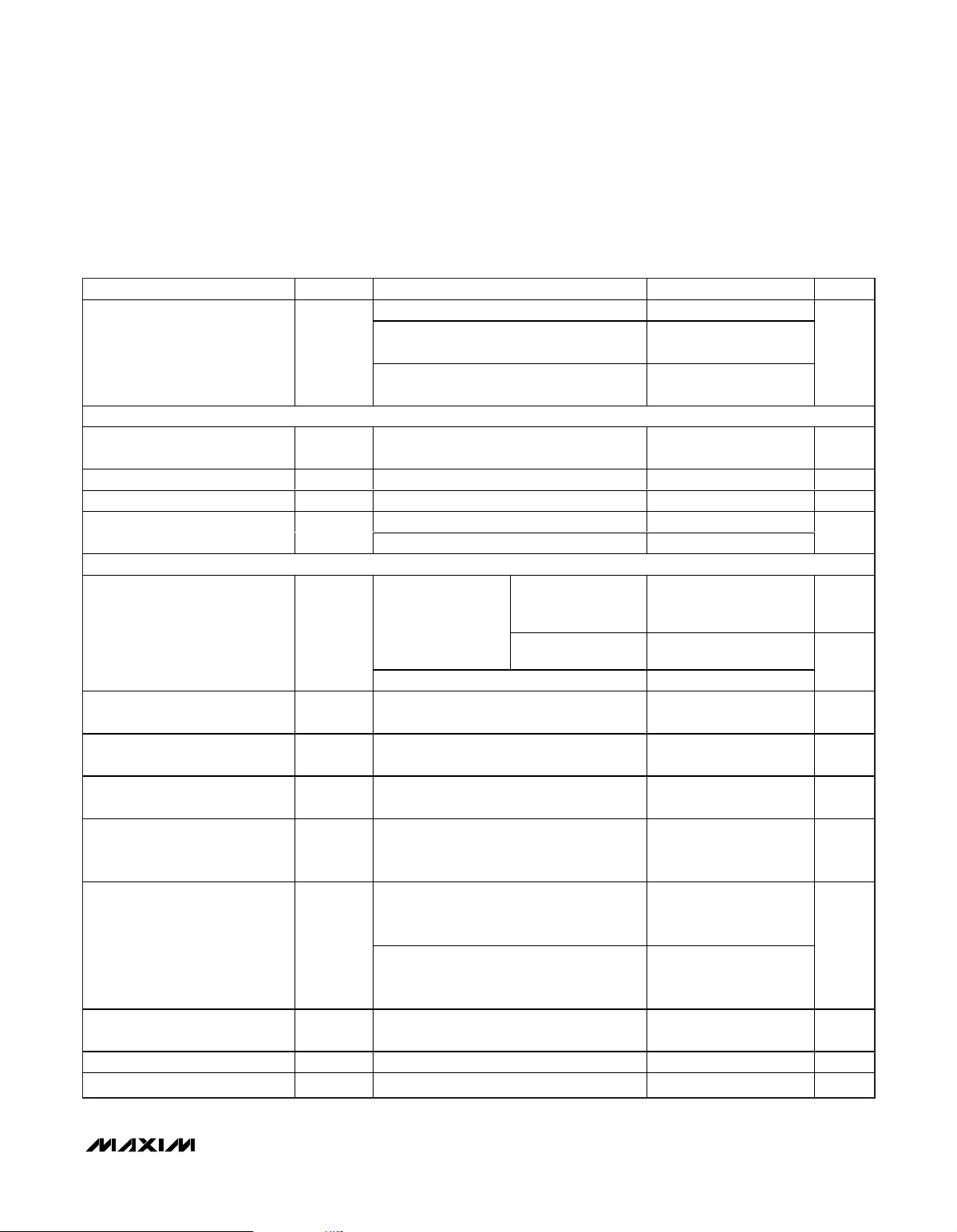

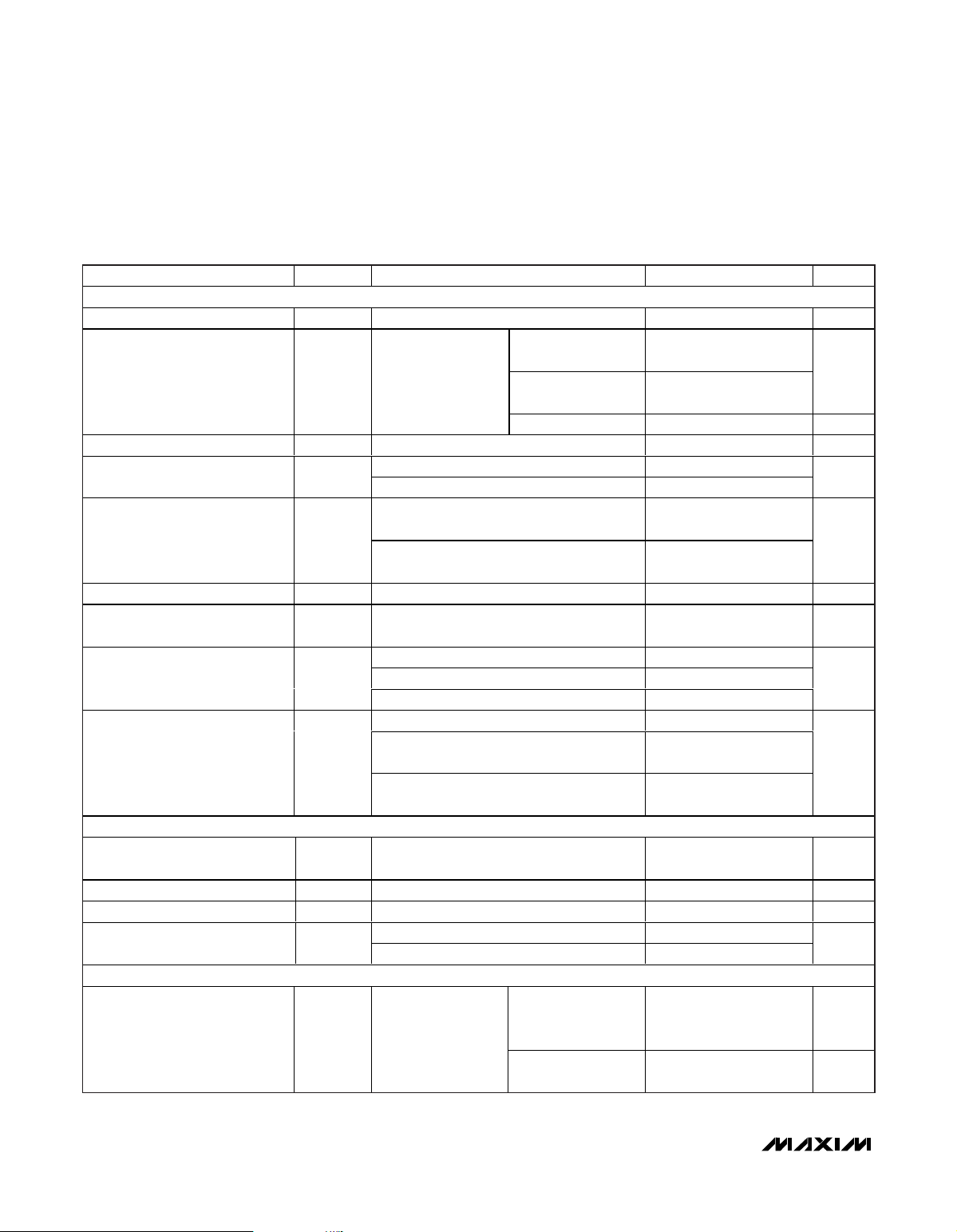

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

are at T

TIME Slew-Rate Accuracy

BIAS AND REFERENCE

Quiescent Supply Current (VCC)I

Shutdown Supply Current (VCC)I

Reference Voltage V

Reference Load Regulation ∆V

FAULT PROTECTION

Output Overvoltage-Protection

Threshold

Output Overvoltage Propagation

Delay

Output Undervoltage-Protection

Threshold

Output Undervoltage

Propagation Delay

VROK Transition Blanking Time t

= +25°C.)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, OSC = REF, V

SHDN

CC

CC(SHDN

REF

V

OVP

t

OVP

V

UVP

t

UVP

BLANK

= V

FBS

= V

REF

VPS

R

= 143kΩ (6.25mV/µs) -10 +10

TIME

R

= 47kΩ (19mV/µs) to 392kΩ

TIME

(2.28mV/µs)

Startup and shutdown, R

(4.75mV/µs) to 392kΩ (0.57mV/µs)

Measured at VCC, VPS and FBS forced

above the regulation points

Measured at VCC, SHDN = GND 0.05 10 µA

V

= 4.5V to 5.5V, I

CC

I

= 0 to 500µA -2 -0.2

REF

REF

I

= -100µA to 0 0.21 6.2

REF

Measured at VPS

with respect to

unloaded output

voltage, rising edge,

8mV hysteresis

Minimum OVP level 1.1

VPS forced 25mV above trip threshold 10 µs

Measured at VPS with respect to 70% of the

unloaded nominal output voltage

VPS forced 25mV below trip threshold 10 µs

Measured from the time when VPS reaches

the target voltage, slew rate set by R

(Note 2)

= V

CRSN

= 0°C to +85°C, unless otherwise specified. Typical values

A

TIME

= 0 1.986 2.000 2.014 V

PWM (SKIP = GND)

or SKIP mode when

V

≤ V

OUT

SKIP = V

V

> V

OUT

CRSP

= 47kΩ

TRIP

and

CC

TRIP

= V

TIME

= 1.20V, V

CSP_

-15 +15

-20 +20

150 200 250 mV

1.70 1.75 1.80

-30 +30 mV

= 0.8V, OFS = SUS =

SUSV

712mA

20 µs

MAX8707

%

mV

V

Undervoltage measured at VPS with

respect to 87.5% unloaded output voltage,

VROK Threshold

VROK Delay t

VROK Output Low Voltage I

VROK Leakage Current High state, VROK forced to 5.5V 1 µA

_______________________________________________________________________________________ 3

VROK

falling edge, 15mV hysteresis

Overvoltage measured at VPS with respect

to 112.5% of the unloaded output voltage,

rising edge, 15mV hysteresis

VPS forced 25mV outside the VROK trip

thresholds

= 3mA 0.4 V

SINK

-30 +30

-30 +30

10 µs

mV

Page 4

用于

)

)

)

)

)

)

)

AMD Hammer CPU

核电源的多相、

固定频率控制器

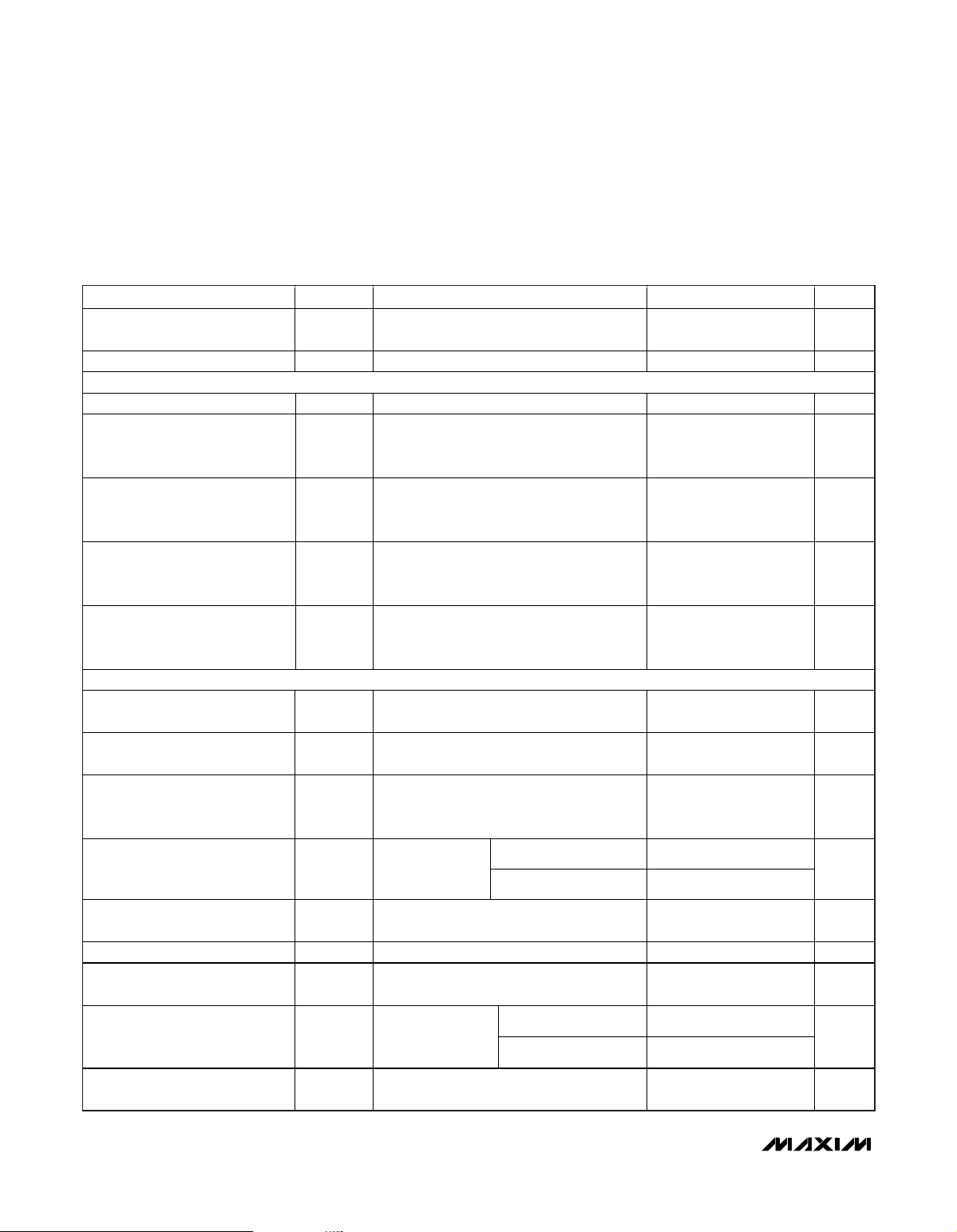

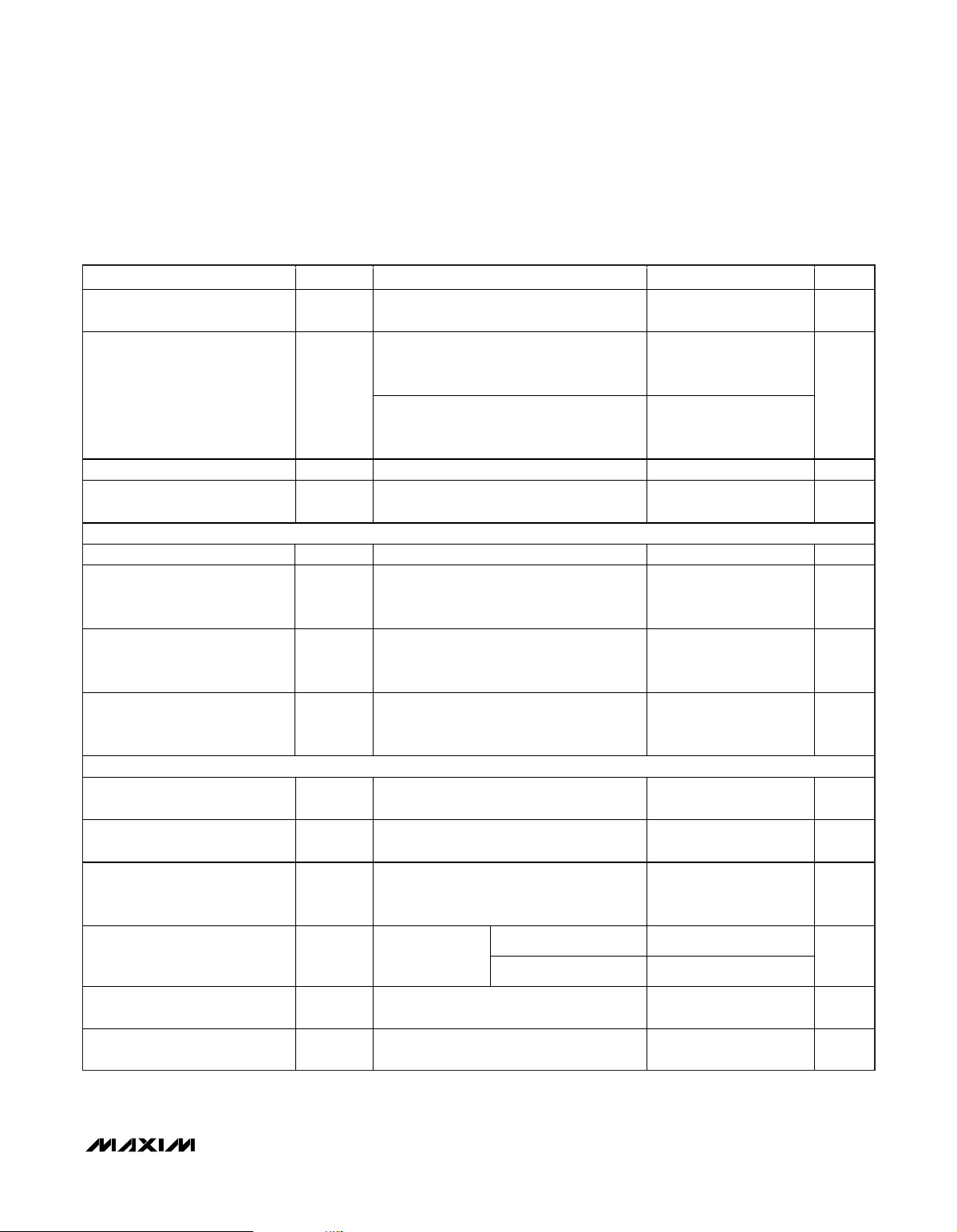

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

are at T

= +25°C.)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

VCC Undervoltage-Lockout

Threshold

MAX8707

Thermal-Shutdown Threshold T

DROOP AND TRANSIENT RESPONSE

DC Droop Amplifier Offset -1.5 +1.5 mV

DC Droop Amplifier

Transconductance

(CRS Sense Enabled)

= 5V, OSC = REF, V

SHDN

V

UVLO(VCC

SHDN

G

m(VPS

= V

FBS

= V

VPS

Rising edge, hysteresis = 20mV, PWM_

disabled below this level

= V

CRSN

= 0°C to +85°C, unless otherwise specified. Typical values

A

CRSP

= V

CSP_

= 1.20V, V

= 0.8V, OFS = SUS =

SUSV

4.10 4.25 4.45 V

Rising edge hysteresis = 15°C +160 °C

∆I

V

CRSP

VPS

/ (N x ∆V

- V

CRSN

), V

VPS

= V

CRSN

CRS

= -60mV to +60mV,

= 1.2V,

194 200 206 µS

N = number of phases enabled

DC Droop Amplifier

Transconductance

(CRS Sense Disabled)

Transient-Droop Transresistance R

Transient Detection Threshold

CURRENT LIMIT AND BALANCE

Current-Sense Input Preamplifier

Offsets

ILIM(AVE) Input Range

(Adjustable Mode)

V

ILIM(AVE) Average Current-Limit

Threshold Voltage

V

(Positive, Default)

ILIM(AVE) Average Current-Limit

Threshold Voltage

V

(Positive, Adjustable)

ILIM(AVE) Average Current-Limit

Threshold Voltage (Negative)

ILIM(AVE) Input Current I

ILIM(AVE) Current-Limit Default

Switchover Threshold

ILIM(PK) Peak Current-Limit

Threshold Voltage (Positive)

ILIM(PK) Peak Current-Limit

Threshold Voltage (Negative)

G

m(VPS

TRANS

ILIM(AVE

AVELIMIT

AVELIMIT

ILIM(AVE

V

PKLIMIT

∆I

V

V

VPS

VPS

CSP

/ (Σ∆VCS), V

= V

_ = 1.2V,

CSN

_ – V

CSN

_ = -60mV to +60mV

CRSP

= VCC,

194 200 206 µS

Current-sense gain (ACS = 10 typ) divided

by the voltage preamplifier

transconductance (G

m(TRC)

= 2ms typ)

4.75 5.0 5.25 kΩ

Measured at VPS with respect to steadystate VPS regulation voltage; falling edge,

-30 -25 -20 mV

5.5mV hysteresis (typ)

CSP_ - CSN_ -2.0 +2.0 mV

V

REF

- 0.2

V

mV

CRSP - CRSN; ILIM(AVE) = V

V

ILIM(AVE

CRSP - CRSN

V

ILIM(AVE

CRSP - CRSN; ILIM(AVE) = V

CC

= V

= V

CC

V

REF

- 1.0

22 25 28 mV

- 0.2V 7 10 13

REF

- 1.0V 46 50 54

REF

-30 -25 -20 mV

-0.1 +0.1 µA

CC

V

CC

- 0.4

V

mV

CSP_ - CSN_,

ILIM(PK)

LIM(PK)

= R

TRC

R

8V / V

CSP_ - CSN_, R

V

PKLIMIT

, V

PKLIMIT

x

ILIM(PK)

= 50mV

V

PKLIMIT

V

PKLIMIT

= R

V

3

- 1.0

= 30mV 24 30 36

= 50mV 40 50 60

x 8V /

TRC

-60 -50 -40 mV

4 _______________________________________________________________________________________

Page 5

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

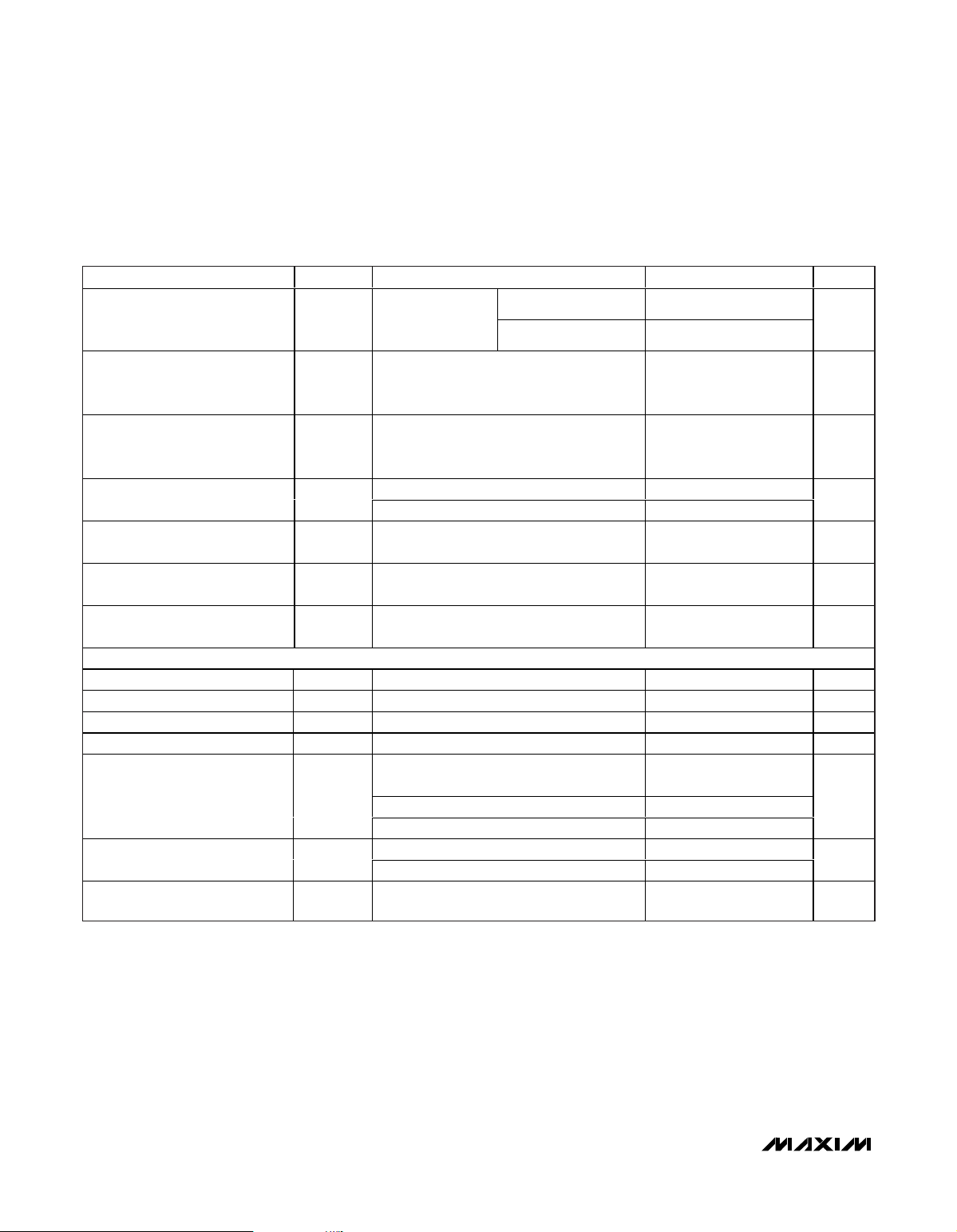

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

are at T

ILIM(PK) Idle Current-Limit

Threshold Voltage (Skip Mode)

Current-Sense Input Current

Current-Sense Common-Mode

Input Range

Phase Disable Threshold CSP4 3 VCC - 1

CRS Sense Input Disable

Threshold

LOGIC AND I/O

Logic Input High Voltage V

Logic Input Low Voltage V

SHDN No-Fault Threshold To enable no-fault mode 11 13 V

D0–D4 Logic Input High Voltage 0.8 V

D0–D4 Logic Input Low Voltage 0.4 V

OSC 3-Level Input Logic Levels V

SKIP Input Logic Levels V

Logic Input Current SHDN, SKIP, SUS, OSC, D0–D4 = 0 to 5V -1 +1 µA

Logic Output High Voltage V

Logic Output Low Voltage V

= +25°C.)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, OSC = REF, V

SHDN

V

IDLE

OSC

SKIP

IH

IL

OH

OL

= V

FBS

S KI P

T RC

= V

≥ 1.2V ,

x 8V / V

SOURCE

SINK

VPS

C S P _ - C S N _, V

I LI M ( P K )

P KL IM IT

= R

= 50m V

R

V

CSP_, CRSP -0.2 +0.2

CSN_, CRSN -1.0 +1.0

CRSP, CRSN, CSP_, CSN_ 0 2 V

CRSP 3 V

SHDN, SUS 2.4 V

SHDN, SUS 0.8 V

PWM_, DRSKP; I

PWM_, DRSKP; I

= V

CRSN

= 0°C to +85°C, unless otherwise specified. Typical values

A

P KL IM IT

High (VCC)

Medium (REF) 1.8 2.2

Low (GND) 0.4

High 1.2

Low (GND) 0.8

= 3mA

= 3mA 0.4 V

CRSP

,

= V

CSP_

= 1.20V, V

258mV

V

-

CC

0.4

V

-

CC

0.4

= 0.8V, OFS = SUS =

SUSV

V

CC

0.4

V

-

CC

- 1

CC

0.4

-

MAX8707

µA

V

V

V

V

V

_______________________________________________________________________________________ 5

Page 6

用于

)

AMD Hammer CPU

核电源的多相、

固定频率控制器

ELECTRICAL CHARACTERISTICS

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

PWM CONTROLLER

Input Voltage Range V

MAX8707

DC Output Voltage Accuracy V

SUSV Input Range V

OFS Input Range V

OFS GAIN A

GNDS Input Range V

GNDS Gain A

Switching Frequency Accuracy

(Per Phase)

TIME Slew-Rate Accuracy

BIAS AND REFERENCE

Quiescent Supply Current (VCC)I

Shutdown Supply Current (VCC)I

Reference Voltage V

Reference Load Regulation ∆V

FAULT PROTECTION

Output Overvoltage-Protection

Threshold

= 5V, OSC = REF, V

SHDN

OUT

SUSV

OFS

OFS

GNDS

GNDS

f

SW

CC(SHDN

V

OVP

CC

CC

REF

REF

= V

VPS

Includes loadregulation error

(VPS = FBS)

Negative offsets 0 0.8

Positive offsets 1.2 2.0

∆V

/ ∆V

OUT

V

OFS

∆V

OUT

V

OFS

∆V

OUT

-200mV ≤ V

OSC = GND 180 220

OSC = REF 270 330

OSC = V

R

TIME

R

TIME

(2.28mV/µs)

Startup and shutdown, R

(4.75mV/µs) to 392kΩ (0.57mV/µs)

Measured at VCC, VPS and FBS forced

above the regulation points

Measured at VCC, SHDN = GND 10 µA

V

CC

I

REF

I

REF

Measured at VPS

with respect to

unloaded output

voltage, rising edge,

8mV hysteresis

OFS

= 0 to 0.8V

/ ∆V

OFS

= 1.2V to 2V

/ ∆V

GNDS

GNDS

CC

= 143kΩ (6.25mV/µs) -10 +10

= 47kΩ (19mV/µs) to 392kΩ

= 4.5V to 5.5V, I

= 0 to 500µA -2

= -100µA to 0 6.2

= V

FBS

; ∆V

; ∆V

,

≤ +200mV

= V

CRSN

= -40°C to +85°C, unless otherwise specified.) (Note 3)

A

DAC codes from

1.10V to 1.55V

DAC codes from

0.80V to 1.075V

SUS = V

= V

OFS

OFS,

= V

OFS

OFS

TIME

= 0 1.98 2.02 V

REF

PWM (SKIP = GND)

or SKIP mode when

≤ V

V

OUT

SKIP = V

V

> V

OUT

CRSP

CC

- V

REF,

= 47kΩ

TRIP

and

CC

TRIP

= V

= 1.20V, V

CSP_

4.5 5.5 V

-1.0 +1.0

-3.0 +3.0

-25 +25 mV

0.4 2.0 V

-0.131 -0.118

-0.131 -0.118

-200 +200 mV

0.95 1.05 V/V

540 660

-15 +15

-20 +20

150 250 mV

1.70 1.80 V

= 0.8V, OFS = SUS =

SUSV

%

V

V/V

kHz

%

12 mA

mV

6 _______________________________________________________________________________________

Page 7

用于

)

)

)

)

)

)

AMD Hammer CPU

核电源的多相、

固定频率控制器

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

Output Undervoltage-Protection

Threshold

VROK Threshold

VROK Output Low Voltage I

VCC Undervoltage-Lockout

Threshold

DROOP AND TRANSIENT RESPONSE

DC Droop Amplifier Offset -2 +2 mV

DC Droop Amplifier

Transconductance

(CRS Sense Enabled)

DC Droop Amplifier

Transconductance

(CRS Sense Disabled)

= 5V, OSC = REF, V

SHDN

V

V

UVLO(VCC

G

m(VPS

G

m(VPS

UVP

= V

VPS

Measured at VPS with respect to 70% of the

unloaded nominal output voltage

Undervoltage, measured at VPS with

respect to 87.5% of the unloaded output

voltage, falling edge, 15mV hysteresis

Overvoltage, measured at VPS with respect

to 112.5% of the unloaded output voltage,

rising edge, 15mV hysteresis

= 3mA 0.4 V

SINK

Rising edge, hysteresis = 20mV, PWM_

disabled below this level

∆I

/ (N x ∆V

VPS

- V

V

CRSP

N = number of phases enabled

∆I

/ (Σ∆VCS), V

VPS

= V

V

VPS

CSP

CSN

_ - V

V

= V

FBS

), V

CRS

= -60mV to +60mV,

CRSN

CRSP

_ = 1.2V,

_ = -60mV to +60mV

CSN

= V

CRSN

= -40°C to +85°C, unless otherwise specified.) (Note 3)

A

= V

VPS

= VCC,

CRSP

CRSN

= V

CSP_

= 1.2V,

= 1.20V, V

-40 +40 mV

-40 +40

-40 +40

4.10 4.45 V

190 210 µS

190 210 µS

= 0.8V, OFS = SUS =

SUSV

MAX8707

mV

Transient-Droop Transresistance R

CURRENT LIMIT AND BALANCE

Current-Sense Input Preamplifier

Offsets

ILIM(AVE) Input Range

(Adjustable Mode)

ILIM(AVE) Average Current-Limit

Threshold Voltage

(Positive, Default)

ILIM(AVE) Average Current-Limit

Threshold Voltage

(Positive, Adjustable)

ILIM(AVE) Average Current-Limit

Threshold Voltage (Negative)

ILIM(AVE) Current-Limit Default

Switchover Threshold

_______________________________________________________________________________________ 7

V

V

V

TRANS

ILIM(AVE

AVELIMIT

AVELIMIT

Current-sense gain (ACS = 10 typ) divided

by the voltage preamplifier

transconductance (G

CSP_ - CSN_ -2.5 +2.5 mV

CRSP - CRSN; ILIM(AVE) = V

CRSP - CRSN

CRSP - CRSN; ILIM(AVE) = V

m(TRC)

V

ILIM(AVE

V

ILIM(AVE

= 2mS typ)

CC

= V

REF

= V

REF

CC

- 0.2V 5 15

- 1.0V 44 56

4.50 5.25 kΩ

V

REF

- 1.0

20 30 mV

-31 -19 mV

3

V

REF

- 0.2

V

CC

- 0.4

mV

V

V

Page 8

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

ELECTRICAL CHARACTERISTICS (continued)

(Circuit of Figure 1. VCC= V

GNDS = PGND = SKIP = GND, D0–D4 set for 1.20V (D0–D4 = 01110). T

PARAMETER SYMBOL CONDITIONS MIN MAX UNITS

ILIM(PK) Peak Current-Limit

Threshold Voltage (Positive)

MAX8707

ILIM(PK) Peak Current-Limit

Threshold Voltage (Negative)

= 5V, OSC = REF, V

SHDN

V

PKLIMIT

= V

VPS

CSP_ - CSN_,

R

8V / V

CSP_ - CSN_,

R

V

ILIM(PK)

LIM(PK)

ILIM(PK)

PKLIMIT

= R

= R

= 50mV

FBS

TRC

TRC

= V

x

x 8V / V

= V

CRSN

= -40°C to +85°C, unless otherwise specified.) (Note 3)

A

V

PKLIMIT

V

PKLIMT

PKLIMIT

= V

CRSP

= 30mV 24 36

= 50mV 40 60

,

CSP_

= 1.20V, V

-60 -40 mV

= 0.8V, OFS = SUS =

SUSV

mV

ILIM(PK) Idle Current-Limit

Threshold Voltage (Skip Mode)

Current-Sense Input Current

Current-Sense Common-Mode

Input Range

Phase Disable Threshold CSP4 3

CRS Sense Input Disable

Threshold

LOGIC AND I/O

Logic Input High Voltage V

Logic Input Low Voltage V

D0–D4 Logic Input High Voltage 0.8 V

D0–D4 Logic Input Low Voltage 0.4 V

OSC 3-Level Input Logic Levels V

SKIP Input Logic Levels V

Logic Output High Voltage V

Note 2: VROK is blanked during the transitions, when the internal target is being slewed. See the Output-Voltage Transition Timing

Note 3: Specifications to T

section. VROK is reenabled in t

= -40°C are guaranteed by design and are not production tested.

A

V

IDLE

OSC

SKIP

OH

BLANK

C S P _ - C S N _, V

R

V

CSP_, CRSP -0.2 +0.2

CSN_, CRSN -1.0 +1.0

CRSP, CRSN, CSP_, CSN_ 0 2 V

CRSP 3

SHDN, SUS 2.4 V

IH

SHDN, SUS 0.8 V

IL

High (VCC)

Medium (REF) 1.8 2.2

Low (GND) 0.4

High 1.2

Low (GND) 0.8

PWM_, DRSKP; I

(20µs) after the transition is completed.

I LI M ( P K )

P KL IM IT

= R

= 50m V

S KI P

T RC

≥ 1.2V ,

x 8V / V

SOURCE

P KL IM IT

= 3mA

,

28mV

µA

V

V

CC

- 0.4

V

CC

- 0.4

CC

- 0.4

V

CC

- 0.4

V

V

V

V

V

8 _______________________________________________________________________________________

Page 9

用于

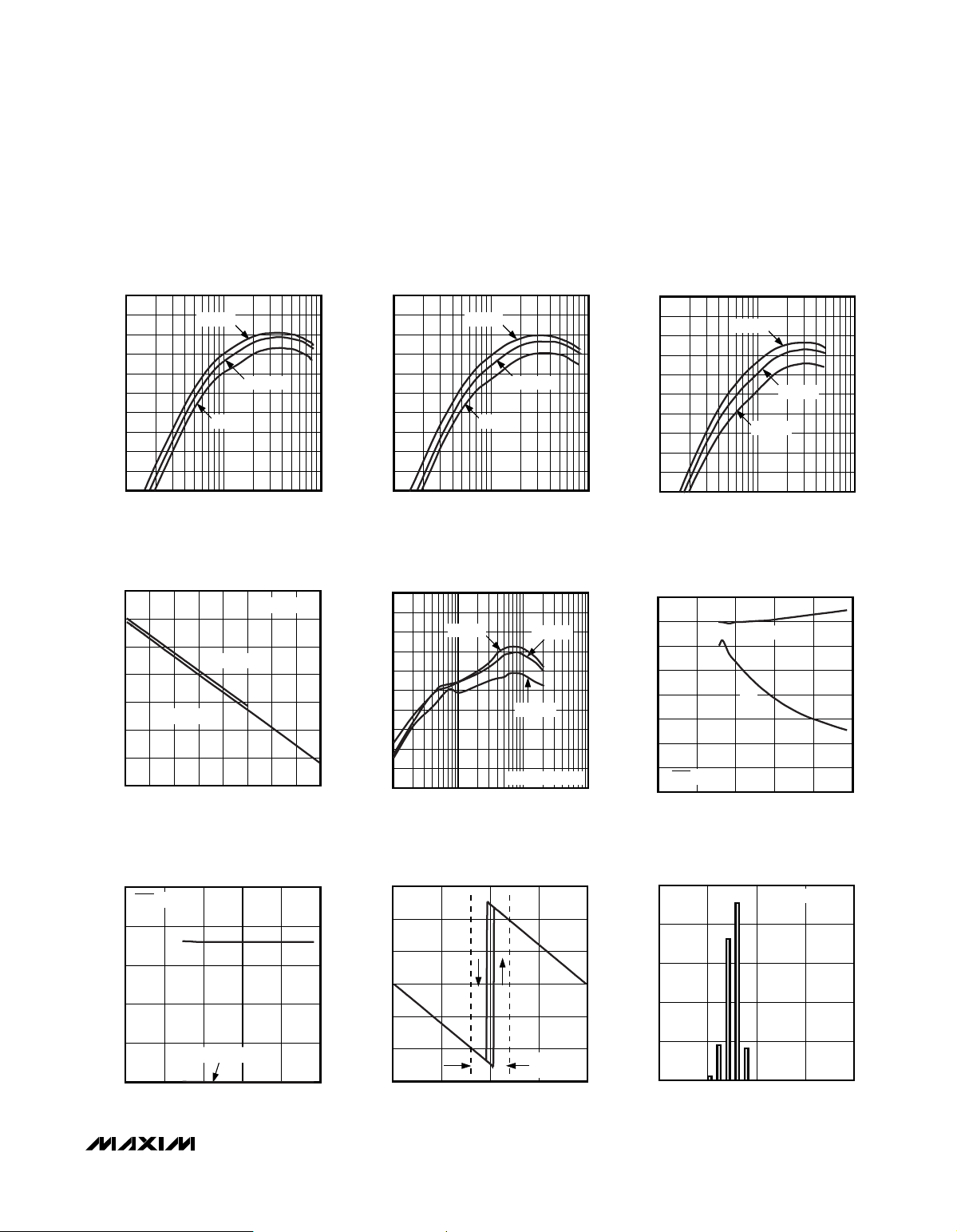

OUTPUT VOLTAGE DEVIATION

vs. LOAD CURRENT

MAX8707 toc04

LOAD CURRENT (A)

OUTPUT VOLTAGE (mV)

604020

-100

-80

-60

-40

-20

0

20

-120

080

V

OUT

= 1.00V

V

OUT

= 1.30V

VIN = 12V

SINGLE-PHASE

EFFICIENCY vs. LOAD CURRENT

(V

OUT

= 0.800V)

MAX8707 toc05

LOAD CURRENT (A)

EFFICIENCY (%)

110

60

70

80

90

100

50

0.1 100

VIN = 8V

VIN = 12V

VIN = 20V

SKIP = SUS = V

CC

0

50

100

150

200

0 5 10 15 20 25

NO-LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE

(4-PHASE FORCED-PWM MODE)

MAX8707 toc06

INPUT VOLTAGE (V)

SUPPLY CURRENT (mA)

I

BIAS

I

IN

SKIP = V

CC

0

2

6

4

8

10

0105152025

NO-LOAD SUPPLY CURRENT

vs. INPUT VOLTAGE

(1-PHASE PULSE SKIPPING)

MAX8707 toc07

INPUT VOLTAGE (V)

SUPPLY CURRENT (mA)

SKIP = GND

I

BIAS

I

IN

= 15µA

OUTPUT OFFSET VOLTAGE

vs. OFS VOLTAGE

MAX8707 toc08

OFS VOLTAGE (V)

OUTPUT OFFSET VOLTAGE (mV)

1.51.00.5

-100

-50

0

50

100

150

-150

0 2.0

UNDEFINED

REGION

REFERENCE VOLTAGE

DISTRIBUTION

MAX8707 toc09

REFERENCE VOLTAGE (V)

SAMPLE PERCENTAGE (%)

2.0052.0001.995

10

20

30

40

50

0

1.990 2.010

SAMPLE SIZE = 100

AMD Hammer CPU

核电源的多相、

固定频率控制器

_______________________________________________________________

(Circuit of Figure 1. VIN= 12V, VCC= 5V, SUS = SKIP = GND, SHDN = VCC, V

EFFICIENCY vs. LOAD CURRENT

(V

100

90

OUT

VIN = 8V

= 1.525V)

MAX8707 toc01

EFFICIENCY vs. LOAD CURRENT

(V

100

90

OUT

VIN = 8V

= 1.300V)

= 0.80V, TA= +25°C, unless otherwise specified.)

SUSV

EFFICIENCY vs. LOAD CURRENT

(V

100

MAX8707 toc02

90

典型工作特性

= 1.000V)

OUT

VIN = 8V

MAX8707

MAX8707 toc03

80

70

EFFICIENCY (%)

60

50

1 100

LOAD CURRENT (A)

VIN = 12V

VIN = 20V

10

80

70

EFFICIENCY (%)

60

50

1 100

LOAD CURRENT (A)

VIN = 12V

VIN = 20V

10

80

VIN = 12V

70

EFFICIENCY (%)

60

50

1100

VIN = 20V

10

LOAD CURRENT (A)

_______________________________________________________________________________________ 9

Page 10

用于

OUTPUT OFFSET VOLTAGE

DISTRIBUTION

MAX8707 toc10

OUTPUT OFFSET VOLTAGE (mV)

SAMPLE PERCENTAGE (%)

1-1-3

10

20

30

40

50

0

-5 53

SAMPLE SIZE = 100

1.550V

0.800V

VPS TRANSCONDUCTANCE

DISTRIBUTION

MAX8707 toc11

TRANSCONDUCTANCE (µS)

SAMPLE PERCENTAGE (%)

203201199197

10

20

30

40

50

60

70

0

195 205

SAMPLE SIZE = 100

-0.2

-0.1

0

0.1

0.2

0.3

0.4

0.5

0.6

0 5 10 15 20 25

CURRENT-SENSE VOLTAGE DIFFERENCE

vs. LOAD CURRENT

MAX8707 toc12

LOAD CURRENT (A)

CURRENT-SENSE DIFFERENCE (mV)

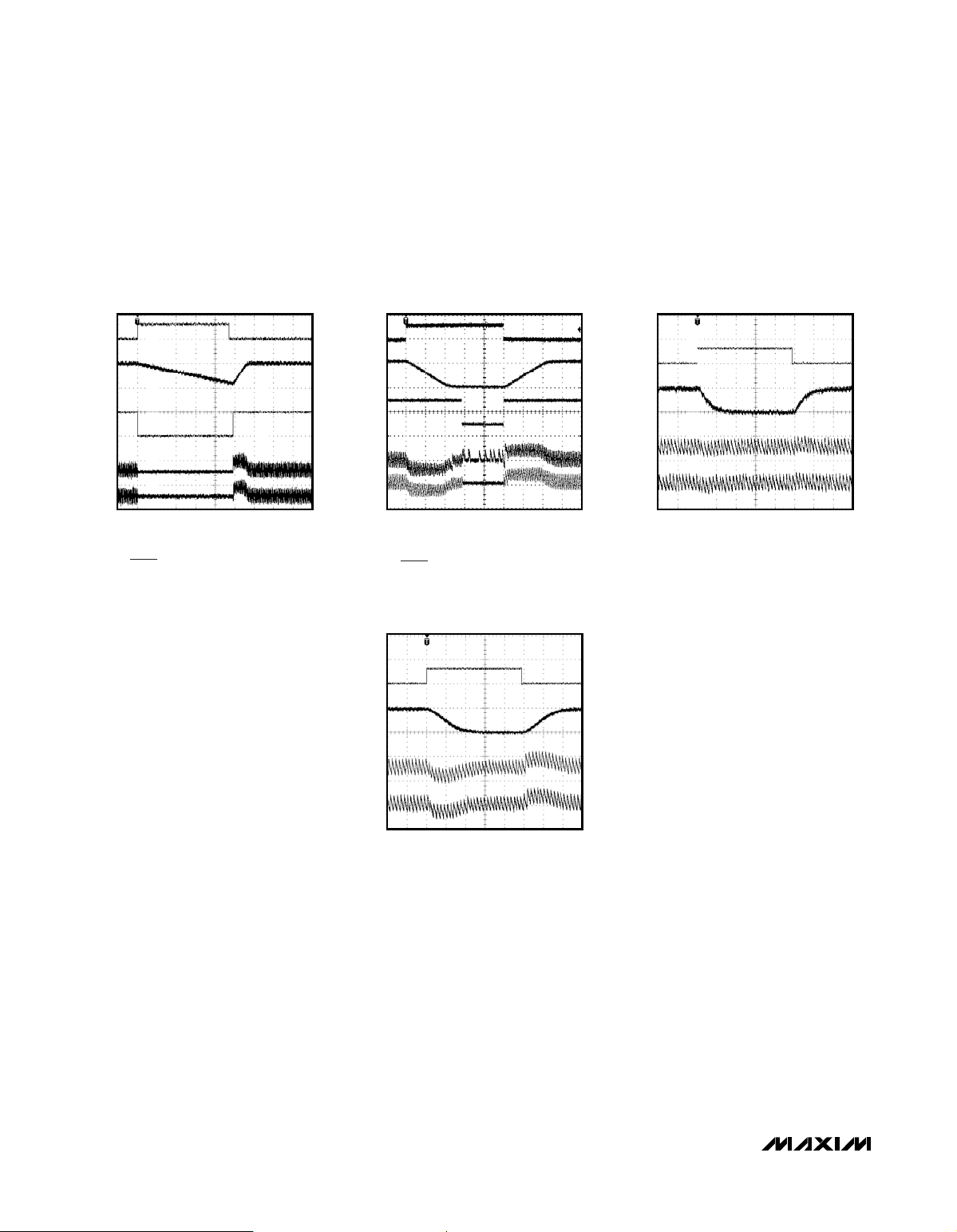

STARTUP WAVEFORM

(NO LOAD)

MAX8707 toc13

A. SHDN, 5V/div

B. DRSKP, 10V/div

C. REF, 2V/div

D. OUT, 1V/div

E. VROK, 10V/div

F. DL1, 10V/div

G. INDUCTOR CURRENT

(I

L1

), 10A/div

200µs/div

0

0

3.3V

A

B

C

D

E

F

G

0

0

5V

2V

1V

STARTUP WAVEFORM

(20A LOAD)

MAX8707 toc14

A. SHDN, 5V/div

B. DRSKP, 10V/div

C. REF, 2V/div

D. OUT, 1V/div

E. VROK, 10V/div

F. DL1, 10V/div

G. INDUCTOR CURRENT

(I

L1

), 10A/div

200µs/div

0

0

3.3V

A

B

C

D

E

F

G

0

0

5V

2V

1V

SHUTDOWN WAVEFORM

(NO LOAD)

MAX8707 toc15

A. SHDN, 5V/div

B VROK, 10V/div

C. OUT, 1V/div

D. DL1, 10V/div

E. INDUCTOR CURRENT

(I

L1

), 10A/div

200µs/div

0

0

3.3V

A

B

C

D

E

0

0

5V

1.3V

AMD Hammer CPU

固定频率控制器

核电源的多相、

____________________________________________________________

(Circuit of Figure 1. VIN= 12V, VCC= 5V, SUS = SKIP = GND, SHDN = VCC, V

= 0.80V, TA= +25°C, unless otherwise specified.)

SUSV

MAX8707

典型工作特性(续

)

10 ______________________________________________________________________________________

Page 11

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

____________________________________________________________

(Circuit of Figure 1. VIN= 12V, VCC= 5V, SUS = SKIP = GND, SHDN = VCC, V

65A

10A

1.30V

12V

20A

10A

0

0

A. I

OUT

50A/div

B. V

OUT

LOAD TRANSIENT

(V

OUT

= 10A TO 65A,

, 100mV/div

= 1.30V)

20µs/div

C. LX1, 10V/div

D. INDUCTOR CURRENT

(I

), 10A/div

L1

MAX8707 toc16

30A

A

B

C

D

1.00V

12V

10A

0

0

0

A. I

50A/div

B. V

= 0 TO 30A,

OUT

, 50mV/div

OUT

LOAD TRANSIENT

= 1.00V)

(V

OUT

20µs/div

C. LX1, 10V/div

D. INDUCTOR CURRENT

(I

= 0.80V, TA= +25°C, unless otherwise specified.)

SUSV

TRANSIENT PHASE REPEAT

0

0

A. I

= 0 TO 70A,

OUT

100A/div

, 100mV/div

B. V

OUT

), 10A/div

L1

MAX8707 toc17

70A

A

0A

1.30V

B

20V

C

20A

10A

D

典型工作特性(续

MAX8707 toc18

VIN = 20V

2µs/div

C. LX1, 10V/div

D. INDUCTOR CURRENT

), 10A/div

(I

L1

MAX8707

)

A

B

C

D

3.3V

0.2V

1.300V

1.275V

5A

5A

0

0

A. DPSLP, 5V/div

B. OFS, 200mV/div

C. V

OUT

DEEP-SLEEP TRANSITION

I

OUT

20µs/div

D. INDUCTOR CURRENT

), 10A/div

(I

, 25mV/div

L1

E. INDUCTOR CURRENT

), 10A/div

(I

L3

MAX8707 toc19

= 20A

SUSPEND EXIT TRANSITION

3.3V

A

B

C

D

E

0

1.30V

0.80V

5V

0

A. SUS, 5V/div

, 500mV/div

B. V

OUT

C. DRSKP, 5V/div

20µs/div

MAX8707 toc20

D. INDUCTOR CURRENT

(IL1), 10A/div

E. INDUCTOR CURRENT

), 10A/div

(I

L3

3.3V

A

0

1.30V

B

0.80V

C

5V

0

D

E

A. SUS, 5V/div

B. V

C. DRSKP, 5V/div

, 500mV/div

OUT

(SKIP = SUS)

200µs/div

MAX8707 toc21

D. INDUCTOR CURRENT

(IL1), 10A/div

E. INDUCTOR CURRENT

), 10A/div

(I

L3

A

B

C

D

E

SUSPEND TRANSITION

______________________________________________________________________________________ 11

Page 12

用于

SUSPEND TRANSITION

(SKIP = SUS)

MAX8707 toc22

A. SUS, 5V/div

B. V

OUT

, 500mV/div

C. DRSKP, 5V/div

D. INDUCTOR CURRENT

(IL1), 10A/div

E. INDUCTOR CURRENT

(I

L3

), 10A/div

100µs/div

0

3.3V

A

B

C

D

E

0

1.30V

0.80V

5V

SUSPEND TRANSITION

(SKIP = GND)

MAX8707 toc23

A. SUS, 5V/div

B. V

OUT

, 500mV/div

C. DRSKP, 5V/div

D. INDUCTOR CURRENT

(IL1), 10A/div

E. INDUCTOR CURRENT

(I

L3

), 10A/div

40µs/div

0

3.3V

A

B

C

D

E

0

1.30V

0.80V

5V

D1 (25mV) VID TRANSITION

MAX8707 toc24

A. D1, 5V/div

B. V

OUT

, 25mV/div

C. INDUCTOR CURRENT

(IL1), 10A/div

D. INDUCTOR CURRENT

(I

L3

), 10A/div

20µs/div

0

0

3.3V

A

B

C

D

0

1.30V

1.275V

D3 (200mV) VID TRANSITION

MAX8707 toc25

A. D3, 5V/div

B. V

OUT

, 200mV/div

C. INDUCTOR CURRENT

(IL1), 10A/div

D. INDUCTOR CURRENT

(I

L3

), 10A/div

20µs/div

0

0

3.3V

A

B

C

D

0

1.30V

1.10V

AMD Hammer CPU

固定频率控制器

核电源的多相、

____________________________________________________________

(Circuit of Figure 1. VIN= 12V, VCC= 5V, SUS = SKIP = GND, SHDN = VCC, V

= 0.80V, TA= +25°C, unless otherwise specified.)

SUSV

MAX8707

典型工作特性(续

)

12 ______________________________________________________________________________________

Page 13

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

___________________________________________________________________

MAX8707

引脚说明

PIN NAME FUNCTION

引脚

1D2

2 D3 Low-Voltage VID DAC Code Input

3 D4 Low-Voltage VID DAC Code Input (MSB)

4 N.C. No Connect. Leave open. Pin internally connected.

5 SKIP

6 SHDN

7 SUS

名称

功能

Low-Voltage VID DAC Code Input. The D0–D4 inputs do not have internal pullups. These 1.0V logic inputs

低电压

VID DAC

are designed to interface directly with the CPU. In normal mode (Table 4, SUS = GND), the output voltage

在正常模式下 (表4中,

is set by the VID code indicated by the logic-level voltages on D0–D4. In suspend mode (SUS = high), the

在挂起模式下 (

output voltage tracks the voltage at SUSV.

低电压

VID DAC

低电压

VID DAC

不连接。保持开路。该引脚有内部连接。

Pulse-Skipping Indicator Input. When pulse skipping, the controller blanks the VROK upper threshold.

跳脉冲指示输入。跳脉冲模式时,控制器屏蔽

3.3V or V

3.3V或V

GND = multiphase forced-PWM operation

GND =

The controller automatically enters forced-PWM mode during startup, shutdown, and the no-CPU VID

在启动、关断和无

mode.

Shutdown Control Input. This input cannot withstand the battery voltage. Connect to V

operation. Connect to ground to put the IC into its 50nA (typ) shutdown state. During the startup and

关断控制输入。该输入端不能承受电池电压。接至

shutdown transitions, the output voltage is ramped at 1/4th the output-voltage slew rate programmed by

状态。在启动和关断过渡过程中,输出电压的变化速率为

. After completing soft-shutdown, the drivers are disabled—DRSKP and PWM_ are pulled low.

R

驱动器——拉低

TIME

并清除故障锁存器。不要将

Forcing SHDN to 11V~13V disables both overvoltage-protection and undervoltage-protection circuits, and

clears the fault latch. Do not connect SHDN to >13V.

Suspend Control Input. When the controller detects a transition on SUS, the controller slews the output

挂起模式控制输入。当控制器检测到

voltage to the new voltage level determined by SUSV (SUS = high) or D0–D4 (SUS = low). The controller

或

D0–D4 (SUS =

blanks VROK during the transition and another 20µs after the new target voltage is reached. When SUS is

当

为高时,偏移 (

SUS

high, the offset (OFS) is automatically disabled.

码输入。

SUS = GND

高),输出电压跟踪

SUS =

码输入

码输入 (

MSB

(high) = 1-phase pulse-skipping operation (phases 2, 3, and 4 disabled)

CC

(高)= 单相跳脉冲工作模式 (2、3和4相被关闭)

CC

多相强制

工作模式

PWM

CPU VID

DRSKP和PWM_。将SHDN

低) 确定的电压。控制器在过渡期间和目标电压到达后的另外

OFS

输入不具有内部上拉。这些

D0–D4

),由

)

模式期间,控制器自动进入强制

接至大于

SHDN

SUS

) 被自动禁止。

的逻辑电平电压表示的

D0–D4

脚的电压。

SUSV

上门限。

VROK

V

CC

强拉到

11V~13V

的电压。

13V

有变化时,控制器将输出电压摆动至新的、由

时正常工作。接地则使IC进入

逻辑输入设计用来直接与

1.0V

码来设定输出电压。

VID

模式。

PWM

设定摆率的

R

TIME

,可禁止过压保护电路和欠压保护电路,

。软关断结束后,禁止

1/4

20µs屏蔽VROK

CPU

for normal

CC

(典型) 关断

50nA

SUSV (SUS =

连接。

高)

。

8 SUSV

9 ILIM(AVE)

10 OFS

Suspend-Mode Voltage Input. Connect to the output of a resistive voltage-divider from REF to GND to

挂起模式电压输入。连接到一个

provide an analog voltage between 0.4V to 2V. The output voltage is set by the voltage at SUSV when SUS

为高时输出电压由

SUS

is high.

Average Current-Limit Threshold Adjustment. The controller uses the accurate CRSP-to-CRSN current-

sense voltage to limit the average current per phase. When the average current-limit threshold is

平均电流限制门限调节端。控制器利用精确的

exceeded, the controller internally reduces the peak inductor current-limit threshold (ILIM(PK))

门限时,控制器内部以每

I

per µs until the average current remains within the programmed limits. When the accurate current

PKLIMIT

的门限内。禁止精确电流检测时 (

sensing is disabled (CRSP = V

connected to V

如果

ILIM(AVE)

The average current-limit threshold defaults to 25mV if ILIM(AVE)

ILIM(AVE)

the average current-limit threshold voltage is precisely 1/20th the voltage difference between ILIM(AVE)

内。切换到

and the reference: (V

threshold for switchover to the 25mV default value is approximately V

Adjustable Offset Voltage Input. For 0 < V

可调偏移电压输入。当

output. For 1.2V < V

REF和OFS

Voltages in the range of 0.8V < V

控制器禁止偏移放大器。

during suspend mode (SUS = high).

______________________________________________________________________________________ 13

CC

电压与基准电压差的

25mV

电压差的

SUSV

.

电压接至

默认值的逻辑门限约为

- V

REF

0 < V

< 2.0V, 1/8th the difference between REF and OFS is added to the output.

OFS

1/8

REF至GND

电压设定。

µs 2% I

PKLIMIT

CRSP = V

), the average current-limit circuit is disabled and I

CC

,则默认平均电流门限为

V

CC

1/20:(V

ILIM(AVE)

被加到输出上。

) / 20 for a range of 1.0V (V

< 0.8V时,OFS

OFS

< 1.2V are undefined. The controller disables the offset amplifier

OFS

之间的电阻分压器输出,提供

CRSP-CRSN

的速率降低峰值电感电流门限 (

),平均电流限制电路被禁止,

CC

- V

REF

ILIM(AVE

。

- 1V

V

CC

< 0.8V, 1/8th the voltage at OFS is subtracted from the

OFS

电压的

0.8V < V

OFS

检流电压来限制每相平均电流。当超过平均电流

。可调模式中,平均电流门限精确等于

25mV

)

)

1/8

< 1.2V

is connected to VCC. In adjustable mode,

/20,在1.0V(V

REF

被从输出中减去。当

范围没有定义。在挂起模式中 (

0.4V至2V

ILIM(PK

I

LIM(AVE)

- 1V)至1.8V(V

REF

- 1V) to 1.8V (V

- 1V.

CC

的模拟电压。

)),直至平均电流回到设定

应该接至

LIM(AVE)

- 0.2V). The logic

REF

1.2V < V

OFS

at 2% of

V

CC

should be

- 0.2V

REF

< 2.0V

SUS =

。

)范围

时,

高),

Page 14

用于

AMD Hammer CPU

固定频率控制器

核电源的多相、

________________________________________________________________

引脚

PIN NAME FUNCTION

11 OSC

MAX8707

12 GNDS

13 TIME

14 ILIM(PK)

名称

功能

振荡器选择输入。

Oscillator Select Input. OSC is a 3-level logic input for selecting the per-phase switching frequency.

对于每相

Connect to GND for 200kHz, connect to REF for 300kHz, or connect to V

Ground Remote-Sense Input. Connect GNDS directly to the CPU ground-sense pin. GNDS internally

地远端检测输入。将

connects to an amplifier that adjusts the output voltage, compensating for voltage drops from the regulator

补偿稳压器地到负载地的压差。

ground to the load ground.

Slew-Rate Adjustment Pin. Connect a resistor from TIME to GND to set the internal slew rate. A 47kΩ to

摆率调节引脚。

392kΩ corresponds to slew rates of 19mV/µs to 2.28mV/µs, respectively, for all suspend voltage

2.28mV/µs

transitions.

where dV

其中,

controller automatically reduces the slew rate by 1/4th. For all dynamic VID transitions, the rate at which

降至

the VID inputs (D0–D4) are clocked sets the slew rate, as long as it is less than the dv/dt set by R

dv/dt

Peak Inductor Current-Limit Threshold Adjustment (Cycle-by-Cycle Current Limit). If the voltage across the

峰值电感电流门限调节端 (逐周期限流 ) 。如果检流输入端(

current-sense inputs (CSP to CSN) exceeds the peak current-limit threshold, the controller immediately

控制器立即结束相应相的导通周期。

terminates the respective phase’s on-time. Connect a resistor R

cycle-by-cycle peak current-limit threshold:

300kHz

的摆率,对于所有挂起电压的转变

TARGET

dV

TARGET

。对于所有动态

1/4

。

为选择每相开关频率的3电平逻辑输入。对于每相

OSC

,接至

TIME对GND

t

TRAN SUS

/ dt = 6.25mV/µs × 143kΩ / R

/dt = 6.25mV/µs x 143kΩ/R

R

REF

GNDS

()

VID

ILIM PK

,对于每相

直接接至

()

CPU

接一只电阻,设置内部摆率。

||

VV

NEW OLD

=

dV dt

TARGET

转变,

VID

ILIM(PK)对GND

VR

×8

=

IR

PKLIMIT CS

,接至

600kHz

地检测引脚。

:

−

/

TIME

为摆率。对于软启动和关断过程,控制器自动将摆率

TIME

输入(

D0–D4

TRC

V

CC

GNDS

is the slew rate. For soft-start and shutdown, the

) 的变化速率决定了摆率,只要其小于

接一只电阻

。

内接至调节输出电压的一个放大器,

47kΩ至392kΩ

CSP至CSN

ILIM(PK)

200kHz

for 600kHz per phase.

CC

的阻值分别对应

) 的压降大于峰值限流门限,

R

,设置逐周期峰值限流门限:

from ILIM(PK) to GND to set the

ILIM(PK)

,接至

引脚说明(续

,

GND

19mV/µs

R

TIME

至

设定的

TIME

)

.

其中,

where R

望的峰值电流门限 (每相)。

R

TRC

Voltage Integrator Capacitor Connection. Connect a 470pF x (4 / η

15 CCV

16 TRC

14 ______________________________________________________________________________________

电压积分器电容连接端。

常数。

analog ground (GND) to set the integration time constant.

Transient-Voltage Preamplifier Output. Connect a resistor (R

瞬态电压预放大器输出。

transient droop based on the voltage-positioning requirements. TRC does not affect the DC steady-state

TRC

droop. Choose R

as defined in the Design Procedure (page 33). If voltage positioning is not required, R

如

设计步骤中所定

by the stability requirements. TRC is high impedance in shutdown.

TRC

为检流元件 (电感的

R

CS

is the resistance value of the current-sense element (inductors’ DCR or current-sense resistor),

CS

is the resistance between TRC and REF, and I

CCV

不影响直流稳态下垂。根据以下公式来选择

TRC

RA

为高阻。

TRC与REF

based on the equation:

=

TRC CS

(第33页)。如果不需要电压定位,则根据稳定性要求来确定

或检流电阻) 的阻值,

DCR

对模拟地 (

⎛

⎜

⎝

GND

间接一只电阻 (

RR

TRANS CS

R

η

PH DROOP AC

) 接一只

R

TRC

()

为

R

PKLIMIT

470pF x (4/η

),根据电压定位要求来设定瞬态下垂。

R

TRC

:

TRC和REF

TRC

is the desired peak current limit (per phase).

) or greater capacitor from CCV to

) 或容值更大的电容,以设置积分时间

PH

PH

) between TRC and REF to set the

TRC

之间的电阻值,

⎞

⎟

⎠

。在关断模式中,

R

TRC

I

is determined

TRC

PKLIMIT

为期

Page 15

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

________________________________________________________________

引脚说明(续

MAX8707

)

引脚

17 REF

18 VROK

19 GND

20 PGND

21 V

22 PWM1

23 PWM2

24 PWM3

25 PWM4

26 DRSKP

27 FBS

名称

CC

功能

基准电压输出。对

2.0V

电流。由于

500µA

开漏极电源好输出。上电后,只要输出电压处于稳压状态,则

(输出电压转换),则控制器屏蔽

(

模拟地。将

功率地。驱动器控制输出 (

模拟电源输入。

大的旁路陶瓷电容到模拟

相1的

相2的

相3的

相4的

驱动器跳脉冲控制输出。推挽逻辑输出,用于控制跳脉冲模式的驱动器IC的工作模式。

PGND

零比较器,并工作在跳脉冲模式。

远端反馈检测输入。

控制器产生了一个与

SKIP =

高)下,

PWM

PWM

PWM

PWM

间摆动。当

REF

VROK

MAX8707

串联一只

V

CC

驱动器控制输出。关断模式中为逻辑低。

驱动器控制输出。关断模式中为逻辑低。

驱动器控制输出。关断模式中为逻辑低。

驱动器控制输出。当禁止 (

DRSKP

FBS接至CPU

接一只

GND

的负载调整误差,加载

上限被禁止。

的裸露垫盘接至模拟地。

PWM_

GND

为高时,驱动器IC工作在强制

输出电流等幅且极性相反的

VPS

0.22µF至1µF

(高阻)。在启动和关断期间,

VROK

)和驱动器跳脉冲输出 (

电阻到系统电源电压 (

10Ω

。

CSP4 = V

输出检测点上。为使因

(最大值)的旁路陶瓷电容。基准电压能为外部负载提供

会降低输出电压精确度。

REF

保持为高阻。一旦摆率控制有效

VROK

) 的地。

DRSKP

4.5V至5.5V

) 时或在关断模式中为逻辑低。

CC

模式。当

PWM

输入串联电阻引起的输出电压误差最小,

FBS

输入偏置电流。在关断模式中,

FBS

被强制拉低。在跳脉冲模式

VROK

) 。尽可能靠近IC接一只

为低时,驱动器IC使能过

DRSKP

1µF

DRSKP在V

为高阻。

FBS

或容值更

和

CC

28 VPS

29 CRSN

电压定位跨导放大器输出。在

下垂 (负载线)(请参见

= R

R

VPS

DROOP

其中,

R

电压 (

CSN_

来降低电压定位斜率的温度依赖性。要禁止电压定位功能,可将

高阻。

检流电阻负极输入。

流电阻,用于精确电压定位和电流限制。不使用时,浮空

______________________________________________________________________________________ 15

DROOP

CRSP和CRSN

) 输入之和。将电感直流电阻 (

电压定位放大器

/ (R

为期望的直流电压定位斜率,

) 的精密检测电阻。当

CRSN

VPS和FBS

x G

SENSE

为差分负极输入,用于1相电感电流的精确检测。在

之间接一只电阻

一节) 。

)

M(VPS)

为检流阻值,

R

SENSE

CRSP接至V

) 用作检流元件时 (无损检测) ,

R

DCR

CC

,根据要求的电压定位斜率来设定直流稳态

R

VPS

)

G

时,跨导放大器的输入电压为检流电压 (

VPS与FBS

CRSN(CRSP

M(VPS

= 200µs。R

应该包括一只

R

VPS

短接。在关断模式下,

CRSP和CRSN

上拉至

) 。

V

CC

SENSE

为形成检流

NTC

间接一只检

和

CSP_

热敏电阻

为

VPS

Page 16

用于

AMD Hammer CPU

固定频率控制器

核电源的多相、

________________________________________________________________

引脚

30 CRSP

名称

正极检流电阻输入。

电阻。如果所有相 (

检流(

CRSP和CRSN

功能

为差分正极输入,用于1相电感电流的精确检测。在

CRSP

CSP_和CSN_

) 功能。

) 都使用检流电阻,则将

CRSP接至V

CC

并浮空

MAX8707

31 CSP1

32 CSN1

33 CSN2

34 CSP2

35 CSP3

36 CSN3

37 CSN4

38 CSP4

相1的正极检流输入。根据检流的实现方式,该输入引脚应该接至检流电阻或

相1的负极检流输入。

相2的负极检流输入。

相2的正极检流输入。根据检流的实现方式,该输入引脚应该接至检流电阻或

相3的正极检流输入。根据检流的实现方式,该输入引脚应该接至检流电阻或

相3的负极检流输入。

相4的负极检流输入。

相4的正极检流输入。根据检流的实现方式,该输入引脚应该接至检流电阻或

若为固定3相工作时,则

CSP4接至V

CC

。

引脚说明(续

CRSP和CRSN

,省掉这个额外的

CRSN

检测滤波电容的正端。

DCR

检测滤波电容的正端。

DCR

检测滤波电容的正端。

DCR

检测滤波电容的正端。

DCR

)

间接一只检流

低压

39 D0

40 D1

VID-DAC

模式下 (表4中,

电压跟踪

低压

VID-DAC

____________________________

除了电池,

MAX8707

一般来说,这个

系统电源。采用外部偏置电源,可提高效率,并省下了

一个

线性稳压器的成本,否则的话,还需要集成一

+5V

个线性稳压器来为

独运行,则可外接一只线性稳压器来提供

16 ______________________________________________________________________________________

还需要一个外部的

偏置电源取自效率高达

+5V

电路和栅极驱动器供电。若需单

PWM

SUSV

码输入。

SUS =

脚的电压。

码输入。

偏置电源

+5V

+5V

+5V

输入没有内部上拉。这些

D0–D4

低),输出电压由

详细说明

(

)

V

CC

偏置电源。

95%的+5V

偏置电源。

D0– D4上VID-DAC

+5V

V

DRV

其中,

x Q

G

1.0V

偏置电源必须提供给

(

的栅极-驱动电源),这样需要的最大电流为:

FET

取自

I

CC

(每相) 确定的驱动器电源电流,如驱动器数据资料

中所确定。如果

须延迟使能信号 (

绪,以确保启动。

逻辑输入设计用来直接与

输入来设定。在挂起模式下(

(用于

V

CC

I

= ICC+ I

BIAS

DRIVE

Electrical Characteristics

偏置电源比电池电源先上电,则必

+5V

由低变高) ,直至电池电压已就

SHDN

连接。在正常

CPU

SUS =

PWM

表,

高),输出

控制器)和

为

I

DRIVE

f

SW

Page 17

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

开关频率

三电平逻辑输入可用来设置每相开关频率。

OSC

与

GND、REF或V

300kHz和600kHz

减小元件的尺寸,使应用在尺寸方面得到优化,但由于

较高的开关损耗,效率方面有所折扣。负载电流比较低

的超轻便设备能够接受这种折衷。低工作频率 (

OSC = GND

寸和板上空间为代价。

) 提供最佳的总体效率,但要以更大的元件尺

连接分别可设置工作频率为

CC

。高工作频率 (

600kHz,OSC = V

(OSC)

直接

OSC

200kHz

CC

200kHz

) 可

交错式多相工作

MAX8707

式对于输入和输出滤波的要求最低,降低了电磁干扰

(

EMI

流,这些相电路之间相位差

工作。正常工作时,不会同时开启高侧

输入电流随着工作相数的增加而同比降低,从而降低了

输入电压纹波、

入电容选择

少了元件数量——这就降低了成本,节省了板面空间,并

降低了元件的功率要求——使

本敏感应用的理想器件。

的所有工作相交错运行——这种错相工作方

) ,并提高了效率。多相控制器在多个相之间分摊电

相) 或

90°(4

功率损耗和

ESR

一节) 。因此,控制器获得了高性能,同时减

RMS

MAX8707

120°(3

MOSFET

纹波电流(请参见

成为大功率、成

相) 错相

。瞬态

输

瞬态相重复

出现一个瞬变时,控制器的响应时间取决于其自身快速

响应输出电压偏移和将电感电流摆动至新的电流水平的

能力。多相、固定频率控制器一般只在时钟沿响应,这

样就产生了一个相对于实际瞬态事件的响应延迟。为消

除这种延迟时间,

使控制器检测到重负载瞬态变化时立即响应。如果控制

器检测到输出电压降低了

重新触发已完成前一次导通周期的相。后面的相依然正

MAX8707

采用一种瞬态相重复功能,

,则瞬态检测比较器立即

25mV

常触发——在对应的振荡器边沿。这相当于提前一个整周

期触发了某一相,提高了总电感电流的摆率,提供一个

立即的瞬态响应。

、

反馈-调节放大器

电压定位放大器(稳态下垂

多相控制器集成了一个跨导放大器,用来给电压定位检

,

测通道增加增益。电流检测输入以差分方式检测一只检

流电阻(使能

上的压降。

单相检测 (

的检流输入(

出接至调节器的电压定位反馈输入(

输出电压检测点 (

其中,目标电压(

给出,跨导放大器输出电流 (

(

) 来确定(当

η

PH

I

VPS

或者:

当禁止

其中,如

为

阻而引起输出电压误差,另一个跨导放大器产生一个等

值且反向的电流施加到

将

CRS

Electrical Characteristics

。为避免因

200µs

VPS与FBS

检测时) 或电感

CRS

(电压定位检测) 放大器的输入可以来自于

VPS

检测) 结果乘以工作相数,或所有工作相

CRS

) 之和(

CS_

V

OUT

CRS

= η

I

= ∑ (V

VPS

检测时 (

直接短路,可禁止电压定位。

CRSP = V

) 之间的电阻确定了电压定位增益:

FBS

= V

TARGET

V

PH (VCRSP

) 的定义在

TARGET

I

检测被使能时) :

CRSP = V

VPS

VPS

- V

- V

CSP_

FBS

CSN_

CC

电流流经引线电阻或反馈滤波电

输入。

(禁止

DCR

) 。跨导放大器的输

CC

) ,因此,

VPS

- R

VPS IVPS

额定电压选择

) 由检流电压和工作相数

) G

CRSN

) 。

M(VPS)

) G

M(VPS)

表所示,

CRS

G

M(VPS

检测时)

和

VPS

一节中

一般

)

MAX8707

)

______________________________________________________________________________________ 17

Page 18

用于

AMD Hammer CPU

固定频率控制器

5V BIAS

MAX8707

VDD1

C

VCC1

R

4.7µF

10Ω

CC

DD

V

V

C

VCC1

TSET

核电源的多相、

VDD2

4.7µF

C

DRHOT

100kΩ

R

1.0µF

TSET1

R

AGND

VRON

SHDN

DRHOT

SKIP

PWM1

PWM2

R

VCC2

VCC2

C

1.0µF

TSET2

TSET

R

SKIP

AGND

10Ω

CC

DD

V

V

PWM1

PWM2

VRON

DRHOT

SHDN

R

VCC

8V TO 20V

5V BIAS

10Ω

CC

V

BST1

PWR INPUT

IN

C

CSP1

R

1.5kΩ

VCC

1.0µF

C

GND

CSP1

D0D1D2D3D4

N

CS1

C

H1

BST2

0.22µF

DH1

CSN1

SHDN

R

CSN1

C

L1

CRSP

4700pF

SKIP

MAX8702

LX1

DL1

L1

N

CRSENSE

R

100Ω

R

CRSP

H2

N

CRSN

CRS

C

1.0mΩ

100Ω

1000pF

DH2

CRSN

LX2

DL2

PGND

L2

N

L2

CSP3

R

1.5kΩ

CS2

0.22µF

C

CSN2

C

4700pF

CSN2

CSP2

PWM2

PWM1

DRSKP

PWM3

8V TO 20V

CCV

C

PWM4

BST1

IN

C

PWR INPUT

1000pF

CCV

H3

N

BST2

TIME

R

TIME

DH1

143kΩ

LX1

L3

CSN3

MAX8702

DL1

H4

N

CSP3

R

1.5kΩ

CS3

0.22µF

C

CSN3

4700pF

C

L3

N

CSP3

DH2

LX2

DL2

PGND

L4

N

L4

CSP4

R

1.5kΩ

CS4

0.22µF

C

CSN4

C

4700pF

CSP4

CSN4

PGND

OUTPUT

(CPU CORE SUPPLY)

MAX8707

TRC

REF

ILIM(AVE)

OFS

ILIM(PK)

VROK

OSC

SUS

SUSV

GNDS

VPS

CPU REMOTE-SENSE CONNECTIONS

FBS

VID INPUTS

图

1. 标准MAX8707 AMD Hammer

(VRON)

ON

OFF

SKIP

TRC

R

2.0kΩ

PWM

应用电路

ILIMAVE1

REF

C

R

0.22µF

OFS1

R

49.9kΩ

ILIMAVE2

R

182kΩ

150kΩ

OFS2

R

20kΩ

ILIM(PK)

200kΩ

R

VROK

100kΩ

R

DPRSLPVR

3-LEVEL PIN

5V

REF

SUSV1

R

120kΩ

SUSV2

R

81kΩ

VPS

R

18 ______________________________________________________________________________________

6.49kΩ

GNDS

C

C

1000pF

R

FBS

GNDS

FBS

R

1000pF

10Ω

10Ω

Page 19

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

瞬态下垂放大器

MAX8707

控制负载的瞬态变化 (在

控制器集成了一个瞬态下垂跨导放大器,用来

应用中很常见)。瞬态下垂

CPU

放大器可控制负载瞬变期间的电压定位,使其具有合适

的斜率,以补偿较慢的稳态电压定位放大器。检流输入

以差分方式检测

CSP_和CSN_

检流元件(电感的

DCR

或

检流电阻)上的压降。跨导放大器的输出连接到调节器的

瞬态响应输入端 (

间的电阻决定了瞬态电压定位增益,正如

率设计步骤

一节中所定义的。

如果不需要电压定位,则

载 (

∆V

OUT

/ ∆I

OUT

定性要求影响。

TRC

),因此,

和基准电压 (

TRC

REF

多相、固定频

R

由最差情况下的瞬态负

DROOP

) 的最大输出电压下降量来确定,受稳

在关断模式中为高阻抗。

TRC

) 之

差分远端检测

多相控制器还包含了差分远端检测输入,以补偿电压在

印刷板走线和处理器电源引脚上的电压降。

MAX8707的GNDS

放大器直接对目标电压叠加一个偏移

量,调节输出电压,抵消地通道的压降。将反馈检测

(

) 、电压定位电阻 (

FBS

) 和地检测 (

R

VPS

GNDS

) 输入直接

接到处理器的核电源远端检测输出端。

积分放大器

积分放大器驱使

电压的直流平均值等于目标电压。

VPS

这个跨导放大器对反馈电压积分,精细调整输出电压

(图2) ,提供一个精确的、与输出纹波电压无关的直流输

出电压。积分放大器能使输出电压偏移

值) 。差分输入电压范围至少为

和交流纹波量。

地确定积分时间常数。采用

引脚外接的一只补偿电容可很方便

CCV

470pF x(4/η

,包括直流偏移量

±60mV

±100mV

PH

(典型

) 或容值更高

的陶瓷电容。

如果在跳脉冲模式 (

SKIP =

高) 发生瞬态变化,

MAX8707

会在瞬态过程开始时将放大器的输入端短接来禁止积分

器。积分器一直保持无效,直到瞬态过程结束 (内部目标

电压稳定下来) ,并且输出进入稳定状态 (检测到误差比

较器跳变)

当禁止电压定位 (

放大器的

20µs

±80mV

后。

VPS = FBS

) 时,瞬态下垂必须小于积分

最小调节范围,以保证足够的直流输出

精度。

表

标准多相应用中的元件选择

1.

MAX8707

DESIGNATION

Input Voltage Range 7V to 24V

VID Output Voltage (D4–D0) 1.50V (D4–D0 = 00010)

SUSV Suspend Voltage

(SUS = High)

Maximum Load Current 80A

Number of Phases (η

Inductor (Per Phase)

Switching Frequency

(Per Phase)

High-Side MOSFET

(N

, Per Phase)

H

Low-Side MOSFET

(N

, Per Phase)

L

Total Input Capacitance (CIN)

Total Output Capacitance

)

(C

OUT

Current-Sense Resistor

SENSE

)

(R

TOTAL

)

AMD HAMMER

COMPONENTS

Circuit of Figure 1

0.80V

4 phases

(1) MAX8705 + (2) MAX8702

0.56µH, 1.6mΩ

Panasonic ETQP4LR56WFC

300kHz (OSC = REF)

Siliconix (1) Si7892DP

Siliconix (2) Si7356DP

(8) 10µF, 25V

TDK C3225X7R1E106M

Taiyo Yuden

TMK325BJ106MN

(6) 330µF, 2.5V, 9mΩ

Sanyo 2R5TPE330M9

1.0mΩ

Panasonic ERJM1WTJ1M0U

偏移放大器

多相控制器还包括第五个放大器,用于给电压定位的负

载线叠加一个很小的偏移量。偏移放大器的输出直接与

目标电压相加,使偏移增益与

够使输出电压偏移

±100mV

来调节偏移量。输入为0至

。利用

0.8V

电压叠加一个负偏移电压,偏移量等于

电压 (

V

OFFSET

= -0.125 x V

OFS

码无关。该放大器能

DAC

输入端的分压电阻

OFS

时,偏移放大器对输出

1/8倍OFS

) 。输入为

1.2V至2V

输入端

时,

偏移放大器对输出电压叠加一个正偏移电压,偏移量等

MAX8707

______________________________________________________________________________________ 19

Page 20

用于

AMD Hammer CPU

固定频率控制器

V

CC

核电源的多相、

REF

GND

D4

DECODER

D3

MAX8707

D2

D1

D0

SUSV

SUS

SHDN

FBS

TRC

SKIP

REF

(2.0V)

DAC

TRC

CLAMP

FAULT

G

REFOK

M(TRC)

UVLO

TARGET

REF

ERROR

x 4

AMP

CHANGE

C

SLEW

TARGET

x 4

A = 10

RUN

WINDOW

COMPARATOR

REF

OSCILLATOR

R-TO-I

CONVERTER

PHASE ENABLE

DETECT

MAX8707

SUS

G

M

OFS

GNDS

G

M

TIME

CSP_

CSN_

SKIP

OSC

R-TO-I

CONVERTER

CURRENT-

LIMIT

COMPARATOR

DROOP

G

M(VPS)

INTEGRATOR

160µS

AMP

EA[4:1]

SUS

25mV

500kΩ

VPS

TARGET

RUN

TRAN

LOAD-TRANSIENT

DETECT COMPARATOR

CHANGE

FAULT

(UVP + THERMAL)

4-PHASE

FIXED-FREQ

CURRENT-MODE

PWM LOGIC

PGOOD AND

FAULT DETECT

图

2. MAX8707

ILIM(PK)

ILIM(AVE)

CRSP

CRSN

VPS

CCV

功能框图

20 ______________________________________________________________________________________

PWM_

DRSKP

PGND

VROK

Page 21

用于

表

元件供应商

2.

MANUFACTURER WEBSITE

BI Technologies www.bitechnologies.com

Central Semiconductor www.centralsemi.com

Coilcraft www.coilcraft.com

Coiltronics www.coiltronics.com

Fairchild Semiconductor www.fairchildsemi.com

International Rectifier www.irf.com

Kemet www.kemet.com

Panasonic www.panasonic.com

Sanyo www.secc.co.jp

Siliconix (Vishay) www.vishay.com

Sumida www.sumida.com

Taiyo Yuden www.t-yuden.com

TDK www.component.tdk.com

TOKO www.tokoam.com

AMD Hammer CPU

核电源的多相、

固定频率控制器

MAX8707

表

X =

工作模式真值表

3.

SHDN SUS SKIP OFS

GND X X X GND

V

CC

V

CC

V

CC

V

CC

V

CC

无关

GND GND GND or REF

GND V

GND X

V

CC

X X X GND

CC

XX

GND或REF

GND或REF

GND or REF

0 to 0.8V

0至0.8V

或

or

1.2V至2.0V

1.2V to 2.0V

OUTPUT

输出电压

VOLTAGE

GND

D0–D4

D0–D4

(无偏差)

(no offset)

D0–D4

D0–D4

(无偏差)

(no offset)

D0–D4

D0–D4

(加偏差)

(plus offset)

SUSV

SUSV

(无偏差)

(no offset)

GND

工作模式

OPERATING MODE

Low-Power Shutdown Mode. PWM_ outputs are forced low,

低功耗关断模式。强制拉低

and the controller is disabled. The supply current drops to

电源电流降低至

10µA (max).

Normal Operation. The no-load output voltage is determined

正常工作。由选定的

by the selected VID DAC code (D0–D4, Table 4).

空载输出电压。

Pulse-Skipping Operation. When SKIP is pulled high, the

跳脉冲工作。当拉高

MAX8707 immediately enters pulse-skipping operation

工作模式,可在轻载情况下自动在

allowing automatic PWM/PFM switchover under light loads.

上限被屏蔽。

VROK

The VROK upper threshold is blanked.

Deep-Sleep Mode. The no-load output voltage is determined

深睡眠模式。由选定的

by the selected VID-DAC code (D0–D4, Table 4) plus the

引脚设定的偏移电压之和来确定空载输出电压。

offset voltage set by OFS.

Suspend Mode/One Phase Skip. The no-load output voltage

挂起模式/单相跳脉冲。空载输出电压由出现在

is determined by the suspend voltage present on SUSV,

挂起电压决定,忽略其他所有有效的工作模式。

overriding all other active modes of operation.

Fault Mode. The fault latch has been set by either UVP or

故障模式。故障锁存器已被

控制器将一直保持

thermal shutdown. The controller remains in FAULT mode

切换

until V

。

SHDN

power is cycled or SHDN toggled.

CC

(最大值)。

10µA

VID DAC

SKIP时,MAX8707

VID DAC

模式,直到循环加载

FAULT

输出,禁止控制器。

PWM_

码 (表4中,

立即进入跳脉冲

PWM/PFM

码 (表4中,

或热关断故障置位。

UVP

) 来确定

D0 –D4

模式间切换。

D0–D4

SUSV

V

CC

) 与

上的

或

OFS

______________________________________________________________________________________ 21

Page 22

用于

AMD Hammer CPU

固定频率控制器

核电源的多相、

于基准电压与

0.125 x (V

REF-VOFS

输入电压差值的

OFS

1/8

倍 (

))。利用这种方式,控制器只需单个

V

OFFSET

输入就可实现正和负偏移。图3给出了这种分段线性传递

函数。传递函数中零以下、

个域没有定义。

输入不允许在这些区域,对于输出

OFS

2.0V

以上以及

0.8V至1.2V

的影响也没有规定。

在挂起模式中 (

高),控制器禁止偏移放大器。

SUS =

MAX8707

额定输出电压选择

额定空载输出电压 (

DAC或SUSV

V

TARGET

)与偏移电压以及远端地检测调整量(

之和确定,如下式所示:

V

TARGET

(当

SUD = GND

其中,

V

DAC

电压,

VID

在挂起模式(

压跟踪

(当

SUSV

SUS = V

MAX8707

一种 (图2)

CC

使用一个多路复用器,从三种不同输入中选择

—VID DAC

= V

DAC

时)

为正常工作 (

V

SUS =

为

OFFSET

高) ,偏移电压放大器被关闭,目标电

输入电压:

V

TARGET

时)

制器被关闭) 。启动时,

提升到

(

SUS =

D0–D4

高)。

在正常的强制

D0–D4

输入来设定输出电压。

输入,可直接与

D0–D4

可在

译码后的电压(

工作模式下 (

PWM

CPU

MAX8707

新的输出电压。必须同时改变

时间偏差不要大于

50ns

据,造成输出在部分时间内向错误的电压摆动,随后才

摆向需要的电压,延长了总的转换时间。

应的输出电压兼容于

AMD Hammer

) 由选定的电压基准 (

+ V

OFFSET

SUS =

引脚确定的偏移电压(表3) 。

OFS

= V

SUSV

的输出、

MAX8707

D0– D4

连接。不要悬空

+ V

GNDS

低,见表4) 期间选定的

+ V

GNDS

挂起电压或地 (控

SUSV

将目标电压从地逐渐

低) 或

SUS =

DAC

SUS =

输入

低) ,

为低压 (

SUSV

(

DAC

1.0V

D0–D4

工作的时候改变,以转变到一个

D0– D4

。否则,

,各位之间的转换

会读取不正确的数

DAC

DAC

编码和对

的规定 (表4)。

VID

V

GNDS

电压

D0–D4

利用

)逻辑

引脚。

几

=

OUTPUT OFFSET VOLTAGE

vs. OFS INPUT VOLTAGE

200mV

100mV

0

)

图

OUTPUT OFFSET VOLTAGE

-100mV

-200mV

输出偏移电压与

3.

0.8V 1.2V

0 2.0V

OFS VOLTAGE (V

输入电压。

OFS

UNDEFINED

REGION

1.5V0.5V 1.0V

)

OFS

当进入小功率挂起模式时,处理器可将电压调节器设置

到更低的输出电压,以降低功耗。

带缓冲的挂起电压输入(

SUSV

入。挂起电压可利用外部连接在

MAX8707

) 和一个数字

REF、SUSV

间的一个电阻分压器来调节。挂起电压调节范围为

至

2.0V(V

当

CPU

)

D0–D4

SUSV

蔽掉两个

式电压

切换到1相、跳脉冲控制方式,强制拉低

掉

VROK

)。

REF

挂起时(

设置的5位

高),控制器关闭偏移放大器,忽略

SUS =

VID-DAC

码,并将输出电压调整到由

电压设定的目标电压。转换过程中,

门限检测,直到摆率控制器到达挂起模

VROK

20µs

后。

20µs

后,

MAX8707(SKIP

DRSKP

上限检测。

输出电压的过渡过程

MAX8707

输入浪涌电流减至最小。这个特性给电路设计者带来了

以一种受控的方式实现模式间的过渡,自动使

挂起模式

集成了一个

控制输

SUS

和模拟地之

0.4V

MAX8707

屏

被拉低) 自动

,并屏蔽

22 ______________________________________________________________________________________

Page 23

用于

AMD Hammer CPU

核电源的多相、

固定频率控制器

表

4. AMD Hammer

D4 D3 D2 D1 D0

0 0 0 0 0 1.550 1 0 0 0 0 1.150

0 0 0 0 1 1.525 1 0 0 0 1 1.125

0 0 0 1 0 1.500 1 0 0 1 0 1.100

0 0 0 1 1 1.475 1 0 0 1 1 1.075

0 0 1 0 0 1.450 1 0 1 0 0 1.050

0 0 1 0 1 1.425 1 0 1 0 1 1.025

0 0 1 1 0 1.400 1 0 1 1 0 1.000

0 0 1 1 1 1.375 1 0 1 1 1 0.975

0 1 0 0 0 1.350 1 1 0 0 0 0.950

0 1 0 0 1 1.325 1 1 0 0 1 0.925

0 1 0 1 0 1.300 1 1 0 1 0 0.900

0 1 0 1 1 1.275 1 1 0 1 1 0.875

0 1 1 0 0 1.250 1 1 1 0 0 0.850

0 1 1 0 1 1.225 1 1 1 0 1 0.825

0 1 1 1 0 1.200 1 1 1 1 0 0.800

0 1 1 1 1 1.175 1 1 1 1 1 No CPU*

*无CPU

升到新的

模式:控制器进入无

输出电压。在无

VID

输出电压

模式时,以关断摆率将输出电压降低到0V。退出无

CPU

模式中,控制器保持待命状态,可以检测到

CPU

VID DAC

OUTPUT VOLTAGE

(V)

编码 (

SUS = GND

D4 D3 D2 D1 D0

VID

)

CPU

的变化。

OUTPUT VOLTAGE

模式时,控制器以启动摆率控制输出电压上

MAX8707

(V)

近乎理想的过渡过程,保证新输出电压的到来恰到好

处,同时又尽可能降低给定输出电容下的峰值电流。

输出电压的过渡过程开始时,

门限检测,阻止

VROK

VROK

MAX8707

开漏输出在过渡过程中改

屏蔽掉两个

变状态。在摆率控制器达到目标输出电压后再经过约

,控制器开启

20µs

在强制

PWM

模式时才开启

进入跳脉冲工作模式,则一直关闭

率 (由电阻

设定) 必须足够快,以确保在最长允许期

R

TIME

下限检测,但只有控制器工作

VROK

上限检测。如果控制器

VROK

VROK

上限检测。摆

限内完成过渡。

当过渡过程发生在跳脉冲模式时,

,并在开始时关闭积分器。

1.75V

MAX8707

OVP

设置

值保持在

OVP

1.75V

至

积分器保持关闭状态,一直到过渡过程完成 (内部目标达

到) ,并且输出进入稳定状态 (检测到一个误差比较器跳变

沿) 后

20µs

。

______________________________________________________________________________________ 23

MAX8707

自动将电流控制到在计算出的时间内完成过渡

过程所需的最低水平。摆率控制器利用一个内部的电容

和一个由

过程。总的过渡时间取决于

的精度 (

和

C

SLEW

ILIM(PK

设定的电流源来控制输出电压的过渡

R

TIME

、电压差和摆率控制器

R

TIME

的精度)。只要浪涌电流小于

)设定的电流门限,则摆率与输出总电容无

关。对于进入和退出挂起模式的过渡过程,过渡时间

(

)取决于下式:

t

TRAN

VV

||

-

NEW OLD

=

dV dt

TARGET

V

/

为新的目标电压。有

NEW

Electrical Characteristics

指标。在软启动和关断中,控

:

1/4

,

其中,

dV

V

OLD

的极限值参见

SLEW

TARGET

为初始输出电压,

率,

关

t

TIME Slew-Rate Accuracy

制器自动将摆率降低到

t

TRAN SUS

()

/ dt = 6.25mV/µs x 143kΩ / R

ILIM(AVE

为摆

TIME

表中的

)

Page 24

用于

AMD Hammer CPU

固定频率控制器

核电源的多相、

V

4

tt

TRAN START TRAN SHDN

() ()

在所有动态

率决定了电压的摆率,摆率的最大极限由

定。实际

于

MAX8707

压而摆动,使过渡过程相当平滑。

要产生一定的输出电压变化,每相需要提供的平均电感

电流为:

其中,

值,

R

TIME

19mV/µs至2.28mV/µs

dV

TARGET

为工作相数。

η

PH

==

过渡过程中,

VID

的阻值范围是

C

OUT

I

≅×

L

η

PH

为要求的摆率,

/dt

VID

47kΩ至392kΩ

的摆率。输出电压跟踪目标电

dV dt

(/)

TARGET

TARGET

dV dt

TARGET

输入(

D0–D4

R

TIME

为输出总电容

C

OUT

/

)的变化速

,分别对应

挂起模式过渡过程

(

选择强制

当配置为强制

挂起模式时,控制器按照

低到预先设定的

VROK

电压等于

控制器自动关断相2、相3和相4(拉低

相跳脉冲操作模式。跳脉冲模式下

退出挂起模式时 (拉低

使能的相 (拉高

摆率上升。在此期间控制器屏蔽

到转换结束—内部目标电压等于选定的

20µs

(强制为高阻态),直到过渡过程结束—内部目标

SUSV

后。

PWM

电压—

DRSKP

模式的

SUSV

MAX8707(SKIP

R

TIME

电压。 在此期间控制器屏蔽

后。在此屏蔽过程结束后,

20µs

) ,

SUS

MAX8707

) ,使输出电压按照

设定的速率将输出电压降

VROK

VROK

DRSKP

(强制为高阻) ,直

VID-DAC

工作模式

PWM

被拉低) 进入

),进入单

只监测下限。

立即激活所有被

R

TIME

挂起模式过渡过程

(

选择跳脉冲工作模式

如果

MAX8707

变高时,

SUS

DRSKP

载和输出电容确定的速率下降。内部目标电压仍然按以

前的速率变化,

),进入跳脉冲操作模式 (图5)。输出电压按照负

被设置成跳脉冲模式 (

MAX8707

VROK

立即关闭相2、相3和相4(拉低

保持为高阻态,直至输出到达新

SKIP =

高),则当

阻值设

确定的

电压—

的目标电压并经过了额外的

只进行下限监测。

VROK

退出深睡眠模式时 (拉低

电压向新的目标摆动。当输出电压高于内部目标时控制

器维持跳脉冲模式。随着内部目标电压接近输出电压,

MAX8707

压按照

VROK

在软启动、软关断和正常工作—

SKIP =

PWM

驱动器关闭过零比较器,迫使低侧栅极驱动波形完全互

补于高侧栅极驱动波形。这就使开关频率保持恒定,并

允许电感电流在轻载时反向,迅速给输出电容放电,实

现快速、精确的负向输出电压跳变。

强制

电流保持在每相

)

MOSFET

控制器进入挂起模式后,切换到一种低功率跳脉冲控制

方式。

启动所有被使能的相(拉高

R

(强制为高阻),直到过渡过程结束

控制方式。强制

PWM

确定的摆率上升。在此期间控制器屏蔽

TIME

低) —过程中,

工作模式的代价是:空载时

10mA至200mA

和开关频率有关。为在轻载情况下保持高效,

SUS),MAX8707

强制

PWM

MAX8707

PWM

后。这个时段结束后,

20µs

调整内部目标

DRSKP

20µs

工作模式(正常工作模式

正常运行(表5中,

CPU

工作于低噪声、强制

模式强行拉高

之间,和所用的外部

DRSKP

+5V

轻载跳脉冲模式

MAX8707

关闭多余的相,并使能/禁止驱动器的过零比较器。当使

能驱动器的过零比较器(拉低

关闭相的

零时拉低

迫使控制器在轻载时跳过一定数量的脉冲,防止输出电

容被过充电。当禁止过零比较器时,每个控制器在轻载

时保持

当配置为强制

起模式时,控制器会在目标电压到达预定的

)

经过

当跳脉冲工作模式被使能时,控制器在输出电压大于反

馈门限,并且电流检测电压超过

(

V

IDLE

连续的电感电流始终在

具有一个轻载工作模式控制输入(

DRSKP

为低,当其检流输入检测到电感电流为

PWM_

。这样可以阻止电感对输出电容放电,并

DL_

工作模式(强制

PWM

模式的

PWM

后自动切换到跳脉冲控制方式。

20µs

=0.1xV

PKLIMIT

PWM

MAX8707

)时终止导通周期。在重载时,

Idle Mode

SKIP

)时,控制器强制被

)。

(拉低

SKIP

SUSV

Idle Mode

检流门限以上,因此导

),使输出电

后。

,命令

偏置电源的

),用来

)进入挂

电压并

TM

检流门限

)

Idle Mode是Maxim Integrated Products, Inc.

24 ______________________________________________________________________________________

的商标。

Page 25

CPU CORE

VOLTAGE

SUS

INTERNAL

PWM CONTROL

PWM1

PWM2

PWM3

PWM4

DRSKP

FORCED-PWM

用于

AMD Hammer CPU

AUTO 1-PHASE SKIP

核电源的多相、

固定频率控制器

MAX8707

VID

SUSV

FORCED-PWM

图

4. 强制PWM

VROK

NOTE: OVP CONSTANTLY TRACKS THE INTERNAL TARGET, AND THE INTEGRATOR (CCV) IS CONSTANTLY ENABLED.

模式

(

SKIP =

CPU CORE

VOLTAGE

SKIP = SUS

INTERNAL

PWM CONTROL

PWM1

PWM2

PWM3

PWM4

DRSKP

HIGH-Z

t

BLANK

20µs typ

低)与挂起模式间的过渡。

LOW THRESHOLD ONLY

ACTUAL V

OUT

TARGET

1-PHASE SKIP FORCED PWM

HIGH-Z

t

BLANK

20µs typ

VID

SUSV

图

5.

OVP/CCV

跳脉冲模式

VROK

(

SKIP = SUS

HIGH-Z

OVP = 1.8V INTEGRATOR DISABLED

t

BLANK

20µs

)

与挂起模式间的过渡。

LOW VROK THRESHOLD ONLY

HIGH-Z

OVP TRACKS INTERNAL TARGET

INTEGRATOR ENABLED

t

BLANK

20µs

______________________________________________________________________________________ 25

Page 26

用于

AMD Hammer CPU

固定频率控制器

核电源的多相、

表

5. SKIP

SKIP

(输入)

(INPUT)

MAX8707

Low

低

(GND)

(GND)

High

高

(>1.2V)

(>1.2V)

设置表

SUS

(输入)

(INPUT)

Low

(GND)

(GND)

High

(3.3V或V

(3.3V or V

Don’t Care

低

高

无关

CC

CC

)

)

模式

MODE

Multiphase

多相

强制

PWM

Forced-PWM

1-Phase Pulse

单相

Skipping

跳脉冲

1-Phase Pulse

单相

跳脉冲

Skipping

通时间只取决于反馈电压门限。在轻载时,控制器始终

在反馈电压门限以上, 因此导通时间只取决于

Idle Mode

设定) 的

当控制器进入挂起模式,同时

器立即关闭另外三相,只保留一个主相

工作于跳脉冲模式时,控制器屏蔽

OVP

接,

PWM

闲置模式

检流门限,它接近于满负载限流门限 (由

。

10%

SKIP

门限跟踪选定的

MAX8707

在软启动和软关断期间都会自动采用强制

VID DAC

编码。无论

模式。

闲置模式

(

Idle Mode

) 电流门限迫使调节器在轻载时于每

被拉高时,多相控制

(

VROK

PWM1

)工作。当

上限检测,

SKIP

电流门限

(Idle Mode

)

个导通周期向负载输送一个最小数量的能量,因为控制

器不能在电流检测电压超过闲置模式电流门限

0.1 x V

PKLIMIT

) 前终止导通周期。由于过零比较器阻止开

(

关调节器吸收电流,因此控制器必须跳过一些脉冲,以

免对输出电容过度充电。当时钟沿到来时,如果输出电

压仍然大于反馈门限,控制器不会启动另一个导通周

期。实际上,这就迫使控制器在轻载工作条件下对输出

电压纹波的谷值进行调节。

DRSKP

DRSKP

输出)

(

(OUTPUT)

High

(V

(V

Low

(PGND)

(PGND)

Low

(PGND)

(PGND)

ILIM(PK)

如何连

V

IDLE

工作方式

OPERATION

The controller operates with a constant switching

frequency, providing low-noise forced-PWM operation. The

高

DD

低

低

DD

)

)

控制器工作在恒定的开关频率下,提供低噪强制

controller disables the zero-crossing comparators, forcing

方式。控制器禁止过零比较器,迫使低侧栅极驱动波形

the low-side gate-drive waveform to constantly be the

恒为高侧栅极驱动波形的互补。

complement of the high-side gate-drive waveform.

The controller automatically switches to pulse-skipping

operation 20µs after the target voltage reaches the SUSV

控制器在目标电压到达

voltage. Pulse-skipping operation forces the controller into

跳脉冲方式。跳脉冲方式迫使控制器在轻载时进入

PFM operation under light loads. Phase 1 remains active

工作模式。相1保持工作,而其他三相被关闭 (

PWM3和PWM4

while the other three phases are disabled—PWM2, PWM3,

and PWM4 pulled low.

Pulse-skipping operation forces the controller into PFM

跳脉冲模式强制控制器在轻载时进入

operation under light loads. Phase 1 remains active while

相1保持工作,其他三相被关闭—

the other three phases are disabled—PWM2, PWM3, and

PWM4 pulled low.

PWM4

被拉低。

SUSV电压20µs

被拉低)。

后自动切换到

工作模式。

PFM

PWM2、PWM3

跳脉冲模式的自动切换

在跳脉冲模式中,

DRSKP

,命令跳脉冲模式驱动器激活过零比较器。这样,

MAX8707

轻载时控制器会自动切换到

关闭三个相并强制拉低

工作模式 (图6),提供更

PFM

高的效率。这种切换受控于一个比较器,该比较器在电

感电流过零时终止低侧开关的导通周期。驱动器的过零

比较器在低侧

MOSFET

驱动器数据手册)。一旦

上检测电感电流 (参见跳脉冲模式

V

LX-VPGND

压差降低到过零比

较器阀值以下,则驱动器强制拉低DL。这种机制形成的

跳脉冲

PFM

和非跳脉冲