Page 1

___________________________________

概述

MAX8563/MAX8564/MAX8564A

是超低输出电压、双路和

三路

LDO

控制器,广泛应用于主板、台式笔记本、笔记本

以及其它领域的负载点电压变换,灵活方便,成本低廉。

这些器件含有精度为

±1%的0.5V

基准电压源,可对输出电

压进行精密的调节。

MAX8563有3路n沟道MOSFET

控制

输出,

MAX8564/MAX8564A有2

路控制输出。

当

VDD= 12V

时,每路的控制器输出可在

0.5V至3.3V

之间

调节。

VDD=5V

时,每路控制器输出可在

0.5V至1.8V

之

间调节。各路输出可独立使能,并在输出电压达到设定电

压的

94%

时产生

POK

信号。每路输出都具有保护电路,当

输出电压跌落到低于设定电压的

80%

而且持续时间大于

50µs

时,欠压比较器禁止输出,对电路提供短路保护。对

于灾难性短路故障,当输出电压下降至低于设定电压的

60%

时,稳压器会被立即关断。

MAX8563

采用16引脚

QSOP

封装,

MAX8564/MAX8564A

采用10引脚

µMAX

®

封装。

___________________________________

应用

主板

双路/三路电源

台式笔记本和笔记本

图形卡

___________________________________

特性

♦

MAX8563:3

路输出

♦

MAX8564/MAX8564A:2

路输出

♦

±1%

的反馈调整率

♦

输出电压可低至

0.5V

♦

可使用陶瓷输出电容

♦

宽工作电压范围,可采用5V或

12V

电压供电

♦

独立使能控制,

POK

信号实现顺序上电

♦

对于短路故障提供过载保护

♦

欠压短路保护

♦

可驱动n沟道

MOSFET

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

_______________________________

定购信息

19-3290; Rev 2; 6/06

可提供评估板

_________________________________________________________________________

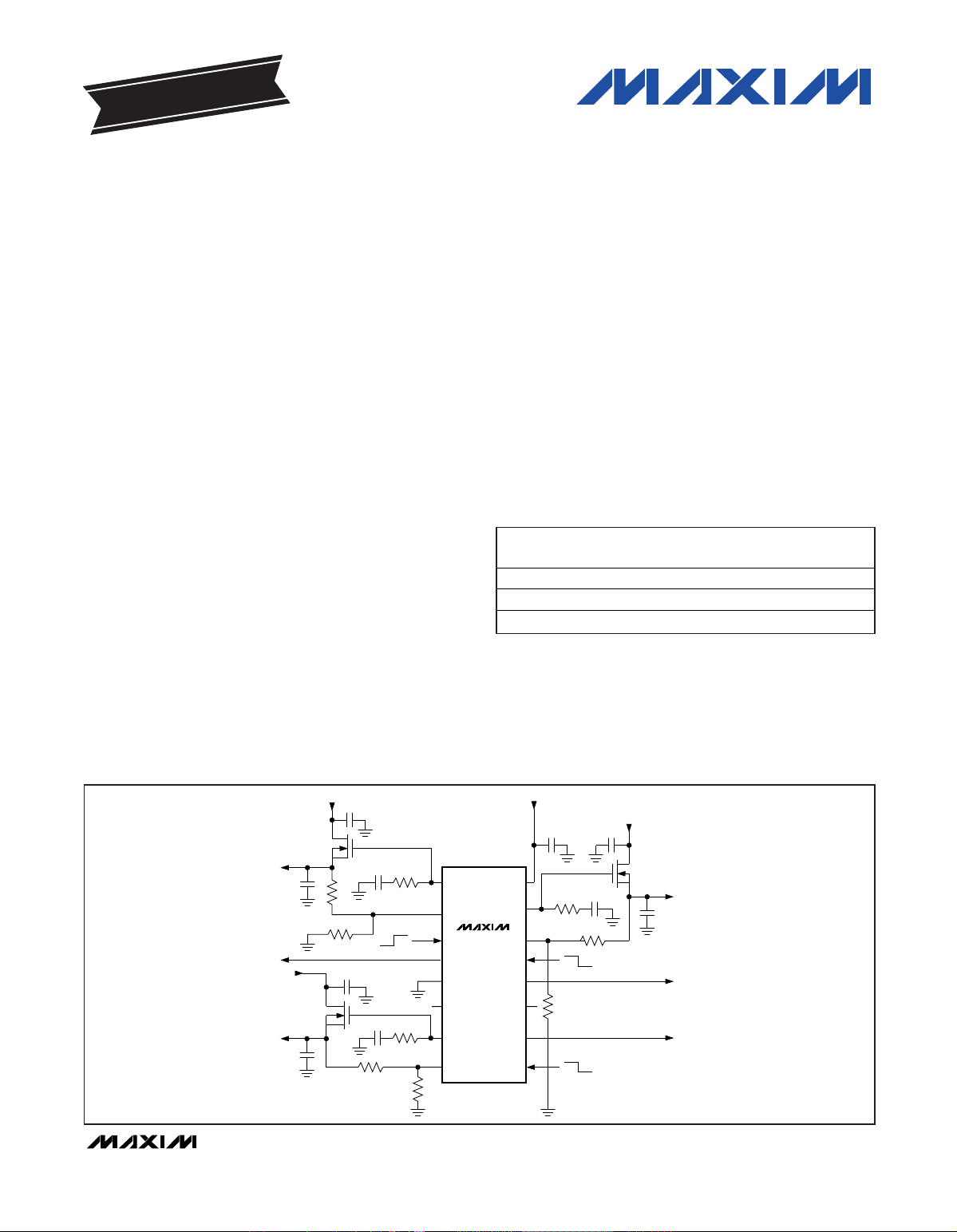

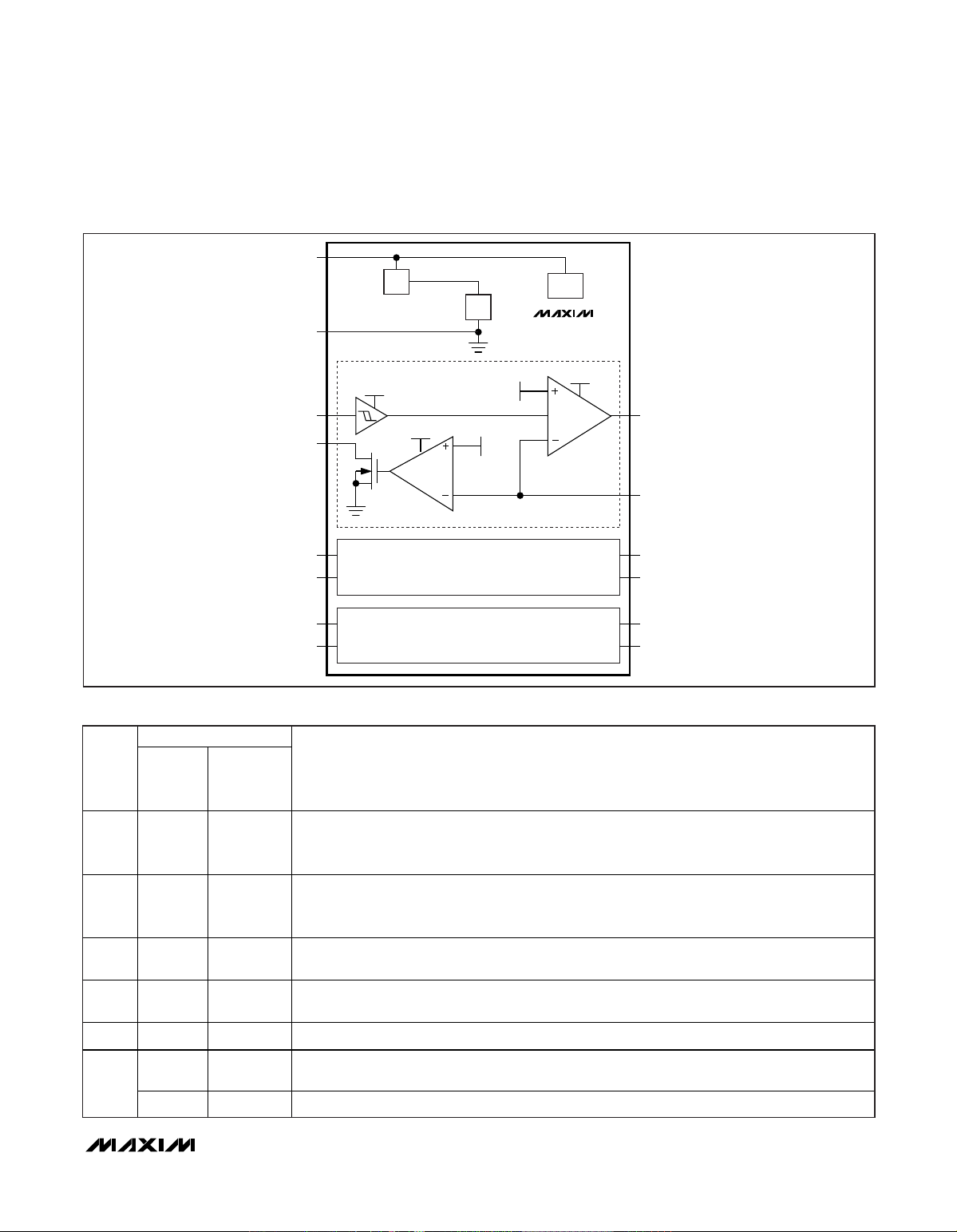

典型工作电路

+

表示无铅封装。

引脚配置在数据资料的最后给出。

µMAX是Maxim Integrated Products, Inc.

的注册商标。

________________________________________________________________ Maxim Integrated Products 1

本文是Maxim 正式英文资料的译文,Maxim不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

翻译错误,如需确认任何词语的准确性,请参考 Maxim提供的英文版资料。

索取免费样品和最新版的数据资料,请访问Maxim的主页:www.maxim-ic.com.cn。

超低压差稳压器

低电压

DSP、µP

和

微控制器电源

OFF

ON

OFF

ON

OFF

ON

DRV1

FB1

EN1

POK1

GND

N.C.

DRV3

FB3

V

DD

DRV2

FB2

EN2

POK2

N.C.

POK3

EN3

MAX8563

1.8V ±5% IN

C1

C5

R2

R1

C4

OUT1

1.5V/1.5A

R3

Q1

POK1

3.3V ±5% IN

OUT3

2.5V/2A*

C9

C10

C8

Q3

R8

R7

R9

R6

R5

R4

C6

C2 C3

C7

Q2

OUT2

1.05V/3A

POK2

POK3

5V OR 12V

IN

1.2V ±5% IN

*2.5V OUTPUT ONLY WITH V

DD

= 12V

PART TEMP RANGE

MAX8563EEE -40°C to +85°C 16 QSOP E16-1

MAX8564EUB -40°C to +85°C 10 µMAX U10-2

MAX8564AEUB+ -40°C to +85°C 10 µMAX U10-2

PINPACKAGE

PKG

CODE

Page 2

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VDD= V

EN1

= V

EN2

= V

EN3

= 5V, V

GND

= 0V, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VDDto GND............................................................-0.3V to +14V

DRV1, DRV2, DRV3, EN1, EN2,

EN3 to GND............................................-0.3V to (V

DD

+ 0.3V)

FB1, FB2, FB3, POK1, POK2, POK3 to GND ...........-0.3V to +6V

Continuous Power Dissipation (T

A

= +70°C)

10-Pin µMAX (derate 5.6mW/°C above +70°C) ........444.4mW

16-Pin QSOP (derate 8.3mW/°C above +70°C)........666.7mW

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

GENERAL

VDD Voltage Range 4.5 13.2 V

VDD Undervoltage-Lockout Threshold Rising, 200mV hysteresis (typ) 3.56 3.76 4.00 V

VDD Quiescent Current

VDD Shutdown Current EN1 = EN2 = EN3 = GND, VDD = 12V 25 µA

LDOs

FB_ Accuracy

FB_ Input Bias Current

DRV_ Soft-Start Charging Current

DRV_ Max Sourcing Current V

DRV_ Max Sinking Current V

DRV_ Max Voltage

FB_ Slow Short-Circuit Threshold Measured at FB_ (falling) 400 mV

FB_ Fast Short-Circuit Threshold Measured at FB_ (falling) 300 mV

Slow Short-Circuit Timer 50 µs

FB_ to DRV_ Transconductance 0.115 0.24 0.460 Mho

LOGIC

EN_ Input Low Level 0.7 V

EN_ Input High Level 1.3 V

EN_ Input Leakage Current

PARAMETER CONDITIONS MIN TYP MAX UNITS

V

= VDD = 12V (MAX8563) 930 1600

EN_

= VDD = 12V (MAX8564/MAX8564A) 660 1200

V

EN_

TA = 0°C to +85°C 0.494 0.5 0.504

= -40°C to +85°C 0.489 0.509

T

A

TA = +25°C -100 +100

T

= +85°C -8

A

MAX8563, MAX8564 100

MAX8564A 10

= 0.45V

FB_

= 0.6V

FB_

VDD = 5V, V

= 13.2V, V

V

DD

V

= 0 and VDD,

EN_

V

= 13.2V

DD

FB_

TA = 0°C to +85°C 4

= -40°C to +85°C 3 7

T

A

TA = 0°C to +85°C 3

= -40°C to +85°C 1.8 7

T

A

= 0.46V 4.7

= 0.46V 8.0 10.9

FB_

TA = +25°C -0.1 +0.1

T

= +85°C 0.001

A

µA

V

nA

µA

mA

mA

V

µA

Page 3

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)

(VDD= V

EN1

= V

EN2

= V

EN3

= 5V, V

GND

= 0V, TA = -40°C to +85°C, unless otherwise noted. Typical values are at TA = +25°C.) (Note 1)

Note 1: Specifications are production tested at TA= +25°C. Maximum and minimum specifications over temperature are guaranteed by

design.

_________________________________________________________________

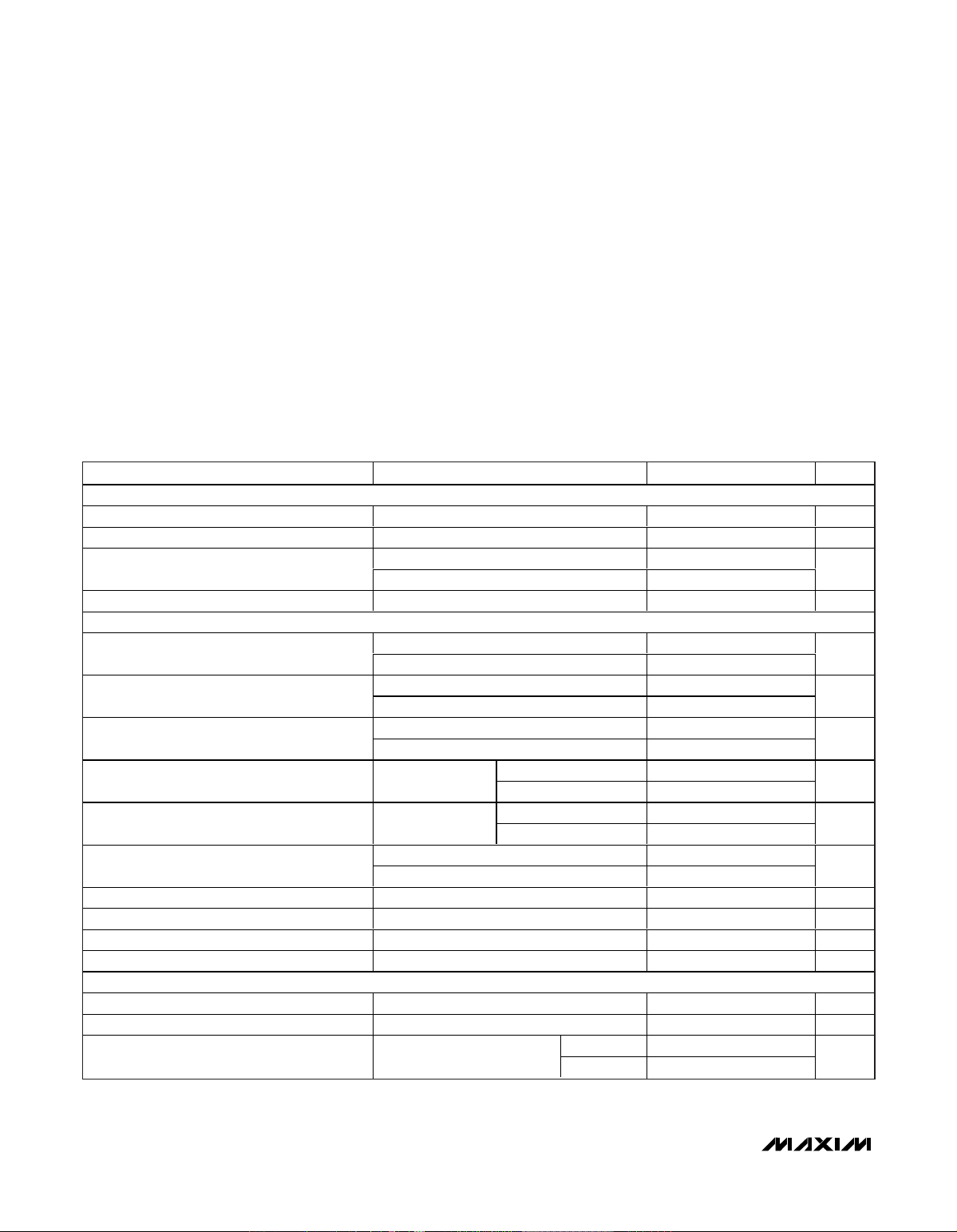

典型工作特性

(Circuit of Figure 1, TA = +25°C.)

OUTPUT VOLTAGE vs. INPUT VOLTAGE

MAX8563 toc01

INPUT VOLTAGE (V)

OUTPUT VOLTAGE (V)

1.91.81.71.61.51.41.31.21.1

1.1

1.2

1.3

1.4

1.5

1.6

1.0

1.0 2.0

VDD = 5V

V

OUT1

V

OUT2

OUTPUT VOLTAGE vs. INPUT VOLTAGE

MAX8563 toc02

INPUT VOLTAGE (V)

OUTPUT VOLTAGE (V)

3.41.4 2.2 2.61.8 3.0

1.2

1.4

1.6

1.8

2.0

2.2

2.4

2.6

1.0

1.0

VDD = 12V

V

OUT3

V

OUT1

V

OUT2

OUTPUT VOLTAGE vs. OUTPUT CURRENT

MAX8563 toc03

OUTPUT CURRENT (A)

OUTPUT VOLTAGE (V)

2.52.01.51.00.5

1.1

1.2

1.3

1.4

1.5

1.6

1.7

1.8

1.9

2.0

2.1

2.2

2.3

2.4

2.5

2.6

1.0

0 3.0

VDD = 12V

V

OUT3

V

OUT1

V

OUT2

FEEDBACK VOLTAGE

vs. TEMPERATURE

MAX8563 toc04

TEMPERATURE (°C)

FEEDBACK VOLTAGE (V)

603510-15

0.4988

0.4990

0.4992

0.4994

0.4996

0.4998

0.5000

0.4986

-40 85

VDD = 5V

VDD = 12V

PSRR vs. FREQUENCY

MAX8563 toc05

FREQUENCY (Hz)

PSRR (dB)

10k1k

10

30

40

20

50

60

70

80

90

100

0

100 100k

V

OUT1

= 1.5V

V

IN1

= 2V

LOAD = 1.25Ω

V

DD

= 12V

LOAD TRANSIENT

MAX8563 toc06

I

OUT2

V

DRV2

V

IN2

V

OUT2

20mV/div

AC-COUPLED

2V/div

200mV/div

AC-COUPLED

2A/div

0

10µs/div

0

VDD = 12V

FIGURE 1, C7 = 100µF 6TPE100MI

POK_ Threshold Falling Measured at FB_ (falling) 425 440 455 mV

POK_ Threshold Rising at Startup Measured at FB_ (rising) 455 470 485 mV

POK_ Output Low Level Sinking 1mA, VDD = 4.5V, V

POK_ Output High Leakage VDD = 5.5V

PARAMETER CONDITIONS MIN TYP MAX UNITS

= 0.4V 0.1 V

FB_

TA = +25°C 0.1

= +85°C 0.001

T

A

µA

Page 4

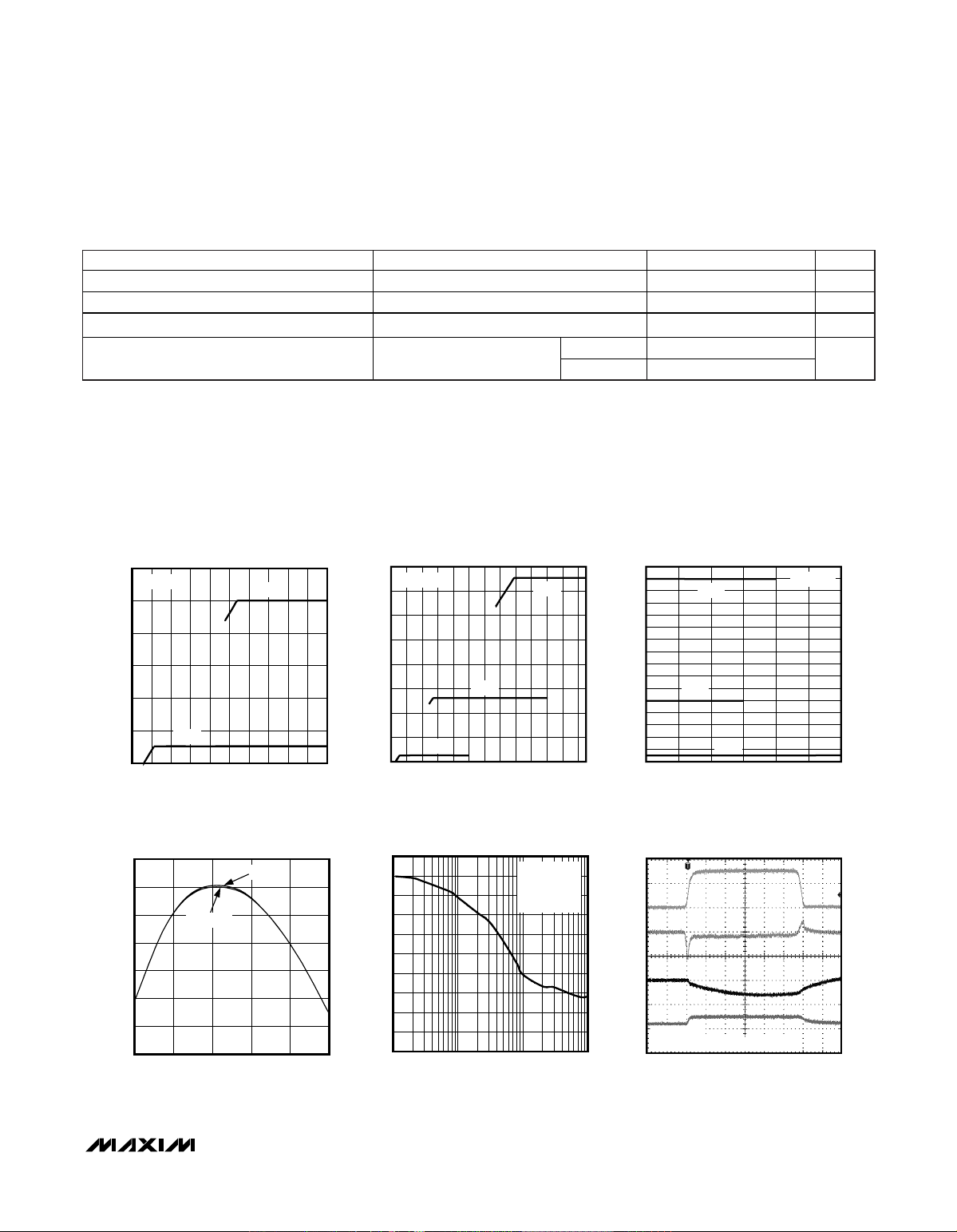

____________________________________________________________________

典型工作特性(续

)

(Circuit of Figure 1, TA = +25°C.)

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

4 _______________________________________________________________________________________

POWER-ON SEQUENCING WITH V

V

DD

V

OUT1

V

IN1

V

POK1

20ms/div

ENABLE-ON SEQUENCING

V

IN1

V

EN1

OUT1

DD

MAX8563 toc07

MAX8563 toc09

20V/div

0

2V/div

0

2V/div

0

2V/div

0

2V/div

0

2V/div

0

2V/div

0

POWER-ON SEQUENCING WITH V

V

DD

V

IN1

V

OUT1

V

POK1

SHORT-CIRCUIT PROTECTION

I

OUT1

V

OUT1

ENABLE CONFIGURED AS

SHOWN IN FIGURE 4

RD = 100kΩ, RE = 4kΩ

10ms/div

IN

MAX8563 toc08

20V/div

0

2V/div

0

2V/div

0

2V/div

0

MAX8563 toc10

5A/div

0

1V/div

0

V

POK1

2V/div

0

20ms/div

V

DRV1

20µs/div

2V/div

0

Page 5

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

_______________________________________________________________________________________ 5

_____________________________________________________________________

功能框图

______________________________________________________________________

引脚说明

引脚

名称

功能

n-MOSFET

驱动输出端。驱动外部n沟道

MOSFET

的栅极,对第1路输出进行调节。

EN1

为逻辑

低电平时,

DRV1

在内部被拉至地。该引脚外部串联一个RC电路用于补偿。参见

稳定补偿

部分。

输出1的反馈输入端。该引脚与第1路输出和

GND

间的电阻分压器的中点相连,设定第1路输出

电压。反馈调节电压为

0.500V

。参见

输出电压设置

部分。

第1路输出的使能控制端。该引脚为逻辑高电平时第1路输出工作,该引脚为逻辑低电平时第1路

输出禁止。该引脚接

V

DD

时第1路输出始终处于工作状态。

第1路输出的电源就绪状态指示端。当第1路输出低于标称稳压值的

12%

时,漏极开路输出拉低。

地。

第2路输出的电源就绪状态指示端。当第2路输出低于标称稳压值的

12%

时,漏极开路输出拉低。

无内部连接。

V

DD

VL

0.5V

REF

GND

V

DD

EN1

POK1

EN2

POK2

EN3

POK3 FB3

VL

POK

COMPARATOR

0.5V

UVLO

MAX8563

MAX8564

MAX8564A

GM

CONTROLLER 1

CONTROLLER 2

CONTROLLER 3

V

DD

DRV1

FB1

LDO

DRV2

LDO

FB2

DRV3

LDO

MAX8563

1 DRV1 DRV1

2FB1 FB1

3 EN1 EN1

4 POK1 POK1

5 GND GND

6

N.C. —

MAX8564/

MAX8564A

—POK2

Page 6

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

6 _______________________________________________________________________________________

____________________________________________________________________

引脚说明(续

)

引脚

名称

功能

第2路输出的使能控制端。该引脚为逻辑高电平时第2路输出工作,该引脚为逻辑低电平时第

2

路输出禁止。该引脚接

V

DD

时第2路输出始终处于工作状态。

n-MOSFET

驱动第3路输出。驱动外部n沟道

MOSFET

的栅极,对第3路输出进行调节。当

EN3

为逻辑低电平时,

DRV3

在内部被拉至地。该引脚外部串联一个RC电路用于补偿。参见

稳定补偿

部分。

第2路输出的反馈输入端。该引脚与第2路输出和

GND

间的电阻分压器的中点相连接,设定第

2

路输出电压。反馈调节电压为

0.500V

。参见

输出电压设置

部分。

第3路输出的反馈输入端。该引脚与第3路输出和

GND

间的电阻分压器的中点相连,设定第3路

输出的输出电压。反馈调节电压为

0.500V

。参见

输出电压设置

部分。

n-MOSFET

驱动的第2路输出。驱动外部n沟道

MOSFET

的栅极,对第2路输出进行调节。

当

EN2

为逻辑低电平时,

DRV2

在内部被拉至地。该引脚外部串联一个RC电路进行补偿。

参见

稳定补偿

部分。

第3路输出的使能控制端。该引脚为逻辑高电平时第3路输出工作,该引脚为逻辑低电平时第

3

路输出禁止。该引脚接

V

DD

时第3路输出始终处于工作状态。

+5V或+12V

电源输入端。该引脚与外部的

+5V或+12V

电源连接。该引脚与地间应连接一个

0.1µF

或容量更大的陶瓷旁路电容。

第3路输出的电源就绪状态指示信号输出端。当第3路输出低于标称稳压值的

12%

时,漏极开路

输出拉低。

无内部连接。

第2路输出的电源就绪状态指示信号输出端。当第2路输出低于标称稳压值的

12%

时,漏极开路

输出拉低。

第2路输出的使能控制端。该引脚为逻辑高电平时第2路输出工作,该引脚为逻辑低电平时第

2

路输出禁止。该引脚接

V

DD

时第2路输出始终处于工作状态。

第2路输出的反馈输入端。该引脚与第2路输出和

GND

间的电阻分压器的中点相连接,设定第

2

路输出的输出电压。反馈调节电压为

0.500V

。参见

输出电压设置

部分。

n-MOSFET

驱动的第2路输出。驱动外部n沟道

MOSFET

的栅极,对第2路输出进行调节。

当

EN2

为逻辑低电平时,

DRV2

在内部被拉至地。该引脚外部串联一个RC电路进行补偿。

参见

稳定补偿

部分。

+5V或+12V

电源输入端。该引脚与外部的

+5V或+12V

电源连接。该引脚与地间应连接一个

0.1µF

或更大的陶瓷旁路电容。

MAX8563

7

DRV3 —

8

FB3 —

9

10

11 N.C. —

EN3 —

POK3 —

MAX8564/

MAX8564A

— EN2

— FB2

— DRV2

—V

DD

12 POK2 —

13 EN2 —

14 FB2 —

15 DRV2 —

16 V

DD

—

Page 7

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

_______________________________________________________________________________________ 7

________________________________________________________________

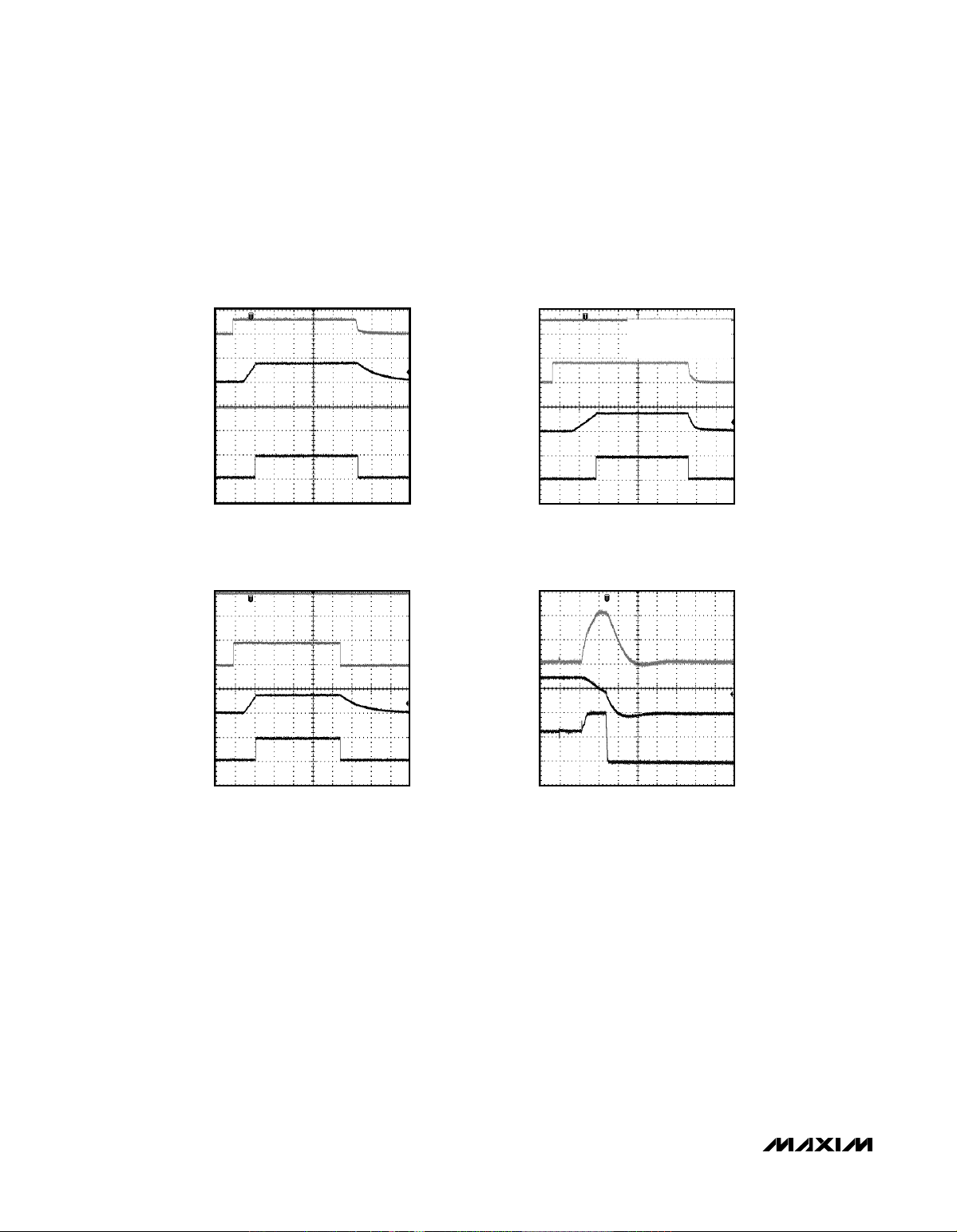

典型应用电路

MAX8563

:三路输出

图

1. MAX8563

典型应用电路

V

DRV2

FB2

EN2

POK2

5V OR 12V

DD

IN

C2 C3

C6

R4

R5

ON

OFF

1.2V ±5% IN

Q2

OUT1

1.5V/1.5A

POK1

3.3V ±5% IN

1.8V ±5% IN

C1

Q1

C5

R2

C4

R1

R3

ON

OFF

C8

DRV1

FB1

EN1

POK1

GND

MAX8563

OUT2

1.05V/3A

C7

POK2

OUT3

2.5V/2A*

*2.5V OUTPUT ONLY WITH V

C9

Q3

C10

R7

R8

R9

= 12V

DD

N.C.

DRV3

FB3

N.C.

POK3

EN3

R6

POK3

ON

OFF

Page 8

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

8 _______________________________________________________________________________________

_____________________________________________________________

典型应用电路(续

)

MAX8564/MAX8564A

:双输出

图

2. MAX8564/MAX8564A

典型应用电路

MAX8563

外部元件清单

MAX8564/MAX8564A

外部元件清单

V

DRV2

FB2

EN2

POK2

5V OR 12V

IN

C11 C17

DD

R13

1.2V ±5% IN

C18

R15

R14

ON

OFF

OUT1

1.5V/1.5A

C14

POK1

1.8V ±5% IN

C15

Q4

R16

R17

C20

OFF

R18

ON

DRV1

FB1

EN1

POK1

GND

MAX8564

MAX8564A

Q5

OUT2

1.05V/3A

C12

POK2

COMPONENTS QTY DESCRIPTION

C1, C3, C8 3

C4, C7, C9 3

C5, C6, C10 3 1µF, 16V X7R ceramic capacitors

Q1/Q2 (dual) 1

2.2µF, 10V X5R ceramic capacitors

(optional 100µF, 18mΩ, 6.3V

aluminum electrolytic, Sanyo

GTPE100MI in parallel)

C2 1 0.1µF, 16V X7R ceramic capacitor

100µF, 18mΩ, 6.3V aluminum

electrolytic capacitors

Sanyo GTPE100MI

Dual n-channel MOSFETs, 30V, 18mΩ

Vishay Si4922DY

Q3 1

R1 1 665Ω ±1% resistor

R2 1 620Ω ±5% resistor

R3 1 332Ω ±1% resistor

R4 1 390Ω ±5% resistor

R5 1 182Ω ±1% resistor

R6 1 165Ω ±1% resistor

R7 1 910Ω ±5% resistor

R8 1 1kΩ ±1% resistor

R9 1 249Ω ±1% resistor

n-channel MOSFET, 30V, 50mΩ

Fairchild Semiconductor FDD6630A

COMPONENTS QTY DESCRIPTION

C11 1 0.1µF, 16V X7R ceramic capacitor

C12, C14 2

C15, C17 2

C18, C20 2 1µF, 16V X7R ceramic capacitors

Q4/Q5 (dual) 1

R13 1 165Ω ±1% resistor

R14 1 182Ω ±1% resistor

R15 1 390Ω ±5% resistor

R16 1 665Ω ±1% resistor

R17 1 332Ω ±1% resistor

R18 1 620Ω ±5% resistor

100µF, 18mΩ, 6.3V aluminum

electrolytic capacitors

Sanyo GTPE100MI

2.2µF, 10V X5R ceramic capacitors

(optional 100µF, 18mΩ, 6.3V

aluminum electrolytic, Sanyo

GTPE100MI in parallel)

Dual n-channel MOSFETs, 30V, 18mΩ

Vishay Si4922DY

Page 9

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

_______________________________________________________________________________________ 9

____________________________

详细说明

MAX8563/MAX8564/MAX8564A

双路和三路

LDO

控制器采

用源极跟随结构,可通过控制外部n沟道

MOSFET

的栅极

电压实现灵活、廉价的电压变换。

MAX8563/MAX8564/

MAX8564A

由多个相同的

LDO

控制器组成。每个

LDO

控

制器都有一个使能输入端(

EN_

)和一个“电源就绪”输出

(

POK_)。MAX8563/MAX8564/MAX8564A

还内含一个

0.5V

电压基准、一个内部稳压器和一个欠压锁定 (

UVLO

)

电路。

MAX8563/MAX8564/MAX8564A

内部的跨导放大

器可检测

FB_

上的反馈电压,并将该反馈电压同连接在正

输入端的内部

0.5V

基准电压相比较,如果

FB_

上的反馈电

压低于

0.5V

,则栅极驱动输出端

DRV_

上的电流将会增

加;如果

FB_

上的反馈电压高于

0.5V

,则栅极驱动输出端

DRV_

上的电流将会减小。

偏置电压

(

V

DD

)

、

UVLO

和软启动

MAX8563/MAX8564/MAX8564A

内部电路的偏置电流是由

V

DD

提供的。

V

DD

的范围是

4.5V至13.2V

。如果

V

DD

降至

低于

3.76V

(典型值),那么

MAX8563/MAX8564/MAX8564A

会认为电源电压和基准电压都太低并启动

UVLO

电路。在

欠压锁定期间,内部稳压器(VL)和内部带隙基准均被强制

关闭,

DRV_

被拉至

GND,POK_

也被拉低。

激活内部启动电路之前,

V

DD

必须高于

UVLO

门限电压。

当

UVLO

电路指示

V

DD

电压已足够高时,内部VL稳压

器、内部带隙基准和偏置电路被激活。如果内部电压基

准和偏置电路被激活之后

EN_

为逻辑高电平,那么相应

的

DRV_

输出端开始软启动过程。一旦

FB_

上的电压达到

调整门限的

94%后,LDO

控制器允许满载输出电流。

当某一路

LDO

被激活后,典型的DRV软启动电流将相应

的

DRV_

电位从

GND

拉高。软启动电流限制了输出电压的

摆率,同时还降低了上电初始外部

n-MOSFET

漏极吸收的

电流毛刺。补偿电容

(CC)

的大小限制了摆率(见图3),该

摆率等于(DRV_软启动电流

/C

C

)

mV/ms

,其中的

C

C

以

µF

为单位。启动期间的最大漏极电流等于

C

OUT

和

C

C

的比值

乘以软启动电流。

输入电压(外部

n-MOSFET

的漏极电压

)

n-MOSFET

漏极上输入电压的最小值是所期望输出电压和

n-MOSFET

上压差的函数。该电压值的计算方法见

功率

MOSFET

选择

部分。

n-MOSFET

漏极上输入电压的最大值取决于击穿电压及器

件工作期间的散热条件。

MOSFET

的漏源击穿电压在其

数据资料中给出。理论上输入电压的最大值是输出电压

和击穿电压之和。在考虑最大输入电压时,热限制往往

成为最主要的制约因素。关于这方面计算的细节参见

功

率

MOSFET

选择

部分。

MOSFET

封装和电路板的散热能

力是耗散

n-MOSFET

热量的关键。由于输出电压通常是设

定的,并且最大输出电流也是固定值,因此最大输入电

压就受限于

n-MOSFET

的功率容量(如果该电压低于击穿

电压的话,实际情况通常如此)。同时应确保输入电容能

承受最大输入电压。

如果以

V

DD

和

EN_

先于

n-MOSFET

漏极输入的顺序上电,

MAX8563/MAX8564/MAX8564A

会驱动

DRV_

为高,但

输出电压并不升高。随着

DRV_

上升而

V

FB_

仍然低于调

整点的

80%,MAX8563/MAX8564/MAX8564A

会认为出

现了短路故障并关断稳压器。为了避免这种错误状态,

可在

V

DD

和

IN_

间连接一个电阻分压器,并将该分压器的

中点与相应的

EN_

端连接(见图4)。分压电阻阻值的计算

公式如下:

当

V

IN_

关闭或处于低压状态时:

当

V

IN_

开启或处于高压状态时:

图

3.

软启动和补偿原理

V

IN_

Q1

OUT1

C

OUT

07.

13.

C

C

⎛

R

E

>

⎜

+

RR

⎝

ED

⎛

R

E

<

⎜

+

RR

⎝

ED

R

C

⎞

×

()

⎟

⎠

⎞

×

()

⎟

⎠

VV V

DD IN IN

VV V

DD IN IN

MAX8563

MAX8564

DRV_

MAX8564A

+−

__

+−

__

Page 10

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

10 ______________________________________________________________________________________

取

RD= 100kΩ

。以上等式同时假定

V

IN_

导通且处于高电

压状态时

VDD>V

IN_

>1V

,并且

VDD>3V

。

例如:在EN与

V

DD

之间接一个

100kΩ

的电阻,在

EN_

与

IN_

之间接一个

4kΩ

的电阻。这样,当

VDD= 12V,V

IN_

=

0V

时,

V

EN_

= 0.46V

。当

VDD= 12V,V

IN_

= 1.2V

时,

V

EN_

= 1.6V

。

作为另外一种选择,为避免由于

V

IN

相对于

V

DD

的滞后引

起错误关断,可用一个独立的控制逻辑拉低

EN_

,直到

V

IN

达到稳态值时,该控制逻辑再将其拉高。

输出电压

当

V

DD

为

12V

时,n沟道

MOSFET

的源极输出电压范围为

0.5V至3.3V

,当

V

DD

为5V时,其输出电压范围为

0.5V

至

1.8V

。最大输出电压值是

MOSFET

栅源最小电压(

V

GS

) 与

V

DD

的函数。

外部n沟道

MOSFET

源极与漏极之间有一个寄生二极管。

如果输出电压有可能高于输入电压,会有电流从源极流

入漏极。如果不希望出现这种情况,就需要有外部保

护。比较简单的方法就是在

IN_

端和n沟道

MOSFET

的漏

极之间串联一个二极管,来确保无反向电流。由于二极

管有正向压降,因此降低了最大输出电压,而且二极管

还要消耗额外的能量。

使能和

POK

MAX8563/MAX8564/MAX8564A

具有独立的使能控制输

入端 (

EN1、EN2和EN3

)。拉高

EN1

,第1路输出工作;

拉高

EN2

,第2路输出工作;拉高

EN3

,第3路输出工

作。拉低

EN_

时,相应的

DRV_

被拉低至

GND,POK_

也

被内部拉低。

POK_

是一个漏极开路输出,可提供输出电压的状态指

示,根据电路的状态被拉低。在启动期间,一旦

FB_

的电

压达到

POK_

的阈值时,

POK_

信号将变为高电平。

POK_

阈值有

30mV

的滞回。当输出电压下降幅度超过稳

压额定值的

12%

时,

POK_

拉低。在

UVLO

被激活或内置

的VL稳压器和基准电压源还没有稳定时,所有

POK_

输

出为低电平。

输出欠压和过载保护

在出现过载或短路时,最容易损坏的器件就是外部的n沟

道

MOSFET。MAX8563/MAX8564/MAX8564A

通过监测

输出电压来保护

MOSFET。当DRV_

电压处于最大值而输

出电压降到标称电压值的

80%

以下(仍在

60%

以上),且持

续时间大于

50µs时,MAX8563/MAX8564/MAX8564A

就

会把

DRV_

拉至

GND

,关断这个稳压器输出。需要注意

的是,在关断

MOSFET

时,存在一个固有延迟。这个延

迟时间与补偿电容、

MOSFET

有关。如果在

50µs

内输出

电压又恢复到标称电压的

80%

以上,就不将其视为过

载,也不采取任何保护措施。当输出电压降到额定电压

的

60%

以下时,

MAX8563/MAX8564/MAX8564A

立即将

DRV_

拉至

GND

,关断这个稳压器输出。要想重新启动该

LDO

,必须将

V

DD

拉低到

UVLO

门限以下并重新加载,

或拉低相应的

EN_

后再重新加载。过载保护功能如

典型

工作特性

所示。

____________________________

设计过程

输出电压设置

MAX8563/MAX8564/MAX8564A

每个控制器的最小输出电

压的典型值均为

0.5V

。当

VDD= 12V

时,最大输出电压可

调节至

3.3V

,当

VDD= 5V

时,则可调节至最高

1.8V

。将

FB_

引脚接到

OUT_与GND

之间的分压器的中点(图5),来

设定输出电压值的大小。对于1A最大输出电流,电阻分压

器的电流至少应为

1mA

。也就是说,对于3A的最大输出

电流,则应将电阻分压器的偏流设为

≥ 3mA

。

图

4. EN_

上的分压器

MAX8563

MAX8564

MAX8564A

R

D

EN_

R

E

V

DD

IN_

I

OUT MIN

()

V

R

B

FB

≤=× =1000

I

() () ()

OUT MIN

I

OUT MAX

≥

()

1000

V

FB

II

OUT MAX OUT MAX

500

Page 11

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

______________________________________________________________________________________ 11

若要将输出电压设定为

0.5V

,可将

R

B

从

FB_

端断开,并

将其接至

OUT_

端。这种改变能够保证输出端的最小负载

要求。在本例中,

R

A

可在

1kΩ与10kΩ

之间取值。

输入和输出电容选择

输入滤波电容可以向稳压器提供较低的输入阻抗,也可

在瞬态响应期间降低输入电源的峰值电流。

IN_

端 (外部

n

沟道

MOSFET

漏极)与

GND

之间的输入电容的最小值为

2.2µF

,可采用陶瓷电容(参见图1和图2)。如果预计的输

入电压瞬变或负载瞬变更大的话,就要增加输入电容以

最大限度地减小输出电压的变化。

输出滤波电容及其等效串联电阻(

ESR

)有助于稳压器的稳

定(参见

稳定补偿

部分),并对负载瞬态响应有影响。如果

存在较大的阶跃负载 (从无负载到满负载),并要求极快的

响应(响应时间要小于几个微秒),此时要用一个

100µF

,

18mΩ的POSCAP

输出电容。若想采用更大的电容,注意

要保持电容与

ESR乘积(C

OUTxRESR

)在1µs至5µs

范围内。

如果应用中预计的负载阶跃较小(小于满量程负载的

50%)

,则每安培最大输出电流可采用一个

6.8µF

或更大

的陶瓷输出电容。这样将减小稳压电路的尺寸,降低成

本。需要注意的是,某些陶瓷电容随温度会有较大的变

化。采用

X7R或X5R

系列电容以确保在所有工作温度下

都具有足够的容量。不推荐选用钽电容和铝电容。

功率

MOSFET

选择

MAX8563/MAX8564/MAX8564A

选用n沟道的

MOSFET

作为调整管,而不是采用p沟道的

MOSFET

,这样可以降

低成本。所选用的

MOSFET

的栅极阈值电压必须满足以

下要求:

V

GS_MAX

≤ VDD- V

OUT_

其中,

V

DD

是控制器的偏置电压,

V

GS_MAX

是提供导通

电阻(

R

DS_ON

)所需的最大栅极电压,在器件制造商的数据

资料中有规定。

R

DS_ON

与最大输出电流(负载电流)相乘就

是

MOSFET

两端的最大电压差

V

DS_MIN

。要确保

V

DS_MIN

满足以下条件,以免其进入电压跌落状态 。电压跌落状态

下,输出电压开始下降,并且输入中的所有纹波都会直通

到输出:

V

IN_MIN

> VDS_

MIN

+ V

OUT

其中,

V

IN_MIN

是

MOSFET

漏极的最小输入电压,

V

DS_MIN

的温度系数为正,因此,要使用在最高工作结温

时的

V

DS_MIN

值。

考虑到散热问题,

MOSFET

的最大功耗的计算公式如下:

PD= (V

IN_MAX

- V

OUT

) x I

OUT_MAX

MOSFET

通常采用

SMT

封装,参考

MOSFET

的器件数

据资料中所规定的满足最大工作结温时对于

PCB

面积的

要求。

稳定补偿

电阻

R

C

和电容

C

C

串联后一端接

DRV_

引脚,另一端接

地。这个补偿网络的取值大小是由外部

MOSFET

的电气

特性、输出电流的范围以及所设定输出电压的大小来决

定的。下列这些参数均可从

MOSFET

的数据资料上获

得:输入电容(在

VDS=1V时的C

ISS

的值) 、典型前向跨

导(

g

FS

)以及规定

g

FS

时的电流(

I

DFS

)。在最大负载电流下

(

I

OUT_MAX

)计算

FET

跨导:

图

5.

可调节的输出电压

⎡

⎛

V

RR

=×

AB

OUT

⎢

⎜

V

⎝

⎢

FB

⎣

⎤

⎞

−−12 1

⎟

⎠

RV

=××

⎥

⎥

⎦

()

B OUT

MAX8563

MAX8564

MAX8564A

FB_

OUT_

R

A

R

B

gg

C MAX FS

=×

()

I

OUT MAX

_

I

DFS

Page 12

MAX8563/MAX8564/MAX8564A

为了能在较大阶跃负载应用中获得最佳的瞬态响应(参见

输入和输出电容选择

部分所描述的对输出电容的要求),

可采用如下公式来选择补偿元件:

其中

C

OUT

是输出电容,

R

ESR

是

C

OUT

输出电容的

ESR

。

若要选用低成本的陶瓷电容(参见

输入和输出电容选择

部

分对负载瞬态响应特性的描述),可采用如下公式来选择

补偿元件:

举例

本例基于图1的

OUTPUT 1。表1

为计算补偿所需要的参数。

这些数值都来自于图1和相应器件的数据资料。

PCB

布局准则

大多数应用都要求大电流和严格的输出精度,因此,要求

仔细的

PCB

布局。利用该器件的评估板(

MAX8563EVKIT

)

可以加快设计的进程。

要确保所有布线都尽可能短,这对增大大电流线径以降

低寄生电感的影响非常重要。由于存在大电流,

MOSFET

可能会产生大量的热量,特别是当输入电压和输出电压

之间的压差较大时。为了把

MOSFET

产生的热量散发出

去,可使功率连线非常宽,并且有足够的敷铜面积。当

采用表面贴封装的器件时,若想达到较好的散热效果,

最有效的方法就是在

MOSFET

的正下方,在多个层面上

敷铜,并将这些敷铜通过过孔连接。采用一个地平面可

将阻抗和电感减至最小。除了和大功率有关的一般注意

事项外,这里还特别强调四点,来保证高精度的输出:

•

确保到

C

OUT_

的反馈连接短且直。

•

反馈电阻要紧挨着FB引脚放置。

•R

C

和

C

C

要紧挨着

DRV_

引脚放置。

•

保证

FB_和DRV_

布线远离噪声源,以确保高精度。

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

12 ______________________________________________________________________________________

表

1.

计算补偿所需的参数

选用

1µF

电容。

选用

620Ω

电容。

VC

.

×× ×

016

C

C

R

=×

C

⎡

⎢

ggR

⎢

⎣

()

59

OUT OUT

××+

() ()

C MAX C MAX ESR

gVI

C MAX OUT OUT MAX

Cxg V I

()

×+

() _

VxCg xR

OUT OUT C MAX ESR

()

C C MAX OUT OUT

()

×+

() _

()

⎤

⎥

1

⎥

⎦

−

2

=

C

ISS

+

MAXMAX

1

Cxg

C

C

gxVI

()

C MAX OUT OUT MAX

OUT C MAX

() _

Rx

=−15

C

()

+

C

OUT

Cxg

C C MAX

()

C

=

ISS

PARAMETER CONDITIONS VALUE UNITS

MOSFET C

MOSFET GFS IDFS = 8.8A 30 S

V

OUT1

I

OUT_MAX

C

OUT1

R

ESR

VDS = 1V 2500 pF

ISS

Figure 1 1.5 V

Figure 1 1.5 A

Figure 1 100 µF

Figure 1 18 mΩ

A

.

gSx

Cx

.

=

016

59

RRx

=

C

==

C MAXC()

1 5 100 12 4

1 5 100 12 4 18 1

. , .

30

Vx Fx Sx

. .

12 4 1 5 1 5

()

pF F use F

2500 0 90 1

Vx Fx Sx m

. .

1 124 15 15

µ

FSxV A

()

=

599 4 620

15

.

88

µ

Sx V A

. . .

µµ

=

., .

µ

()

. . .

ΩΩ

use

A

+

12 4

+

⎛

⎜

⎝

.

12 4

18 1

S

Sx

.

m

Ω

2

Ω

⎞

⎟

+

⎠

−

+

Page 13

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

______________________________________________________________________________________ 13

_____________________________________________________________________

引脚配置

_____________________________

芯片信息

TRANSISTOR COUNT: 1801

PROCESS: BiCMOS

TOP VIEW

DRV1

FB1

EN1

POK1

GND

N.C.

DRV3

FB3

1

2

3

MAX8563

4

5

6

7

8

QSOP

V

16

DD

15

DRV2

14

FB2

13

EN2

12

POK2

N.C.

11

10

POK3

9

EN3

DRV1

FB1

EN1

1

2

3

4

5

MAX8564

MAX8564A

µMAX

10

V

DD

DRV2

9

FB2

8

EN2POK1

7

POK2GND

6

Page 14

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

14 ______________________________________________________________________________________

_____________________________________________________________________________

封装信息

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外形信息,请查询 www.maxim-ic.com.cn/packages。)

QSOP.EPS

PACKAGE OUTLINE, QSOP .150", .025" LEAD PITCH

21-0055

F

1

1

Page 15

MAX8563/MAX8564/MAX8564A

±1%

、超低输出电压、

双路和三路线性

n-FET

控制器

___________________________________________________________________________

封装信息(续)

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外形信息,请查询 www.maxim-ic.com.cn/packages。)

Maxim北京办事处

北京 8328信箱 邮政编码 100083

免费电话:800 810 0310

电话:010-6211 5199

传真:010-6211 5299

Maxim不对 Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600 ___________________15

© 2006 Maxim Integrated Products

是

Maxim Integrated Products, Inc.

的注册商标。

____________________________

修订历史

Rev 2

中的修改页:1、12、14、15。

0.6±0.1

e

10

Ø0.50±0.1

1

0.6±0.1

TOP VIEW

D2

A2

4X S

H

A

GAGE PLANE

BOTTOM VIEW

10

1

E2

INCHES

DIM

MIN

-A

0.002

A1

A2 0.030 0.037 0.75 0.95

0.116

D1

0.114

D2

0.116

E1

0.114

E2

0.187

H

0.0157

L

L1

0.037 REF

0.007

b

e

0.0197 BSC

0.0035

c

0.0196 REF

S

α

0° 0° 6°

c

MAX

0.043

0.006

0.120

0.118

0.120

0.118

0.199

0.0275

0.0106

0.0078

6°

MILLIMETERS

MIN

-

0.05

2.95

2.89

2.95

2.89

4.75

0.40

0.940 REF

0.177

0.500 BSC

0.090

0.498 REF

MAX

1.10

0.15

3.05

3.00

3.05

3.00

5.05

0.70

0.270

0.200

10LUMAX.EPS

b

D1

FRONT VIEW

A1

α

E1

SIDE VIEW

L

L1

PROPRIETARY INFORMATION

TITLE:

PACKAGE OUTLINE, 10L uMAX/uSOP

21-0061

REV.DOCUMENT CONTROL NO.APPROVAL

1

1

Loading...

Loading...