Page 1

19-3173; Rev 2; 9/04

భᄋຶৰۇ

భᄋຶৰۇ

专为台式机、笔记本和图形卡提供的

DDQ

0.7V

概述

的同步

V

TTR

的输出,

的连

1.5A

内存

DDR

的

________________________________

MAX8550/MAX8551

buck PWM

收能力的

10mA

道

MOSFET

控制器、一个用于产生

LDO

基准输出缓冲器。

,可从2V至

输出电流可高达

续电流及3A峰值电流。

均能跟踪

REFIN

非常适合于台式机、笔记本电脑及图形卡中的

集成了一个用于产生

V

V

的具有供出及吸

TT

线性稳压器以及一个用于产生

控制器驱动两个外部N沟

Buck

的输入产生最低

28V

15A。LDO

电压。这些特性使得

可吸收或供出高达

输出及

LDO

10mA

MAX8550/MAX8551

基准缓冲输出

应用。

MAX8550/MAX8551

TM

Quick-PWM

架构,具有高达

中的

PWM

控制器采用

600kHz

的可编程开关频率。

Maxim

专有的

这种控制方案易于处理宽范围的输入/输出电压比,并具

有

定的开关频率。

的负载瞬变响应,同时还能保持高效率及相对恒

100ns

MAX8550

提供完全可编程的

UVP/OVP

及

跳跃模式选项,非常适合于便携式设备应用。跳跃模式

在较轻负载下可提供高效率。

MAX8551

的目标应用为台

式机及图形卡,不具有跳脉冲功能。

VTT及VTTR

输出能够以1%的精度跟踪

V

REFIN

/2。LDO

调节器的高带宽可提供优异的瞬态响应,无需使用大容

量电容,因此可减少尺寸及成本。

Buck

视低边

控制器与

MOSFET

稳压器具有独立的电流限制。通过监

LDO

的漏-源压降,实现了

Buck

调节器的可

调节、无损耗、折返式电流限制。此外,器件还内置有

过/欠压保护机制。一旦过流故障排除,调节器即可重新

进入软启动,这有利于减少短路时的功耗。通过

SHDNA、SHDNB及STBY

输入,

MAX8550/MAX8551

允

许灵活的排序及待机功率管理。

MAX8550及MAX8551

脚薄型

QFN

封装。

均备有细小的

5mm x 5mm、28

________________________________

DDR I及DDR II

存储器电源

引

应用

台式计算机

笔记本电脑及台式笔记本电脑

图形卡

游戏控制台

RAID

网络

集成式

DDR

电源方案

____________________________________________

控制器

Buck

♦ 100ns

♦

♦ 2V至28V

♦ 1.8V/2.5V

♦

♦

♦ 1.7ms

♦过/

♦ Power-Good

LDO

♦

♦ VTT

♦ VTT与VTTR

♦

♦ 1.0V至2.8V

♦ Power-Good

____________________________

MAX8550ETI -40°C to +85°C 28 5mm × 5mm TQFN

MAX8550ETI+ -40°C to +85°C 28 5mm × 5mm TQFN

MAX8551ETI -40°C to +85°C 28 5mm × 5mm TQFN

表示无铅封装。

+

____________________________

负载阶跃响应的

高达

95%

的效率

Quick-PWM

输入电压范围

最高

固定或

600kHz

0.7V至5.5V

的可选开关频率

可调输出

折返式可编程电流限制

数字软启动及独立的关断控制

欠压保护选项

窗口比较器

单元

完全集成的

具有

±3A

VTT及VTTR

的供出/吸收能力

输出跟踪

功能

V

REFIN

/ 2

全陶瓷输出电容设计

输入电压范围

窗口比较器

PART TEMP RANGE PIN-PACKAGE

TOP VIEW

TON

OVP/UVP

(N.C. FOR

MAX8551)

REF

ILIM

POK1

POK2

STBY

1

2

3

4

5

6

7

DD

AV

SKIP

26

MAX8550

MAX8551

10

VTTR

AX8551)

(TP1 FOR

M

25

11

PGND2

GND

24

12

VTT

SHDNB

SHDNA

28

27

8

9

SS

VTTS

5mm x 5mm Thin QFN

PGND1

23

13

VTTI

DD

V

22

14

REFIN

定购信息

引脚配置

DL

21

20

BST

19

LX

18

DH

17

V

IN

16

OUT

FB

15

特性

MAX8550/MAX8551

________________________________________________________________ Maxim Integrated Products 1

本文是

正式英文资料的译文,

Maxim

不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

Maxim

翻译错误,如需确认任何词语的准确性,请参考

索取免费样品和最新版的数据资料,请访问

Maxim

Maxim

典型工作电路见本数据手册末尾。

Quick-PWM是Maxim Integrated Products, Inc.

提供的英文版资料。

的主页:

www.maxim-ic.com.cn

的商标。

。

Page 2

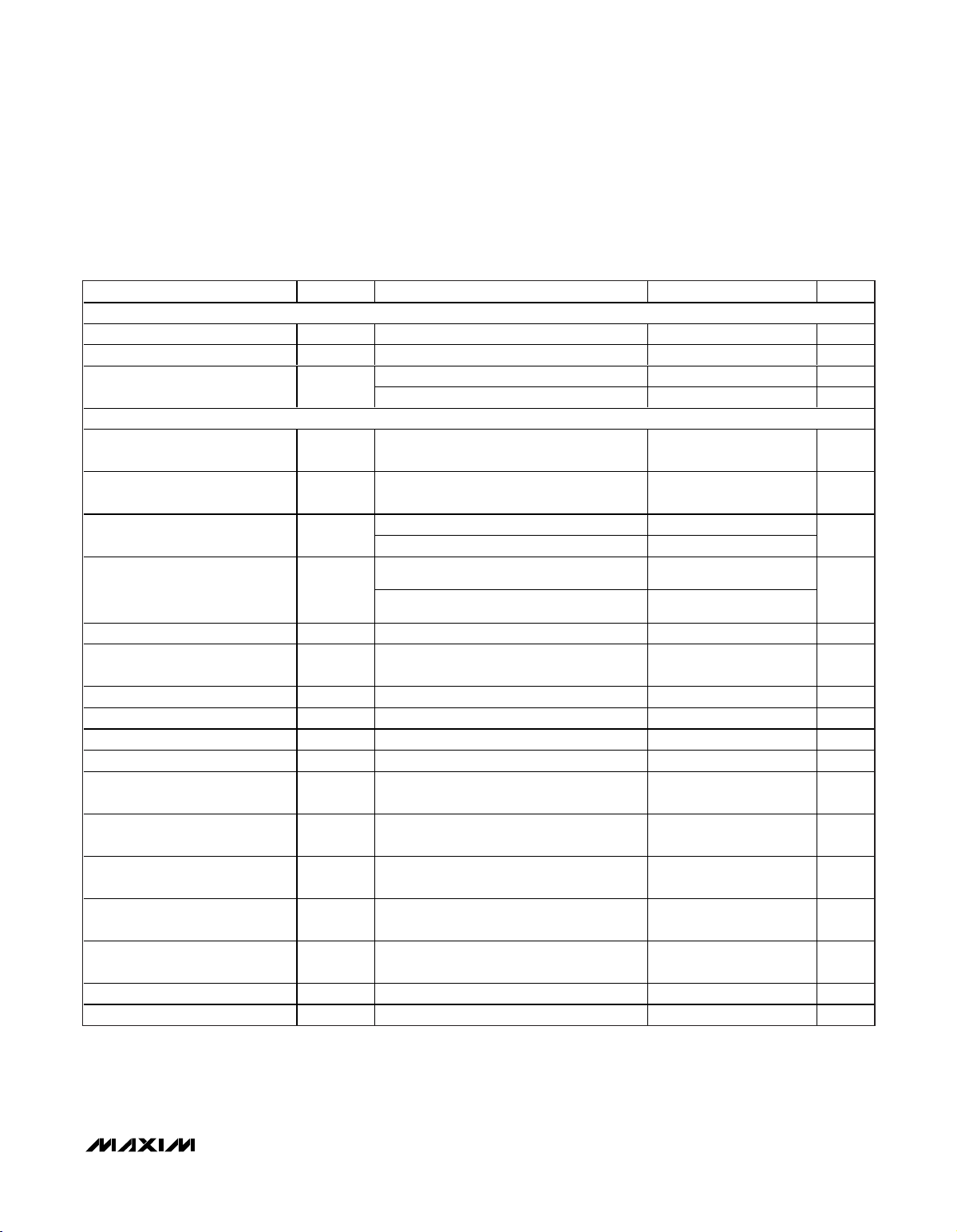

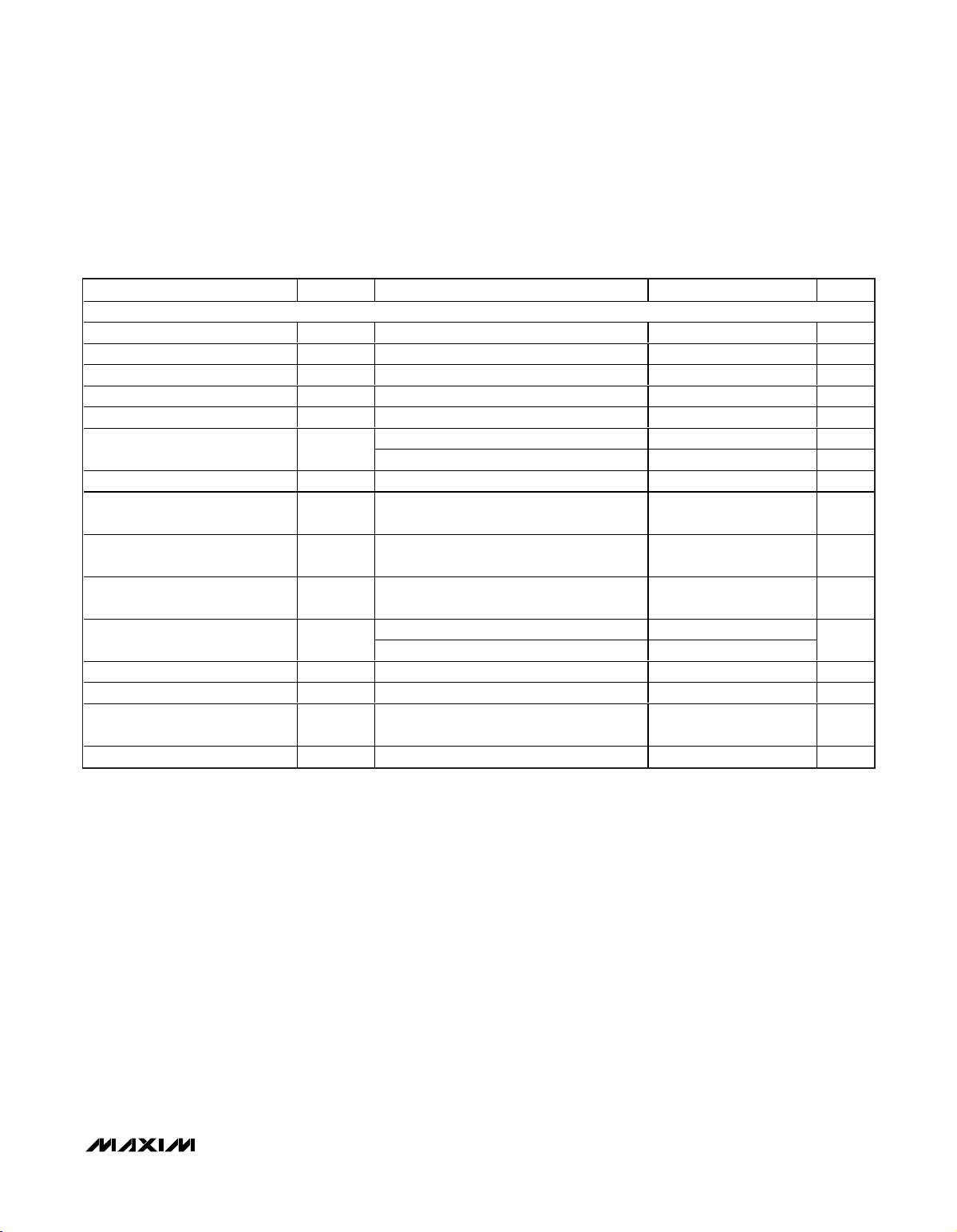

PARAMETER

CONDITIONS

MAIN PWM CONTROLLER

V

IN

228

Input Voltage Range

4.5 5.5

V

Output Adjust Range V

OUT

0.7 5.5 V

FB = OUT

0.7

FB = GND

2.5

Output Voltage Accuracy

(Note 2)

FB = V

DD

1.8

V

Soft-Start Ramp Time t

SS

Rising edge of SHDNA to full current limit 1.7 ms

TON = GND (600kHz)

219

TON = REF (450kHz)

273

389

On-Time t

ON

VIN = 15V,

V

OUT

= 1.5V

(Note 3)

571

ns

Minimum Off-Time

(Note 3)

450 ns

VIN Quiescent Supply Current I

IN

25 40 µA

VIN Shutdown Supply Current SHDNA = SHDNB = GND 1 5 µA

All on (PWM, VTT, and VTTR on) 2.5 5

SHDNA = GND (only VTT and VTTR on) 2 4

STBY = AVDD (only VTTR and PWM on) 1 2

AVDD Quiescent Supply Current I

AVDD

SHDNB = GND (only PWM on) 0.5 1

mA

AVDD + VDD Shutdown Supply

Current

SHDNA = SHDNB = GND 2 10 µA

Rising edge of V

IN

4.1

4.4 V

AVDD Undervoltage-Lockout

Threshold

Hysteresis 50 mV

VDD Quiescent Supply Current I

VDD

Set VFB = 0.8V 1 5 µA

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

ABSOLUTE MAXIMUM RATINGS

VINto GND .............................................................-0.3V to +30V

V

DD, AVDD

SHDNA, SHDNB, REFIN to GND..............................-0.3V to +6V

SS, POK1, POK2, SKIP, ILIM, FB to GND ................-0.3V to +6V

STBY, TON, REF, UVP/OVP to GND ........-0.3V to (AV

OUT, VTTR to GND ..................................-0.3V to (AV

DL to PGND1..............................................-0.3V to (V

DH to LX....................................................-0.3V to (V

LX to BST..................................................................-6V to +0.3V

LX to GND .................................................................-2V to +30V

VTT to GND...............................................-0.3V to (V

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

, VTTI to GND .........................................-0.3V to +6V

+ 0.3V)

DD

+ 0.3V)

DD

+ 0.3V)

DD

+ 0.3V)

BST

+ 0.3V)

VTTI

VTTS to GND............................................-0.3V to (AV

PGND1, PGND2 to GND .......................................-0.3V to +0.3V

REF Short Circuit to GND ...........................................Continuous

Continuous Power Dissipation (T

28-Pin 5mm x 5mm TQFN (derate 35.7mW/°C

above +70°C).................................................................2.86W

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +165°C

Lead Temperature (soldering, 10s) .................................+300°C

= +70°C)

A

DD

MAX8550/MAX8551

ELECTRICAL CHARACTERISTICS

(VIN= +15V, VDD= AVDD= V

= GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V

are at T

= +25°C.) (Note 1)

A

SHDNA

= V

SHDNB

SYMBOL

= V

BST

= V

ILIM

VTTS

= 5V, V

= V

VTT

= V

OUT

, TA= -40°C to +85°C, unless otherwise noted. Typical values

REFIN

= V

= 2.5V, UVP/OVP = STBY = FB = SKIP

VTTI

MIN TYP MAX UNITS

+ 0.3V)

VDD, AV

2 _______________________________________________________________________________________

t

OFF_MIN

DD

0.693

2.47

1.78

TON = OPEN (300kHz) 316 352

TON = AVDD (200kHz) 461 516

170 194

213 243

200 300

4.25

0.707

2.53

1.82

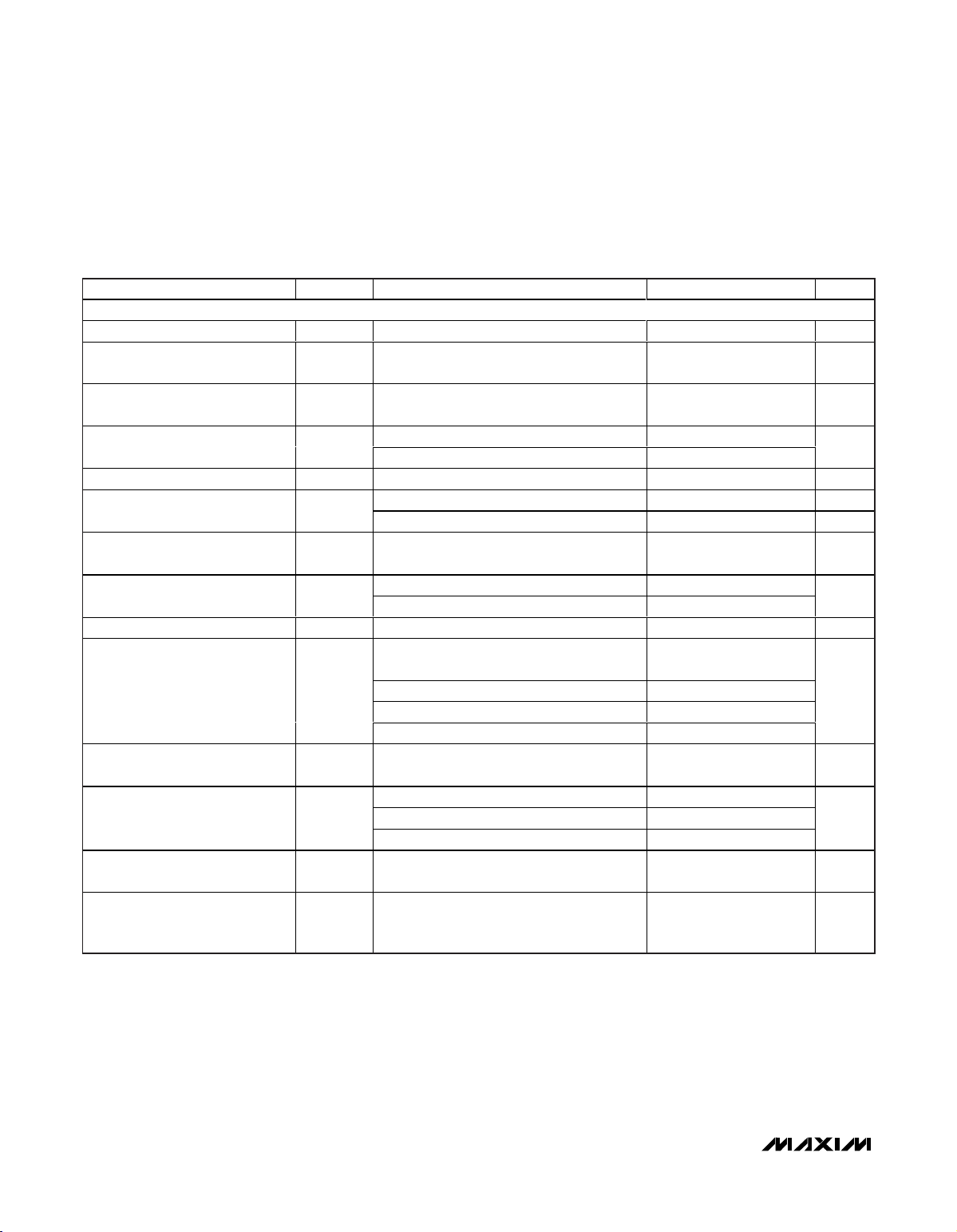

Page 3

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

ELECTRICAL CHARACTERISTICS (continued)

(VIN= +15V, VDD= AVDD= V

= GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V

are at T

REFERENCE

Reference Voltage V

Reference Load Regulation I

REF Undervoltage Lockout

FAULT DETECTION

OVP Trip Threshold

(Referred to Nominal V

UVP Trip Threshold

(Referred to Nominal V

POK1 Trip Threshold

(Referred to Nominal V

POK2 Trip Threshold

(Referred to Nominal V

and V

UVP Blanking Time From rising edge of SHDNA 10 20 40 ms

OVP, UVP, POK_ Propagation

Delay

POK_ Output Low Voltage I

POK_ Leakage Current V

ILIM Adjustment Range V

ILIM Input Leakage Current 0.1 µA

Current-Limit Threshold (Fixed)

PGND1 to LX

Current-Limit Threshold

(Adjustable) PGND1 to LX

Current-Limit Threshold (Negative

Direction) PGND1 to LX

Current-Limit Threshold (Negative

Direction) PGND1 to LX

Zero-Crossing Detection

Threshold PGND1 to LX

Thermal-Shutdown Threshold +160 °C

Thermal-Shutdown Hysteresis 15 °C

= +25°C.) (Note 1)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

)

OUT

)

OUT

)

OUT

VTTS

VTTR

)

SHDNA

= V

SHDNB

REF

ILIM

= V

= V

BST

AVDD = 4.5V to 5.5V; I

= 0 to 50µA 0.01 V

REF

V

rising 1.93 V

REF

Hysteresis 300 mV

UVP/OVP = AVDD (Note 4) 112 116 120 %

Lower level, falling edge, 1% hysteresis 87 90 93

Upper level, rising edge, 1% hysteresis 107 110 113

Lower level, falling edge, 1% hysteresis 87.5 90 92.5

Upper level, rising edge, 1% hysteresis 107.5 110 112.5

OVP not applicable in MAX8551 10 µs

= 4mA 0.3 V

SINK

= 5.5V, VFB = 0.8V, V

POK_

= 2V 170 200 235 mV

V

ILIM

SKIP = AV

SKIP = AV

= 5V, V

ILIM

= V

VTTS

VTT

(Note 4) -75 -60 -45 mV

DD

, V

DD

ILIM

= V

OUT

, TA= -40°C to +85°C, unless otherwise noted. Typical values

= 0 1.98 2 2.02 V

REF

= 2V (Note 4) -250 mV

= V

REFIN

= 1.3V 1 µA

VTTS

= 2.5V, UVP/OVP = STBY = FB = SKIP

VTTI

65 70 75 %

0.25 2.00 V

45 50 55 mV

3mV

MAX8550/MAX8551

%

%

_______________________________________________________________________________________ 3

Page 4

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

ELECTRICAL CHARACTERISTICS (continued)

(VIN= +15V, VDD= AVDD= V

= GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V

are at T

MOSFET DRIVERS

DH Gate-Driver On-Resistance V

DL Gate-Driver On-Resistance in

High State

DL Gate-Driver On-Resistance in

Low State

Dead Time (Additional to

Adaptive Delay)

INPUTS AND OUTPUTS

MAX8550/MAX8551

Logic Input Threshold

(SHDN_, STBY, SKIP (Note 4))

Logic Input Current

(SHDN_, STBY, SKIP (Note 4))

Dual-Mode™ Input Logic

Levels (FB)

Input Bias Current (FB) -0.1 +0.1 µA

Four-Level Input Logic Levels

(TON, OVP/UVP (Note 4))

Logic Input Current

(TON, OVP/UVP (Note 4))

OUT Discharge-Mode

On-Resistance

DL Turn-On Level During

Discharge Mode

(Measured at OUT)

Dual Mode is a trademark of Maxim Integrated Products, Inc.

= +25°C.) (Note 1)

A

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SHDNA

= V

SHDNB

= V

= V

BST

- VLX = 5V 1 4 Ω

BST

DH falling to DL rising 30

DL falling to DH rising 30

Rising edge 1.20 1.7 2.20 V

Hysteresis 225 mV

Low (2.5V output) 0.05

High (1.8V output) 2.1

High

Floating 3.15 3.85

REF 1.65 2.35

Low 0.5

FB = GND 90 175 350

FB = AV

FB adjustable mode 400 800 1600

(Note 4) 10 25 Ω

(Note 4) 0.3 V

ILIM

VTTS

DD

= 5V, V

= V

VTT

= V

OUT

, TA= -40°C to +85°C, unless otherwise noted. Typical values

REFIN

= V

= 2.5V, UVP/OVP = STBY = FB = SKIP

VTTI

14Ω

0.5 3 Ω

-1 +1 µA

AV

-

DD

0.4

-3 +3 µA

70 135 270OUT Input Resistance

ns

V

V

kΩ

4 _______________________________________________________________________________________

Page 5

专为台式机、笔记本和图形卡提供的

PARAMETER

CONDITIONS

UNITS

LINEAR REGULATORS (VTTR AND VTT)

VTTI Input Voltage Range V

VTTI

1 2.8 V

VTTI Supply Current I

VTTI

I

VTT

= I

VTTR

= 0

1mA

VTTI Shutdown Current SHDNA = SHDNB = GND 10 µA

REFIN Input Impedance V

REFIN

= 2.5V 12 20 30 kΩ

REFIN Range V

REFIN

1

V

V

REFIN

rising 0.7 0.9 V

REFIN Lockout Threshold

Hysteresis 75 mV

Soft-Start Charge Current I

SS

VSS = 0 4 µA

VTT Internal MOSFET High-Side

On-Resistance

I

VTT

= -100mA, V

VTTI

= 1.5V,

AV

DD

= 4.5V

0.3 Ω

VTT Internal MOSFET Low-Side

On-Resistance

I

VTT

= 100mA, AVDD = 4.5V 0.3 Ω

VTT Output Accuracy

(Referred to V

REFIN

/ 2)

V

REFIN

= 1.5V or 2.5V, I

VTT

= 1mA -1 +1 %

V

REFIN

= 2.5V, I

VTT

= 0 to ±1.5A 1

VTT Load Regulation

V

REFIN

= 1.5V, I

VTT

= 0 to ±1A 1

%

VTT Current Limit VTT = 0 or VTTI ±3 ±5

A

VTTS Input Current I

VTTS

V

VTTS

= 1.5V, VTT open

1µA

VTTR Output Error

(Referred to V

REFIN

/ 2)

V

REFIN

= 1.5V or 2.5V, I

VTTR

= 0 -1 +1 %

VTTR Current Limit V

VTTR

= 0 or V

VTTI

mA

ELECTRICAL CHARACTERISTICS (continued)

(VIN= +15V, VDD= AVDD= V

= GND, PGND1 = PGND2 = LX = GND, TON = OPEN, V

are at T

= +25°C.) (Note 1)

A

SHDNA

= V

SHDNB

SYMBOL

= V

BST

= V

ILIM

VTTS

= 5V, V

= V

VTT

集成式

= V

OUT

, TA= -40°C to +85°C, unless otherwise noted. Typical values

REFIN

= V

VTTI

DDR

= 2.5V, UVP/OVP = STBY = FB = SKIP

MIN TYP MAX

电源方案

<0.1

2.8

MAX8550/MAX8551

0.1

Note 1: Specifications to -40°C are guaranteed by design, not production tested.

Note 2: When the inductor is in continuous conduction, the output voltage has a DC regulation level higher than the error-compara-

tor threshold by 50% of the ripple. In discontinuous conduction, the output voltage has a DC regulation level higher than the

Note 3: On-time and off-time specifications are measured from 50% point to 50% point at the DH pin with LX = GND, V

Note 4: Not applicable to the MAX8551.

trip level by approximately 1.5% due to slope compensation.

and a 250pF capacitor connected from DH to LX. Actual in-circuit times may differ due to MOSFET switching speeds.

_______________________________________________________________________________________ 5

±23 ±40 ±60

±6.5

BST

= 5V,

Page 6

专为台式机、笔记本和图形卡提供的

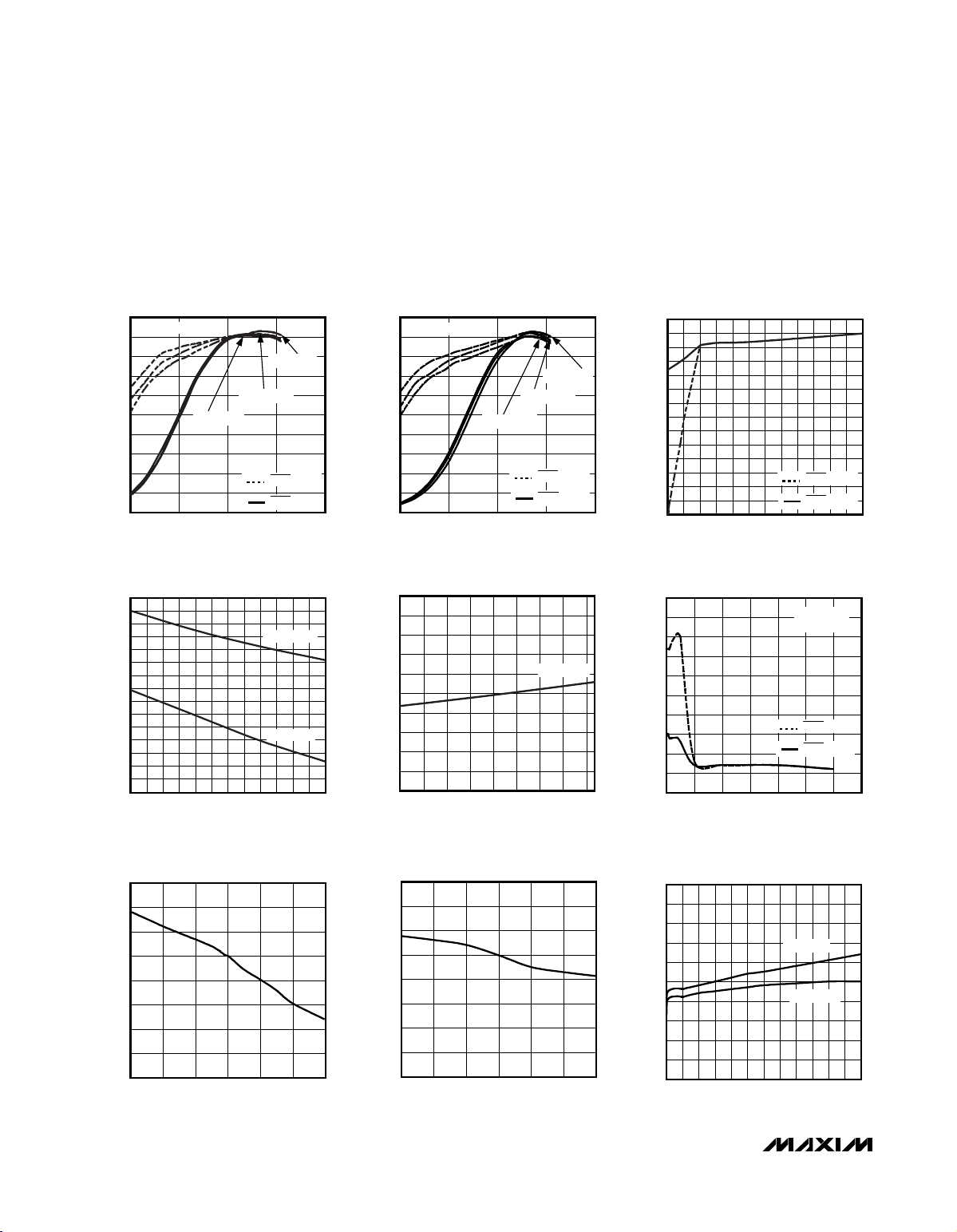

EFFICIENCY vs. LOAD CURRENT

(TON = GND)

MAX8550/51 toc01

I

LOAD

(A)

EFFICIENCY (%)

1010.1

60

70

80

90

100

50

10

20

30

40

0

0.01 100

fSW = 600kHz

V

OUT

= 2.5V

V

OUT

= 1.8V

V

OUT

= 1.5V

SKIP = GND

SKIP = AV

DD

EFFICIENCY vs. LOAD CURRENT

(TON = OPEN)

MAX8550/51 toc02

I

LOAD

(A)

EFFICIENCY (%)

1010.1

10

20

30

40

50

60

70

80

90

100

0

0.01 100

fSW = 300kHz

V

OUT

= 2.5V

V

OUT

= 1.8V

V

OUT

= 1.5V

SKIP = GND

SKIP = AV

DD

SWITCHING FREQUENCY vs. LOAD CURRENT

(TON = GND)

MAX8550/51 toc03

I

LOAD

(A)

FREQUENCY (kHz)

11108 92 3 4 5 6 71

50

100

150

200

250

300

350

400

450

500

550

600

650

700

0

012

SKIP = GND

SKIP = AV

DD

SWITCHING FREQUENCY vs. INPUT VOLTAGE

(TON = GND)

MAX8550/51 toc04

VIN (V)

FREQUENCY (kHz)

262420 228 10 12 14 16 186

420

440

460

480

500

540

520

560

580

600

620

640

660

680

700

400

428

I

LOAD

= 12A

I

LOAD

= 0A

SWITCHING FREQUENCY vs. TEMPERATURE

(TON = GND)

MAX8550/51 toc05

TEMPERATURE (°C)

FREQUENCY (kHz)

80655035205-10-25

650

660

670

680

690

700

600

640

630

620

610

-40

I

LOAD

= 12A

OUTPUT VOLTAGE

vs. LOAD CURRENT

MAX8550/51 toc06

I

LOAD

(A)

V

OUT

(V)

12106 842

2.495

2.500

2.505

2.510

2.515

2.520

2.525

2.530

2.535

2.540

2.490

014

VIN = 15V,

TON = GND

SKIP = GND

SKIP = AV

DD

VTT VOLTAGE

vs. VTT CURRENT

MAX8550/51 toc07

I

VTT

(A)

V

VTT

(V)

21-2 -1 0

1.21

1.22

1.23

1.24

1.25

1.26

1.27

1.28

1.20

-3 3

VTTR VOLTAGE

vs. VTTR CURRENT

MAX8550/51 toc08

I

VTTR

(mA)

V

VTTR

(V)

105-10 -5 0

1.21

1.22

1.23

1.24

1.25

1.26

1.27

1.28

1.20

-15 15

LINE REGULATION

(V

OUT

vs. VIN)

MAX8550/51 toc09

VIN (V)

V

OUT

(

V

)

262420 228 10 12 14 16 186

2.46

2.47

2.48

2.49

2.50

2.51

2.52

2.53

2.54

2.55

2.45

428

I

LOAD

= 0A

I

LOAD

= 12A

集成式

DDR

电源方案

_______________________________________________________________

(V

VIN

= 12V, V

= 2.5V, TON = GND, SKIP = AVDD, circuit of Figure 8, TA= +25°C, unless otherwise noted.)

OUT

MAX8550/MAX8551

典型工作特性

6 _______________________________________________________________________________________

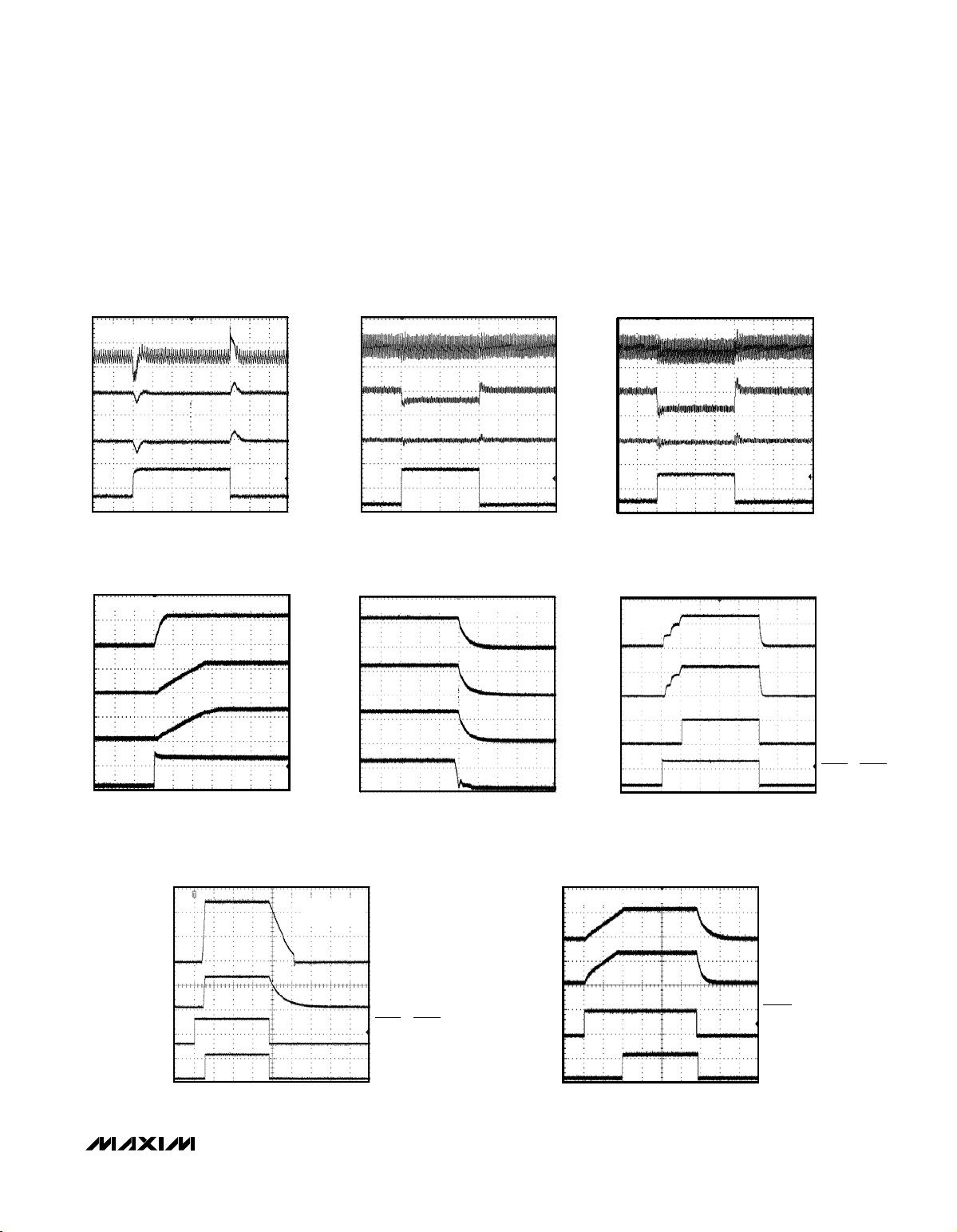

Page 7

专为台式机、笔记本和图形卡提供的

V

DDQ

STARTUP AND SHUTDOWN INTO

LIGHT LOAD, DISCHARGE ENABLED

MAX8550/51 toc16

2ms/div

V

OUT

1V/div

VTT

1V/div

SHDNA + SHDNB

5V/div

POK1

5V/div

0V

0V

0V

0V

R

LOAD

= 10Ω,

R

VTT

= 20Ω

VTT, VTTR STARTUP AND SHUTDOWN

MAX8550/51 toc17

200µs/div

VTT

1V/div

VTTR

1V/div

SHDNB

5V/div

POK2

5V/div

0V

0V

0V

0V

I

VTT

= 1.5A, I

VTTR

= 15mA

集成式

____________________________________________________________

(V

12A

0.1A

= 12V, V

VIN

LOAD TRANSIENT (BUCK)

I

= 1.5A, I

VTT

POWER-UP WAVEFORMS

VDD = 5V, I

LOAD

0V

0V

0V

0V

= 2.5V, TON = GND, SKIP = AVDD, circuit of Figure 8, TA= +25°C, unless otherwise noted.)

OUT

VTTR

= 12A, I

= 15mA

20µs/div

VTT

200µs/div

= 1.5A, I

MAX8550/51 toc10

MAX8550/51 toc13

= 15mA

VTTR

V

OUT

100mV/div

VTT

100mV/div

VTTR

100mV/div

I

LOAD

10A/div

OUT

1V/div

VTT

2V/div

VTTR

1V/div

V

IN

10V/div

LOAD TRANSIENT VTT (-1.5A TO +1.5A)

I

= 12A, I

LOAD

0A

VTTR

= 15mA

40µs/div

POWER-DOWN WAVEFORMS

VDD = 5V, I

0V

0V

0V

0V

LOAD

= 12A, I

200µs/div

VTT

= 1.5A, I

MAX8550/51 toc11

MAX8550/51 toc14

VTTR

= 15mA

V

OUT

50mV/div

VTT

50mV/div

VTTR

50mV/div

I

VTT

2A/div

OUT

1V/div

VTT

2V/div

VTTR

1V/div

V

IN

10V/div

LOAD TRANSIENT VTT (-3A TO +3A)

I

LOAD

0A

V

DDQ

HEAVY LOAD, DISCHARGE DISABLED

I

LOAD

= 1.5A

I

VTT

0V

0V

0V

0V

= 12A, I

STARTUP AND SHUTDOWN INTO

= 12A,

DDR

电源方案

典型工作特性(续

VTTR

= 15mA

40µs/div

1ms/div

MAX8550/51 toc12

MAX8550/51 toc15

)

V

OUT

50mV/div

VTT

50mV/div

VTTR

50mV/div

I

VTT

5A/div

V

OUT

2V/div

VTT

1V/div

POK1

5V/div

SHDNA + SHDNB

5V/div

MAX8550/MAX8551

_______________________________________________________________________________________ 7

Page 8

专为台式机、笔记本和图形卡提供的

SHORT CIRCUIT AND

RECOVERY OF V

DDQ

MAX8550/51 toc19

400µs/div

V

OUT

2V/div

I

LOAD

10A/div

V

IN

10V/div

I

IN

2A/div

0A

0V

0A

0V

UVP DISABLED, FOLDBACK CURRENT LIMIT

SHORT CIRCUIT AND

RECOVERY OF V

DDQ

MAX8550/51 toc20

400µs/div

V

OUT

2V/div

I

LOAD

10A/div

V

IN

10V/div

I

IN

2A/div

0A

0V

0A

0V

UVP ENABLED

SHORT CIRCUIT OF VTT

MAX8550/51 toc21

400µs/div

VTT

1V/div

I

VTT

5A/div

0A

0V

集成式

DDR

电源方案

____________________________________________________________

(V

VIN

MAX8550/MAX8551

= 12V, V

= 2.5V, TON = GND, SKIP = AVDD, circuit of Figure 8, TA= +25°C, unless otherwise noted.)

OUT

OVERVOLTAGE AND TURN-OFF

OF BUCK OUTPUT

0A

0V

0V

0V

20µs/div

MAX8550/51 toc18

I

L

25A/div

V

OUT

2V/div

DH

20V/div

DL

5V/div

典型工作特性(续

)

8 _______________________________________________________________________________________

Page 9

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

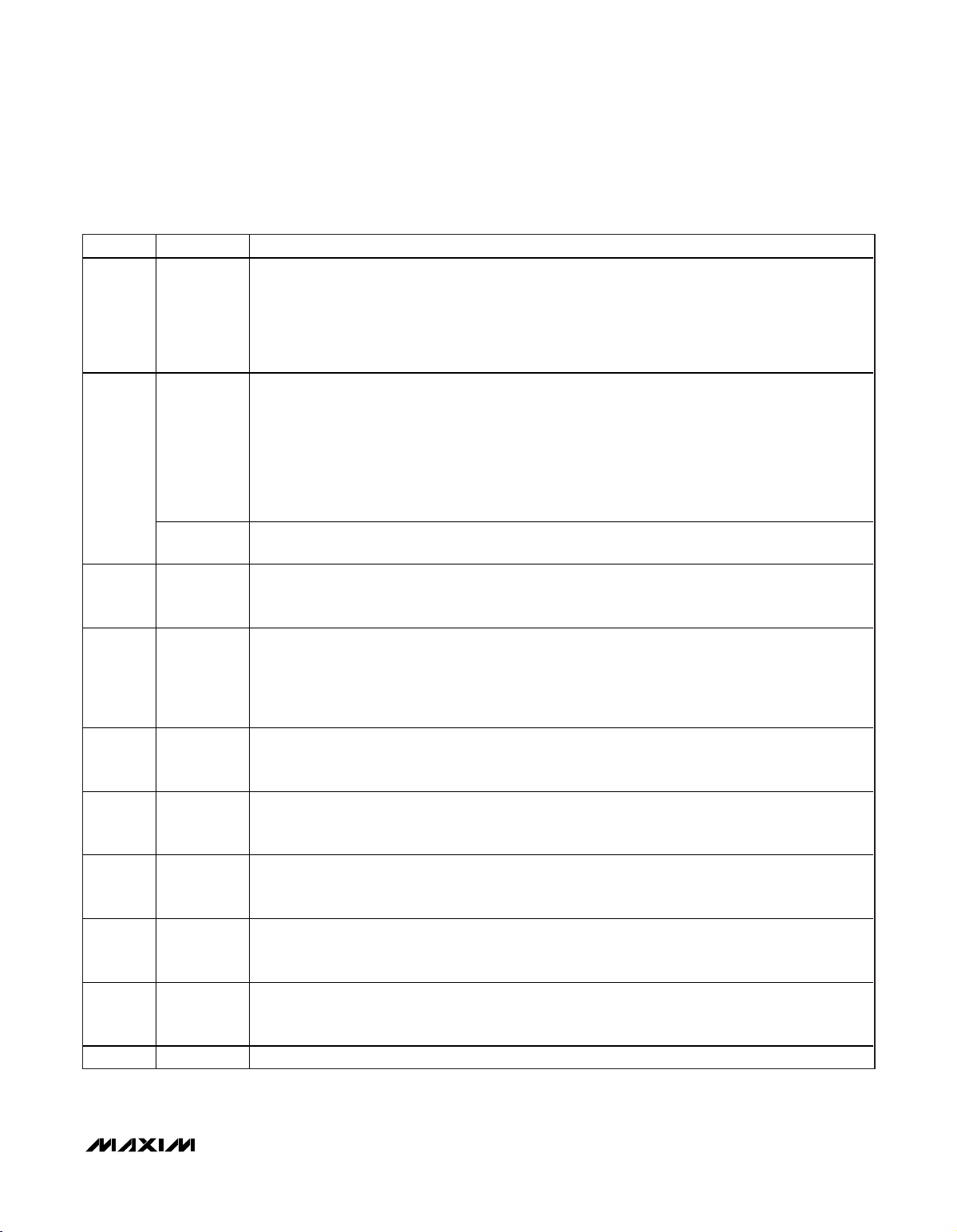

___________________________________________________________________

引脚

1TON

2

3REF

名称

OVP/

UVP

(MAX8550)

N.C.

(MAX8551)

导通时间选择控制输入。这个四电平逻辑输入设置额定DH导通时间。连接至

接

来选择以下额定开关频率:

TON

TON = AV

TON = OPEN (300kHz)

TON = REF (450kHz)

TON = GND (600kHz)

过/欠压保护控制输入。这个四电平逻辑输入启用或禁用过压和/或欠压保护。过压极限为额定输出电压的

。欠压极限为额定输出电压的

116%

脚可启用所需功能:

OVP/UVP = AV

OVP/UVP = OPEN (启用OVP

OVP/UVP = REF (禁用OVP

OVP/UVP = GND (禁用OVP

不连接,保持开路

+2.0V

置

ILIM

(200kHz)

DD

(启用OVP

DD

*

基准电压输出。用一个

电压。当

SHDNA、SHDNB及STBY

。启用

70%

及放电模式,启用

及放电模式,禁用

及放电模式,启用

及放电模式,禁用

0.1µF (最小)

功能

OVP

UVP)

UVP)

UVP)

UVP)

电容旁路至

为低时,

的同时启用放电模式。将

GND。REF

REF

可为外部负载提供

关断。

GND、REF、AV

OVP/UVP

引脚连接至以下引

电流。可用来设

50µA

引脚说明

或不连

DD

MAX8550/MAX8551

4 ILIM

5POK1

6POK2

7STBY

8SS

9 VTTS

10 VTTR

* MAX8551

不具有

OVP

用于调整

一个电阻分压器,通常从

0.25V至2V

Buck Power-Good

低。当输出达到稳定且软启动过程结束时,

LDO Power-Good

2) 10%时,POK2

POK2

待机。连接至高电位时进入低静态模式,

效。在此模式下,

VTT与VTTR

使SS开路可禁用软启动。当

终端电源输出检测引脚。一般与

分压器连接可将

终端参考电压。

或放电模式,仅具有

调节器的谷值限流阀值。

buck

电压范围。连接

漏极开路输出。当

漏极开路输出。在正常模式下,当

为低。

为低。在待机模式下,

POK2仅从VTTR

软启动控制。从SS至地连接一个电容

调整至比

VTT

VTTR跟踪V

功能。

UVP

REF至GND

ILIM至AV

SHDNB

VTT

REFIN

/ 2

REFIN

PGND与LX

,可将限流阀值设置在

可选择

DD

输出电压高于或低于正常调整点

buck

POK2

VTT

上引入输入。

为低时SS放电至地。参见

引脚连接来精确调整至

一半的电压更高的电压。

。

两端的限流阀值为

默认限流阀值。参见

50mV

为高阻抗。关断时

POK1

VTTR或VTTS

只响应

VTTR

输出被禁用,但如果

输出根据

PWM

典型应用电路

(

上电压的

ILIM

25mV至200mV

高于或低于正常调整点(通常为

输入。关断以及当

SHDNB

SHDNA

中的C9,参见

、

POR

电压的一半。与从

REFIN

之间。这对应于

设置电流限

、或当软启动时,

10%

为低。

POK1

V

REFIN

为高,则

的状态可为开通或关断。

软启动电容选择

及软启动

UVLO

倍。连接

0.1

ILIM

部分。

低于

0.8V

缓冲器保持有

VTTR

部分。

VTT至GND

ILIM

上的

POK1

REFIN /

时,

部分)。

的电阻

至

为

_______________________________________________________________________________________ 9

Page 10

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

________________________________________________________________

引脚

11 PGND2

12 VTT

13 VTTI

14 REFIN

15 FB

MAX8550/MAX8551

16 OUT

17 V

18 DH

19 LX

名称

IN

VTT及VTTR

终端电源输出。连接

VTT及VTTR

外部参考输入。用来将

输出反馈输入。连接至

Buck

出

(0.7V至5.5V)

输出电压检测连接。连接至

典型应用电路

(

启用放电模式时,输出电容通过

UVP

输入电压检测连接。连接至输入电源。

之间。

高边栅极驱动器输出。在LX与

外部电感连接。LX与电感输入侧连接。LX同时用于电流限制及DH驱动器电源的回线。

功率地。

VTT至VTTS

的电源输入。对于

,则在FB与输出之间连接一个电阻分压器。FB调整为

中的

Q1)

从外部与底部的裸露垫片连接。

PGND2

来调整至

应用,一般与

DDR

VTT及VTTR

buck

的开通时间。在固定输出模式,

输出调整为

得到

AV

+1.8V

DD

输出滤波电容的正端。

OUT与GND

V

IN

之间摆动。当关断或处于

BST

功能

V

REFIN

只用来设置

。

/ 2

调节器的输出连接。

buck

。

/ 2

V

REFIN

的固定输出,连接至

OUT

OUT

之间的一个内部

PWM

GND得到+2.5V

+0.7V

通过检测输出电压来确定高边开关

也充当

的开通单稳态定时器。IN电压介于2V至

UVLO时,DH

输出的反馈输入。当通过

buck

电阻放电。

10Ω

引脚说明(续

固定输出。对于可调输

。

为低。

)

MOSFET

OVP/

28V

20 BST

21 DL

22 V

23 PGND1

24 GND

25

26 AV

27 SHDNA

28 SHDNB

DD

SKIP

(MAX8550)

TP1

(MAX8551)

DD

自举浮动电容连接。可按照

部分。

容选择

同步整流栅极驱动器输出。在

栅极驱动电源输入。与

DL

控制器功率地。

Buck

Buck及LDO

跳脉冲控制输入。连接至

MAX8551

Buck及LDO

的陶瓷电容旁路至

关断控制输入A。用来控制

正常工作时连接至

关断控制输入B。用来控制

模拟地。

特有,此引脚为测试引脚,必须与

模拟电源输入。通过一个

GND

AV

PGND1

GND

DD

+4.5V 至+5.5V

从外部与底部的裸露垫片连接。

AV

。

buck

。

VTT及VTTR

典型应用电路

PGND与V

从外部与底部的裸露垫片连接。

选择低噪声强制

DD

10Ω

输出。

连接至一个外部电容及二极管。参见

(图8)

之间摆动。

DD

的系统电源连接。用一个

模式。连接至

PWM

GND (引脚24)

串连电阻与

SHDNA

输出。关断时

+4.5V至+5.5V

的上升沿清除过/欠压保护故障锁存器(参见表2及表3)。

VTT及VTTR

连接。

自举电源二极管及电

1µF (最小)

GND

的系统电源连接。用一个

均为高阻抗(见表2)。

陶瓷电容旁路至

选择跳脉冲模式。

PGND1

或更大

1µF

。

10 ______________________________________________________________________________________

Page 11

专为台式机、笔记本和图形卡提供的

图

功能框图

1.

OVP/UVP

(N.C. IN MAX8551)

SHDNA

SHDNB

POK1

POK2

*POWER-DOWN

FORCES POK2 LOW

AND VTT, VTTR TO

HIGH IMPEDANCE.

TON

STBY

FB

BUCK ON/OFF

SHUTDOWN

DECODER

VTT ON/OFF VTTR ON/OFF

N

REFIN

N

REFIN

BIAS ON/OFF

INTREF + 10%

/

2 - 10%

/

2 - 10%

TRIG

QUAD LEVEL

DECODE

0.7 x INTREF

IN

ON-TIME

COMPUTE

ONE-SHOT

1.16 x INTREF

REFIN

REFIN

t

ON

INTREF - 10%

/

2 + 10%

/

2 + 10%

OVP/UVP

LATCH

OUT

Q

20ms

TIMER

INTREF

POWER-DOWN*

CURRENT

LIMITS

SS

+0.4V

V

= 2.5V

OUT

VTT ILIM

VTTR ILIM

S

R

V

Q

OUT

DECODE

LX

= 1.8V

FB

ONE-SHOT

S

R

Q

t

OFF

1.0V

TRIG

Q

ZERO CROSSING

INTREF

VTTI

PGND2

集成式

MAX8550/

MAX8551

DISCHARGE

LOGIC

2V

REFERENCE

10kΩ 10kΩ

REFIN

/

2

V

DD

V

DD

DDR

- 1V

V

DD

LX

N

N

N

电源方案

BST

DH

LX

V

DD

DL

PGND

ILIM

SKIP

(TP1 IN MAX8551

MUST BE CONNECTED TO GND)

OUT

AV

DD

GND

REF

VTTS

REFIN

VTTI

VTT

PGND2

VTTR

MAX8550/MAX8551

______________________________________________________________________________________ 11

Page 12

专为台式机、笔记本和图形卡提供的

集成式

DDR

____________________________

MAX8550/MAX8551

线性稳压器以及

两个外部N沟道

最低至

线性稳压器可吸收或供出高达

值电流,同时还具有较快的瞬态响应。这些特性使得

恒导通时间

开关频率。这种控制方案易于处理很宽的输入/输出电压

比,并能提供

保持高效率和相对恒定的开关频率。

MAX8550/MAX8551

制。

现无损折返式电流限制。

果选择了过压保护,当输出电压超过设定值的

将锁定低边同步

如果选择欠压保护,在过流状态下,当输出电压低于规

定输出的

态。这有助于降低短路时的功耗。

二者均没有过压或欠压保护。当这两路输出的电流到达

限定值时,输出将从稳压变成稳流,电流被稳定于限

定值。

除输入电压

部的

率,并省下了一个

为

运行,则可用一个外部的线性稳压器,例如

产生这个

源,则可将

的其余部分供电。

供应IC和

如下:

0.7V

MAX8550/MAX8551

MAX8550/MAX8551

控制器、

Buck

Buck

和基准缓冲器的电流限分别为

LDO

+5V

电路及栅极驱动器供电)。如果要求其能够独立

PWM

为

V

buck

DD

10mA

MOSFET

的输出,并提供高达

Quick-PWM

100ns

LDO

调节器通过监视低边

FET

时,它就会锁定

70%

(VIN)外,MAX8550/MAX8551

偏置电源。将偏置电源放在IC外部可以改善效

电源。如果输入为固定的

+5V

、

V

DD

调节器的

MOSFET

电源方案

详细说明

结合了同步

基准输出缓冲器。

成为

中的

架构,可达到最高

的“瞬时导通”负载瞬态响应,同时

及基准输出缓冲器具有独立的限流控

为开通状态,高边

线性稳压器的成本(这个电源用来

+5V

及IN连接在一起。

AV

DD

MOSFET

和

AV

DD

栅极驱动器所需电流。最大电流估算

buck PWM

,可从

+2V至+28V

12A

的连续电流及3A的峰

1.5A

存储器应用的理想选择。

DDR

调节器采用

buck

上的漏-源电压降实

FET

输入用来调整电流限。如

ILIM

MOSFET

偏置电源

+5V

驱动器供电,

电源的输出电流必须能够

V

DD

控制器、

控制器驱动

Buck

的输入产生

的负载电流。

Maxim

600kHz

116%

为关断状态。

FET

驱动器为关断状

±5A和±40mA

和

(V

DD

还需要一个外

MAX1615

+4.5V至+5.5V

AV

DD

LDO

LDO

专有的

的固定

时,

AVDD)

电

则为

IC

IIIfQQ

=+ +×+

BIAS VDD AVDD

其中

Q

G1

下的总栅极电荷,

5V

及

I

VDD

+ I

为

Q

G2

AVDD

典型应用电路

为流入

f

SW

V

DD

中

是开关频率。

()

GG

SW

及

MOSFET Q1及Q2在V

12

的静态电源电流,

AV

DD

自由运行的恒导通时间

Quick-PWM

恒导通时间、电流模式的调节器(图1)。这种架构利用输

出滤波电容的

压提供了

导通时间仅由一个单稳态来决定,其脉宽与输入电压成

反比而与输出电压成正比。而另一个单稳态则设置

的最小关断时间(典型值)。导通单稳态的触发条件为:

误差比较器为低;低边开关电流低于谷电流阀值;且最

小关断时间已过。

控制架构是一种带电压前馈的伪固定频率、

来作为检流电阻,因此,输出纹波电

ESR

斜坡信号。控制算法很简单:高边开关的

PWM

导通时间单稳态

控制器的核心部分是一个单稳态触发器,它设定了

PWM

高边开关的导通时间。这个快速、低抖动、可调节的单

稳态电路能够根据输入、输出电压的变化改变导通时间。

高边开关的导通时间与输入电压

,

压成正比:

VI R

tK

ON

其中

1),R

导通电阻。这钟算法能产生近乎恒定的开关频率,尽管

没有固定频率的时钟发生器。恒定开关频率的好处有

两点:

,

1)

2)

开关周期)可通过

K (

DS(ON)Q2

可通过选择频率,避开噪声敏感频段(如

频段)。

电感纹波电流工作点保持相对恒定,简化了设计,并

易于对输出电压纹波进行预测。

()

=×

是

典型应用电路

+×

OUT LOAD DS ON Q

输入引脚的连接来选择(表

TON

成反比而与输出电

(VIN)

()

V

IN

中同步整流器Q2的

(图8)

2

455kHz

=

GS

PWM

300ns

(TON)

中频

12 ______________________________________________________________________________________

Page 13

专为台式机、笔记本和图形卡提供的

导通单稳态在

上有良好的精度(在

在

200kHz与300kHz

Electrical Characteristics

Electrical Characteristics

600kHz及450kHz

上约为

±10%)

表格中的规定,导通时间可能会

在一个更宽的范围内变化。例如,当频率设定为

表格规定的工作点

频率上约为

±12.5%

。如果工作条件远离

600kHz

,

时,如果输入比5V大得多,由于所需导通时间很短,实

际的运行频率要低将近

10%

。

恒导通时间仅确定了一个大致恒定的开关频率。

Electrical Characteristics

性损耗及高边

电感、两个

路

PCB

MOSFET

MOSFET

走线中的电阻等)随负载增加趋向于使开关频率升

表格中所保证的导通时间还受阻

开关延时的影响。阻性损耗(包括

、输出电容的

、输出和地线回

ESR

高。死时间效应增加了等效的导通时间,由于等效导通

时间中增加了一个或两个死时间,因而使开关频率降低。

只有在

PWM

模式下

(SKIP = VDD)

,在输出电压动态转变

期间,当电感电流在轻载或负的负载电流下发生反转时,

才会发生死时间效应。电感电流反转时,电感的感生电

动势使LX比正常情况下更早地变高,使开通时间延长了

一个DH前沿死时间。对于临界传导点以上的负载,不发

生死时间效应,实际开关频率为:

VV

+

OUT DROP

=

tV V

()

ON IN DROP

+

其中

V

DROP1

f

SW

为电感放电路径中的寄生压降之和——包括

同步整流器、电感及任何PC板中的电阻等;

充电路径中的电阻压降之和——包括高边开关

电路

中的

的开通时间(参见

、电感以及PC板电阻等;

Q1)

开通单稳态

(TON)

1

2

t

ON

部分)。

V

则为

DROP2

典型应用

(

为单稳态确定

自动跳脉冲模式

(SKIP = GND)

在跳跃模式

的自动切换(图2)。这种切换受一个比较器的影响,

PFM

(SKIP = GND)

中,在轻负载情况下将发生至

这个比较器在电感电流过零时关断低边开关。过零比较

器在同步整流

MOSFET (图8

检测电感电流。当

对于默认的

(

50mV

V

PGND

电流门限,此值为

典型应用电路

低于电流门限5%以下后

- V

LX

中的

2.5mV)

上差分

Q2)

,比较器将

集成式

拉低(图1)。这种方式使跳脉冲的

DL

工作模式之间的分界点,正好与连续及非连续电感

PWM

DDR

电源方案

与非跳脉冲的

PFM

电流工作方式之间的分界点(亦称为临界传导点)相重合。

PFM/PWM

切换点的负载电流——

I

LOAD(SKIP)

,等于峰-

峰纹波电流的一半,它是电感量的函数(图2)。此门限相

对恒定,只受输入电压

I

LOAD SKIP

=

()

其中K为导通时间比例因子(见表1)。例如,在图

应用电路

1µH

中

(K = 1.7µs、V

),跳脉冲转换发生在:

⎛

25 17

. .

VsHV

×

⎜

21

×

⎝

µ

的轻微影响:

(VIN)

VK

⎛

OUT IN OUT

⎜

⎝

2

OUT

⎞

12 2

µ

⎛

⎜

⎟

⎝

⎠

⎛

×

VV

⎞

⎟

⎜

⎠

⎝

L

= 2.5V、VIN= 12V及L =

- .5V

⎞

=

⎟

12

⎠

V

V

IN

168

.

⎞

⎟

⎠

典型

8

A

如果使用回转(软饱和)电感,则切换点发生在更低的值

上。当轻负载引起跳脉冲工作时,开关波形可能会表现

出更大的噪声且不同步,但这是一种常用的工作状态,

因为它在轻负载下具有高效率。

表

近似K因子误差

1.

TON SETTING

200

(TON = AV

(TON = OPEN)

(TON = REF)

(TON = GND)

DD

300

450

600

TYPICAL

FACTOR

(µs)

5.0 ±10 3.15

)

3.3 ±10 3.47

2.2 ±12.5 4.13

1.7 ±12.5 5.61

K-

K-FACTOR

ERROR

(%)

MINIMUM V

V

OUT

(h = 1.5, SEE THE

DROPOUT

PERFORMANCE

SECTION)

IN

= 2.5V

AT

MAX8550/MAX8551

______________________________________________________________________________________ 13

Page 14

专为台式机、笔记本和图形卡提供的

集成式

DDR

通过改变电感值,可在

电源方案

噪声及轻负载效率之间取得

PFM

较好的平衡。一般而言,低电感值可产生较宽的效率-

负载曲线,而高电感值则可产生较高的满负载效率(假设

线圈电阻保持固定)以及较低的输出电压纹波。使用高值

电感的代价是更大的物理尺寸及变差的负载瞬态响应,

尤其是在低输入电压时。

直流输出精度指标与误差比较器的门限有关。当电感处

于连续传导模式时,

MAX8550/MAX8551

调整输出纹波

的谷值,因此实际的直流输出电压要比触发电平高出输

出纹波的

I

LOAD(SKIP)

差比较器的门限高大约

MAX8550/MAX8551

低噪声强制

。在非连续模式

50%

,由于有斜率补偿,输出电压的调整点比误

)

1.5%

模式下

PWM

(SKIP = GND

。

强制

PWM

模式

(SKIP = AVDD)

以及

(SKIP = AV

仅限于

MAX8550)

,控制低边开关

I

导通时间的过零比较器被禁止。这迫使低边栅极驱动波

形始终与高边栅极驱动波形互补,因此电感电流在轻负

载时会发生反转,同时DH保持

制

模式的开关频率相当稳定。但以强制

PWM

V

OUT

工作也要付出一定代价,即:由于外部

电荷及开关频率,空载时的

与

20mA

之间。强制

PWM

偏置电流将保持在

V

DD

模式对于减少音频噪声、改善

的占空比。强

/ V

IN

MOSFET

PWM

负载瞬态响应以及提供电流吸收能力(以便输出电压的动

态调节)非常有用。

LOAD

DD

模式

的栅极

2mA

限流特性和最大负载能力与检流电阻、电感值及输入电

压有关。当与欠压保护电路一起使用时,这种限流方式

几乎可在所有环境下有效。

在强制

限制功能,以防

PWM

模式中,

buck

MAX8550/MAX8551

调节器输出在吸收电流时出现过量

的反向电感电流。反向限流阀值被设置为正电流限的

120%

用接在

,并在

ILIM

被调整时跟踪正电流限。限流阀值可

V

ILIM

引脚上的外部电阻分压器来进行调整。为保

证精度及足够的抗噪声干扰能力,建议分压器电流设定

在

<

2µA至20µA

限流阀值调整范围为

流阀值电压(从

ILIM与AV

,

50mV

默认值的逻辑门限大约为

之间。

25mV至200mV

PGND1至LX)等于ILIM

连接时,门限电压默认值为

DD

AVDD- 1V

。在可调模式下,限

上电压的

50mV

。

请仔细遵照PC板布局准则,以确保噪声及直流误差不会

破坏LX与

之间的差分检流信号。

GND

VIN - V

∆I

∆t

OUT

=

L

还具有负电流

。当

1/10

。切换至

I

PEAK

限制电流的

Buck

调节器

(ILIM)

谷电流限制

MAX8550/MAX8551 buck

种独特的“谷值”电流检测法,这种方法检测LX与

PGND1

电路

两端的压降,利用整流

中的

的导通电阻作为检流元件。如果检流信号幅

Q2)

度在谷电流限阀值以上,则不允许

调节器的电流限制电路采用一

MOSFET (即图8

PWM

典型应用

控制器启动新的

INDUCTOR CURRENT

ON-TIME0 TIME

周期(图4)。采用谷电流控制方式,实际的峰值电流将比

谷电流门限大出一个电感纹波电流的量。因此,精确的

14 ______________________________________________________________________________________

图

跳脉冲/非连续切换点

2.

I

LOAD

= I

/ 2

PEAK

Page 15

专为台式机、笔记本和图形卡提供的

TO PWM

CONTROLLER

(SEE FIGURE 1)

1.0V

LX

图

可调限流阀值

3.

I

PEAK

I

LOAD

INDUCTOR CURRENT

I

LIR

2

(POR)

LIMIT

LOAD

及软启动

:复位

0

图

谷值电流限制门限

4.

当

高于2V时,即启动内部上电复位

AV

DD

TIME

I

LOAD(MAX)

I

LIM(VAL) =

1 - x I

()

POR、UVLO

故障锁存器和软启动计数器;启动基准电路;并为

调节器的工作做好准备。在

前,

AV

欠压锁定

DD

(UVLO)

AV

DD

达到

4.25V (

典型值)以

电路阻止开关动作。锁定状

buck

MAX8550/

MAX8551

集成式

REF

ILIM

- 1V

V

DD

DDR

R

A

R

B

态下,控制器将DH拉低,如果

止

(OVP/UVP = REF或GND

及关断放电功能开启

OVP

则强制DL为高。有关

表3。当

AV

DD

高于

(OVP/UVP = AV

OVP/UVP

时,控制器即启动

4.25V

C

REF

C

ILIM

OVP

),则保持DL为低;如果

电源方案

及关断放电功能被禁

或

OPEN)

及关断设置的细节请参见

DD

buck

调节器

与内部软启动。

调节器的内部软启动在启动时使电流限逐渐增加,

Buck

以减少输入浪涌电流。

MAX8550/MAX8551

的软启动分

为5个阶段:第一阶段,控制器将电流限限制在总电流限

的

上。如果输出未在

20%

动进入第二阶段,电流限再增加

直至

后达到最大电流限,或输出达到额定调整电压,

1.7ms

以先到者为准。增加一个与外部

可为

LDO

容来实现。当

SS

内部电路输出

斜坡电压使

上升,直至SS接近

调节器输出增加连续可调的模拟软启动功能。

buck

部分的软启动可通过在SS引脚与地之间连接一个电

SHDNB

电容被放电。当

4µA

被驱动为低,或当

SHDNB

电流(典型值)对SS电容充电。SS上的

VTT及VTTR

时达到整个电流限。在启动期间

1.6V

内达到稳定,则软启动自

425µs

。此过程一直重复,

20%

电阻相并联的电容,

ILIM

热关断时,

LDO

被驱动为高或过热状态解除后,

两路输出的限流比较器门限线性

降低电流限,可限制启动时的浪涌电流,这在驱动容性

负载时尤其有用。选择合适的SS电容来设置软启动时间

窗口。使SS浮空则关闭软启动功能。

MAX8550/MAX8551

,

______________________________________________________________________________________ 15

Page 16

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

Power-OK (POK1)

是一个窗口比较器的漏极开路输出,这个比较器连

POK1

续监视

软启动期间,

输出电压进入由FB设置的稳定电压的

POK1

以上,

10%

障条件都会将

AV

DD

得到逻辑电平的输出信号,可在

一个外部上拉电阻,一个

用。请注意,

及与

VTTS及VTTR

输出。当

V

OUT

POK1

即变为高阻抗。如果

MAX8550/MAX8551

POK1

电源降低到1V以下,使故障锁存器清除为止。要

POK1

SHDNA

被拉低。当数字软启动终止后,只要

拉低,直到通过触发

窗口比较器与过/欠压保护检测器以

的状态无关。

为低以及在

±10%

从稳定电压下降或升高

V

OUT

即将

POK1

POK1与AV

的电阻即适用于大多数应

100kΩ

调节器的

buck

范围内,

拉低。任何故

SHDNA

之间连接

DD

MAX8550/MAX8551

SHDNA

SHDNA

器部分进入低功率模式(参见

表)。

故障。

当输出放电被启用

及

且

个内部连接到地的

过

被关闭,但参考仍保持有效以提供精确的门限。一旦输

出电压低于

从而可有效地将

输入用于控制

SHDNA

SHDNB

V

OUT

OUT

也用来复位故障信号,例如过压或欠压

(OVP/UVP = AV

被拉低时,或

下降至稳定值的

10Ω

输入)。当输出放电时,DL被拉低且

0.3V,MAX8550

buck

调节器,用于使IC的

buck

Electrical Characteristics

DD

被启用

UVP

以下时,

70%

开关为

输出及LX箝位至地。

(OVP/UVP = AVDD)

调节器的输出放电(通

buck

即关断参考并将DL拉高,

与输出放电

或开路)且

MAX8550

PWM

buck

即通过一

或将

调节

SHDNA

控制器

当输出放电被禁用时

不主动对

况下,

定。

Buck

设定的放电模式。

对于

MAX8551,OVP/UVP

开启输出放电功能(参见表3)。

输出放电,DL驱动器保持为低。在此种情

buck

输出的放电速度由负载电流及其输出电容决

buck

调节器在启动时检测并锁定由

(OVP/UVP = REF或GND

OVP/UVP

在内部被连接至

SHDNB与STBY

SHDNB

IC

Characteristics表)

高阻抗。

STBY

STBY

输入,故即使当

输出亦无效。

对应于

的线性稳压器部分进入低功率模式(参见

是一个高有效输入,用来单独关断

为高时,

VTT及VTTR

。当

为高阻抗。

VTT

SHDNB

输出,当被拉低时,可使

SHDNB

为高时,如果

为低时,

输入可超越

STBY

STBY

VTT及VTTR

Power-OK (POK2)

是一个窗口比较器的漏极开路输出,这个比较器连

POK2

续监视

当

SHDNB

REFIN

V

VTTS

以上时,

10%

逻辑电平输出,可在

拉电阻,一个

输入和

VTTS

为低时,

设置的稳定电压的

或

V

VTTR

VTTR

POK2

从

REFIN

MAX8550/MAX8551将POK2

POK2与AV

的电阻即适用于大多数应用。

100kΩ

输出。当

被拉低。只要输出电压不超出由

±10%

所设定的稳定电压上升或下降

REFIN

范围,

DD

即为高阻抗。当

POK2

之间连接一个外部上

),控制器

引脚所

,永久地

REF

Electrical

输出。当

VTT

SHDNB

为高,则

低于

拉低。要得到

0.8V

VTT

,或

为

表

关断及待机控制逻辑

2.

STBY SHDNA SHDNB BUCK OUTPUT VTT VTTR

GND AV

GND AV

AV

DD

GND GND AV

GND GND GND OFF OFF OFF

16 ______________________________________________________________________________________

AV

DD

DD

DD

AV

DD

GND ON OFF OFF

AV

DD

DD

ON ON ON

ON OFF ON

OFF ON ON

Page 17

专为台式机、笔记本和图形卡提供的

电流限制

为一个线性稳压器,它将输入

VTT

电压的一半。

可吸收及供出至少

VTT及VTTR

任意一路输出到达电流限时,输出将从电压调节变为电

流调节。

的反馈点在

VTT

1.5A

的电流限典型值分别为

(VTT LDO及VTTR

(VTTI)

输入上(图1)。

VTTS

的连续电流以及3A的峰值电流。

±5A与±40mA

调整为

缓冲器

V

REFIN

VTT

。当

)

故障保护

MAX8550/MAX8551的buck

保护功能。选择

用故障保护功能,如表3所示。启用后,控制器连续监视

输出上的欠/过压故障。

当输出电压上升到额定值的

并且

OVP

即置位故障锁存器,关断

低而将DL拉高。同步整流

的

Q2)以100%

输出箝位至地。请注意,迅速将DL锁定为高会使输出电

压略微摆向负压,这是由于在

电路中的能量的缘故。如果负载不能容忍负电压,则可

在输出端接一个功率肖特基二极管来充当反极性箝位。

通过触发

器并重启控制器。当

被禁用(表3)。

OVP

输出不具有过压保护。

OVP/UVP

被使能

SHDNA

(OVP/UVP = AV

的占空比导通,迅速将输出电容放电并将

或降低

OVP

控制器具有过压及欠压故障

引脚的连接方式,可启用或禁

过压保护

以上(仅限于

116%

或开路),

DD

控制器,并立即将DH拉

PWM

MOSFET (图8

发生时储存在输出

OVP

到1V以下可清除故障锁存

AV

DD

OVP/UVP与REF或GND

仅用于

buck

输出。

MAX8550)

典型应用电路

VTT及VTTR

(OVP)

电路

OVP

中

LC

连接时,

,

集成式

DDR

电源方案

欠压保护

当输出电压下降至稳定电压的

,控制器即置位故障锁存器并开始放电模式(参见

UVP

断及输出放电

典型应用电路

器

(

在启动或

被忽略。触发

锁存器并重启控制器。当

接时,

输出不具有欠压保护。

VTTR

MAX8550/MAX8551

来监视IC的

压器

(VTT)

MAX8551的buck

传感器即置位故障锁存器,将

OVP/UVP

结温下降

以下可重启控制器。如果IC的

的芯片温度超过

阻态,当这部分芯片的温度下降

热故障保护电路独立工作,例如,如果

并触发其热故障保护,则

部分)。当输出电压下降至

中的

SHDNA

UVP

15°C

上升沿后的至少

SHDNA

被禁用(表3)。

调节器部分,另一个则用来监视线性稳

buck

与基准缓冲输出

调节器部分的结温超过

设置如何都用放电模式来关断

后,通过触发

+160°C

打开,将

Q2)

或降低

AV

OVP/UVP

UVP

具有两个热故障保护电路。一个用

SHDNA

,则

VTT及VTTR

调节器仍能继续工作。

buck

以下时,如果启用

70%

0.3V

输出箝位至地。

buck

10ms内(

到1V以下可清除故障

DD

保持开路或与

仅用于

buck

(VTTR)

VTT及VTTR

。当

+160°C

拉低,且无论

POK1

buck

或降低

后重新启动。两个

15°C

VTT

(UVP)

关

,同步整流

最小值

输出。

) UVP

GND

VTT

连

及

热故障保护

MAX8550/

时,温度

控制器。在

到

AV

调节器部分

关断,进入高

输出过载,

DD

1V

MAX8550/MAX8551

表

3. OVP/UVP

OVP/UVP DISCHARGE UVP PROTECTION OVP PROTECTION

AV

DD

OPEN

REF

GND

故障保护

Yes.

DL forced high when SHDNA and

SHDNB are low.

Yes.

DL forced high when SHDNA and

SHDNB are low.

No.

DL forced low when SHDNA is low.

No.

DL forced low when SHDNA is low.

______________________________________________________________________________________ 17

Discharge sequence activated. DL

forced high when shut down.

Discharge sequence activated. DL

forced high when shut down.

Enabled.

DH pulled low and DL forced high.

Disabled.

Enabled.

Disabled. Disabled.

DH pulled low and DL forced high.

Enabled.

Enabled.

Disabled.

Page 18

专为台式机、笔记本和图形卡提供的

集成式

DDR

____________________________

在选择开关频率及电感工作点(纹波电流比或

应严格地确定

载电流

(I

LOAD

buck

。主要的设计折衷是要选择一个合适的开

)

电源方案

调节器的输入电压范围

设计步骤

LIR)

及最大负

(VIN)

关频率及电感工作点,以下为除此之外的其他四个设计

要素:

输入电压范围。最大值

•

下的电压,最小值

(V

(V

IN(MIN)

IN(MAX)

)

必须考虑最坏情况

)

必须考虑接插件及保险丝

上的压降。如果可能,选择较低的输入电压将获得较

高的效率。

最大负载电流。有两个值需要考虑。峰值负载电流

•

(I

输出电容选择、电感饱和指标以及限流电路的设计。

MAX8550/MAX8551

连续负载电流

容、

开关频率。此项选择决定器件尺寸与效率之间的折衷。

•

由于

决定瞬时器件应力及滤波要求,并由此而决定

)

PEAK

决定热应力并因此而决定输入电

)

LOAD

V

MOSFET

MOSFET

(I

、及其他关键发热器件的选择。

的开关损耗正比于频率和

2

,因此最

IN

佳频率很大程度上取决于最大输入电压。最佳频率也

因时而异,

MOSFET

技术的迅速提高使得更高工作频

率成为可能。

电感工作点。此项选择需折衷考虑:尺寸与效率;瞬

•

态响应与输出纹波。低电感值可提供更好的瞬态响应

及更小的物理尺寸,但也会导致更低的效率和更高的

输出纹波,因为纹波电流增加了。最小的实用电感值

使电路工作于临界传导模式的边缘(此时电感电流在最

大负载下每一周期刚好到零)。低于此值的电感将不会

带来进一步的尺寸方面的好处。最佳工作点通常具有

20%至50%

SKIP

的纹波电流。当发生跳脉冲时(轻载,且

为低),电感值也决定了发生

PFM/PWM

切换时的

负载电流值。

设置输出电压

预置的输出电压

MAX8550/MAX8551

无需外部元件(图5)。连接FB至

出,连接FB至

至

选择固定的

OUT

的双工作模式允许选择常用电压而

可获得固定

GND

AV

为固定的

DD

0.7V

输出。

输出,或直接连接

1.8V

以前,

(Buck)

2.5V

FB

输

用FB引脚上的电阻分压器来设置

调节器的输出电压

Buck

调节器输出电压可用一个电阻分压器在

Buck

之间进行调节(图6)。

固定参考电压

其中

V

FB

终端电源输出

可将

VTT

为

V

REFIN

可将

VTTS

大值为

V

I

x 0.3Ω (

VTT

终端参考电压

FB

REF (2.0V)

0.1V

(0.7V)

VV

OUT FB

为

0.7V,R

V LIR I R

RIPPLE LOAD MAX ESR

(VTT)

输出直接与

。第二种,从

/ 2

VTT

- V

VTTI

最大)。

(VTTR)跟踪1/2 V

AMPLIFIER

MAX8550/MAX8551

。可调输出电压为:

⎛

R

=+

及

R

C

C

⎜

R

⎝

D

如图6所示,

D

=× ×

设置

VTT及VTTR

可用两种不同的方法来设置。第一种,

输入连接,强制将

VTTS

VTT

调整成高于

DROPOUT

TO

ERROR

V

,其中

REFIN

TA= +85°C时V

REFIN

(V

OUT

0.7V至5.5V

调整FB至一个

⎞

V

RIPPLE

+1

⎟

⎠

()

2

V

RIPPLE

电压

VTT

为:

(LDO)

调整

连接一个电阻分压器到

的电压。

/ 2

的最

VTT

DROPOUT

。

MAX8550/

MAX8551

OUT

1.8V

(FIXED)

2.5V

(FIXED)

)

=

图

双模式反馈解码器

5.

18 ______________________________________________________________________________________

Page 19

专为台式机、笔记本和图形卡提供的

V

OUT

R

C

R

D

电感选择

C

OUT

(Buck)

MAX8550/

MAX8551

图

利用电阻分压器设定

6.

PGND1

GND

OUT

LX

DL

FB

V

OUT

L

Q2

电感量和开关频率及电感工作点的关系由下式决定:

VVV

-

()

L

例如:当

= 600kHz、30%

f

SW

L

=

V f I LIR

I

LOAD(MAX)

=

12 600 12 0 3

OUT IN OUT

×× ×

IN SW LOAD MAX

()

= 12A、VIN= 12V、V

纹波电流或

VV

. (

25 12

V kHz A

.

×××

LIR = 0.3

- 2.5V)

时,有:

≈

OUT

1

µ

= 2.5V

H

找一个直流电阻尽量小,并能安装到规定空间内的低损

耗电感。尽管铁粉芯电感价格便宜且能很好地工作至

200kHz

够大,在峰值电感电流

大多数电感厂商都提供具有标准值的电感,例如

1.5µH、2.2µH及3.3µH

,但铁氧体芯电感仍然是最佳选择。磁芯必须足

下不应饱和:

(I

)

PEAK

LIR

II

=+

PEAK LOAD MAX

⎛

1

⎜

()

⎝

⎞

⎟

⎠

2

1.0µH

等。也可考虑非标值,以便在整

集成式

DDR

个输入电压范围内取得最佳折衷的

电源方案

。如果使用回转电

LIR

感(空载电感量随电流增加线性降低),则应按照适当调

整后的电感量来估计

LIR

。

输入电容选择

输入电容必须能够承受供应开关电流所需的纹波电流

):

(I

RMS

当

VIN= 2 x V

II

=

RMS LOAD

OUT

时

具有最大值

I

RMS

VVV

OUT IN OUT

-

()

V

IN

I

/ 2

LOAD

数应用,更愿意选择非钽电容(陶瓷、铝电解、

OSCON等)

,因为它们能有效地抑制上电时的浪涌电流,

这是输入端串有机械开关或接头的系统的一个典型问题。

如果将

MAX8550/MAX8551

用作两级功率变换系统的第

二级,则可使用钽输入电容。在任何配置中,所选电容

在

输入电流的作用下温升都应低于

RMS

10°C

高的可靠性及寿命。

输出电容选择

输出滤波电容必须具有足够低的等效串联电阻

满足输出纹波及负载瞬变要求,同时也必须具有足够高

的

来满足稳定性要求。

ESR

对于处理器核电压转换器,或其他需要应付剧烈的瞬态

、

负载的应用,输出电容的尺寸取决于所需的

态负载的作用下,它不应使输出跌落的过低。忽略因容

量有限而导致的电压跌落:

V

R

≤

ESR

在没有很大及快速负载瞬变的应用中,输出电容的大小

常常取决于需要多大的

R

波。降压控制器的输出纹波电压大约为总电感纹波电流乘

以输出电容的

、

。因此,满足纹波指标的最大

R

ESR

R

≤

ESR

I LIR

LOAD MAX

STEP

∆

I

LOAD MAX

()

来保持可接受的输出电压纹

ESR

V

RIPPLE

×

()

(Buck)

。对于大多

POS

,以获得较

(Buck)

,以

(R

)

ESR

,在瞬

R

ESR

为:

R

ESR

MAX8550/MAX8551

或

______________________________________________________________________________________ 19

Page 20

w

专为台式机、笔记本和图形卡提供的

集成式

实际的电容值要求与

以及电容器的化学特性有关。故通常是按

标而不是按电容值来选择电容(对于钽电容、

聚合物电容以及其他电解电容都是如此)。

当使用陶瓷电容这样的低容值滤波电容时,其大小通常

根据负载瞬变期间,

准则来确定。一般而言,只要容量增加到满足过冲要求,

则负载上升沿处的下冲也不会有问题(参见

中的

V

SAG

具有较高的

定性要求

DDR

与

V

SOAR

零点,它可能会影响整体稳定性(参见

ESR

部分)。

电源方案

及满足该

ESR

及

V

计算公式)。但低容值滤波电容一般

SAG

V

SOAR

所需的物理尺寸,

ESR

及电压指

ESR

OSCON

不超出容许范围这一

瞬态响应

稳定性要求

对于

MAX8550/MAX8551

Quick-PWM

开关频率的位置。不稳定边界由下式给出:

其中:

:

here

如果

C

OUT

所示,则其

对于典型的

190kHz

150µF/4V Sanyo POS

零点频率为

为确保稳定,请不要未加考虑地将高容值陶瓷电容直接

连接在反馈检测点。大陶瓷电容具有较高的

率,因此容易引起异常的不稳定工作。不过,这个问题

很容易解决,只需将电容放置在反馈点下游数英寸之外

即可,反馈点应尽可能靠近电感。

工作的不稳定性以两种相关但明显不同的方式表现出来:

双脉冲和不稳定的快反馈环。双脉冲的产生是由于输出

上的噪声,或由于

够的电压斜坡。这能“欺骗”误差比较器在经过

最小关断时间后立即触发一次新的周期。

,最好低于

控制器,稳定性取决于

f

f

ESR

=

f

ESR

由多个相同的电容组成,如图

与单个电容的

f

ESR

600kHz

42kHz

应用,

100kHz

电容来提供

,很好地处于稳定边界内。

太低而没有在输出信号中产生足

ESR

SW

≤

π

××

π12

f

ESR

ESR

。典型应用中我们使用两只

RC

ESR OUT

值相等。

零点频率必须远远低于

12mΩ (最大)的R

零点相对于

ESR

典型应用电路

8

ESR

400ns

部分

稳

ESR

零点频

的

双脉冲虽不具有破坏性但很恼人,除了增加输出纹波外

没有其他更坏的后果。然而,它可能预示着由于

不足,环路可能没有稳定。不稳定的控制环在经历了输

、

入或负载阶跃后会在输出上产生振荡。这种振荡通常会

被衰减下来,但它可能会使输出电压超出或低于容限。

检查稳定性最简单的方法是,施加一个快速的零到满负

载瞬变,并仔细观察输出电压纹波的包络,检查它的过

冲和振铃。同时用一个交流电流探头监视电感电流也很

有帮助。阶跃响应引起的上/下冲之后的振铃不应让它超

过一个周期。

输出电容选择

VTT

对于最高至

定

大约

定。为了保证该电容在调节器的带宽范围内表现为容性,

应选择低

由于增益带宽也受输出

电流增加而增加,故如果负载电流超过

必须大于

电容亦可小于

容及输出电容的最大

,

其中

给出:

当这些稳定条件满足后,如有必要,还可另外增加一些

电容(包括电解及钽电容等)和陶瓷电容并联来进一步降

低噪声或纹波。

输出。此电容值将调节器的单位增益带宽限制在

VTT

700kHz (

ESR和ESL

60µF

应是单位增益带宽频率下的值,该频率由下式

R

ESR

的负载,需要用最小

±1.5A

典型值),以便有足够的相位余量来保证稳

的陶瓷电容,这一点非常重要。

跨导的影响,

FET

,但如果最大负载电流小于

。通常,可按下列公式来选择最小电

60µF

:

ESR

CF

OUT MIN

Rm

ESR MAX

f

GBW

=×

60

_

_

=×

µ

=×

5

Ω

40

C

OUT

I

I

LOAD

I

LOAD

.

15

60µF

FET

1.5A

LOAD

.

15

A

.

15

A

A

1.5A

的

ESR

(LDO)

的电容来稳

跨导随负载

,输出电容

,则输出

20 ______________________________________________________________________________________

Page 21

专为台式机、笔记本和图形卡提供的

输出电容选择

VTTR

缓冲器是

VTTR

跨导。因此其补偿电容可以更小,

要负载电流高达

最小电容值的陶瓷电容

在

与模拟地平面之间。

VTTR

VTT与VTTR

出电压都以同一

了限制

上的纹波/噪声量,或限制负载瞬变时电压的

VTTI

下降幅度。通常

调节器的缩小版,具有小得多的输出

VTT

可以更大。对于需

ESR

±20mA

输出级均由同一

REFIN

VTTI

的典型应用,建议使用具有

(R

< 0.3Ω)

ESR

VTTI

VTTI

输入为基准。

被连接到

。应将此电容连接

输入电容选择

输入供电,它们的输

VTTI

调节器的输出,上面

buck

已经具备了大值电容。但还是需要一个至少

电容,并使其尽可能靠近

或从

引脚到电源的走线较长,具有明显的阻抗,此

VTTI

电容值必须相应增大。另外,为防止

合到

REFIN

REFIN

直接接至

输入,并因此而带来潜在的环路不稳定性,

引脚最好从单独的低阻抗直流源上接出,而不要

输入。如果不可避免,则可增加

VTTI

上的旁路电容量,同时在

引脚。如果负载电流更大,

VTTI

VTTI

引脚上再增加另外的旁

REFIN

路电容。

(LDO)

1µF

(LDO)

旁路电容是为

的陶瓷

10µF

反射噪声被耦

输入

VTTI

集成式

方式的不同,高边

损耗成分。低边

MOSFET

MOSFET

作为一个零电压开关工作,故

DDR

与低边

电源方案

MOSFET

其损耗主要为:

沟道传导损耗

•

体二极管传导损耗

•

栅极驱动损耗

•

P

LSCC

利用

T

J(MAX)

PIVtf

其中

f

为体二极管的正向压降,

V

F

为开关频率。由于是零电压开关工作,故低边

SW

⎛

=

⎜

⎝

下的

=×××2

LSDC LOAD F DT SW

栅极驱动损耗主要源于对输入电容

(P

LSCC

(P

LSDR

-

R

DS(ON)

(P

V

)

LSDC

):

OUT

V

IN

:

)

⎞

××1

⎟

⎠

2

IR

LOAD DS ON

为死时间

t

DT

的充放电,该损

)

(C

ISS

耗分布于栅极驱动器的平均上拉及下拉电阻

及

MOSFET

的内部栅极电阻

R

GATE

上。驱动功耗由

(≈2Ω)

下式计算:

具有不同的

()

(≈30ns)

MOSFET

R

(≈1Ω)

DL

MAX8550/MAX8551

,

以

选择

(Buck)

MOSFET

MAX8550/MAX8551

MOSFET

利用外部、逻辑电平、N沟道

来充当开关元件,其关键参数包括:

导通电阻

(R

最大漏-源电压

输入电源

栅极电荷

应选择在

20%

(QG, QGD, QGS)

V

GS

DS(ON)

。

= 4.5V

:越低越好;

)

:应至少高出高边

(V

)

DSS

:越低越好;

下具有额定

R

DS(ON)

MOSFET

的

MOSFET

漏极

。作

为一个效率与成本之间的很好的折衷,可选择在额定输

入电压及最大输出电流下传导损耗等于开关损耗的高边

MOSFET (

会因为高边

如下所述)。对于低边

MOSFET

导通所引起的

MOSFET

dV/dt

会导致直通电流而使效率下降。具有较低

MOSFET

具有较高的

dV/dt

承受力。

,应保证其不

而错误导通,这

GS

比的

QGD/Q

对于合理的热管理设计,必须在预期的最大工作结温、

最大输出电流以及最坏情况下的输入电压下计算功耗。

对于低边

MOSFET

MOSFET,V

IN(MIN)

,最坏情况为

或

V

IN(MAX)

都是最坏情况。由于工作

V

IN(MAX)

。对于高边

HSCC

)

2

)

)

PCVf

=× ××

LSDR ISS GS SW

高边

MOSFET

沟道传导损耗

•

开关损耗

•VI

驱动损耗

•

高边

(

MOSFET

用作占空比控制开关,具有以下主要损耗:

(P

(P

HSSW

(P

HSDR

没有体二极管传导损耗,因为该二极管不

导通):

V

OUT

P

HSCC

利用

T

J(MAX)

PVIf

HSSW IN LOAD SW

=× ×

V

下的

R

DS(ON)

IR

IN

LOAD DS ON

:

=× ××

R

GATE

RR

2

+

GATE DL

()

QQ

+

GS GD

I

GATE

______________________________________________________________________________________ 21

Page 22

专为台式机、笔记本和图形卡提供的

集成式

其中

I

GATE

其中

R

DH

1Ω),且R

PQVf

HSDR G GS SW

其中

V

GS

留出大约

及低边

MAX8550/MAX8551

上所造成的损耗,这种损耗在

DDR

为DH驱动器平均输出电流,按下式计算:

I

GATE ON

为高边

20%

MOSFET

MOSFET

为

GATE

=×××

= VDD= 5V

的额度,其中包括由于

体二极管反向恢复电荷在高边

很好的规定。参照

电源方案

25

.

=

()

RR

驱动器的导通电阻(典型值为

MOSFET

的内部栅极电阻

。除上述损耗外,还应为其他损耗

MOSFET

数据资料中的热阻规范,利

V

+

DH GATE

RR

MOSFET

MOSFET

(≈2Ω)

R

GATE

GATE DH

数据资料中没有

:

+

输出电容

MOSFET

用上面得出的功耗,可计算出保证器件工作在预期的最

大结温范围内所需要的PC板面积。为减少由开关噪声所

引起的

一个

关转换速度。增加串联电阻会增加

此需确信这不会使

,可在高边开关漏极与低边开关源极之间增加

EMI

陶瓷电容,或在DH及DL上串联电阻来减慢开

0.1µF

MOSFET

MOSFET

过热。

MOSFET

阻尼电路

的功耗,因

快速开关转换会产生振铃,因为开关节点上的寄生电感

和电容形成谐振电路。这种高频振铃发生在LX的上升及

下降转换阶段,会影响电路的性能并产生

。为减少这

EMI

种振铃,可在每个开关的两端增加一个串联RC阻尼电路。

以下为选择阻尼电路串联RC值的简单步骤:

用一个示波器探头测量

1)

并观察振铃频率

找到一个可将振铃频率降低一半的电容(电容连接在

2)

LX至PGND1

约为上述电容的

C

PAR

再按下式来估算电路的寄生电感

3)

;

f

R

之间),然后估算电路的离散电容

1/3

V

。

LX

至

PGND1

(L

之间的信号,

:

)

PAR

(C

(Buck)

。

)

PAR

再按下式来估算临界阻尼电阻

4)

fRx L

。可上下调整该电阻以获得满意的阻尼及峰

PAR

(R

SNUB

):R

SNUB

= 2π x

值电压飘移。

电容

5)

(C

阻尼电路的功耗

SNUB

应至少为

)

(P

RSNUB

的2至4倍才有效。

C

PAR

主要由电阻耗散,可按下式

)

计算:

2

的功率

R

SNUB

其中

PCVf

RSNUB SNUB IN SW

为输入电压,

V

IN

=××

为开关频率。按照特定应用所

f

SW

要求的降额幅度,根据算出的功耗来选取

指标。

MAX8550/ MAX8551

中的

应采用

数,并考虑到

的导通电阻

Q2)

MOSFET

R

利用低边

(R

DS(ON)

MOSFET (

检测电流。在计算电流限时,

)

数据资料中最坏情况下的最大

会随温度上升,应再增加一定的余

DS(ON)

量。一个通用的规律是:温度上升

设置电流限

电阻增加

1°C

(Buck)

典型应用电路

DS(ON)

0.5%

参

。

R

最小电流限制门限必须足够大,以便电流限位于容差范

围的最小值时仍能支持最大负载电流。电感电流的谷值

为

I

LOAD(MAX)

II

LIM VAL LOAD MAX

其中

I

LIM(VAL)

通电阻

减去一半纹波电流,故:

I LIR

⎛

LOAD MAX

⎜

⎝

()

2

() ( )

-

等于最小谷值电流限制门限电压除以Q2导

(R

DS(ON)Q2

)。连接

ILIM至AV

DD

可获得

>×

⎞

⎟

⎠

50mV

的

默认设置。在可调模式中,谷值电流限制门限精确地等

于

器,并将

外部

上电压的

ILIM

ILIM

250mV至2V

1/10*

。从

REF至GND

连接一个电阻分压

与中心抽头连接,即可对门限进行调整。

的调节范围对应于

25mV至200mV

的谷

值电流限制门限。在调节电流限时,可使用1%容差的电

阻及大约

的分压器电流,以免给谷值电流门限带来

10µA

显著的误差。

L

=

PAR

22 ______________________________________________________________________________________

22π

()

1

×

fC

×

R PAR

在负向,可调电流限典型为

*

ILIM

上电压的

-1/8

。

Page 23

专为台式机、笔记本和图形卡提供的

折返式电流限制

作为另外一种选择,如果没有

折返式限流功能。折返式限流可减少外部器件的功耗,

因此能够忍受无限期的过载和短路,过载或短路故障解

除后还可自动恢复。要实现折返式限流,可从

连接一个电阻(图7及

ILIM

设置可调电流限的电阻分压网络仍然保留

图7所示。

以下为R4、R5及R6的计算步骤:

计算输出电压为额定值时,

1)

V

ILIM(NOM)

VI

ILIM NOM LOAD MAX

2)从15%至40%

计算输出电压短路时

3)

按下式计算R4:

4)

:

=× ×

() ()

MAX8550/

MAX8551

10 1

选取一个折返百分比,

VPV

ILIM V FB ILIM NOM() ( )

0

R

4

典型应用电路

×

R

DS ON Q

()

(0V)

=×

VV

2

-

=

REF

ILIM

锁定功能,则可使用

UVP

上所需的电压,

ILIM

2

PFB

的电压

10

ILIM V

0

()

A

µ

C

REF

V

ILIM(0V)

R4

R6

中的

R6)

(R4与R5)

⎛

LIR

-

⎜

2

⎝

;

:

V

OUT

R5

V

OUT

,用于

⎞

⎟

⎠

到

,如

集成式

5) R 5与R6

然后,R6可按下式计算:

6)

7) R5

的并联电阻(用

R

R

6

=

⎡

VV V R

OUT ILIM NOM ILIM V

()

⎢

⎢

VVR

⎢

()

()

⎣

为:

VRR

-- 4-

()

() ()

ILIM NOM ILIM V

R

DDR

表示)计算如下:

R56

⎛

V

2

=

OUT

5

=

⎜

A

10

µ

⎝

4 5

××

() ()

−

RR

656

×

RR

656

-

电源方案

⎞

R56

- 4

⎟

⎠

6

0

×

0

56

⎤

×

⎥

⎥

⎥

⎦

自举电源二极管及电容的

选择

(Buck)

低电流肖特基二极管,例如由

提供的

结电容较大的大功率二极管,因为它会将

压充高,乃至超过6V极限。自举电容应在

之间选取,取决于输入及输出电压、外接元件与PC板布

局。自举电容应尽可能大,以免它被充至过高电压,同

时还应足够小,以便在低边

充分充电,低边

作占空比时(也就是输入电压最小时)。此外,还应确保

自举电容不会因放电而使电压跌落到无法充分打开高边

栅-源电压

CMDSH-3

MOSFET

的程度,以保证足够小的导通电阻。这个最小

,可很好地适应大多数应用。不要使用

MOSFET

=

()

由下式决定:

)

(V

GS(MIN)

VVx

GS MIN DD

Central Semiconductor

BST到LX

0.1µF至4.7µF

MOSFET

的最小导通时间发生在最大工

的最小导通时间内

Q

G

C

BOOST

公司

的电

MAX8550/MAX8551

图

折返式电流限制

7.

GND

______________________________________________________________________________________ 23

Page 24

专为台式机、笔记本和图形卡提供的

集成式

1.25V

1.25V

MAX8550/MAX8551

POK1

POK2

/

±1.5A

VTTR

/

10mA

100kΩ

VTT

R2

DDR

10µF

C4

60µF

R3

100kΩ

C10

0.22µF

R5

20kΩ

R6

41.2kΩ

电源方案

C2

C6

1µF

C9

3.9nF

VTTI

VTT

VTTS

PGND2

VTTR

OVP/UVP

POK

SKIP

TON

GND

SS

REF

R4

187kΩ

ILIM

FB

OUT STBY

REFIN

MAX8550

C1

0.01µF

AV

V

V

BST

DH

PGND1

SHDNA

SHDNB

C3

1µF

DD

R1

10Ω

DD

D1

CMOSH-3

IN

C7

0.22µF

LX

DL

C5

4.7µF

C8

2 x 10µF

Q1

IRF7821

N-CHANNEL

30V, 9mW

L1

TOKO FDA1254-1R0M

1.0µH, 21A, 1.6mΩ

Q2

IRF7832

N-CHANNEL

30V,5mW

ON

OFF

C14

470µF

(OPTIONAL)

5V

BIAS

SUPPLY

(4.5V TO 28V)

V

IN

C12

150µF

C11

150µF

C11, C12 (150mF, 4V,

25mW, LOW-ESR POS

CAPACITOR (D2E)

SANYO 4TPE150M

C13

1µF

2.5V

/

12A

图

典型应用电路

8.

其中

为自举电容值,

V

DD

为5V,

Q

G

C

BOOST

为高边

为

MOSFET

的总栅极电荷,

典型应用电路

中的

C

C7 (图8)

BOOST

。

电感纹波电流也影响器件的瞬态响应——尤其当

差值较小时。低值电感允许电感电流更快地摆动,

V

OUT

补足输出滤波电容上因负载突增而被抽走的电荷。

24 ______________________________________________________________________________________

瞬态响应

(Buck)

VIN-

Page 25

专为台式机、笔记本和图形卡提供的

输出跌落量也与最大占空比有关,根据导通时间和最小

关断时间计算如下:

V

=

SAG

2

CV

其中

t

OFF(MIN)

从表1中选取。

K

⎡

LI

×

∆

LOAD MAX

×

OUT OUT

2

⎢

() ()

⎣

⎡

VV K

()

IN OUT

⎢

⎢

⎣

为最小关断时间(参见

VK

×

-

OUT

V

V

IN

IN

×

+

+

t

OFF MIN

t

Electrical Characteristics )

()

OFF MIN

⎤

⎥

⎦

⎤

⎥

⎥

⎦

,

当负载从满载到空载瞬变时,由电感的储能所引起的过

冲可按下式计算:

IL

∆

V

SOAR

LOAD MAX

=

CV

××

2

OUT OUT

____________________________

2

()

×

应用信息

压差性能

(Buck)

连续传导工作模式下,输出电压的调节范围受限于不可

调节的最小关断时间单稳态。为获得最佳的压差性能,

可使用较慢

(200kHz)

的开通时间设置。工作于低输入电

压时,极限占空比必须根据最坏情况下的导通和关断时

间来计算。制造容差及内部传导延时将给

TON K

因子引

入误差,此误差在较高频率上更为明显(参见表1)。请注

意,过于接近压差条件工作的

态响应,常常需要使用很大尺寸的输出电容(参见

骤

中的

V

SAG

计算公式)。

当最小关断时间内电感电流的下降量

间内的上升量

∆IUP/ ∆I

DOWN

持平时,即达到极限压差点。比值

(∆IUP)

表示控制器拉高电感电流以响应增加负载

调节器具有较差的瞬

buck

(∆I

DOWN

设计步

与开通时

)

h =

的能力,它必须总是大于1。当h接近于1时——即最小压

差点,电感电流不能在每个开关周期内增加同样多的量,

将极大地增加,除非使用更多的输出电容。

V

SAG

合理的最小h值为

,但亦可上下调整,以便在

1.5

V

SAG

、

输出电容及最小工作电压之间取得更好的平衡。对于给

定的h值,最小工作电压可按下式计算:

集成式

其中

V

见

导通时间单稳态

Characteristics,K

时取

h = 1

如果计算出的

DROP1

。

与

V

V

DDR

为充、放电路径上的寄生压降(参

DROP2

IN(MIN)

部分),

(TON)

从表1中选取。计算绝对最小输入电压

大于所需的最小输入电压,则必

电源方案

t

OFF(MIN)

参见

Electrical

须降低工作频率,或通过增加输出电容来获得一个可以

接受的

要计算

。如果预计会在靠近压差的条件下工作,则

V

SAG

看是否具有足够的瞬态响应。

V

SAG

压差设计举例如下:

= 2.5V

V

OUT

f

= 600kHz

SW

K = 1.7µs

t

OFF(MIN)

V

DROP1

= 450ns

= V

DROP2

= 100mV

h = 1.5

V

IN MIN()

⎡

⎢

⎢

⎢

⎢

⎢

⎣

. .

25 01

⎛

.

1 5 450

1

-

⎜

⎝

VV

+

Vns

×

.

17

µ

⎤

⎥

⎥

VV V

. . .=

+=

01 01 43

⎥

⎞

⎥

⎟

s

⎥

⎠

⎦

-

电压定位

(Buck)

在具有快速负载瞬变的应用中,输出电压会瞬时变化

x C

R

ESR

OUT

x ∆I

。电压定位可使这些应用使用更少

LOAD

的输出电容,并使输出电压的交流和直流容差窗口最大

化,这对容差很紧张的应用非常有利。

图9显示了在一个电压定位电路中

非电压定位电路中,

MAX8550/MAX8551

容上的电压。在电压定位电路中,

电压定位电阻的电感侧进行调整。

VV RI

OUT VPS OUT NO LOAD POS LOAD() (_ )

=× -

OUT与FB

MAX8550/MAX8551

V

OUT

的连接。在

调节的是输出电

在

被降低至:

MAX8550/MAX8551

V

IN MIN

⎡

⎢

⎢

⎢

⎢

1-

⎢

⎣

×

VV

OUT DROP

×

ht

⎛

⎜

⎝

OFF MIN

()

K

______________________________________________________________________________________ 25

⎤

⎥

⎥

1

+

VV

⎥

DROP DROP()

⎞

⎥

⎟

⎥

⎠

⎦

=

-

21

Page 26

专为台式机、笔记本和图形卡提供的

集成式

MAX8550/MAX8551

图

9.

DDR

电压定位输出

电源方案

AV

DD

MAX8550/

MAX8551

FB

V

DD

IN

BST

DH

LX

DL

PGND1

GND

OUT

板布局准则

PC

精心的PC板布局对于实现低开关损耗及干净、稳定的工

作非常关键,尤其对开关功率级的布局需特别注意。如

果可能,应将所有功率器件安装在电路板的顶层,且使

其接地端齐平。良好的PC板布局应遵循以下准则:

使高电流路径尽可能短,尤其是接地端。这对于实现

•

稳定及无抖动工作很关键。

承载大功率的走线和到负载的连线尽可能短,这对于

•

获得高效率很重要。使用厚敷铜的PC板

(2oz对比1oz)

可使满负载效率提高1%或更多。正确的PC板布线是

一项艰巨的任务,需达到了几分之一厘米的程度,

级的引线电阻就会造成明显的效率损失。

到低边

•

MOSFET的LX及PGND1

连接必须采用开尔文

感应连接方式。

当必须走比较长的线时,应优先考虑在电感的充电路

•

径上增加长度,而尽量不要增加放电路径的长度。例

如,最好将额外的距离放在输入电容与高边

之间,而不要增加电感与低边

MOSFET

MOSFET

或电感与输出

滤波电容之间的距离。

mΩ

+5V BIAS

SUPPLY

V

IN

VOLTAGE-

)。

POSITIONED

OUTPUT

远离敏感的模

MOSFET

的

MOSFET

R

POS

使高速开关节点

•

拟区

(REF、FB及ILIM

必须使输入陶瓷电容的位置尽可能靠近高边

•

漏极和低边

(BST、LX、DH及DL)

MOSFET

的源极,输入电容端子与

之间的阻抗要尽可能小。

部分的特殊布局考虑

LDO

应使

及

11)

PGND2

片上。必须将裸露垫片以星形方式连接至

PGND1 (

容器

线远离可能的噪声源,例如

上的电容尽可能靠近

VTT

VTT及PGND2 (

引脚

,以减少走线的串联电阻/电感。电容器连接

的一侧必须用低阻抗路径短接至IC底部的裸露垫

GND (引脚24)

引脚

23)、PGND2 (引脚11)

侧的输出电压接回

VTT

VTTS (

PGND1或PGND2

。可用较窄的线将电

引脚9),但应使这条

。这能防止

12

噪声被注入误差放大器的输入中。为获得最佳性能,应

使

的走线单独连接

GND

旁路电容尽可能靠近

VTTI

REFIN (

VTTI (引脚13)

引脚

,并提供足够的旁路至

14)

。进一步的PC板布局准则,请参见

。应使用干净

MAX8550

评估

板数据手册。

、

26 ______________________________________________________________________________________

Page 27

专为台式机、笔记本和图形卡提供的

集成式

DDR

________________________________________________________________

C1

0.01µF

REFIN

0.9V - 1.25V / 1.5A

0.9V - 1.25V / 10mA

VTT

VTTR

POK1

POK2

C2

C4

C6

R2

R3

C9

C10

R5

R6

VTTI

AV

V

BST

PGND1

SHDNA

SHDNB

STBY

DD

DD

V

IN

LX

DH

DL

VTT

VTTS

PGND2

MAX8550/

VTTR

MAX8551

OVP/UVP

POK

SKIP

TON

GND

SS

REF

R4

ILIM

FB

OUT

R1

10Ω

C7

C3

1µF

Q1

Q2

5V

BIAS

C5

C8

L1

ON

OFF

SUPPLY

(4.5V TO 28V)

V

IN

C11

1.8V - 2.5V / 12A

电源方案

MAX8550/MAX8551

典型工作电路

____________________________

芯片信息

TRANSISTOR COUNT: 5100

PROCESS: BiCMOS

______________________________________________________________________________________ 27

Page 28

专为台式机、笔记本和图形卡提供的

集成式

DDR

电源方案

___________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

D2

C

L

k

D2/2

b

0.10M C A B

E2/2

MARKING

D

XXXXX

0.15 C A

D/2

E/2

0.15

C B

E

(NE-1)Xe

MAX8550/MAX8551

L

PIN#1

I.D.

DETAILA

e

L

L1

e

(ND-1)Xe

DETAILB

L

C

E2

L

k

PIN#1I.D.

0.35x45∞

CC

L

封装信息

QFN THIN.EPS

C

-DRAWINGNOTTOSCALE-

LL

0.10 C

A

0.08 C

A3

A1

e e

PACKAGEOUTLINE,

16,20,28,32LTHINQFN,5x5x0.8mm

21-0140

1

F

2

28 ______________________________________________________________________________________

Page 29

专为台式机、笔记本和图形卡提供的

集成式

DDR

_______________________________________________________________

电源方案

封装信息(续

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)