Page 1

19-3380; Rev 2; 4/05

THIN QFN

MAX7317ATE

13

14

15

1234

5

6

16

12 11 10 9

8

7

V+

DIN

SCLK

P0

P1

P2

P3

P9

P8

P7

CS

P5

P6

GND

P4

DOUT

TOP VIEW

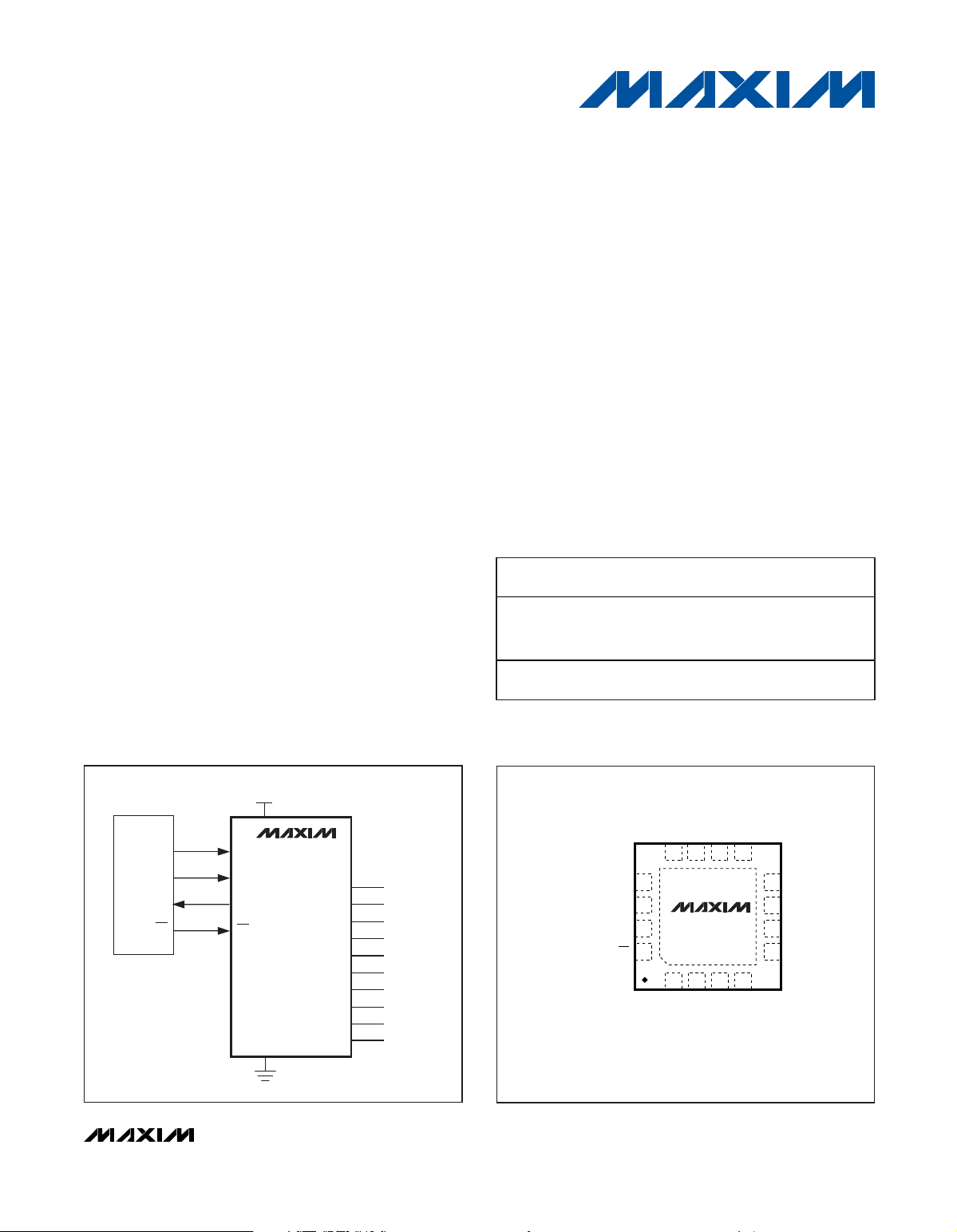

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

____________________________________

概述

MAX7317串行接口外设器件能够为微处理器提供10个I/O

端口,额定电压为7V。每个端口都可单独配置为漏极开

路输出或带有过压保护的施密特输入。

MAX7317支持热插入。所有端口引脚在关闭电源时 (V+ =

0V) 具有高阻抗,并允许有8V电压。

MAX7317采用16引脚、薄型QFN和QSOP封装,工作在

-40°C至+125°C的温度范围。

如需具有恒定电流输出和8位PWM控制的类似器件,请

参考MAX6966/MAX6967的数据资料。

____________________________________

应用

便携式设备

蜂窝电话

白色家电

工业控制器

汽车

系统监视

____________________________________

高速、26MHz、SPITM/QSPITM/MICROWIRE

♦

兼容的串行接口

2.25V至3.6V工作电压

♦

I/O端口输入过压保护至7V

♦

I/O端口为7V额定电压的开漏极输出

♦

I/O端口支持热插入

♦

0.7µA (典型值),1.9µA (最大值) 的待机电流

♦

微型3mm x 3mm、高度为0.8mm的薄型QFN 封装

♦

-40°C至+125°C工作温度范围

♦

________________________________

PART

MAX7317ATE

TEMP

RANGE

-40°C to

+125°C

PINPACKAGE

16 Thin QFN

3mm x 3mm x

0.8mm

TM

定购信息

TOP

MARK

ACH T1633-4

特性

MAX7317

PKG

CODE

SPI与 QSPI是Motorola, Inc.的商标。

MICROWIRE是 National Semiconductor Corp.的商标。

____________________________

+3.3V

µC

MAX7317

SCLK

MOSI

MISO

CS

本文是Maxim 正式英文资料的译文,Maxim 不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

SCLK

DIN

DOUT

CS

GND

________________________________________________________________ Maxim Integrated Products 1

典型应用电路

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

I/O PORTS

MAX7317AEE

_______________________________

引脚配置 (续) 见数据资料的最后部分。

-40°C to

+125°C

16 QSOP — —

引脚配置

翻译错误,如需确认任何词语的准确性,请参考 Maxim提供的英文版资料。

索取免费样品和最新版的数据资料,请访问Maxim的主页:www.maxim-ic.com.cn。

Page 2

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

ABSOLUTE MAXIMUM RATINGS

Voltage (with respect to GND)

V+ .............................................................................-0.3V to +4V

SCLK, DIN, CS, DOUT .................................-0.3V to (V+ + 0.3V)

P_ .............................................................................-0.3V to +8V

DC Current into P_ .............................................................24mA

DC Current into DOUT ........................................................10mA

Total GND Current ............................................................200mA

MAX7317

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Continuous Power Dissipation (T

16-Pin Thin QFN

(derate 14.7mW/°C above +70°C).........................1176mW

16-Pin QSOP (derate 8.3mW/°C above +70°C)...........667mW

Operating Temperature Range

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

to T

(T

MIN

) ..............................................-40°C to +125°C

MAX

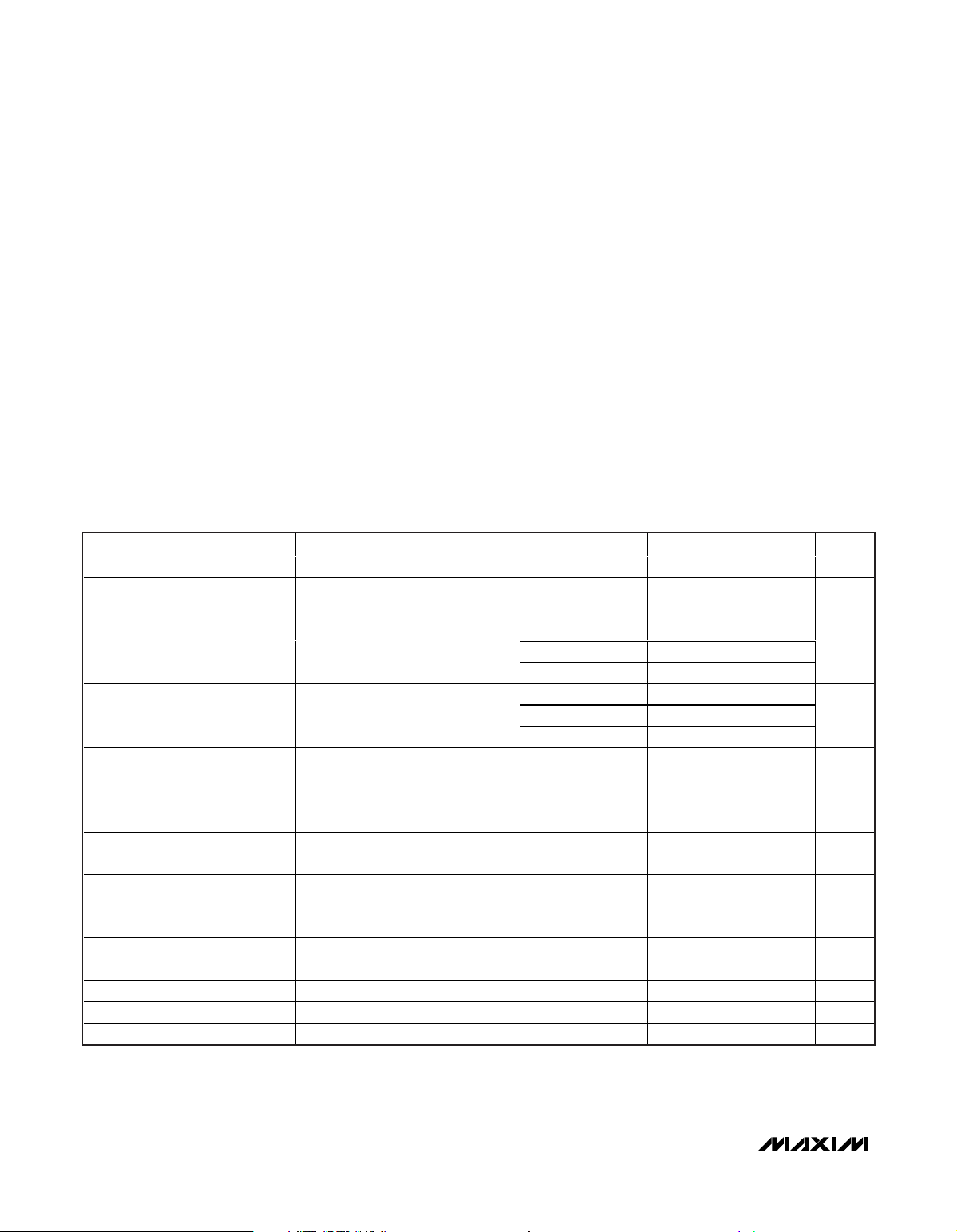

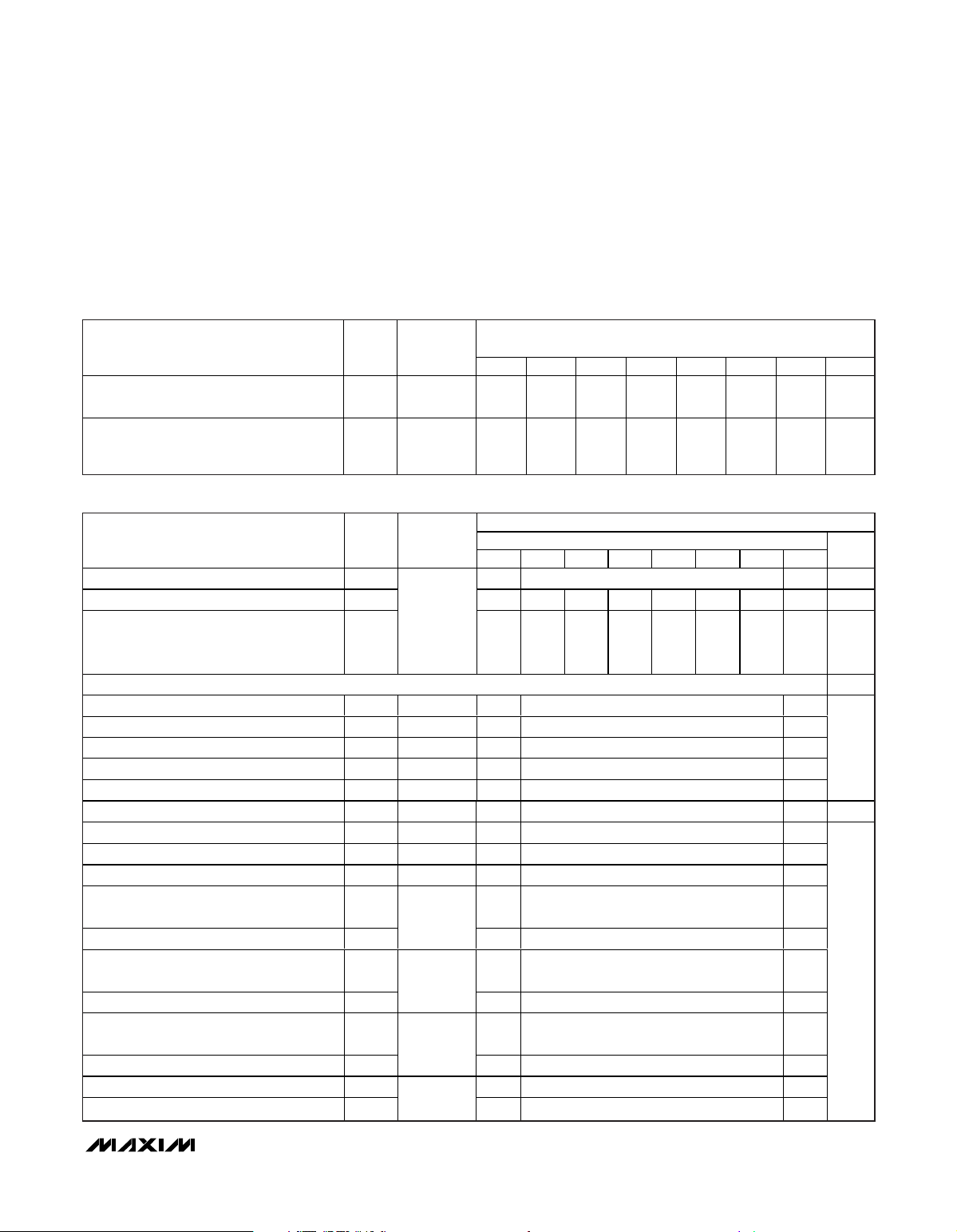

ELECTRICAL CHARACTERISTICS

(Typical Operating Circuit, V+ = 2.25V to 3.6V, TA= T

(Note 1)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Operating Supply Voltage V+ 2.25 3.60 V

Output Load External Supply

Voltage P0–P9

Standby Current

(Interface Idle)

Supply Current I

Input High Voltage

(P0–P9, DIN, SCLK, CS)

Input Low Voltage

(P0–P9, DIN, SCLK, CS)

Input Leakage Current

(P0–P9, DIN, SCLK, CS)

Input Capacitance

(P0–P9, DIN, SCLK, CS

Output Low Voltage (P0–P9) V

Output Low Short-Circuit Current

(P0–P9)

Output High Voltage (DOUT) V

Output Low Voltage (DOUT) V

Power-On Reset Voltage V

V

EXT

I

STBY

+

V

IH

V

IL

I

, I

IH

IL

OLP_ISINK

OHDOUTISOURCE

OLDOUTISINK

POR

to T

MIN

All digital inputs at V+

or GND

f

= 26MHz; other

SCLK

digital inputs at V+ or

GND; DOUT unloaded

P0–P9 output register set to 0x01 0.7 x V+ V

P0–P9 output register set to 0x01 0.3 x V+ V

(Note 2) 10 pF

= 0.5mA, output register set to 0x00 0.4 V

V

OLPOUT

= 6mA 0.3 V

, unless otherwise noted. Typical values are at V+ = 3.3V, TA= +25°C.)

MAX

TA = +25°C 0.70 1.5

T

A

T

A

TA = +25°C 385 620

T

A

T

A

= 5V 10.8 20 mA

= -6mA V+ - 0.3V V

to +85°C 1.7

= T

MIN

to T

= T

MIN

MAX

to +85°C 680

= T

MIN

to T

= T

MIN

MAX

= +70°C)

A

7V

1.9

730

-0.2 +0.2 µA

2V

µA

µA

2 _______________________________________________________________________________________

Page 3

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

TIMING CHARACTERISTICS

(Typical Operating Circuit, V+ = 2.25V to 3.6V, TA= T

(Note 1)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SCLK Clock Period t

SCLK Pulse-Width High t

SCLK Pulse-Width Low t

CS Fall to SCLK Rise Setup

SCLK Rise to CS Rise Hold

DIN Setup Time t

DIN Hold Time t

Output Data Propagation Delay t

DOUT Output Rise and Fall

Times

Minimum CS Pulse High t

Note 1: All parameters are tested at TA= +25°C. Specifications over temperature are guaranteed by design.

Note 2: Guaranteed by design.

CP

CH

CL

t

CSS

t

CSH

DS

DH

DO

t

FT

CSW

C

to T

MIN

= 20pF (Note 2) 10 ns

LOAD

, unless otherwise noted. Typical values are at V+ = 3.3V, TA= +25°C.)

MAX

38.4 ns

19 ns

19 ns

9.5 ns

2.5 ns

9.5 ns

2.5 ns

38.4 ns

MAX7317

19 ns

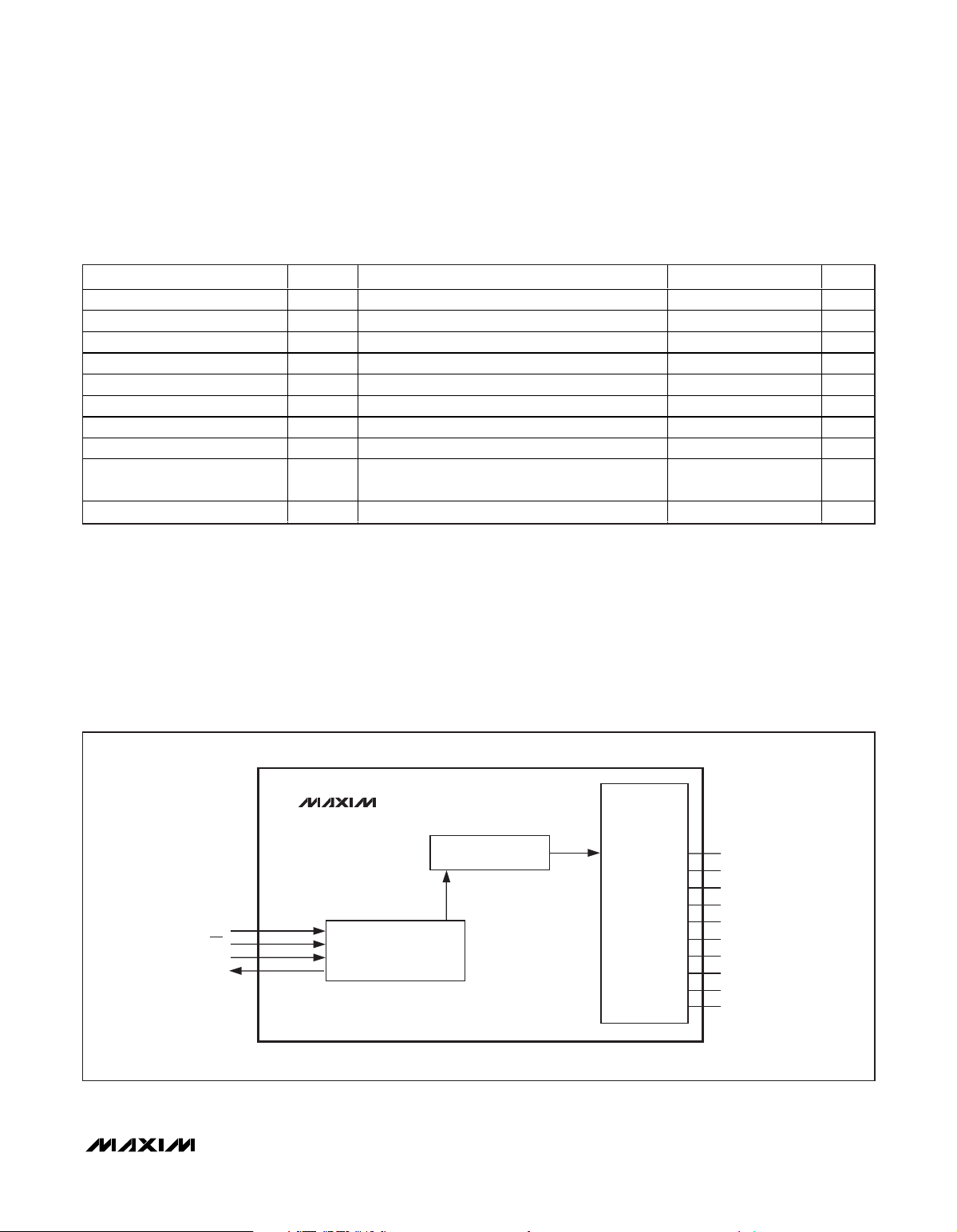

____________________________________________________________________

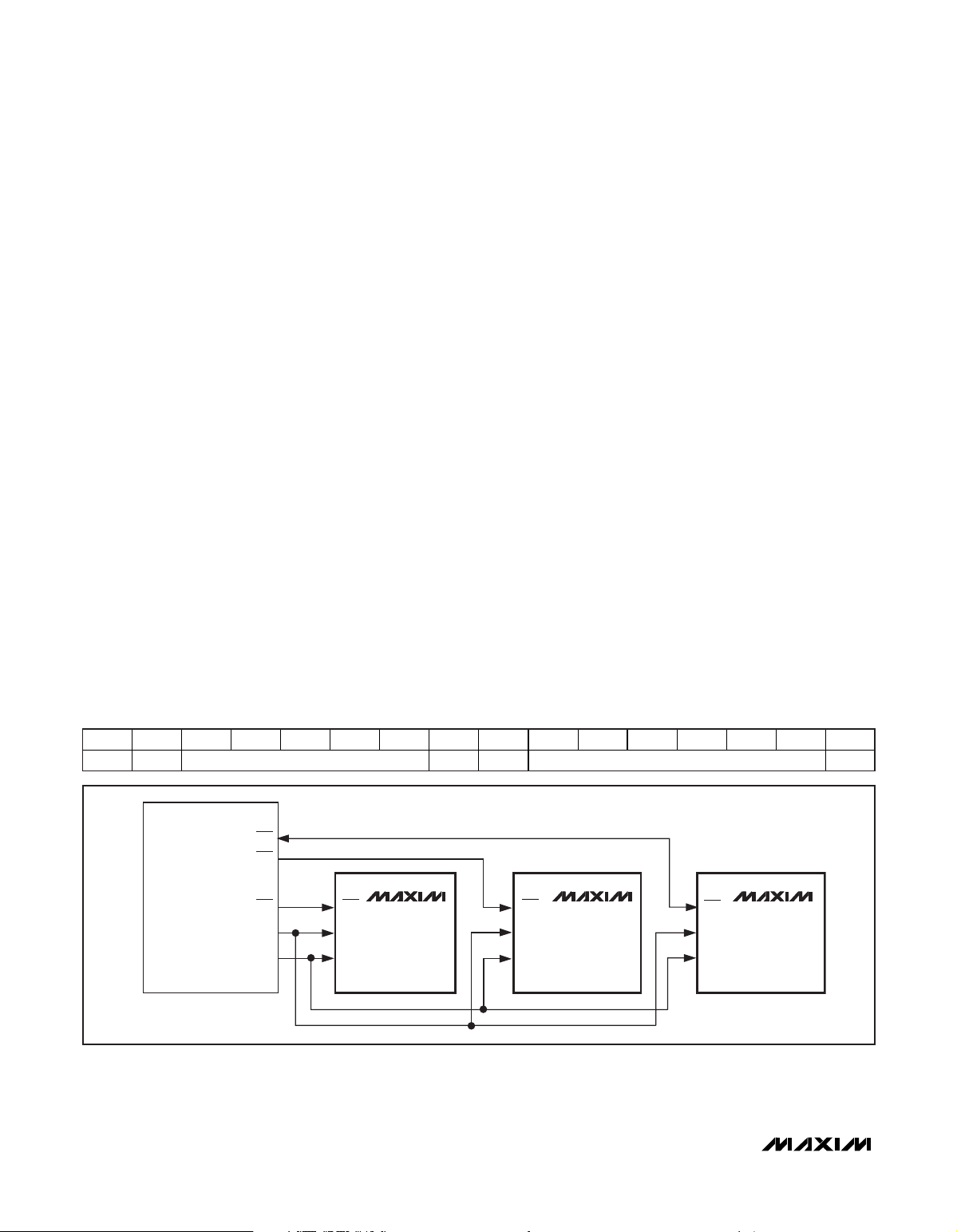

MAX7317

I/O REGISTER

I/O PORTS

SCLK

CS

DIN

DOUT

_______________________________________________________________________________________ 3

4-WIRE SERIAL INTERFACE

MAX7317方框图

P0

P1

P2

P3

P4

P5

P6

P7

P8

P9

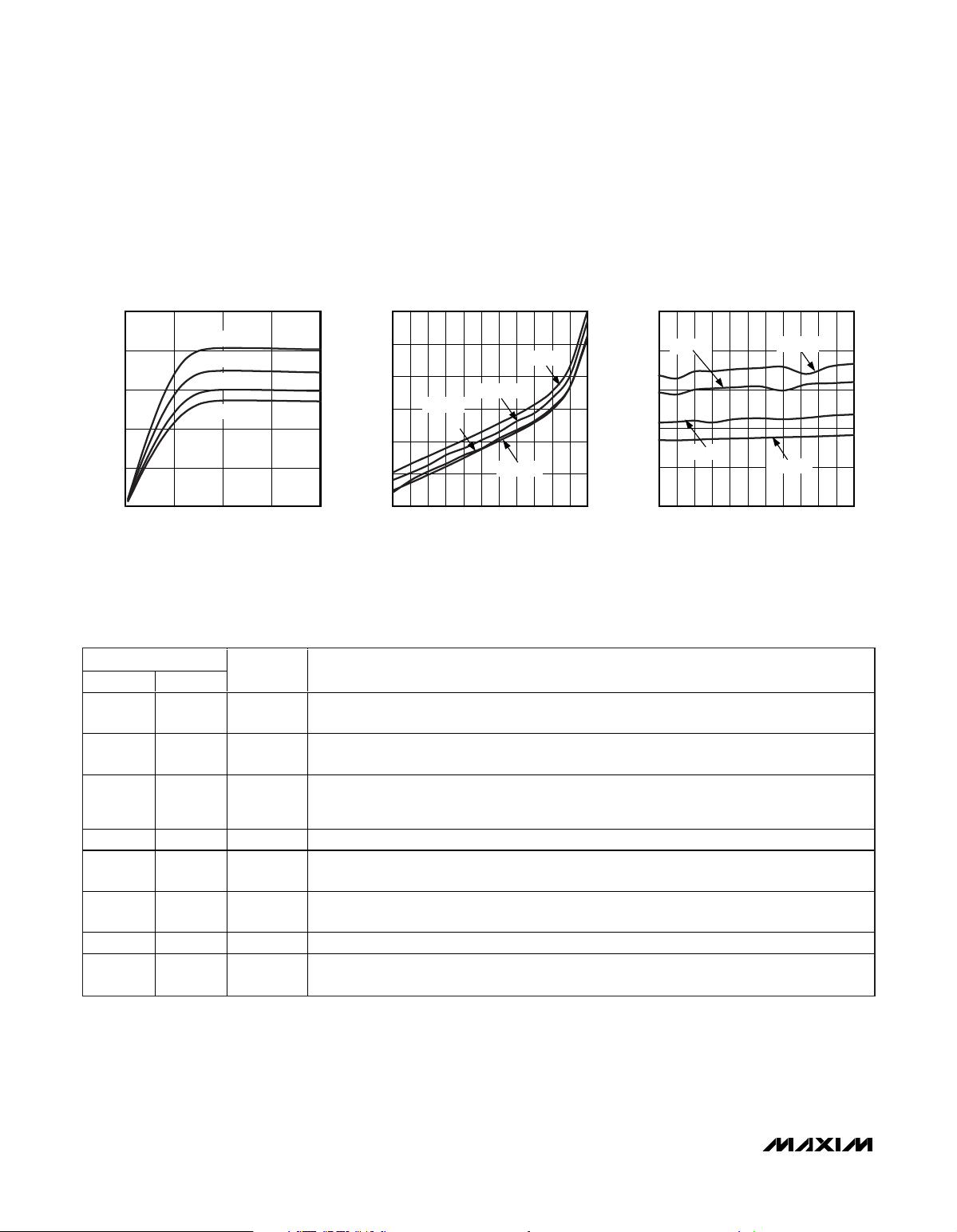

Page 4

10端口、SPI接口I/O扩展器,

0

3

9

6

12

15

PORT SINK CURRENT

vs. PORT VOLTAGE

MAX7317 toc01

PORT VOLTAGE (V)

PORT SINK CURRENT (mA)

04268

TA = -40°C

TA = +25°C

TA = +85°C

TA = +125°C

0.4

0.6

0.5

0.8

0.7

0.9

1.0

-40 -10 5 20-25 35 50 65 80 95 110 125

STANDBY CURRENT

vs. TEMPERATURE

MAX7317 toc02

TEMPERATURE (°C)

STANDBY CURRENT (µA)

V+ = 3.6V

V+ = 3.3V

V+ = 2.7V

V+ = 2.25V

0

0.1

0.3

0.2

0.4

0.5

-40 -10 5 20-25 35 50 65 80 95 110 125

SUPPLY CURRENT (I+)

vs. TEMPERATURE

MAX7317 toc03

TEMPERATURE (°C)

STANDBY CURRENT (mA)

V+ = 3.6V

V+ = 3.3V

V+ = 2.7V

V+ = 2.25V

具有过压和热插入保护

_______________________________________________________________________典型工作特性

(TA = +25°C, unless otherwise noted.)

MAX7317

___________________________________________________________________________

QSOP QFN

3–7, 9–13 1–5, 7–11 P0–P9

4 _______________________________________________________________________________________

引脚

PIN

1 15 SCLK

216CS

8 6 GND Ground

14 12 DOUT

15 13 DIN

16 14 V+ Positive Supply Voltage. Bypass V+ to GND with a 0.047µF ceramic capacitor.

— PAD

NAME FUNCTION

名称 功能

Serial-Clock Input. On SCLK’s rising edge, data shifts into the internal shift register. On

串行时钟输入。数据在SCLK 信号的上升沿移入内部移位寄存器。数据在SCLK信号的下降沿由

DOUT同步输出。只有在CS为低电平时SCLK 才有效。

SCLK’s falling edge, data is clocked out of DOUT. SCLK is active only while CS is low.

Chip-Select Input. Serial data is loaded into the shift register while CS is low. The most recent

片选输入。当CS为低电平时,串行数据装入移位寄存器。最后的16 位数据在CS信号的上升沿

锁存。

16 bits of data latch on CS’s rising edge.

I/O Ports. P0 to P9 can be configured as open-drain, current-sink outputs rated at 20mA

I/O端口。P0至P9 可以配置为开漏极输出,输出能吸收20mA 的最大额定电流,或者配置为CMOS

maximum, or as CMOS inputs, or as open-drain outputs. Loads should be connected to a

输入,或者开漏极输出。负载应接至不超过7V 的电源电压上。

supply voltage no higher than 7V.

地

Serial-Data Output. The data into DIN is valid at DOUT 15.5 clock cycles later. Use this pin to

串行数据输出。进入DIN 的数据经过15.5个时钟周期后在DOUT输出。使用该引脚可以以菊花链

daisy-chain several devices or allow data readback. Output is push-pull.

结构连接多个器件,或者允许数据回读。输出为推挽式结构。

Serial-Data Input. Data from DIN loads into the internal 16-bit shift register on SCLK’s rising

串行数据输入。数据在SCLK 信号的上升沿由DIN移入内部16位移位寄存器。

edge.

正电源电压。用0.047µF陶瓷电容将 V+ 旁路至 GND。

Exposed

裸露焊盘

pad

Exposed Pad on Package Underside. Connect to GND.

封装底部的裸露焊盘。接GND。

引脚说明

Page 5

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

________________________________

详细说明

MAX7317是一款通用的输入/输出 (GPIO) 外设器件,能

提供P0至P9共10个I/O端口,并通过高速SPI兼容串行接

口控制。10个I/O端口可用作输入或者漏极开路输出,并

能以任意形式组合。无论用作输入还是输出,端口都能

耐受7V电压,且与MAX7317的电源电压无关。

图1给出了MAX7317的I/O端口结构。

寄存器结构

MAX7317带有10个内部寄存器以控制外围设备 (表2),寄

存器地址为0x00至0x09。另外两个地址,0x0E和0x0F,不

存储数据,而是在读取时返回端口的输入状态。四个虚

拟地址,0x0A至0x0D,允许多个寄存器写入相同的数据,

从而简化软件设计。RAM寄存器提供1个字节的存储空间,

供用户使用。空操作地址,0x20,读取或者写入时不产生

任何操作。当从多个级联器件中访问一个MAX7317时,

可用作空寄存器。

初始上电

上电时,所有的控制寄存器均复位 (表2)。上电状态将I/O

端口P0至P9设置为高阻态,并使器件进入关断模式。

RAM寄存器

RAM寄存器提供一个字节的存储空间,可以任意使用。

10个寄存器,0x00至0x09,分别控制每个I/O端口 (表4)。

四个伪寄存器地址,0x0A至0x0D,通过将相同的数据写

入多个输出寄存器,可使用单个命令将成组的输出设置

为相同数值。

串行接口

MAX7317通过SPI兼容的4线串行接口通信。接口具有三

个输入:时钟 (SCLK)、片选 (CS)、数据输入 (DIN) 和数

据输出 (DOUT)。CS必须拉低以实现同步输入或输出数据。

并且,在SCLK的上升沿进行采样时DIN必须稳定。在

SCLK的上升沿DOUT是稳定的。

可用SCLK和DIN将数据传送至其它外设。除非CS为低电

平,否则MAX7317将忽略SCLK与DIN上的所有信号变化。

注意,在不访问MAX7317时,SPI协议要求DOUT保持高

阻态;MAX7317的DOUT并不是高阻态。如果需要,请

访问www.maxim-ic.com.cn/an1879,了解将MAX7317转换

为三态的方法。

利用4线接口进行控制和操作

控制MAX7317需要发送16位字。第一个字节D15至D8为

命令,第二个字节D7至D0为数据字节 (表5)。

MAX7317

GPIO端口方向配置

10个I/O端口P0至P9,可以配置为输入与输出的任意组

合。无论用作输入还是输出,端口均能耐受7V电压,与

MAX7317的电源电压无关。通过将端口的输出寄存器设

置为0x01,可把端口配置为输入,这同时将端口输出设

为高阻态 (表4)。

输入端口寄存器

读取输入端口寄存器将返回I/O端口引脚的逻辑电平。输

入端口寄存器为只读。对输入端口寄存器的写操作将被

忽略。

输出寄存器

MAX7317使用一个8位寄存器来控制每个输出端口 (表4)。

每个端口都可配置为输入或者漏极开路输出。将0x00写

入输出寄存器可将端口设置为逻辑低输出,写入0x01会

将端口设置为逻辑高输出或者逻辑输入。

_______________________________________________________________________________________ 5

OUTPUT

DATA FROM

SHIFT REGISTER

WRITE PULSE

READ PULSE

图1. I/O 端口的简化原理图

PORT REGISTER

D

CK

INPUT

PORT REGISTER

D

CK

FF

FF

Q

Q

Q

Q

OUTPUT PORT

REGISTER DATA

INPUT PORT

REGISTER DATA

I/O PIN

N

GND

Page 6

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

表1. 寄存器地址分配图

REGISTER

Port P0 output level R/W 0 0 0 0 0 0 0 0x00

Port P1 output level R/W 0 0 0 0 0 0 1 0x01

Port P2 output level R/W 0 0 0 0 0 1 0 0x02

MAX7317

Port P3 output level R/W 0 0 0 0 0 1 1 0x03

Port P4 output level R/W 0 0 0 0 1 0 0 0x04

Port P5 output level R/W 0 0 0 0 1 0 1 0x05

Port P6 output level R/W 0 0 0 0 1 1 0 0x06

Port P7 output level R/W 0 0 0 0 1 1 1 0x07

Port P8 output level R/W 0 0 0 1 0 0 0 0x08

Port P9 output level R/W 0 0 0 1 0 0 1 0x09

Write ports P0 through P9 with same output level 0

Read port P0 output level 1

Write ports P0 through P3 with same output level 0

Read port P0 output level 1

Write ports P4 through P7 with same output level 0

Read port P4 output level 1

Write ports P8 or P9 with same output level 0

Read port P8 output level 1

Read ports P7 through P0 inputs 1 0 0 0 1 1 1 0 0x0E

Read ports P9 and P8 inputs 1 0 0 0 1 1 1 1 0x0F

RAM R/W 0 0 1 0 0 1 1 0x13

No-op R/W 0 1 0 0 0 0 0 0x20

Factory reserved; do not write to this register R/W 1 1 1 1 1 0 1 0x7D

D15 D14 D13 D12 D11 D10 D9 D8

COMMAND ADDRESS

0 0 0 1 0 1 0 0x0A

0 0 0 1 0 1 1 0x0B

0 0 0 1 1 0 0 0x0C

0 0 0 1 1 0 1 0x0D

CODE

(hex)

表2. 初始上电的寄存器状态

ADDRESS

REGISTER POWER-UP CONDITION

Port P0 output level Port 0 high impedance 0x00 1 1 11111 1

Port P1 output level Port 1 high impedance 0x01 1 1 11111 1

Port P2 output level Port 2 high impedance 0x02 1 1 11111 1

Port P3 output level Port 3 high impedance 0x03 1 1 11111 1

Port P4 output level Port 4 high impedance 0x04 1 1 11111 1

Port P5 output level Port 5 high impedance 0x05 1 1 11111 1

Port P6 output level Port 6 high impedance 0x06 1 1 11111 1

Port P7 output level Port 7 high impedance 0x07 1 1 11111 1

Port P8 output level Port 8 high impedance 0x08 1 1 11111 1

Port P9 output level Port 9 high impedance 0x09 1 1 11111 1

RAM 0x00 0x13 0 0 00000 0

6 _______________________________________________________________________________________

CODE

(hex)

D7 D6 D5 D4 D3 D2 D1 D0

REGISTER DATA

Page 7

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

4线总线上挂接多个MAX7317

可以将多个MAX7317挂接在同一SPI总线,这时,需将

MAX7317 器件提供独立的CS信号 (图2)。无论DOUT/OSC

如何配置,这种连接都能工作,但是不允许读取MAX7317。

各DIN输入接到一起,各SCLK输入接到一起,并为每个

表3. 输入端口寄存器

ADDRESS

REGISTER R/W

Read input ports P7–P0 1 0X0E

Read input ports P9, P8 1 0X0F 0 0 0 0 0 0

CODE

(hex)

D7 D6 D5 D4 D3 D2 D1 D0

PortP7PortP6PortP5PortP4PortP3PortP2PortP1Port

REGISTER DATA

PortP9Port

表4. 输出寄存器格式

ADDRESS

CODE

(hex)

Port P0 level — MSB Output P0 level and PWM LSB

Port P0 is open-drain logic low — 000000000x00

Port P0 is open-drain logic high (high

impedance without external pullup) or

logic input

—

0x00

D7 D6 D5 D4 D3 D2 D1 D0

000000010x01

REGISTER DATA

BINARYREGISTER R/W

hex

MAX7317

P0

P8

Port P1 level — 0x01 MSB Port P1 level LSB

Port P2 level — 0x02 MSB Port P2 level LSB

Port P3 level — 0x03 MSB Port P3 level LSB

Port P4 level —- 0x04 MSB Port P4 level LSB

Port P5 level — 0x05 MSB Port P5 level LSB

Port P6 level — 0x06 MSB Port P6 level LSB

Port P7 level — 0x07 MSB Port P7 level LSB

Port P8 level — 0x08 MSB Port P8 level LSB

Port P9 level — 0x09 MSB Port P9 level LSB

Writes ports P0 through P9

with same level

Reads port P0 level 1

Writes ports P0 through P3

with same level

Reads port P0 level 1

Writes ports P4 through P7

with same level

Reads port P4 level 1

Write ports P8 and P9 with same level 0 MSB Ports P8, P9 level LSB

Read port P8 level 1

_______________________________________________________________________________________ 7

0 MSB Ports P0 through P9 level LSB

0 MSB Ports P0 through P3 level LSB

0 MSB Ports P4 through P7 level LSB

0x0A

0x0B

0x0C

0x0D

MSB Port P0 level LSB

MSB Port P0 level LSB

MSB Port P4 level LSB

MSB Port P8 level LSB

0x00

or

0x01

Page 8

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

还有一种选择方案,通过将一个器件的DOUT接至下一

个器件的DIN,且并行驱动SCLK与CS(图3),可以实现

MAX7317的菊花链连接。这种连接方式允许读取MAX7317。

DIN上的数据通过内部移位寄存器传送,15.5个时钟周期

后数据出现在DOUT上,并在SCLK的下降沿同步输出。

当发送命令至菊花链连接的MAX7317时,同时访问所有

器件。一次访问需要 (16 x n) 个时钟周期,其中n为所连

MAX7317

接的MAX7317数目。当多个器件采用菊花链连接时,由

于DOUT的传输延迟和DIN建立时间的影响,串行接口的

速度 (最大SCLK) 限制为10MHz。

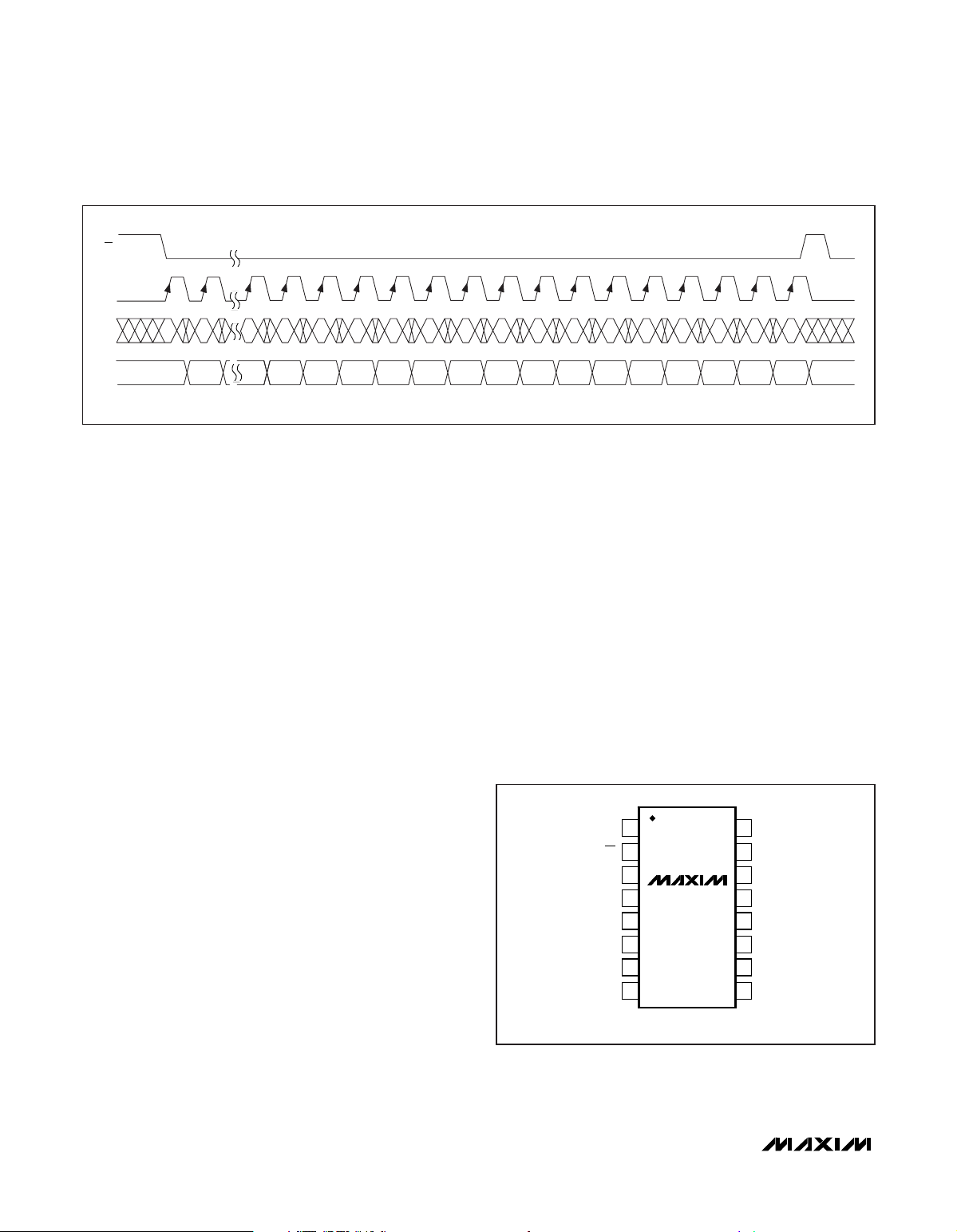

采用以下时序写入MAX7317 (图5):

1) 拉低SCLK。

2) 拉低CS。这会使能内部16位移位寄存器。

3) 16位数据同步输入到DIN,最先发送D15,最后发送

D0,注意建立和保持时间。D15为低,表示写命令。

4) 拉高CS(最后一个数据位同步输入后SCLK仍为高电平

时,或者拉低SCLK之后)。

5) 拉低 SCLK (如果尚未拉低)。

如果在拉低CS与重新拉高CS之间,有少于或多于16位数

据同步输入到MAX7317,MAX7317会存储最后接收的16

位数据,包括以前发送的数据。通常的情况是,n位 (其

中n > 16) 数据传送到MAX7317。包括 {n-15} 至{n}的最

后数据位将会保留,且相应装入16位锁存器的D15至D0

位 (图6)。

读取器件寄存器

MAX7317内的任何寄存器数据都可以通过发送逻辑高至

D15位进行读取。其时序为:

1) 拉低SCLK。

2) 拉低CS。这可使能内部16位移位寄存器。

3) 同步输入16位数据至DIN,最先发送D15,最后发送D0。

D15位为高电平,表示读命令。D14至D8包含所要读的

寄存器地址。D7至D0位为无效数据,将被丢弃。

4) 拉高CS(最后的数据位同步输入后SCLK仍为高电平

时,或者拉低SCLK之后)。此时,移位寄存器的D7至

D0位装入D15至D8所寻址的寄存器数据。

5) 拉低SCLK (如果尚未拉低)。

6) 发出另一个读或者写命令,检查DOUT比特流;第二个

8位为步骤3中D14至D8位所寻址的寄存器的内容。

表5. 串行数据格式

D15 D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

R/ W MSB ADDRESS LSB MSB DATA LSB

CS3

CS2

µC

图2. MAX7317 多CS线连接

8 _______________________________________________________________________________________

CS1

MOSI

SCLK

CS1

DIN

SCLK

CS2

DIN

SCLK

CS3

DIN

SCLK

MAX7317MAX7317MAX7317

Page 9

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

MAX7317

MOSI

SCLK

µC

MISO

图3. MAX7317 菊花链连接

CS

SCLK

DIN DOUT DOUT

CS CS CS CS

SCLK

t

CL

t

CSS

t

DS

t

DH

t

CH

SCLK

MAX7317MAX7317

t

CSW

t

t

CP

CSH

DOUTDIN DIN

MAX7317

SCLK

DIN

DOUT

图4. 时序图

CS

SCLK

DIN

DOUT

D15

D14 D13 D12 D11 D10 D9 D8 D7 D6 D5 D4 D3 D2 D1 D0

= 0

图5. 16 位写操作发送至MAX7317

_______________________________________________________________________________________ 9

D1D14D15

.

D0

t

DO

D15

D15 = 0

Page 10

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

CS

SCLK

DIN

MAX7317

BIT1BIT

N-15

2

N-14 N-13 N-12 N-11 N-10 N-9 N-8 N-7 N-6 N-5 N-4 N-3 N-2 N-1 N

DOUT

图6. 向 MAX7317发送超过16位数据

________________________________

N-31 N-30 N-29 N-28 N-27 N-26 N-25 N-24 N-23 N-22 N-21 N-20 N-19 N-18 N-17 N-16

应用信息

热插入

当 MAX7317断电 (V+ = 0V) 时,I/O端口P0–P9保持高阻

态,最高能接受8V的电压。因此,MAX7317可用于热插

拔系统。

SPI布线考虑

在2.5V电源下,MAX7317的SPI接口能确保工作于26Mbps,

3.3V供电时通常可工作于35Mbps。这意味着,当接口连

接超过100mm时,应该考虑传输线问题,尤其对于较高

的电源电压更是如此。在没有GND引线隔离的情况下,

应避免相邻的SCLK、DIN以及CS覆铜线的长距离走线;

否则,信号会产生交叉耦合,从而导致错误的时钟或片

选信号。振铃会引起间歇性的通讯问题,这通常是SCLK

输入端振铃产生的双时钟造成的。在DIN、SCLK和CS输

入端与GND或者V+之间接入1kΩ至10kΩ的终端电阻,以

衰减较长的接口引线的振铃。板间互连时,采用传输线

终端阻抗匹配。

输出电平转换

漏极开路输出结构允许将端口输出电平转换为比MAX7317

电源更高或者更低的电平。外部上拉电阻可用于任何输

出端口,将高阻抗的逻辑高电平转换为正电压电平。该

电阻可以接至不高于7V的任意电压。当在恒定电流输出

上使用上拉时,选择适当的电阻值以在逻辑低条件下吸

收不超过几百µA的电流。这可以确保输出饱和且接近于

GND。连接CMOS输入时,220kΩ的上拉电阻值是一个合

.

适的起始点。在功耗问题并不突出,或者对于给定的容

性负载需要更快上升时间的应用中,使用较低的电阻可

以改善噪声抑制。

电源考虑

MAX7317工作于2.25V至3.6V电源电压。用一个尽可能靠

近器件的0.047µF陶瓷电容将电源旁路至GND。对于QFN

封装,底部的裸露焊盘接至GND。

________________________________

TRANSISTOR COUNT: 14,865

PROCESS: BiCMOS

____________________________

TOP VIEW

SCLK

GND

CS

P0

P1

P2

P3

P4

1

2

3

MAX7317AEE

4

5

6

7

8

QSOP

16

15

14

13

12

11

10

9

芯片信息

引脚配置 (续)

V+

DIN

DOUT

P9

P8

P7

P6

P5

10 ______________________________________________________________________________________

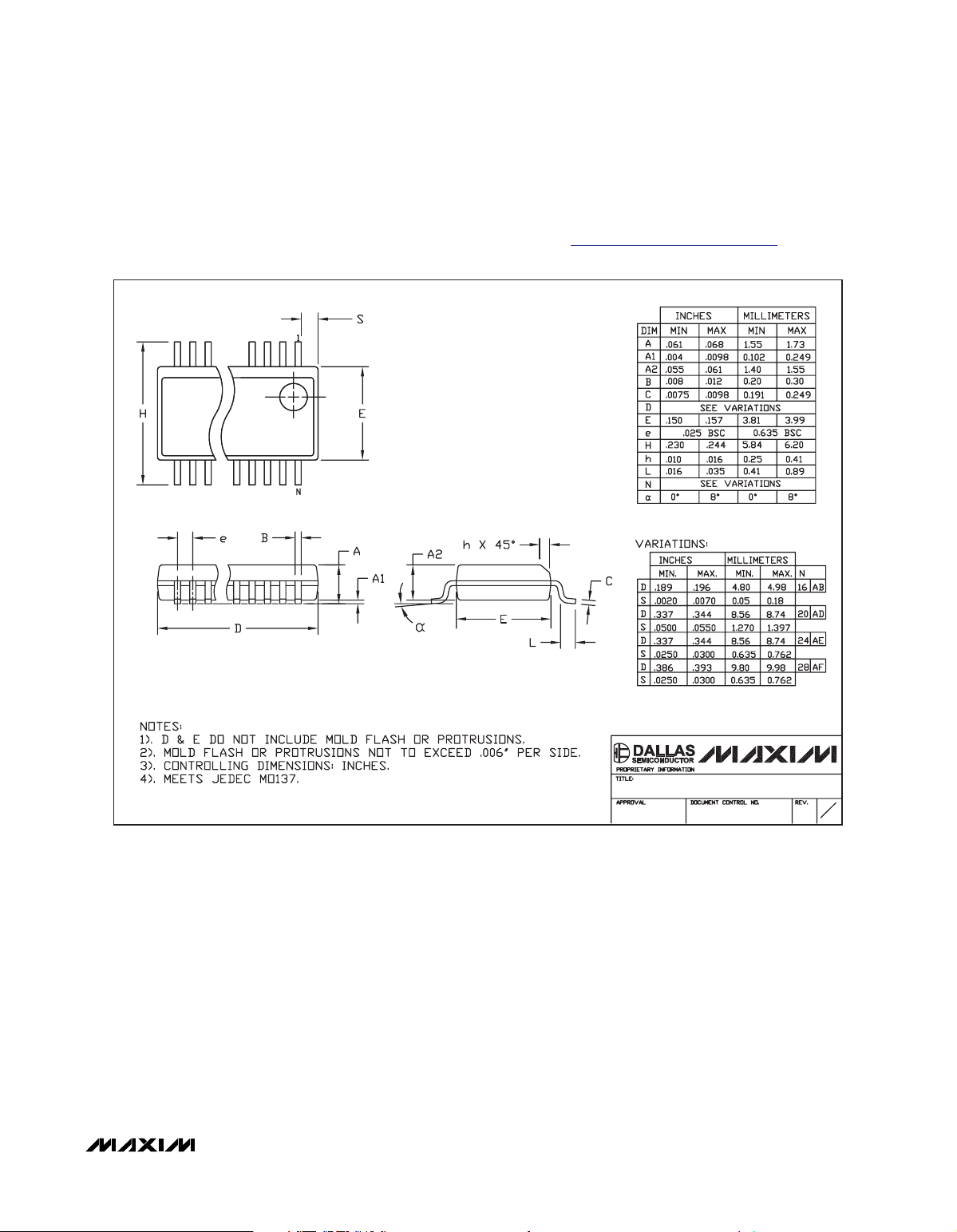

Page 11

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

____________________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

MAX7317

封装信息

QSOP.EPS

PACKAGE OUTLINE, QSOP .150", .025" LEAD PITCH

1

21-0055

______________________________________________________________________________________ 11

E

1

Page 12

10端口、SPI接口I/O扩展器,

具有过压和热插入保护

______________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

D2

b

0.10 M

MAX7317

C

L

0.10 C 0.08 C

D

D/2

E/2

E

C

L

A

A2

A1

(NE - 1) X e

L

D2/2

e

C

L

e

PACKAGE OUTLINE

12, 16L, THIN QFN, 3x3x0.8mm

E2/2

k

(ND - 1) X e

C

L

e

21-0136

C A B

E2

L

L

1

E

2

封装信息 (续)

12x16L QFN THIN.EPS

PKG

12L 3x3

REF. MIN.

NOM. MAX. NOM.

0.70

0.75

A

b

0.20

0.25

D

2.90

3.00

3.00

2.90

E

e

0.50 BSC.

0.55

0.45

L

N

12

ND

NE

3

0.0230.05

A1

0

A2

0.20 REF

-

0.25

k

NOTES:

1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994.

2. ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

3. N IS THE TOTAL NUMBER OF TERMINALS.

4. THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO

JESD 95-1 SPP-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED

WITHIN THE ZONE INDICATED. THE TERMINAL #1 IDENTIFIER MAY BE EITHER A MOLD OR

MARKED FEATURE.

5. DIMENSION b APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.20 mm AND 0.25 mm

FROM TERMINAL TIP.

6. ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

7. DEPOPULATION IS POSSIBLE IN A SYMMETRICAL FASHION.

8. COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220 REVISION C.

MIN. MAX.

0.80

0.70

0.30

0.20

3.10

2.90

2.90

3.10

0.30

0.65

0

-

0.25

16L 3x3

0.75

0.25

3.00

3.00

0.50 BSC.

0.40

16

4

4

0.02

0.20 REF

-

0.80

0.30

3.10

3.10

0.50

0.05

-

PKG.

CODES

T1233-1

T1233-3

T1633-1 0.95

T1633-2

T1633F-3 0.65

T1633-4

EXPOSED PAD VARIATIONS

D2

MAX.

NOM.

1.10

1.10

1.10

1.10

0.80

1.10

MIN.

1.25

0.95

1.25

0.95 1.10

1.25

0.95

1.25

0.95

0.95

0.65

1.25

0.95

MIN.

0.95

0.95

0.95

0.95

E2

PIN ID

NOM.

MAX.

1.10

1.25

0.35 x 45∞

0.35 x 45∞1.25 WEED-1

1.25

1.10

0.35 x 45∞ WEED-2

1.25

1.10

0.35 x 45∞

0.95

0.80

0.225 x 45∞

1.25

1.10

0.35 x 45∞

PACKAGE OUTLINE

12, 16L, THIN QFN, 3x3x0.8mm

JEDEC

WEED-1

WEED-2

WEED-2

WEED-2

21-0136

DOWN

BONDS

ALLOWED

NO

YES

NO

YES

N/A

NO

2

E

2

Maxim不对 Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

12 __________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 2005 Maxim Integrated Products Printed USA

是

Maxim Integrated Products, Inc.

的注册商标。

Loading...

Loading...