_______________General Description

The MAX509/MAX510 are quad, serial-input, 8-bit voltage-output digital-to-analog converters (DACs). They

operate with a single +5V supply or dual ±5V supplies.

Internal, precision buffers swing rail-to-rail. The reference input range includes both supply rails.

The MAX509 has four separate reference inputs, allowing each DAC's full-scale range to be set independently.

20-pin DIP, SSOP, and SO packages are available. The

MAX510 is identical to the MAX509 except it has two reference inputs, each shared by two DACs. The MAX510

is housed in space-saving 16-pin DIP and SO packages.

The serial interface is double-buffered: A 12-bit input

shift register is followed by four 8-bit buffer registers and

four 8-bit DAC registers. A 12-bit serial word is used to

load data into each register. Both input and DAC registers can be updated independently or simultaneously

with single software commands. Two additional asynchronous control pins provide simultaneous updating

(LDAC) or clearing (CLR) of input and DAC registers.

The interface is compatible with MicrowireTMand SPI/

QSPITM. All digital inputs and outputs are TTL/CMOS

compatible. A buffered data output provides for readback or daisy-chaining of serial devices.

____________________________Features

♦ Single +5V or Dual ±5V Supply Operation

♦ Output Buffer Amplifiers Swing Rail-to-Rail

♦ Reference Input Range Includes Both Supply Rails

♦ Calibrated Offset, Gain, and Linearity (1LSB TUE)

♦ 10MHz Serial Interface, Compatible with SPI, QSPI

(CPOL = CPHA = 0) and Microwire

♦ Double-Buffered Registers for Synchronous

Updating

♦ Serial Data Output for Daisy-Chaining

♦ Power-On Reset Clears Serial Interface and Sets

All Registers to Zero

______________Ordering Information

Ordering Information continued on last page.

* Dice are specified at +25°C, DC parameters only.

**Contact factory for availability and processing to MIL-STD-883.

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

________________________________________________________________

Maxim Integrated Products

1

20

19

18

17

16

15

14

13

12

11

1

2

3

4

5

6

7

8

9

10

OUTC

OUTD

V

DD

REFC

REFB

V

SS

OUTA

OUTB

TOP VIEW

MAX509

REFD

CS

N.C.

SCLK

DGND

N.C.

AGND

REFA

DIN

CLR

DOUT

LDAC

DIP/SO/SSOP

_________________Pin Configurations

MAX509

OUTA

DAC A

DAC B

DAC C

DAC D

REFAREFB

DAC

REG A

DECODE

CONTROL

INPUT

REG A

DAC

REG B

INPUT

REG B

DAC

REG C

INPUT

REG C

DAC

REG D

INPUT

REG D

12-BIT

SHIFT

REGISTER

SR

CONTROL

CS DIN

SCLK REFC

REFD

OUTB

OUTC

OUTD

DOUT

LDAC

CLR

V

DD

DGND

V

SS

AGND

_______________Functional Diagrams

19-0155; Rev 2; 1/96

PART TEMP. RANGE PIN-PACKAGE

MAX509ACPP

0°C to +70°C 20 Plastic DIP

MAX509BCPP 0°C to +70°C 20 Plastic DIP

MAX509ACWP 0°C to +70°C 20 Wide SO

±1

±1 1/2

±1

MAX509BCWP 20 Wide SO ±1 1/2

MAX509ACAP 0°C to +70°C 20 SSOP ±1

0°C to +70°C

MAX509BCAP 0°C to +70°C 20 SSOP ±1 1/2

MAX509BC/D 0°C to +70°C Dice* ±1 1/2

Pin Configurations continued at end of data sheet.

Functional Diagrams continued at end of data sheet.

TUE

(LSB)

Microwire is a trademark of National Semiconductor. SPI and QSPI are trademarks of Motorola.

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

2 _______________________________________________________________________________________

VDDto DGND ..............................................................-0.3V, +6V

V

DD

to AGND...............................................................-0.3V, +6V

V

SS

to DGND...............................................................-6V, +0.3V

V

SS

to AGND...............................................................-6V, +0.3V

V

DD

to VSS.................................................................-0.3V, +12V

Digital Input Voltage to DGND ......................-0.3V, (V

DD

+ 0.3V)

REF_....................................................(V

SS

- 0.3V), (VDD+ 0.3V)

OUT_..............................................................................V

DD

, V

SS

Maximum Current into Any Pin............................................50mA

Continuous Power Dissipation (T

A

= +70°C)

16-Pin Plastic DIP (derate 10.53mW/°C above +70°C)....842mW

16-Pin Wide SO (derate 9.52mW/°C above +70°C).........762mW

16-Pin CERDIP (derate 10.00mW/°C above +70°C) ........800mW

20-Pin Plastic DIP (derate 11.11mW/°C above +70°C)....889mW

20-Pin Wide SO (derate 10.00mW/°C above +70°C).......800mW

20-Pin SSOP (derate 10.00mW/°C above +70°C)............800mW

20-Pin CERDIP (derate 11.11mW/°C above +70°C) ........889mW

Operating Temperature Ranges:

MAX5_ _ _C_ _.....................................................0°C to +70°C

MAX5_ _ _E_ _..................................................-40°C to +85°C

MAX5_ _ _MJ_ ................................................-55°C to +125°C

Storage Temperature Range.............................-65°C to +150°C

Lead Temperature (soldering, 10sec).............................+300°C

ELECTRICAL CHARACTERISTICS

(VDD= +5V ±10%, VSS= 0V to -5.5V, V

REF

= 4V, AGND = DGND = 0V, RL= 10kΩ, CL= 100pF, TA= T

MIN

to T

MAX

,

unless otherwise noted.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

PARAMETER CONDITIONS MIN TYP MAX UNITS

Note: The outputs may be shorted to VDD, VSS, or AGND if the package power dissipation is not exceeded. Typical short-circuitcurrent

to AGND is 50mA. Do not bias AGND more than +1V above DGND, or more than 2.5V below DGND.

ABSOLUTE MAXIMUM RATINGS

Resolution 8 Bits

±1MAX5_ _A

VREF = +4V,

VSS= 0V or -5V ±10%

MAX5_ _B

±1MAX5_ _A

Total Unadjusted Error

VREF = -4V,

VSS= -5V ±10%

±1.5

LSB

Differential Nonlinearity ±1 LSBGuaranteed monotonic

14MAX5_ _C

16MAX5_ _E

MAX5_ _B

±10 µV/°CCode = FF hex

14MAX5_ _C

Full-Scale Error ±14 mVCode = FF hex

±10 µV/°CCode = 00 hex

Zero-Code-Error Supply Rejection 12mV

Code = 00 hex,

VSS= 0V

20MAX5_ _M

SYMBOL

TUE

DNL

±14MAX5_ _C

±16MAX5_ _E

Zero-Code Error

Code = 00 hex,

VSS= -5V ±10%

±20

mV

MAX5_ _M

ZCE

±1.5

Code = 00 hex, VDD= 5V ±10%,

V

SS

= 0V or -5V ±10%

Zero-Code

Temperature Coefficient

18MAX5_ _E

Full-Scale-Error Supply Rejection

Code = FF hex,

VDD= +5V ±10%,

VSS= 0V or -5V ±10%

112

mV

MAX5_ _M

Full-Scale-Error

Temperature Coefficient

STATIC ACCURACY

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

_______________________________________________________________________________________ 3

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +5V ±10%, VSS= 0V to -5.5V, V

REF

= 4V, AGND = DGND = 0V, RL= 10kΩ, CL= 100pF, TA= T

MIN

to T

MAX

,

unless otherwise noted.)

PARAMETER

CONDITIONS MIN TYP MAX UNITS

Input Voltage Range

SYMBOL

V

SS

V

DD

V

MAX509 16 24

MAX510

Input Resistance (Note 1)

812

kΩCode = 55 hex

MAX509 15

(Note 4)AC Feedthrough -70 dB

(Note 3)Channel-to-Channel Isolation -60 dB

MAX510

Input Capacitance (Note 2)

30

pFCode = 00 hex

10

2

VREF = 4V, load regulation ≤ 1/4LSB 2

Full-Scale Output Voltage V

SS

V

DD

V

Resistive Load

10

kΩ

Input High Voltage 2.4 VV

IH

VREF = -4V, V

SS

= -5V ±10%,

load regulation ≤ 1/4LSB

VREF = VDDMAX5_ _C/E,

load regulation ≤ 1LSB

VREF = VDDMAX5_ _M,

load regulation ≤ 2LSB

Input Low Voltage 0.8 VV

IL

VIN= 0V or V

DD

Input Current 1.0 µAI

IN

(Note 5)Input Capacitance 10 pFC

IN

I

SOURCE

= 0.2mAOutput High Voltage VDD- 0.5 VV

OH

I

SINK

= 1.6mAOutput Low Voltage 0.4 VV

OL

MAX5_ _E 0.7

MAX5_ _C 1.0

MAX5_ _M

Voltage-Output Slew Rate

0.5

V/µsPositive and negative

To 1/2LSB, 10kΩ II 100pF loadOutput Settling Time (Note 6) 6 µs

Digital Feedthrough 5 nV-s

Wideband Amplifier Noise 60

MHzVREF = 0.5V

p-p

, 3dB bandwidthMultiplying Bandwidth 1

VREF = 4V

p-p

at 1kHz, VDD= 5V,

code = FF hex

Digital-to-Analog Glitch Impulse

87

Code 128➝127

12 nV-s

Code = 00 hex, all digital inputs

from 0V to V

DD

Signal-to-Noise + Distortion Ratio

VREF = 4V

p-p

at 20kHz, VSS= -5V ±10% 74

dBSINAD

µV

RMS

REFERENCE INPUTS

DAC OUTPUTS

DIGITAL INPUTS

DIGITAL OUTPUTS

DYNAMIC PERFORMANCE

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

4 _______________________________________________________________________________________

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +5V ±10%, VSS= 0V to -5.5V, V

REF

= 4V, AGND = DGND = 0V, RL= 10kΩ, CL= 100pF, TA= T

MIN

to T

MAX

,

unless otherwise noted.)

PARAMETER CONDITIONS MIN TYP MAX UNITS

Positive Supply Voltage

SYMBOL

4.5 5.5 VFor specified performanceV

DD

Negative Supply Voltage -5.5 0 VFor specified performanceV

SS

510

Positive Supply Current

512

mAI

DD

Negative Supply Current mAI

SS

510

MAX5_ _C/E

MAX5_ _M

MAX5_ _C/E

512MAX5_ _M

VSS= -5V ±10%, outputs

unloaded, all digital

inputs = 0V or V

DD

Note 1: Input resistance is code dependent. The lowest input resistance occurs at code = 55 hex.

Note 2: Input capacitance is code dependent. The highest input capacitance occurs at code = 00 hex.

Note 3: VREF = 4V

p-p

, 10kHz. Channel-to-channel isolation is measured by setting the code of one DAC to FF hex and setting the

code of all other DACs to 00 hex.

Note 4: VREF = 4V

p-p

, 10kHz. DAC code = 00 hex.

Note 5: Guaranteed by design.

Note 6: Output settling time is measured by taking the code from 00 hex to FF hex, and from FF hex to 00 hex.

TIMING CHARACTERISTICS

(VDD= +5V ±10%, VSS= 0V to -5V, V

REF

= 4V, AGND = DGND = 0V, CL= 50pF, TA= T

MIN

to T

MAX

, unless otherwise noted.)

PARAMETER

CONDITIONS MIN TYP MAX UNITS

CLR Pulse Width Low

SYMBOL

50 25

ns

MAX5_ _M

MAX5_ _C/E 40 20

t

CLW

MAX5_ _M 50 25

ns

MAX5_ _C/E 40 20

SCLK Fall to CS Rise Hold Time

0 nst

CSH2

SCLK Fall to CS Fall Hold Time

0 ns(Note 7)t

CSH0

40MAX5_ _C/E

10 100MAX5_ _C/E

MAX5_ _C/E 40

40MAX5_ _C/E

20 12.5MAX5_ _C/E

DIN to SCLK Rise Hold Time 0 nst

DH

SCLK Rise to CS Rise Hold Time

(Note 9) 40 nst

CSH1

LDAC Pulse Width Low

(Notes 7, 8) 0 ns

t

LDW

t

CLL

CS Rise to LDAC Fall Setup Time

40MAX5_ _C/E

CS Fall to SCLK Setup Time

50

ns

MAX5_ _M

t

CSS

DIN to SCLK Rise Setup Time

50

ns

MAX5_ _M

t

DS

SCLK Clock Frequency

20 10

MHz

MAX5_ _M

f

CLK

SCLK Pulse Width High

50

ns

MAX5_ _M

t

CH

SCLK Pulse Width Low

MAX5_ _M 50

nst

CL

SCLK to DOUT Valid

10 100

ns

MAX5_ _M

t

DO

Note 7: Guaranteed by design.

Note 8: If LDAC is activated prior to CS's rising edge, it must stay low for t

LDW

or longer after CS goes high.

Note 9: Minimum delay from 12th clock cycle to CS rise.

Outputs unloaded, all

digital inputs = 0V or V

DD

POWER SUPPLIES

SERIAL INTERFACE TIMING

MAX509/MAX510

Quad, Serial 8-Bit DACs

with Rail-to-Rail Outputs

_______________________________________________________________________________________

5

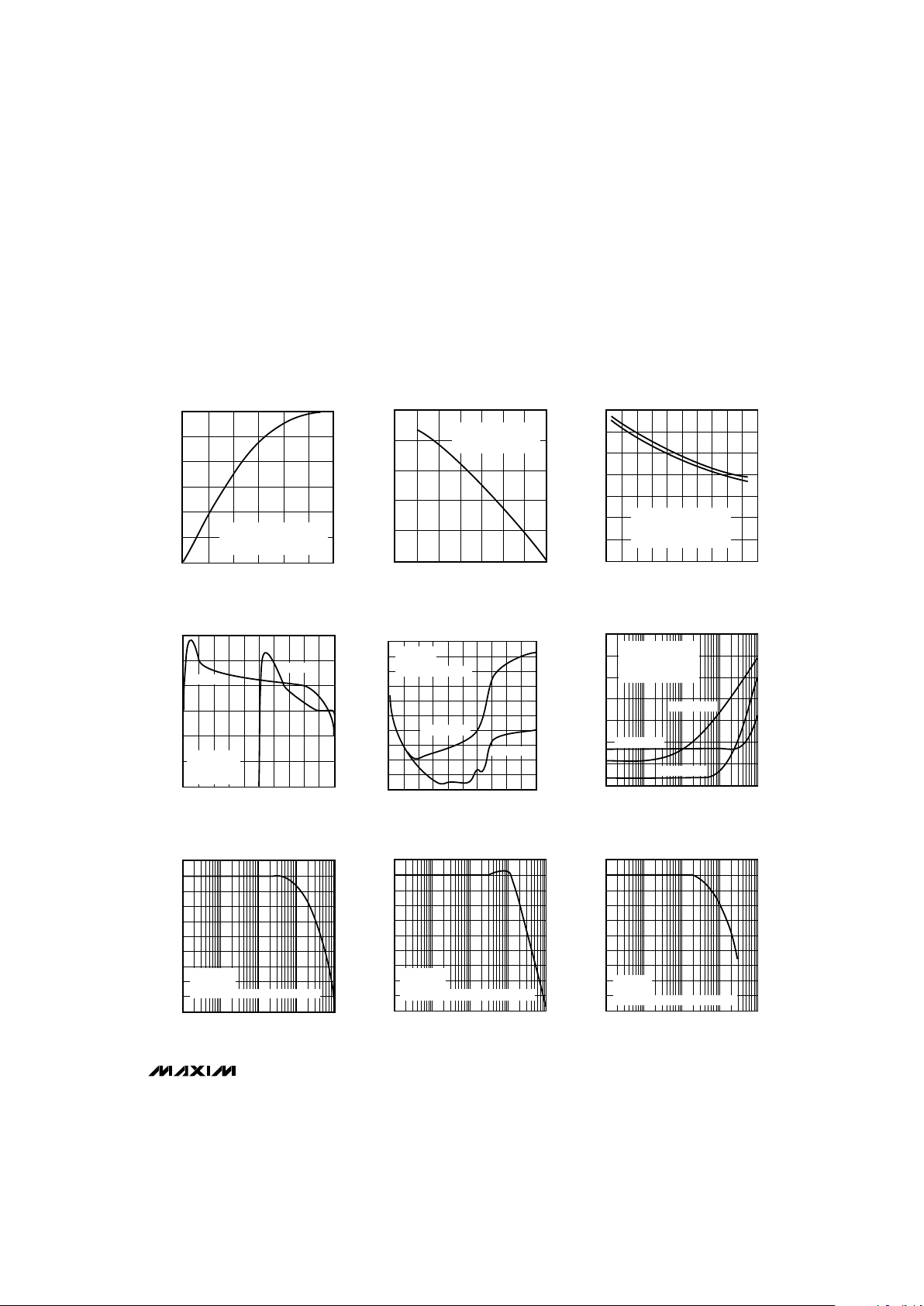

12

0

0 1.2

OUTPUT SINK CURRENT

vs. (V

OUT

- VSS)

2

10

MAX509-FG01

V

OUT

- VSS (V)

I

OUT

(mA)

0.8

6

4

0.2 0.6 1.0

8

0.4

VDD = VREF = +5V

V

SS

= GND = 0V

ALL DIGITAL INPUTS = 00 HEX

-25

0

3.6 4.6

-20

MAX509-FG10

V

OUT

(V)

I

OUT

(mA)

4.4

-10

-5

3.8 4.0

-15

OUTPUT SOURCE CURRENT

vs. OUTPUT VOLTAGE

4.8

5.0

4.2

VDD = VREF = +5V

V

SS

= GND

DIGITAL INPUT = FF HEX

7

0

-60 -20 40 100

SUPPLY CURRENT

vs. TEMPERATURE

2

6

MAX509-FG02

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

20 80

4

5

3

1

-40 0 60 120

140

I

DD

I

SS

VDD = +5.5V

V

SS

= -5.5V

VREF = -4.75

ALL DIGITAL INPUTS = +5V

6

0

-5 5

SUPPLY CURRENT

vs. REFERENCE VOLTAGE

1

5

MAX509-FG03

VREF VOLTAGE (V)

I

DD

(mA)

0

3

2

-4 -2 2

4

431-1-3

VDD = +5V

ALL LOGIC

INPUTS = +5V

VSS = -5V

VSS = 0V

0

1k 10k 100k

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

-40

MAX509-FG06

FREQUENCY (Hz)

RELATIVE OUTPUT (dB)

-30

-20

-10

1M

10M

VDD = +5V

V

SS

= AGND

VREF = 2.5VDC + 0.5Vp-p SINE WAVE

-40

-90

02 6 10

THD + NOISE AT DAC OUTPUT

vs. REFERENCE AMPLITUDE

-80

-50

MAX509-FG04

REFERENCE AMPLITUDE (Vp-p)

THD + NOISE (dB)

48

-60

-70

-85

-75

-65

-55

-45

1%

0.01%

0.1%

FREQ = 20kHz

FREQ = 1kHz

VDD = +5V

V

SS

= -5V

INPUT CODE = FF HEX

THD + NOISE (%)

-20

-80

10 1k 100k

THD + NOISE AT DAC OUTPUT

vs. REFERENCE FREQUENCY

-70

MAX509-FG05

REFERENCE FREQUENCY (Hz)

THD + NOISE (dB)

-60

-50

-40

-90

-30

100 10k

VREF = 8Vp-p

VREF = 1Vp-p

VREF = 4Vp-p

VDD = +5V

V

SS

= -5V

INPUT CODE = FF HEX

FREQ = SWEPT

10%

1%

0.1%

0.01%

THD + NOISE (%)

0

1k 10k 100k

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

-40

MAX509-FG07

FREQUENCY (Hz)

RELATIVE OUTPUT (dB)

-30

-20

-10

1M

10M

VDD = +5V

V

SS

= AGND

VREF = 2.5VDC + 0.05Vp-p SINE WAVE

0

1k 10k 100k

REFERENCE VOLTAGE INPUT

FREQUENCY RESPONSE

-40

MAX509-FG08

FREQUENCY (Hz)

RELATIVE OUTPUT (dB)

-30

-20

-10

1M

10M

VDD = +5V

V

SS

= -5V

VREF = 2.5VDC + 4Vp-p SINE WAVE

__________________________________________Typical Operating Characteristics

(TA = +25°C, unless otherwise noted.)

MAX509/MAX510

Quad, Serial 8-DACs

with Rail-to-Rail Outputs

6 _______________________________________________________________________________________

____________________________Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

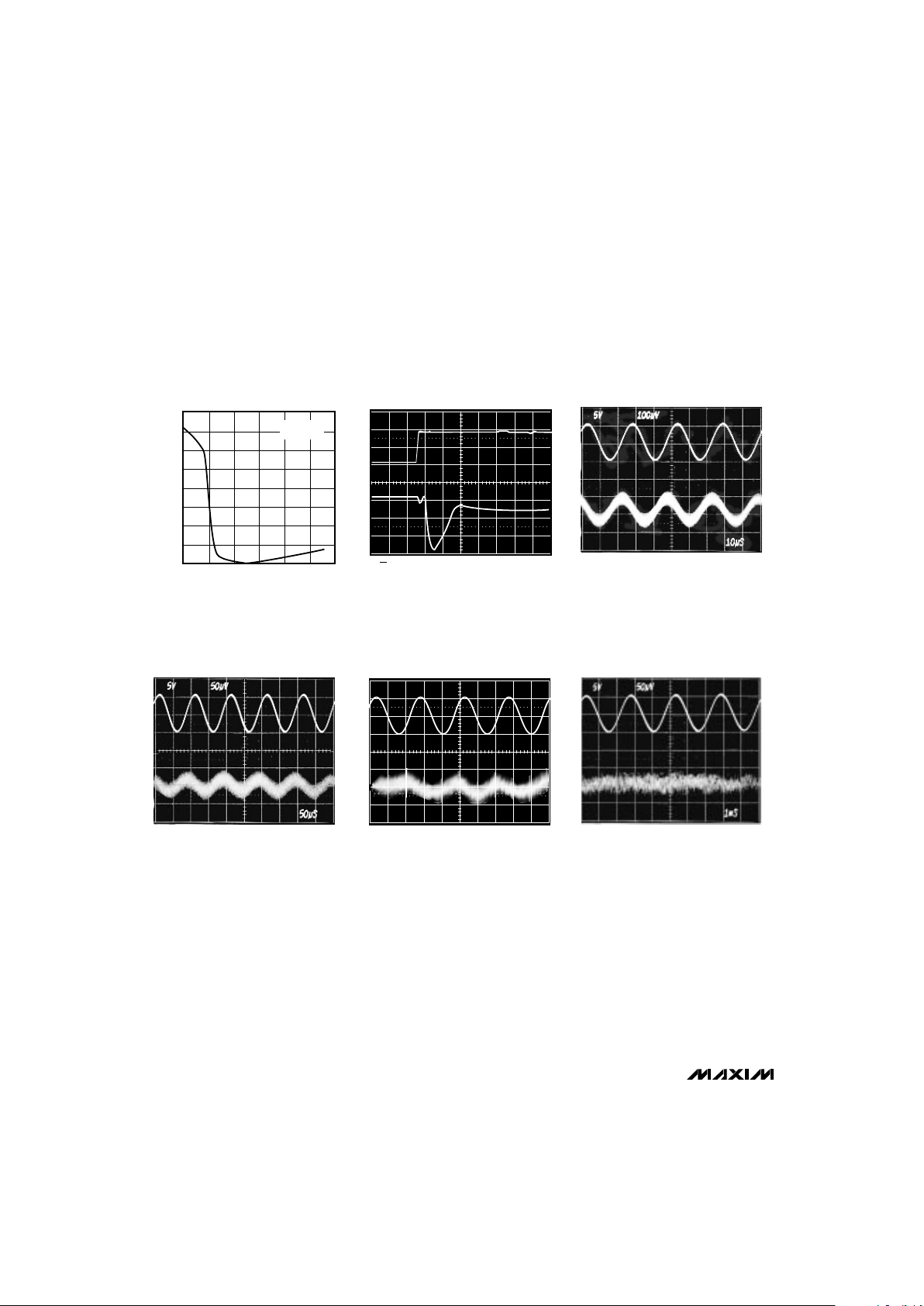

A = REFA, 10V

p-p

B = OUTA, 100µV/div, UNLOADED

TIMEBASE = 10µs/div

V

DD

= +5V, VSS = -5V

CODE = ALL 0s

REFERENCE FEEDTHROUGH AT 40kHz

A

B

A = REFA, 10V

p-p

B = OUTA, 50µV/div, UNLOADED

TIMEBASE = 1ms/div

REFERENCE FEEDTHROUGH AT 400Hz

A

B

A = REFA, 10V

p-p

B = OUTA, 50µV/div, UNLOADED

TIMEBASE = 50µs/div

REFERENCE FEEDTHROUGH AT 10kHz

A

B

5V 50µV

100µS

A = REFA, 10V

p-p

B = OUTA, 50µV/div, UNLOADED

TIMEBASE = 100µs/div

REFERENCE FEEDTHROUGH AT 4kHz

A

B

10

5.0

3.6

0-4

ZERO-CODE ERROR

vs. NEGATIVE SUPPLY VOLTAGE

3.8

4.8

MAX509-FG09

VSS (V)

ZERO-CODE ERROR (mV)

-3

4.4

4.0

-1 -2

4.6

3.4

4.2

-5

-6

VDD = +5V

VREF = +4V

A = CS, 2V/div

B = OUTA, 20mV ˜

TIMEBASE = 200ns/div

WORST-CASE 1LSB DIGITAL STEP CHANGE

A

B

200nS

2V 20mV

Loading...

Loading...