19-0448; Rev 0; 11/95

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

_______________General Description

The MAX395 8-channel, serially controlled, single-pole/single-throw (SPST) analog switch offers eight separately

controlled switches. The switches conduct equally well in

either direction. On-resistance (100Ω max) is matched

between switches to 5Ω max and is flat (10Ω max) over

the specified signal range.

These CMOS devices can operate continuously with

dual power supplies ranging from ±2.7V to ±8V or a

single supply between +2.7V and +16V. Each switch

can handle rail-to-rail analog signals. The off leakage

current is only 0.1nA at +25°C or 5nA at +85°C.

Upon power-up, all switches are off, and the internal shift

registers are reset to zero. The MAX395 is electrically

equivalent to two MAX391 quad switches controlled by a

serial interface, and is pin compatible with the MAX335.

The serial interface is compatible with SPI™/QSPI™ and

____________________________Features

♦ SPI™/QSPI™, Microwire™-Compatible Serial

Interface

♦ 8 Separately Controlled SPST Switches

♦ 100Ω Signal Paths with ±5V Supplies

♦ Rail-to-Rail Signal Handling

♦ Asynchronous RESET

♦ Pin Compatible with Industry-Standard MAX335

♦ ±2.7V to ±8V Dual Supplies

+2.7V to +16V Single Supply

♦ >2kV ESD Protection per Method 3015.7

♦ TTL/CMOS-Compatible Inputs (with +5V or

±5V Supplies)

Input

Microwire™. Functioning as a shift register, it allows data

(at DIN) to be clocked in synchronously with the rising

edge of clock (SCLK). The shift register’s output (DOUT)

enables several MAX395s to be daisy chained.

All digital inputs have 0.8V to 2.4V logic thresholds, ensuring both TTL- and CMOS-logic compatibility when using

±5V supplies or a single +5V supply.

________________________Applications

Serial Data-Acquisition Industrial and ProcessSystems Control Systems

Avionics ATE Equipment

Audio Signal Routing Networking

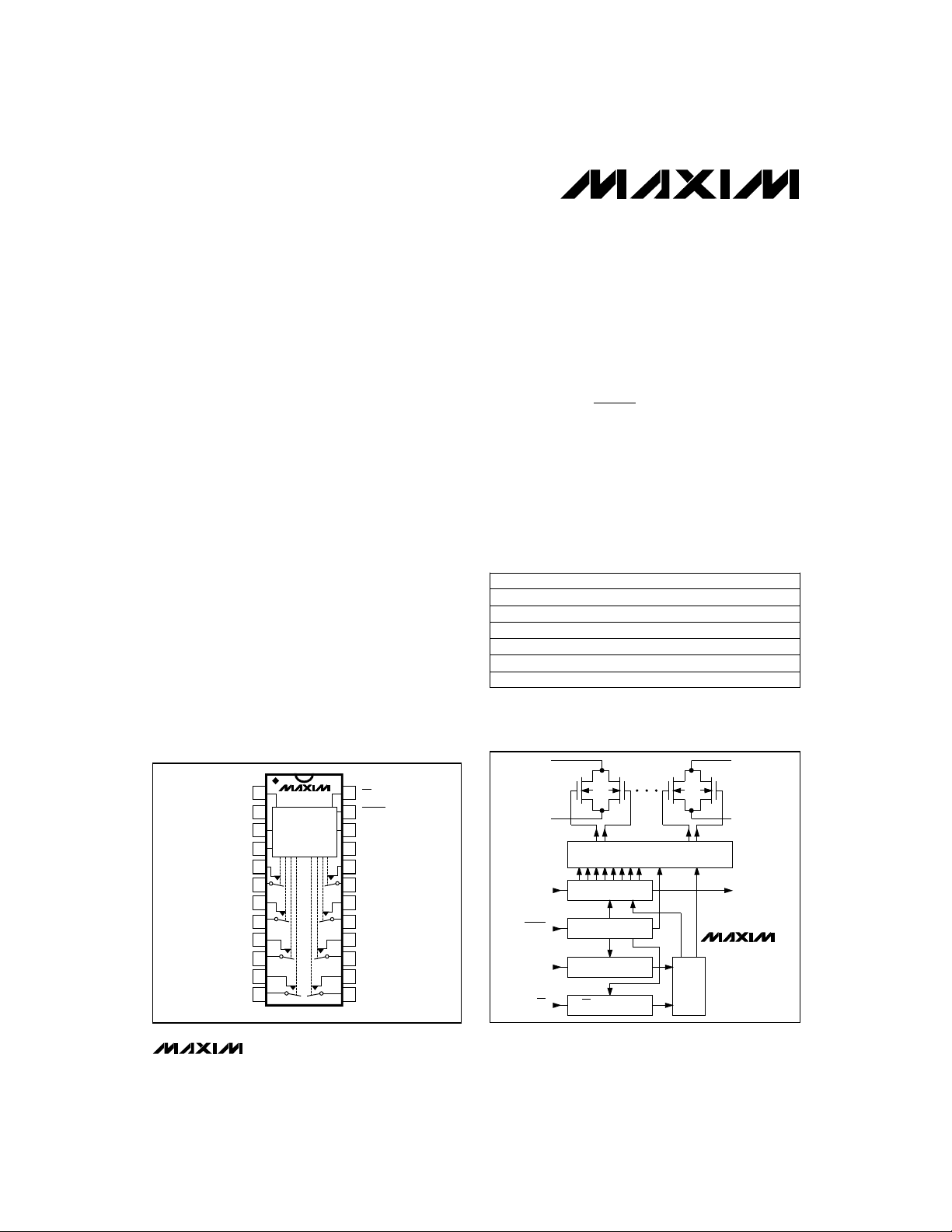

__________________Pin Configuration

TOP VIEW

SCLK

1

V+

DIN

GND

NO0

COM0

NO1

COM1

NO2

COM2

NO3

COM3

SPI and QSPI are trademarks of Motorola, Inc. Microwire is a trademark of National Semiconductor Corp.

MAX395

2

3

LOGIC

4

5

6

7

8

9

10

11

12

DIP/SO

________________________________________________________________

24

CS

23

RESET

22

DOUT

21

V-

20

NO7

19

COM7

18

NO6

17

COM6

16

NO5

15

COM5

14

NO4

13

COM4

______________Ordering Information

PART

MAX395CNG

MAX395CWG

MAX395C/D 0°C to +70°C

MAX395ENG

MAX395EWG

MAX395MRG -55°C to +125°C

* Contact factory for dice specifications.

** Contact factory for availability.

TEMP. RANGE PIN-PACKAGE

0°C to +70°C

0°C to +70°C

-40°C to +85°C 24 Narrow Plastic DIP

-40°C to +85°C

________________Functional Diagram

NO0

COM0

PARALLEL REGISTER AND TRANSLATOR

DIN

8-BIT SHIFT REGISTER

RESET

SCLK

CS

CLOCK TRANSLATOR

CS TRANSLATOR

Maxim Integrated Products

Call toll free 1-800-998-8800 for free samples or literature.

MAX395

24 Narrow Plastic DIP

24 Wide SO

Dice*

24 Wide SO

24 Narrow CERDIP**

NO7

COM7

DOUT

MAX395

LATCH

1

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

ABSOLUTE MAXIMUM RATINGS

Voltages Referenced to GND

V+...........................................................................-0.3V, +17V

V-............................................................................-17V, +0.3V

V+ to V-...................................................................-0.3V, +17V

SCLK, CS

NO, COM.................................................(V- - 2V) to (V+ + 2V)

Continuous Current into Any Terminal..............................±30mA

MAX395

Peak Current, NO_ or COM_

(pulsed at 1ms,10% duty cycle)..................................±100mA

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

, DIN, DOUT, RESET .................-0.3V to (V+ + 0.3V)

Continuous Power Dissipation (T

Narrow Plastic DIP (derate 13.33mW/°C above +70°C)...1067mW

Wide SO (derate 11.76mW/°C above +70°C)...............941mW

Narrow CERDIP (derate 12.50mW/°C above +70°C)....1000mW

Operating Temperature Ranges

MAX395C_ G .......................................................0°C to +70°C

MAX395E_ G ....................................................-40°C to +85°C

MAX395MRG..................................................-55°C to +125°C

Storage Temperature Range.............................-65°C to +150°C

Lead Temperature (soldering, 10sec).............................+300°C

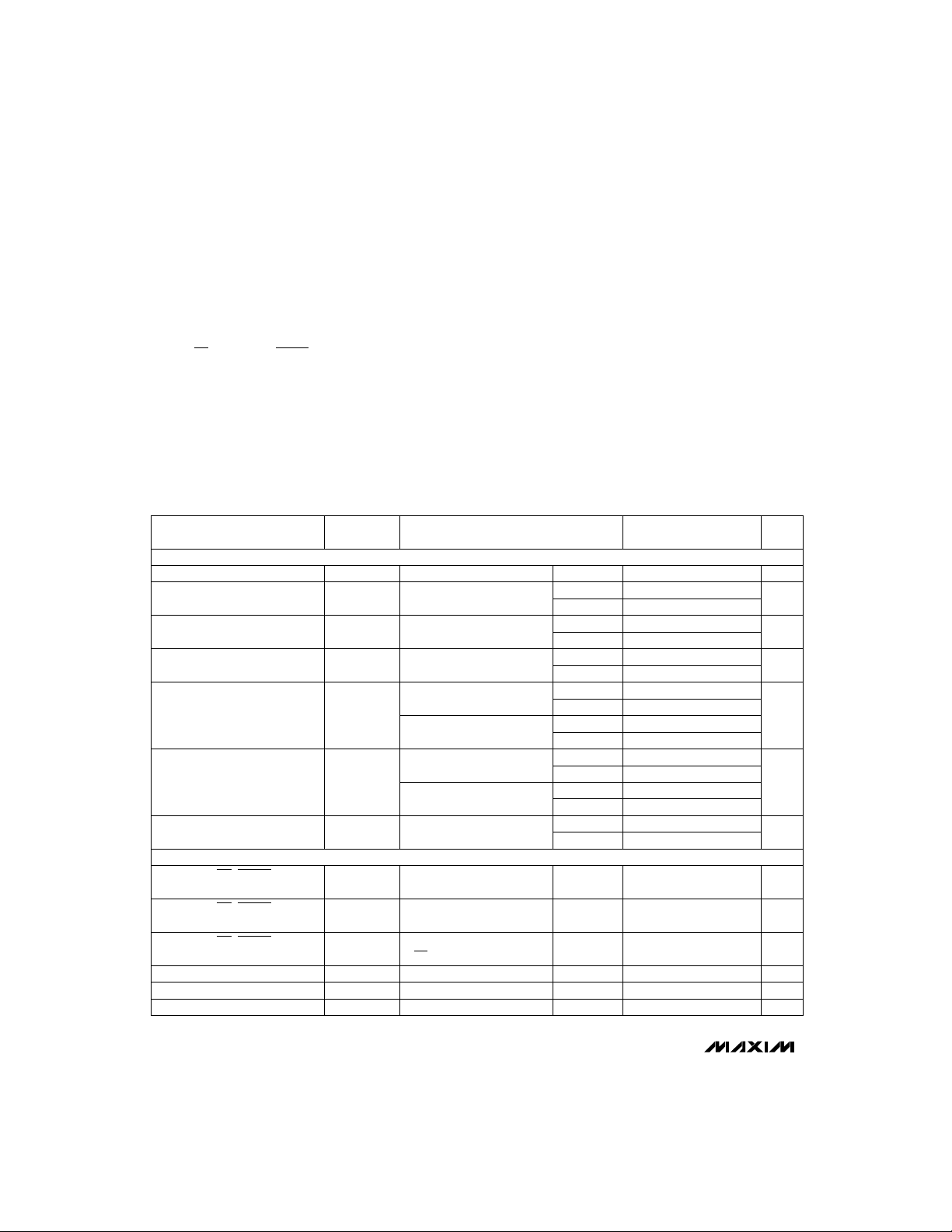

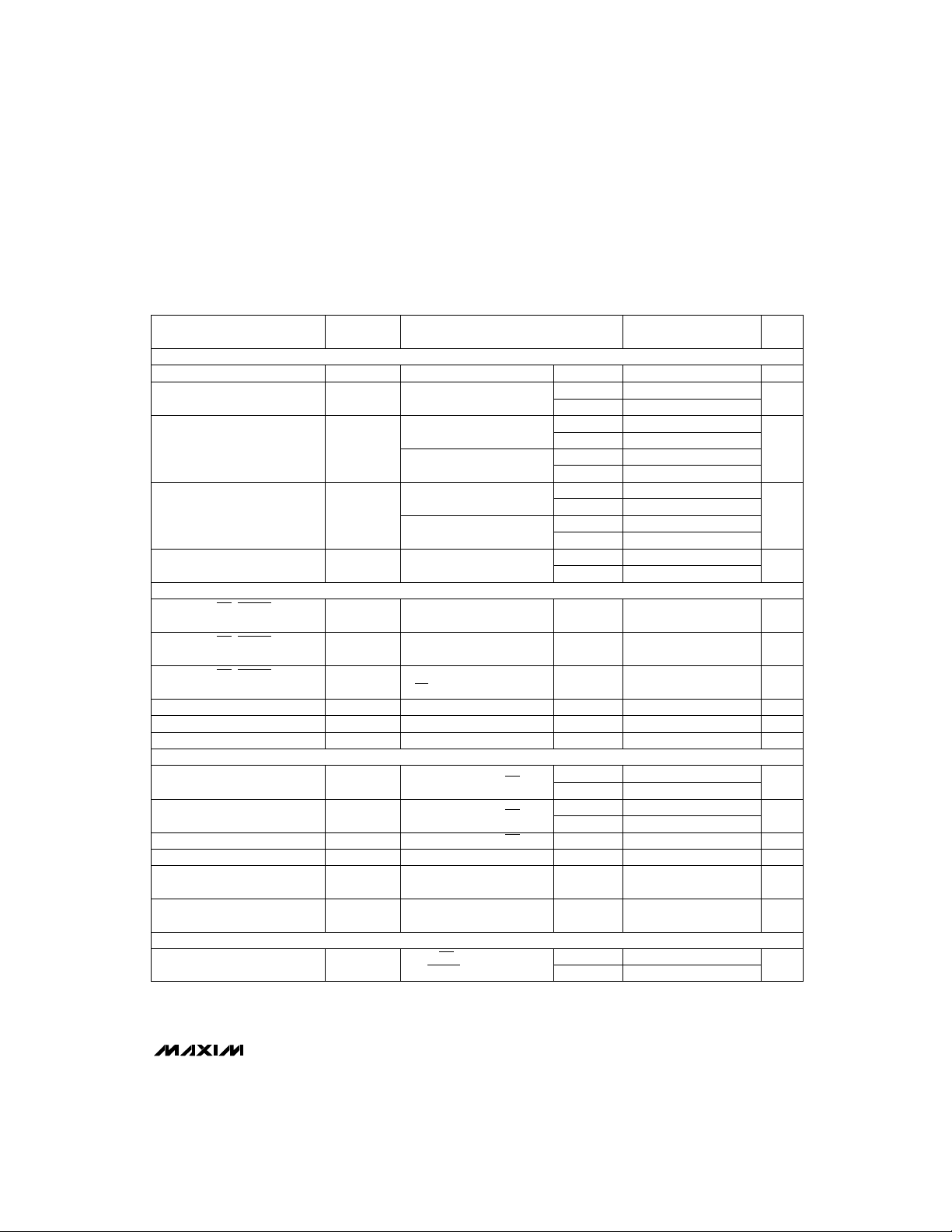

ELECTRICAL CHARACTERISTICS—Dual Supplies

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

SYMBOLPARAMETER

ANALOG SWITCH

Analog Signal Range

COM, NO On-Resistance

COM, NO On-Resistance Match

Between Channels (Note 2)

COM, NO On-Resistance

Flatness (Note 2)

NO Off Leakage Current

(Note 3)

COM Off Leakage Current

(Note 3)

COM On Leakage Current

(Note 3)

DIGITAL I/O

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold High

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold Low

DIN, SCLK, CS, RESET Input

Current Logic High or Low

DOUT Output Voltage Logic High

DOUT Output Voltage Logic Low

SCLK Input Hysteresis

COM

R

ON

∆R

ON

R

FLAT(ON)

I

NO(OFF)

I

COM(OFF)

COM(ON)

IH

IL

IH, IIL

DOUT

DOUT

to T

MIN

MAX

, V

NO

V+ = 5V, V- = -5V,

V

= ±3V, INO= 1mA

COM

V+ = 5V, V- = -5V,

V

= ±3V, INO= 1mA

COM

V+ = 5V, V- = -5V, INO= 1mA,

V

= -3V, 0V, 3V

COM

V+ = 5.5V, V- = -5.5V,

V

= -4.5V, VNO= 4.5V

COM

V+ = 5.5V, V- = -5.5V,

V

= 4.5V, VNO= -4.5V

COM

V+ = 5.5V, V- = -5.5V,

V

= -4.5V, VNO= 4.5V

COM

V+ = 5.5V, V- = -5.5V,

V

= 4.5V, VNO= -4.5V

COM

V+ = 5.5V, V- = -5.5V,

V

= VNO= ±4.5V

COM

V

, V

DIN

SCLK

VCS= 0.8V or 2.4V

I

= 0.8mA

DOUT

I

= -1.6mA

DOUT

HYST

, unless otherwise noted. Typical values are at TA= +25°C.)

CONDITIONS UNITS

C, E, M

TA= +25°C

C, E, M

TA= +25°C 5

C, E, M

TA= +25°C 10

C, E, M

TA= +25°C -0.1 0.002 0.1

C, E, M

TA= +25°C -0.1 0.002 0.1

C, E, M

TA= +25°C -0.1 0.002 0.1

C, E, M

TA= +25°C 0.1 0.002 0.1

C, E, M

TA= +25°C -0.2 0.01 0.2

C, E, M

C, E, M

C, E, M

,

C, E, M

C, E, M

C, E, M

C, E, M

= +70°C)

A

MIN TYP MAX

(Note 1)

60 100

125

10

15

-10 10

-10 10

-10 10

-10 10

-20 20

VV- V+V

Ω

Ω

Ω

nA

nA

nAI

V2.4V

V0.8V

µA-1 0.03 1I

V2.8 V+V

V0 0.4V

mV100SCLK

2 _______________________________________________________________________________________

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

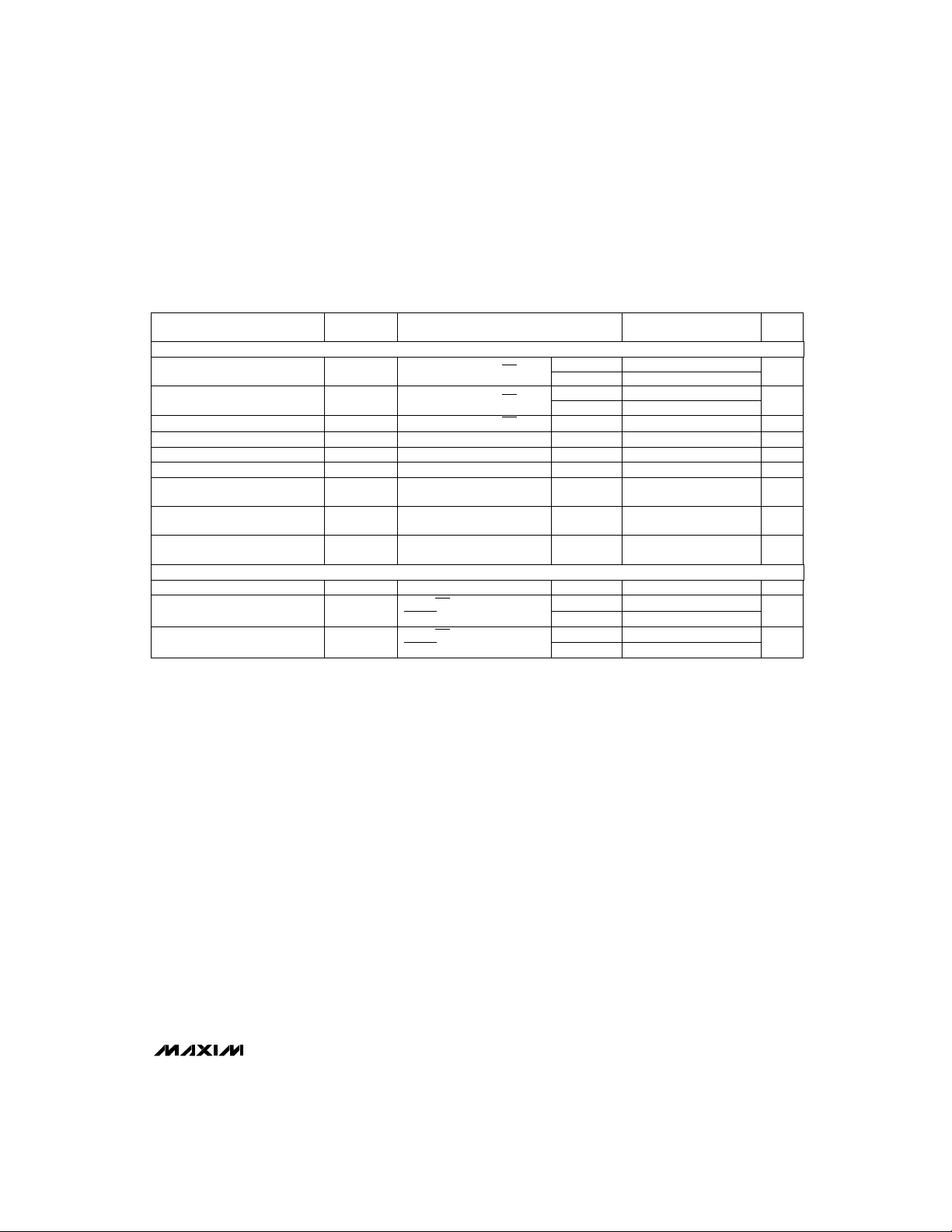

ELECTRICAL CHARACTERISTICS—Dual Supplies (continued)

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

SYMBOLPARAMETER

SWITCH DYNAMIC CHARACTERISTICS

Turn-On Time

Turn-Off Time

Break-Before-Make Delay

Charge Injection (Note 4)

NO Off Capacitance

COM Off Capacitance

Switch On Capacitance

Off Isolation

Channel-to-Channel Crosstalk

POWER SUPPLY

t

ON

t

OFF

t

BBM

V

CTE

C

NO(OFF)

COM(OFF)

C

(ON)

ISO

CT

I+V+ Supply Current

I-V- Supply Current

to T

MIN

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

From rising edge of CS

From rising edge of CS ns

From rising edge of CS

CL= 1nF, VNO= 0V, RS= 0Ω

VNO= GND, f = 1MHz

V

= GND, f = 1MHzC

COM

V

= VNO= GND,

COM

f = 1MHz

RL= 50Ω, CL= 15pF,

VNO= 1V

RL= 50Ω, CL= 15pF,

VNO= 1V

DIN = CS = SCLK = 0V or V+,

RESET = 0V or V+

DIN = CS = SCLK = 0V or V+,

RESET = 0V or V+

, f = 100kHz

RMS

, f = 100kHz

RMS

TA= +25°C 200 400

C, E, M

TA= +25°C 90 400

C, E, M

TA= +25°C 515

T

= +25°C

A

T

= +25°C 2

A

TA= +25°C

TA= +25°C

TA= +25°C

TA= +25°C

C, E, M

TA= +25°C

C, E, M

TA= +25°C

C, E, M

MIN TYP MAX

(Note 1)

500

500

210

2

8

-90

<-90 dBV

720

30

-1 0.1 1

-2 2

MAX395

UNITS

ns

ns

pC

pF

pF

pF

dBV

V±3 ±8V+, V-Power-Supply Range

µA

µA

_______________________________________________________________________________________ 3

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

TIMING CHARACTERISTICS—Dual Supplies (Figure 1)

(V+ = +4.5V to +5.5V, V- = -4.5V to -5.5V, TA= T

PARAMETER SYMBOL

SERIAL DIGITAL INTERFACE

SCLK Frequency f

Cycle Time

MAX395

CS Lead Time

CS Lag Time t

SCLK High Time

SCLK Low Time

Data Setup Time t

Data Hold Time

DIN Data Valid after Falling SCLK

(Note 4)

Rise Time of DOUT (Note 4) t

Allowable Rise Time at DIN, SCLK

(Note 4)

Fall Time of DOUT (Note 4) t

Allowable Fall Time at DIN, SCLK

(Note 4)

RESET Minimum Pulse Width t

Note 1: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 2: ∆R

Note 3: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at room temp.

Note 4: Guaranteed by design.

Note 5: Leakage testing at single supply is guaranteed by testing with dual supplies.

Note 6: See Figure 6. Off isolation = 20log

Note 7: Between any two switches. See Figure 3.

= R

ON

specified voltages. Flatness is defined as the difference between the maximum and minimum value of on-resistance as

measured over the specified analog signal range.

ON(max)

- R

ON(min)

SCLK

t

CH +tCL

t

CSS

CSH2

t

CH

t

CL

DS

t

DH

t

DO

DR

t

SCR

DF

t

SCF

RW

. On-resistance match between channels and on-resistance flatness are guaranteed only with

10VCOM/VNO

to T

MIN

50% of SCLK to 10% of DOUT,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

, V

= output. NO = input to off switch.

COM

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

TA= +25°C

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

MIN TYP MAX

(Note 1)

0 2.1nsMHz

480

240 ns

240 ns

190

190 ns

200 17 ns

0 -17

85

70 nsTA= +25°C

UNITS

400

100 ns

2 µs

100 ns

2 µs

ns

ns

ns

4 _______________________________________________________________________________________

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

ELECTRICAL CHARACTERISTICS—Single +5V Supply

(V+ = +4.5V to +5.5V, V- = 0V, TA= T

PARAMETER SYMBOL

ANALOG SWITCH

Analog Signal Range

COM, NO On-Resistance R

NO Off Leakage Current

(Notes 4, 5)

COM Off Leakage Current

(Notes 4, 5)

COM On Leakage Current

(Notes 4, 5)

DIGITAL I/O

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold High

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold Low

DIN, SCLK, CS, RESET Input

Current Logic High or Low

DOUT Output Voltage Logic High

DOUT Output Voltage Logic Low V

SCLK Input Hysteresis SCLK

SWITCH DYNAMIC CHARACTERISTICS

Turn-On Time t

Turn-Off Time t

Break-Before-Make Delay t

Charge Injection (Note 4) V

Off Isolation (Note 6) V

Channel-to-Channel Crosstalk

(Note 7)

POWER SUPPLY

V+, V- Supply Current I+

to T

MIN

COM,VNO

ON

I

NO(OFF)

I

COM(OFF)

I

COM(ON)

V

IH

V

IL

IIH, I

V

DOUT

DOUT

HYST

ON

OFF

BBM

CTE

ISO

V

CT

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

V+ = 5V, V

INO= 1mA

V+ = 5.5V, V

VNO= 0V

V+ = 5.5V, V

VNO= 4.5V

V+ = 5.5V, V

VNO= 0V

V+ = 5.5V, V

VNO= 4.5V

COM

COM

COM

COM

COM

= 3.5V,

= 4.5V,

= 0V,

= 4.5V,

= 0V,

V+ = 5.5V,

V

= VNO= 4.5V

COM

V

, V

IL

VCS= 0.8V or 2.4V

I

DOUT

DOUT

DIN

,

SCLK

= -0.8mA C, E, M

= 1.6mA C, E, M

From rising edge of CS

From rising edge of CS

From rising edge of CS

CL= 1nF, VNO= 0V, RS= 0Ω

RL= 50Ω, CL= 15pF,

VNO= 1V

, f = 100kHz

RMS

RL= 50Ω, CL= 15pF,

VNO= 1V

, f = 100kHz

RMS

DIN = CS = SCLK = 0V or

V+, RESET = 0V or V+

MIN TYP MAX

(Note 2)

C, E, M

V- V+

125 175TA= +25°C

C, E, M

225

-0.1 0.002 0.1TA= +25°C

C, E, M

-10 10

-0.1 0.002 0.1TA= +25°C

C, E, M

-10 10

-0.1 0.002 0.1TA= +25°C

C, E, M

-10 10

-0.1 0.002 0.1TA= +25°C

C, E, M

-10 10

-0.2 0.002 0.2TA= +25°C

-20 20C, E, M

C, E, M

C, E, M

C, E, M

TA= +25°C

C, E, M

TA= +25°C

C, E, M

TA= +25°C

TA= +25°C

TA= +25°C

TA= +25°C

TA= +25°C

2.4

0.8

-1 0.03 1

200 400

500

90 400

500

15 ns

210pC

-90 dB

<-90 dB

720

C, E, M 30

MAX395

UNITS

VV

Ω

nA

nA

nA

V

V

µA

V2.8 V+

V0 0.4I

mV100C, E, M

ns

ns

µA

_______________________________________________________________________________________ 5

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

TIMING CHARACTERISTICS—Single +5V Supply (Figure 1)

(V+ = +4.5V to +5.5V, V- = 0V, TA= T

PARAMETER SYMBOL

SERIAL DIGITAL INTERFACESERIAL DIGITAL INTERFACE

SCLK Frequency f

Cycle Time (Note 4)

MAX395

CS Lead Time (Note 4)

CS Lag Time (Note 4) t

SCLK High Time (Note 4)

SCLK Low Time (Note 4)

Data Setup Time (Note 4) t

Data Hold Time (Note 4)

DIN Data Valid after Falling SCLK

(Note 4)

Rise Time of DOUT (Note 4) t

Allowable Rise Time at DIN,

SCLK (Note 4)

Fall Time of DOUT (Note 4)

Allowable Fall Time at DIN,

SCLK (Note 4)

RESET Minimum Pulse Width t

to T

MIN

SCLK

t

CH +tCL

t

CSS

CSH2

t

t

t

t

t

SCR

t

SCF

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

CH

CL

DS

DH

DO

DR

DF

RW

50% of SCLK to 10% of

DOUT, CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

TA= +25°C

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

MIN TYP MAX

(Note 2)

0 2.1 MHz

480

240 ns

240 ns

190

190 ns

200 17 ns

0 -17

85

70 nsTA= +25°C

UNITS

400

100 ns

2 µs

2 µs

ns

ns

ns

ns

ns100t

Note 1: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 2: ∆R

Note 3: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at room temp.

Note 4: Guaranteed by design.

Note 5: Leakage testing at single supply is guaranteed by testing with dual supplies.

Note 6: See Figure 6. Off isolation = 20log

Note 7: Between any two switches. See Figure 3.

6 _______________________________________________________________________________________

= R

ON

specified voltages. Flatness is defined as the difference between the maximum and minimum value of on-resistance as

measured over the specified analog signal range.

ON(max)

- R

. On-resistance match between channels and on-resistance flatness are guaranteed only with

ON(min)

, V

10VCOM/VNO

= output. NO = input to off switch.

COM

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

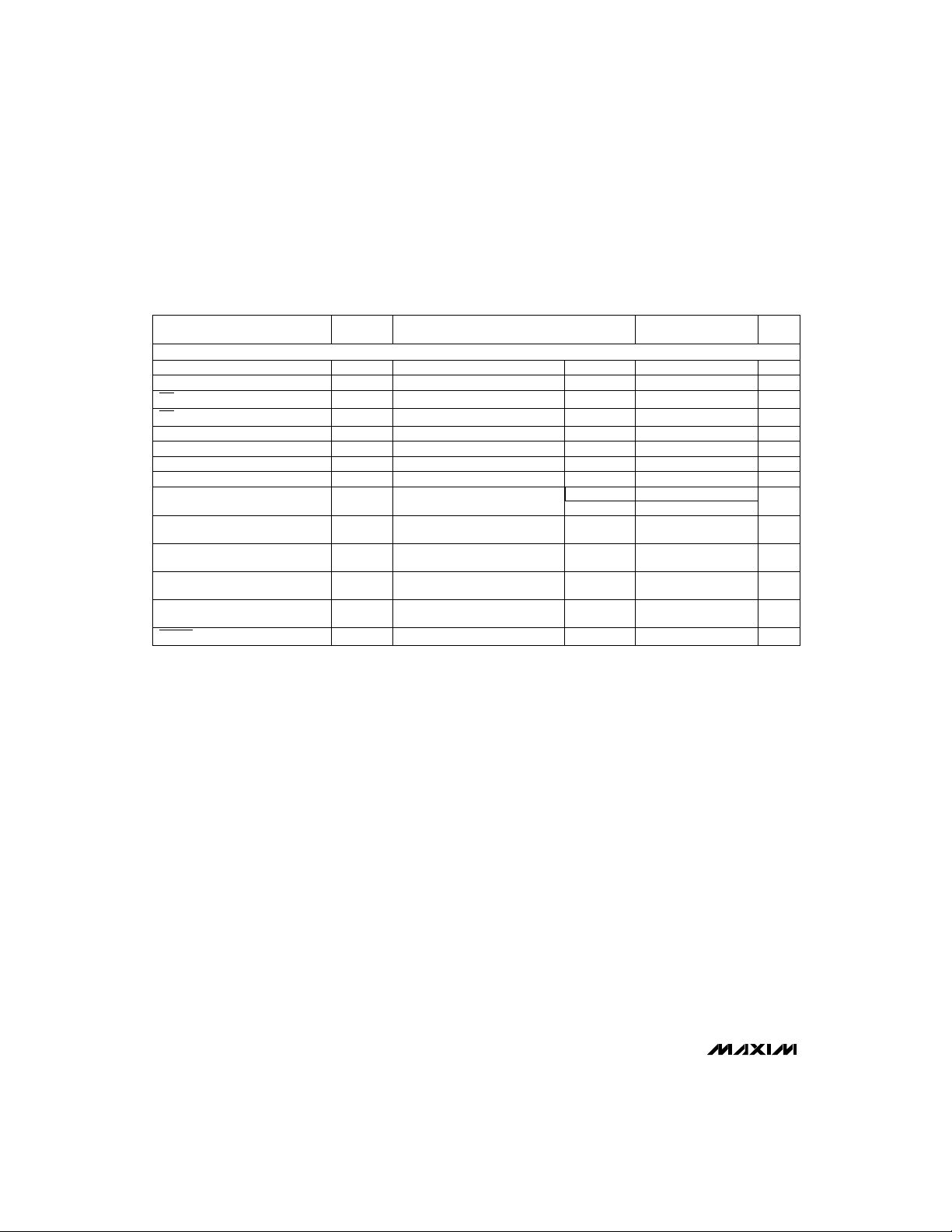

ELECTRICAL CHARACTERISTICS—Single +3V Supply

(V+ = +3.0V to +3.6V, V- = 0V, TA= T

ANALOG SWITCH

COM, NO On-Resistance

NO Off Leakage Current

(Notes 4, 5)

COM Off Leakage Current

(Notes 4, 5)

COM On Leakage Current

(Notes 4, 5)

DIGITAL I/O

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold High

DIN, SCLK, CS, RESET Input

Voltage Logic Threshold Low

DIN, SCLK, CS, Input

Current Logic High or Low

DOUT Output Voltage Logic High

DOUT Output Voltage Logic Low

SCLK Input Hysteresis

SWITCH DYNAMIC CHARACTERISTICS

Turn-On Time

Turn-Off Time

Break-Before-Make Delay

Charge Injection (Note 4)

Off Isolation (Note 6)

Channel-to-Channel Crosstalk

(Note 7)

POWER SUPPLY

to T

MIN

SYMBOLPARAMETER

, V

COM

R

ON

NO(OFF)

I

COM(OFF)

COM(ON)

IH

IL

IH, IIL

DOUT

DOUT

t

ON

t

OFF

BBM

CTE

ISO

CT

I+V+ Supply Current

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

NO

HYST

V+ = 3.0V, V

INO= 1mA

V+ = 3.0V, V

VNO= 0V

V+ = 3.6V, V

VNO= 3V

V+ = 3.6V, V

VNO= 0V

V+ = 3.6V, V

VNO= 3V

V+ = 3.6V, V

VNO= 0V

V+ = 3.6V, V

VNO= 3V

V

, V

DIN

SCLK

VCS= 0.8V or 2.4V

I

= 0.1mA

DOUT

I

= -1.6mA

DOUT

COM

COM

COM

COM

COM

COM

COM

,

= 1.5V,

= 3V,

= 0V,

= 3V,

= 0V,

= 3V,

= 0V,

From rising edge of CS ns

From rising edge of CS ns

CL= 1nF, VNO= 0V, RS= 0Ω pC210V

RL= 50Ω, CL= 15pF,

VNO= 1V

, f = 100kHz

RMS

RL= 50Ω, CL= 15pF,

VNO= 1V

, f = 100kHz

RMS

DIN = CS = SCLK = 0V or V+,

RESET = 0V or 5V

MIN TYP MAX

(Note 2)

V- V+

TA= +25°C 270 500

C, E, M

600

TA= +25°C -0.1 0.002 0.1

C, E, M

-5 5

TA= +25°C -0.1 0.002 0.1

C, E, M

-5 5

TA= +25°C -0.1 0.002 0.1

C, E, M

-5 5

TA= +25°C 0.1 0.002 0.1

C, E, M

-5 5

TA= +25°C -0.1 0.002 0.1

C, E, M

-10 10

TA= +25°C -0.1 0.002 0.1

C, E, M

-10 10

C, E

C, E

C, E

C, E, M

C, E, M

C, E, M

TA= +25°C

C, E, M

TA= +25°C

C, E, M

100SCLK

260 600

800

90 300

400

TA= +25°CFrom rising edge of CS

TA= +25°C

TA= +25°C

-90V

TA= +25°C

TA= +25°C

C, E, M

620

30

MAX395

UNITS

VAnalog Signal Range C, E, MV

Ω

nAI

nA

nAI

V2.4V

V0.8V

µA-1 0.03 1I

V2.8 V+V

V0 0.4V

mV

ns15t

dB

dB<-90V

µA

_______________________________________________________________________________________ 7

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

TIMING CHARACTERISTICS—Single +3V Supply (Figure 1)

(V+ = +3.0V to +3.6V, V- = 0V, TA= T

PARAMETER SYMBOL

SERIAL DIGITAL INTERFACE

SCLK Frequency f

Cycle Time (Note 4)

MAX395

CS Lead Time (Note 4)

CS Lag Time (Note 4) t

SCLK High Time (Note 4)

SCLK Low Time (Note 4)

Data Setup Time (Note 4) t

Data Hold Time (Note 4)

DIN Data Valid after Falling SCLK

(Note 4)

Rise Time of DOUT (Note 4) t

Allowable Rise Time at DIN,

SCLK (Note 4)

Fall Time of DOUT (Note 4) t

Allowable Fall Time at DIN,

SCLK (Note 4)

RESET Minimum Pulse Width t

to T

MIN

SCLK

t

CH +tCL

t

CSS

CSH2

t

t

t

t

t

SCR

t

SCF

, unless otherwise noted. Typical values are at TA= +25°C.)

MAX

CONDITIONS

CH

CL

DS

DH

DO

DR

DF

RW

50% of SCLK to 10% of

DOUT, CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

20% of V+ to 70% of V+,

CL= 10pF

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

TA= +25°C

C, E, M

C, E, M

C, E, M

C, E, M

C, E, M

MIN TYP MAX

(Note 2)

0 2.1 MHz

480

240 ns

240 ns

190

190 ns

200 38 ns

0 -38

150

105 nsTA= +25°C

UNITS

400

300 ns

2 µs

300 ns

2 µs

ns

ns

ns

ns

Note 1: The algebraic convention is used in this data sheet; the most negative value is shown in the minimum column.

Note 2: ∆R

Note 3: Leakage parameters are 100% tested at maximum rated hot temperature and guaranteed by correlation at room temp.

Note 4: Guaranteed by design.

Note 5: Leakage testing at single supply is guaranteed by testing with dual supplies.

Note 6: See Figure 6. Off isolation = 20log

Note 7: Between any two switches. See Figure 3.

8 _______________________________________________________________________________________

= R

ON

specified voltages. Flatness is defined as the difference between the maximum and minimum value of on-resistance as

measured over the specified analog signal range.

ON(max)

- R

. On-resistance match between channels and on-resistance flatness are guaranteed only with

ON(min)

, V

10VCOM/VNO

= output. NO = input to off switch.

COM

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

__________________________________________Typical Operating Characteristics

(V+ = +5V, V- = -5V, GND = 0V, TA = +25°C, unless otherwise noted.)

ON-RESISTANCE vs. V

(DUAL SUPPLIES)

140

120

100

80

(Ω)

ON

R

60

40

20

0

-5 -3 1

ON-RESISTANCE vs. V

AND TEMPERATURE

180

160

140

120

(Ω)

ON

100

R

80

60

40

02

(SINGLE SUPPLY)

V+ = 5V

V- = 0V

153

CHARGE INJECTION vs. V

5

4

3

2

1

(pC)

0

j

Q

-1

-2

-3

-4

-5

-5 -3 1

COM

V± = ±2.5V

-1 3

V

(V)

COM

COM

= +125°C

T

A

TA = +85°C

T

= +25°C

A

TA = -55°C

V

(V)

COM

MAX395 TOC1

V± = ±3V

V± = ±5V

5-4 0-2 2 4

MAX395 TOC4

4

COM

MAX395 TOC7

-1 3

V

(V)

COM

5-4 0-2 2 4

ON-RESISTANCE vs. V

AND TEMPERATURE

110

100

90

80

(Ω)

70

ON

R

60

50

40

30

-5 -3 1

1000

100

10

OFF-LEAKAGE (pA)

1

0.1

(DUAL SUPPLIES)

V± = ±5.5V

TA = +125°C

TA = +85°C

TA = +25°C

TA = -55°C

-1 3

V

OFF-LEAKAGE vs.

TEMPERATURE

V± = ±5.5V

-50 12525-25 0 7550 100

TEMPERATURE (°C)

TURN-ON/OFF TIMES vs. V

250

A: V+ = 5V, V- = 5V

B: V+ = 5V, V- = 0V

200

150

(ns)

OFF

, t

A = t

ON

100

t

A = t

50

0

-5 -3 1

ON

OFF

B = t

B = t

-1 3

V

COM

COM

COM

400

350

MAX395 TOC2

300

250

(Ω)

200

ON

R

150

100

(V)

5-4 0-2 2 4

MAX395 TOC5

10,000

1000

100

ON-LEAKAGE (pA)

0.1

COM

MAX395 TOC8

ON

OFF

(V)

DATA HOLD TIME (ns)

5-4 0-2 2 4

-10

-20

-30

-40

-50

ON-RESISTANCE vs. V

(SINGLE SUPPLY)

V+ = 2.5V

V+ = 3V

V+ = 5V

50

0

04

210126

V

COM

ON-LEAKAGE vs.

TEMPERATURE

V± = ±5.5V

10

1

-50 12525-25 0 7550 100

TEMPERATURE (°C)

DATA HOLD TIME vs.

POWER-SUPPLY VOLTAGE

50

40

30

20

10

0

04

26

SUPPLY VOLTAGE (V)

COM

V+ = 9V

8

(V)

V- = 0V

V+ = 12V

8

MAX395

MAX395 TOC3

MAX395 TOC6

MAX395 TOC9

_______________________________________________________________________________________

9

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

____________________________Typical Operating Characteristics (continued)

(V+ = +5V, V- = -5V, GND = 0V, TA = +25°C, unless otherwise noted.)

DATA SETUP TIME vs.

POSITIVE SUPPLY VOLTAGE

100

90

80

MAX395

70

60

50

40

30

DATA SETUP TIME (ns)

20

10

0

04

26

SUPPLY VOLTAGE (V)

0

-20

-40

LOSS (dB)

-60

-80

-100

FREQUENCY RESPONSE

ISOLATION OF

A BARE SOCKET

10k 100k 10M 1G

1M 100M

FREQUENCY (Hz)

8

INSERTION LOSS

OFF ISOLATION

V± = ±5V

50Ω IN AND OUT

MAX395 TOC10

I+, I-, (µA)

0.001

PHASE

______________________________________________________________Pin Description

PIN

1 SCLK Serial Clock Digital Input

2 V+ Positive Analog Supply Voltage Input

3 DIN Serial Data Digital Input

4 GND

5, 7, 9, 11, 14, 16, 18, 20 NO0–NO7 Normally Open Analog Switches 0–7

6, 8, 10, 12, 13, 15, 17, 19 COM0–COM7 Common Analog Switches 0–7

21 V- Negative Analog Supply Voltage Input. Connect to GND for single-supply operation

22 DOUT Serial Data Digital Output. (High is sourced from V+.)

23 RESET

24 CS Chip-Select Digital Input (Figure 1)

Note: NO_ and COM_ pins are identical and interchangeable. Either may be considered as an input or an output; signals pass

equally well in either direction.

10 ______________________________________________________________________________________

NAME FUNCTION

POWER-SUPPLY CURRENT

100

10

1

0.1

0.01

vs. TEMPERATURE

V± = ±5.5V

-50 125

20

0

MAX395 TOC13

-20

-40

-60

-80

-100

-120

25

-25 0 7550

TEMPERATURE (°C)

PHASE (DEGREES)

MAX395 TOC11

I+

I-

100

TOTAL HARMONIC DISTORTION

100

V± = ±5V

600Ω IN AND OUT

10

1

TDH (%)

0.1

0.01

10 100 1k 10k

MINIMUM SCLK PULSE WIDTH vs.

POSITIVE SUPPLY VOLTAGE

35

30

25

SCLK (ns)

20

15

10

04

26

SUPPLY VOLTAGE (V)

vs. FREQUENCY

FREQUENCY (Hz)

MAX395 TOC14

Ground. Connect to digital ground. (Analog signals have no ground reference;

they are limited to V+ and V-.)

Reset Input. Connect to digital (logic) supply (or V+). Drive low to set all switches off and set internal shift registers to 0.

MAX395 TOC12

8

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

_______________Detailed Description

The MAX395’s interface can be thought of as an 8-bit

shift register controlled by CS (Figure 2). While CS is

low, input data appearing at DIN is clocked into the

shift register synchronously with SCLK’s rising edge.

The data is an 8-bit word, each bit controlling one of

eight switches in the MAX395 (Table 1). DOUT is the

shift register’s output, with data appearing synchronously with SCLK’s falling edge. Data at DOUT is simply the input data delayed by eight clock cycles.

When shifting the input data, D7 is the first bit in and

out of the shift register. While shifting data, the switches

remain in their previous configuration. When the eight

bits of data have been shifted in, CS is driven high. This

updates the new switch configuration and inhibits further data from entering the shift register. Transitions at

DIN and SCLK have no effect when CS is high, and

DOUT holds the first input bit (D7) at its output.

More or less than eight clock cycles can be entered

during the CS low period. When this happens, the shift

CS

t

CSH0

SCLK

DIN

Basic Operation

t

CSS

t

t

CH

DS

t

DH

t

DO

register will contain only the last eight serial data bits,

regardless of when they were entered. On the rising

edge of CS

, all the switches will be set to the corre-

sponding states.

The MAX395’s three-wire serial interface is compatible

with SPI™, QSPI™, and Microwire™ standards. If interfacing with a Motorola processor serial interface, set

CPOL = 0. The MAX395 is considered a slave device

(Figures 2 and 3). Upon power-up, the shift register

contains all zeros, and all switches are off.

The latch that drives the analog switch is updated on

the rising edge of CS, regardless of SCLK’s state. This

meets all the SPI and QSPI requirements.

Daisy Chaining

For a simple interface using several MAX395s, “daisy

chain” the shift registers as shown in Figure 5. The CS

pins of all devices are connected together, and a

stream of data is shifted through the MAX395s in series.

When CS is brought high, all switches are updated

simultaneously. Additional shift registers may be included anywhere in series with the MAX395 data chain.

t

CLL

t

t

CSH1

CSH2

t

OFF

• • •

• • •

t

CL

• • •

MAX395

DOUT

COM OUT

Figure 1. Timing Diagram

______________________________________________________________________________________ 11

• • •

• • •

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

CS

SWITCHES

UPDATED

SCLK

MAX395

DIN

D7 D6 D5 D4 D3 D2 D1 D0

DATA BITS

DOUT

D0

D7 D6 D5 D4 D3 D2 D1 D0

DATA BITS FROM PREVIOUS DATA INPUT

Figure 2. Three-Wire Interface Timing

Table 1. Serial-Interface Switch Programming

RESET

D7

D6

X0

01

11

X1

X1

X1

X1

X1

X1

X1

X1

X1

X1

X1

X1

X1

X

X

X

0

1

X

X

X

X

X

X

X

X

X

X

X

X XX XX1 1X Switch 0 closed (on)X

D5

X

X X

X

X

0

1

X

X

X

X

X

X

X

X

X

DATA BITS

D4

X

X

XX

X

X

X

0

1

X

X

X

X

X

X

X

When several serial devices are configured as slaves,

Addressable Serial Interface

addressable by the processor, DIN pins of each

decode logic individually control CS of each slave

device. When a slave is selected, its CS pin is driven

low, data is shifted in, and CS is driven high to latch the

data. Typically, only one slave is addressed at a time.

DOUT is not used.

__________Applications Information

The MAX395 can be used as a multiplexer, but to

obtain the same electrical performance with slightly

improved programming speed, use the MAX349 8channel mux or the MAX350 dual 4-channel mux, both

in 18-pin packages.

D3

X

X X

X

X

X

X

X

X

0

1

X

X

X

X

X

D2

D1

X

X

XX

X

X

X

X

X

X

X

0

1

X

X

X

X

X X

X

X

X

X

X

X

X

X

X

X

0

1

X

D0

X

X

XX

X

X

X

X

X

X

X

X

X

X

X

0

FUNCTION

All switches open, D7–D0 = 0

Switch 7 open (off)

Switch 7 closed (on)

Switch 6 open (off)

Switch 6 closed (on)

Switch 5 open (off)

Switch 5 closed (on)

Switch 4 open (off)

Switch 4 closed (on)

Switch 3 open (off)

Switch 3 closed (on)

Switch 2 open (off)

Switch 2 closed (on)

Switch 1 open (off)

Switch 1 closed (on)

Switch 0 open (off)

Multiplexers

12 ______________________________________________________________________________________

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

To use the MAX395 as an 8x1 multiplexer, connect all

8x1 Multiplexer

common pins together (COM0–COM7) to form the mux

output; the mux inputs are NO0–NO7.

The mux can be programmed normally, with only one

channel selected for every eight clock pulses, or it can

be programmed in a fast mode, where channel changing occurs on each clock pulse. In this mode, the channels are selected by sending a single high pulse

(corresponding to the selected channel) at DIN, and a

corresponding CS low pulse for every eight clock pulses. As this is clocked through the register by SCLK,

each switch sequences one channel at a time, starting

with Channel 7.

SCLK

MAX395

DIN

DOUT

CS

THE DOUT-SI CONNECTION IS NOT REQUIRED FOR WRITING TO THE

MAX395, BUT MAY BE USED FOR DATA-ECHO PURPOSES.

Figure 3. Connections for Microwire

SK

SO

SI

I/O

MICROWIRE

PORT

Dual, Differential 4-Channel Multiplexer

To use the MAX395 as a dual (4x2) mux, connect

COM0–COM3 together and connect COM4–COM7

together, forming the two outputs. The mux input pairs

become NO0/NO4, NO1/NO5, NO2/NO6, and NO3/NO7.

The mux can be programmed normally, with only one

differential channel selected for every eight clock pulses, or it can be programmed in a fast mode, where

channel changing occurs on each clock pulse.

In fast mode, the channels are selected by sending two

high pulses spaced four clock pulses apart (corresponding to the two selected channels) at DIN, and a

corresponding CS low pulse for each of the first eight

clock pulses. As this is clocked through the register by

DOUT

MAX395

DIN

SCLK

CS

THE DOUT-MISO CONNECTION IS NOT REQUIRED FOR WRITING TO THE

MAX395, BUT MAY BE USED FOR DATA-ECHO PURPOSES.

Figure 4. Connections for SPI and QSPI

MISO

MOSI

SPI

PORT

SCK

I/O

CPOL = 0, CPHA = 0

MAX395

SCLK

DIN

CS

Figure 5. Daisy-Chained Connection

SCLK

MAX395

DIN

CS

______________________________________________________________________________________ 13

SCLK

MAX395

DOUT DOUT DOUT

DIN

CS

SCLK

MAX395

DIN

CS

TO OTHER

SERIAL DEVICES

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

DIN

SCLK

CS1

MAX395

CS2

CS3

TO OTHER

SERIAL

DEVICES

CS

MAX395

SCLK

DIN

Figure 6. Addressable Serial Interface

D4

SCLK

SW4

DIN

Figure 7. Differential Multiplexer Input Control

FOUR CLOCK

PULSES

D0

SW0

SCLK, each switch sequences one differential channel

at a time, starting with channel 7/0. After the first eight

bits have been sent, subsequent channel sequencing

can occur by repeating this sequence or, even faster,

by sending only one DIN high pulse and one CS low

pulse for each four clock pulses.

SPDT Switches

To use the MAX395 as a quad, single-pole/doublethrow (SPDT) switch, connect COM0 to NO1, COM2 to

NO3, COM4 to NO5, and COM6 to NO7, forming the

four “common” pins. Program these four switches with

pairs of instructions, as shown in Table 2.

CS

MAX395

SCLK

DIN

CS

MAX395

SCLK

DIN

Reset Function

RESET is the internal reset pin. It is usually connected

to a logic signal or V+. Drive RESET low to open all

switches and set the contents of the internal shift register to zero simultaneously. When RESET is high, the

part functions normally and DOUT is sourced from V+.

RESET must not be driven beyond V+ or GND.

Power-Supply Considerations

The MAX395 construction is typical of most CMOS analog switches. It has three supply pins: V+, V-, and

GND. V+ and V- are used to drive the internal CMOS

switches and to set the limits of the analog voltage on

any switch. Reverse ESD-protection diodes are internally connected between each analog signal pin and

both V+ and V-. If any analog signal exceeds V+ or V-,

one of these diodes will conduct. During normal operation, these (and other) reverse-biased ESD diodes leak,

forming the only current drawn from V+ or V-.

Virtually all the analog leakage current is through the

ESD diodes. Although the ESD diodes on a given signal pin are identical, and therefore fairly well balanced,

they are reverse biased differently. Each is biased by

either V+ or V- and the analog signal. This means their

leakages vary as the signal varies. The difference in the

two diode leakages to the V+ and V- pins constitutes

the analog signal-path leakage current. All analog leak-

Overview

14 ______________________________________________________________________________________

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

Table 2. SPDT Switch Programming

RESET

D7

X0

01

11

X1

X1

X1

X1

D6

X

1

0

X

X

X

X

X XX XX1 10 Switch 1 off and 0 onX

X XX XX1 01 Switch 0 off and 1 onX

D5

X

X

X

0

1

X

X

age current flows to the supply terminals, not to the

other switch terminal. This is why both sides of a given

switch can show leakage currents of either the same or

opposite polarity.

There is no connection between the analog signal

paths and GND.

V+ and GND power the internal logic and logic-level

translators, and set both the input and output logic limits. The logic-level translators convert the logic levels to

switched V+ and V- signals to drive the analog signal

gates. This drive signal is the only connection between

the logic supplies (and signals) and the analog supplies. V+, and V- have ESD-protection diodes to GND.

The logic-level inputs and output have ESD protection

to V+ and to GND.

The logic-level thresholds are CMOS and TTL compatible when V+ is +5V. As V+ is raised, the threshold

increases slightly. So when V+ reaches +12V, the

threshold is about 3.1V; slightly above the TTL guaranteed high-level minimum of 2.8V, but still compatible

with CMOS outputs.

The MAX395 operates with bipolar supplies between

±3.0V and ±8V. The V+ and V- supplies need not be

symmetrical, but their sum cannot exceed the absolute

maximum rating of 17V. Do not connect the MAX395

V+ to +3V and connect the logic-level pins to TTL

logic-level signals. This exceeds the absolute maximum ratings and can damage the part and/or external circuits.

DATA BITS

D4

X

X

X

1

0

X

X

D3

Bipolar Supplies

D2

X

X

X

X

X

0

1

X

X

X

X

X

1

0

D1

X

X

X

X

X

X

X

D0

X

X

X

X

X

X

X

FUNCTION

All switches open, D7–D0 = 0

Switch 7 off and 6 on

Switch 6 off and 7 on

Switch 5 off and 4 on

Switch 4 off and 5 on

Switch 3 off and 2 on

Switch 2 off and 3 on

The MAX395 operates from a single supply between

+3V and +16V when V- is connected to GND. All of the

bipolar precautions must be observed.

High-Frequency Performance

In 50Ω systems, signal response is reasonably flat up

to 50MHz (see

Typical Operating Characteristics)

Above 20MHz, the on-response has several minor

peaks that are highly layout dependent. The problem is

not turning the switch on, but turning it off. The off-state

switch acts like a capacitor and passes higher frequencies with less attenuation. At 10MHz, off isolation is

about -45dB in 50Ω systems, becoming worse (approximately 20dB per decade) as frequency increases.

Higher circuit impedances also make off isolation

worse. Adjacent channel attenuation is about 3dB

above that of a bare IC socket, and is due entirely to

capacitive coupling.

MAX395

Single Supply

.

______________________________________________________________________________________ 15

Serially Controlled, Low-Voltage,

8-Channel SPST Switch

___________________Chip Topography

NO5

COM5

NO4

COM4

MAX395

COM6

NO6

COM7

NO7

V-

DOUT CS V+

RESET

0.100"

(2.54mm)

TRANSISTOR COUNT: 500

SUBSTRATE CONNECTED TO V+.

NO3 NO2

COM3

SCLK

COM2

DIN

COM1

NO1

COM0

NO0

GND

0.120"

(3.05mm)

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16

__________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1995 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

Loading...

Loading...