General Description

The MAX3890 serializer is ideal for converting 16-bitwide, 155Mbps parallel data to 2.5Gbps serial data in

ATM and SDH/SONET applications. Operating from a

single +3.3V supply, this device accepts low-voltage

differential-signal (LVDS) clock and data inputs for

interfacing with high-speed digital circuitry, and delivers PECL serial data and clock outputs. A fully integrated PLL synthesizes an internal 2.5GHz serial clock from

a 155.52MHz, 77.76MHz, 51.84MHz, or 38.88MHz reference clock. A loopback data output is provided to

facilitate system diagnostic testing.

The MAX3890 is available in the extended temperature

range (-40°C to +85°C) in a 64-pin TQFP exposedpaddle (EP) package.

Applications

2.5Gbps SDH/SONET Transmission Systems

2.5Gbps ATM/SONET Access Nodes

Add/Drop Multiplexers

Digital Cross-Connects

ATM Backplanes

Features

♦ Single +3.3V Supply

♦ 495mW Power Consumption

♦ Exceeds ANSI, ITU, and Bellcore Specifications

♦ 155Mbps (16-bit wide) Parallel to 2.5Gbps Serial

Conversion

♦ Clock Synthesis for 2.5Gbps

♦ Multiple Clock Reference Frequencies

(155.52MHz, 77.76MHz, 51.84MHz, 38.88MHz)

♦ LVDS Parallel Clock and Data Inputs

♦ Additional High-Speed Output for System

Loopback Testing

MAX3890

+3.3V, 2.5Gbps, SDH/SONET 16:1 Serializer

with Clock Synthesis and LVDS Inputs

________________________________________________________________

Maxim Integrated Products

1

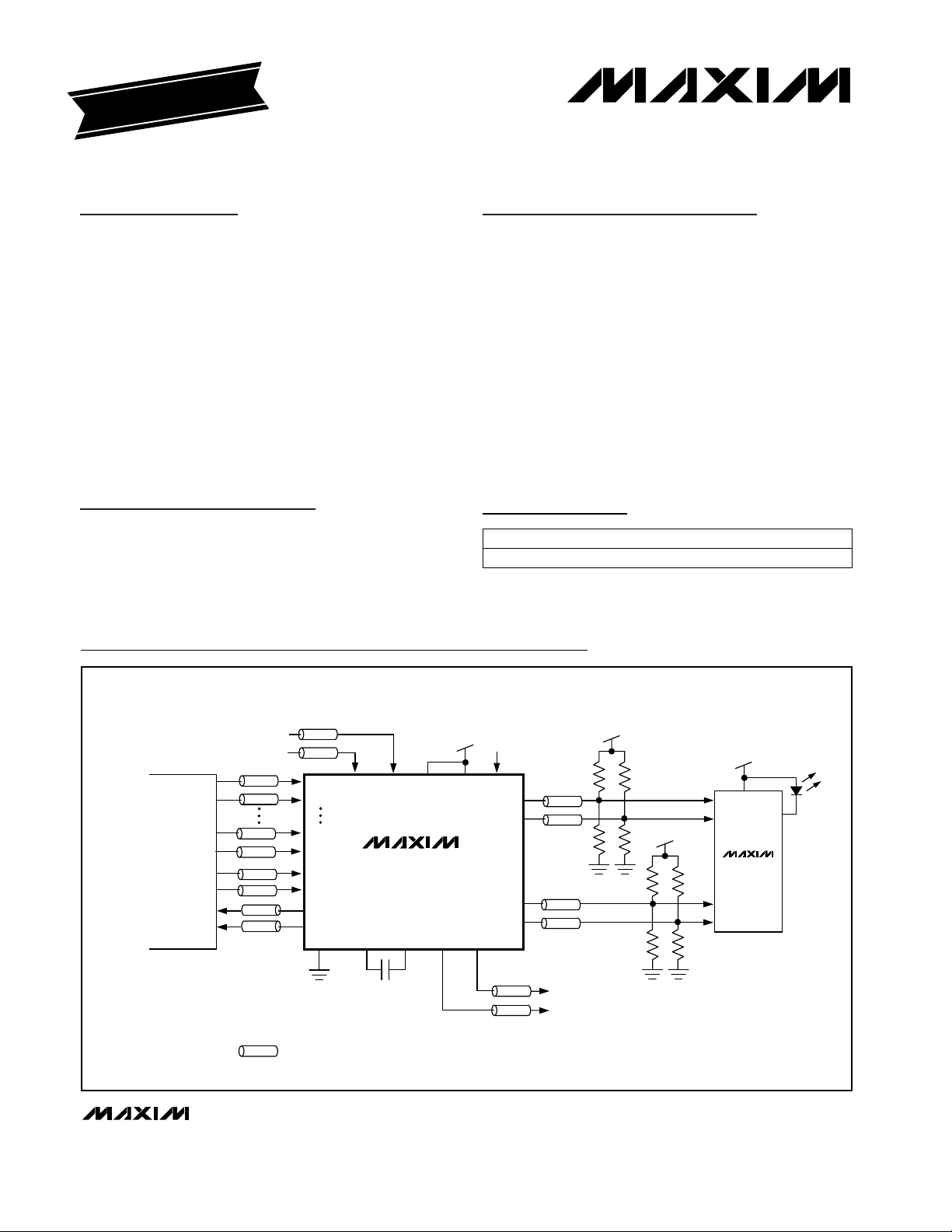

Typical Operating Circuit

19-1498; Rev 0; 6/99

PART

MAX3890ECB -40°C to +85°C

TEMP. RANGE PIN-PACKAGE

64 TQFP-EP*

Ordering Information

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

Pin Configuration appears at end of data sheet.

EVALUATION KIT

AVAILABLE

*

EP = Exposed Paddle

155MHz REF. CLOCK INPUT

OVERHEAD

GENERATION

+3.3V

RCLK+ RCLK- V

PDI0+

PDI0-

PDI15+

PDI15-

PCLKI+

PCLKI-

PCLKO+

PCLKO-

GND

THIS SYMBOL REPRESENTS A TRANSMISSION LINE

OF CHARACTERISTIC IMPEDANCE (Z

FIL+

MAX3890

330nF

FIL-

CLKSET

SLBO+

= 50Ω).

0

CC

SLBO-

TTL

SOS

SDO+

SDO-

SCLKO+

SCLKO-

+3.3V

130Ω

82Ω

OPTIONAL CONNECTION TO MAX3880

FOR SYSTEM LOOPBACK TESTING.

130Ω

82Ω

+3.3V

130Ω

82Ω

130Ω

82Ω

+3.3V

V

CC

MAX3867

MAX3890

+3.3V, 2.5Gbps, SDH/SONET 16:1 Serializer

with Clock Synthesis and LVDS Inputs

2 _______________________________________________________________________________________

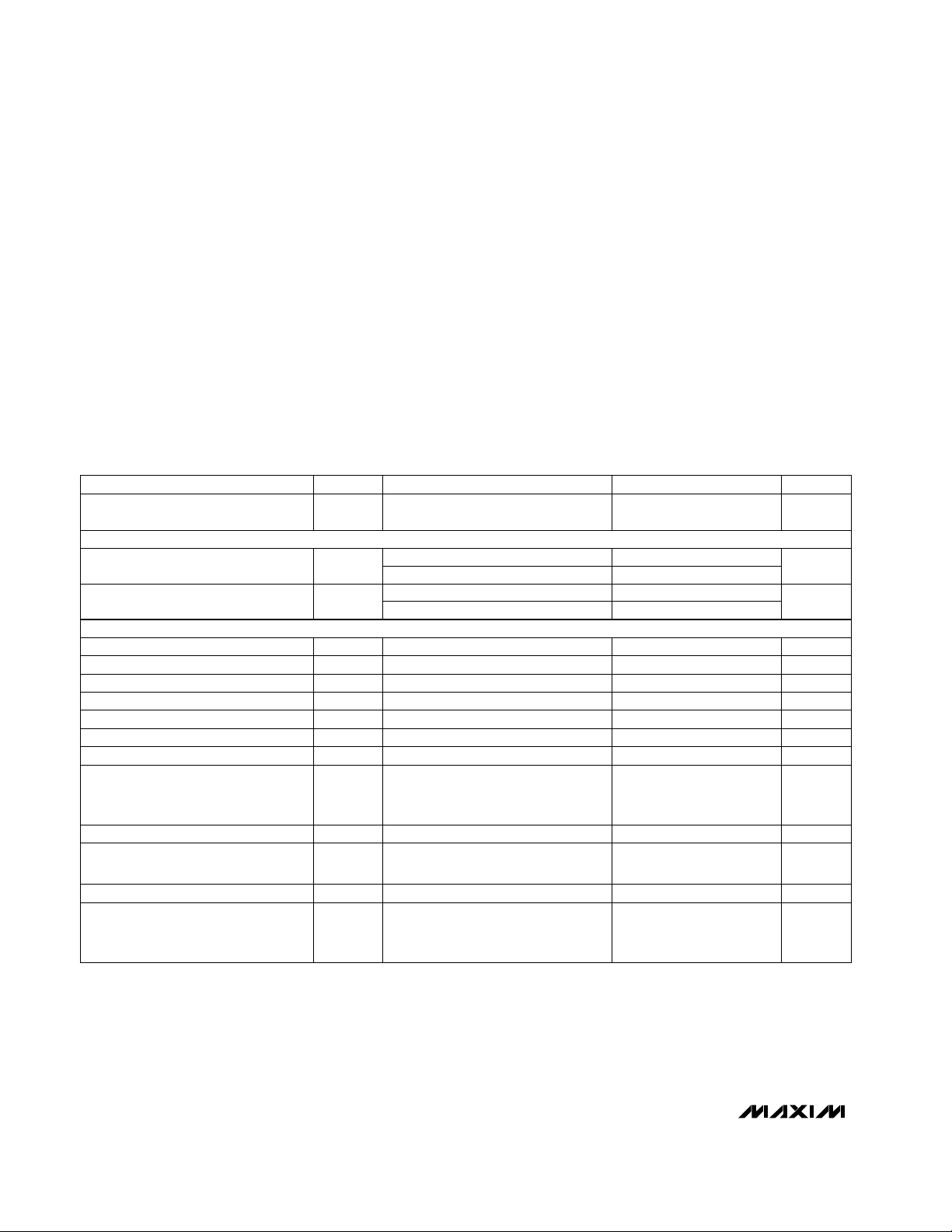

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(VCC= +3.0V to +3.6V, differential LVDS loads = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), CML loads = 50Ω ±1% to VCC,

T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Terminal Voltage (with respect to GND)

V

CC

.......................................................................-0.5V to +5V

All Inputs, FIL+, FIL-...............................-0.5V to (V

CC

+ 0.5V)

Output Current

LVDS Outputs (PCLKO±)................................................10mA

PECL Outputs (SDO±, SCLKO±)....................................50mA

CML Outputs (SLBO±)....................................................15mA

Continuous Power Dissipation (T

A

= +85°C)

TQFP-EP (derate 44.8mW/°C above +85°C) ......................1W

Operating Temperature Range ...........................-40°C to +85°C

Storage Temperature Range .............................-60°C to +150°C

Lead Temperature (soldering, 10sec) .............................+300°C

T

A

= 0°C to +85°C

PECL outputs unterminated,

SOS = low

TA= 0°C to +85°C

Differential input voltage = 100mV

CONDITIONS

V

VCC- 1.025 VCC- 0.88

V

OH

Output Voltage High

mA150 230I

CC

Supply Current

V0.925V

OL

Output Voltage Low

V1.475V

OH

Output Voltage High

Ω

85 100 115R

IN

Differential Input Resistance

mV60V

HYST

Threshold Hysteresis

V

VCC- 1.81 VCC- 1.62

V

OL

Output Voltage Low

V0 2.4V

I

Input Voltage Range

mV-100 100V

IDTH

Differential Input Threshold

UNITSMIN TYP MAXSYMBOLPARAMETER

Figure 5

%±2.5 ±10

∆R

O

Change in Magnitude of Single-Ended

Output Resistance for Complementary

Outputs

Ω

40 95 140R

O

Single-Ended Output Resistance

mV±25

∆V

OS

Change in Magnitude of Output Offset

Voltage for Complementary States

mV250 400

|VOD|

Differential Output Voltage

mV±25

∆|VOD|

Change in Magnitude of Differential

Output Voltage for Complementary

States

V1.125 1.275V

OS

Output Offset Voltage

TA= -40°C V

CC

- 1.085 VCC- 0.88

TA= -40°C VCC-1.83 VCC- 1.555

PECL OUTPUTS (SDO±, SCLKO±)

LVDS INPUTS AND OUTPUTS (PCLKO±, PDI_±, PCLKI±, RCLKI±)

MAX3890

+3.3V, 2.5Gbps, SDH/SONET 16:1 Serializer

with Clock Synthesis and LVDS Inputs

_______________________________________________________________________________________ 3

Note 1: AC characteristics guaranteed by design and characterization.

Note 2: Setup and hold times are relative to the rising edge of PCLKI+, measured by applying a 155.52MHz differential parallel

clock with rise/fall time = 1ns (20% to 80%). See Figure 2.

Note 3: For f

RCLK

= 38.88MHz, the minimum reference clock amplitude is ≥ 200mV.

(Note 2)

(Note 2)

Figure 2

Jitter bandwidth = 12kHz to 20MHz,

RCLK amplitude >

|V

IDTH

| (Note 3)

20% to 80%

CONDITIONS

ps700t

H

Parallel Data-Hold Time

ps300t

SU

GHz2.488f

SCLK

Serial Clock Rate

Parallel Data Setup Time

ns0 +4.0t

SKEW

PCLKO to PCLKI Skew

ps

RMS

3

Φ

0

Output Jitter Generation (SCLKO±)

ps120t

R, tF

PECL Differential Output Rise/Fall

Time

UNITSMIN TYP MAXSYMBOLPARAMETER

AC ELECTRICAL CHARACTERISTICS

(VCC= +3.0V to +3.6V, differential LVDS load = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), CML loads = 50Ω ±1% to VCC,

T

A

= -40°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C.) (Note 1)

MHz155.52f

PCLKI

Parallel Input Clock Rate

20% to 80%, f = 155.52MHz ns1.0

t

R

, t

F

Reference Clock Input (RCLKI)

Rise/Fall Time

20% to 80% ns1.0

t

R

, t

F

Parallel Clock Output (PCLKO)

Rise/Fall Time

SCLKO rising edge to SDO edge ps110 290t

SCLK-SD

Serial Clock Output (SCLKO) to

Serial-Data Output (SDO) Delay

DC ELECTRICAL CHARACTERISTICS (continued)

(VCC= +3.0V to +3.6V, differential LVDS loads = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), CML loads = 50Ω ±1% to V

CC,

TA= -40°C to +85°C, unless otherwise noted. Typical values are at VCC= +3.3V, TA= +25°C.)

CONDITIONS

µA-10 10I

IL

V0.8V

IL

Input Voltage Low

µA-10 10I

IH

Input Current High

Input Current Low

UNITSMIN TYP MAXSYMBOLPARAMETER

Ω50R

O

Single-Ended Output Resistance

mV100 400

|VOD|

Differential Output Voltage

CLKSET = 0 or V

CC

µA±500I

CLKSET

CLKSET Input Current

V2.0V

IH

Input Voltage High

TTL INPUT (SOS)

PROGRAMMING INPUT (CLKSET)

CURRENT MODE LOGIC (CML) OUTPUTS (SLBO±)

MAX3890

+3.3V, 2.5Gbps, SDH/SONET 16:1 Serializer

with Clock Synthesis and LVDS Inputs

4 _______________________________________________________________________________________

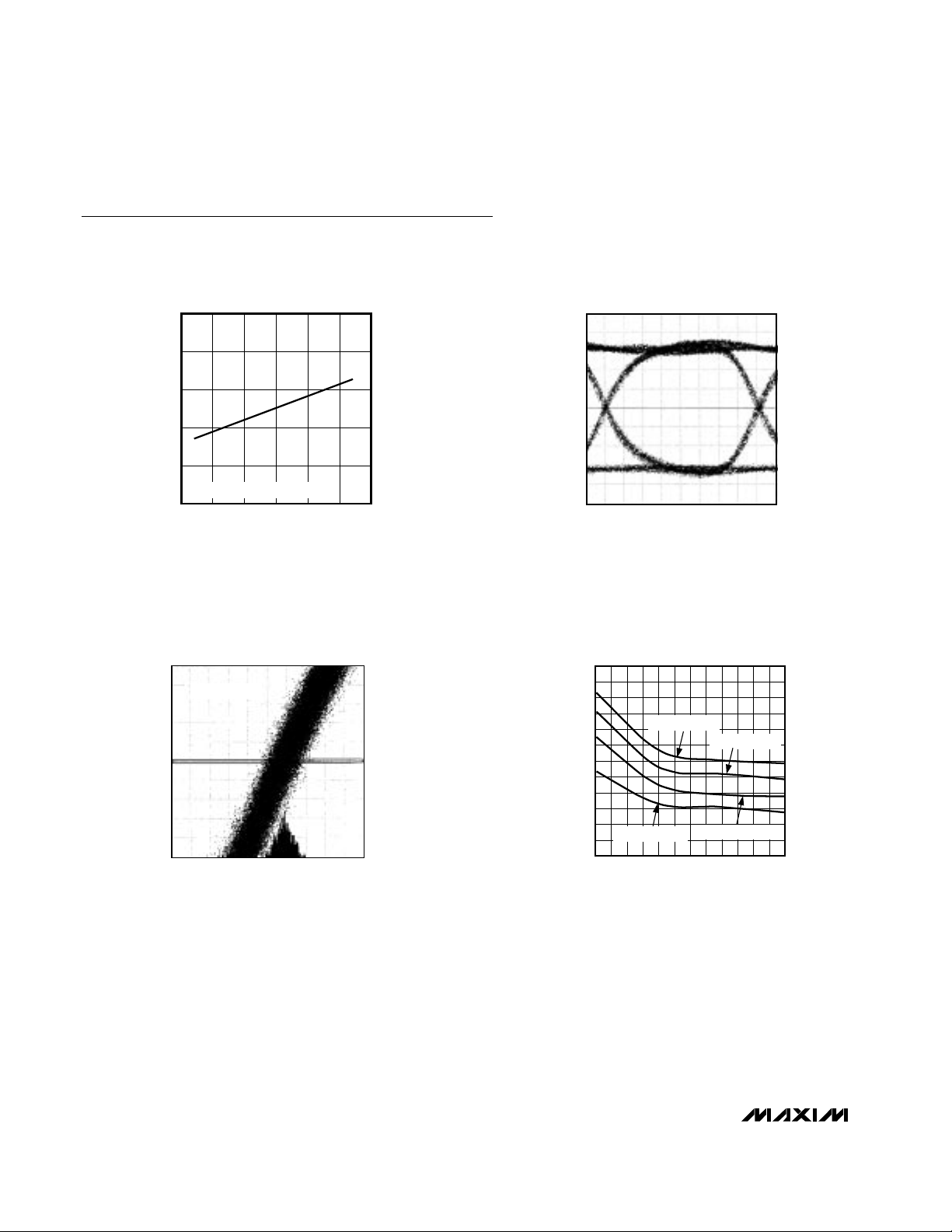

Typical Operating Characteristics

(VCC= +3.3V, PECL loads = 50Ω ±1%, TA= +25°C, unless otherwise noted.)

SUPPLY CURRENT

200

vs. TEMPERATURE

SERIAL-DATA OUTPUT EYE DIAGRAM

180

160

140

SUPPLY CURRENT (mA)

120

PECL OUTPUTS UNTERMINATED

100

-50 -25 25 100

SERIAL-DATA OUTPUT JITTER

f

RCK

050

TEMPERATURE (°C)

= 155.52MHz

MAX3890-01

75

50ps/div

MAX3890-02

OUTPUT JITTER GENERATION

vs. RCLK AMPLITUDE

f

= 38.88MHz

RCLK

f

RCLK

MAX3890 toc04

= 51.84MHz

MAX3890-03

3.0

2.5

2.0

1.5

1.0

f

= 155.52MHz

RCK

5ps/div

TOTAL WIDEBAND RMS JITTER = 2.155ps,

PEAK-TO-PEAK JITTER = 15.7ps

OUTPUT JITTER GENERATION (ps)

0.5

f

= 155.52MHz

RCLK

0

100 150 200 250 300 350 400

RCLK AMPLITUDE (mV)

f

RCLK

= 77.76MHz

Loading...

Loading...