General Description

The MAX3693 serializer is ideal for converting 4-bitwide, 155Mbps parallel data to 622Mbps serial data in

ATM and SDH/SONET applications. Operating from a

single +3.3V supply, this device accepts low-voltage

differential-signal (LVDS) clock and data inputs for

interfacing with high-speed digital circuitry, and delivers a 3.3V PECL serial-data output. A fully integrated

PLL synthesizes an internal 622Mbps serial clock from

a 155.52MHz, 77.76MHz, 51.84MHz, or 38.88MHz reference clock.

The MAX3693 is available in the extended temperature

range (-40°C to +85°C), in a 32-pin TQFP package.

Applications

622Mbps SDH/SONET Transmission Systems

622Mbps ATM/SONET Access Nodes

Add/Drop Multiplexers

Digital Cross Connects

Features

♦ Single +3.3V Supply

♦ 155Mbps (4-bit-wide) Parallel to

622Mbps Serial Conversion

♦ Clock Synthesis for 622Mbps

♦ 215mW Power

♦ Multiple Clock Reference Frequencies

(155.52MHz, 77.76MHz, 51.84MHz, 38.88MHz)

♦ LVDS Parallel Clock and Data Inputs

♦ Differential 3.3V PECL Serial-Data Output

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

________________________________________________________________

Maxim Integrated Products

1

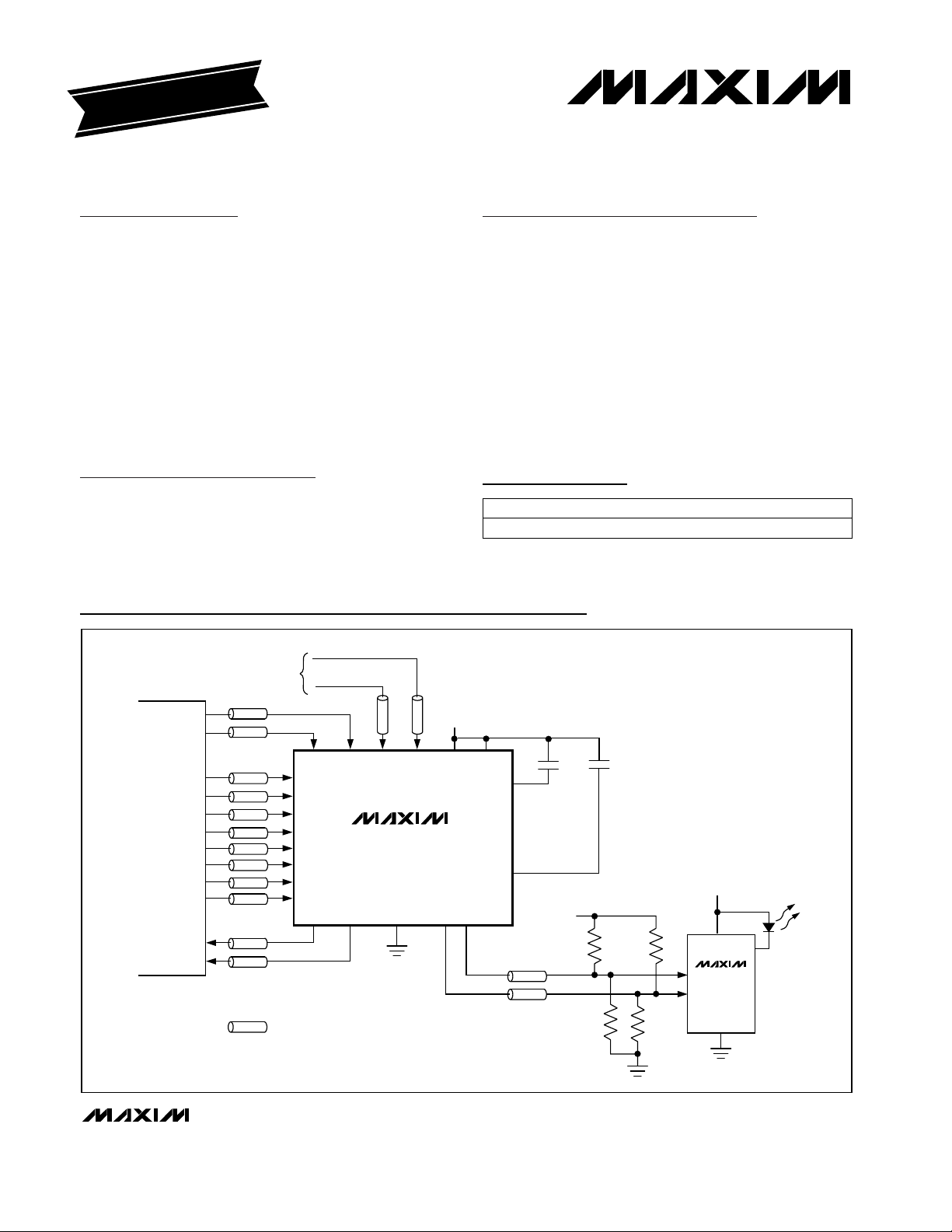

Typical Operating Circuit

19-4775; Rev 1; 4/99

PART

MAX3693ECJ -40°C to +85°C

TEMP. RANGE PIN-PACKAGE

32 TQFP

Ordering Information

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800.

For small orders, phone 1-800-835-8769.

Pin Configuration appears at end of data sheet.

EVALUATION KIT

AVAILABLE

(155MHz LVDS CRYSTAL REFERENCE)

OVERHEAD

GENERATION

= +3.3V

V

CC

PCLKI- PCLKI+ RCLK- V

PD0+

PD0-

PD1+

PD1-

PD2+

PD2PD3+

PD3-

THIS SYMBOL REPRESENTS A TRANSMISSION LINE

OF CHARACTERISTIC IMPEDANCE (Z

RCLK+

MAX3693

= 50Ω)

0

CKSET

CC

FIL+

FIL-

SD-GNDPCLKO- PCLKO+

SD+

V

= +3.3V

CC

130Ω 130Ω

1µF

1µF

82Ω

= +3.3V

V

CC

MAX3668

82Ω

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

2 _______________________________________________________________________________________

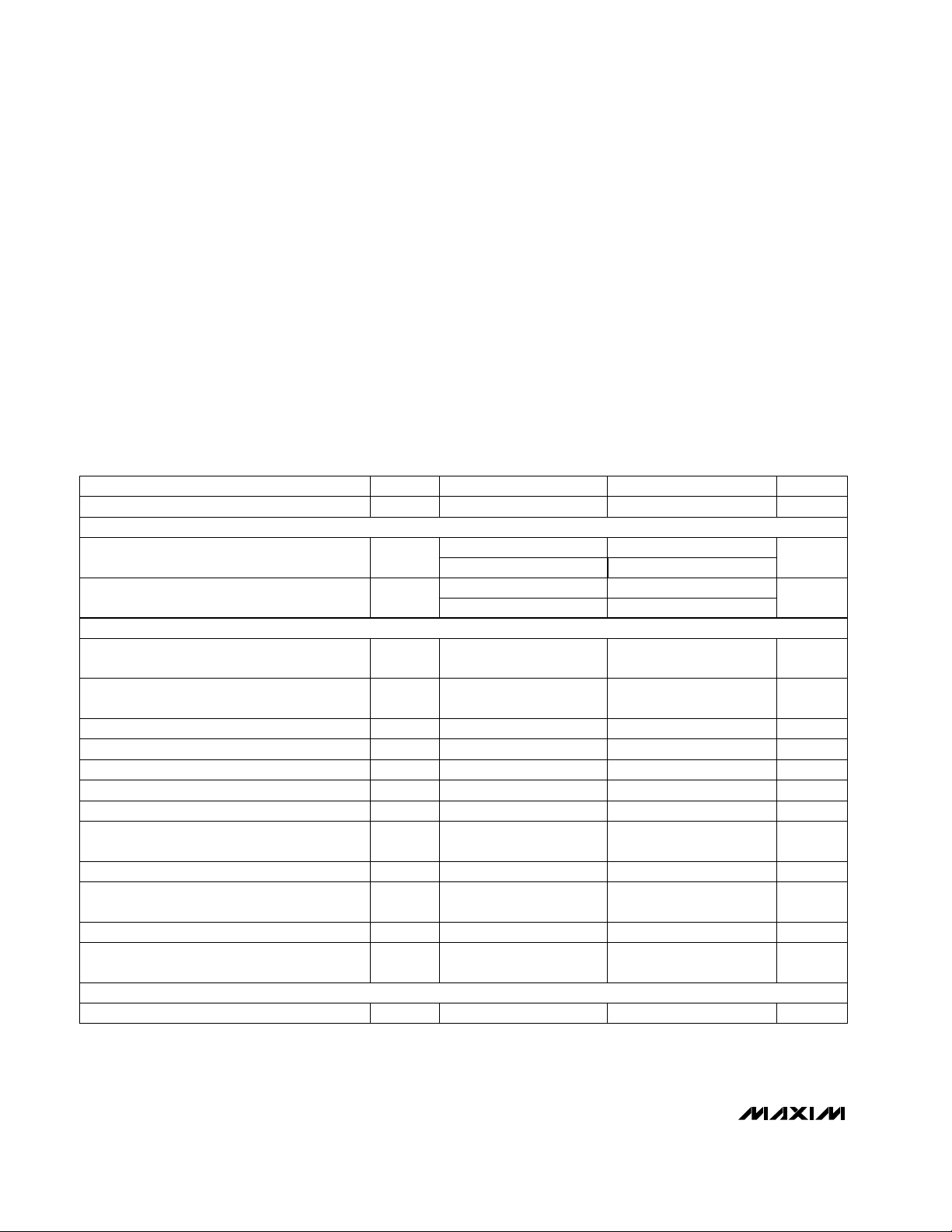

ABSOLUTE MAXIMUM RATINGS

DC ELECTRICAL CHARACTERISTICS

(V

CC

= +3V to +3.6V, differential LVDS loads = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), TA= -40°C to +85°C, unless other-

wise noted. Typical values are at V

CC

= +3.3V, TA= +25°C.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Terminal Voltage (with respect to GND)

V

CC

.......................................................................-0.5V to +5V

All Inputs, FIL+, FIL-,

PCLKO+, PCLKO- ..............................-0.5V to (V

CC

+ 0.5V)

Output Current

LVDS Outputs (PCLKO±)................................................10mA

PECL Outputs (SD±).......................................................50mA

Continuous Power Dissipation (T

A

= +85°C)

TQFP (derate 10.20mW/°C above +85°C)...................663mW

Operating Temperature Range ...........................-40°C to +85°C

Storage Temperature Range .............................-60°C to +160°C

Lead Temperature (soldering, 10sec) .............................+300°C

T

A

= 0°C to +85°C

PECL outputs unterminated

TA= 0°C to +85°C

Differential input voltage =

100mV

Common-mode voltage =

50mV

CONDITIONS

V

VCC- 1.025 VCC- 0.88

V

OH

Output High Voltage

mA38 65 100I

CC

Supply Current

V0.925V

OL

Output Low Voltage

V1.475V

OH

Output High Voltage

Ω

85 100 115R

IN

Differential Input Resistance

mV60V

HYST

Threshold Hysteresis

V

VCC- 1.81 VCC- 1.62

V

OL

Output Low Voltage

V0 2.4V

I

Input Voltage Range

mV-100 100V

IDTH

Differential Input Threshold

UNITSMIN TYP MAXSYMBOLPARAMETER

%±2.5 ±10

∆R

O

Change in Magnitude of Single-Ended Output

Resistance for Complementary Outputs

Ω

40 95 140R

O

Single-Ended Output Resistance

mV±25

∆V

OS

Change in Magnitude of Output Offset Voltage

for Complementary States

mV250 400

|VOD|

Differential Output Voltage

mV±25

∆|VOD|

Change in Magnitude of Differential Output

Voltage for Complementary States

V1.125 1.275V

OS

Output Offset Voltage

TA= -40°C V

CC

- 1.085 VCC- 0.88

TA= -40°C VCC-1.83 VCC- 1.555

CKSET = 0 or V

CC

µA±500I

CKSET

CKSET Input Current

PECL OUTPUTS (SD±)

LVDS INPUTS AND OUTPUTS (PCLKI±, RCLK±, PCLKO±, PD_±)

PROGRAMMING INPUT (CKSET)

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

_______________________________________________________________________________________ 3

Note 1: AC characteristics guaranteed by design and characterization.

TA= +25°C

CONDITIONS

ps600t

H

Parallel Data-Hold Time

ps200t

SU

MHz622.08f

SCLK

Serial Clock Rate

Parallel Data-Setup Time

ns0 +4.0t

SKEW

PCLKO to PCLKI Skew

ps

RMS

11

Φ

0

Output Random Jitter

ps200t

R, tF

PECL Differential Output

Rise/Fall Time

UNITSMIN TYP MAXSYMBOLPARAMETER

AC ELECTRICAL CHARACTERISTICS

(V

CC

= +3V to +3.6V, differential LVDS load = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), TA= -40°C to +85°C, unless other-

wise noted. Typical values are at V

CC

= +3.3V, TA= +25°C.) (Note 1)

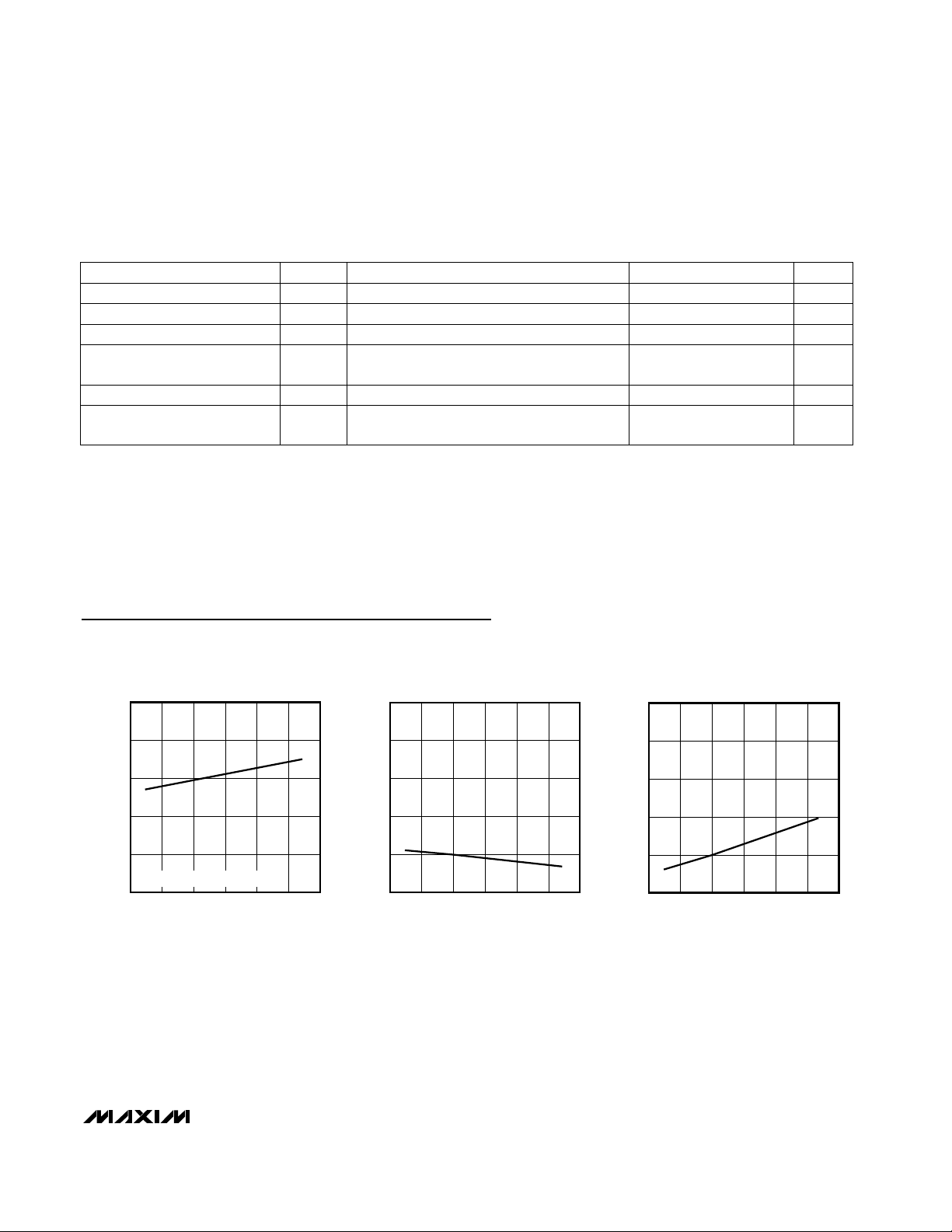

100

0

-50 -25 25 100

SUPPLY CURRENT

vs. TEMPERATURE

20

60

80

MAX3693-01

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

050

40

75

PECL OUTPUTS UNTERMINATED

200

-50

-50 -25 25 100

PARALLEL DATA-SETUP TIME

vs. TEMPERATURE

0

100

150

MAX3693-02

TEMPERATURE (°C)

PARALLEL DATA-SETUP TIME (ps)

050

50

75

250

0

-50 -25 25 100

PARALLEL DATA-HOLD TIME

vs. TEMPERATURE

50

150

200

MAX3693-03

TEMPERATURE (°C)

PARALLEL DATA-HOLD TIME (ps)

050

100

75

Typical Operating Characteristics

(V

CC

= +3.3V, differential LVDS loads = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), TA= +25°C, unless otherwise noted.)

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

4 _______________________________________________________________________________________

Typical Operating Characteristics (continued)

(V

CC

= +3.3V, differential LVDS loads = 100Ω ±1%, PECL loads = 50Ω ±1% to (V

CC

- 2V), TA= +25°C, unless otherwise noted.)

1.1V

0.536V

200ps/div

SERIAL-DATA OUTPUT EYE DIAGRAM

57mV/

div

MAX3693-05

1.0042V

0.904V

10ps/div

SERIAL-DATA OUTPUT JITTER

10mV/

div

MAX3693-06

Mean 25.22ns

RMS∆ 4.073ps

PkPk 32.6ps

µ±1σ 70.373%

µ±2σ 95.357%

µ±3σ 99.759%

f

RCLK

= 155.52MHz

Pin Description

NAME FUNCTION

1, 3, 5, 7 PD0+ to PD3+ Noninverting LVDS Parallel Data Inputs. Data is clocked in on the PCLKI signal’s positive transition.

2, 4, 6, 8 PD0- to PD3- Inverting LVDS Parallel Data Inputs. Data is clocked in on the PCLKI signal’s positive transition.

PIN

9, 17, 18, 19,

24, 25, 32

GND Ground

10 PCLKO-

Inverting LVDS Parallel-Clock Output. Use positive transition of PCLKO to clock the overhead management circuit.

15 SD+ Noninverting PECL Serial-Data Output

14 SD- Inverting PECL Serial-Data Output

12, 13, 16,

21, 28, 29

V

CC

+3.3V Supply Voltage

11 PCLKO+

Noninverting LVDS Parallel-Clock Output. Use positive transition of PCLKO to clock the overhead

management circuit.

23 FIL+ Filter Capacitor Input. See

Typical Operating Circuit

for external-component connections.

22 FIL- Filter Capacitor Input. See

Typical Operating Circuit

for external-component connections.

26 RCLK+

Noninverting LVDS Reference Clock Input. Connect an LVDS-compatible crystal reference clock to

the RCLK inputs.

30 PCLKI+

Noninverting LVDS Parallel Clock Input. Connect the incoming parallel-data-clock signal to the

PCLKI inputs. Note that data is updated on the positive transition of the PCLKI signal.

27 RCLK-

Inverting LVDS Reference Clock Input. Connect an LVDS-compatible crystal reference clock to the

RCLK inputs.

31 PCLKI-

Inverting LVDS Parallel Clock Input. Connect the incoming parallel-data-clock signal to the PCLKI

inputs. Note that data is updated on the positive transition of the PCLKI signal.

20 CKSET

Reference Clock Rate Programming Pin.

CKSET = VCC: Reference Clock Rate = 155.52MHz

CKSET = Open: Reference Clock Rate = 77.76MHz

CKSET = 20kΩ to GND: Reference Clock Rate = 51.84MHz

CKSET = GND Reference Clock Rate = 38.88MHz

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

_______________________________________________________________________________________ 5

_______________Detailed Description

The MAX3693 serializer comprises a 4-bit parallel input

register, a 4-bit shift register, control and timing logic, a

PECL output buffer, LVDS input/output buffers, and a

frequency-synthesizing PLL (consisting of a phase/

frequency detector, loop filter/amplifier, voltagecontrolled oscillator, and prescaler). This device converts 4-bit-wide, 155Mbps data to 622Mbps serial data

(Figure 1).

The PLL synthesizes an internal 622Mbps reference

used to clock the output shift register. This clock is

generated by locking onto the external 155.52MHz,

77.76MHz, 51.84MHz, or 38.88MHz reference-clock

signal (RCLK).

The incoming parallel data is clocked into the

MAX3693 on the rising transition of the parallel-clockinput signal (PCLKI). The control and timing logic

ensure proper operation if the parallel-input register is

latched within a window of time that is defined with

respect to the parallel-clock-output signal (PCLKO).

PCLKO is the synthesized 622Mbps internal serialclock signal divided by four. The allowable PCLKO-toPCLKI skew is 0 to +4ns. This defines a timing window

at about the PCLKO rising edge, during which

a PCLKI rising edge may occur (Figure 2).

Figure 1. Functional Diagram

PD3+

PD3-

PD2+

PD2-

PD1+

PD1-

LVDS

LVDS

LVDS

4-BIT

PARALLEL

INPUT

REGISTER

MAX3693

PD0+

PD0-

PCLKI+

PCLKI-

RCLK+

RCLK-

LVDS

LVDS

LVDS

PHASE/FREQ

DETECT

PRESCALER

FIL+

FIL-

CKSET

VCO

CONTROL

PCLKO+

LVDS

PCLKO-

SHIFT

LATCH

4-BIT

SHIFT

REGISTER

PECL

SD+

SD-

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

6 _______________________________________________________________________________________

Low-Voltage Differential-Signal (LVDS)

Inputs and Outputs

The MAX3693 features LVDS inputs and outputs for

interfacing with high-speed digital circuitry. The LVDS

standard is based on the IEEE 1596.3 LVDS specification. This technology uses 250mV to 400mV differential low-voltage swings to achieve fast transition

times, minimized power dissipation, and noise immunity.

For proper operation, the parallel-clock LVDS outputs

(PCLKO+, PCLKO-) require 100Ω differential DC termi-

nation between the inverting and noninverting outputs.

Do not terminate these outputs to ground.

The parallel data and parallel clock LVDS inputs (PD_+,

PD_-, PCLKI+, PCLKI-, RCLK+, RCLK-) are internally

terminated with 100Ω differential input resistance, and

therefore do not require external termination.

PECL Outputs

The serial-data PECL outputs (SD+, SD-) require 50Ω

DC termination to (VCC- 2V) (see the

Alternative PECL-

Output Termination

section).

Figure 2. Timing Diagram

PCLKO

PCLKI

t

SU

t

SKEW

PD_

SD

NOTE: SIGNALS SHOWN ARE DIFFERENTIAL. FOR EXAMPLE, PCLKO = (PCLKO+) - (PCLKO-).

*PD3 = D3; PD2 = D2; PD1 = D1; PD0 = D0.

VALID PARALLEL DATA*

t

H

D0D1D2D3

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

_______________________________________________________________________________________ 7

___________________Chip Information

TRANSISTOR COUNT: 2925

Figure 3. Alternative PECL-Output Termination

Applications Information

Alternative PECL-Output Termination

Figure 3 shows alternative PECL output-termination

methods. Use Thevenin-equivalent termination when a

(VCC- 2V) termination voltage is not available. If AC

coupling is necessary, be sure that the coupling capac-

itor is placed following the 50Ω or Thevenin-equivalent

DC termination.

Layout Techniques

For best performance, use good high-frequency layout

techniques. Filter voltage supplies and keep ground

connections short. Use multiple vias where possible.

Also, use controlled-impedance transmission lines to

interface with the MAX3693 clock and data inputs and

outputs.

TQFP

TOP VIEW

FIL+

FIL-

VCCCKSET

GND

GND

GND

GND

PD0-

PD1+

PD1-

PD2+

PD2-

PD0+

PD3-

PD3+

SD+

SD-

PCLKO-

V

CC

V

CC

PCLKO+

V

CC

GND

RCLK+

RCLK-

PCLKI-

V

CC

V

CC

PCLKI+

GND

GND

32

31

30

29

28

27

26

25

17

18

19

20

21

22

23

24

9

10

11

12

13

14

15

16

8

7

6

5

4

3

2

1

MAX3693

Pin Configuration

+3.3V

130Ω

PECL

INPUTS

MAX3693

SD+

SD-

Z

Z

= 50Ω

0

= 50Ω

0

130Ω

82Ω 82Ω

MAX3693

SD+

SD-

= 50Ω

Z

0

Z

= 50Ω

0

50Ω 50Ω

V

- 2V

CC

HIGHIMPEDENCE

INPUTS

MAX3693

+3.3V, 622Mbps, SDH/SONET 4:1 Serializer

with Clock Synthesis and LVDS Inputs

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

8

_____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1999 Maxim Integrated Products Printed USA is a registered trademark of Maxim Integrated Products.

________________________________________________________Package Information

32L/48L,TQFP.EPS

Loading...

Loading...