Page 1

19-0067; Rev 0; 2/05

可提供评估板

高中频(HI-IF)单片宽带调谐器

_________________________________

概述

MAX3570/MAX3571/MAX3573低成本、宽带、两次变频调

谐器芯片设计用于数字电视接收机。每款芯片集成了所

有必需的射频功能模块,其中包括一个集成的高中频滤

波器、全集成VCO、中频VGA。工作频率范围从50MHz

至878MHz,同时提供超过60dB的RF及IF可控增益范围。

MAX3570/MAX3571具有以44MHz为中心的中频频率,而

MAX3573具有以36MHz为中心的中频输出。

这三款芯片都包括了可变增益射频前端,噪声系数仅为

8dB。双频合成器产生两个本振 (LO) 频率,提供优异的

相位噪声性能,在10kHz频偏时相位噪声为-86dBc/Hz。集

成的高中频(HI-IF ) 滤波器有55dBc (典型值) 的镜像抑制。

仅需要一个中频SAW滤波器、无源环路滤波器和晶体振

荡器即可构建完整的单芯片调谐器。MAX3570芯片编程

和配置由3线串行接口完成,而MAX3571/MAX3573芯片

编程和配置由2线串行接口完成。

MAX3570/MAX3571/MAX3573采用48引脚QFN-EP封装,

可工作于商业温度范围 (0°C 至 +70°C)。

_________________________________

应用

DVB-C数字电视接收机

ATSC数字电视接收机

有线电视调制解调器

DOCSIS/EURO DOCSIS调制解调器

ITU J.83数字机顶盒

_____________________________

PART SERIAL INTERFACE

MAX3570 3-Wire 44

MAX3571 2-Wire 44

MAX3573 2-Wire 36

选择指南

IF CENTER

FREQUENCY

(MHz)

___________________________________ 特性

全集成HI-IF滤波器

♦

全集成VCO,无需外部元器件和走线。

♦

8dB低噪声系数

♦

高线性—大于54dBc, CSO, CTB, X-MOD。

♦

业界最小的封装

♦

优异的相位噪声,可用于256-QAM、8-VSB和

♦

COFDM。

______________________________

PART TEMP RANGE PIN-PACKAGE

MAX3570CGM 0°C to +70°C 48 QFN-EP*

MAX3571CGM 0°C to +70°C 48 QFN-EP*

MAX3573CGM 0°C to +70°C 48 QFN-EP*

*

EP = 裸露焊盘。

定购信息

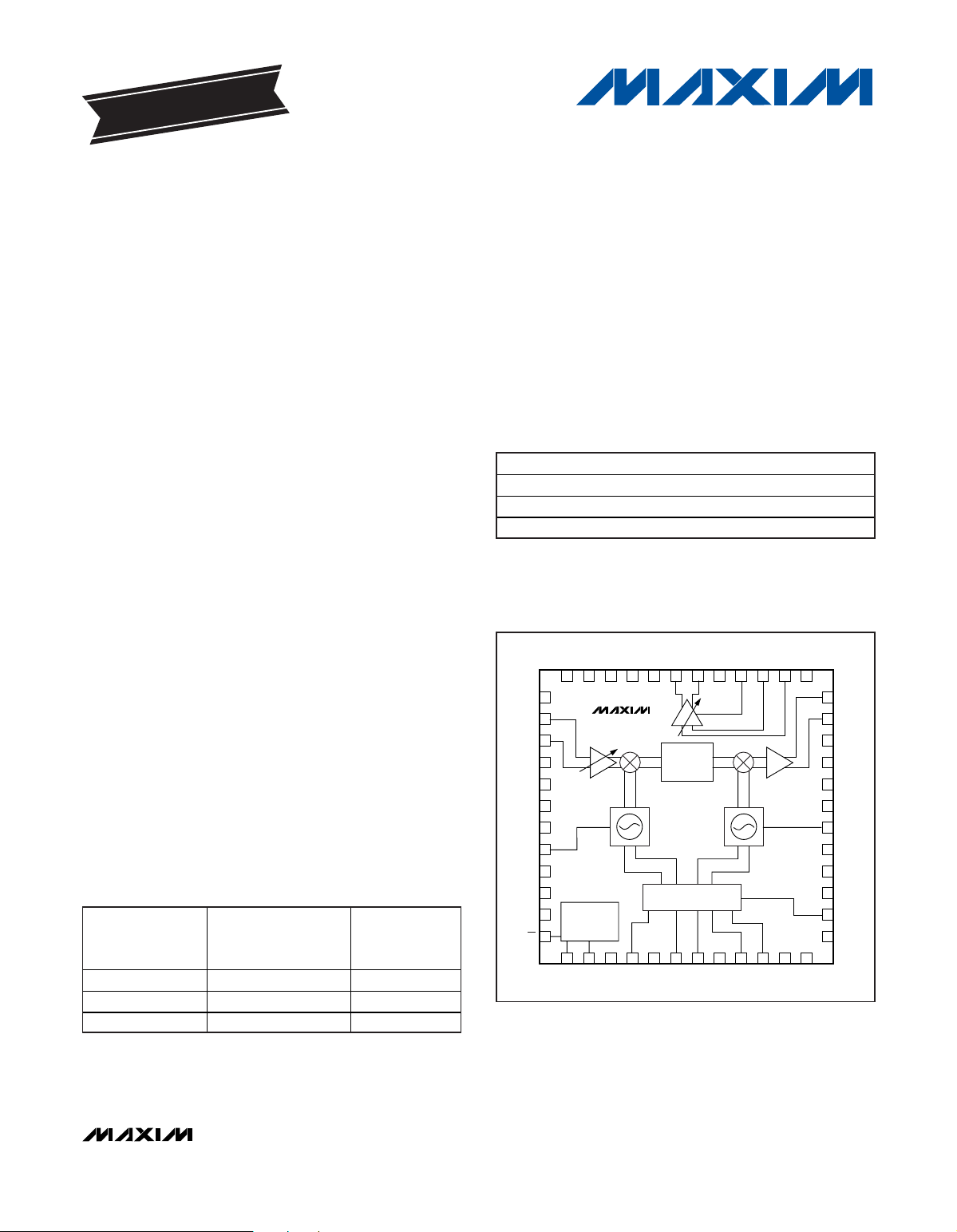

_____________________ 引脚排列和功能框图

IFIN-

OSCIN

IFIN+

GND

V

CC

GND

36

35

34

33

32

31

30

29

28

27

26

25

IFOUT1-

IFOUT1+

GND

V

CC

GND

V

CC

TUNE2

LOCFLT2

GND

V

CC

CPOUT2

V

CC

HI-IF

FILTER

CPOUT1

IFOUT2+

CC

V

CC

V

GND

IFVGA

OSCOUT

RFIN+

RFIN-

GND

GND

TUNE1

LOCFLT1

GND

RFVGA

GND

V

BIAS

CC

DIV/LD

VCCIFOUT2-

I.C.

DUAL SYNTHESIZER

LNABIAS

48 47 46 45 44 43 42 41 40 39 38 37

V

1

CC

2

3

4

V

5

CC

6

V

7

CC

8

9

10

11

I.C.

12

CS

MAX3570

3-WIRE SERIAL

INTERFACE

13 14 15 16 17 18 19 20 21 22 23 24

SCL

SDA

引脚排列和功能框图 (续) 见本数据手册的最后。

MAX3570/MAX3571/MAX3573

________________________________________________________________ Maxim Integrated Products 1

本文是Maxim正式英文资料的译文,Maxim不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

翻译错误,如需确认任何词语的准确性,请参考 Maxim提供的英文版资料。

索取免费样品和最新版的数据资料,请访问Maxim的主页:www.maxim-ic.com.cn。

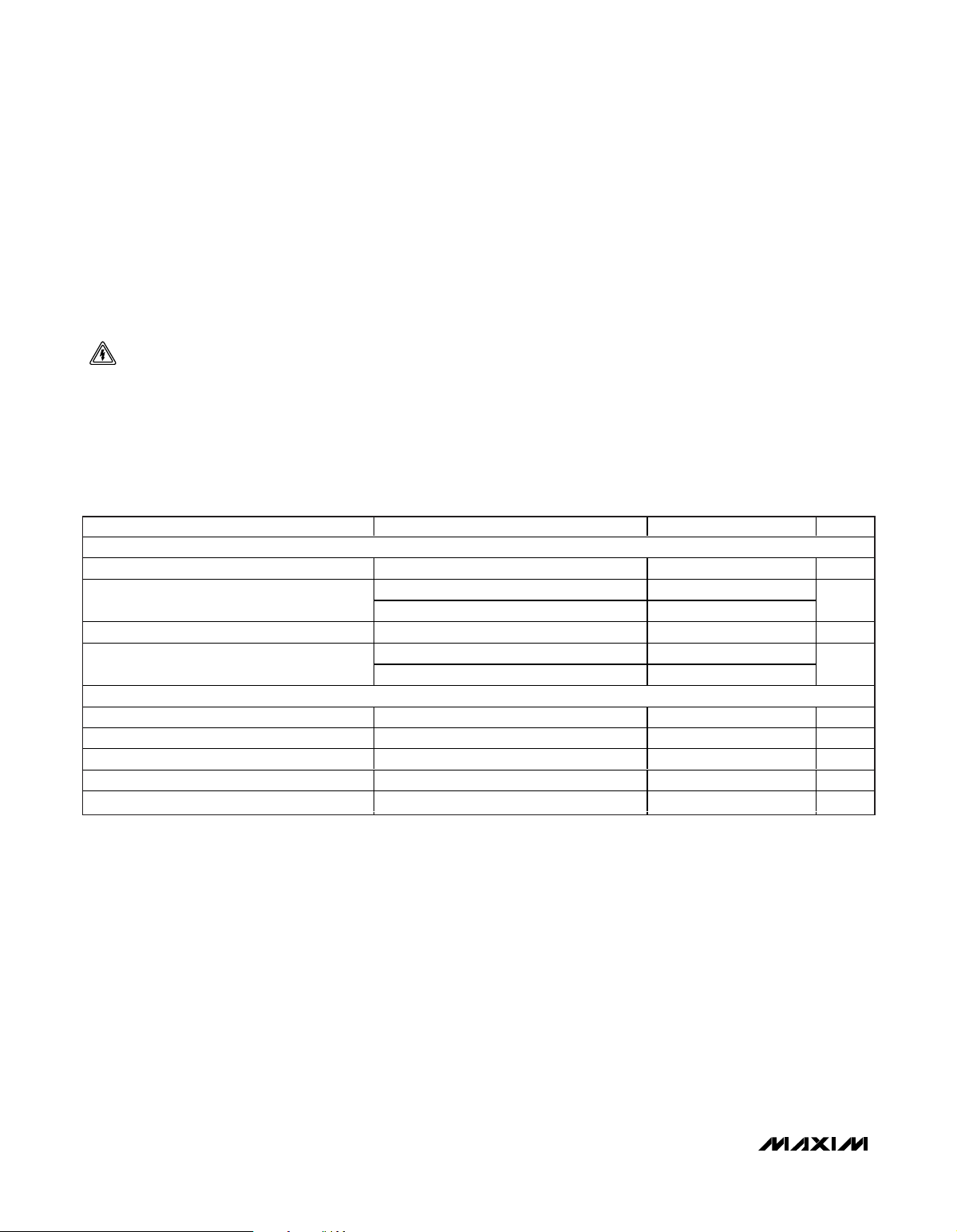

Page 2

高中频(HI-IF)单片宽带调谐器

ABSOLUTE MAXIMUM RATINGS

VCCto GND...........................................................-0.3V to +5.5V

IFIN_, IFOUT1_, IFOUT2_, RFIN_, TUNE_,

LOCFLT_, CPOUT_, OSCIN, OSCOUT,

IFVGA, RFVGA, BIAS, LNABIAS,

ADDR_, CS, SCL, SDA, DIV/LD...............-0.3V to (V

CAUTION! ESD SENSITIVE DEVICE

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

CC

+ 0.3V)

Continuous Power Dissipation (T

48-Pin QFN (derate 27mW/°C above +70°C) ............2162mW

Operating Temperature Range...............................0°C to +70°C

Junction Temperature......................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

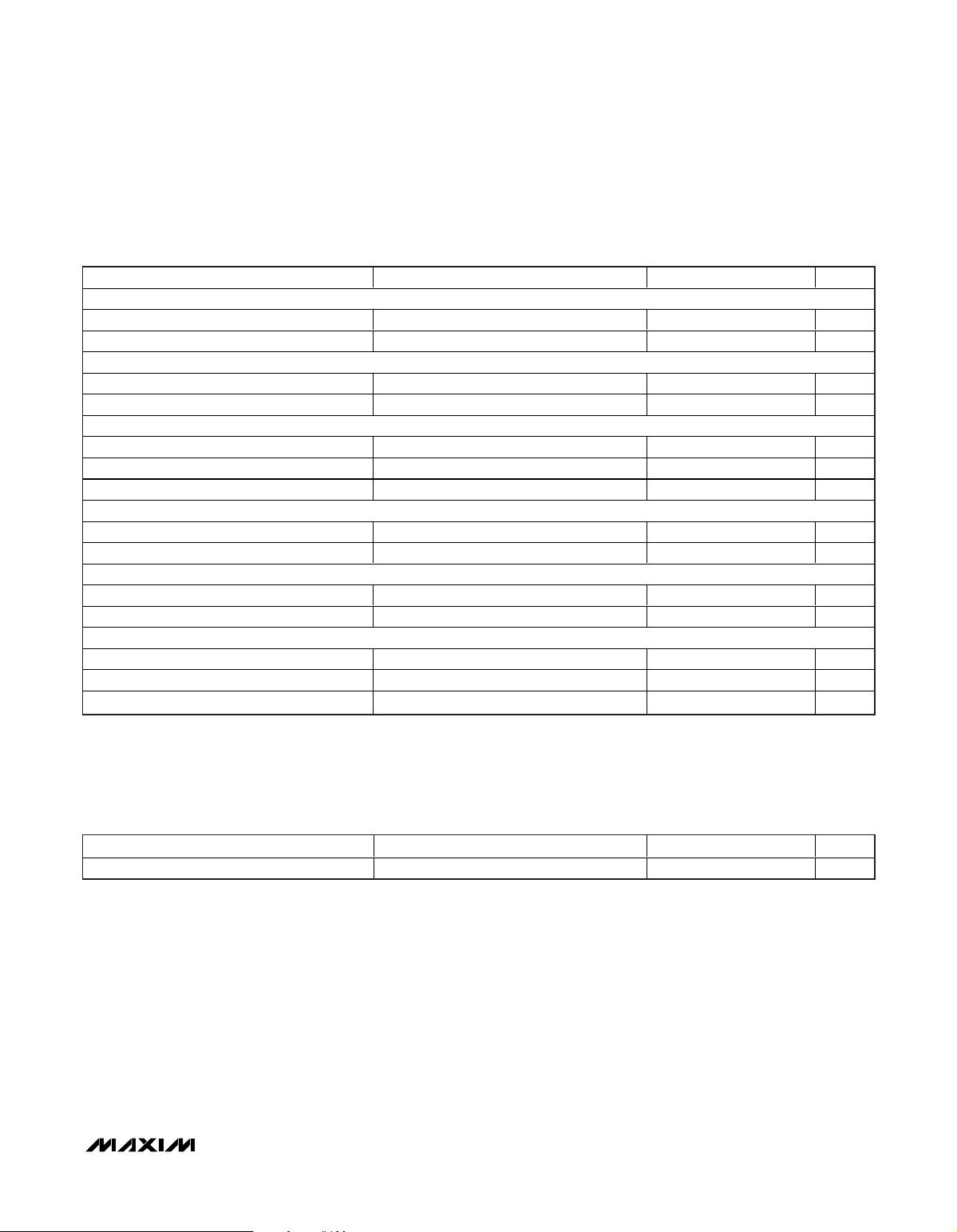

DC ELECTRICAL CHARACTERISTICS

(MAX357_ EV kit, VCC= +4.75V to +5.25V, R

Typical values are at V

PARAMETER CONDITIONS MIN TYP MAX UNITS

SUPPLY VOLTAGE AND SUPPLY CURRENT

Supply Voltage 4.75 5.25 V

Supply Current

= +5.0V, TA= +25°C, unless otherwise noted.) (Note 1)

CC

MAX3570/MAX3571/MAX3573

RF and IF VGA Input Bias Current V

RF and IF VGA Control Voltage

LOGIC INTERFACE

Input-Logic Low (VIL) 0.9 V

Input-Logic High (VIH) 2.3 V

Input Logic Current -10 +10 µA

Output-Logic Low Sink current = 3mA 0.4 V

Output-Logic High Source current = 3mA 2.8 V

= 5.9kΩ ±1%, no AC signal applied, TA= 0°C to +70°C, unless otherwise noted.

BIAS

At TA = +25°C, V

= +70°C, V

At T

A

= V

RFVGA

Maximum gain 3

Minimum gain 0.5

IFVGA

= +3.0V 320

RFVGA

= +0.5V 385

RFVGA

= +0.5V and +3.0V -50 +50 µA

= +70°C)

A

mA

V

2 _______________________________________________________________________________________

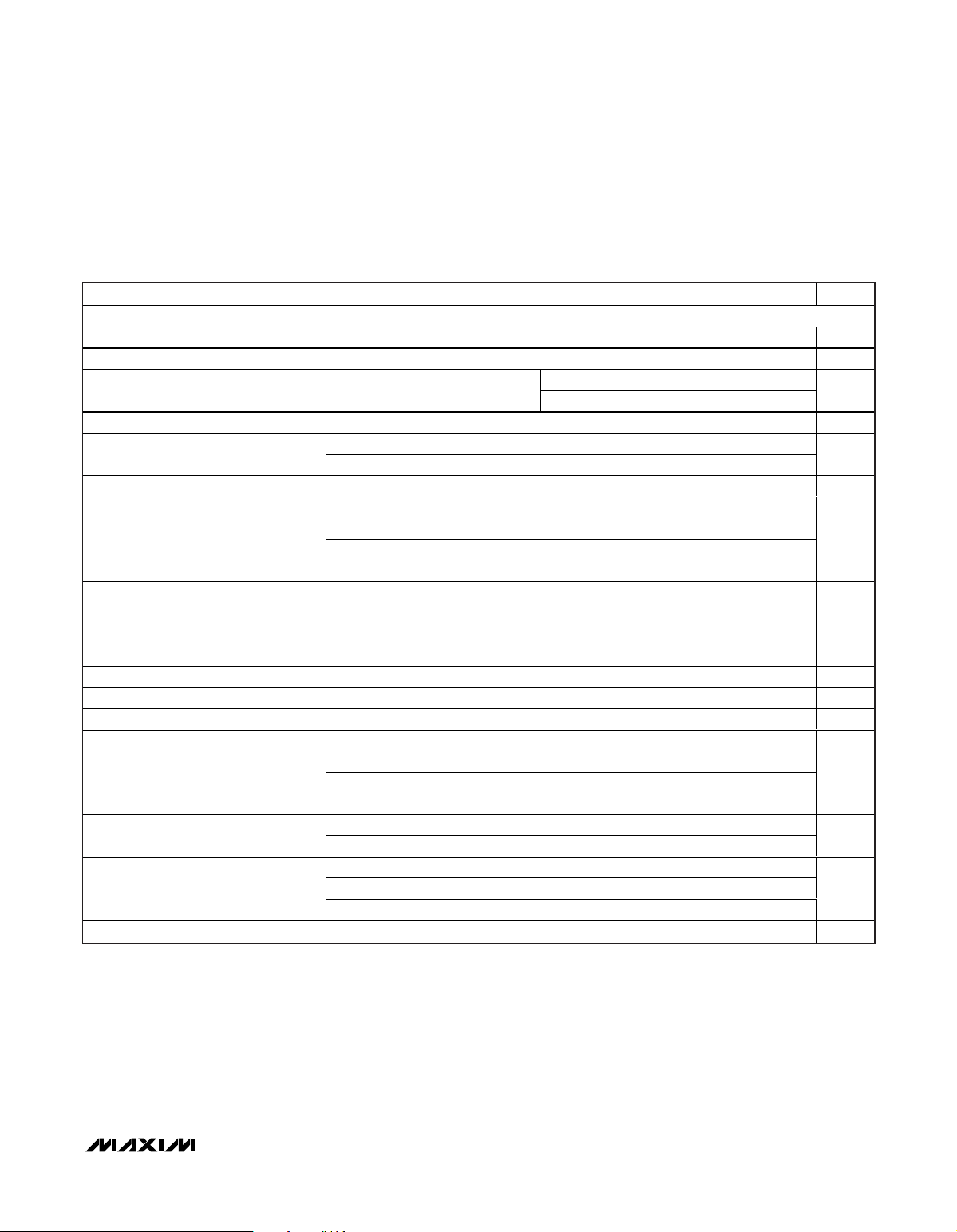

Page 3

高中频(HI-IF)单片宽带调谐器

AC ELECTRICAL CHARACTERISTICS

MAX3570/MAX3571/MAX3573

(MAX357_ EV kit, VCC= +4.75V to +5.25V, R

45.75MHz (MAX3570/MAX3571), f

wise noted. Typical values are at V

= 38.9MHz (MAX3573), f

IF

= +5.0V, TA= +25°C, unless otherwise noted.) (Note 1)

CC

PARAMETER CONDITIONS MIN TYP MAX UNITS

OVERALL REQUIREMENTS (RF INPUT TO 1st IF OUTPUT)

Operating Frequency Range Gain specification met across this frequency band 50 878 MHz

Input Return Loss Worst case across band, 75Ω, any RFVGA setting 8 dB

Z

Voltage Gain

SOURCE

V

RFVGA

Gain-Reduction Range Measured at 50MHz 30 dB

V

Gain Flatness

Noise Figure V

IIP2

IIP3

RFVGA

V

RFVGA

RFVGA

V

RFVGA

V

CC

At 12dB gain reduction, T

V

CC

V

RFVGA

V

CC

At 12dB gain reduction, T

V

CC

Beats within Output 0dBmV PIX carrier level (Note 2) -48 dBc

Channel Flatness From PIX to (PIX + 4) MHz -0.5 +0.3 +1.0 dB

Isolation 5M Hz to 150M H z, RF i np ut to IF output (N ote 3) -63 -68 dBc

Measured at 91MHz above desired PIX

Image Rejection

(MAX3570/MAX3571)

Measured at 77.75MHz above desired PIX

(MAX3573)

Spurious at RF Input (Note 3)

Single Sideband Phase Noise

50MHz to 878MHz -54 -48

Above 878MHz (LO and LO harmonics) +3

f

OFFSET

f

OFFSET

f

OFFSET

Output Return Loss Balanced, 50Ω 9dB

= 5.9kΩ ±1%, inputs terminated to 75Ω, f

BIAS

= 75Ω, Z

= +3.0V

= +3.0V at f

= 0.5V at f

LOAD

RFIN

= 1MHz, f

COMP1

= 200Ω,

= 878MHz vs. 50MHz -1.5 +1.5

RFIN

COMP2

TA = +25°C 31.5 38.5 45.0

= +70°C 30.0 37 43.5

T

A

= 878MHz vs. 50MHz -2 +2

= 62.5kHz, TA= 0°C to +70°C, unless other-

= 50MHz to 878MHz, fIF=

RFIN

= +3.0V 7.9 dB

= +3.0V, TA = +25°C to +70°C,

= 4.85V to 5.15V, fRF = 860MHz

= +25°C to +70°C,

A

= 4.85V to 5.15V, fRF = 860MHz

= +3.0V, TA = +25°C to +70°C,

= 4.85V to 5.15V

= +25°C to +70°C,

A

= 4.85V to 5.15V

34

52.5

+8

+18

50 55

50 55

= 1kHz -62

= 10kHz, BW

= 100kHz, BW

= 2.5kHz -86

LOOP

= 2.5kHz -105

LOOP

dB

dB

dBm

dBm

dBc

dBmV

dBc/Hz

_______________________________________________________________________________________ 3

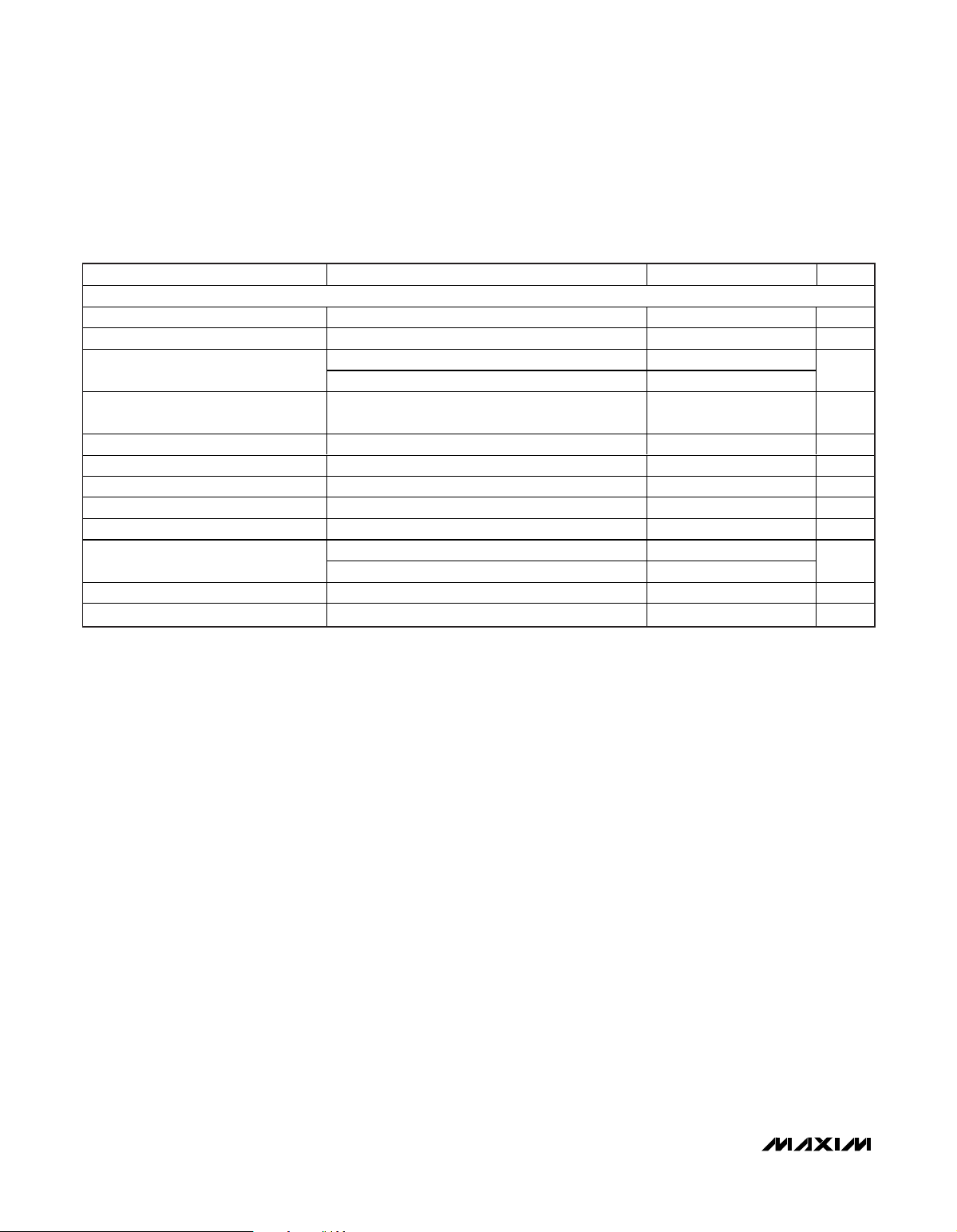

Page 4

高中频(HI-IF)单片宽带调谐器

AC ELECTRICAL CHARACTERISTICS

(MAX357_ EV kit, VCC= +4.75V to +5.25V, R

= 0°C to +70°C, unless otherwise noted. Typical values are at VCC= +5.0V, TA= +25°C, unless otherwise noted.) (Note 1)

T

A

PARAMETER CONDITIONS MIN TYP MAX UNITS

SECOND IF STAGE

Input Impedance Balanced 1.7 kΩ

Output Impedance Balanced (Note 3) 100 Ω

Passband Voltage Gain

Passband Flatness

Maximum Output Voltage 3.2 V

VGA Gain Slope V

-3dB Bandwidth (Note 3) 180 MHz

Noise Figure fIF = 44MHz, V

Noise Figure vs. Attenuation First 10dB back-off 0.3 dB/dB

IIP3

OIP3 V

PSRR 50mV

MAX3570/MAX3571/MAX3573

Z

V

From PIX to (PIX - 4) MHz for 45.75MHz PIX

frequency (Note 3)

Gain = 45dB, V

Gain = 27dB, V

= 5.9kΩ ±1%, inputs terminated to 1kΩ, Z

BIAS

= 1.1kΩ, Z

SOURCE

= +0.5V 14.5 23

IFVGA

= +3.0V to +0.5V 10 20 dB/V

IFVGA

IFVGA

OUT

OUT

OUT

= 1.5V

P-P

, V

P-P

at 200kHz -57 dB

= 300Ω, V

LOAD

= +3.0V 5.1 dB

= 1.5V

P-P

= 1.5V

P-P

= +3.0V to +0.5V (Note 3) 25 dBm

IFVGA

= +3.0V 50 53 57

IFVGA

= 300Ω, fIF= 40MHz to 48MHz,

LOAD

0.2 dB

-27.5

-11.3

dB

P-P

dBm

4 _______________________________________________________________________________________

Page 5

高中频(HI-IF)单片宽带调谐器

SYNTHESIZER ELECTRICAL CHARACTERISTICS

(MAX357_ EV kit, VCC= +4.75V to +5.25V, R

erwise noted. Typical values are at V

PARAMETER CONDITIONS MIN TYP MAX UNITS

1st LOCAL OSCILLATOR (LO1)

Tuning Range 1274 2111 MHz

VCO Tuning Gain 40 120 MHz/V

1st LOCAL OSCILLATOR (LO1) DIVIDER

RF1 N-Divider Ratio 256 8191

RF1 R-Divider Ratio 131

1st LOCAL OSCILLATOR (LO1) PHASE DETECTOR AND CHARGE PUMP

Phase-Detector Phase Noise f

Charge-Pump Source/Sink Matching Correlate locked vs. unlocked 6 %

Charge-Pump Tri-State Current RF1 -7 +7 nA

2nd LOCAL OSCILLATOR (LO2)

Tuning Range 1175 1193 MHz

VCO Tuning Gain 25 70 MHz/V

2nd LOCAL OSCILLATOR (LO2) DIVIDER

RF2 N-Divider Ratio 512 65,535

RF2 R-Divider Ratio 2 127

2nd LOCAL OSCILLATOR (LO2) PHASE DETECTOR AND CHARGE PUMP

Phase-Detector Phase Noise f

Charge-Pump Source/Sink Matching Correlate locked vs. unlocked 6 %

Charge-Pump Tri-State Current RF2 -7 +7 nA

= +5.0V, TA= +25°C, unless otherwise noted.) (Note 1)

CC

= 5.9kΩ ±1%, f

BIAS

OFFSET

OFFSET

= 1MHz, f

COMP1

= 2kHz (Note 3) -142 dBc

= 2kHz (Note 3) -142 dBc

= 62.5kHz, TA= 0°C to +70°C, unless oth-

COMP2

MAX3570/MAX3571/MAX3573

LOGIC INTERFACE

(MAX357_ EV kit, VCC= +4.75V to +5.25V, R

PARAMETER CONDITIONS MIN TYP MAX UNITS

Maximum Clock Frequency 400 kHz

Note 1: These parameters are production tested from TA= +25°C to +70°C, and are guaranteed by design and characterization at

T

= 0°C.

Note 2: When using the tuning table provided in the EV kit documentation.

Note 3: These parameters are guaranteed by design and characterization, and are not production tested.

A

_______________________________________________________________________________________ 5

= 5.9kΩ ±1%, TA= 0°C to +70°C, unless otherwise noted.) (Note 1)

BIAS

Page 6

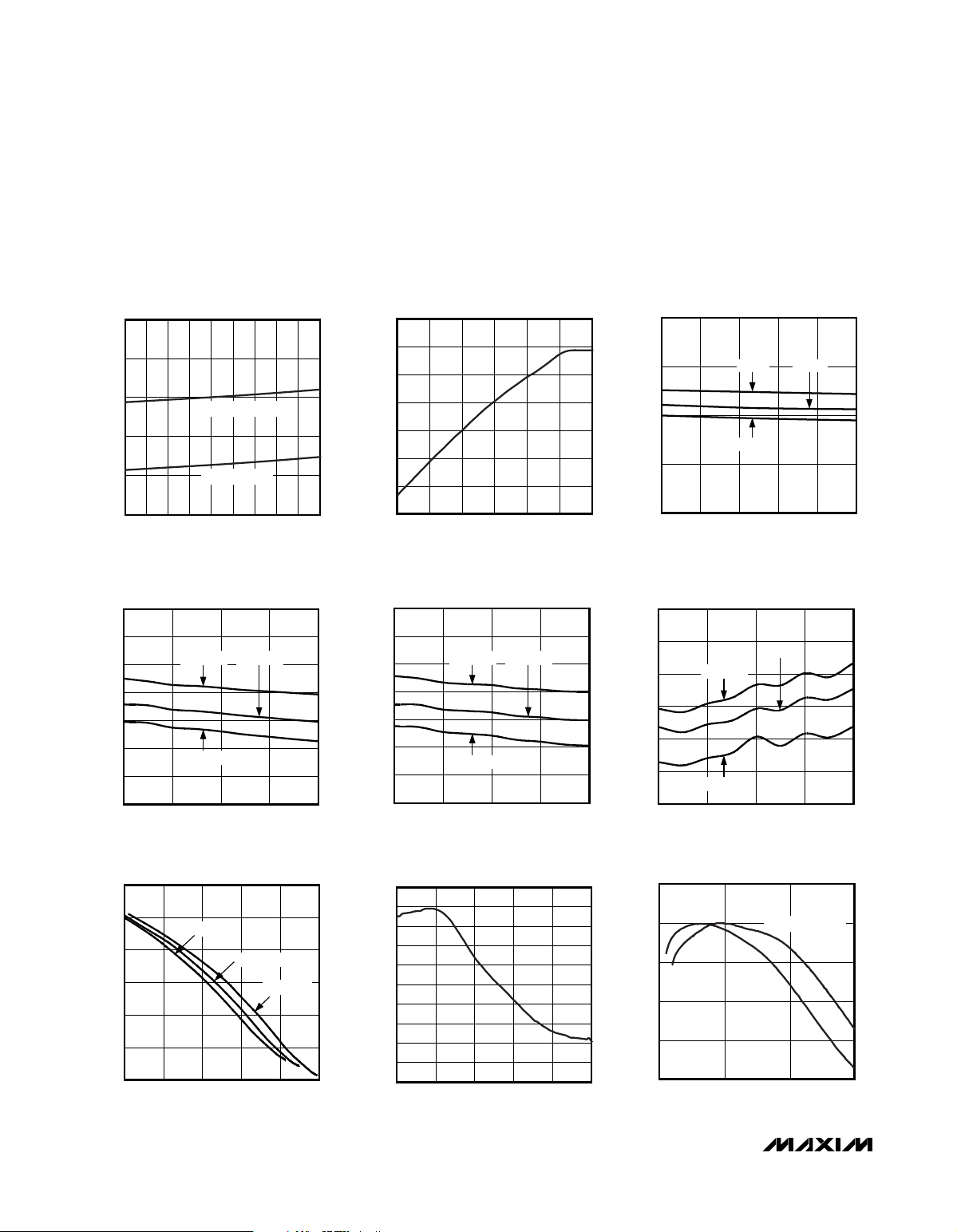

高中频(HI-IF)单片宽带调谐器

300

320

340

360

380

400

25 40 4530 35 50 55 60 65 70

SUPPLY CURRENT vs. TEMPERATURE

MAX3570/71/73 toc01

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

12dB ATTENTUATION

MAXIMUM GAIN

-20

0

-10

20

10

40

30

50

0 1.0 1.50.5 2.0 2.5 3.0

VOLTAGE GAIN

vs. RFVGA VOLTAGE

MAX3570/71/73 toc02

RFVGA VOLTAGE (V)

VOLTAGE GAIN (dB)

36

39

38

37

40

VOLTAGE GAIN

vs. SUPPLY VOLTAGE

MAX3570/71/73 toc03

SUPPLY VOLTAGE (V)

VOLTAGE GAIN (dB)

4.75 4.85 4.95 5.05 5.15 5.25

850MHz

50MHz

450MHz

VOLTAGE GAIN

vs. FREQUENCY (MAX GAIN)

MAX3570/71/73 toc04

FREQUENCY (MHz)

VOLTAGE GAIN (dB)

650450250

37

36

35

38

39

40

41

34

50 850

TA = +25°C

TA = +70°C

TA = +55°C

VOLTAGE GAIN

vs. FREQUENCY (MAX -12dB)

MAX3570/71/73 toc05

FREQUENCY (MHz)

VOLTAGE GAIN (dB)

650450250

23

24

25

26

27

28

29

22

50 850

TA = +25°C

TA = +70°C

TA = +55°C

7.0

8.0

7.5

9.0

8.5

9.5

10.0

50 450250 650 850

NOISE FIGURE vs. FREQUENCY

MAX3570/71/73 toc06

FREQUENCY (MHz)

NOISE FIGURE (dB)

TA = +70°C

TA = +25°C

TA = +55°C

NOISE FIGURE vs. VOLTAGE GAIN

MAX3570/71/73 toc07

VOLTAGE GAIN (dB)

NOISE FIGURE (dB)

37353331

10

12

14

16

18

20

8

29 39

TA = +70°C

TA = +55°C

TA = +25°C

-150

-120

-130

-140

-110

-100

-90

-80

-70

-60

-50

100 10k1k 100k 1M 10M

PHASE NOISE vs. OFFSET FREQUENCY

MAX3570/71/73 toc08

FREQUENCY (Hz)

PHASE NOISE (dBc/Hz)

-40

-30

-10

-20

0

10

IFOUT1 FREQUENCY RESPONSE

MAX3570/71/73 toc09

IF FREQUENCY (MHz)

AMPLITUDE (dB)

0 50 100 150

MAX3570/MAX3571

MAX3573

___________________________________________________________________

(MAX357_ EV kit, VCC= +5.0V, R

unless otherwise noted.)

= 5.9kΩ, fRF= 860MHz, fIF= 44MHz (MAX3570/MAX3571), 36MHz (MAX3573), TA= +25°C,

BIAS

MAX3570/MAX3571/MAX3573

典型工作特性

6 _______________________________________________________________________________________

Page 7

高中频(HI-IF)单片宽带调谐器

_______________________________________________________________

(MAX357_ EV kit, VCC= +5.0V, R

unless otherwise noted.)

= 5.9kΩ, fRF= 860MHz, fIF= 44MHz (MAX3570/MAX3571), 36MHz (MAX3573), TA= +25°C,

BIAS

MAX3570/MAX3571/MAX3573

典型工作特性 (续)

RFIN INPUT RETURN LOSS

-7.5

-8.0

-8.5

RETURN LOSS (dB)

-9.0

-9.5

50 250 450 650 850

RF FREQUENCY (MHz)

IFVGA VOLTAGE GAIN vs. IFVGA VOLTAGE

60

55

50

45

40

35

30

25

IFVGA VOLTAGE GAIN (dB)

20

15

10

0.3 3.3

IFVGA VOLTAGE (V)

INPUT IP2 vs. VOLTAGE GAIN

60

55

MAX3570/71/73 toc10

INPUT IP2 (dBm)

50

TA = +70°C

45

40

35

30

19 2924 34 39

VOLTAGE GAIN (dB)

TA = +25°C

TA = +55°C

MAX3570/71/73 toc11

INPUT IP3 (dBm)

IFVGA VOLTAGE GAIN vs. IF FREQUENCY

58

56

MAX3570/71/73 toc13

2.82.31.81.30.8

54

52

50

48

46

IFVGA VOLTAGE GAIN (dB)

44

42

40

TA = +55°C

TA = +70°C

11000

IF FREQUENCY (MHz)

TA = +25°C

MAX3570/71/73 toc14

NOISE FIGURE (dB)

10010

INPUT IP3 vs. VOLTAGE GAIN

28

23

18

TA = +25°C

13

8

3

19 2924 34 39

TA = +55°C

TA = +70°C

VOLTAGE GAIN (dB)

IFVGA NOISE FIGURE vs. IFVGA VOLTAGE

30

25

20

TA = +70°C

15

10

TA = +25°C

5

0.6 3.3

TA = +55°C

IFVGA VOLTAGE (V)

MAX3570/71/73 toc12

MAX3570/71/73 toc15

3.02.72.42.11.81.51.20.9

IFVGA INPUT IP3 vs. IFVGA VOLTAGE

-5

-10

-15

-20

-25

INPUT IP3 (dBm)

-30

-35

-40

0.3 3.3

TA = +70°C

TA = +25°C

IFVGA VOLTAGE (V)

TA = +55°C

MAX3570/71/73 toc16

2.82.31.81.30.8

_______________________________________________________________________________________ 7

Page 8

高中频(HI-IF)单片宽带调谐器

_______________________________________________________________________

引脚

PIN NAME FUNCTION

1V

2, 3

4, 6, 10,

20, 23,

24, 28,

32, 34, 45

5V

7V

8 TUNE1

9 LOCFLT1

11

12

MAX3570/MAX3571/MAX3573

13 SCL

14 SDA

名称 功能

CC

RFIN+,

RFIN-

GND

CC

CC

I.C.

ADDR2

CS

ADDR1

射频可变增益放大器 (VGA) 电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与

其他支路共用。

差分LNA输入。需要交流耦合,可由差分平衡或者单端驱动。单端驱动时,建议使用引脚3驱动,并将引脚2

交流接地,以获得最优的输入IP2性能。

地。连接到印刷板地平面。

第一级混频器电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

第一级VCO电路电源。需接旁路电容,旁路电容尽可能靠近该引脚。旁路电容地过孔不能与其他支路共用。

第一级VCO调谐输入。连接这个输入模拟电压至三阶环路滤波器的输出级。

第一级LO噪声滤波器电容连接。连接一个电容到地。(参考评估板)

内部连接。让该引脚悬空 (MAX3570)。

2线串行接口第二位地址设置引脚 ( MAX3571/MAX3573)。

3线串行接口使能输入引脚 (SPI

2线串行接口第一位地址设置引脚 (MAX3571/MAX3573)。

3线串行接口时钟输入引脚 (SPI/QSPI/MICROWIRE兼容) (MAX3570)。

2线串行接口时钟输入引脚 (MAX3571/MAX3573)。

3线串行接口数据输入引脚 (SPI/QSPI/MICROWIRE兼容) (MAX3570)。

2线串行接口数据输入引脚 (MAX3571/MAX3573)。

TM

/QSPITM/MICROWIRETM兼容) (MAX3570)。

引脚说明

15 V

16 DIV/LD

17 I.C.

18 CPOUT1

19 V

21 OSCOUT

22 OSCIN

25 V

26 CPOUT2

SPI和 QSPI 是Motorola, Inc.的商标。

MICROWIRE是National Semiconductor Corp. 的商标。

8 _______________________________________________________________________________________

CC

CC

CC

数字电路电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

分频器和锁定检测逻辑输出。

内部连接。该引脚悬空。

第一级PLL电荷泵输出。连接该高阻抗电流输出至三阶环路滤波器输入。

第一级频率合成器电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路

共用。

参考振荡器缓冲输出

参考振荡器输入。通过耦合电容连接外部参考振荡器或者晶体至该模拟输入。

第二级频率合成器电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路

共用。

第二级PLL电荷泵输出。连接该高阻抗电流输出至三阶环路滤波器的输入。

Page 9

高中频(HI-IF)单片宽带调谐器

___________________________________________________________________

PIN NAME FUNCTION

引脚

27 V

29 LOCFLT2

30 TUNE2

31 V

33 V

35, 36

37 V

38, 39

40 IFVGA

41 V

42, 43

44 V

名称

CC

CC

CC

IFOUT1+,

IFOUT1-

CC

IFIN+,

IFIN-

CC

IFOUT2+,

IFOUT2-

CC

第二级电荷泵电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

第二级LO噪声滤波电容连接管脚。连接一个电容到地。(参考评估板)

第二级VCO调谐输入。连接这个模拟电压输入至三阶环路滤波器。

第二级VCO电路电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

第二级LO发生器。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

第一个差分中频输出。这些输出交流耦合到SAW滤波器输入。

第二级混频器和第一级中频放大器电源。使用尽可能靠近该引脚的电容旁路。旁路电容地过孔不能与

其他支路共用。

差分中频输入。连接至SAW滤波器输出。

中频VGA控制。见

中频VGA电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路共用。

中频VGA输出

高中频滤波器电路电源。需接旁路电容,旁路电容尽可能地靠近该引脚。旁路电容地过孔不能与其他支路

共用。

典型工作特性

。

功能

引脚说明 (续)

MAX3570/MAX3571/MAX3573

46 BIAS

47 RFVGA

48 LNABIAS

EP GND

偏置电阻连接。连接5.9kΩ、精度±1%的电阻到地。电阻值增大可减小工作电流,但是牺牲了线性度。欲获

取详细信息,请参考应用笔记:

射频VGA控制。见

LNA偏置输入。用电感连接到地。(参考评估板)

裸露地焊盘。芯片的直流和交流地。使用多个过孔连接至印刷板地平面。

_______________________________________________________________________________________ 9

典型工作特性

MAX3570/MAX3571/MAX3573 Bias Resistor Setting

。

。

Page 10

高中频(HI-IF)单片宽带调谐器

______________________________

详细说明

可编程寄存器

MAX3570/MAX3571/MAX3573包括九个可编程寄存器 (寄

存器1–9),其中有6个分频器寄存器(寄存器1–6),一个

VCO控制寄存器 (寄存器7)和一个测试寄存器 (寄存器8)。

最后一个寄存器 (寄存器9) 控制HI-IF滤波器频率偏移和

DIV/LD输出的MUX状态。大多数寄存器包含一些无关位。

这些位可以为“0”或“1”,不影响工作模式 (表1)。数据

的高有效位MSB先移入寄存器,使用正逻辑。

3线串行接口

MAX3570使用3线SPI/QSPI/MICROWIRE 兼容的串行接口。

低有效的芯片选择 (CS) 使能芯片从串行输入 (SDA) 端

接收数据。在串行时钟信号 (SCL) 上升沿,寄存器地址

和数据信息顺序进入。在串行数据移入时,芯片保持原

来的配置。在CS的上升沿将数据锁存到MAX3570内部寄

存器后,器件状态改变。图1给出了3线接口地址和数据

设置的信息。

MAX3570/MAX3571/MAX3573

图1. 3线串行接口地址和数据配置

2线串行接口

MAX3571/MAX3573使用2线I2C*兼容串行接口。串行总线

不断地监视、等待START条件以及后面的地址信息。地址

中5个最高位通过内部设置,而后面两位ADDR2和ADDR1

由外部引脚设置。LSB确定是读信号还是写信号。当器件

识别出地址后,将SDA线拉低一个时钟周期作为应答;然

后准备接收数据第一个字节的寄存器地址。一旦寄存器

地址被接收,发送另一个应答 (ACK)。器件准备接收数

据字节。更多的数据字节可发送到后续地址的寄存器,

在每个字节发送完成后发送一个ACK。在最后的ACK发

送后,主机发送STOP条件释放总线。图2给出了2线接口

结构的细节。

在MAX3571/MAX3573仅有一个回读寄存器。在发送

START条件后通过外部的ADDR2和ADDR1引脚设置读地

址来访问。在发送ACK之后,主机开始读从设备。在八

个字节读完后,主设备产生NACK,然后是STOP条件。

MSB LSB

4 ADDRESS BITS 8 DATA BITS

A3 A2 A1 A0 D7 D6 D5 D4 D3 D2 D1 D0

图2. 2线串行接口寄存器写例子

START

DEVICE ADDRESS REGISTER ADDRESS DATA DATA

8b11000<ADDR2><ADDR1>0

ACK

8b0000XXXX

ACK

D7–D0

ACK

D7–D0

ACK STOP

图3. 2线串行接口寄存器读例子

START

DEVICE ADDRESS READ BYTE (8 Bits)

8b11000<ADDR2><ADDR1>1

ACK

8bXXXXXXXX

NACK STOP

表1. 2线串行接口地址配置 (由ADDR2和

ADDR1设置)

*

购买 Maxim Integrated Products, Inc. 或其从属授权关联公司的

2

I

C产品,即得到了 Philips I2C的专利许可、将这些产品用于

符合Philips 定义的 I

10 ______________________________________________________________________________________

2

C标准规范的系统。

ADDRESS (WRITE/READ) ADDR2 ADDR1

C0/C1

C2/C3

C4/C5

C6/C7

hex

hex

hex

hex

Low Low

Low High

High Low

High High

Page 11

表2. 寄存器配置

高中频(HI-IF)单片宽带调谐器

MAX3570/MAX3571/MAX3573

REGISTER

NUMBER

1 VCO1_N1 00

2 VCO1_N2 01

3 VCO1_R 02

4 VCO2_N1 03

5 VCO2_N2 04

6 VCO2_R 05

7 VCO_SET 06

8 TEST 07

9 HI-IF 08

REGISTER

NAME

X = 无关。

表3. 寄存器说明

REGISTER

NUMBER

1 VCO1_N1 00

2 VCO1_N2 01

3 VCO1_R 02

4 VCO2_N1 03

5 VCO2_N2 04

6 VCO2_R 05

7 VCO_SET 06

8 TEST 07

9 HI-IF 08

REGISTER

ADDRESS

REGISTER

NAME

hex

hex

hex

hex

hex

hex

hex

hex

hex

REGISTER

ADDRESS

MSB LSB

8 DATA BITS

D7 D6 D5 D4 D3 D2 DB1 D0

X X X 1N12 1N11 1N10 1N9 1N8

1N7 1N6 1N5 1N4 1N3 1N2 1N1 1N0

X X X 1R4 1R3 1R2 1R1 1R0

2N15 2N14 2N13 2N12 2N11 2N10 2N9 2N8

2N7 2N6 2N5 2N4 2N3 2N2 2N1 2N0

X 2R6 2R5 2R4 2R3 2R2 2R1 2R0

1VCO2 1VCO1 1VCO0 X 1CP1 1CP0 2CP1 2CP0

X 1T4 1T3 1T2 1T1 1T0 ST1 ST0

X X F1 F0 MUX3 MUX2 MUX1 MUX0

FUNCTION

hex

hex

hex

hex

hex

hex

hex

hex

hex

VCO1 N-divider high

VCO1 N-divider low

VCO1 R-divider

VCO2 N-divider high

VCO2 N-divider low

VCO2 R-divider

VCO select and charge-pump settings

Test mode. For test purposes only. Program to 20

Mode select, MUX output select

hex

.

表4. 第一级VCO N分频器高位寄存器 (VCO1_N1)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

X X 7, 6, 5 Reserved

1N 1st VCO N-Divider 4–0 1st VCO N-divider MSB bits

表5. 第一级VCO N分频器低位寄存器 (VCO1_N2)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

1N 1st VCO N-Divider 7–0 1st VCO N-divider LSB bits

______________________________________________________________________________________ 11

Page 12

高中频(HI-IF)单片宽带调谐器

表6. 第一级VCO R分频器高位寄存器 (VCO1_R)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

X X 7, 6, 5 Reserved

1R 1st VCO R-Divider 4–0 1st VCO R-divider

表7. 第二级VCO N分频器高位寄存器 (VCO2_N1)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

2N 2nd VCO N-Divider 7–0 2nd VCO N-divider MSB bits

表8. 第二级VCO N分频器低位寄存器 (VCO2_N2)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

2N 2nd VCO N-Divider 7–0 2nd VCO N-divider LSB bits

表9. 第二级VCO R分频器高位寄存器 (VCO2_R)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

X X 7 Reserved

MAX3570/MAX3571/MAX3573

2R 2nd VCO R-Divider 6–0 2nd VCO R-divider

表10. VCO谐振回路和电荷泵选择寄存器 (VCO_SET)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

1st VCO Tank Select:

• 000 = 1st VCO tank (the lowest frequency oscillator)

• 001 = 2nd VCO tank

• 010 = 3rd VCO tank

1VCO 1st VCO Tank Select 7, 6, 5

X X 4 Reserved

1CP

2CP

1st VCO Charge-Pump

Current

2nd VCO Charge-Pump

Current

3, 2

1, 0

• 011 = 4th VCO tank

• 100 = 5th VCO tank

• 101 = 6th VCO tank

• 110 = 7th VCO tank

• 111 = 8th VCO tank (the highest frequency oscillator)

1st VCO Charge-Pump Current:

• 00 = 0.2mA

• 01 = 0.4mA

• 10 = 0.6mA

• 11 = 0.8mA

2nd VCO Charge-Pump Current:

• 00 = 0.2mA

• 01 = 0.4mA

• 10 = 0.6mA

• 11 = 0.8mA

12 ______________________________________________________________________________________

Page 13

高中频(HI-IF)单片宽带调谐器

表11. HI-IF步进控制和MUX输出寄存器 (HI-IF)

BIT ID BIT NAME BIT LOCATION (0 = LSB) FUNCTION

X X 7, 6 Reserved

HI-IF Filter Control:

F HI-IF Filter Control 5, 4

MUX

Lock-Detect and MUX

Output Control

表12. 读模式寄存器配置

REGISTER

NUMBER

1 LD_POR LOCK1 LOCK2 POR OU1 OU2 X X X

REGISTER

NAME

MSB LSB

D7 D6 D5 D4 D3 D2 DB1 D0

3–0

• 00 = Step down 5MHz

• 01 = Nominal

• 11 = Step up 5MHz

Lock-Detect and MUX Output Control:

• 0000 = Normal, low-noise operation

• 0001 = Lock detect for the 1st VCO

• 0010 = Lock detect for the 2nd VCO

• 0011 = 1st VCO N-divider

• 0100 = 1st VCO R-divider

• 0101 = 2nd VCO N-divider

• 0110 = 2nd VCO R-divider

• 0111 = Reference oscillator

• 1000 = AND output of lock detector

• 1001 = NAND output of lock detector

• 1010 = 1st VCO V

• 1011 = 2nd VCO V

8 DATA BITS

over/under indicator

TUNE

over/under indicator

TUNE

MAX3570/MAX3571/MAX3573

表13. 读模式寄存器说明

REGISTER NUMBER REGISTER NAME FUNCTION

1 LD_POR Lock detect and power-on reset

表14. 锁定检测和 POR寄存器

BIT ID BIT NAME

LOCK1 LOCK1 7 Lock indicator for 1st VCO (see Table 15)

LOCK2 LOCK2 6 Lock indicator for 2nd VCO

POR POR 5 Power-on reset indicator; 1 indicates successful power-on reset

OU1 OU1 4 Over or Under V

OU2 OU2 3 Over or Under V

X X 2, 1, 0 Reserved

BIT LOCATION

(0 = LSB)

FUNCTION

indicator for 1st VCO (see Table 15)

TUNE

indicator for 2nd VCO

TUNE

表15. 第一级VCO真值表

LOCK1 OU1 DESCRIPTION

1 x 1st VCO locked

00(Under) Choose next lower tank

0 1 (Over) Choose next higher tank

______________________________________________________________________________________ 13

Page 14

高中频(HI-IF)单片宽带调谐器

___________________________________________________________________

IF OUTPUT

FROM DAC

BIAS

MAX3570

GND

VCCIFOUT2-

DUAL SYNTHESIZER

RFVGA

LNABIAS

48 47 46 45 44 43 42 41 40 39 38 37

V

CC

1

RFIN+

2

RF

INPUT

MAX3570/MAX3571/MAX3573

RFIN-

GND

V

GND

V

TUNE1

LOCFLT1

GND

I.C.

3

4

CC

5

6

CC

7

8

9

10

11

3-WIRE SERIAL

CS

INTERFACE

12

TO ADC

HI-IF

FILTER

IFOUT2+

FROM DAC

CC

V

IFVGA

IFIN-

IFIN+

CC

V

IFOUT1-

36

IFOUT1+

35

GND

34

V

CC

33

GND

32

V

CC

31

TUNE2

30

LOCFLT2

29

GND

28

V

CC

27

CPOUT2

26

V

CC

25

典型应用电路

13 14 15 16 17 18 19 20 21 22 23 24

SCL

SERIAL INTERFACE

SDA

CC

V

I.C.

DIV/LD

CPOUT1

CC

V

GND

OSCOUT

OSCIN

GND

GND

14 ______________________________________________________________________________________

Page 15

高中频(HI-IF)单片宽带调谐器

______________________________

应用信息

射频输入

LNA提供匹配到75Ω的单端宽带输入。在信号上变频之前,

射频输入提供30dB线性、连续的增益控制。在射频输入

(引脚3) 端需要连接串联的16nH电感与1000pF电容,以获

得最优的匹配 (见

典型应用电路

)。

HI-IF频率的灵活控制

在两次变频接收机中,杂散频率来源于系统中相关的本

振(LO)信号的谐波。在一些情况下,这些杂散频率可

能落入中频频段。如果这种情况发生,可能要重新调谐

LO,使其稍微偏移HI-IF频率。这样可将杂散频率搬移到

IF频带外。MAX3570/MAX3571/MAX3573支持这种功能,

允许用户调节HI-IF 滤波器的中心频率,跟踪LO频率的偏

移,保持最优的镜像抑制和插入损耗性能。HI-IF滤波器

频率偏移由HI-IF频率步进控制位控制 (F0和F1,寄存器

地址8)。(

正在申请专利。)

IF输出

第一差分IF输出 (IFOUT1+, IFOUT1-),虽然用于驱动标准

的中频SAW滤波器,但可以驱动阻抗低至200Ω的负载。

第二差分IF输出 ( IFOUT2+, IFOUT2-) 提供可驱动300Ω负

载的平衡输出,也可以交流耦合到标准的QAM解调器的

ADC。

增益控制

MAX3570/MAX3571/MAX3573具有两个VGA电路,可用

于获得最佳的SNR同时减少失真。在低输入信号电平,

RFVGA电压应当为3.0V。可以设置LNA增益为最大值。

IFVGA 控制电压用于设置所需的输出信号幅度。随着射

频输入电平增加,IFVGA电压降低。当IFVGA电压达到用

户定义的值 (RFVGA触发点) 时,IFVGA电压固定,

RFVGA电压调整至保持需要的输出电平值。

频率合成器比较

频率选择

MAX3570/MAX3571/MAX3573的两个片上合成器支持宽范

围的比较频率。第一个LO (LO1)的PLL提供250kHz至

4MHz的比较频率范围,此时假设参考晶体频率为4MHz。

第二个 LO (LO2 ) PLL支持50kHz至2MHz的比较频率范

围,这里也同样假设参考晶体频率为4MHz。

对MAX3570 和MAX3571的LO1 (R1 = 4) 和LO2 (R2 = 16)

建议分别使用1MHz的比较频率和250kHz的比较频率。对

MAX3573,建议使用LO2比较频率为 142.8571kHz (R2 = 28,

4MHz晶体频率)。这些值保证了最优的分辨率,同时可使环

路滤波器抑制杂散信号能量并提供可接受的锁定时间。

频率合成器环路

滤波器

三阶低噪声环路滤波器用于每个本振,以获取低杂散和

低的相位噪声。选择环路带宽保证充分的杂散抑制和合

理的锁定时间。环路滤波器元件值请参考评估板。

晶体振荡器接口

晶体振荡器引脚 (OSCIN, OSCOUT) 必须连接到晶体或者

外部参考振荡器上。直接连到晶体时,请参考评估板使

用元件值。当连接到外部参考振荡器时,用1.5V

驱动OSCIN,OSCOUT悬空。

P-P

幅度

电源布局

为减少芯片不同部分的耦合,理想的电源布局为星型连

接,在中心VCC节点处放置大的去耦电容。VCC引线从该

节点引出,连接到MAX3570/MAX3571/MAX3573的各个

VCC节点。在每个电源线的末端使用连接到地的旁路电容,

保证在感兴趣的频率上具有低的阻抗。这样的安排使得

在每个VCC的引脚处有本地去耦。在旁路电容处至少使用

一个过孔减少接地感抗。

MAX3570/MAX3571/MAX3573

VCO1选择

VCO1 产生第一本振 ( LO1) 频率用于上变频混频器。包括

八个VCO的阵列,每个调谐至特定的频带,以覆盖需要

的频率范围。通过串行数据接口 (SDI) 选择需要的 VCO。

______________________________________________________________________________________ 15

Page 16

高中频(HI-IF)单片宽带调谐器

引脚排列和

__________________________

RFVGA

SDA

BIAS

MAX3571

MAX3573

CC

V

GND

DIV/LD

LNABIAS

48 47 46 45 44 43 42 41 40 39 38 37

V

1

CC

RFIN+

2

RFIN-

3

GND

4

V

5

CC

GND

6

V

7

CC

TUNE1

8

LOCFLT1

9

GND

10

11

ADDR2

ADDR1

MAX3570/MAX3571/MAX3573

2-WIRE SERIAL

INTERFACE

12

13 14 15 16 17 18 19 20 21 22 23 24

SCL

IFOUT2+

VCCIFOUT2-

HI-IF

FILTER

DUAL SYNTHESIZER

CC

I.C.

V

CPOUT1

功能框图 (续)

CC

IFIN-

V

IFVGA

GND

OSCIN

OSCOUT

IFIN+

GND

CC

V

IFOUT1-

36

35

IFOUT1+

34

GND

V

33

CC

32

GND

V

31

CC

30

TUNE2

29

LOCFLT2

28

GND

V

27

CC

26

CPOUT2

V

25

CC

GND

匹配网络布局

匹配网路的布局对电路中的寄生成份非常敏感。为减少

寄生电感,应保证所有连线尽可能短,元件尽可能靠近

芯片。为减少寄生电容,可将匹配网络元件下面的地平

面挖空。请参考评估板推荐的匹配网络。

______________________________

TRANSISTOR COUNT: 18,970

PROCESS: SiGe BiCMOS

芯片信息

16 ______________________________________________________________________________________

Page 17

高中频(HI-IF)单片宽带调谐器

_______________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

32, 44, 48L QFN.EPS

PACKAGE OUTLINE

32,44,48L QFN, 7x7x0.90 MM

21-0092

1

H

2

封装信息

MAX3570/MAX3571/MAX3573

U

PACKAGE OUTLINE,

32,44,48L QFN, 7x7x0.90 MM

21-0092

2

H

2

Maxim不对Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 17

© 2005 Maxim Integrated Products Printed USA

是Maxim Integrated Products, Inc.的注册商标。

Loading...

Loading...