Page 1

MAX31782 User’s Guide

Revision 0; 8/11

Page 2

MAX31782 User’s Guide

TABLE OF CONTENTS

SECTION 1: Overview . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1-1

SECTION 2: Architecture . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2-1

SECTION 3: System Register Descriptions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3-1

SECTION 4: Peripheral Register Modules . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4-1

SECTION 5: Interrupts . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 5-1

SECTION 6: Analog-to-Digital Converter (ADC) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6-1

SECTION 7: I2C-Compatible Slave Interface. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7-1

SECTION 8: I2C-Compatible Master Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 8-1

SECTION 9: PWM Outputs. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9-1

SECTION 10: Fan Tachometer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 10-1

SECTION 11: General-Purpose Input/Output (GPIO) Pins . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 11-1

SECTION 12: Timer B Module . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 12-1

SECTION 13: Supply Voltage Monitor . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 13-1

SECTION 14: Hardware Multiplier . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 14-1

SECTION 15: Watchdog Timer . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 15-1

SECTION 16: Test Access Port (TAP) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 16-1

SECTION 17: In-Circuit Debug Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 17-1

SECTION 18: In-System Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 18-1

SECTION 19: Programming . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 19-1

SECTION 20: Instruction Set Summary . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 20-1

SECTION 21: Utility ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 21-1

REVISION HISTORY. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . R-1

����������������������������������������������������������������� Maxim Integrated Products i

Revision 0; 8/11

Page 3

MAX31782 User’s Guide

SECTION 1: OVERVIEW

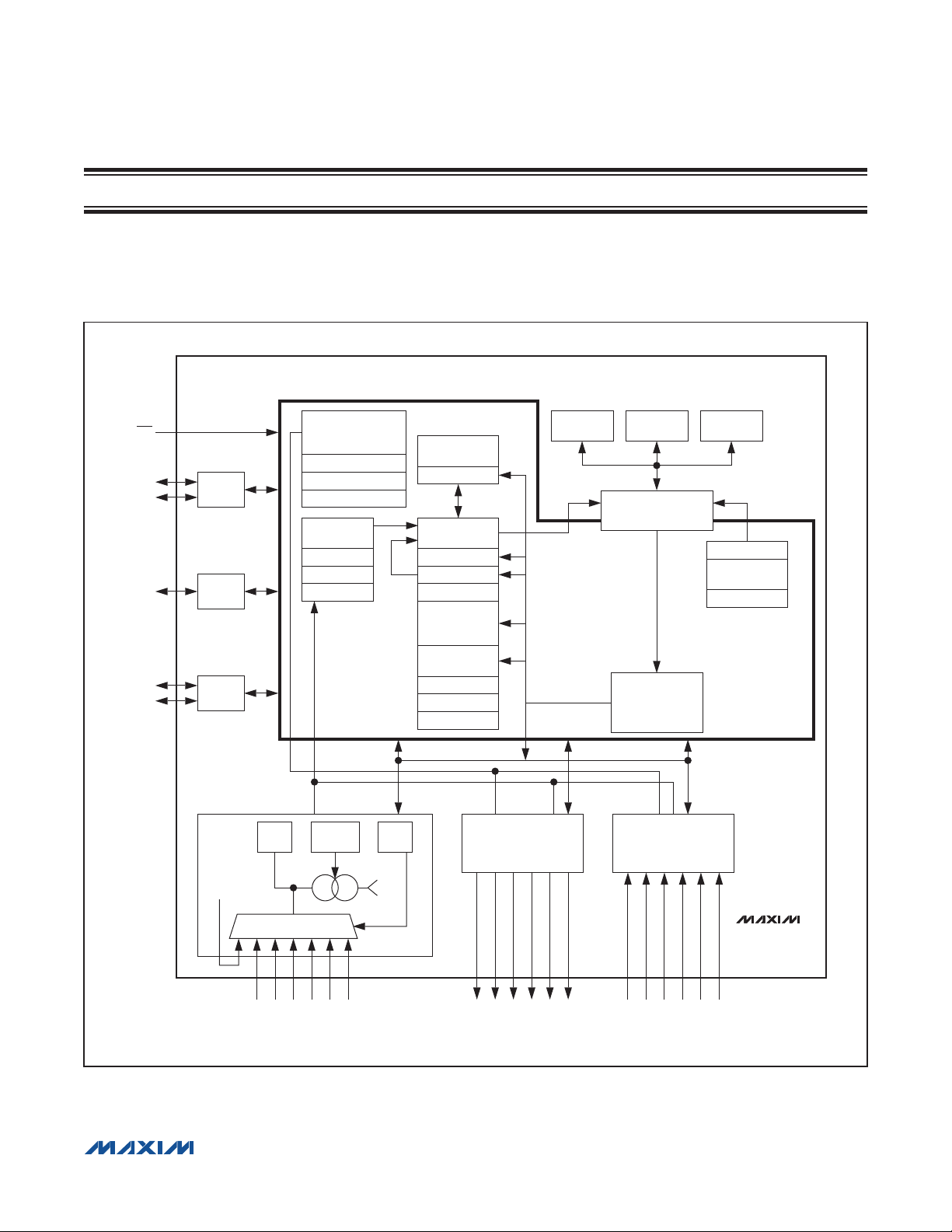

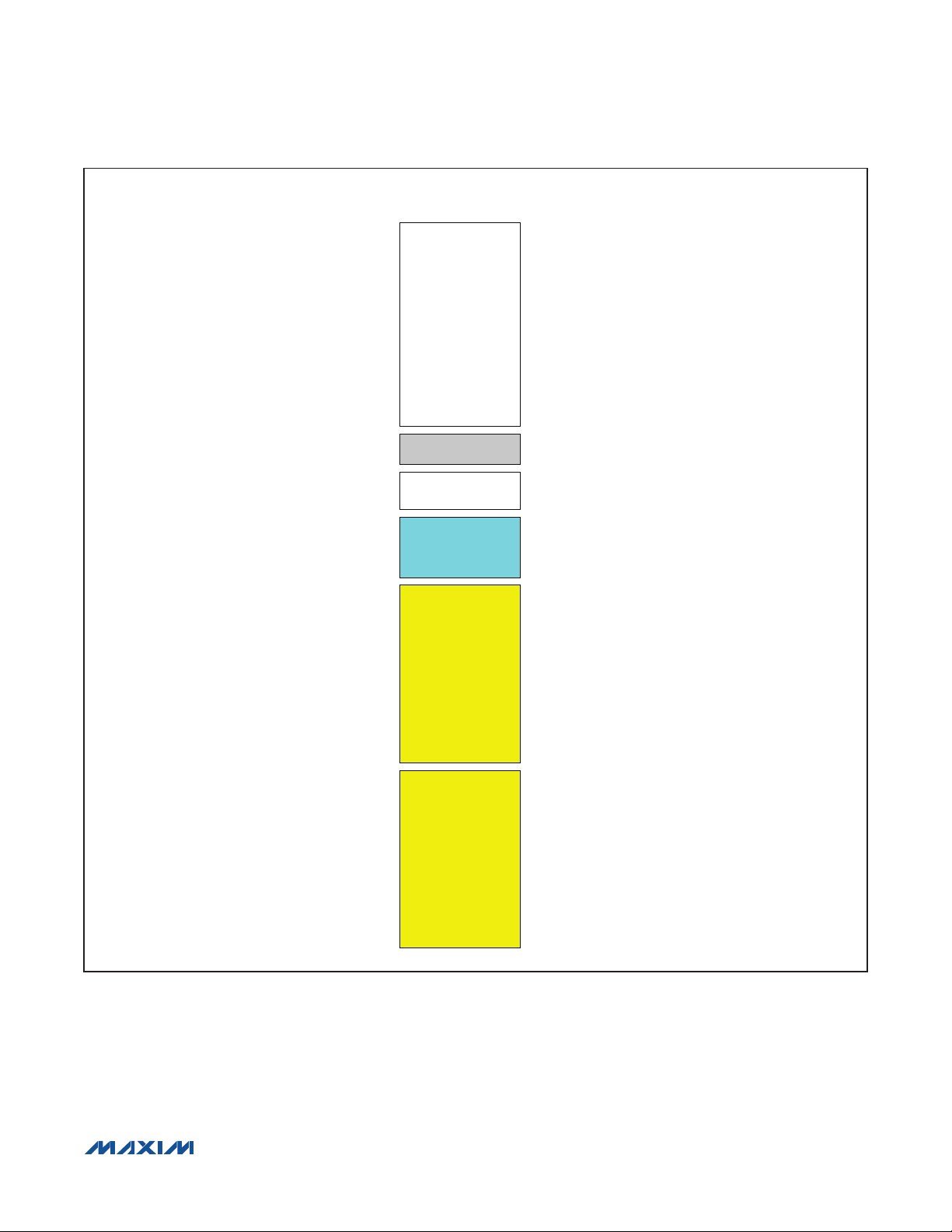

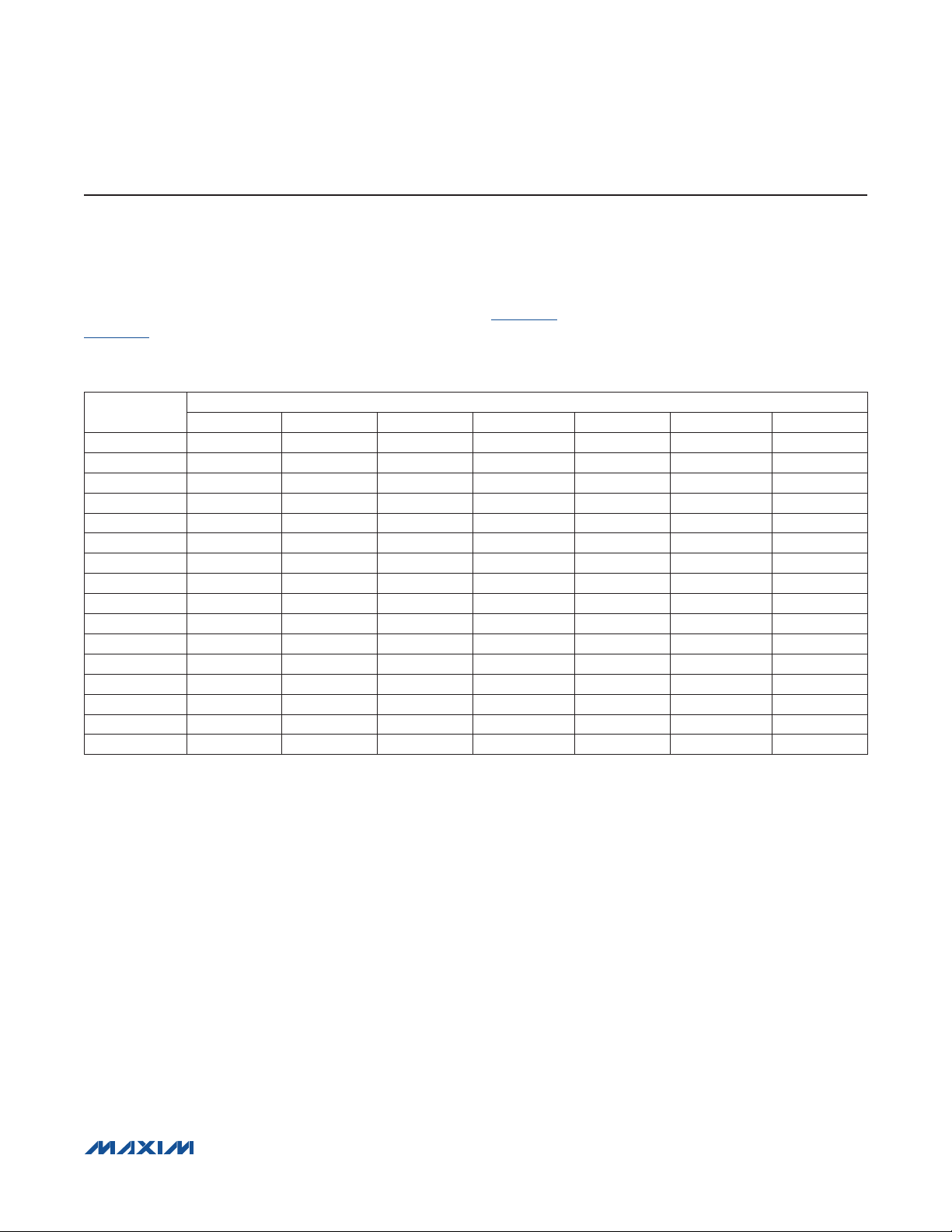

The MAX31782 system management microcontroller provides a complete solution for the monitoring and controlling

of complex system physical health characteristics. The MAX31782 is based on the high-performance 16-bit family of

MAXQM reduced instruction set computing (RISC) microcontrollers. The MAX31782 provides generous amounts of

flash program memory and SRAM data memory.

MAX31782 SYSTEM MANAGEMENT MICROCONTROLLER

RST

MSDA

MSCL

P6.n

n = 0−4

SCL

SDA

2

I

C

MASTER

GPIO

2

I

C

SLAVE

SYSTEM CLOCK

12-BIT

ADC

CLOCK CONTROL,

WATCHDOG TIMER, AND

POWER MONITOR

CKCN

WDCN

IC

INTERRUPT

LOGIC

IC IP

IMR

IIR

CURRENT

SOURCES

ADCH

STACK MEMORY

16 x 16

SP

ADDRESS

GENERATION

LOOP COUNTERS

LC[n]

BOOLEAN

VARIABLE

MANIPULATION

ACCUMULATORS

(16)

AP

APC

PSF

6-CHANNEL PULSE-WIDTH

MODULATOR

32KWords

FLASH

1KWords

SRAM

MEMORY MANAGEMENT

UNIT (MMU)

INSTRUCTION

DECODE

(src, dst TRANSPORT

DETERMINATION)

6-CHANNEL TACHOMETER

4KWords

UTILITY ROM

DATA POINTERS

DP[0], DP[1],

FP = (BP+OFFS)

DPC

MAXQ20 CORE

SYSTEM MODULES/

REGISTERS

V

INTERNAL TEMP

AD5P

MUX

AD4P

AD3P

AD2P

AD1P

DD

AD0P

MAXQ is a registered trademark of Maxim Integrated Products, Inc.

��������������������������������������������������������������� Maxim Integrated Products 1-1

PWM.5

PWM.4

PWM.3

PWM.2

PWM.1

PWM.0

TACH.5

TACH.4

TACH.3

TACH.2

TACH.1

MAX31782

TACH.0

Revision 0; 8/11

Page 4

MAX31782 User’s Guide

Some of the resources and features that the MAX31782 provides for monitoring and controlling a complex system

include the following:

• Remote temperature measurement of diode connected transistors on up to 6 channels

• Accurate voltage measurement using the 12-bit analog to digital converter (ADC) on up to 6 channels

• Internal temperature sensor

• Independent slave and master I2C-compatable interfaces

• Six independent PWM outputs and tachometer Inputs

• Hardware multiplier unit

• 32KWords of flash and 1KWords of SRAM memory

• Included ROM routines that allow bootloading and in-application programming flash memory

• In-system debugging

This document is provided as a supplement to the MAX31782 IC data sheet. This user’s guide provides the information

necessary to develop applications using the MAX31782. All electrical and timing specifications, pin descriptions, package information, and ordering information can be found in the MAX31782 IC data sheet.

��������������������������������������������������������������� Maxim Integrated Products 1-2

Revision 0; 8/11

Page 5

MAX31782 User’s Guide

SECTION 2: ARCHITECTURE

This section contains the following information:

2.1 Instruction Decoding . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

2.2 Register Space. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-3

2.3 Memory Types . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.3.1 Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

2.3.2 SRAM Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.3.3 Utility ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.3.4 Stack Memory. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.4 Program and Data Memory Mapping and Access . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-5

2.4.1 Program Memory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.4.2 Program Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.4.3 Data Memory Access. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.4.3.1 Data Pointers . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-6

2.4.3.2 Frame Pointer. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.4.4 Data Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-8

2.4.4.1 Memory Map When Executing from Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

2.4.4.2 Memory Map When Executing from Utility ROM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

2.4.4.3 Memory Map When Executing from SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

2.5 Data Alignment. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.6 Reset Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.6.1 Power-On/Brownout Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-12

2.6.2 Watchdog Timer Reset. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.6.3 External Reset . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.6.4 Internal System Resets. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

2.7 Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

2.8 Power Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

LIST OF FIGURES

Figure 2-1. Instruction Word Format . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-2

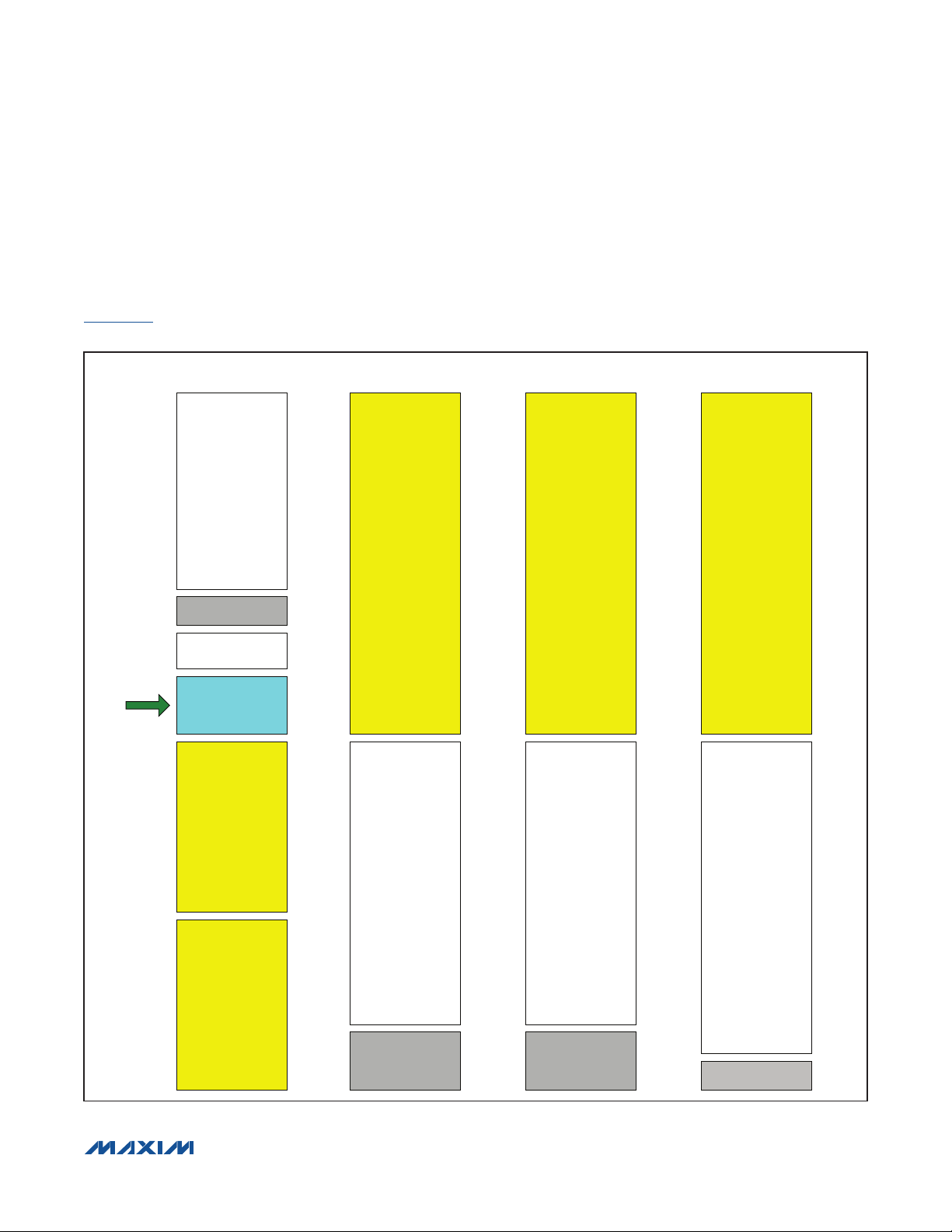

Figure 2-2. Program Memory Mapping . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-7

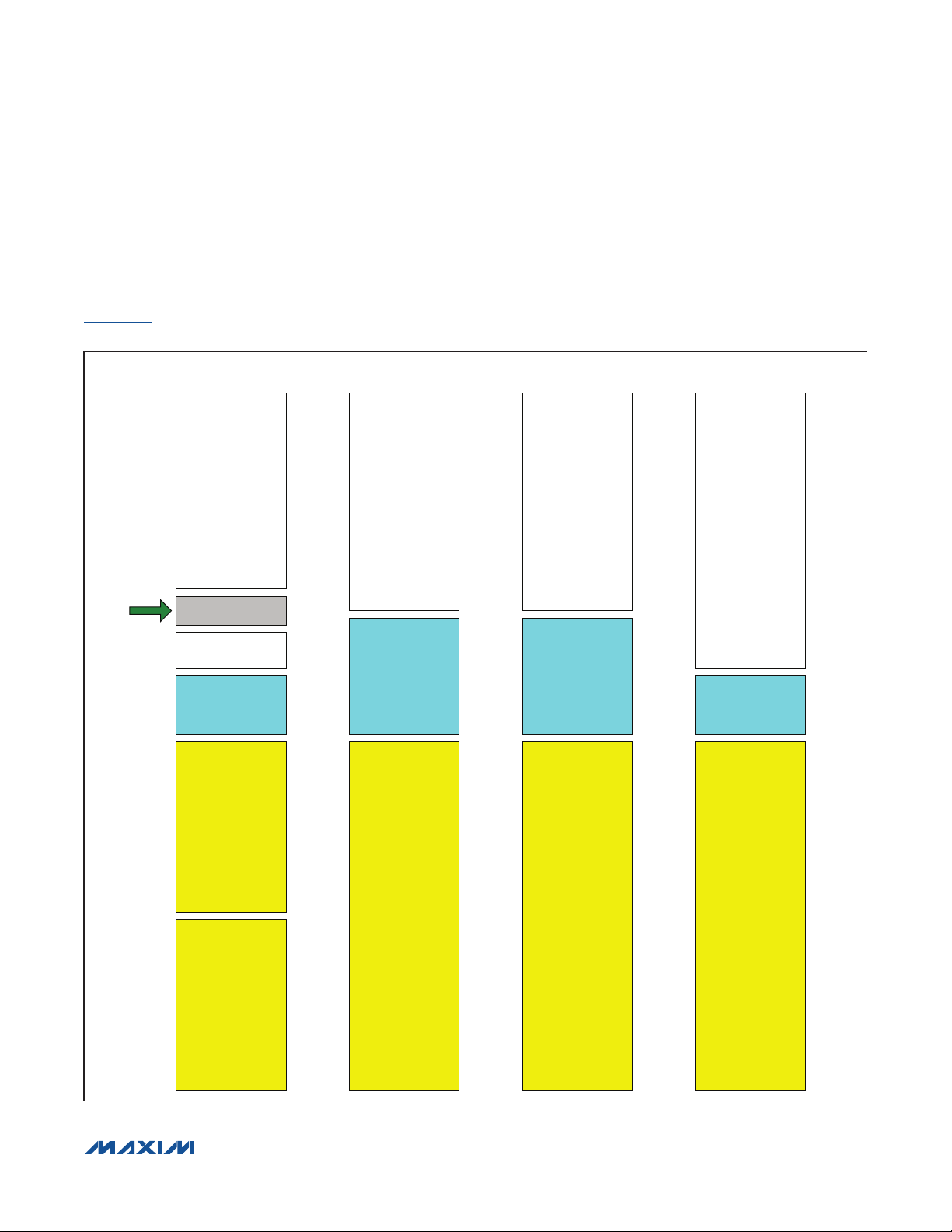

Figure 2-3. Memory Map When Executing from Flash Memory . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-9

Figure 2-4. Memory Map When Executing from Utility ROM. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-10

Figure 2-5. Memory Map When Executing from SRAM . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-11

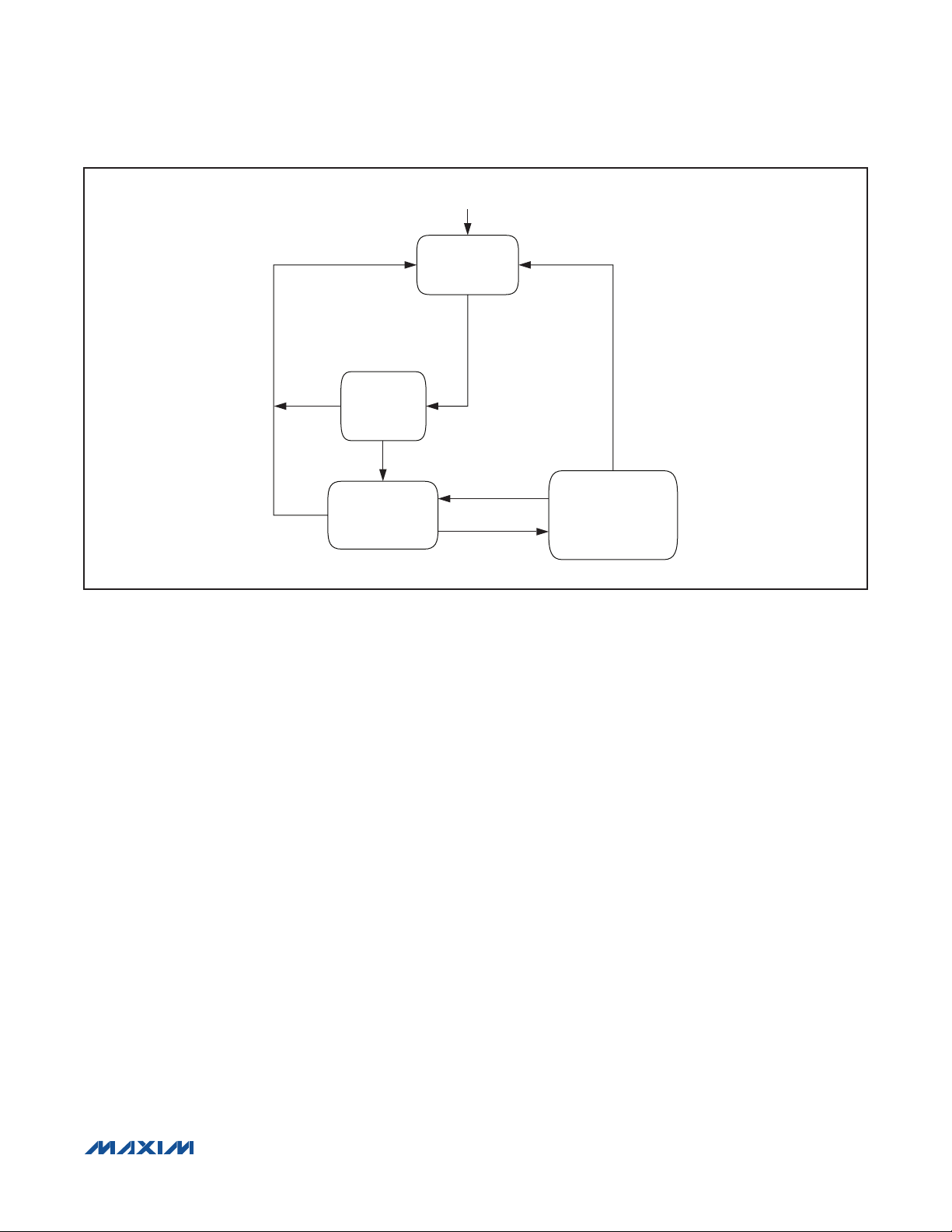

Figure 2-6. MAX31782 State Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-13

LIST OF TABLES

Table 2-1. Register-to-Register Transfer Operations. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-4

Table 2-2. State of Circuits During Different Modes . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .2-14

��������������������������������������������������������������� Maxim Integrated Products 2-1

Revision 0; 8/11

Page 6

MAX31782 User’s Guide

SECTION 2: ARCHITECTURE

The MAX31782 contains a MAXQ20 low-cost, high-performance, CMOS, fully static microcontroller with flash memory.

It is structured on a highly advanced, 16-accumulator-based, 16-bit RISC architecture. Fetch and execution operations

are completed in one cycle without pipelining, since the instruction contains both the op code and data. The highly

efficient core is supported by 16 accumulators and a 16-level hardware stack, enabling fast subroutine calling and task

switching.

Data can be quickly and efficiently manipulated with three internal data pointers. Two of these data pointers, DP0 and

DP1, are stand-alone 16-bit pointers. The third data pointer, frame pointer, is composed of a 16-bit base pointer (BP)

and an 8-bit offset register (OFFS). All three pointers support postincrement/decrement functionality for read operations

and preincrement/decrement for write operations. For the frame pointer (FP = BP[OFFS]), the increment/decrement

operation is executed on the OFFS register and does not affect the base pointer. Multiple data pointers allow more than

one function to access data memory without having to save and restore data pointers each time.

Stack functionality is provided by dedicated memory with a 16-bit width and a depth of 16. An on-chip memory management unit (MMU) allows logical remapping of the program and data spaces, and thus facilitates in-system programming

and fast access to data tables, arrays, and constants located in flash memory.

This section provides details on the following topics.

1) Instruction decoding

2) Register space

3) Memory types

4) Program and data memory mapping and access

5) Data alignment

6) Reset conditions

7) Clock generation

8) Power modes

2.1 Instruction Decoding

The MAX31782 uses the standard 16-bit MAXQ20 core instruction set, which is described in SECTION 20: Instruction

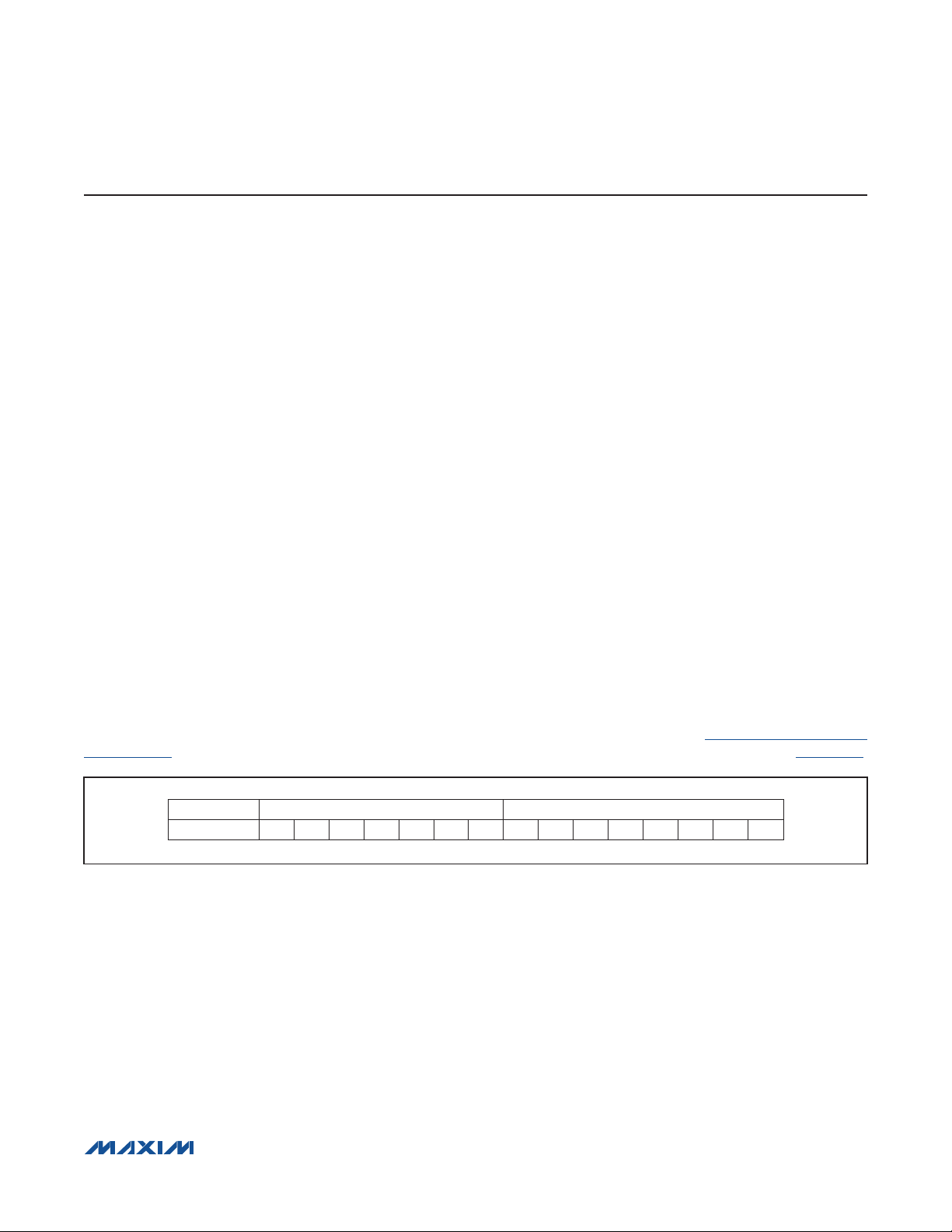

Set Summary. Every instruction is encoded as a single 16-bit word. The instruction word format is shown in Figure 2-1.

FORMAT DESTINATION SOURCE

f d d d d d d d s s s s s s s s

Figure 2-1. Instruction Word Format

Bit 15 (f) indicates the format for the source field of the instruction as follows:

If f equals 0, the instruction is an immediate source instruction. The source field represents an immediate 8-bit value.

If f equals 1, the instruction is a register source instruction. The source field represents the register from which the

source value is read.

Bits 14 to 8 (ddddddd) represent the destination for the transfer. This value always represents a destination register. The

lower four bits contain the module specifier and the upper three bits contain the register index in that module.

Bits 7 to 0 (ssssssss) represent the source for the transfer. Depending on the value of the format field, this can either

be an immediate value or a source register. If this field represents a register, the lower four bits contain the module

specifier and the upper four bits contain the register index in that module.

��������������������������������������������������������������� Maxim Integrated Products 2-2

Revision 0; 8/11

Page 7

MAX31782 User’s Guide

This instruction word format presents the following limitations.

1) There are 32 registers per register module, but only 4 bits are allocated to designate the source register and only 3

bits are allocated to designate the destination register.

2) The source field only provides 8 bits of data for an immediate value; however, a 16-bit immediate value can be

required.

The MAX31782 uses a prefix register (PFX) to address these limitations. The PFX register provides the additional bits

required to access all 32 registers within a module. The PFX register also provides the additional 8 bits of data required

to make a 16-bit immediate data source. The data that is written to the PFX register survives for only one clock cycle.

This means the write to the PFX register must occur immediately prior to the instruction requiring the PFX register. The

PFX register is cleared to zero after one cycle so it does not affect any other instructions. The write to the PFX register is

done automatically by the assembler and requires one additional execution cycle. So, while most instructions execute

in a single cycle, two cycles are needed for instructions that require the PFX register.

The architecture of the MAX31782 is transport-triggered. This means that writing to or reading from certain register

locations also causes side effects to occur. These side effects form the basis of the MAX31782’s higher level op codes,

such as ADDC, OR, and JUMP. While these op codes are actually implemented as MOVE instructions between certain register locations, the encoding is handled by the assembler and need not be a concern to the programmer. The

unused “empty” locations in the system register modules are used for these higher level op codes.

The instruction set is designed to be highly orthogonal. All arithmetic and logical operations that use two registers can

use any register along with the accumulator. Data can be transferred between any two registers in a single instruction.

2.2 Register Space

The MAX31782 provides a total of 13 register modules broken up into two different groups. These groupings are

descriptive only, as there is no difference between accessing the two register groups from a programming perspective.

The two groups are:

1) Peripheral Registers: These are the lower six modules (Modules 0h through 5h). The peripheral registers in the

MAX31782 are used for functionalities such as ADC, PWM outputs, tachometer inputs, GPIO, etc. The peripheral

registers are not used to implement op codes.

2) System Registers: These are modules 8h, 9h, and Bh through Fh. The system registers in the MAX31782 are used

to implement higher level op codes as well as the following common system features.

• 16-bit ALU and associated status flags (zero, equals, carry, sign, overflow)

• 16 working accumulator registers, each 16-bit, along with associated control registers

• Instruction pointer

• Registers for interrupt control, handling, and identification

• Auto-decrementing loop counters for fast, compact looping

• Two data pointer registers and a frame pointer for data memory access

Each system register module has 16 registers, while each peripheral register module has 32 registers. The number of

cycles required to access a particular register depends upon the register’s index within the module. The access times

based upon the register index are grouped as follows:

• The first eight registers (index 0h to 7h) in each module can be read from or written to in a single cycle.

• The second eight registers (index 8h to 0Fh) can be read from in a single cycle and written to in two cycles (by using

the PFX register).

• The last 16 registers (10h to 1Fh) in peripheral register modules can be read or written in two cycles (always requiring use of the PFX register).

��������������������������������������������������������������� Maxim Integrated Products 2-3

Revision 0; 8/11

Page 8

MAX31782 User’s Guide

Registers can be 8 or 16 bits in length. Some registers can contain reserved bits. The user should not write to any

reserved bits. Data transfers between registers of different sizes are handled as shown in Table 2-1.

• If the source and destination registers are both 8 bits wide, data is copied bit to bit.

• If the source register is 8 bits wide and the destination register is 16 bits wide, the data from the source register is

transferred into the lower 8 bits of the destination register. The upper 8 bits of the destination register are set to the

current value of the PFX register; this value is normally zero, but it can be set to a different value by the previous

instruction if needed. The PFX register reverts back to zero after one cycle, so this must be done by the instruction

immediately before the one that is using the value.

• If the source register is 16 bits wide and the destination register is 8 bits wide, the lower 8 bits of the source are

transferred to the destination register.

• If both registers are 16 bits wide, data is copied bit to bit.

The above rules apply to all data movements between defined registers. Data transfer to/from undefined register locations has the following behavior:

• If the destination is an undefined register, the MOVE is a dummy operation but can trigger an underlying operation

according to the source register (e.g., @DPn--).

• If the destination is a defined register and the source is undefined, the source data for the transfer depends upon

the source module width. If the source is from a module containing 8-bit or 8-bit and 16-bit source registers, the

source data is equal to the prefix data as the upper 8 bits and 00h as the lower 8 bits. If the source is from a module

containing only 16-bit source registers, 0000h source data is used for the transfer.

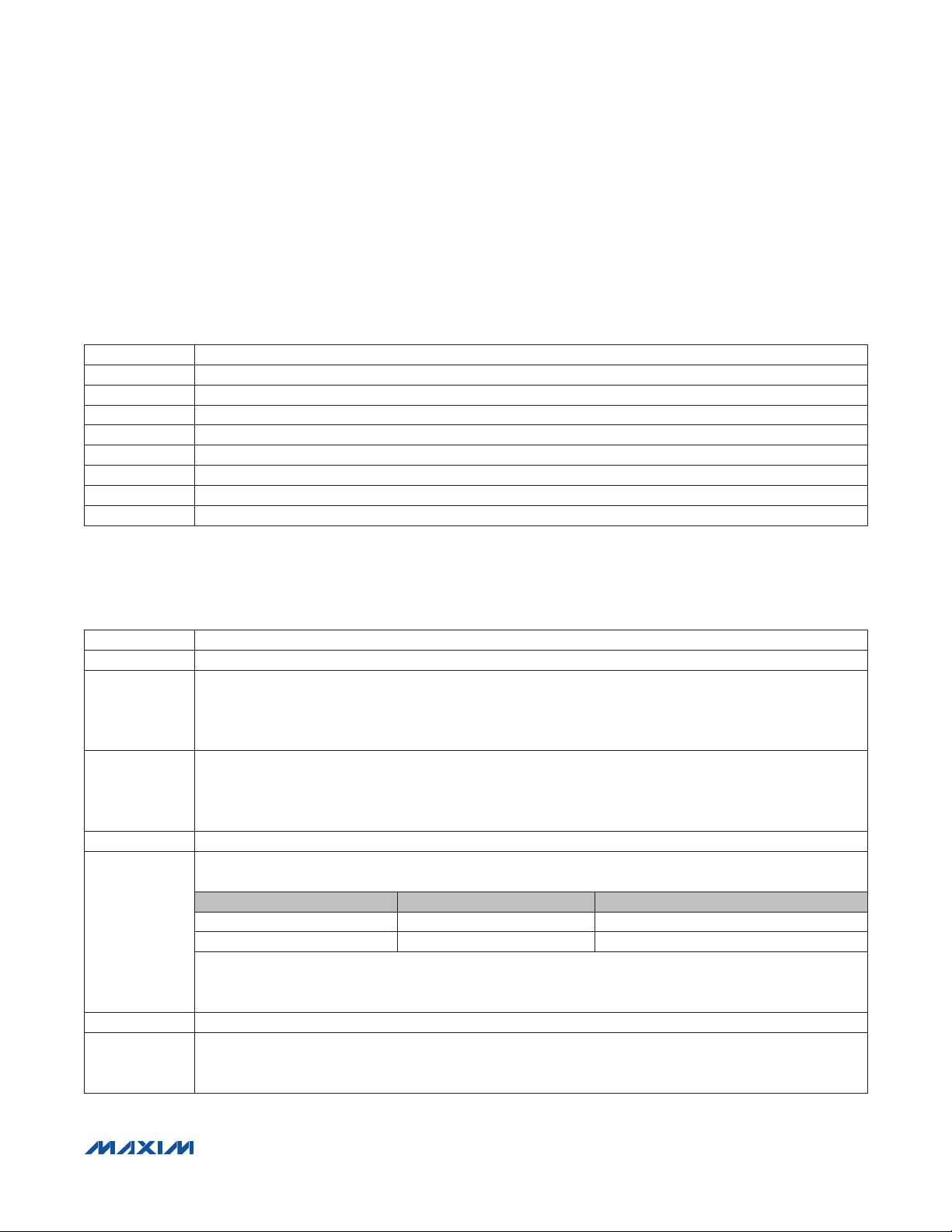

Table 2-1. Register-to-Register Transfer Operations

SOURCE REGISTER SIZE

(BITS)

8 8 X — Source [7:0]

8 16 No 00h Source [7:0]

8 16 Yes PFX [7:0] Source [7:0]

16 8 X — Source [7:0]

16 16 X Source [15:8] Source [7:0]

DESTINATION REGISTER SIZE

(BITS)

PREFIX

SET?

DESTINATION SET TO VALUE

HIGH 8 BITS LOW 8 BITS

2.3 Memory Types

In addition to the internal register space, the MAX31782 incorporates the following memory types:

• 32KWords of flash memory

• 1KWords of SRAM

• 4KWords of utility ROM contain a debugger and program loader

• 16-level stack memory for storage of program return addresses and general-purpose use

The memory on the MAX31782 is organized according to a Harvard architecture. This means that there are separate busses for both program and data memory. Stack memory is also separate and is accessed through a dedicated register set.

2.3.1 Flash Memory

The MAX31782 contains 32KWords (32K x 16) of flash memory. The flash memory begins at address 0000h and is

contiguous through word address 7FFFh. The flash memory can also be used for storing lookup tables and other nonvolatile data.

The incorporation of flash memory allows the contents of the flash memory to be upgraded in the field, either by the

application or by one of the bootloaders (JTAG or I2C). Writing to flash memory must be done indirectly by using routines that are provided by the utility ROM. See SECTION 21: Utility ROM and SECTION 18: In-System Programming for

more details.

��������������������������������������������������������������� Maxim Integrated Products 2-4

Revision 0; 8/11

Page 9

MAX31782 User’s Guide

2.3.2 SRAM Memory

The MAX31782 contains 1KWords (1K x 16) of SRAM memory. The SRAM memory address begins at address 0000h

and is contiguous through word address 03FFh. The contents of the SRAM are indeterminate after power-on reset, but

are maintained during stop mode and non-POR resets.

When using the in-circuit debugging features, the highest 19 bytes of the SRAM must be reserved for saved state

storage and working space for the debugging routines. If in-circuit debug is not used, the entire 1KWords of SRAM is

available for application use.

2.3.3 Utility ROM

The utility ROM is a 4KWord segment of memory. The utility ROM memory address begins at word address 8000h and

is contiguous through word address 8FFFh. The utility ROM is programmed at the factory and cannot be modified. The

utility ROM provides the following system utility functions:

• Reset vector (not user code reset vector)

• In-system programming (bootstrap loader) over JTAG or I2C-compatible interfaces

• In-circuit debug routines

• Routines for in-application flash programming

Following any reset, the MAX31782 automatically starts execution at the reset vector, which is address 8000h in the utility

ROM. The ROM code determines whether the program execution should immediately jump to the start of application code

(flash address 0000h), or to one of the special routines mentioned. Routines within the utility ROM are firmware-accessible

and can be called as subroutines by the application software. See SECTION 21: Utility ROM, SECTION 18: In-System

Programming, and SECTION 17: In-Circuit Debug Mode for more information on the routines provided by the utility ROM.

2.3.4 Stack Memory

A 16-bit, 16-level on-chip stack provides storage for program return addresses and general-purpose use. The stack is

used automatically by the processor when the CALL, RET, and RETI instructions are executed, and when an interrupt is

serviced. The stack can also be used explicitly to store and retrieve data by using the @SP- - source, @++SP destination, or the PUSH, POP, and POPI instructions. The POPI instruction acts identically to the POP instruction except that

it additionally clears the INS bit.

The width of the stack is 16 bits to accommodate the instruction pointer size. On reset, the stack pointer SP initializes

to the top of the stack (0Fh). The CALL, PUSH, and interrupt vectoring operations first increment SP and then store a

value at @SP. The RET, RETI, POP, and POPI operations first retrieve the value at @SP and then decrement SP.

The stack memory is initialized to indeterminate values upon reset or power-up. Stack memory is dedicated for stack

operations only and cannot be accessed by the MAX31782 program or data busses.

When using the in-circuit debugging features, one word of the stack must be reserved for the debugging routines. If

in-circuit debug is not used, the entire stack is available for application use.

2.4 Program and Data Memory Mapping and Access

The memory on the MAX31782 is implemented using a Harvard architecture, with separate buses for program and data

memory. The memory management unit (MMU) allows the MAX31782 to also support a pseudo-Von Neumann memory

map. The pseudo-Von Neumann memory map allows each of the memory segments (flash, SRAM, and utility ROM) to

be logically mapped into a single contiguous memory map. This allows all the memory segments to be accessed as

both program and memory data. The advantages the pseudo-Von Neumann memory map provides are:

• Program execution can occur from the flash, SRAM, or utility ROM memory segments.

• The SRAM and flash memory segments can both be used for data memory.

Using the pseudo-Von Neumann memory map does have one restriction. This restriction is that a particular memory

segment cannot be simultaneously accessed as both program and data memory.

��������������������������������������������������������������� Maxim Integrated Products 2-5

Revision 0; 8/11

Page 10

MAX31782 User’s Guide

2.4.1 Program Memory Access

The instructions that the MAX31782 is executing reside in what is defined as the program memory. The MMU fetches

the instructions using the program bus. The instruction pointer (IP) register designates the program memory address of

the next instruction to fetch. The IP register is read/write accessible by the user software. A write to the IP register forces

program flow to the new address on the next cycle following the write. The content of the IP register is incremented

by 1 automatically after each fetch operation. From an implementation perspective, system interrupts and branching

instructions simply change the contents of the IP register and force the op code to fetch from a new program location.

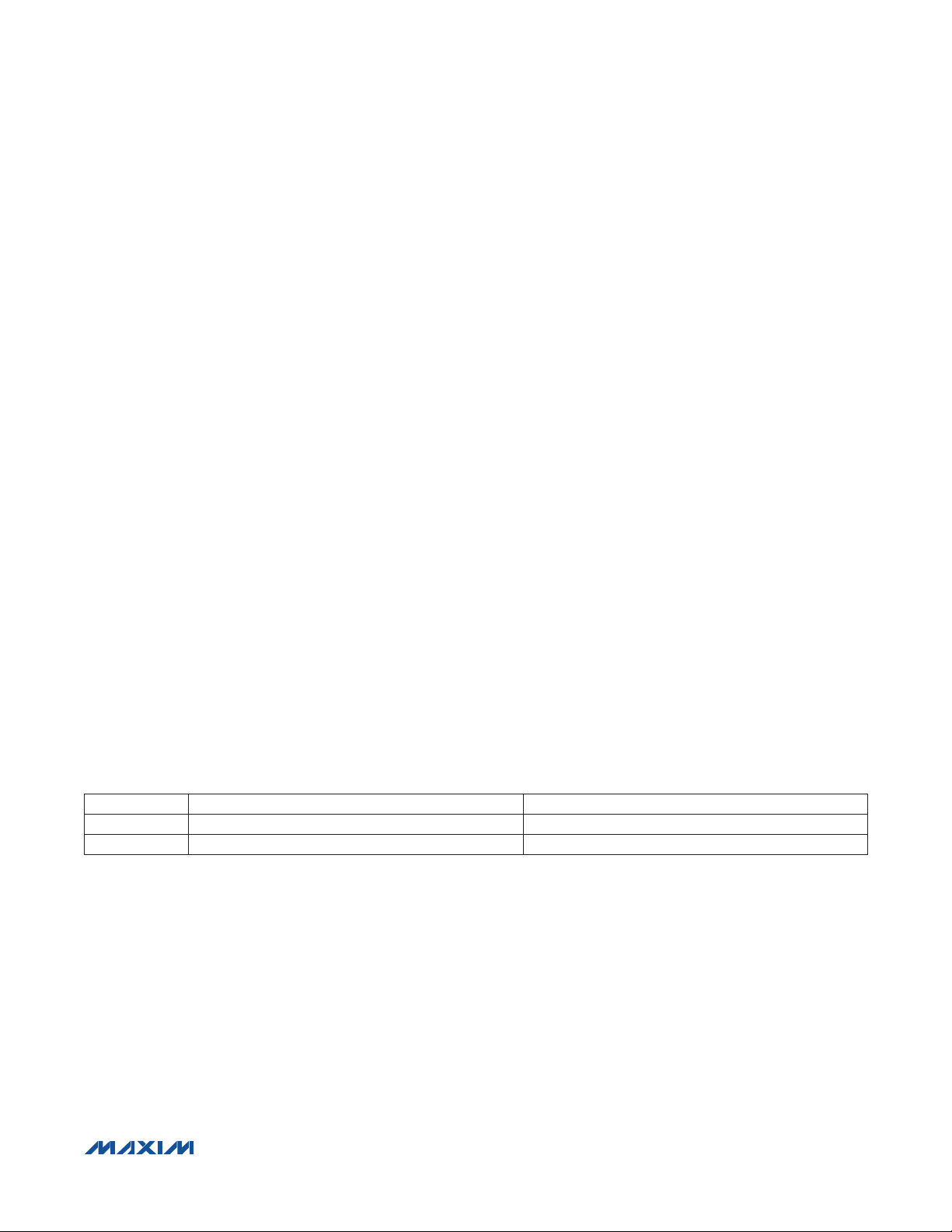

2.4.2 Program Memory Mapping

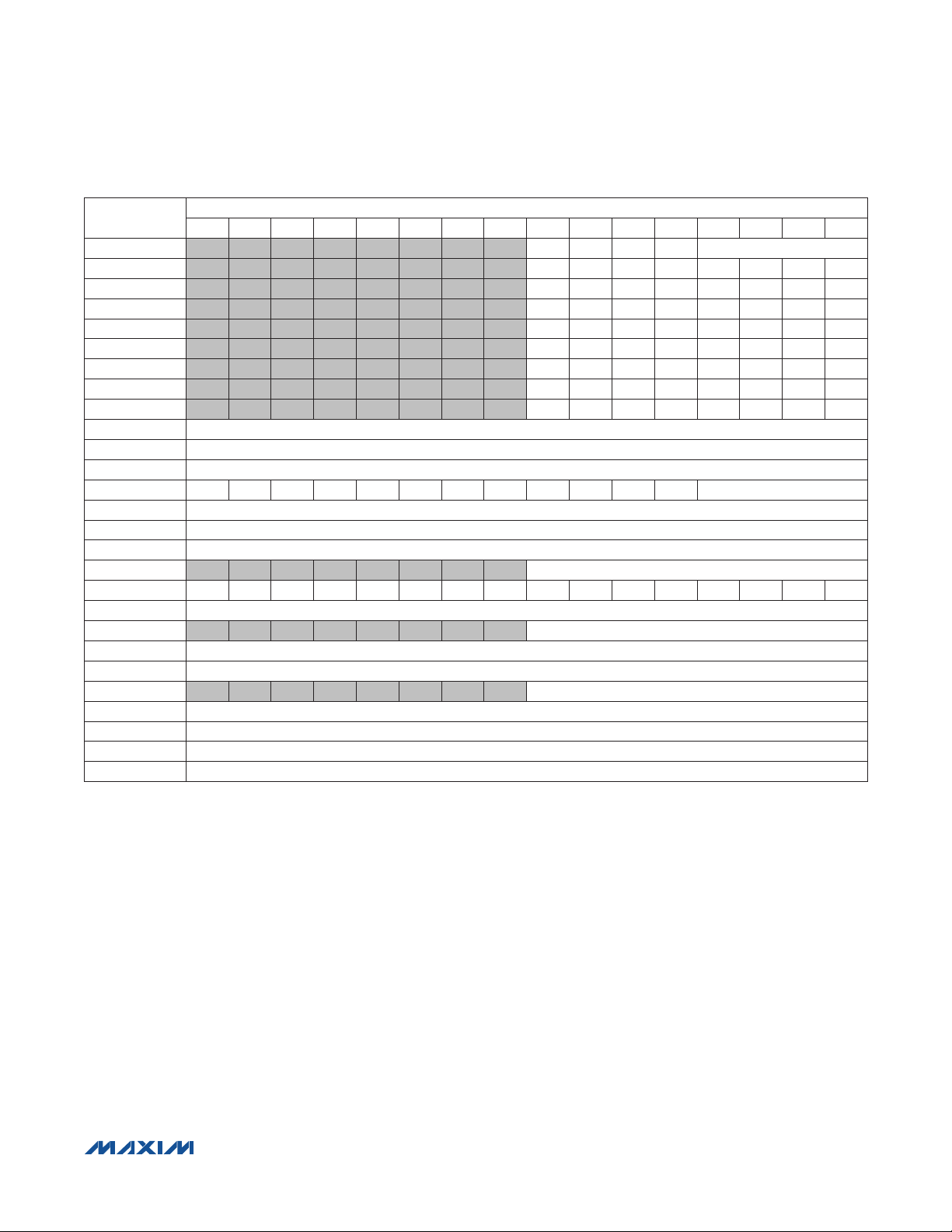

The MAX31782’s mapping of the three memory segments (flash, SRAM, and utility ROM) as program memory is shown

in Figure 2-2. The mapping of memory segments into program space is always the same. When referring to memory

as program memory, all addresses are given as word addresses. The 32KWord flash memory segment is located at

memory location 0000h through 7FFFh and is logically divided into two pages, each containing 16KWords. The utility

ROM is located from location 8000h through 8FFFh, followed by the SRAM memory segment at location A000h through

A3FFh. The user code reset vector, which is the first instruction of user program code that is executed, is located at

flash memory address 0000h. User program code should always begin at this address.

2.4.3 Data Memory Access

Data memory mapping and access control are handled by the memory management unit (MMU). Read/write access

to data memory can be in word or in byte mode. The MAX31782 provides three pointers that can be used for indirect

accessing of data memory. The MAX31782 has two data pointers (@DPn) and one frame pointer (@BP[OFFS]). These

pointers are implemented as registers that can be directly accessed by user software. A data memory access requires

only one system clock period.

2.4.3.1 Data Pointers

To access data memory, the data pointers are used as one of the operands in a MOVE instruction. If the data pointer is

used as a source, the core performs a load operation that reads data from the memory location addressed by the data

pointer. If the data pointer is used as destination, the core performs a store operation that writes data to the memory

location addressed by the data pointer. Following are some examples of setting and using a data pointer.

moveDP[0], #0100h ;set pointerDP[0]toaddress100h

moveAcc, @DP[0] ;readdatafromlocation100h

move@DP[0], Acc ;writetolocation100h

The address pointed to by the data pointers can be automatically incremented or decremented. If the data pointer is

used as a source, the pointer can be incremented or decremented after the data access. If the data pointer is used as

a destination, the increment or decrement can occur prior to the data access. Following are examples of using the data

pointers increment/decrement features.

moveAcc, @DP[0]++ ;increment DP[0]afterread

moveAcc, @DP[1]-- ;decrement DP[1]afterread

move@++DP[0], Acc ;increment DP[0]beforewrite

move@--DP[1], Acc ;decrement DP[0]beforewrite

��������������������������������������������������������������� Maxim Integrated Products 2-6

Revision 0; 8/11

Page 11

PROGRAM

SPACE

MAX31782 User’s Guide

FFFFh

1K x 16

SRAM

4K x 16

UTILITY ROM

16K x 16

FLASH

(PAGE 1)

16K x 16

FLASH

(PAGE 0)

A3FFh

A000h

8FFFh

8000h

7FFFh

4000h

3FFFh

Figure 2-2. Program Memory Mapping

��������������������������������������������������������������� Maxim Integrated Products 2-7

0000h

Revision 0; 8/11

Page 12

MAX31782 User’s Guide

2.4.3.2 Frame Pointer

The frame pointer (BP[OFFS]) is formed by the 16-bit unsigned addition of the 16-bit frame pointer base register (BP)

and the 8-bit frame pointer offset register (OFFS). The method the MAX31782 uses to access data using the frame

pointer is similar to the data pointers. When increments or decrements are used, only the value of OFFS is incremented

or decremented. The base pointer (BP) remains unaffected by increments or decrements of the OFFS register, including when the OFFS register rolls over from FFh to 00h or from 00h to FFh. Following are examples of how to use the

frame pointer.

moveBP, #0100h ;setbasepointer toaddress100h

moveOFFS, #10h ;settheoffset to10h,

moveAcc, @BP[OFFS] ;read datafromlocation0110h

move@BP[OFFS], Acc ;write datatolocation0110h

moveAcc, @BP[OFFS++] ;increment OFFSafterread

moveAcc, @BP[OFFS++] ;decrement OFFSafterread

move@BP[++OFFS], Acc ;increment OFFSbeforewrite

move@BP[--OFFS], Acc ;decrement OFFSbeforewrite

2.4.4 Data Memory Mapping

The MAX31782’s pseudo-Von Neumann memory map allows the MMU to read data from each of the three memory segments (flash, SRAM, utility ROM). The MMU can also write data directly to the SRAM memory segment. Data memory

can be written to the flash memory segment, but because writing to flash requires the use of the utility ROM routines,

this is not a direct access. The logical mapping of the three memory segments as data memory varies depending upon:

• from which memory segment instructions are currently being executed

• if data memory is being accessed in word or byte mode

In all cases, whichever memory segment is currently being used as program memory cannot be accessed as data

memory.

When the program is currently executing instructions from either the SRAM or utility ROM memory segments, the flash

memory is mapped to half the data memory space. If word access mode is selected, both pages (32KWords) can

be logically mapped to data memory space. If byte access mode is selected, only one page (32KB) can be logically

mapped to half of the data memory space. When operating in byte access mode, the selection of which flash page is

mapped into data memory space is determined by the code data access bit (CDA0):

CDA0 SELECTED PAGE IN BYTE MODE SELECTED PAGE IN WORD MODE

0 P0 P0 and P1

1 P1 P0 and P1

The next three sections detail the mapping of the different memory segments as data memory depending upon from

which memory segment instructions are currently being executed.

��������������������������������������������������������������� Maxim Integrated Products 2-8

Revision 0; 8/11

Page 13

MAX31782 User’s Guide

2.4.4.1 Memory Map When Executing from Flash Memory

When executing from the flash memory:

• Read and write operations of SRAM memory are executed normally.

• The utility ROM can be read as data, starting at 8000h of the data space. The utility ROM cannot be written.

Figure 2-3 illustrates the mapping of the SRAM and utility ROM memory segments into data memory space when code

is executing from the flash memory segment.

PROGRAM

SPACE

1K x 16

SRAM

4K x 16

UTILITY ROM

DATA SPACE

(BYTE MODE)

FFFFh FFFFh FFFFh

A3FFh

A000h

8FFFh

8000h 8000h

7FFFh 7FFFh

8K x 8

UTILITY ROM

9FFFh

DATA SPACE

(WORD MODE)

8FFFh

4K x 16

UTILITY ROM

8000h

7FFFh

16K x 16

FLASH

(PAGE 1)

4000h

3FFFh

EXECUTING FROM

16K x 16

FLASH

(PAGE 0)

0000h 0000h 0000h

Figure 2-3. Memory Map When Executing from Flash Memory

��������������������������������������������������������������� Maxim Integrated Products 2-9

2K x 8

SRAM

07FFh

1K x 16

SRAM

03FFh

Revision 0; 8/11

Page 14

MAX31782 User’s Guide

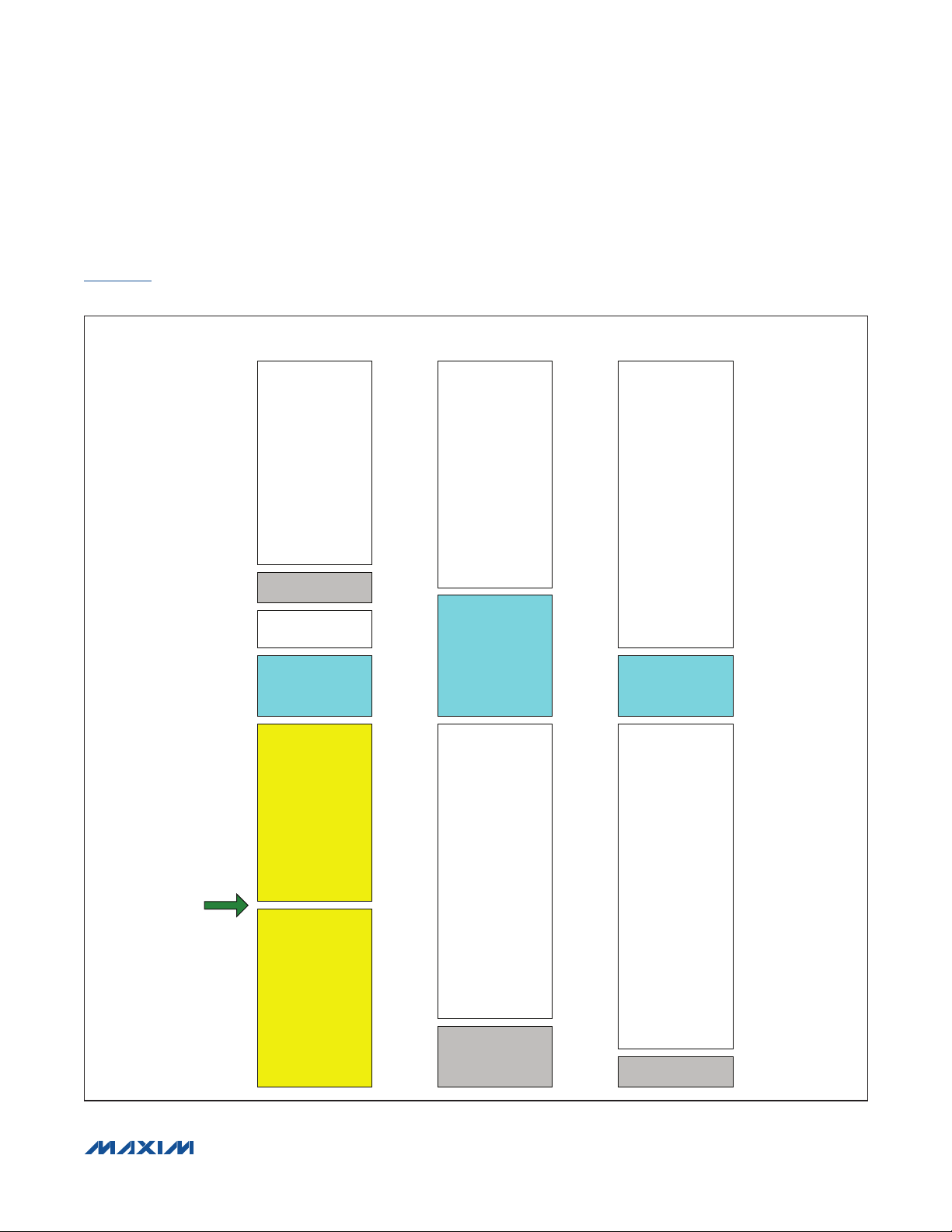

2.4.4.2 Memory Map When Executing from Utility ROM

When executing from the utility ROM:

• Read and write operations of SRAM memory are executed normally.

• Reading of flash memory is executed normally. Writing to flash memory requires the use of the utility ROM routines.

• One page (byte access mode) or both pages (word access mode) of the flash memory can be accessed as data

with an offset of 8000h as determined by the CDA0 bit.

Figure 2-4 illustrates the mapping of the SRAM and flash memory segments into data memory space when code is

executing from the utility ROM memory segment.

EXECUTING FROM

PROGRAM

SPACE

1K x 16

SRAM

4K x 16

UTILITY ROM

16K x 16

FLASH

(PAGE 1)

DATA SPACE

(BYTE MODE, CDA0 = 0)

FFFFh FFFFh FFFFh

32K x 8

LOWER HALF

(PAGE 0) OF

FLASH

A3FFh

A000h

8FFFh

8000h 8000h 8000h

7FFFh

DATA SPACE

(BYTE MODE, CDA0 = 1)

32K x 8

UPPER HALF

(PAGE 1) OF

FLASH

DATA SPACE

(WORD MODE)

FFFFh

32K x 16

FLASH

8000h

4000h

3FFFh

16K x 16

FLASH

(PAGE 0)

2K x 8

SRAM

0000h 0000h

Figure 2-4. Memory Map When Executing from Utility ROM

�������������������������������������������������������������� Maxim Integrated Products 2-10

07FFh

2K x 8

SRAM

07FFh

1K x 16

0000h 0000h

SRAM

03FFh

Revision 0; 8/11

Page 15

MAX31782 User’s Guide

2.4.4.3 Memory Map When Executing from SRAM

When executing from the SRAM:

The utility ROM can be read as data, starting at 8000h of the data space. The utility ROM cannot be written.

Reading of flash memory is executed normally. Writing to flash memory requires the use of the utility ROM routines.

One page (byte access mode) or both pages (word access mode) of the flash memory can be accessed as data with

an offset of 0000h. For byte access mode, the page of flash accessed is determined by the CDA0 bit.

Figure 2-5 illustrates the mapping of the flash and utility ROM memory segments into data memory space when code

is executing from the SRAM memory segment.

EXECUTING FROM

PROGRAM

SPACE

1K x 16

SRAM

4K x 16

UTILITY ROM

16K x 16

FLASH

(PAGE 1)

DATA SPACE

(BYTE MODE, CDA0 = 0)

FFFFh FFFFh FFFFh FFFFh

A3FFh

A000h

8FFFh

8000h

7FFFh

8K x 8

UTILITY ROM

8000h

7FFFh

DATA SPACE

(BYTE MODE, CDA0 = 1)

8K x 8

UTILITY ROM

9FFFh9FFFh

8000h

7FFFh

DATA SPACE

(WORD MODE)

8FFFh

4K x 16

UTILITY ROM

8000h

7FFFh

4000h

3FFFh

16K x 16

FLASH

(PAGE 0)

0000h 0000h 0000h 0000h

LOWER HALF

(PAGE 0) OF

Figure 2-5. Memory Map When Executing from SRAM

�������������������������������������������������������������� Maxim Integrated Products 2-11

32K x 8

FLASH

32K x 8

UPPER HALF

(PAGE 1) OF

FLASH

32K x 16

FLASH

Revision 0; 8/11

Page 16

MAX31782 User’s Guide

2.5 Data Alignment

To support merged program and data memory operation while maintaining efficient memory space usage, the data

memory must be able to support both byte and word mode accessing. Data is aligned in data memory as words, but

the effective data address is resolved to bytes. This data alignment allows program instruction fetching in words while

maintaining data accessibility at the byte level. It is important to realize that this accessibility requires strict word alignment. All executable or data words must align to an even address in byte mode. Care must be taken when updating a

code segment as misalignment of words likely results in loss of program execution control.

Memory is always read as a complete word, whether for program fetch or data access. The program decoder always

uses a full 16-bit word. The data access can utilize a word or an individual byte. Data memory is organized as two bytewide memory banks with common word address decode but two 8-bit data buses. In byte mode, data pointer hardware

reads out the full word containing the selected byte using the effective data word address pointer (the least significant

bit of the byte data pointer is not initially used). Then, the least significant data pointer bit functions as the byte select

that is used to place the correct byte on the data bus. For write access, data pointer hardware addresses a particular

word using the effective data word address while the least significant bit selects the corresponding data bank for write.

The contents of the other byte are left unaffected.

2.6 Reset Conditions

The MAX31782 has several possible sources of reset:

• Power-On/Brownout Reset

• Watchdog Timer Reset

• External Reset

• Internal System Reset

Once a reset condition has completed or been removed, code execution begins at the beginning of utility ROM, which

is address 8000h. The utility ROM code interrogates the I2C_SPE, JTAG_SPE, and PWL bits to determine if bootloading

is necessary. If bootloading is not required, execution jumps to the user code reset vector, which is at flash memory

address 0000h.

The RST pin is an output as well as an input. If a reset condition is generated by one of the MAX31782’s internal reset

sources (brownout, watchdog timer, or internal reset), an output reset pulse is generated on the RST pin while the

MAX31782 remains in reset.

2.6.1 Power-On/Brownout Reset

The MAX31782 provides a power-on reset (POR) circuit to ensure proper initialization of internal device states and analog circuits. The POR voltage threshold range is between approximately 1.1V and 1.7V. When VDD is below the POR

level, the state of all the MAX31782 pins, including RST, is indeterminate.

The MAX31782 also includes brownout detection capability. This is an on-chip precision reference and comparator that

monitors the supply voltage, VDD, to ensure that it is within acceptable limits. If VDD is below the brownout level (VBO),

the power monitor generates a reset. This can occur when:

• The MAX31782 is being powered up and VDD is above the POR level but still less than VBO.

• VDD drops from an acceptable level to less than VBO.

Once VDD exceeds VBO, the MAX31782 exits the reset condition and the internal oscillator starts up. After approximately 1000 clock cycles (t

• All registers and circuits enter their reset state.

• The POR flag in the watchdog control register (WDCN) is set to indicate the source of the reset.

• The MAX31782 begins normal operation (CPU state).

• Code execution begins at utility ROM location 8000h.

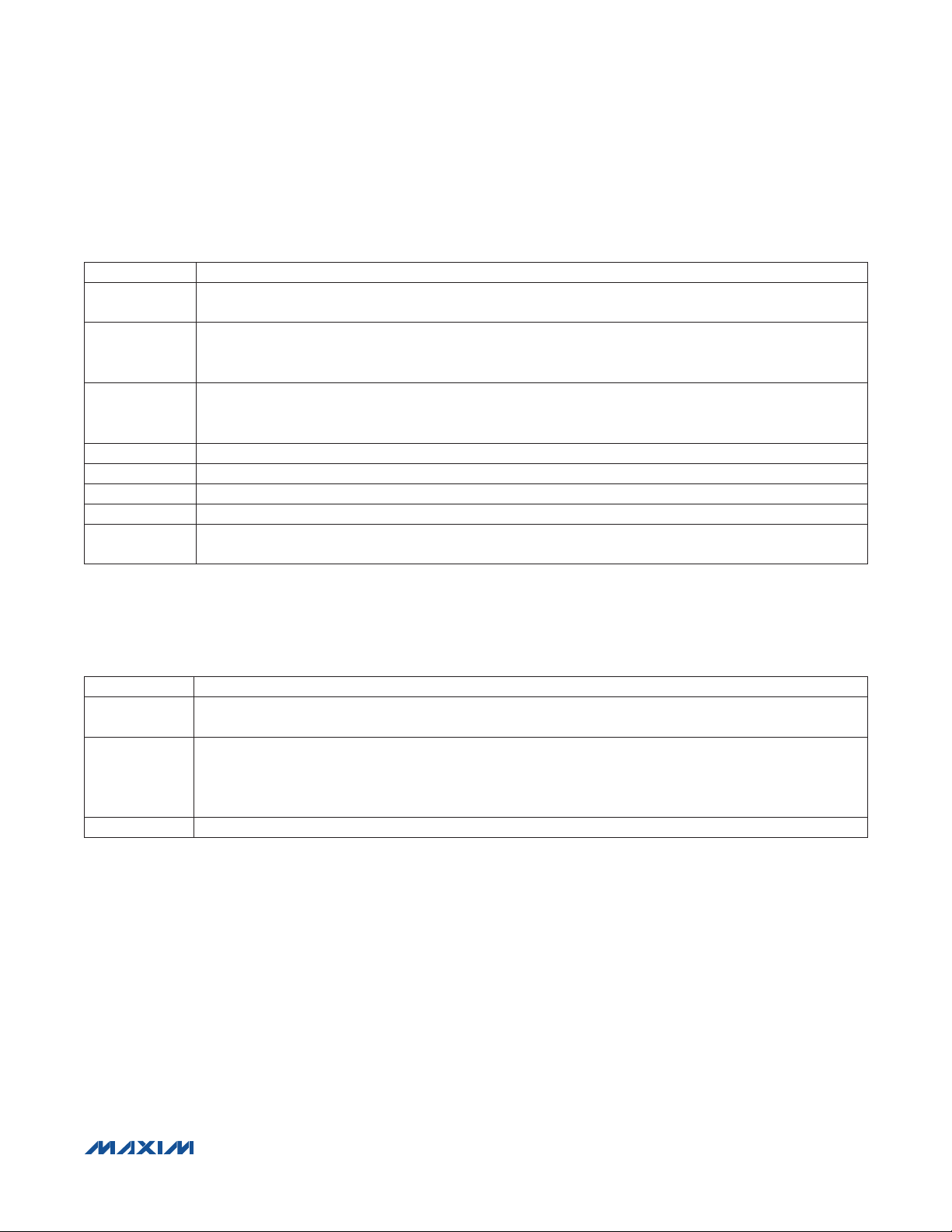

The transition between POR, brownout, and normal operation is detailed in Figure 2-6. Note: If VDD is below VBO, there

is a chance that the SRAM was corrupted. If the POR flag in WDCN is set, all data in SRAM should be reinitialized.

�������������������������������������������������������������� Maxim Integrated Products 2-12

SU:MOSC

) the MAX31782 performs the following tasks.

Revision 0; 8/11

Page 17

VDD < V

VDD < V

BO

STARTUP DELAY

DIGITAL CORE ON

BO

CODE IS EXECUTING

SYSTEM CLOCK

t

SU:MOSC

CPU MODE

ANALOG ON

POR

BROWNOUT STATE

CPU DISABLED

ANALOG ACTIVE

> V

V

DD

BO

PORT6 GPIO INT, I2C

START INT, SVM INT

OR EXT RESET

CKCN.STOP = 1

MAX31782 User’s Guide

VDD < V

BO

STOP MODE

DIGITAL CORE OFF

ANALOG ON

SVM MONITOR DEPENDS

ON SVMEN AND SVMSTOP

Figure 2-6. MAX31782 State Diagram

2.6.2 Watchdog Timer Reset

The watchdog timer is a programmable hardware timer that can be used to reset the processor in case a software

lockup or other unrecoverable error occurs. Once the watchdog is enabled, software must reset the watchdog timer

periodically. If the processor does not reset the watchdog timer before it elapses, the watchdog can initiate a reset.

If the watchdog resets the processor, the MAX31782 remains in reset and holds the RST pin low for 12 clock cycles.

When a reset occurs due to a watchdog timeout, the watchdog timer reset flag (WTRF) in the WDCN register is set to

indicate the source of the reset.

2.6.3 External Reset

During normal operation, the MAX31782 is placed into external reset when the RST pin is held at logic 0 for at least four

clock cycles. Once the MAX31782 enters reset mode, it remains in reset as long as the RST pin is held at logic 0. After

the RST pin returns to logic 1, the processor exits reset within 12 clock cycles.

An external reset pulse on the RST pin can also bring the MAX31782 out of its low-power stop mode. When this occurs,

the MAX31782 resets and returns to normal CPU mode operation within 10 clock cycles.

2.6.4 Internal System Resets

There are two possible sources of internal system resets. An internal reset holds the MAX31782 in reset mode for 12

clock cycles.

1) When data BBh is written to the special I2C slave address 34h.

2) When in-system programming is complete and the ROD bit is set to 1.

�������������������������������������������������������������� Maxim Integrated Products 2-13

Revision 0; 8/11

Page 18

MAX31782 User’s Guide

2.7 Clock Generation

The MAX31782 generates its 4MHz instruction clock using an internal oscillator. This oscillator starts up when VDD

exceeds the brownout voltage level, VBO. There is a delay of approximately 1000 clock cycles (t

SU:MOSC

when the oscillator starts and when clocking of the MAX31782 begins. This delay ensures that the clock is stable prior

to beginning normal operation.

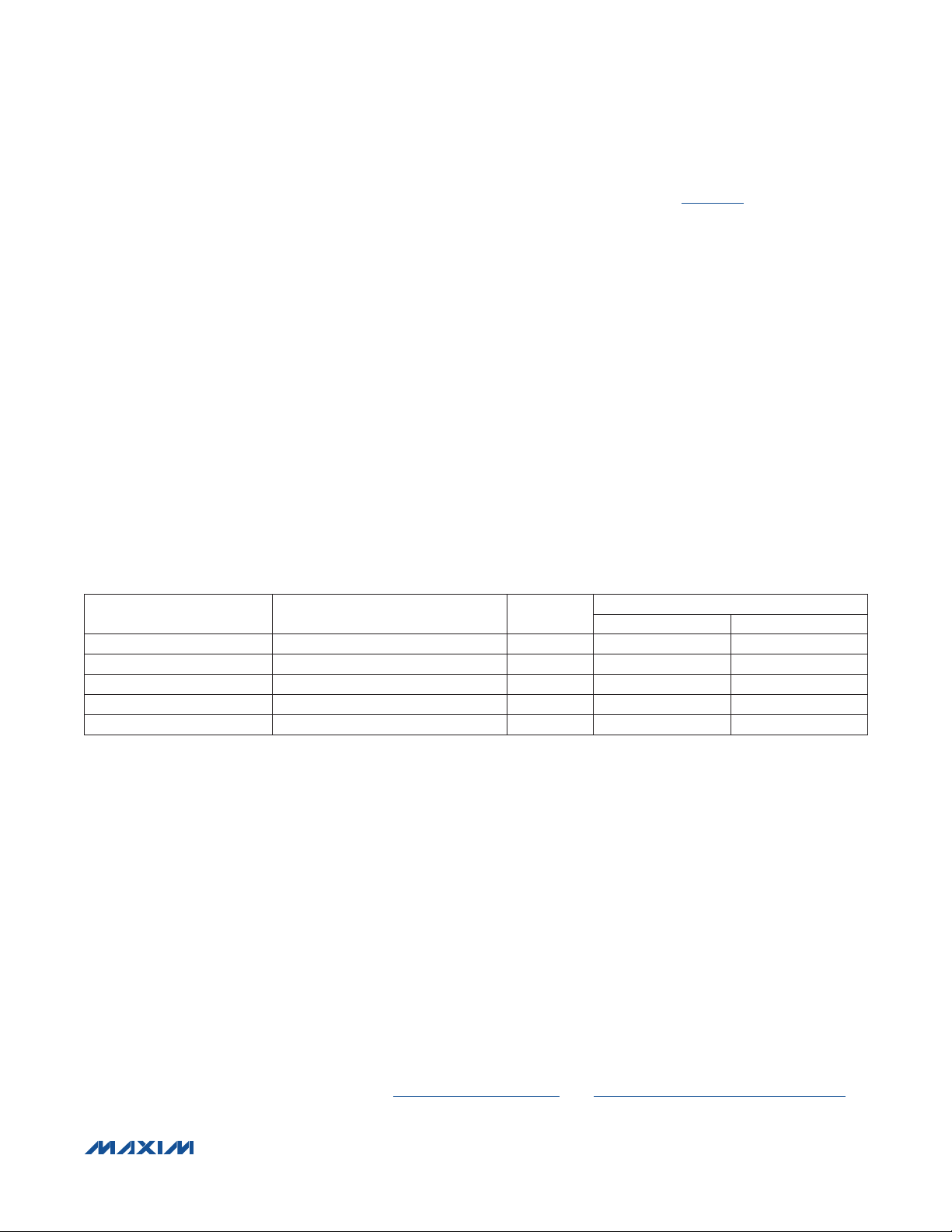

2.8 Power Modes

The MAX31782 has two modes of operation. These two modes of operation are detailed in the state diagram as shown

in Figure 2-6.

1) Normal CPU mode

2) Stop mode

The MAX31782 enters stop mode when the STOP bit in the system clock control register (CKCN) is set. Upon entering

stop mode, the digital core is no longer clocked, thus making the core inactive. In stop mode, the ADC is also disabled

and the Supply Voltage Monitor (SVM) can be disabled. The internal oscillator, brownout detection, and regulators

(REG18 and REG25 pins) remain active during stop mode. Table 2-2 details the state of the MAX31782’s analog and

digital blocks during the different modes of operation.

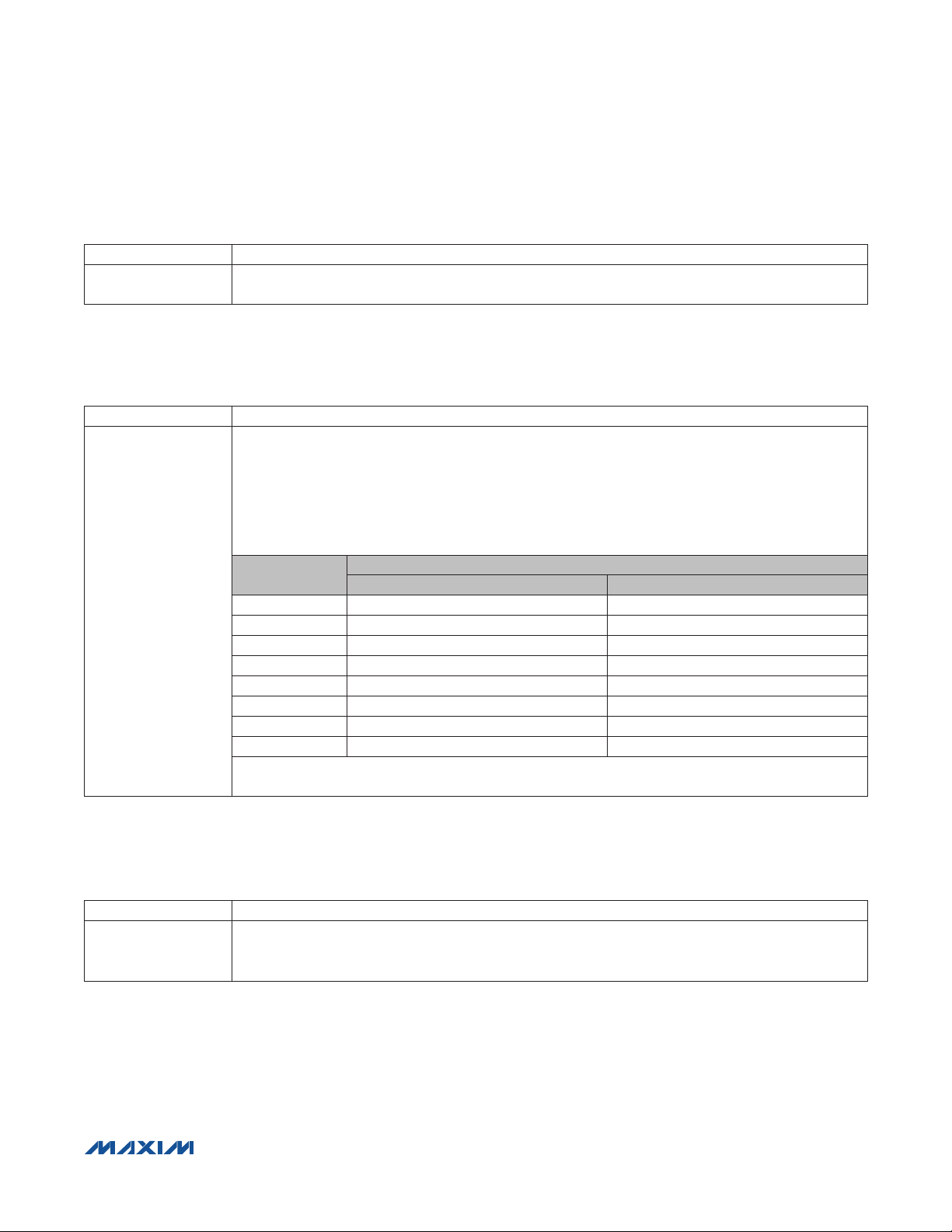

Table 2-2. State of Circuits During Different Modes

CKCN.STOP SVM.SVMEN SVM.SVMSTOP

0 0 X

0 1 X

1 0 X

1 1 0

1 1 1

POWER

MODE

CPU

Mode

CPU

Mode

Stop

Mode

Stop

Mode

Stop

Mode

REGULATORS

CPU

1.8V 2.5V

On On On On On Off On/Off

On On On On On On On/Off

Off On On On On Off Off

Off On On On On Off Off

Off On On On On On Off

INTERNAL

OSCILLATOR

BROWNOUT

DETECTION

MONITOR

SVM

) between

ADC

The MAX31782 exits stop mode when any of the following interrupt conditions occurs:

• GPIO interrupt from Port 6

• I2C START interrupt

• SVM interrupt

• External reset

The interrupt sources listed must be enabled prior to entering stop mode if they are going to be used to bring the

MAX31782 out of stop mode. After receiving one of these interrupts, the MAX31782 exits stop mode and returns to CPU

mode within 10 system clock cycles. If an interrupt causes the system to come out of stop mode, the program execution

starts from the point where stop mode was asserted. However, if an external reset is used to come out of stop mode,

the program execution begins from utility ROM location 8000h.

�������������������������������������������������������������� Maxim Integrated Products 2-14

Revision 0; 8/11

Page 19

MAX31782 User’s Guide

SECTION 3: SYSTEM REGISTER DESCRIPTIONS

This section contains the following information:

3.1 System Register Bit Descriptions. . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.1.1 Accumulator Pointer Register (AP, 8h[0h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.1.2 Accumulator Pointer Control Register (APC, 8h[1h]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-4

3.1.3 Processor Status Flags Register (PSF, 8h[4h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

3.1.4 Interrupt and Control Register (IC, 8h[5h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-5

3.1.5 Interrupt Mask Register (IMR, 8h[6h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.1.6 System Control Register (SC, 8h[8h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-6

3.1.7 Interrupt Identification Register (IIR, 8h[Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.1.8 System Clock Control Register (CKCN, 8h[Eh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-7

3.1.9 Watchdog Control Register (WDCN, 8h[Fh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-8

3.1.10 Accumulator n Register (A[n], 9h[nh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.1.11 Prefix Register (PFX[n], Bh[n]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.1.12 Instruction Pointer Register (IP, Ch[0h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-9

3.1.13 Stack Pointer Register (SP, Dh[1h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.1.14 Interrupt Vector Register (IV, Dh[2h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.1.15 Loop Counter 0 Register (LC[0], Dh[6h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.1.16 Loop Counter 1 Register (LC[1], Dh[7h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.1.17 Frame Pointer Offset Register (OFFS, Eh[3h]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-10

3.1.18 Data Pointer Control Register (DPC, Eh[4h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

3.1.19 General Register (GR, Eh[5h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

3.1.20 General Register Low Byte (GRL, Eh[6h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-11

3.1.21 Frame Pointer Base Register (BP, Eh[7h]). . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.22 General Register Byte-Swapped (GRS, Eh[8h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.23 General Register High Byte (GRH, Eh[9h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.24 General Register Sign Extended Low Byte (GRXL, Eh[Ah]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.25 Frame Pointer Register (FP, Eh[Bh]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.26 Data Pointer 0 Register (DP[0], Fh[3h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-12

3.1.27 Data Pointer 1 Register (DP[1], Fh[7h]) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-13

LIST OF TABLES

Table 3-1. System Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-2

Table 3-2. System Register Bit Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .3-3

��������������������������������������������������������������� Maxim Integrated Products 3-1

Revision 0; 8/11

Page 20

MAX31782 User’s Guide

SECTION 3: SYSTEM REGISTER DESCRIPTIONS

Most MAX31782 functions are controlled by sets of registers. These registers provide a working space for memory operations as well as configuring and addressing peripheral registers on the device. Registers are divided into two major

types: system registers and peripheral registers. The common register set, also known as the system registers, includes

ALU access and control registers, accumulator registers, data pointers, interrupt vectors and control, and stack pointer.

The peripheral registers define additional functionality and the functionality is broken up into discrete modules.

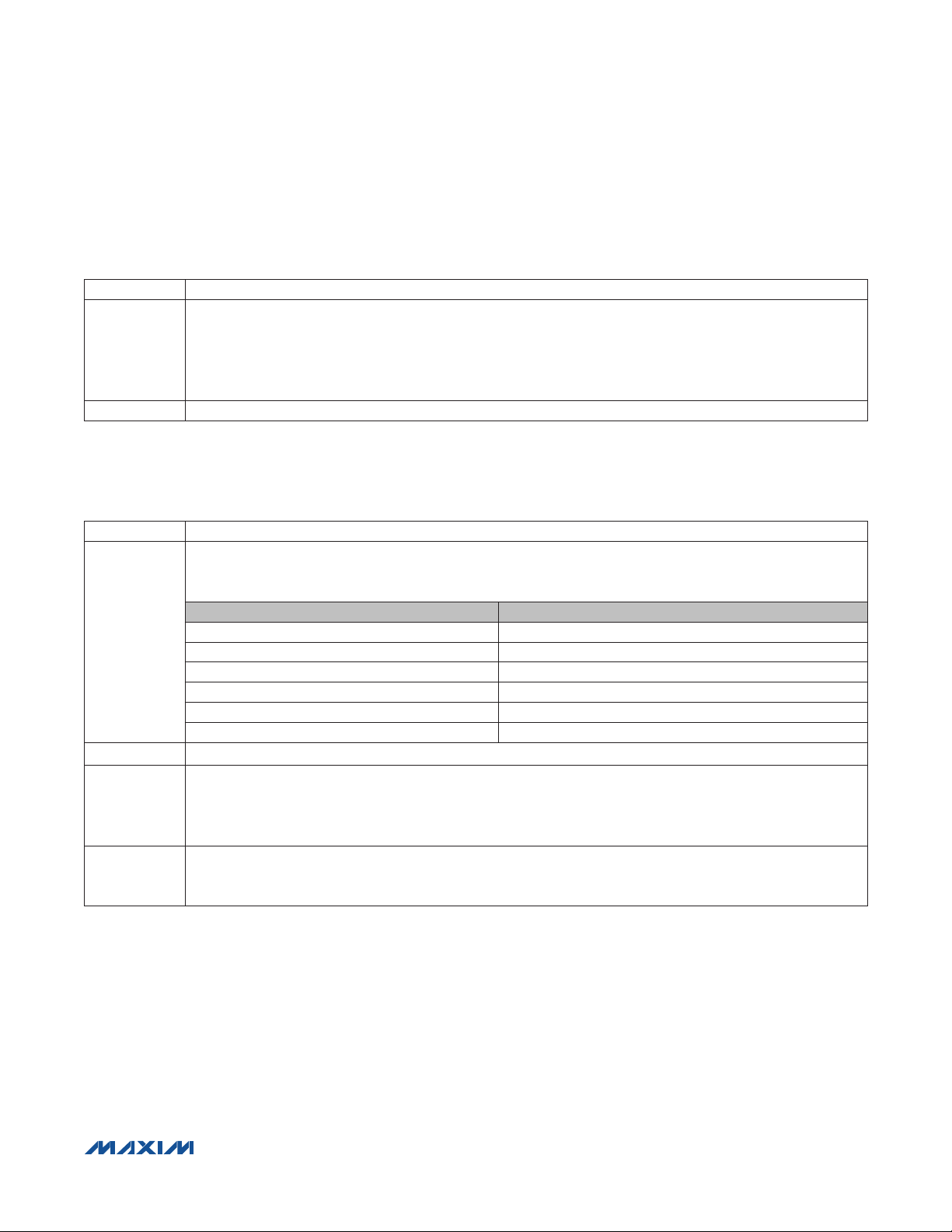

This section describes the MAX31782’s system registers. Table 3-1 shows the MAX31782 system register map.

Table 3-2 explains system register bit functions. This is followed by a detailed bit description.

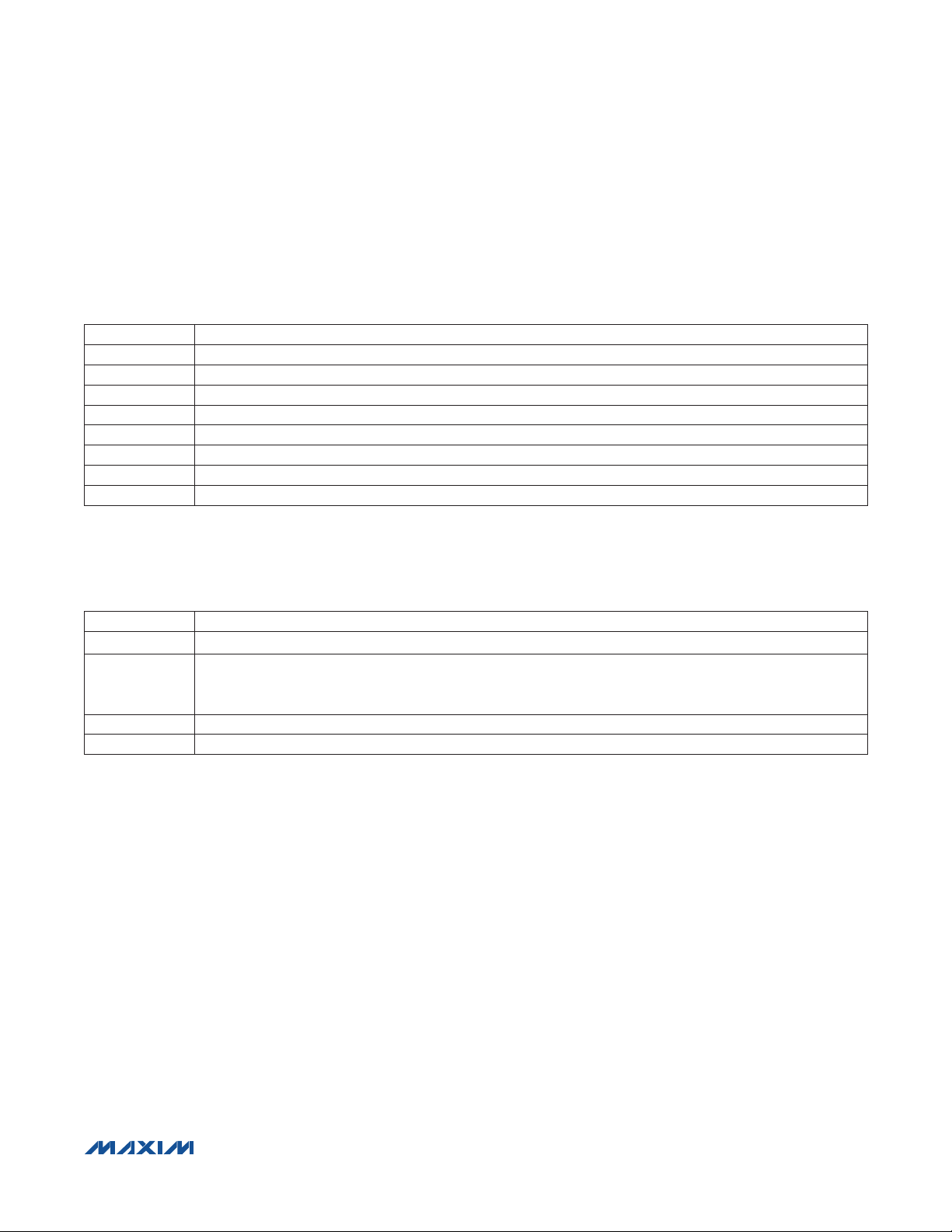

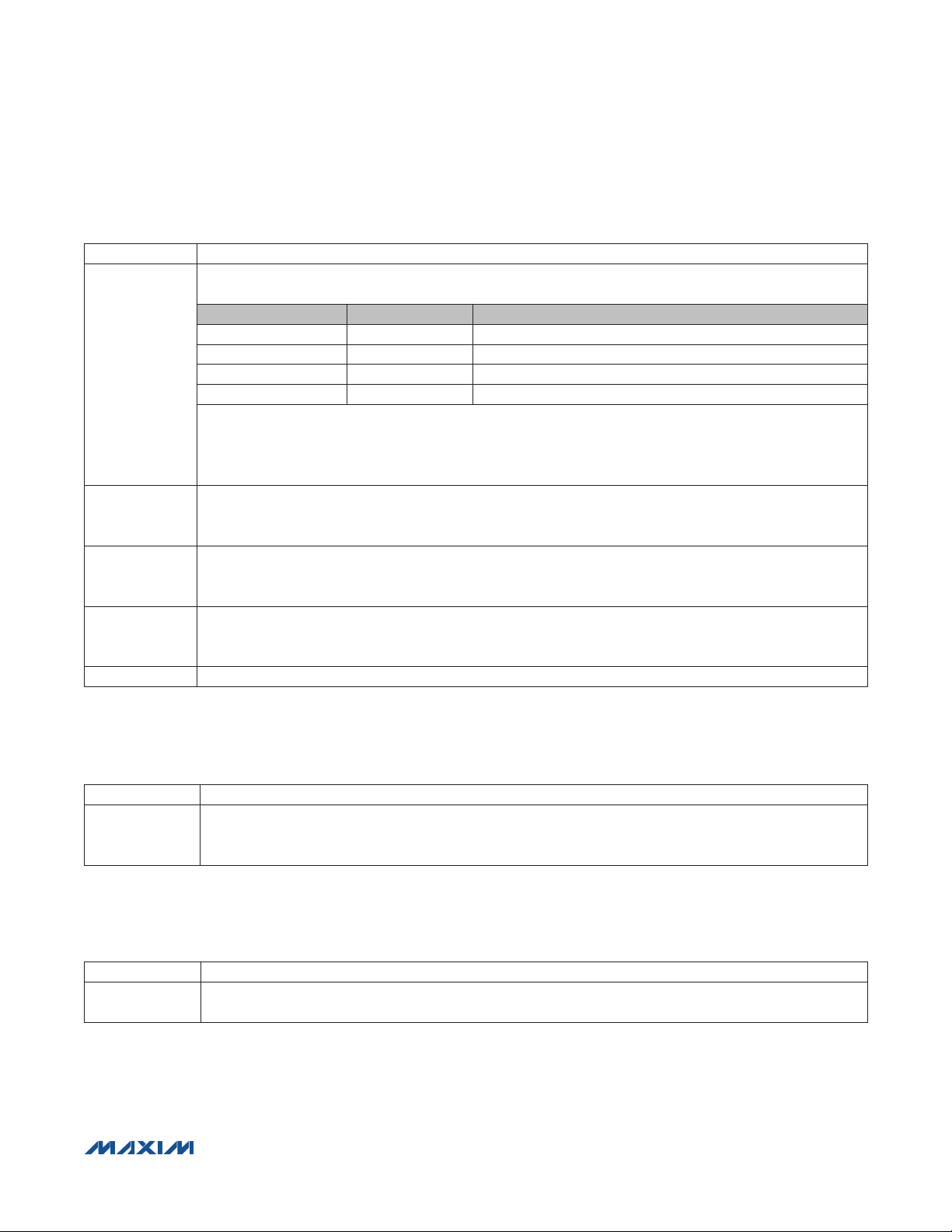

Table 3-1. System Register Map

REGISTER

INDEX

00h AP A[0] PFX[0] IP — — —

01h APC A[1] PFX[1] — SP — —

02h — A[2] PFX[2] — IV — —

03h — A[3] PFX[3] — — OFFS DP[0]

04h PSF A[4] PFX[4] — — DPC —

05h IC A[5] PFX[5] — — GR —

06h IMR A[6] PFX[6] — LC[0] GRL —

07h — A[7] PFX[7] — LC[1] BP DP[1]

08h SC A[8] — — — GRS —

09h — A[9] — — — GRH —

0Ah — A[10] — — — GRXL —

0Bh IIR A[11] — — — FP —

0Ch — A[12] — — — — —

0Dh — A[13] — — — — —

0Eh CKCN A[14] — — — — —

0Fh WDCN A[15] — — — — —

AP (8h) A (9h) PFX (Bh) IP (Ch) SP (Dh) DPC (Eh) DP (Fh)

REGISTER MODULE

��������������������������������������������������������������� Maxim Integrated Products 3-2

Revision 0; 8/11

Page 21

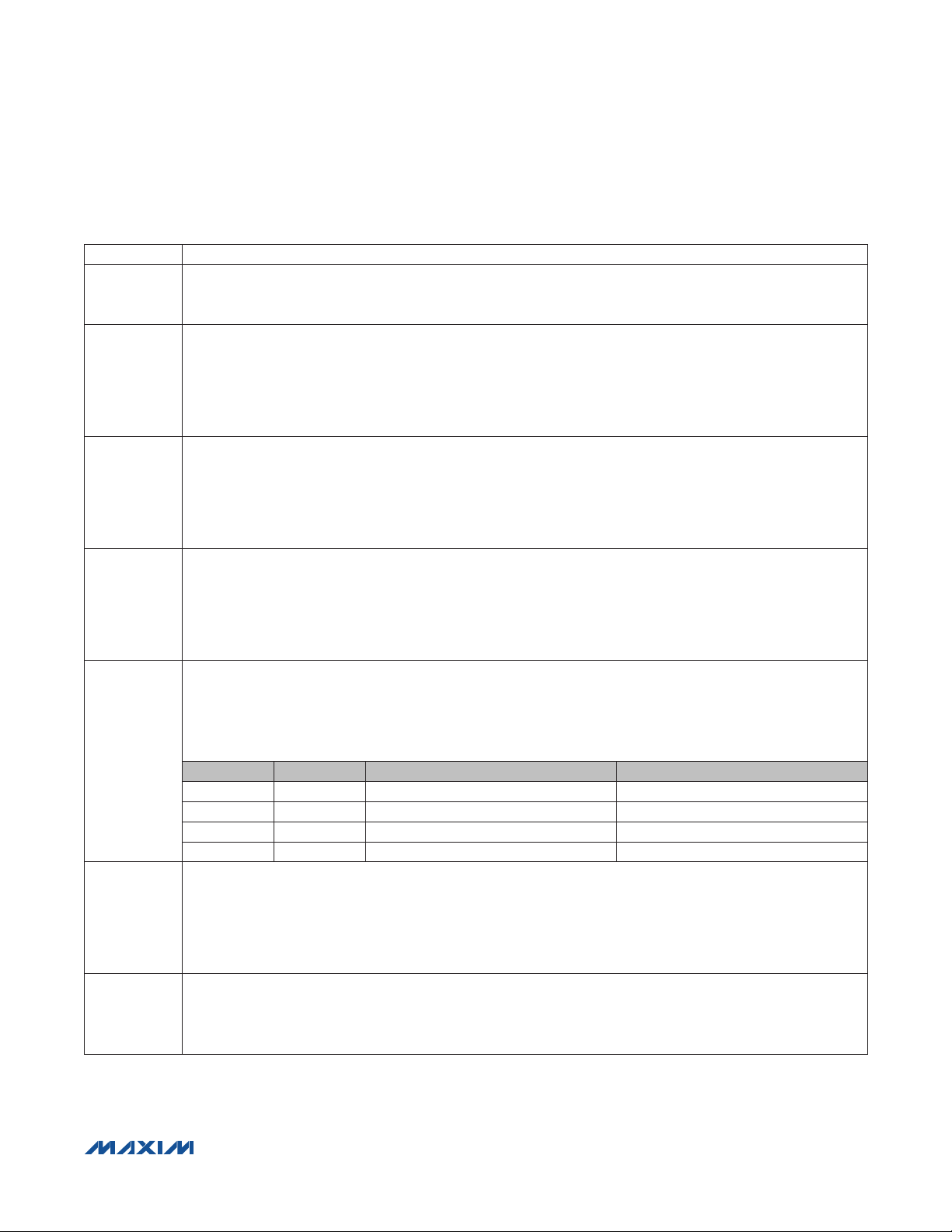

Table 3-2. System Register Bit Functions

MAX31782 User’s Guide

REGISTER

AP — — — — AP (4 bits)

APC CLR IDS — — — MOD2 MOD1 MOD0

PSF Z S — GPF1 GPF0 OV C E

IC — — — — — — INS IGE

IMR IMS — IM5 IM4 IM3 IM2 IM1 IM0

SC TAP — — CDA0 — ROD PWL —

IIR IIS — II5 II4 II3 II2 II1 II0

CKCN — — — STOP — — — —

WDCN POR EWDI WD1 WD0 WDIF WTRF EWT RWT

A[n] (n = 15:0) A[n] (16 bits)

PFX[n] (n = 7:0) PFX[n] (16 bits)

IP IP (16 bits)

SP — — — — — — — — — — — — SP (4 bits)

IV IV (16 bits)

LC[0] LC[0] (16 bits)

LC[1] LC[1] (16 bits)

OFFS OFFS (8 bits)

DPC — — — — — — — — — — — WBS2 WBS1 WBS0 SDPS1 SDPS0

GR GR (16 bits)

GRL GRL (8 bits)

BP BP (16 bits)

GRS GRS (16 bits) = (GRL:GRH)

GRH GRH (8 bits)

GRXL GRXL (16 bits) = (GRL.7, 8 bits): (GRL, 8 bits)

FP FP = BP[OFFS] (16 bits)

DP[0] DP[0] (16 bits)

DP[1] DP[1] (16 bits)

15 14 13 12 11 10 9 8 7 6 5 4 3 2 1 0

BIT

��������������������������������������������������������������� Maxim Integrated Products 3-3

Revision 0; 8/11

Page 22

MAX31782 User’s Guide

3.1 System Register Bit Descriptions

3.1.1 Accumulator Pointer Register (AP, 8h[0h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

Active Accumulator Select. These bits select which of the 16 accumulator registers are used for arithmetic and

logical operations. If the APC register has been set to perform automatic increment/decrement of the active

AP.[3:0]

AP.[7:4] Reserved. All reads return 0.

3.1.2 Accumulator Pointer Control Register (APC, 8h[1h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

APC.[2:0]

(MOD[2:0])

APC.[5:3] Reserved. All reads return 0.

APC.6 (IDS)

accumulator, this setting is automatically changed after each arithmetic or logical operation. If a ‘MOVE AP,

Acc’ instruction is executed, any enabled AP inc/dec/modulo control takes precedence over the transfer of Acc

data into AP.

Accumulator Pointer Auto Increment/Decrement Modulus. If these bits are set to a nonzero value, the accumulator pointer (AP[3:0]) is automatically incremented or decremented following each arithmetic or logical operation.

The mode for the auto increment/decrement is determined as follows:

MOD[2:0] AUTO INCREMENT/DECREMENT MODE

000 No auto increment/decrement (default)

001 Increment/decrement AP[0] modulo 2

010 Increment/decrement AP[1:0] modulo 4

011 Increment/decrement AP[2:0] modulo 8

100 Increment/decrement AP modulo 16

101 to 111 Reserved (modulo 16 when set)

Increment/Decrement Select. If this bit is set to 0, the accumulator pointer AP is incremented following each

arithmetic or logical operation according to MOD[2:0]. If this bit is set to 1, the accumulator pointer AP is decremented following each arithmetic or logical operation according to MOD[2:0]. If MOD[2:0] is set to 000, the setting of this bit is ignored.

APC.7 (CLR)

AP Clear. Writing this bit to 1 clears the accumulator pointer AP to 0. Once set, this bit is automatically reset to 0

by hardware. If a ‘MOVE APC, Acc’ instruction is executed requesting that AP be set to 0 (i.e., CLR = 1), the AP

clear function overrides any enabled inc/dec/modulo control. All reads from this bit return 0.

��������������������������������������������������������������� Maxim Integrated Products 3-4

Revision 0; 8/11

Page 23

MAX31782 User’s Guide

3.1.3 Processor Status Flags Register (PSF, 8h[4h])

Initialization: This register is cleared to 80h on all forms of reset.

Access: Bit 7 (Z), bit 6 (S), and bit 2 (OV) are read-only. Bits 4 and 3 (GPF1, GPF0), bit 1 (C), and bit 0 (E) are unrestricted read/write.

BIT FUNCTION

PSF.0 (E)

PSF.1 (C)

PSF.2 (OV)

PSF.3 (GPF0) General-Purpose Flag 0

PSF.4 (GPF1) General-Purpose Flag 1. These general-purpose flag bits are provided for user software control.

PSF.5 Reserved. All reads return 0.

PSF.6 (S) Sign Flag. This bit flag mirrors the current value of the high bit of the active accumulator (Acc.15).

PSF.7 (Z)

Equals Flag. This bit flag is set to 1 whenever a compare operation (CMP) returns an equal result. If a CMP

operation returns not equal, this bit is cleared.

Carry Flag. This bit flag is set to 1 whenever an add or subtract operation (ADD, ADDC, SUB, SUBB) returns a

carry or borrow. This bit flag is cleared to 0 whenever an add or subtract operation does not return a carry or

borrow. Many other instructions potentially affect the carry bit.

Overflow Flag. This flag is set to 1 if there is a carry out of bit 14 but not out of bit 15, or a carry out of bit 15 but

not out of bit 14 from the last arithmetic operation, otherwise, the OV flag remains as 0. OV indicates a negative

number resulted as the sum of two positive operands, or a positive sum resulted from two negative operands.

Zero Flag. The value of this bit flag equals 1 whenever the active accumulator is equal to zero, and it equals 0

otherwise.

3.1.4 Interrupt and Control Register (IC, 8h[5h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

IC.0 (IGE)

IC.1 (INS)

IC.[7:2] Reserved. All reads return 0.

Interrupt Global Enable. This bit enables the interrupt handler if set to 1. No interrupt to the CPU is allowed if

this bit is cleared to 0.

Interrupt In Service. The INS is set by the interrupt handler automatically when an interrupt is acknowledged.

No further interrupts occur as long as the INS bit remains set. The interrupt service routine can clear the INS bit

to allow interrupt nesting. Otherwise, the INS bit is cleared automatically by the interrupt handler upon execution of an RETI/POPI instruction.

��������������������������������������������������������������� Maxim Integrated Products 3-5

Revision 0; 8/11

Page 24

MAX31782 User’s Guide

3.1.5 Interrupt Mask Register (IMR, 8h[6h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted read/write access.

The first six bits in this register are interrupt mask bits for modules 0 to 5, one bit per module. The eighth bit, IMS, serves as a

mask for any system module interrupt sources. Setting a mask bit allows the enabled interrupt sources for the associated module

or system (for the case of IMS) to generate interrupt requests. Clearing the mask bit effectively disables all interrupt sources associated with that specific module or all system interrupt sources (for the case of IMS). The interrupt mask register is intended to

facilitate user-definable interrupt prioritization.

BIT FUNCTION

IMR.0 (IM0) Interrupt Mask for Register Module 0

IMR.1 (IM1) Interrupt Mask for Register Module 1

IMR.2 (IM2) Interrupt Mask for Register Module 2

IMR.3 (IM3) Interrupt Mask for Register Module 3

IMR.4 (IM4) Interrupt Mask for Register Module 4

IMR.5 (IM5) Interrupt Mask for Register Module 5

IMR.6 Reserved. Reads return 0.

IMR.7 (IMS) Interrupt Mask for System Modules

3.1.6 System Control Register (SC, 8h[8h])

Initialization: This register is reset to 100000s0b on all reset. Bit 1 (PWL) is set to 1 on a power-on reset only.

Access: Unrestricted read/write access.

BIT FUNCTION

SC.0 Reserved. All reads return 0.

Password Lock. This bit defaults to 1 on a power-on reset. When this bit is 1, it requires a 32-byte password to

SC.1 (PWL)

SC.2 (ROD)

SC.3 Reserved. All reads return 0.

SC.4 (CDA0)

be matched with the password in the program space before allowing access to the ROM loader’s utilities for

read/write of program memory and debug functions. Clearing this bit to 0 disables the password protection to

the ROM loader.

ROM Operation Done. This bit is used to signify completion of a ROM operation sequence to the control units.

This allows the debug engine to determine the status of a ROM sequence. Setting this bit to logic 1 causes an

internal system reset if the JTAG_SPE bit is also set. Setting the ROD bit clears the JTAG_SPE bit if it is set and

the ROD bit is automatically cleared by hardware once the control unit acknowledges the done indication.

Code Data Access Bit 0. The CDA bit is used to logically map physical program memory page to the data

space for read/write access:

CDA0 BYTE MODE ACTIVE PAGE WORD MODE ACTIVE PAGE

0 P0 P0 and P1

1 P1 P0 and P1

The logical addresses depend on which memory segment is executing. Note that CDA1 (normally at bit position SC.5) is not implemented since the maximum flash memory size is 64KB or 32KWords.

SC.[6:5] Reserved. All reads return 0.

Test Access (JTAG) Port Enable. This bit controls whether the test access port special-function pins are

SC.7 (TAP)

enabled. The TAP defaults to being enabled. Clearing this bit to 0 disables the TAP special-function pins on the

JTAG pins.

��������������������������������������������������������������� Maxim Integrated Products 3-6

Revision 0; 8/11

Page 25

MAX31782 User’s Guide

3.1.7 Interrupt Identification Register (IIR, 8h[Bh])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Read-only.

The first six bits in this register indicate interrupts pending in modules 0 to 5, one bit per module. The eighth bit, IIS, indicates a

pending system interrupt, such as from the watchdog timer. The interrupt pending flags are set only for enabled interrupt sources

waiting for service. The interrupt pending flag is cleared when the pending interrupt sources within that module are disabled or

when the interrupt flags are cleared by software.

BIT FUNCTION

IIR.0 (II0) Interrupt Identifier Flag for Register Module 0

IIR.1 (II1) Interrupt Identifier Flag for Register Module 1

IIR.2 (II2) Interrupt Identifier Flag for Register Module 2

IIR.3 (II3) Interrupt Identifier Flag for Register Module 3

IIR.4 (II4) Interrupt Identifier Flag for Register Module 4

IIR.5 (II5) Interrupt Identifier Flag for Register Module 5

IIR.6 Reserved. Reads return 0.

IIR.7 (IIS) Interrupt Identifier Flag for System Modules

3.1.8 System Clock Control Register (CKCN, 8h[Eh])

Initialization: This register is cleared to 10h on all forms of reset.

Access: Unrestricted read/write access.

BIT FUNCTION

CKCN.[3:0] Reserved. All reads return 0.

Stop Mode Select. Setting this bit to 1 stops program execution and commences low-power operation. This

CKCN.4 (STOP)

CKCN.[6:5] Reserved. All reads return 0.

CKCN.7 Reserved. All reads return 1.

bit is cleared by a reset or any of the enabled external interrupts. Setting and resetting the STOP bit does not

change the system clock source and its divide ratio.

��������������������������������������������������������������� Maxim Integrated Products 3-7

Revision 0; 8/11

Page 26

MAX31782 User’s Guide

3.1.9 Watchdog Control Register (WDCN, 8h[Fh])

Initialization: Bits 5, 4, 3, and 0 are cleared to 0 on all forms of reset; for others, see individual bit descriptions.

Access: Unrestricted direct read/write access.

BIT FUNCTION

WDCN.0

(RWT)

WDCN.1

(EWT)

WDCN.2

(WTRF)

WDCN.3

(WDIF)

Reset Watchdog Timer. Setting this bit to 1 resets the watchdog timer count. If watchdog interrupt and/or reset

modes are enabled, the software must set this bit to 1 before the watchdog timer elapses to prevent an interrupt

or reset from occurring. This bit always returns 0 when read.

Enable Watchdog Timer Reset. If this bit is set to 1 when the watchdog timer elapses, the watchdog resets the

processor 512 system clock cycles later unless action is taken to disable the reset event. Clearing this bit to 0

prevents a watchdog reset from occurring but does not stop the watchdog timer or prevent watchdog interrupts

from occurring if EWDI = 1. If EWT = 0 and EWDI = 0, the watchdog timer is stopped. If the watchdog timer

is stopped (EWT = 0 and EWDI = 0), setting the EWT bit resets the watchdog interval and reset counter, and

enables the watchdog timer. This bit is cleared on power-on reset and is unaffected by other forms of reset.

Watchdog Timer Reset Flag. This bit is set to 1 when the watchdog resets the processor. Software can check this

bit following a reset to determine if the watchdog was the source of the reset. Setting this bit to 1 in software does

not cause a watchdog reset. This bit is cleared by power-on reset only and is unaffected by other forms of reset.

It should also be cleared by software following any reset so that the source of the next reset can be correctly

determined by software. This bit is only set to 1 when a watchdog reset actually occurs, so if EWT is cleared to 0

when the watchdog timer elapses, this bit is not set.

Watchdog Interrupt Flag. This bit is set to 1 when the watchdog timer interval has elapsed or can be set to 1 by

user software. When WDIF = 1, an interrupt request occurs if the watchdog interrupt has been enabled (EWDI =

1) and not otherwise masked, or prevented by an interrupt already in service (i.e., IGE = 1, IMS = 1, and INS = 0

must be true for the interrupt to occur). This bit should be cleared by software before exiting the interrupt service

routine to avoid repeated interrupts. Furthermore, if the watchdog reset has been enabled (EWT = 1), a reset is

scheduled to occur 512 system clock cycles following setting of the WDIF bit.

WDCN.4

(WD0);

WDCN.5

(WD1)

WDCN.6

(EWDI)

WDCN.7

(POR)

Watchdog Timer Mode Select Bit 0; Watchdog Timer Mode Select Bit 1. These bits determine the watchdog interval or the length of time between resetting of watchdog timer and the watchdog generated interrupt in terms of

system clocks. Modifying the watchdog interval through the WD[1:0] bits automatically resets the watchdog timer

unless the 512 system clock reset counter is already in progress, in which case, changing the WD[1:0] bits does

not affect the watchdog timer or reset counter.

WD1 WD0 CLOCKS UNTIL INTERRUPT CLOCKS UNTIL RESET

0 0 2

0 1 2

1 0 2

1 1 2

Watchdog Interrupt Enable. If this bit is set to 1, an interrupt request can be generated when the WDIF bit is set

to 1 by any means. If this bit is cleared to 0, no interrupt occurs when WDIF is set to 1; however, it does not stop

the watchdog timer or prevent watchdog resets from occurring if EWT = 1. If EWT = 0 and EWDI = 0, the watchdog timer is stopped. If the watchdog timer is stopped (EWT = 0 and EWDI = 0), setting the EWDI bit resets the

watchdog interval and reset counter, and enables the watchdog timer. This bit is cleared to 0 by power-on reset

and is unaffected by other forms of reset.

Power-On-Reset Flag. This bit is set to 1 whenever a power-on/brownout reset occurs. It is unaffected by other

forms of reset. This bit can be checked by software following a reset to determine if a power-on/brownout reset

occurred. It should always be cleared by software following a reset to ensure that the sources of following resets

can be determined correctly.

12

15

18

21

212 + 512

215 + 512

218 + 512

221 + 512

��������������������������������������������������������������� Maxim Integrated Products 3-8

Revision 0; 8/11

Page 27

MAX31782 User’s Guide

3.1.10 Accumulator n Register (A[n], 9h[nh])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

A[n].[15:0]

3.1.11 Prefix Register (PFX[n], Bh[n])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

PFX[n].[15:0]

This register acts as the accumulator for all ALU arithmetic and logical operations when selected by the

accumulator pointer (AP). It can also be used as a general-purpose working register.

The Prefix register provides a means of supplying an additional 8 bits of high-order data for use by the

succeeding instruction as well as providing additional indexing capabilities. This register only holds any

data written to it for one execution cycle, after which it reverts to 0000h. Although this is a 16-bit register,

only the lower 8 bits are actually used for prefixing purposes by the next instruction. Writing to or reading

from any index in the prefix module selects the same 16-bit register. However, when the PFX register is

written, the index n used for the PFX[n] write also determines the high-order bits for the register source

and destination specified in the following instruction.

WRITE TO

PFX[0] 0h to Fh 0h to 7h

PFX[1] 10h to 1Fh 0h to 7h

PFX[2] 0h to Fh 8h to Fh

PFX[3] 10h to 1Fh 8h to Fh

PFX[4] 0h to Fh 10h to 17h

PFX[5] 10h to 1Fh 10h to 17h

PFX[6] 0h to Fh 18h to 1Fh

PFX[7] 10h to 1Fh 18h to 1Fh

The index selection reverts to 0 (default mode allowing selection of registers 0h to 7h for destinations)

after one cycle in the same manner as the contents of the PFX register.

SOURCE REGISTER RANGE DESTINATION REGISTER RANGE

SOURCE, DESTINATION INDEX SELECTION

3.1.12 Instruction Pointer Register (IP, Ch[0h])

Initialization: This register is cleared to 8000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

This register contains the address of the next instruction to be executed and is automatically incremented

IP.[15:0]

by 1 after each program fetch. Writing an address value to this register caused program flow to jump to

that address. Reading from this register does not affect program flow.

��������������������������������������������������������������� Maxim Integrated Products 3-9

Revision 0; 8/11

Page 28

MAX31782 User’s Guide

3.1.13 Stack Pointer Register (SP, Dh[1h])

Initialization: This register is cleared to 000Fh on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

SP.[3:0]

SP.[15:4] Reserved. All reads return 0.

3.1.14 Interrupt Vector Register (IV, Dh[2h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

IV.[15:0]

3.1.15 Loop Counter 0 Register (LC[0], Dh[6h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

LC[0].[15:0]

These four bits indicate the current top of the hardware stack, from 0h to Fh. This pointer is incremented

after a value is pushed on the stack and decremented before a value is popped from the stack.

This register contains the address of the interrupt service routine. The interrupt handler generates a CALL

to this address whenever an interrupt is acknowledged.

This register is used as the loop counter for the DJNZ LC[0], src operation. This operation decrements

LC[0] by one and then jumps to the address specified in the instruction by src.

3.1.16 Loop Counter 1 Register (LC[1], Dh[7h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

LC[1].[15:0]

This register is used as the loop counter for the DJNZ LC[1], src operation. This operation decrements

LC[1] by one and then jumps to the address specified in the instruction by src.

3.1.17 Frame Pointer Offset Register (OFFS, Eh[3h])

Initialization: This register is cleared to 00h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

This 8-bit register provides the Frame Pointer (FP) offset from the base pointer (BP). The Frame Pointer is

formed by unsigned addition of Frame Pointer Base register (BP) and Frame Pointer Offset register (OFFS).

OFFS.[7:0]

The contents of this register can be postincremented or postdecremented when using the Frame Pointer

for read operations and can be preincremented or predecremented when using the Frame Pointer for write

operations. A carry out or borrow resulting from an increment/decrement operation has no affect on the

Frame Pointer Base register (BP).

�������������������������������������������������������������� Maxim Integrated Products 3-10

Revision 0; 8/11

Page 29

MAX31782 User’s Guide

3.1.18 Data Pointer Control Register (DPC, Eh[4h])

Initialization: This register is cleared to 001Ch on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION

Source Data Pointer Select Bits 1:0. These bits select one of the three data pointers as the active source pointer for the load operation. A new data pointer must be selected before being used to read data memory:

SDPS1 SDPS0 SOURCE POINTER SELECTION

0 0 DP[0]

DPC.[1:0]

(SDPS[1:0])

These bits default to 00b but do not activate DP[0] as an active source pointer until the SDPS bits are explicitly

cleared to 00b or the DP[0] register is written by an instruction. Also, modifying the register contents of a data/

frame pointer register (DP[0], DP[1], BP, or OFFS) changes the setting of the SDPS bits to reflect the active

source pointer selection.

Word/Byte Select 0. This bit selects access mode for DP[0]. When WBS0 is set to logic 1, the DP[0] is oper-

DPC.2 (WBS0)

DPC.3 (WBS1)

DPC.4 (WBS2)

DPC.[15:5] Reserved. Read returns 0.

ated in word mode for data memory access; when WBS0 is cleared to logic 0, DP[0] is operated in byte mode

for data memory access.

Word/Byte Select 1. This bit selects access mode for DP[1]. When WBS1 is set to logic 1, the DP[1] is operated in word mode for data memory access; when WBS1 is cleared to logic 0, DP[1] is operated in byte mode

for data memory access.

Word/Byte Select 2. This bit selects access mode for BP[OFFS]. When WBS2 is set to logic 1, the BP[OFFS]

is operated in word mode for data memory access; when WBS2 is cleared to logic 0, BP[OFFS] is operated in

byte mode for data memory access.

0 1 DP[1]

1 0 FP (BP[OFFS])

1 1 Reserved (select FP if set)

3.1.19 General Register (GR, Eh[5h])

Initialization: This register is cleared to 0000h on all forms of reset.

Access: Unrestricted direct read/write access.

BIT FUNCTION