For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800

_______________General Description

The MAX146/MAX147 12-bit data-acquisition systems

combine an 8-channel multiplexer, high-bandwidth

track/hold, and serial interface with high conversion

speed and low power consumption. The MAX146 operates from a single +2.7V to +3.6V supply; the MAX147

operates from a single +2.7V to +5.25V supply. Both

devices’ analog inputs are software configurable for

unipolar/bipolar and single-ended/differential operation.

The 4-wire serial interface connects directly to SPI™/

QSPI™ and Microwire™ devices without external logic. A

serial strobe output allows direct connection to TMS320family digital signal processors. The MAX146/MAX147

use either the internal clock or an external serial-interface

clock to perform successive-approximation analog-todigital conversions.

The MAX146 has an internal 2.5V reference, while the

MAX147 requires an external reference. Both parts have

a reference-buffer amplifier with a ±1.5% voltageadjustment range.

These devices provide a hard-wired SHDN pin and a

software-selectable power-down, and can be programmed to automatically shut down at the end of a conversion. Accessing the serial interface automatically

powers up the MAX146/MAX147, and the quick turn-on

time allows them to be shut down between all conversions. This technique can cut supply current to under

60µA at reduced sampling rates.

The MAX146/MAX147 are available in 20-pin DIP and

SSOP packages.

For 4-channel versions of these devices, see the

MAX1246/MAX1247 data sheet.

________________________Applications

Portable Data Logging Data Acquisition

Medical Instruments Battery-Powered Instruments

Pen Digitizers Process Control

____________________________Features

♦ 8-Channel Single-Ended or 4-Channel

Differential Inputs

♦ Single-Supply Operation:

+2.7V to +3.6V (MAX146)

+2.7V to +5.25V (MAX147)

♦ Internal 2.5V Reference (MAX146)

♦ Low Power: 1.2mA (133ksps, 3V supply)

54µA (1ksps, 3V supply)

1µA (power-down mode)

♦ SPI/QSPI/Microwire/TMS320-Compatible

4-Wire Serial Interface

♦ Software-Configurable Unipolar or Bipolar Inputs

♦ 20-Pin DIP/SSOP Packages

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

________________________________________________________________

Maxim Integrated Products

1

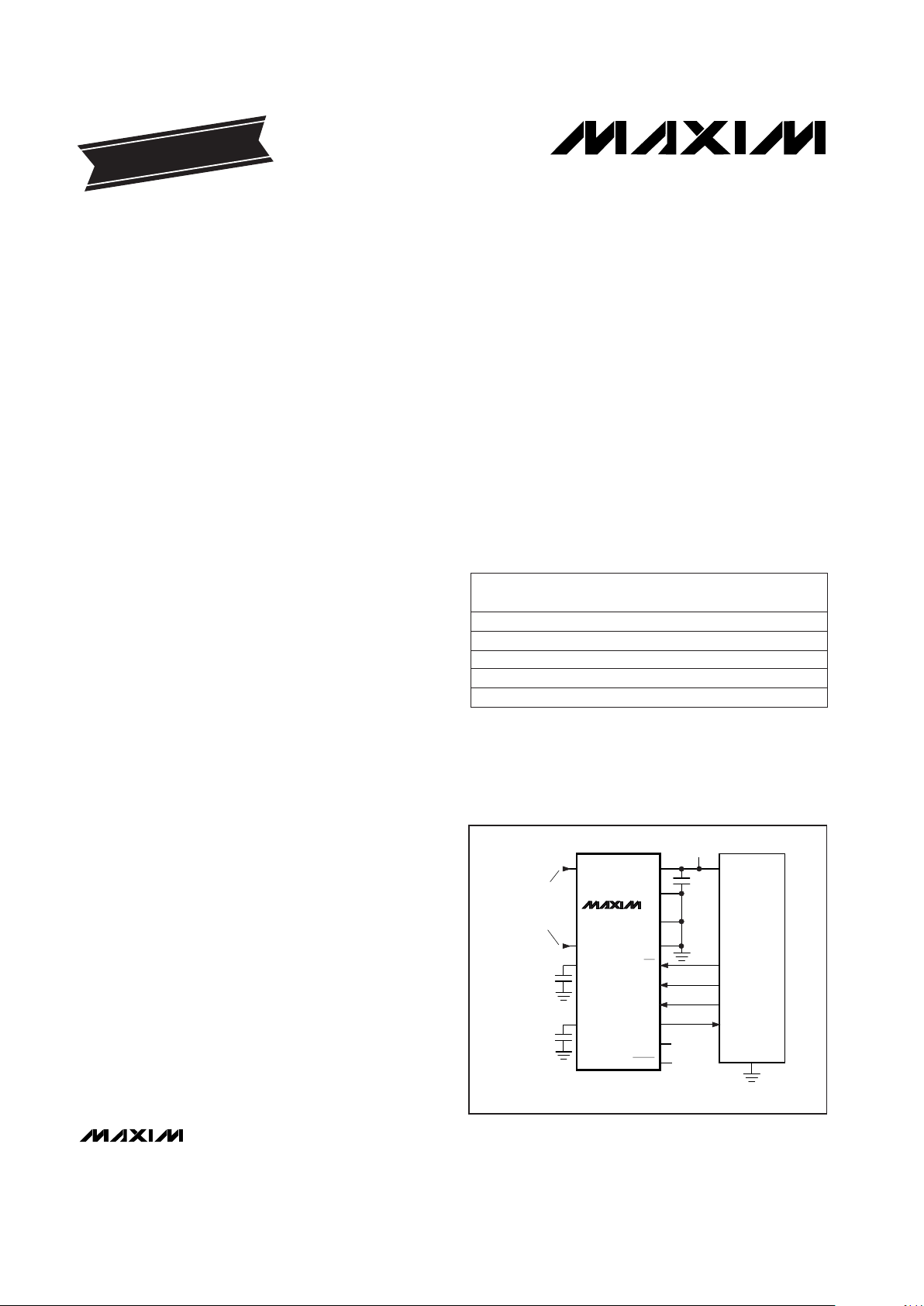

V

DD

I/O

SCK (SK)

MOSI (SO)

MISO (SI)

V

SS

SHDN

SSTRB

DOUT

DIN

SCLK

CS

COM

AGND

DGND

V

DD

CH7

4.7µF

0.1µF

CH0

0V TO

+2.5V

ANALOG

INPUTS

MAX146

CPU

+3V

VREF

0.047µF

REFADJ

__________Typical Operating Circuit

19-0465; Rev 1; 6/97

PART

†

MAX146ACPP

MAX146BCPP

MAX146ACAP 0°C to +70°C

0°C to +70°C

0°C to +70°C

TEMP. RANGE PIN-PACKAGE

20 Plastic DIP

20 Plastic DIP

20 SSOP

EVALUATION KIT

AVAILABLE

______________Ordering Information

Ordering Information continued at end of data sheet.

†

Contact factory for availability of alternate surface-mount

packages.

*Dice are specified at TA= +25°C, DC parameters only.

MAX146BCAP 0°C to +70°C 20 SSOP

INL

(LSB)

±1/2

±1

±1/2

±1

SPI and QSPI are registered trademarks of Motorola, Inc.

Microwire is a registered trademark of National Semiconductor Corp.

Pin Configuration appears at end of data sheet.

MAX146BC/D 0°C to +70°C Dice* ±1

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

2 _______________________________________________________________________________________

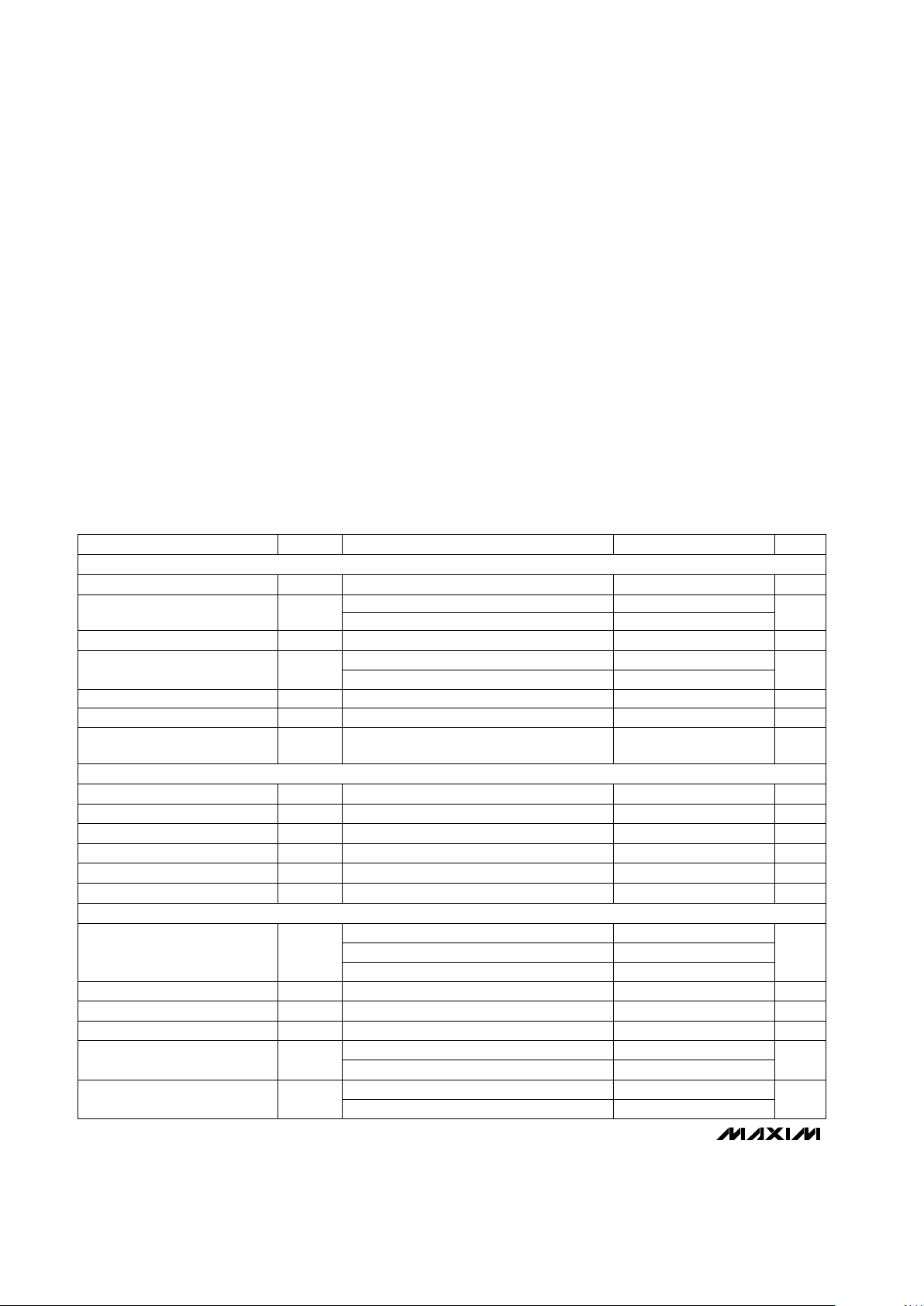

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VDD= +2.7V to +3.6V (MAX146); VDD= +2.7V to +5.25V (MAX147); COM = 0V; f

SCLK

= 2.0MHz; external clock (50% duty cycle); 15

clocks/conversion cycle (133ksps); MAX146—4.7µF capacitor at VREF pin; MAX147—external reference, VREF = 2.500 V applied to

VREF pin; T

A

= T

MIN

to T

MAX

; unless otherwise noted.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

VDDto AGND, DGND................................................. -0.3V to 6V

AGND to DGND...................................................... -0.3V to 0.3V

CH0–CH7, COM to AGND, DGND............ -0.3V to (V

DD

+ 0.3V)

VREF, REFADJ to AGND........................... -0.3V to (V

DD

+ 0.3V)

Digital Inputs to DGND.............................................. -0.3V to 6V

Digital Outputs to DGND........................... -0.3V to (V

DD

+ 0.3V)

Digital Output Sink Current.................................................25mA

Continuous Power Dissipation (T

A

= +70°C)

Plastic DIP (derate 11.11mW/°C above +70°C) ......... 889mW

SSOP (derate 8.00mW/°C above +70°C) ................... 640mW

CERDIP (derate 11.11mW/°C above +70°C).............. 889mW

Operating Temperature Ranges

MAX146_C_P/MAX147_C_P.............................. 0°C to +70°C

MAX146_E_P/MAX147_E_P............................ -40°C to +85°C

MAX146_MJP/MAX147_MJP........................ -55°C to +125°C

Storage Temperature Range............................ -60°C to +150°C

Lead Temperature (soldering, 10sec)............................ +300°C

µs1.5t

ACQ

Differential Nonlinearity

Track/Hold Acquisition Time

ns30Aperture Delay

6

µs

35 65

t

CONV

Conversion Time (Note 5)

5.5 7.5

ps

MHz1.0Full-Power Bandwidth

MHz2.25Small-Signal Bandwidth

dB-85Channel-to-Channel Crosstalk

dB80 90SFDRSpurious-Free Dynamic Range

dB-88 -80THDTotal Harmonic Distortion

dB70 73SINADSignal-to-Noise + Distortion Ratio

LSB±0.25

Channel-to-Channel Offset

Matching

ppm/°C±0.25Gain Temperature Coefficient

±0.5

<50

Bits12Resolution

LSBGain Error (Note 3) ±0.5 ±4

Aperture Jitter

Offset Error

LSB

±1.0

INLRelative Accuracy (Note 2)

LSB±1DNL

±0.5 ±3

LSB

±0.5 ±4

UNITSMIN TYP MAXSYMBOLPARAMETER

External clock = 2MHz, 12 clocks/conversion

Internal clock, SHDN = V

DD

Internal clock, SHDN = FLOAT

MAX14_A

-3dB rolloff

65kHz, 2.500V

p-p

(Note 4)

Up to the 5th harmonic

MAX14_B

No missing codes over temperature

MAX14_A

MAX14_B

CONDITIONS

1.8

SHDN = FLOAT

MHz

0.225

Internal Clock Frequency

SHDN = V

DD

0.1 2.0

MHz

0 2.0

External Clock Frequency

Data transfer only

DC ACCURACY (Note 1)

DYNAMIC SPECIFICATIONS (10kHz sine-wave input, 0V to 2.500Vp-p, 133ksps, 2.0MHz external clock, bipolar input mode)

CONVERSION RATE

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

_______________________________________________________________________________________ 3

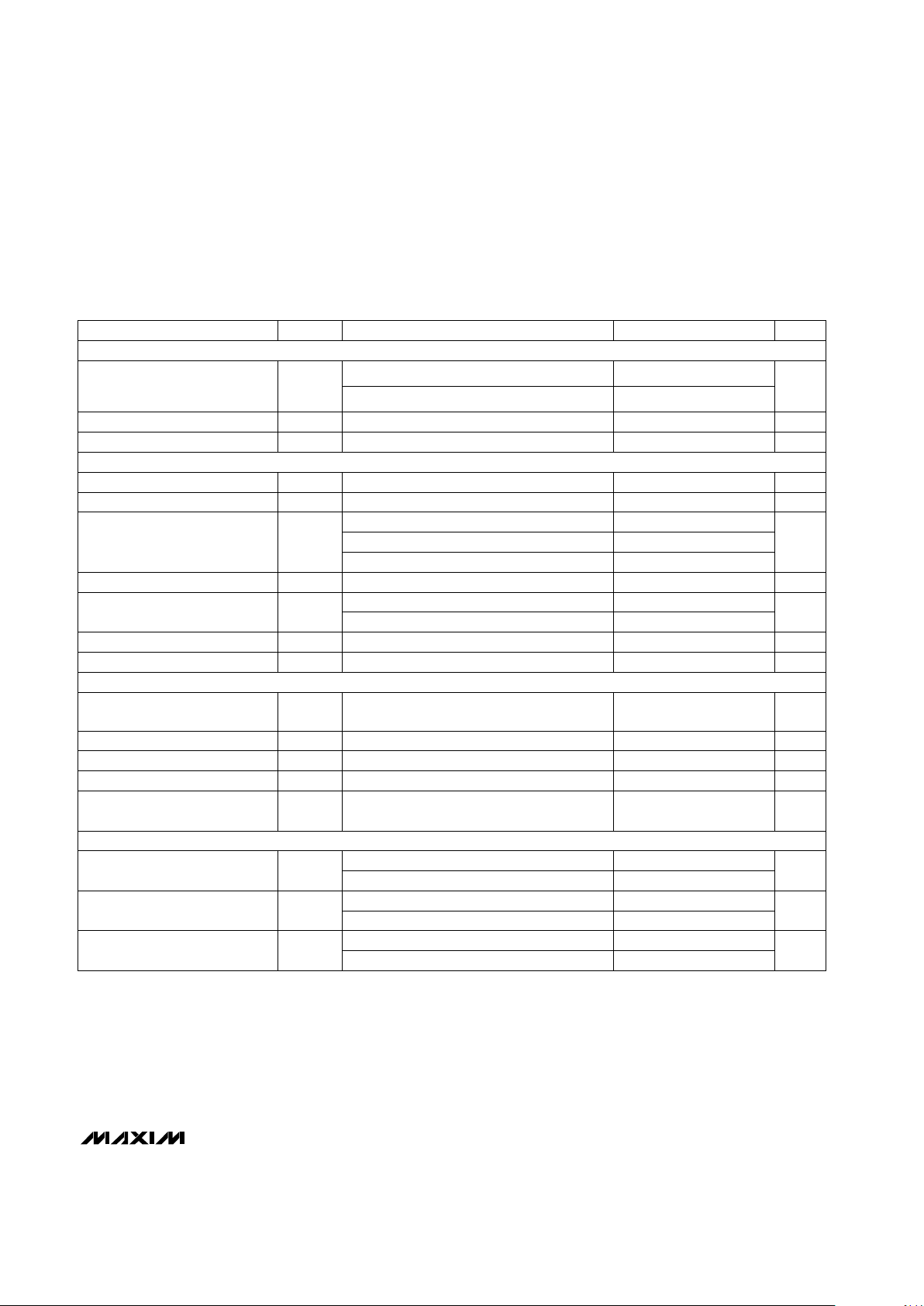

Multiplexer Leakage Current

µA0.01 10Shutdown VREF Input Current

kΩ18 25VREF Input Resistance

µA100 150VREF Input Current

V

1.0

V

DD

+

50mV

VREF Input Voltage Range

(Note 8)

pF16Input Capacitance

0 to VREF

V

±VREF / 2

Input Voltage Range, SingleEnded and Differential (Note 6)

µA±0.01 ±1

UNITSMIN TYP MAXSYMBOLPARAMETER

Unipolar, COM = 0V

VREF = 2.500V

Bipolar, COM = VREF / 2

On/off leakage current, V

CH_

= 0V or V

DD

CONDITIONS

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +2.7V to +3.6V (MAX146); VDD= +2.7V to +5.25V (MAX147); COM = 0V; f

SCLK

= 2.0MHz; external clock (50% duty cycle); 15

clocks/conversion cycle (133ksps); MAX146—4.7µF capacitor at VREF pin; MAX147—external reference, VREF = 2.500 V applied to

VREF pin; T

A

= T

MIN

to T

MAX

; unless otherwise noted.)

V2.480 2.500 2.520VREF Output Voltage TA= +25°C

mA30VREF Short-Circuit Current

±30 ±50MAX146_C

±30 ±60MAX146_E ppm/°C

±30 ±80

VREF Temperature Coefficient

MAX146_M

mV0.35Load Regulation (Note 7) 0mA to 0.2mA output load

0Internal compensation mode

µF

4.7

Capacitive Bypass at VREF

External compensation mode

µF0.047Capacitive Bypass at REFADJ

%±1.5REFADJ Adjustment Range

V

VDD-

0.5

REFADJ Buffer Disable Threshold

µF

0

Capacitive Bypass at VREF

Internal compensation mode

2.00

V/V

2.06

Reference Buffer Gain

4.7

MAX147

MAX146

External compensation mode

±10

µA

±50

REFADJ Input Current

MAX147

MAX146

ANALOG/COM INPUTS

INTERNAL REFERENCE (MAX146 only, reference buffer enabled)

EXTERNAL REFERENCE AT VREF (Buffer disabled)

EXTERNAL REFERENCE AT REFADJ

µA

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

4 _______________________________________________________________________________________

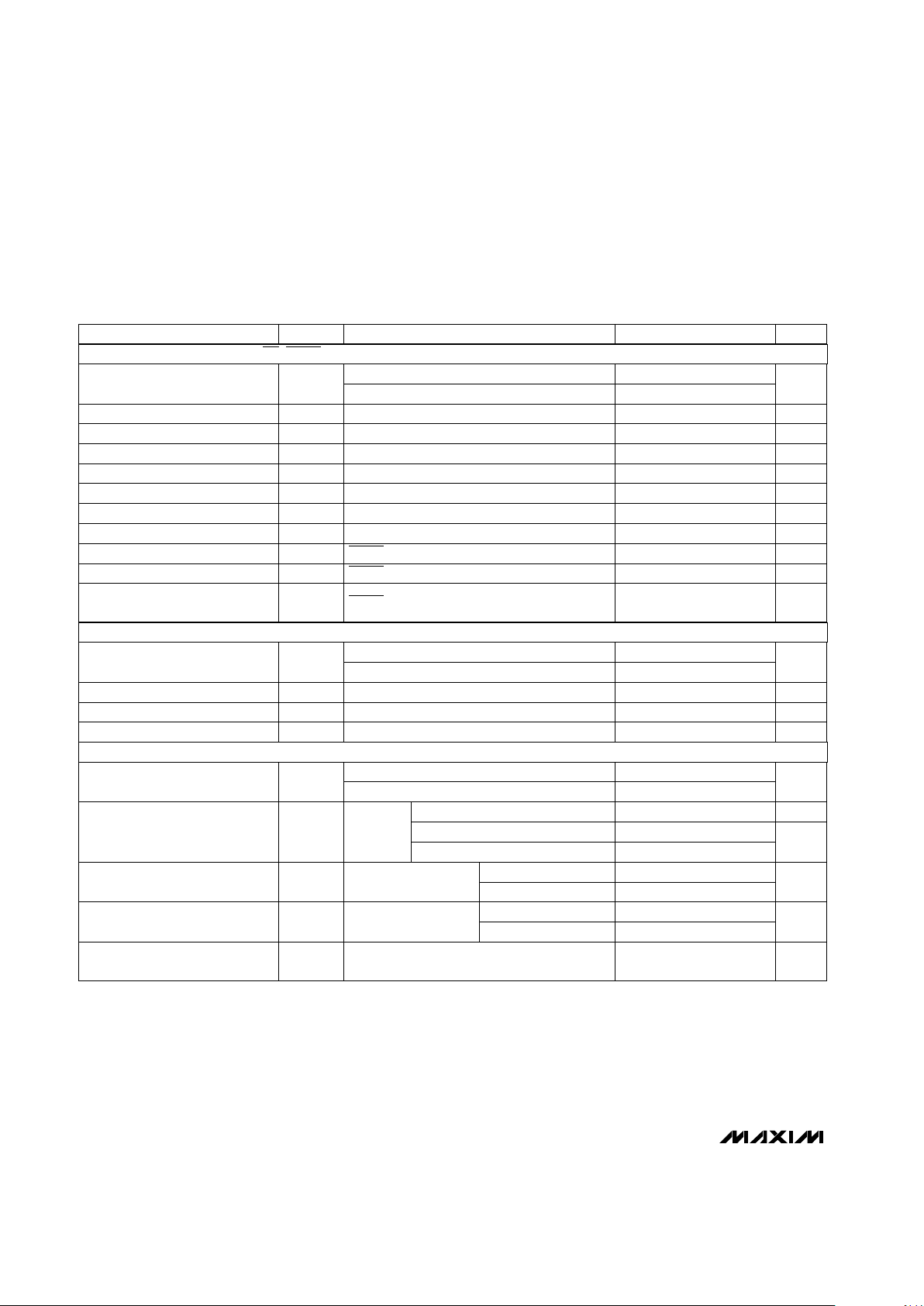

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +2.7V to +3.6V (MAX146); VDD= +2.7V to +5.25V (MAX147); COM = 0V; f

SCLK

= 2.0MHz; external clock (50% duty cycle); 15

clocks/conversion cycle (133ksps); MAX146—4.7µF capacitor at VREF pin; MAX147—external reference, VREF = 2.500 V applied to

VREF pin; T

A

= T

MIN

to T

MAX

; unless otherwise noted.)

V

3.0

V

IH

VDD= 3.6V

DIN, SCLK, CS Input High Voltage

VDD> 3.6V, MAX147 only

mV±0.3PSRSupply Rejection (Note 10)

Full-scale input, external reference = 2.500V,

VDD= 2.7V to V

DD(MAX)

pF15C

IN

DIN, SCLK, CS Input Capacitance

µA±0.01 ±1I

IN

DIN, SCLK, CS Input Leakage

V0.2V

HYST

DIN, SCLK, CS Input Hysteresis

V0.8V

IL

DIN, SCLK, CS Input Low Voltage

2.0

µA±4.0I

S

SHDN Input Current

V0.4V

SL

SHDN Input Low Voltage

VVDD- 0.4V

SH

SHDN Input High Voltage

SHDN = 0V or V

DD

nA±100

SHDN Maximum Allowed

Leakage, Mid Input

VV

DD

/ 2V

FLT

SHDN Voltage, Floating

SHDN = FLOAT

SHDN = FLOAT

UNITSMIN TYP MAXSYMBOLPARAMETER

(Note 9)

VIN= 0V or V

DD

V

DD

≤ 3.6V

I

DD

CONDITIONS

Positive Supply Current, MAX146

µA

1.2 2.0

µA±0.01 ±10I

L

Three-State Leakage Current

VVDD- 0.5V

OH

Output Voltage High

V

0.8

V

OL

Output Voltage Low

0.4

2.70 3.60

pF15C

OUT

Three-State Output Capacitance

MAX146

CS = VDD(Note 9)

CS = V

DD

I

SOURCE

= 0.5mA

I

SINK

= 16mA

I

SINK

= 5mA

V

2.70 5.25

V

DD

Positive Supply Voltage

MAX147

0.9 1.5

Operating mode,

full-scale input

VDD= 5.25V

VDD= 3.6V

2.1 15VDD= 5.25V

VDD= 3.6V 1.2 10

Full power-down

mA

1.8 2.5

30 70

1.2 10

Operating mode, full-scale input

Fast power-down

Full power-down

mA

V1.1 VDD- 1.1V

SM

SHDN Input Mid Voltage

I

DD

Positive Supply Current, MAX147

DIGITAL INPUTS (DIN, SCLK, CS, SHDN)

DIGITAL OUTPUTS (DOUT, SSTRB)

POWER REQUIREMENTS

I

DD

Positive Supply Current, MAX147 µA

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

_______________________________________________________________________________________ 5

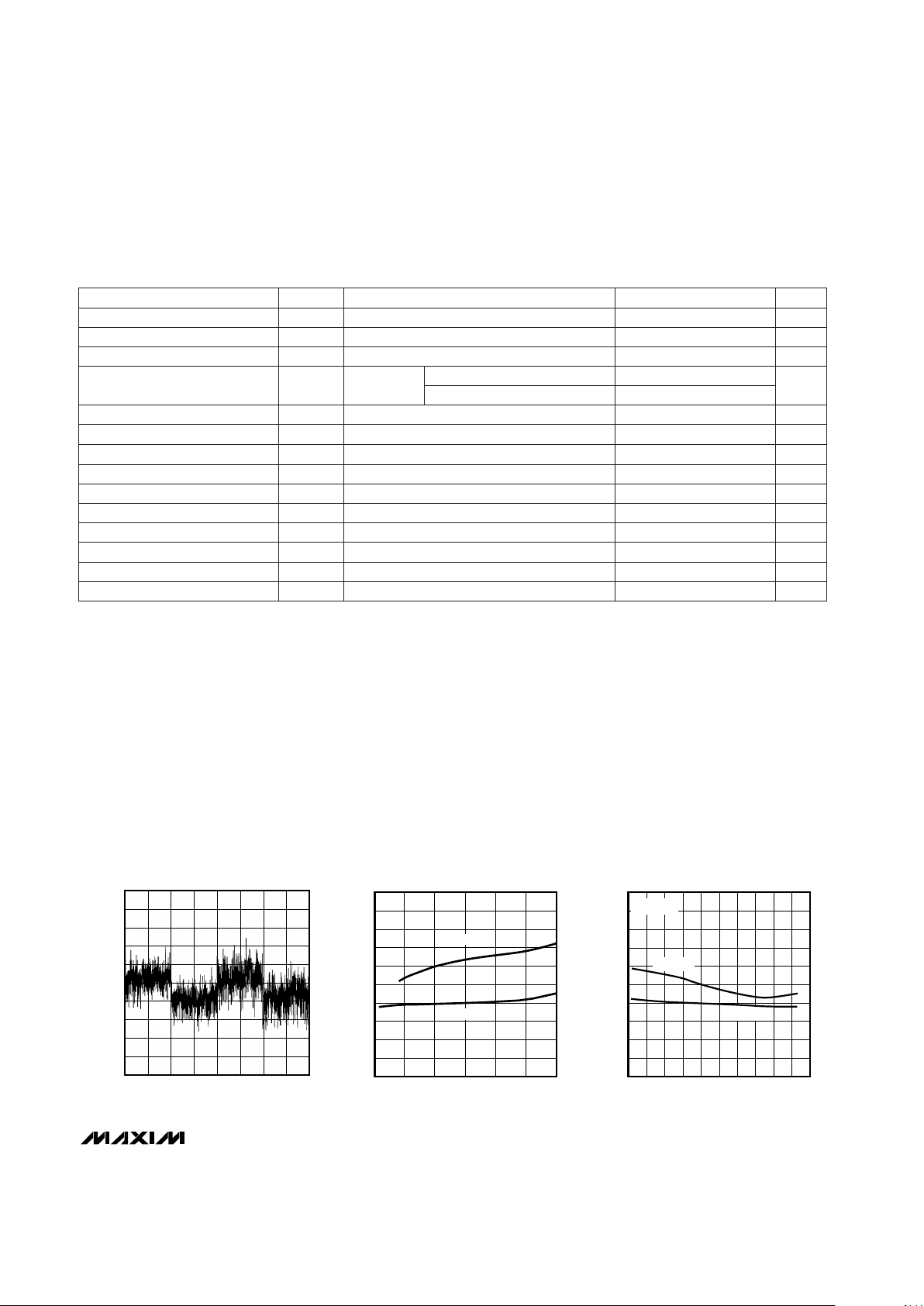

Figure 1

__________________________________________Typical Operating Characteristics

(VDD= 3.0V, VREF = 2.500V, f

SCLK

= 2.0MHz, C

LOAD

= 20pF, TA = +25°C, unless otherwise noted.)

0.5

0 1024 2048 3072 4096

INTEGRAL NONLINEARITY

vs. CODE

0.3

-0.3

-0.5

-0.1

0.1

0.4

0.2

-0.4

-0.2

0

MAX146/47-01

CODE

INL (LSB)

0.50

0

2.25 2.75 4.25

INTEGRAL NONLINEARITY

vs. SUPPLY VOLTAGE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

V

DD

(V)

INL (LSB)

3.75 5.253.25 4.75

MAX146/47-02

MAX146

MAX147

0

0.10

0.20

0.30

0.40

0.50

0.05

0.15

0.25

0.35

0.45

-60 -20 20 60 100 140

INTEGRAL NONLINEARITY

vs. TEMPERATURE

TEMPERATURE (°C)

INL (LSB)

MAX146/47-03

MAX147

MAX146

VDD = 2.7V

TIMING CHARACTERISTICS

(VDD= +2.7V to +3.6V (MAX146); VDD= +2.7V to +5.25V (MAX147); TA= T

MIN

to T

MAX

; unless otherwise noted.)

Note 1: Tested at V

DD

= 2.7V; COM = 0V; unipolar single-ended input mode.

Note 2: Relative accuracy is the deviation of the analog value at any code from its theoretical value after the full-scale range has

been calibrated.

Note 3: MAX146—internal reference, offset nulled; MAX147—external reference (VREF = +2.500V), offset nulled.

Note 4: Ground “on” channel; sine wave applied to all “off” channels.

Note 5: Conversion time defined as the number of clock cycles multiplied by the clock period; clock has 50% duty cycle.

Note 6: The common-mode range for the analog inputs is from AGND to V

DD

.

Note 7: External load should not change during conversion for specified accuracy.

Note 8: ADC performance is limited by the converter’s noise floor, typically 300µVp-p.

Note 9: Guaranteed by design. Not subject to production testing.

Note

10:

Measured as |VFS(2.7V) - VFS(V

DD, MAX

)|.

Internal clock mode only (Note 9)

External clock mode only, Figure 2

External clock mode only, Figure 1

DIN to SCLK Setup

Figure 1

Figure 2

Figure 1

MAX14_ _C/E

CONDITIONS

MAX14_ _M

ns

20 240

Figure 1

ns

t

CSH

ns240t

STR

CS Rise to SSTRB Output Disable

ns240t

SDV

CS Fall to SSTRB Output Enable

240t

SSTRB

SCLK Fall to SSTRB ns

200t

CL

SCLK Pulse Width Low

ns200SCLK Pulse Width High

ns0

CS to SCLK Rise Hold

ns100t

CSS

CS to SCLK Rise Setup

ns240t

TR

CS Rise to Output Disable

ns240t

DV

CS Fall to Output Enable

t

CH

20 200

t

DO

SCLK Fall to Output Data Valid

ns0t

DH

DIN to SCLK Hold

ns

µs1.5t

ACQ

Acquisition Time

0t

SCK

SSTRB Rise to SCLK Rise

ns100t

DS

UNITSMIN TYP MAXSYMBOLPARAMETER

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

6 _______________________________________________________________________________________

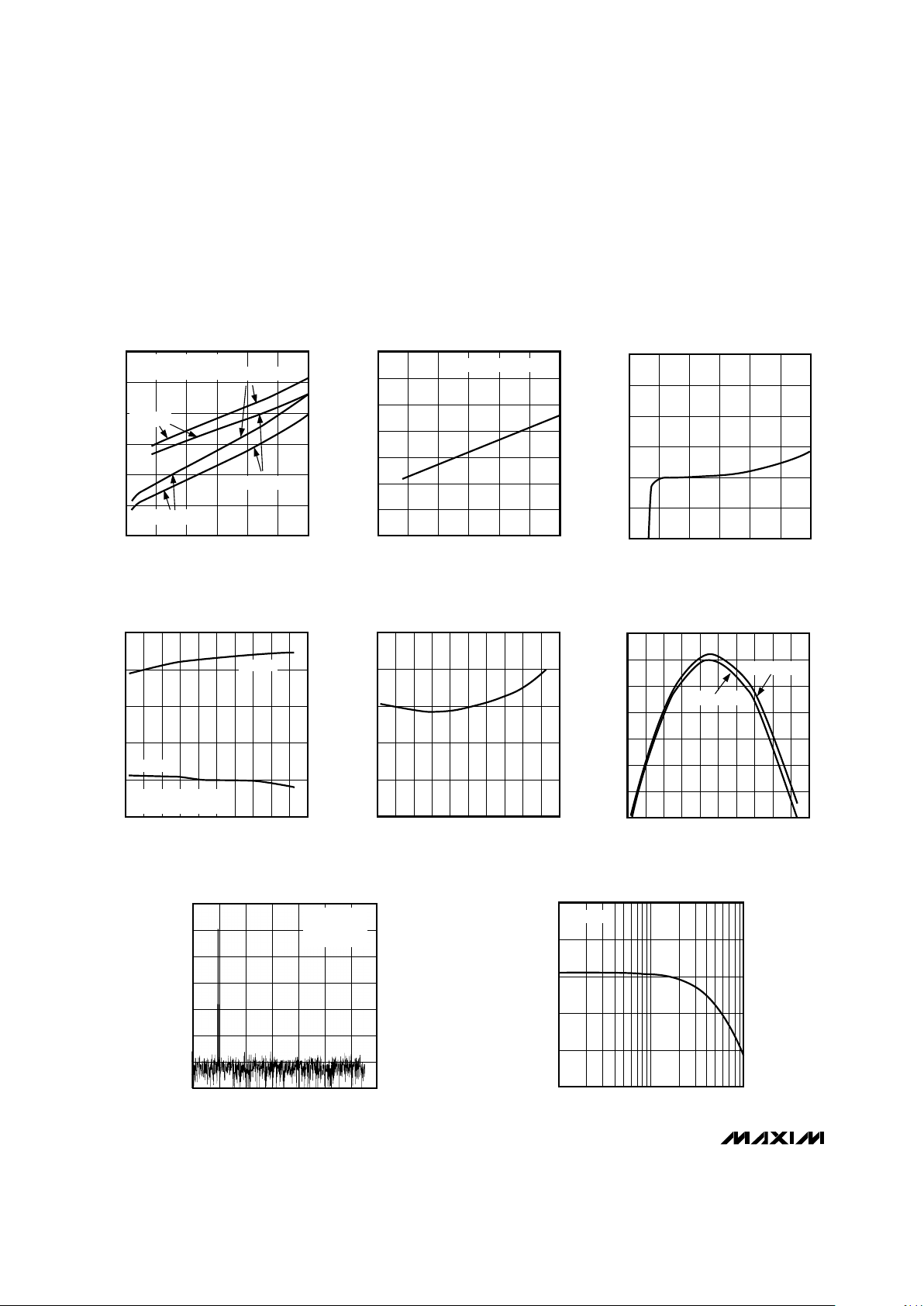

2.00

0.50

2.25 2.75

SUPPLY CURRENT

vs. SUPPLY VOLTAGE

1.75

1.25

1.50

1.00

0.75

SUPPLY VOLTAGE (V)

SUPPLY CURRENT (mA)

3.75 5.253.25 4.25 4.75

MAX146/47-04

RL = ∞

CODE = 101010100000

C

LOAD

= 50pF

MAX147

MAX146

C

LOAD

= 20pF

3.5

3.0

0

2.25 2.75

SHUTDOWN SUPPLY CURRENT

vs. SUPPLY VOLTAGE

2.5

2.0

1.5

1.0

0.5

V

DD

(V)

SHUTDOWN SUPPLY CURRENT (µA)

3.75 5.253.25 4.25 4.75

MAX146/47-05

FULL POWER-DOWN

2.5020

2.4990

2.25 2.75

MAX146

INTERNAL REFERENCE VOLTAGE

vs. SUPPLY VOLTAGE

2.5015

2.5005

2.5010

2.5000

2.4995

V

DD

(V)

VREF (V)

3.75 5.253.25 4.25 4.75

MAX146/47-06

0.8

0.9

1.0

1.1

1.2

1.3

-60 -20 20 60 100 140

SUPPLY CURRENT vs. TEMPERATURE

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

MAX146/47-07

MAX147

MAX146

R

LOAD

= ∞

CODE = 101010100000

0 10 20 30 40 50 60 70

FFT PLOT

FREQUENCY (kHz)

AMPLITUDE (dB)

-120

-100

-80

-60

-40

-20

0

20

MAX146/47-10

VDD = 2.7V

f

IN

= 10kHz

f

SAMPLE

= 133kHz

0

0.4

0.8

1.2

1.6

2.0

-60 -20 20 60 100 140

SHUTDOWN CURRENT

vs. TEMPERATURE

TEMPERATURE (°C)

SHUTDOWN CURRENT (µA)

MAX1247-08

2.494

2.495

2.496

2.497

2.498

2.499

2.500

2.501

-60 -20 20 60 100 140

MAX146

INTERNAL REFERENCE VOLTAGE

vs. TEMPERATURE

TEMPERATURE (°C)

VREF (V)

MAX146/47-09

VDD = 2.7V

VDD = 3.6V

11.0

11.2

11.4

11.6

11.8

12.0

1 10 100

EFFECTIVE NUMBER OF BITS

vs. FREQUENCY

MAX146/47-11

FREQUENCY (kHz)

ENOB

VDD = 2.7V

____________________________Typical Operating Characteristics (continued)

(VDD= 3.0V, VREF = 2.500V, f

SCLK

= 2.0MHz, C

LOAD

= 20pF, TA = +25°C, unless otherwise noted.)

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

_______________________________________________________________________________________

7

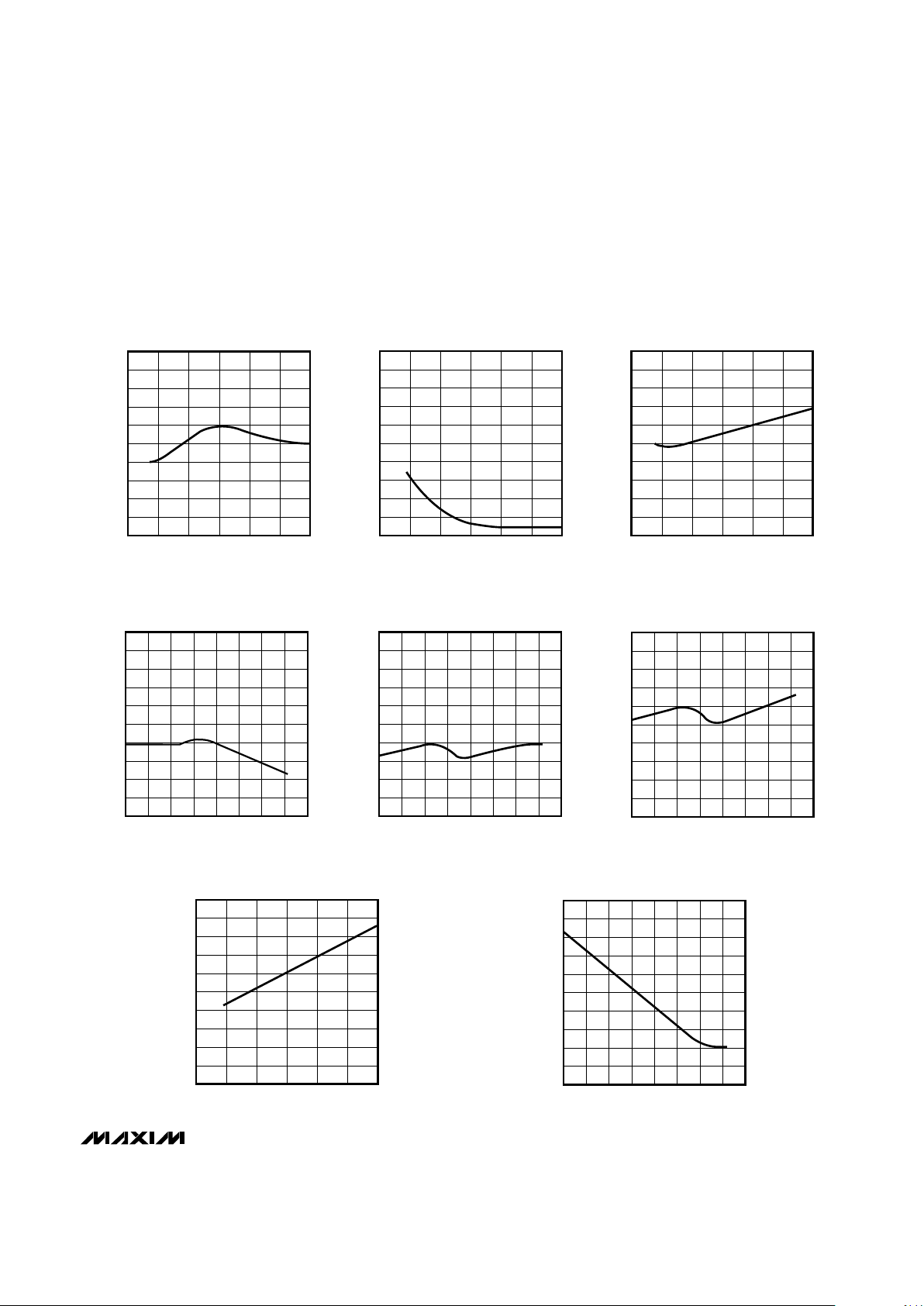

____________________________Typical Operating Characteristics (continued)

(VDD= 3.0V, VREF = 2.500V, f

SCLK

= 2.0MHz, C

LOAD

= 20pF, TA = +25°C, unless otherwise noted.)

0.50

0

2.25 2.75 4.25

OFFSET vs. SUPPLY VOLTAGE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

V

DD

(V)

OFFSET (LSB)

3.753.25 4.75 5.25

MAX146/47-12

0.50

0

2.25

2.75

3.75

GAIN ERROR

vs. SUPPLY VOLTAGE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

V

DD

(V)

GAIN ERROR (LSB)

3.25 4.25 5.254.75

MAX146/47-13

0.50

0

2.25 2.75 3.75

CHANNEL-TO-CHANNEL GAIN MATCHING

vs. SUPPLY VOLTAGE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

V

DD

(V)

GAIN MATCHING (LSB)

3.25 4.25 5.254.75

MAX146/47-14

0.50

0

-55 -30

45

OFFSET vs. TEMPERATURE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

TEMPERATURE (˚C)

OFFSET (LSB)

20-5 70 14512095

MAX146/47-15

0.50

0

2.25

2.75 4.25

CHANNEL-TO-CHANNEL OFFSET MATCHING

vs. SUPPLY VOLTAGE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

V

DD

(V)

OFFSET MATCHING (LSB)

3.753.25 5.254.75

MAX146/47-18

0.50

0

-55

-30

20

GAIN ERROR

vs. TEMPERATURE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

TEMPERATURE (˚C)

GAIN ERROR (LSB)

-5 45 120 1459570

MAX146/47-16

0.50

0

-55

-30

20

CHANNEL-TO-CHANNEL GAIN MATCHING

vs. TEMPERATURE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

TEMPERATURE (˚C)

GAIN MATCHING (LSB)

-5 45

1451209570

MAX146/47-17

0.50

0

-55

-30

45

CHANNEL-TO-CHANNEL OFFSET MATCHING

vs. TEMPERATURE

0.45

0.40

0.35

0.30

0.25

0.20

0.15

0.10

0.05

TEMPERATURE (˚C)

OFFSET MATCHING (LSB)

20

-5

70 14512095

MAX146/47-19

MAX146/MAX147

+2.7V, Low-Power, 8-Channel,

Serial 12-Bit ADCs

8 _______________________________________________________________________________________

NAME FUNCTION

1–8 CH0–CH7 Sampling Analog Inputs

PIN

9 COM

Ground reference for analog inputs. COM sets zero-code voltage in single-ended mode. Must be

stable to ±0.5LSB.

10

SHDN

Three-Level Shutdown Input. Pulling SHDN low shuts the MAX146/MAX147 down; otherwise, they are

fully operational. Pulling SHDN high puts the reference-buffer amplifier in internal compensation mode.

Letting SHDN float puts the reference-buffer amplifier in external compensation mode.

15 DOUT

Serial Data Output. Data is clocked out at SCLK’s falling edge. High impedance when CS is high.

14 DGND Digital Ground

13 AGND Analog Ground

11 VREF

Reference-Buffer Output/ADC Reference Input. Reference voltage for analog-to-digital conversion.

In internal reference mode (MAX146 only), the reference buffer provides a 2.500V nominal output,

externally adjustable at REFADJ. In external reference mode, disable the internal buffer by pulling

REFADJ to VDD.

19 SCLK

Serial Clock Input. Clocks data in and out of serial interface. In external clock mode, SCLK also sets

the conversion speed. (Duty cycle must be 40% to 60%.)

18

CS

Active-Low Chip Select. Data will not be clocked into DIN unless CS is low. When CS is high, DOUT is

high impedance.

17 DIN Serial Data Input. Data is clocked in at SCLK’s rising edge.

16 SSTRB

Serial Strobe Output. In internal clock mode, SSTRB goes low when the MAX146/MAX147 begin the

A/D conversion, and goes high when the conversion is finished. In external clock mode, SSTRB pulses

high for one clock period before the MSB decision. High impedance when CS is high (external clock

mode).

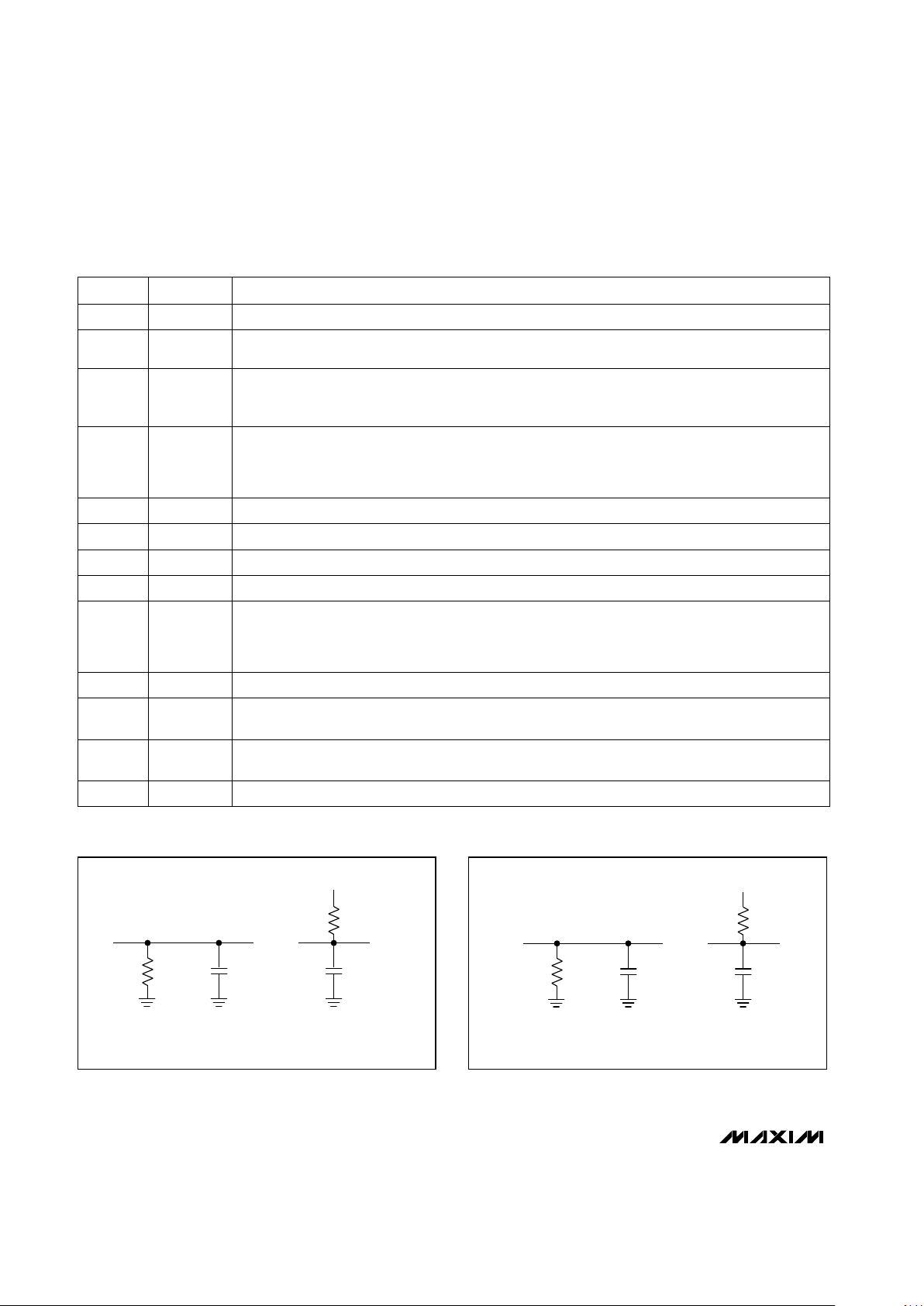

______________________________________________________________Pin Description

V

DD

6k

DGND

DOUT

C

LOAD

50pF

C

LOAD

50pF

DGND

6k

DOUT

a) High-Z to V

OH

and VOL to V

OH

b) High-Z to VOL and VOH to V

OL

V

DD

6k

DGND

DOUT

C

LOAD

50pF

C

LOAD

50pF

DGND

6k

DOUT

a) V

OH

to High-Z b) VOL to High-Z

Figure 1. Load Circuits for Enable Time Figure 2. Load Circuits for Disable Time

12 REFADJ Input to the Reference-Buffer Amplifier. To disable the reference-buffer amplifier, tie REFADJ to VDD.

20 V

DD

Positive Supply Voltage

Loading...

Loading...