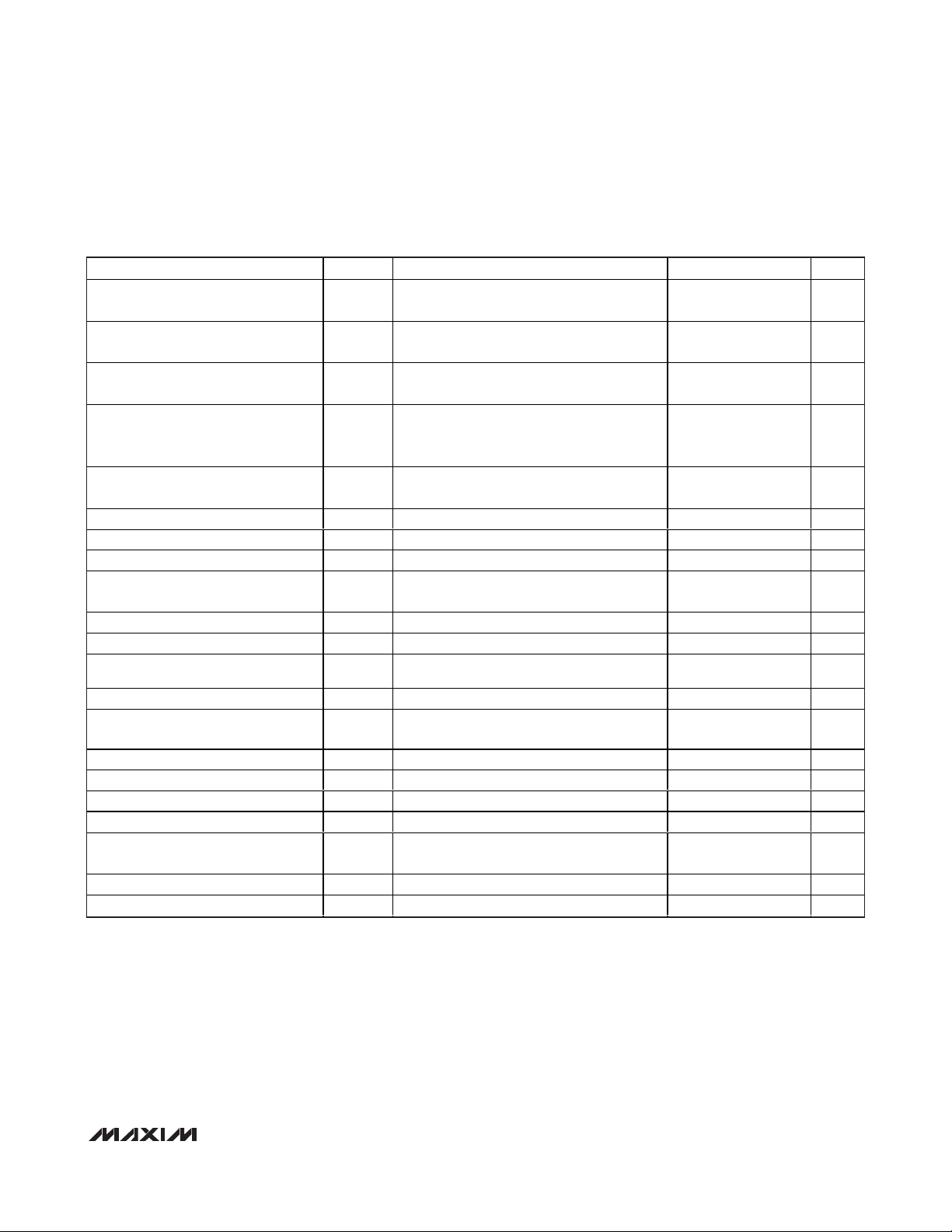

Selector Guide

General Description

The MAX13442E/MAX13444E are fault-protected RS-485

and J1708 transceivers that feature ±80V protection from

signal faults on communication bus lines. The

MAX13442E/MAX13444E feature a reduced slew-rate driver that minimizes EMI and reflections, allowing error-free

transmission up to 250kbps. The MAX13443E driver can

transmit up to 10Mbps. The high-speed MAX13443E

RS-485 tranceiver features ±60V protection from signal

faults on communication bus lines. These transceivers feature foldback current limit. Each device contains one differential line driver with three-state output and one

differential line receiver with three-state input. The 1/4-unitload receiver input impedance allows up to 128 transceivers on a single bus. The devices operate from a 5V

supply. True fail-safe inputs guarantee a logic-high receiver output when the receiver inputs are open, shorted, or

connected to an idle data line.

Hot-swap circuitry eliminates false transitions on the

data bus during circuit initialization or connection to a

live backplane. Short-circuit current-limiting and thermal-shutdown circuitry protect the driver against excessive power dissipation, and on-chip ± 15kV ESD

protection eliminates costly external protection devices.

The MAX13442E/MAX13443E/MAX13444E are available in an 8-pin SO package and are specified over the

automotive temperature range.

Applications

Features

♦ ±15kV ESD Protection

♦ ±80V Fault Protection (±60V MAX13443E)

♦ Guaranteed 10Mbps Data Rate (MAX13443E)

♦ Hot-Swappable for Telecom Applications

♦ True Fail-Safe Receiver Inputs

♦ Enhanced Slew-Rate-Limiting Facilitates

Error-Free Data Transmission

(MAX13442E/MAX13444E)

♦ Allow Up to 128 Transceivers on the Bus

♦ -7V to +12V Common-Mode Input Range

♦ ±6mA FoldBack Current Limit

♦ Industry-Standard Pinout

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

________________________________________________________________

Maxim Integrated Products

1

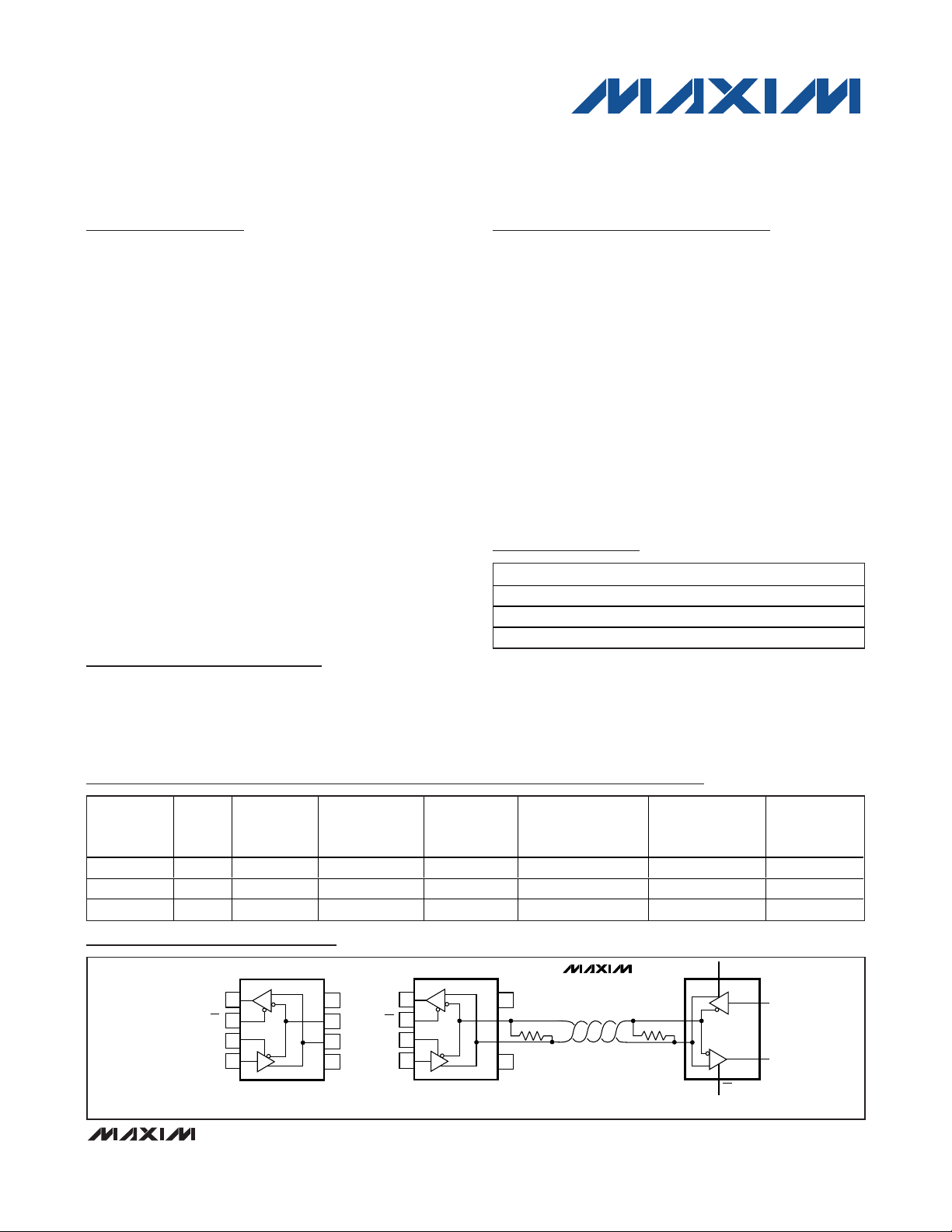

Pin Configurations and Typical Operating Circuits

Ordering Information

19-3898; Rev 3; 3/11

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

Pin Configurations and Typical Operating Circuits continued at end of data sheet.

RS-422/RS-485

Communications

Truck and Trailer

Applications

Industrial Networks

Telecommunications

Systems

Automotive Applications

HVAC Controls

+

Denotes a lead(Pb)-free/RoHS-compliant package.

/V denotes an automotive qualified part.

T = Tape and reel.

PART TEMP RANGE PIN-PACKAGE

MAX13442EASA+ -40°C to +125°C 8 SO

MAX13443EASA+ -40°C to +125°C 8 SO

MAX13444EASA/V+T -40°C to +125°C 8 SO

PART TYPE

MAX13442E RS-485 0.25 ±80 Yes Yes 128 Yes

MAX13443E RS-485 10 ±60 Yes Yes 128 Yes

MAX13444E J1708 0.25 ±80 Yes Yes 128 Yes (only RE)

DATA RATE

(Mbps)

FAULT

PROTECTION

(V)

LOW-POWER

SHUTDOWN

RECEIVER/DRIVER

ENABLE

TRANSCEIVERS

ON BUS

HOT

SWAP

TOP VIEW

+

RO

RE

DE

DI

R

1

2

3

4

D

SO SO

V

8

CC

B

7

A

6

GND

5

+

RO

RE

DE

DI

R

1

2

3

4

D

8

V

CC

B

7

6

A

5

GND

MAX13442E

MAX13443E

R

T

B

R

T

A

DE

D

R

RE

DI

RO

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

2 _______________________________________________________________________________________

ABSOLUTE MAXIMUM RATINGS

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

(Voltages referenced to GND.)

V

CC

........................................................................................+7V

RE, DE, DE, DI, TXD ...................................-0.3V to (V

CC

+ 0.3V)

A, B (Note 1) (MAX13442E/MAX13444E) ............................±80V

A, B (Note 1) (MAX13443E) .................................................±60V

RO ..............................................................-0.3V to (V

CC

+ 0.3V)

Short-Circuit Duration (RO, A, B) ...............................Continuous

Continuous Power Dissipation (T

A

= +70°C)

SO (derate 7.6mW/°C above +70°C)...........................606mW

Operating Temperature Range .........................-40°C to +125°C

Storage Temperature Range .............................-65°C to +150°C

Junction Temperature......................................................+150°C

Lead Temperature (soldering, 10s) .................................+300°C

Soldering Temperature (reflow) .......................................+260°C

PACKAGE THERMAL CHARACTERISTICS (Note 2)

SO

Junction-to-Ambient Thermal Resistance (θ

JA

) .........132°C/W

Junction-to-Case Thermal Resistance (θ

JC

) ................38°C/W

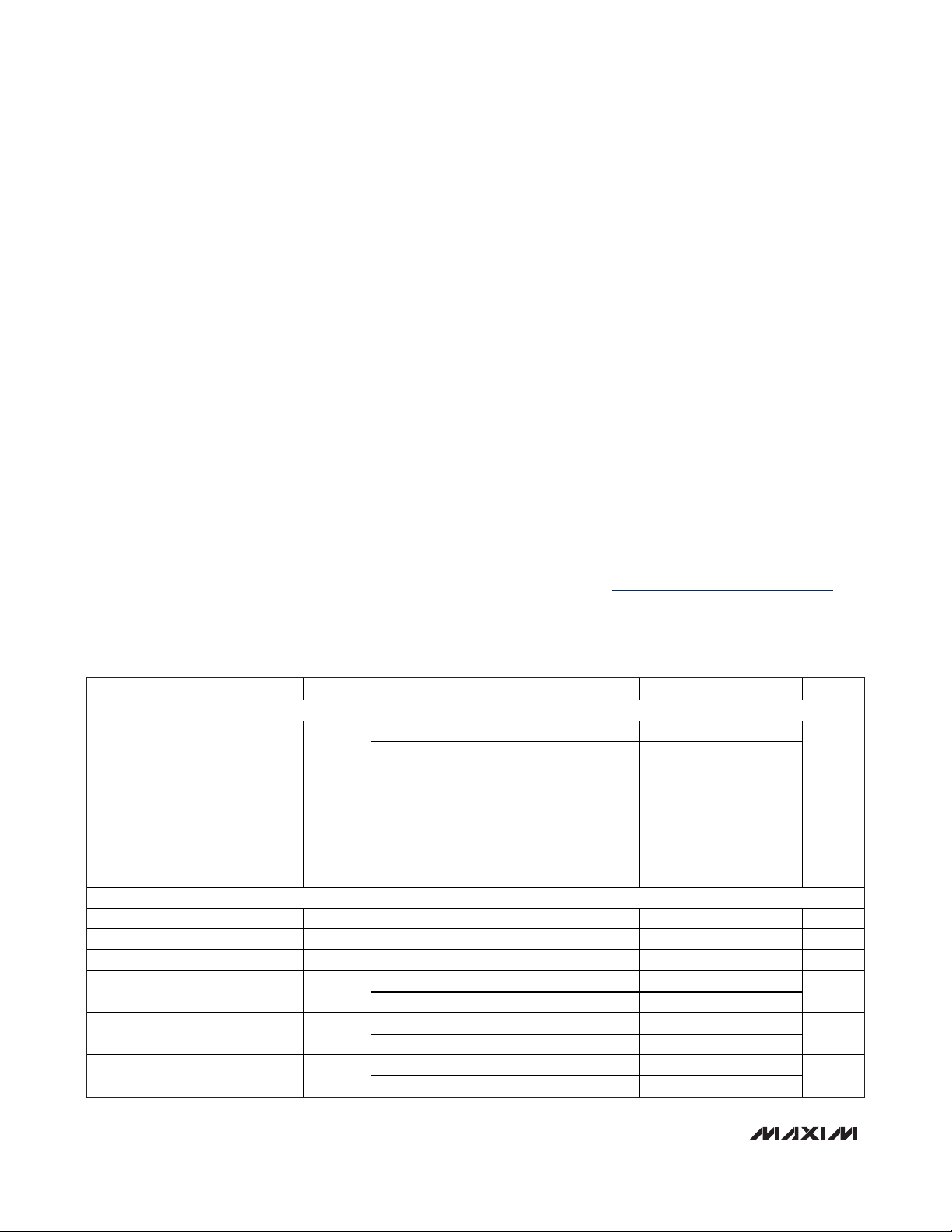

DC ELECTRICAL CHARACTERISTICS

(VCC= +4.75V to +5.25V, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.)

Note 1: During normal operation, a termination resistor must be connected between A and B in order to guarantee overvoltage pro-

tection up to the absolute maximum rating of this device. When not in operation, these devices can withstand fault voltages

up to the maximum rating without a termination resistor and will not be damaged.

Note 2: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-

layer board. For detailed information on package thermal considerations, refer to www.maxim-ic.com/thermal-tutorial

.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

DRIVER

Differential Driver Output V

Change in Magnitude of

Differential Output Voltage

Driver Common-Mode

Output Voltage

Change in Magnitude of

Common-Mode Voltage

DRIVER LOGIC

Driver-Input High Voltage V

Driver-Input Low Voltage V

Driver-Input Current I

Driver Short-Circuit Output Current

(Note 4)

Driver Short-Circuit Foldback

Output Current

Driver-Limit Short-Circuit Foldback

Output Current

Figure 1, RL = 100 2 V

OD

Figure 1, RL = 54 1.5 V

Figure 1, RL = 100 or 54 (Note 3) 0.2 V

V

OD

V

V

DIN

I

OSD

I

OSDF

I

OSDL

Figure 1, RL = 100 or 54 V

OC

Figure 1, RL = 100 or 54 (Note 3)

OC

(MAX13442E/MAX13443E)

2 V

DIH

0.8 V

DIL

±2 μA

0V V

-7V V

(VCC - 1V) V

-7V V

V

OUT

V

OUT

+12V +350

OUT

VCC -350

OUT

+12V (Note 4) +25

OUT

+1V (Note 4) -25

OUT

+20V, RL = 100 +6

-15V, RL = 100 -6

0.2 V

CC

CC

/ 2 3 V

CC

V

mA

mA

mA

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

_______________________________________________________________________________________ 3

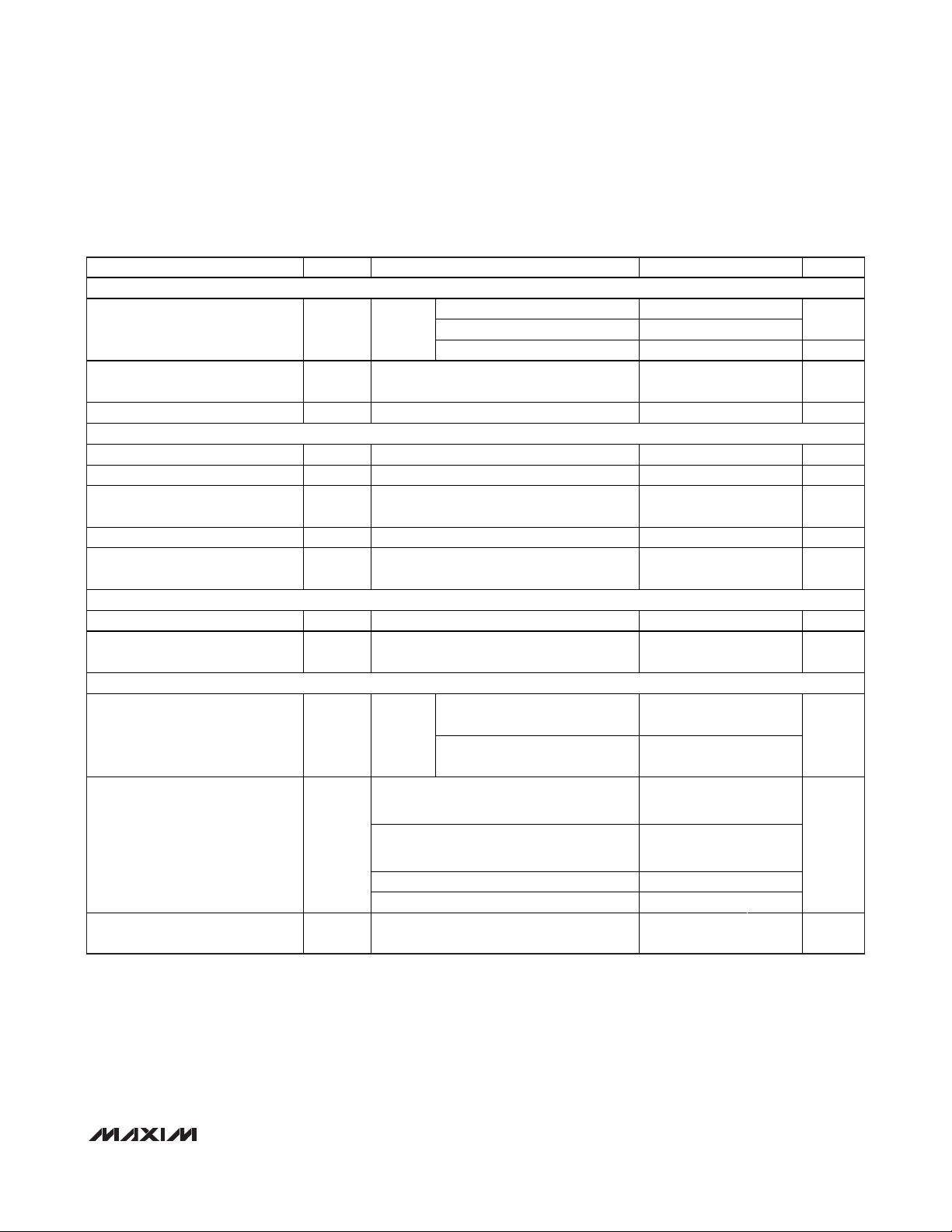

DC ELECTRICAL CHARACTERISTICS (continued)

(VCC= +4.75V to +5.25V, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.)

RECEIVER

Input Current I

Receiver-Differential Threshold

Voltage

Receiver-Input Hysteresis VTH 25 mV

RECEIVER LOGIC

Output-High Voltage VOH Figure 2, IOH = -1.6mA VCC - 0.6 V

Output-Low Voltage VOL Figure 2, IOL = 1mA 0.4 V

Three-State Output Current at

Receiver

Receiver Input Resistance RIN -7V VCM +12V 48 k

Receiver Output Short-Circuit

Current

CONTROL

Control-Input High Voltage V

Input-Current Latch During First

Rising Edge

SUPPLY CURRENT

Normal Operation I

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

A, B

receive

A,B

mode

V

-7V VCM +12V -200 -50 mV

TH

I

0V V

OZR

I

0V VRO V

OSR

DE, DE, RE 2 V

CIH

I

DE, RE 90 μA

IN

No load,

DI = V

CC

or GND

VCC = GND, V

V

= -7V -150

A, B

V

= ±80V ±6 mA

A, B

V

A, B

CC

±1 μA

CC

CC

DE = VCC, RE = GND (MAX13442E)

(DE = RE = GND) (MAX13444E)

(DE = V

CC

(MAX13443E)

= 12V 250

A, B

30

, RE = GND)

10

μA

±95 mA

mA

Supply Current in Shutdown Mode I

Supply Current with Output Shorted

to ±60V

SHDN

I

SHRT

DE = GND, RE = V

(MAX13442E/MAX13443E)

DE = GND, RE = VCC, TA = +25°C

(MAX13442E/MAX13443E)

DE = RE = VCC (MAX13444E) 100

DE = RE = VCC, TA = +25°C (MAX13444E) 10

DE = GND, RE = GND, no load

output in three-state (MAX13443E)

CC

20

10

±15 mA

μA

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

4 _______________________________________________________________________________________

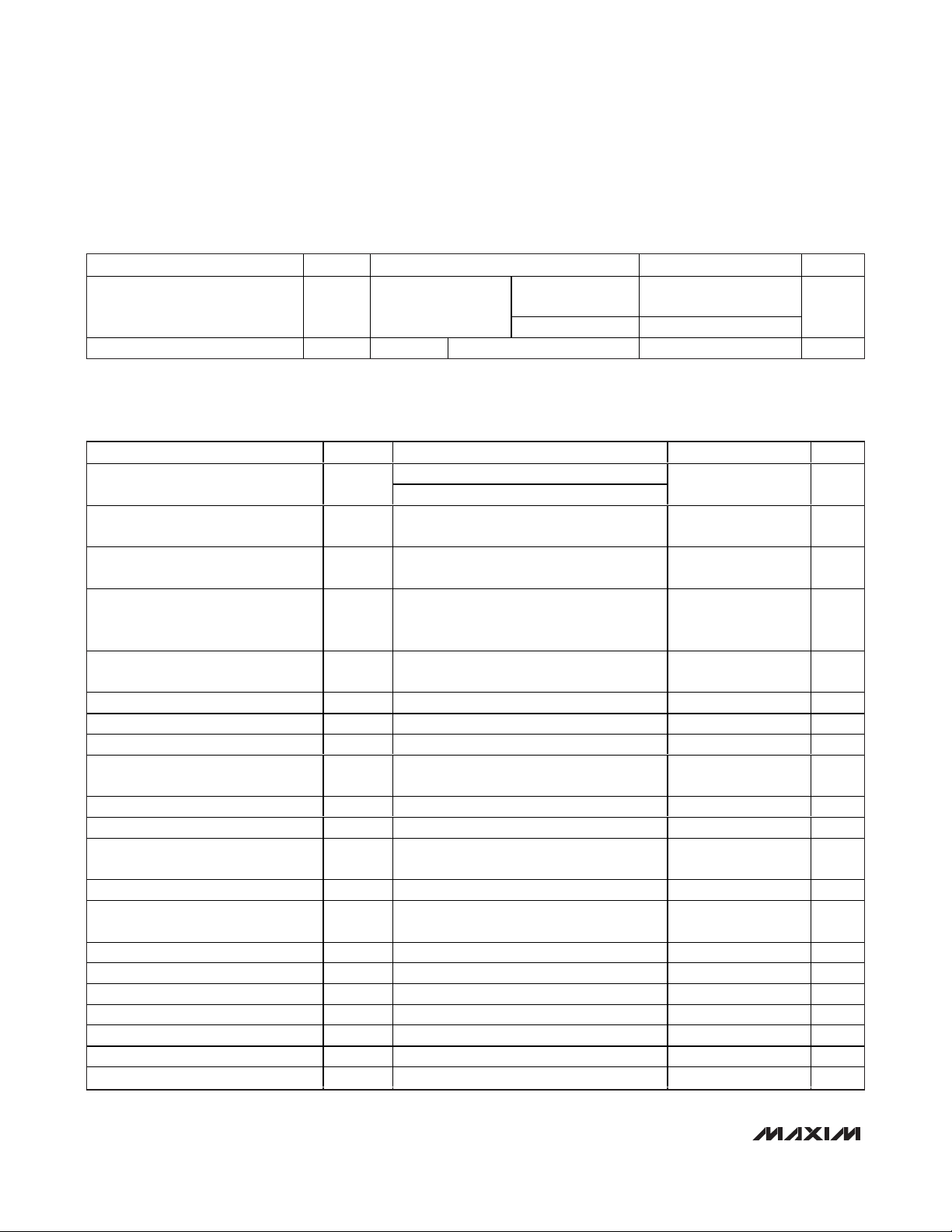

SWITCHING CHARACTERISTICS (MAX13442E/MAX13444E)

(VCC= +4.75V to +5.25V, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.)

PROTECTION SPECIFICATIONS

(VCC= +4.75V to +5.25V, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.)

PARAMETER S YMBOL CONDITIONS MIN TYP MAX UNITS

Overvoltage Protection

ESD Protection A, B Human Body Model ±15 kV

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Driver Propagation Delay

Driver Differential Propagation Delay

Driver Differential Output

Transition Time

Driver Output Skew

Differential Driver Output Skew t

Maximum Data Rate f

Driver Enable Time to Output High t

Driver Disable Time from Output High t

Driver Enable Time from Shutdown to

Output High

Driver Enable Time to Output Low t

Driver Disable Time from Output Low t

Driver Enable Time from Shutdown to

Output Low

Driver Time to Shutdown t

Receiver Propagation Delay

Receiver Output Skew t

Receiver Enable Time to Output High t

Recei ver D i sab l e Ti m e fr om Outp ut H i g ht

Receiver Wake Time from Shutdown t

Receiver Enable Time to Output Low t

Recei ver D i sab l e Ti m e fr om Outp ut Low t

Receiver Time to Shutdown t

A, B; R

SOURCE

= 54

R

L

t

PLHA,

t

PLHB R

t

DPLH,

t

DPHL

t

LH,tHLRL

t

S KEWAB

t

S KEWBA

DSKEW

MAX

PDZH

PDHZ

t

PDHS

PDZL

PDLZ

t

PDLS

SHDN

t

RPLH

t

RPHL

RSKEWCL

RPZH

RPHZ

RPWAKERL

RPZL

RPLZ

SHDN

Figure 3, RL = 54Ω, CL = 50pF (MAX13442E)

DIFF

RL = 54Ω, CL = 50pF, Figure 4 2000 ns

= 54Ω, CL = 50pF, Figure 4 200 2000 ns

RL = 54Ω, CL = 50pF,

,

t

SKEWAB

t

SKEWBA

RL = 54Ω, CL = 50pF,

t

DSKEW

RL = 500Ω, CL = 50pF, Figure 5 2000 ns

RL = 500Ω, CL = 50pF, Figure 5 2000 ns

RL = 500Ω, CL = 50pF, Figure 5 4.2 µs

RL = 500Ω, CL = 50pF, Figure 6 2000 ns

RL = 500Ω, CL = 50pF, Figure 6 2000 ns

RL = 500Ω, CL = 50pF, Figure 6 4.2 µs

RL = 500Ω, CL = 50p F 800 ns

,

C

= 20pF, V

L

= 20pF, t

RL = 1kΩ, C

RL = 1kΩ, CL = 20pF, Figure 8 2000 ns

= 1kΩ, CL = 20pF, Figure 8 4.2 µs

RL = 1kΩ, C

RL = 1kΩ, CL = 20pF, Figure 8 2000 ns

RL = 500Ω, CL = 50pF 800 ns

= 0,

= 60Ω, C

= |t

= |t

= |t

DPLH

L

L

MAX13442E/

MAX13444E

MAX13443E ±60

= 100pF (MAX13444E)

DIFF

- t

- t

PHLB

PHLA

DPHL

= |t

|,

|

|

RPLH

- t

| 200 ns

RPHL

PLHA

PLHB

- t

= 2V, VCM = 0V, Figure 7 2000 ns

ID

RSKEW

= 20pF, Figure 8 2000 ns

= 20pF, Figure 8 2000 ns

±80

250 kbps

2000 ns

350 ns

200 ns

V

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

_______________________________________________________________________________________ 5

SWITCHING CHARACTERISTICS (MAX13443E)

(VCC= +4.75V to +5.25V, TA= T

MIN

to T

MAX

, unless otherwise noted. Typical values are at VCC= +5V and TA= +25°C.)

Note 3: ΔV

OD

and ΔVOCare the changes in VODand VOC, respectively, when the DI input changes state.

Note 4: The short-circuit output current applies to peak current just before foldback current limiting. The short-circuit foldback out-

put current applies during current limiting to allow a recovery from bus contention.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Driver Propagation Delay

Driver Differential Propagation Delay

Driver Differential Output

Transition Time

Driver Output Skew

Differential Driver Output Skew t

Maximum Data Rate f

Driver Enable Time to Output High t

Driver Disable Time from Output High t

Driver Enable Time from Shutdown to

Output High

Driver Enable Time to Output Low t

Driver Disable Time from Output Low t

Driver Enable Time from Shutdown to

Output Low

Driver Time to Shutdown t

Receiver Propagation Delay

Receiver Output Skew t

Receiver Enable Time to Output High t

Recei ver D i sab l e Ti m e fr om Outp ut H i g ht

Receiver Wake Time from Shutdown t

Receiver Enable Wake Time from

Shutdown

Recei ver D i sab l e Ti m e fr om Outp ut Low t

Receiver Time to Shutdown t

t

PLHA,

t

PLHB

t

DPLH,

t

DPHL

t

LH,tHLRL

t

SKEWAB

t

SKEWBA

DSKEW

MAX

PDZH

PDHZ

t

PDHS

PDZL

PDLZ

t

PDLS

SHDNRL

t

RPLH

t

RPHL

RSKEWCL

RPZH

RPHZ

RPWAKERL

t

RPSH

RPLZ

SHDNRL

RL = 27Ω, CL = 50pF, Figure 3 60 ns

RL = 54Ω, CL = 50pF, Figure 4 60 ns

= 54Ω, CL = 50pF, Figure 4 25 ns

RL = 54Ω, CL = 50pF,

,

t

SKEWAB

t

SKEWBA

= |t

= |t

PLHA

PLHB

RL = 54Ω, CL = 50pF,

= |t

t

DSKEW

DPLH

RL = 500Ω, CL = 50pF, Figure 5 1200 ns

RL = 500Ω, CL = 50pF, Figure 5 1200 ns

RL = 500Ω, CL = 50pF, Figure 5 4.2 µs

RL = 500Ω, CL = 50pF, Figure 6 1200 ns

RL = 500Ω, CL = 50pF, Figure 6 1200 ns

RL = 500Ω, CL = 50pF, Figure 6 4.2 µs

,

C

RL = 1kΩ, C

= 500Ω, C

= 20pF, V

L

= 20pF, t

= 50p F, Figure 6 800 ns

L

ID

RSKEW

= 20pF, Figure 8 400 ns

L

RL = 1kΩ, CL = 20pF, Figure 8 400 ns

= 1kΩ, CL = 20pF, Figure 8 4.2 µs

RL = 1kΩ, C

= 20pF, Figure 8 400 ns

L

RL = 1kΩ, CL = 20pF, Figure 8 400 ns

= 500Ω, CL = 50pF 800 ns

10 ns

10 ns

- t

- t

- t

PHLB

PHLA

DPHL

|,

|

|

10 Mbps

= 2V, VCM = 0V, Figure 7 85 ns

= |t

RPLH

- t

|15ns

RPHL

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

6 _______________________________________________________________________________________

Typical Operating Characteristics

(VCC= +5V, TA = +25°C, unless otherwise noted.)

NO-LOAD SUPPLY CURRENT

vs. TEMPERATURE

MAX13442-4E toc01

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

1109580655035205-10-25

1

2

3

4

5

6

0

-40 125

DRIVER AND RECEIVER

ENABLED

MAX13443E

DRIVER DISABLED,

RECEIVER ENABLED

NO-LOAD SUPPLY CURRENT

vs. TEMPERATURE

MAX13442-4E toc02

TEMPERATURE (°C)

SUPPLY CURRENT (mA)

1109580655035205-10-25

4

8

12

16

20

24

0

-40 125

DRIVER AND RECEIVER

ENABLED

MAX13442E/MAX13444E

DRIVER DISABLED,

RECEIVER ENABLED

SHUTDOWN SUPPLY CURRENT

vs. TEMPERATURE

MAX13442-4E toc03

TEMPERATURE (°C)

SHUTDOWN SUPPLY CURRENT (μA)

120100806040200-20

0.00001

0.0001

0.001

0.01

0.1

1

10

0.000001

-40

MAX13442E

DI = DE = GND

RE = V

CC

0

10

5

15

30

35

25

20

40

0 1.0 1.5 2.0 2.50.5 3.0 3.5 4.0 4.5 5.0

RECEIVER OUTPUT CURRENT

vs. OUTPUT-LOW VOLTAGE

MAX13442-4E toc04

OUTPUT LOW VOLTAGE (V)

RECEIVER OUTPUT CURRENT (mA)

0

10

5

15

30

35

25

20

40

0 1.0 1.5 2.0 2.50.5 3.0 3.5 4.0 4.5 5.0

RECEIVER OUTPUT CURRENT

vs. OUTPUT-HIGH VOLTAGE

MAX13442-4E toc05

OUTPUT LOW VOLTAGE (V)

RECEIVER OUTPUT CURRENT (mA)

0

1.0

0.5

2.5

2.0

1.5

3.0

3.5

4.5

4.0

5.0

-40 -10 5-25 20 35 50 65 80 95 110 125

RECEIVER OUTPUT VOLTAGE

vs. TEMPERATURE

MAX13442-4E toc06

TEMPERATURE (°C)

RECEIVER OUTPUT VOLTAGE (V)

VOL, I

OUT

= -10mA

VOH, I

OUT

= 10mA

0

40

20

80

60

140

120

100

10 3020 40 50 60 70 80

DRIVER OUTPUT CURRENT

vs. DIFFERENTIAL OUTPUT VOLTAGE

MAX13442-4E toc07

DIFFERENTIAL OUTPUT VOLTAGE (V)

DRIVER OUTPUT CURRENT (mA)

MAX13442E

DI = GND, DE = V

CC

,

VOLTAGE APPLIED

TO OUTPUT A

RL = 54Ω

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

_______________________________________________________________________________________

7

Typical Operating Characteristics (continued)

(VCC= +5V, TA = +25°C, unless otherwise noted.)

0

30

20

10

40

50

60

70

80

90

100

-80 -50-65 -35 -20 -5

DRIVER OUTPUT CURRENT

vs. DIFFERENTIAL OUTPUT VOLTAGE

MAX13442-4E toc08

DIFFERENTIAL OUTPUT VOLTAGE (V)

DRIVER OUTPUT CURRENT (mA)

MAX13442E

DI = GND, DE = V

CC

,

VOLTAGE APPLIED

TO OUTPUT B

RL = 54Ω

0

1.0

0.5

2.0

1.5

3.0

2.5

3.5

-40 -10 5 20-25 35 50 65 80 95 110 125

DIFFERENTIAL OUTPUT VOLTAGE

vs. TEMPERATURE

MAX13442-4E toc09

TEMPERATURE (°C)

DIFFERENTIAL OUTPUT VOLTAGE (V)

RL = 100Ω

RL = 54Ω

MAX13442E

DIFFERENTIAL OUTPUT VOLTAGE

vs. TEMPERATURE

3.5

3.0

2.5

2.0

1.5

1.0

DIFFERENTIAL OUTPUT VOLTAGE (V)

0.5

RL = 100Ω

RL = 54Ω

MAX13443E

0

-40 -10 5 20-25 35 50 65 80 95 110 125

TEMPERATURE (°C)

A, B CURRENT vs. A, B

VOLTAGE (TO GROUND)

DRIVER DISABLED,

RECEIVER ENABLED

NO LOAD

RL = 54Ω

-60 -40

-20

A, B VOLTAGE (V)

MAX13442-4E toc11

MAX13442E

0

40 6020

80

MAX13442-4E toc10

A, B CURRENT (μA)

3200

2800

2400

2000

1600

1200

800

400

0

-400

-800

-1200

-1600

-2000

-80

A, B CURRENT vs. A, B VOLTAGE

(TO GROUND)

2000

DRIVER DISABLED,

1600

RECEIVER ENABLED

1200

800

400

NO LOAD

0

-400

A, B CURRENT (μA)

-800

-1200

-1600

-2000

-60 -40 -30-50 -20 -10 0 10 20 30 40 6050

RL = 54Ω

MAX13443E

A, B VOLTAGE (V)

MAX13442-4E toc12

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

8 _______________________________________________________________________________________

Figure 1. Driver VODand V

OC

Figure 2. Receiver VOHand V

OL

V

CC

V

OM

3V

0V

V

OH

V

OM

V

OM

V

OM

V

OM

V

OL

V

OH

V

OL

50Ω

R

L

C

L

= 50pF

(NOTE 6)

GENERATOR

(NOTE 5)

D

DI

t

PLHA

1.5V

A

B

OUT

S1

DI

1.5V

t

PHLA

t

PHLB

t

PLHB

≈ 1.5V

V

OH

+ V

OL

2

V

OM

=

A

B

2

Test Circuits and Waveforms

Figure 4. Driver Differential Output Delay and Transition Times

Figure 3. Driver Propagation Times

R

L

A

V

D

DI

B

V

CC

OD

2

R

L

V

OC

2

A

V

ID

B

0

RO

R

V

OL

V

OH

I

OL

(+)

I

OH

(-)

1.5V

t

DPLH

90%

50%

10%

t

LH

(A–B)

DI

C

A

DI

D

GENERATOR

(NOTE 5)

50Ω

B

V

CC

L

C

L

R

L

CL = 50pF (NOTE 6)

OUT

1.5V

90%

t

DPHL

3V

0V

≈ 2.0V

50%

10%

≈ -2.0V

t

HL

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

_______________________________________________________________________________________ 9

Figure 6. Driver Enable and Disable Times

Figure 7. Receiver Propagation Delay

Test Circuits and Waveforms (continued)

Figure 5. Driver Enable and Disable Times

A

B

S1

CL = 50pF

(NOTE 6)

=

V

OM

GENERATOR

(NOTE 5)

DI

D0 OR 3V

DE

50Ω

A

B

S1

= 50pF

C

L

(NOTE 6)

GENERATOR

(NOTE 5)

DI

D0 OR 3V

DE

50Ω

3V

A, B

= 500Ω

R

L

+ V

V

OH

OL

≈ 1.5V

2

V

CC

= 500Ω

R

L

A, B

A, B

A, B

DE

DE

t

PDZH

t

PDHS

t

PDZL

t

PDLS

1.5V

1.5V

V

OM

V

OM

1.5V

1.5V

t

PDHZ

t

PDLZ

0.25V

0.25V

0V

V

OH

0V

3V

0V

V

CC

V

OL

A

V

ID

GENERATOR

(NOTE 5)

1.0V

0V

50Ω

R

B

R

O

= 20pF

C

L

(NOTE 6)

(A–B)

1.0V

t

RPLH

V

RO

OM

1.0V

t

RPHL

V

OM

2.0V

0V

V

0V

CC

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

10 ______________________________________________________________________________________

Figure 8. Receiver Enable and Disable Times

Test Circuits and Waveforms (continued)

Note 5: The input pulse is supplied by a generator with the following characteristics: f = 5MHz, 50% duty cycle; tr≤ 6ns; Z0= 50Ω.

Note 6: C

L

includes probe and stray capacitance.

+1.5V

-1.5V

S3

GENERATOR

(NOTE 5)

A

V

ID

B

R

50Ω

R

O

= 20pF

C

L

(NOTE 6)

1kΩ

S1

S2

V

CC

3V

0V

V

0V

3V

0V

V

0V

OH

OH

S1 OPEN

S2 CLOSED

= 1.5V

V

S3

S1 OPEN

S2 CLOSED

V

= 1.5V

S3

RE

t

RPZL

t

RPSL

RO

RE

RO

1.5V

t

RPLZ

0.5V

1.5V

1.5V

RE

t

RPZH

t

RPSH

t

RPWAKE

RO

RE

RO

0.5V

1.5V

t

RPHZ

1.5V

1.5V

3V

0V

V

CC

V

OL

3V

0V

V

CC

V

OL

S1 CLOSED

S2 OPEN

V

S1 CLOSED

S2 OPEN

V

= -1.5V

S3

= -1.5V

S3

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

______________________________________________________________________________________ 11

Pin Description

PIN

MAX13442E

MAX13443E

1 1 RO

2 2 RE Receiver Output Enable. Pull RE low to enable RO.

3 — DE

4 — DI

5 5 GND Ground

6 6 A Noninverting Receiver Input/Driver Output

7 7 B Inverting Receiver Input/Driver Output

8 8 V

— 3 DE

MAX13444E

NAME FUNCTION

Receiver Output. If the receiver is enabled and (V

- VB) -200mV, RO = low.

A

to GND with a 0.1μF ceramic capacitor. For full ESD

CC

to GND with 1μF ceramic capacitor.

CC

CC

RO = high; if (V

Driver Output Enable. Force DE high to enable driver. Pull DE low

to three-state the driver output. Drive RE high and pull DE low to

enter low-power shutdown mode.

Driver Input. A logic-low on DI forces the noninverting output low

and the in verting output high. A logic-high on

DI forces the nonin verting output h igh and the in verting output

low.

Positive Supply, VCC = +4.75V to +5.25V. For normal operation,

bypass V

protection, bypass V

Driver Output Enable. Pull DE low to enable the outputs. Force DE

high to three- state the outputs. Drive RE and DE high to enter lowpower shutdown mode.

- VB) -50mV,

A

J1708 Input. A logic-low on TXD forces outputs A and B to the

— 4 TXD

dominant state. A logic-high on TXD forces outputs A and B to

the recessi ve state.

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

12 ______________________________________________________________________________________

Table 3. MAX13442E/MAX13443E

(RS-485/RS-422)

X = Don’t care.

Table 4. MAX13444E (RS-485/RS-422)

X = Don’t care.

Function Tables

Table 1. MAX13442E/MAX13443E

(RS-485/RS-422)

X = Don’t care.

Table 2. MAX13444E (J1708) Application

TRANSMITTING

INPUTS OUTPUTS

RE DE DI A B

0 0 X High-Z High-Z

01001

01110

1 0 X Shutdown Shutdown

11001

11110

TRANSMITTING

INPUTS OUTPUTS CONDITIONS

TXD DE AB —

0 1 High-Z High-Z —

1 1 High-Z High-Z —

0 0 0 1 Dominant state

1 0 High-Z High-Z Recessive state

RECEIVING

INPUTS OUTPUTS

RE DE (VA - VB)RO

0 X -0.05V 1

0 X -0.2V 0

0 X Open/shorted 1

1 1 X High-Z

1 0 X Shutdown

RECEIVING

INPUTS OUTPUTS

RE DE (VA - VB)RO

0 X -0.05V 1

0 X -0.2V 0

0 X Open/shorted 1

1 0 X H igh-Z

1 1 X Shutdown

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

______________________________________________________________________________________ 13

Detailed Description

The MAX13442E/MAX13443E/MAX13444E fault-protected transceivers for RS-485/RS-422 and J1708 communication contain one driver and one receiver. These

devices feature fail-safe circuitry, which guarantees a

logic-high receiver output when the receiver inputs are

open or shorted, or when they are connected to a terminated transmission line with all drivers disabled (see the

True Fail-Safe

section). All devices have a hot-swap input

structure that prevents disturbances on the differential

signal lines when a circuit board is plugged into a hot

backplane (see the

Hot-Swap Capability

section). The

MAX13442E/MAX13444E feature a reduced slew-rate driver that minimizes EMI and reduces reflections caused

by improperly terminated cables, allowing error-free data

transmission up to 250kbps (see the

Reduced EMI and

Reflections

section). The MAX13443E driver is not slew-

rate limited, allowing transmit speeds up to 10Mbps.

Driver

The driver accepts a single-ended, logic-level input

(DI) and transfers it to a differential, RS-485/RS-422

level output (A and B). Deasserting the driver enable

places the driver outputs (A and B) into a high-impedance state.

Receiver

The receiver accepts a differential, RS-485/RS-422

level input (A and B), and transfers it to a single-ended,

logic-level output (RO). Deasserting the receiver enable

places the receiver inputs (A and B) into a high-impedance state (see Tables 1–4).

Low-Power Shutdown

The MAX13442E/MAX13443E/MAX13444E offer a lowpower shutdown mode. Force DE low and RE high to

shut down the MAX13442E/MAX13443E. Force DE and

RE high to shut down the MAX13444E. A time delay of

50ns prevents the device from accidentally entering

shutdown due to logic skews when switching between

transmit and receive modes. Holding DE low and RE

high for at least 800ns guarantees that the

MAX13442E/MAX13443E enter shutdown. In shutdown,

the devices consume a maximum 20µA supply current.

±

80V Fault Protection

The driver outputs/receiver inputs of RS-485 devices in

industrial network applications often experience voltage

faults resulting from shorts to the power grid that exceed

the -7V to +12V range specified in the EIA/TIA-485 standard. In these applications, ordinary RS-485 devices

(typical absolute maximum -8V to +12.5V) require costly

external protection devices. To reduce system complexity and eliminate this need for external protection, the dri-

ver outputs/receiver inputs of the MAX13442E/

MAX13444E withstand voltage faults up to ±80V (±60V

for the MAX13443E) with respect to ground without damage. Protection is guaranteed regardless whether the

device is active, shut down, or without power.

True Fail-Safe

The MAX13442E/MAX13443E/MAX13444E use a

-50mV to -200mV differential input threshold to ensure

true fail-safe receiver inputs. This threshold guarantees

the receiver outputs a logic-high for shorted, open, or

idle data lines. The -50mV to -200mV threshold complies with the ±200mV threshold EIA/TIA-485 standard.

±15kV ESD Protection

As with all Maxim devices, ESD-protection structures

are incorporated on all pins to protect against ESD

encountered during handling and assembly. The

MAX13442E/MAX13443E/MAX13444E receiver inputs/

driver outputs (A, B) have extra protection against static electricity found in normal operation. Maxim’s engineers have developed state-of-the-art structures to

protect these pins against ±15kV ESD without damage.

After an ESD event, the MAX13442E/MAX13443E/

MAX13444E continue working without latchup.

ESD protection can be tested in several ways. The

receiver inputs are characterized for protection to

±15kV using the Human Body Model.

ESD Test Conditions

ESD performance depends on a number of conditions.

Contact Maxim for a reliability report that documents

test setup, methodology, and results.

Human Body Model

Figure 9a shows the Human Body Model, and Figure

9b shows the current waveform it generates when discharged into a low impedance. This model consists of

a 100pF capacitor charged to the ESD voltage of interest, which is then discharged into the device through a

1.5kΩ resistor.

Driver Output Protection

Two mechanisms prevent excessive output current and

power dissipation caused by faults or bus contention.

The first, a foldback current limit on the driver output

stage, provides immediate protection against short circuits over the whole common-mode voltage range. The

second, a thermal shutdown circuit, forces the driver outputs into a high-impedance state if the die temperature

exceeds +160°C. Normal operation resumes when the

die temperature cools to +140°C, resulting in a pulsed

output during continuous short-circuit conditions.

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

14 ______________________________________________________________________________________

Figure 10. Simplified Structure of the Driver Enable Pin (DE)

Hot-Swap Capability

Hot-Swap Inputs

Inserting circuit boards into a hot, or powered, backplane may cause voltage transients on DE, RE, and

receiver inputs A and B that can lead to data errors. For

example, upon initial circuit board insertion, the processor undergoes a power-up sequence. During this period,

the high-impedance state of the output drivers makes

them unable to drive the MAX13442E/MAX13443E/

MAX13444E enable inputs to a defined logic level.

Meanwhile, leakage currents of up to 10µA from the

high-impedance output, or capacitively coupled noise

from VCCor GND, could cause an input to drift to an

incorrect logic state. To prevent such a condition from

occurring, the MAX13442E/MAX13443E/MAX13444E

feature hot-swap input circuitry on DE, and RE to guard

against unwanted driver activation during hot-swap situations. The MAX13444E has hot-swap input circuitry

only on RE. When V

CC

rises, an internal pulldown (or

pullup for RE) circuit holds DE low for at least 10µs, and

until the current into DE exceeds 200µA. After the initial

power-up sequence, the pulldown circuit becomes

transparent, resetting the hot-swap tolerable input.

Hot-Swap Input Circuitry

At the driver-enable input (DE), there are two NMOS

devices, M1 and M2 (Figure 10). When VCCramps from

zero, an internal 15µs timer turns on M2 and sets the

SR latch, which also turns on M1. Transistors M2, a

2mA current sink, and M1, a 100µA current sink, pull

DE to GND through a 5.6kΩ resistor. M2 pulls DE to the

disabled state against an external parasitic capacitance up to 100pF that may drive DE high. After 15µs,

the timer deactivates M2 while M1 remains on, holding

DE low against three-state leakage currents that may

drive DE high. M1 remains on until an external current

source overcomes the required input current. At this

time, the SR latch resets M1 and turns off. When M1

turns off, DE reverts to a standard, high-impedance

CMOS input. Whenever VCCdrops below 1V, the input

is reset.

A complementary circuit for RE uses two PMOS

devices to pull RE to VCC.

CHARGE-CURRENT-

LIMIT RESISTOR

DISCHARGE

RESISTANCE

STORAGE

CAPACITOR

C

s

100pF

R

C

1MΩ

R

D

1.5kΩ

HIGH-

VOLTAGE

DC

SOURCE

DEVICE

UNDER

TEST

Figure 9a. Human Body ESD Test Model

IP 100%

90%

36.8%

t

RL

TIME

t

DL

CURRENT WAVEFORM

PEAK-TO-PEAK RINGING

(NOT DRAWN TO SCALE)

I

r

10%

0

0

AMPERES

Figure 9b. Human Body Model Current Waveform

V

CC

TIMER

DE

(HOT SWAP)

15μs

TIMER

5.6kΩ

100μA

M1 M2

2mA

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

______________________________________________________________________________________ 15

Applications Information

128 Transceivers on the Bus

The MAX13442E/MAX13443E/MAX13444E transceivers

1/4-unit-load receiver input impedance (48kΩ) allows

up to 128 transceivers connected in parallel on one

communication line. Connect any combination of these

devices, and/or other RS-485 devices, for a maximum

of 32-unit loads to the line.

Reduced EMI and Reflections

The MAX13442E/MAX13444E are slew-rate limited,

minimizing EMI and reducing reflections caused by

improperly terminated cables. Figure 11 shows the driver output waveform and its Fourier analysis of a

125kHz signal transmitted by a MAX13443E. High-frequency harmonic components with large amplitudes

are evident.

Figure 12 shows the same signal displayed for the

MAX13442E transmitting under the same conditions.

Figure 12’s high-frequency harmonic components are

much lower in amplitude, compared with Figure 11’s,

and the potential for EMI is significantly reduced.

In general, a transmitter’s rise time relates directly to

the length of an unterminated stub, which can be driven

with only minor waveform reflections. The following

equation expresses this relationship conservatively:

length = t

RISE

/ (10 x 1.5ns/ft)

where t

RISE

is the transmitter’s rise time.

For example, the MAX13442E’s rise time is typically

800ns, which results in excellent waveforms with a stub

length up to 53ft. A system can work well with longer

unterminated stubs, even with severe reflections, if the

waveform settles out before the UART samples them.

RS-485 Applications

The MAX13442E/MAX13443E/MAX13444E transceivers

provide bidirectional data communications on multipoint bus transmission lines. Figure 13 shows a typical

network application circuit. The RS-485 standard covers line lengths up to 4000ft. To minimize reflections

and reduce data errors, terminate the signal line at both

ends in its characteristic impedance, and keep stub

lengths off the main line as short as possible.

Figure 11. Driver Output Waveform and FFT Plot of the

MAX13443E Transmitting a 125kHz Signal

Figure 12. Driver Output Waveform and FFT Plot of the

MAX13442E Transmitting a 125kHz Signal

20dB/div

2V/div

5.00MHz500kHz/div0

20dB/div

2V/div

5.00MHz500kHz/div0

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

16 ______________________________________________________________________________________

J1708 Applications

The MAX13444E is designed for J1708 applications. To

configure the MAX13444E, connect DE and RE to GND.

Connect the signal to be transmitted to TXD. Terminate

the bus with the load circuit as shown in Figure 14. The

drivers used by SAE J1708 are used in a dominantmode application. DE is active low; a high input on DE

places the outputs in high impedance. When the driver is

disabled (TXD high or DE high), the bus is pulled high by

external bias resistors R1 and R2. Therefore, a logic-level

high is encoded as recessive. When all transceivers are

idle in this configuration, all receivers output logic-high

because of the pullup resistor on A and pulldown resistor

on B. R1 and R2 provide the bias for the recessive state.

C1 and C2 combine to form a lowpass filter, effective for

reducing FM interference. R2, C1, R4, and C2 combine

to form a 1.6MHz lowpass filter, effective for reducing

AM interference. Because the bus is unterminated, at

high frequencies, R3 and R4 perform a pseudotermination. This makes the implementation more flexible, as no

specific termination nodes are required at the ends of

the bus.

Figure 13. MAX13442E/MAX13443E Typical RS-485 Network

120Ω 120Ω

DI

D

DE

RO

RE

R

MAX13442E

MAX13443E

B

A

BB

D

B

D

AA

R

D

R

A

R

DE

DI

RO

RE

DI RO DE

DE

DI

RO

RERE

MAX13442E/MAX13443E/MAX13444E

R1

4.7kΩ

R3

47Ω

C1

2.2nF

C2

2.2nF

R2

4.7kΩ

RO

R

X

T

X

R4

47Ω

J1708 BUS

A

B

TXD

D

R

DE

RE

MAX13444E

V

CC

Figure 14. J1708 Application Circuit (See Tables 2 and 4)

Chip Information

PROCESS: BiCMOS

Package Information

For the latest package outline information and land patterns

(footprints), go to www.maxim-ic.com/packages

. Note that a

“+”, “#”, or “-” in the package code indicates RoHS status only.

Package drawings may show a different suffix character, but

the drawing pertains to the package regardless of RoHS status.

1

2

3

4

8

5

V

CC

GND

TXD

DE

RE

RO

R

D

R

T

R

T

7

6

D

R

DE

RE

TXD

RO

A

B

1

2

3

4

8

7

6

5

V

CC

B

A

GND

TXD

DE

RE

RO

SO SO

R

D

B

A

MAX13444E

+

+

Pin Configurations and Typical Operating Circuits (continued)

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

______________________________________________________________________________________ 17

PACKAGE

TYPE

PACKAGE

CODE

OUTLINE

NO.

LAND

PATTERN NO.

8 SO S8+4

21-0041 90-0096

MAX13442E/MAX13443E/MAX13444E

±15kV ESD-Protected, ±80V Fault-Protected,

Fail-Safe RS-485/J1708 Transceivers

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are

implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

18

____________________Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2011 Maxim Integrated Products Maxim is a registered trademark of Maxim Integrated Products, Inc.

Revision History

REVISION

NUMBER

0 10/05 Initial release —

1 3/06

2 11/10

3 3/11

REVISION

DATE

DESCRIPTION

Corrected the part numbers in the conditions for V

Characteristics table; corrected the A, B current unit s from mA to μA for the A, B

Current vs. A, B Voltage (to Ground) graphs in the Typical Operating Characteristics

section

Added lead(Pb)-free parts to the Ordering Information table; added the so ldering

temperature to the Absolute Maximum Ratings section; updated Table 2 output s

Added an automotive qualified part to the Ordering Information; added the Package

Thermal Characteristics section

in the DC Electrical

OC

PAGES

CHANGED

1, 2, 12

2, 7

1, 2

Loading...

Loading...