24

23

22

21

20

19

18

17

1

2

3

4

5

6

7

8

AGND1

AGND2

AV

DD2

AGND3CH2

CH1

CH0

AV

DD1

TOP VIEW

REF

REFCAP

DV

DD

DV

DDO

CH6

CH5

CH4

CH3

16

15

14

13

9

10

11

12

DGND

DGNDO

DOUT

SCLKSSTRB

DIN

CS

CH7

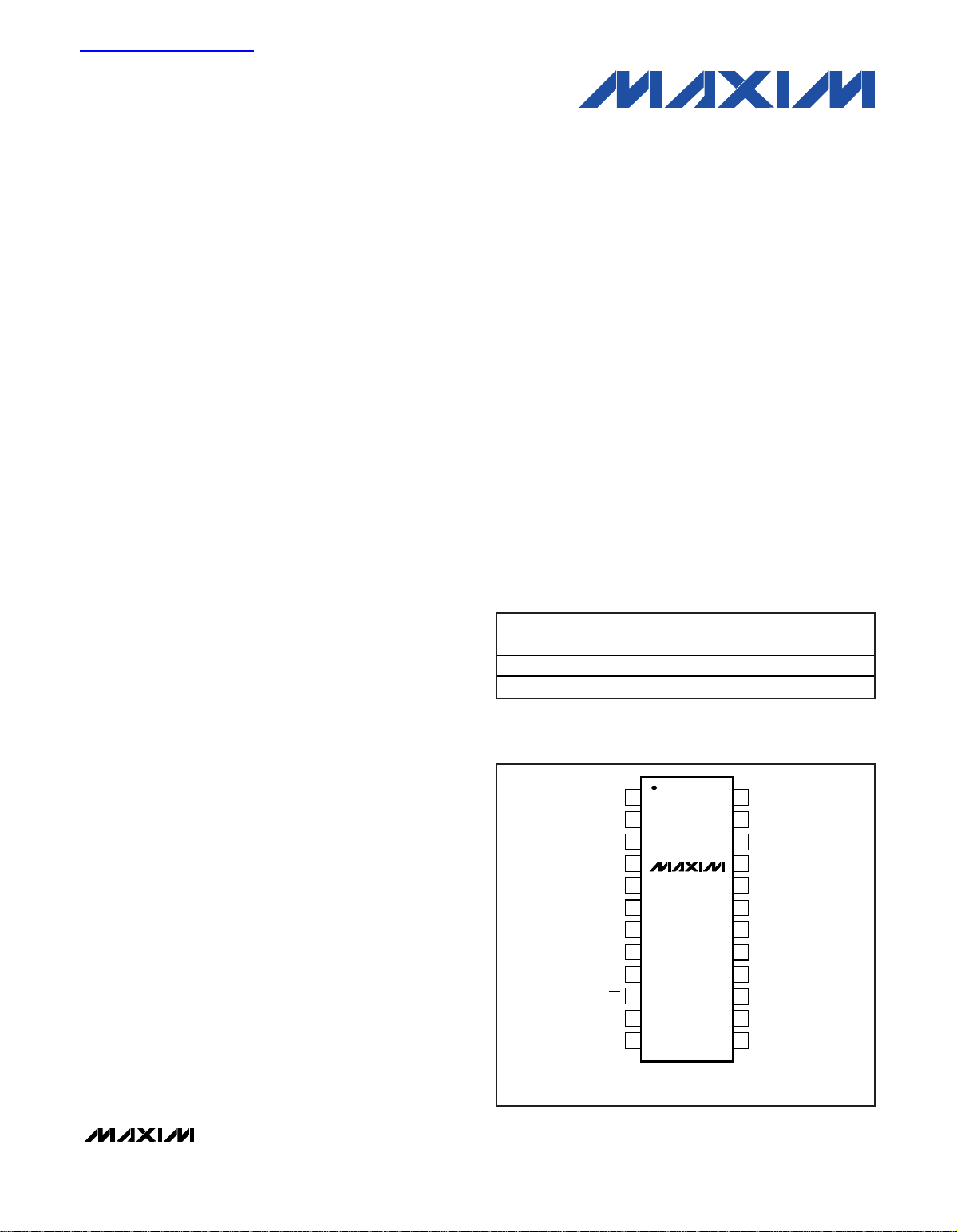

TSSOP

MAX1034

查询MAX1032供应商

19-3574; Rev 0; 5/05

____________________________________概述

MAX1034/MAX1035多量程、低功耗、14位逐次逼近型模

数转换器 (ADC),采用+5V单电源供电,转换速率高达

115ksps。独立的数字电源允许通过SPITM/QSPITM/MICROWIRE

TM

兼容的串行接口与2.7V至5.25V系统连接。局部关断模式

可将电源电流降至 1.3mA (典型值)。完全关断模式则可将

电源电流降至 1µA (典型值)。

MAX1034 提供8路 (单端) 或4路 (真差分) 模拟输入通道。

MAX1035 则具有4路 (单端) 或2路 (真差分) 模拟输入通

道。每个模拟输入通道都可通过软件独立编程设置为7种

单端输入范围 (0至+V

至0、±V

(±V

REF

REF

/2 、±V

/4、±V

REF

/2、-V

REF

/2和±V

REF

和±2 x V

REF

REF

REF

)。

/2至0、0至+V

REF

、-V

) 和3种差分输入范围

REF

片上+4.096V基准可实现小巧、便利的ADC解决方案。

MAX1034/MAX1035还可接受3.800V至4.136V之间的外部

基准。

MAX1034采用24引脚TSSOP封装,MAX1035采用 20 引脚

TSSOP封装。每款器件都可工作在-40°C至+85°C温度范

围内。

____________________________________应用

工业控制系统

数据采集系统

航空电子

机器人技术

8/4通道,±V

REF

多量程输入、

串行14位ADC

____________________________________特性

♦ 每个通道的输入范围可通过软件编程设置

♦ 单端输入范围

0至+V

-V

REF

/2、-V

REF

至0、±V

♦ 差分输入范围

±V

/2、±V

REF

♦ 8路单端或4路差分模拟输入 (MAX1034)

♦ 4路单端或2路差分模拟输入 (MAX1035)

♦ ±6V过压容限输入

♦ 内部或外部基准

♦ 115ksps最高采样速率

♦ +5V单电源供电

♦ 20/24引脚TSSOP封装

________________________________定购信息

PART TEMP RANGE

MAX1034EUG* -40°C to +85°C 24 TSSOP 8

MAX1035EUP -40°C to +85°C 20 TSSOP 4

*

未来产品——供货信息请与厂商联系。

________________________________引脚配置

REF

REF

REF

/4、±V

和±2 x V

/2至0、0至+V

/2和±V

REF

REF

PINPACKAGE

REF

REF

、

CHANNELS

MAX1034/MAX1035

SPI和 QSPI是Motorola, Inc.的商标。

MICROWIRE是 National Semiconductor Corp. 的商标。

本文是Maxim 正式英文资料的译文,Maxim不对翻译中存在的差异或由此产生的错误负责。请注意译文中可能存在文字组织或

翻译错误,如需确认任何词语的准确性,请参考 Maxim提供的英文版资料。

索取免费样品和最新版的数据资料,请访问Maxim的主页:www.maxim-ic.com.cn。

________________________________________________________________ Maxim Integrated Products 1

引脚配置 (续) 在数据资料的最后部分给出。

8/4通道,±V

REF

多量程输入、

串行14位ADC

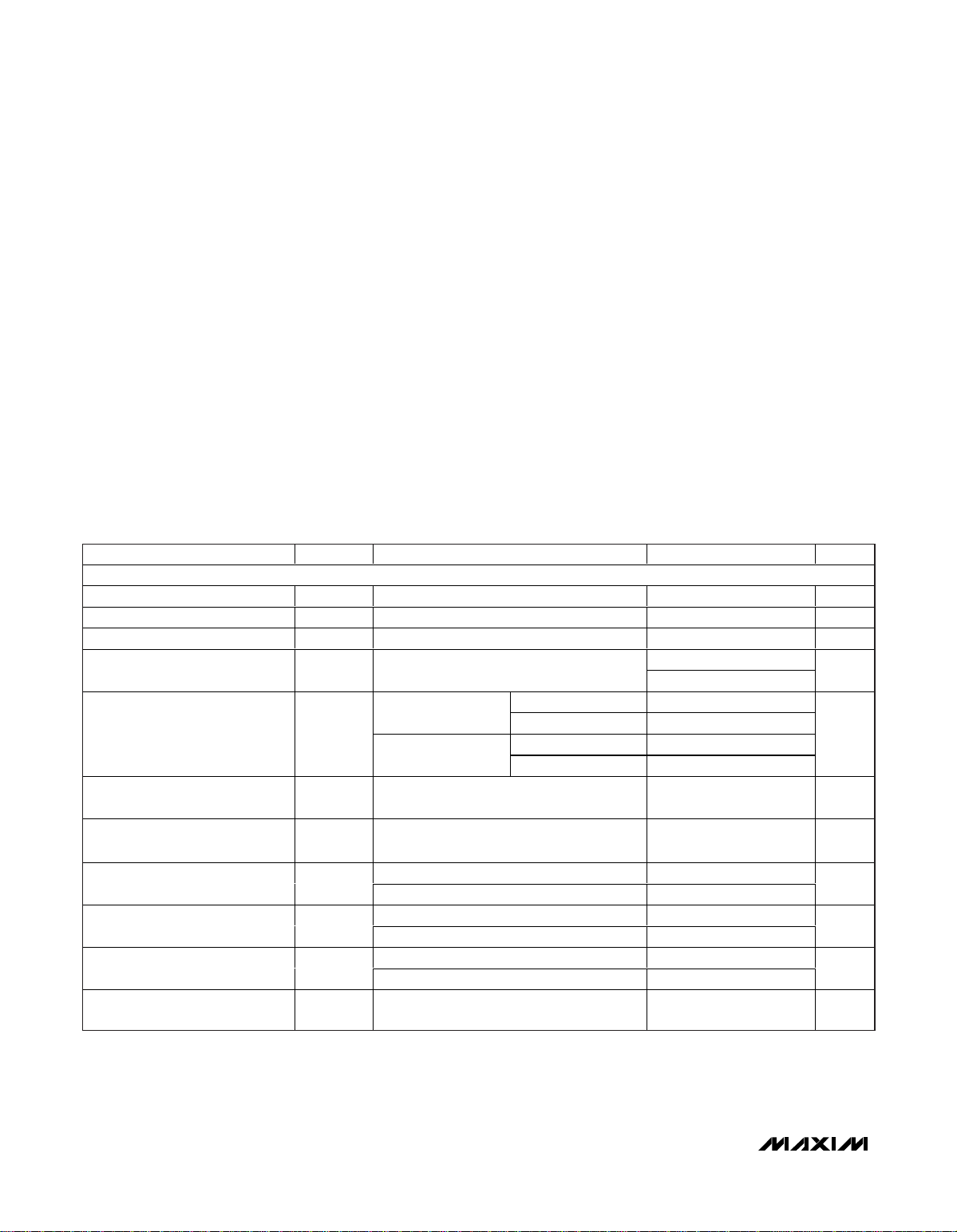

ABSOLUTE MAXIMUM RATINGS

AV

to AGND1 ....................................................-0.3V to +6V

DD1

AV

to AGND2 ....................................................-0.3V to +6V

DD2

DVDDto DGND ........................................................-0.3V to +6V

DV

DVDDto DV

DVDD, DV

AV

DGND, DGNDO, AGND3, AGND2 to AGND1 ......-0.3V to +0.3V

CS, SCLK, DIN, DOUT, SSTRB to

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

ELECTRICAL CHARACTERISTICS

MAX1034/MAX1035

(AV

clock mode, V

= 50pF, C

to DGNDO ..................................................-0.3V to +6V

DDO

, DVDD, DV

DD1

DGNDO ............................................-0.3V to (DV

= AV

DD1

DC ACCURACY (Notes 1, 2)

Resolution 14 Bits

Integral Nonlinearity INL ±0.25 ±1 LSB

Differential Nonlinearity DNL No missing codes ±1 LSB

Transition Noise External or internal reference

Offset Error

Channel-to-Channel Gain

Matching

Channel-to-Channel Offset Error

Matching

Offset Temperature Coefficient

Gain Error

Gain Temperature Coefficient

Unipolar Endpoint Overlap

......................................................-0.3V to +6V

DDO

to AV

DDO

= DVDD= DV

DD2

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

SSTRB

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

........................................-0.3V to +6V

DD1

DDO

to AV

..........................-0.3V to +6V

DD2

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

+ 0.3V)

DDO

Single-ended inputs

Differential inputs

(Note 3)

Unipolar or bipolar 0.025 %FSR

Unipolar or bipolar 1.0 mV

Unipolar 10

Bipolar 5

Unipolar ±0.5

Bipolar ±0.3

Unipolar 1.5

Bipolar 1.0

Negative unipolar full scale to positive

unipolar zero-scale

CH0–CH7 to AGND1 ...................................................-6V to +6V

REF, REFCAP to AGND1.......................-0.3V to (AV

Continuous Current (any pin) ...........................................±50mA

Continuous Power Dissipation (T

20-Pin TSSOP (derate 11mW/°C above +70°C) ..........879mW

24-Pin TSSOP (derate 12.2mW/°C above +70°C) .......976mW

Operating Temperature Range ...........................-40°C to +85°C

Junction Temperature .....................................................+150°C

Storage Temperature Range .............................-65°C to +150°C

Lead Temperature (soldering, 10s) .................................+300°C

, maximum single-ended bipolar input range (±V

DD1

Unipolar 0 ±10

Bipolar -1.0 ±10

Unipolar 0 ±20

Bipolar -2 ±20

CLK

= +70°C)

A

= 3.5MHz (50% duty cycle), external

0.5

2

0 5 LSB

DD1

REF

), C

+ 0.3V)

DOUT

LSB

RMS

mV

ppm/°C

%FSR

ppm/°C

2 _______________________________________________________________________________________

8/4通道,±V

REF

多量程输入、

串行14位ADC

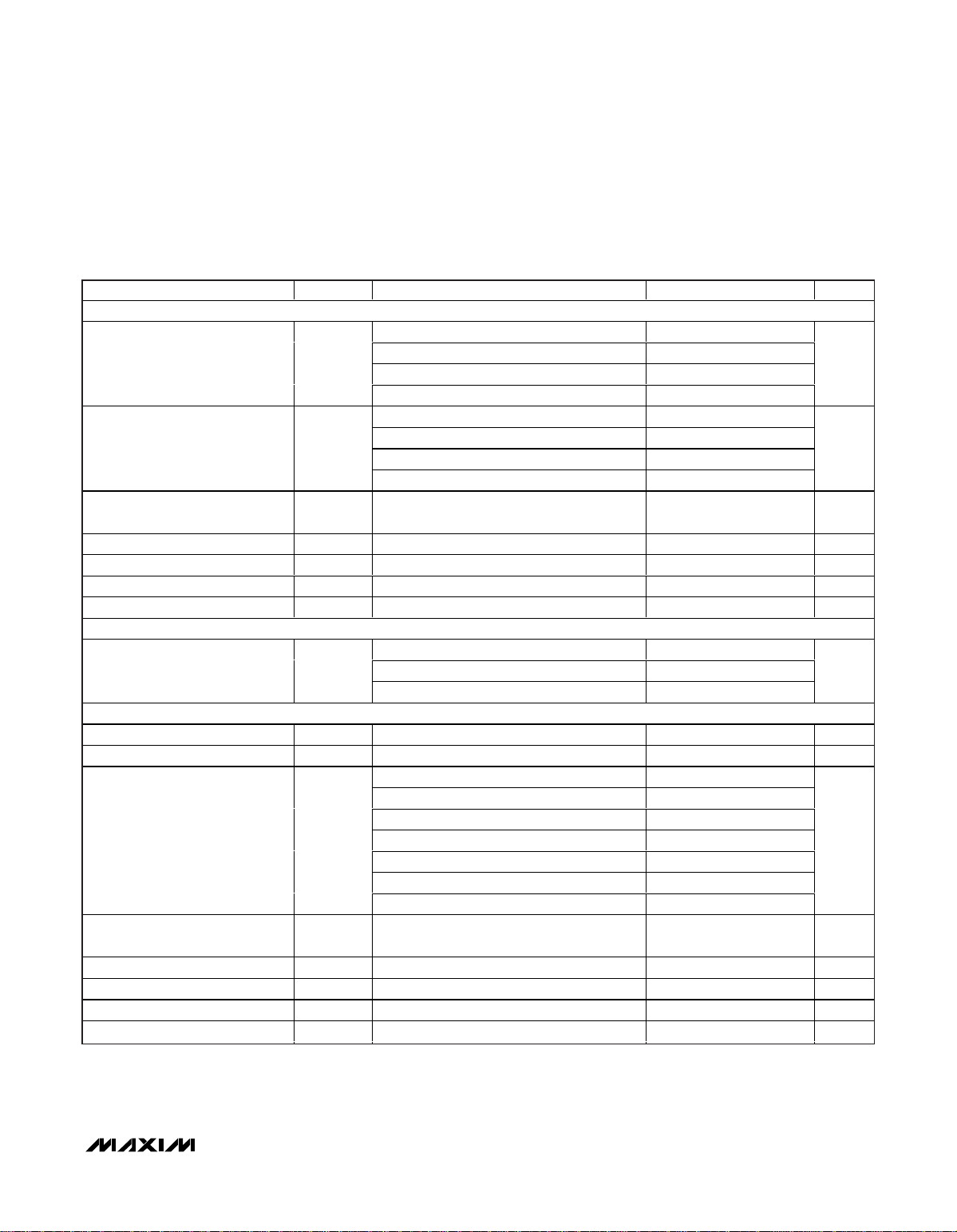

ELECTRICAL CHARACTERISTICS (continued)

(AV

= AV

DD1

clock mode, V

= 50pF, C

DYNAMIC SPECIFICATIONS f

Signal-to-Noise Plus Distortion SINAD

Signal-to-Noise Ratio SNR

Total Harmonic Distortion

(Up to the 5th Harmonic)

Spurious-Free Dynamic Range SFDR 92 99 dB

Aperture Delay t

Aperture Jitter t

Channel-to-Channel Isolation 105 dB

CONVERSION RATE

ANALOG INPUTS (CH0–CH3 MAX1035, CH0–CH7 MAX1034, AGND1)

Small-Signal Bandwidth All input ranges, VIN = 100mV

Full-Power Bandwidth All input ranges, VIN = 4V

Input Voltage Range (Table 6) V

True-Differential Analog

Common-Mode Voltage Range

Common-Mode Rejection Ratio CMRR DIF/SGL = 1, input voltage range = ±V

Input Current I

Input Capacitance C

Input Resistance R

= DVDD= DV

DD2

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

SSTRB

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

IN(SINE-WAVE)

SAMPLE

V

= 5kHz, VIN = FSR - 0.05dB, f

Differential inputs, FSR = 2 x V

Single-ended inputs, FSR = V

Single-ended inputs, FSR = V

Single-ended inputs, FSR = V

Differential inputs, FSR = 2 x V

Single-ended inputs, FSR = V

Single-ended inputs, FSR = V

Single-ended inputs, FSR = V

THD -98 dB

AD

AJ

CH_

CMDR

CH_

CH_

CH_

Figure 21 15 ns

Figure 21 100 ps

External clock mode, Figure 2 114

External acquisition mode, Figure 3 84Byte-Wide Throughput Rate f

Internal clock mode, Figure 4 106

R[2:1] = 001 -V

R[2:1] = 010 -V

R[2:1] = 011 0 +V

R[2:1] = 100 -V

R[2:1] = 101 -V

R[2:1] = 110 0 +V

R[2:1] = 111 -V

DIF/SGL = 1 -4.75 +5.50 V

-V

< V

CH_

< +V

REF

, maximum single-ended bipolar input range (±V

DD1

SAMPLE

REF

REF

REF

REF

REF

REF

REF

REF

P-P

(Note 2) 700 kHz

P-P

REF

= 3.5MHz (50% duty cycle), external

CLK

= 130ksps (Notes 1, 2)

84.5

84

/ 2 82.5

/ 4 79 80.5

84.5

84

/ 2 82.5

/ 4 80.5

(Note 2) 2 MHz

/4 +V

REF

/2 0

REF

/2 +V

REF

REF

REF

/4 75 dB

REF

-1500 +650 µA

+V

5pF

6kΩ

REF

REF

REF

0

REF

REF

REF

/4

/2

/2

), C

ksps

MAX1034/MAX1035

DOUT

dB

dB

V

_______________________________________________________________________________________ 3

8/4通道,±V

REF

多量程输入、

串行14位ADC

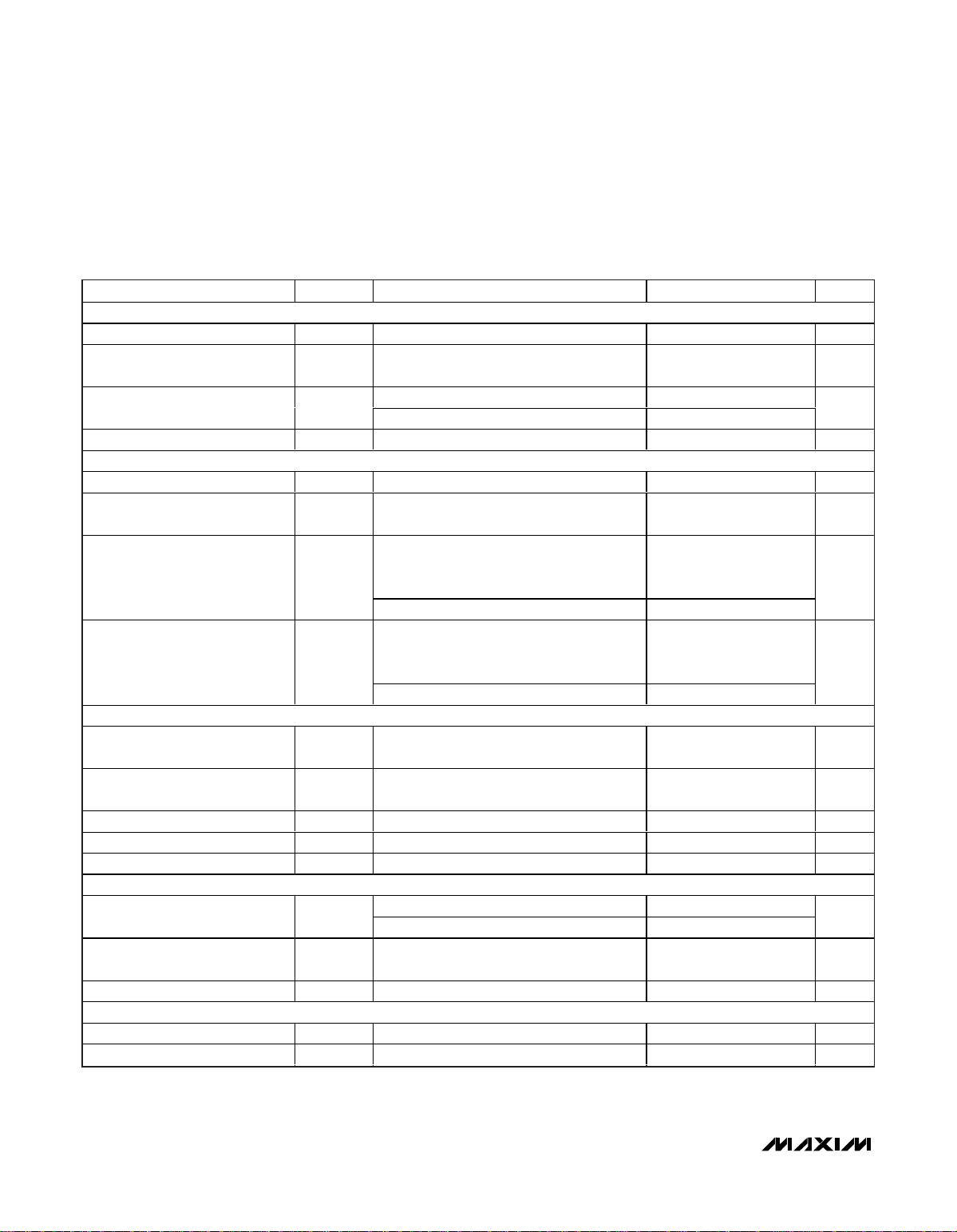

ELECTRICAL CHARACTERISTICS (continued)

(AV

= AV

DD1

clock mode, V

= 50pF, C

INTERNAL REFERENCE (Bypass REFCAP with 0.1µF to AGND1 and REF with 1.0µF to AGND1)

Reference Output Voltage V

Reference Temperature

Coefficient

Reference Short-Circuit Current I

Reference Load Regulation I

EXTERNAL REFERENCE (REFCAP = AVDD)

MAX1034/MAX1035

Reference Input Voltage Range V

REFCAP Buffer Disable

Threshold

Reference Input Current I

Reference Input Resistance R

DIGITAL INPUTS (DIN, SCLK, CS)

Input High Voltage V

Input Low Voltage V

Input Hysteresis V

Input Leakage Current I

Input Capacitance C

DIGITAL OUTPUTS (DOUT, SSTRB)

Output Low Voltage V

Output High Voltage V

DOUT Tri-State Leakage Current I

POWER REQUIREMENTS (AV

Analog Supply Voltage AV

Digital Supply Voltage DV

= DVDD= DV

DD2

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

SSTRB

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

and AGND1, AV

DD1

REF

TC

REF

REFSC

REF

V

RCTH

REF

REF

IH

IL

HYST

IN

IN

OL

OH

DDO

DD1

DD

REF shorted to AGND1 10

REF shorted to AV

= 0 to 0.5mA 0.1 10 mV

REF

(Note 4)

V

= +4.096V, external clock mode,

REF

external acquisition mode, internal clock

mode, or partial power-down mode

V

= +4.096V, full power-down mode ±0.1 ±10

REF

External clock mode, external acquisition

mode, internal clock mode, or partial

power-down mode

Full power-down mode 40

VIN = 0 to DV

DV

DDO

DV

DDO

I

SOURCE

CS = DV

DD2

DDO

= 4.75V, I

= 2.7V, I

= 0.5mA

DDO

and AGND2, DVDD and DGND, DV

, maximum single-ended bipolar input range (±V

DD1

DD

= 10mA 0.4

SINK

= 5mA 0.4

SINK

= 3.5MHz (50% duty cycle), external

CLK

4.056 4.096 4.136 V

±30 ppm/°C

-1

3.800 4.136 V

AV

DD1

- 0.4

90 200

20 45

0.7 x

DV

DDO

0.2 V

-10 +10 µA

10 pF

DV

DDO

- 0.4

-10 +10 µA

and DGNDO)

DDO

4.75 5.25 V

4.75 5.25 V

AV

- 0.1

0.3 x

DV

REF

DD1

DDO

), C

DOUT

mA

V

µA

kΩ

V

V

V

V

4 _______________________________________________________________________________________

8/4通道,±V

REF

多量程输入、

串行14位ADC

ELECTRICAL CHARACTERISTICS (continued)

(AV

= AV

DD1

clock mode, V

= 50pF, C

Preamplifier Supply Voltage AV

Digital I/O Supply Voltage DV

AV

Supply Current I

DD1

DVDD Supply Current I

AV

Supply Current I

DD2

DV

Supply Current I

DDO

Total Supply Current

Power-Supply Rejection Ratio PSRR All analog input ranges ±0.125 LSB

TIMING CHARACTERISTICS (Figures 15 and 16)

SCLK Period t

DIN to SCLK Setup t

DIN to SCLK Hold t

SCLK Fall to DOUT Valid t

CS Fall to DOUT Enable t

CS Rise to DOUT Disable t

CS Fall to SCLK Rise Setup t

CS High Minimum Pulse Width t

SCLK Fall to CS Rise Hold t

SSTRB Rise to CS Fall Setup 40 ns

DOUT Rise/Fall Time CL = 50pF 10 ns

SSTRB Rise/Fall Time CL = 50pF 10 ns

= DVDD= DV

DD2

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

SSTRB

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

DD2

DDO

AVDD1

DVDD

AVDD2

DVDDO

CP

CH

CL

DS

DH

DO

DV

TR

CSS

CSPW

CSH

External clock mode,

external acquisition

mode, or internal

clock mode

External clock mode, external acquisition

mode, or internal clock mode

External clock mode, external acquisition

mode, or internal clock mode

External clock mode, external acquisition

mode, or internal clock mode

Partial power-down mode 1.3 mA

Full power-down mode 1 µA

External clock mode 272 62

External acquisition mode 228 62

Internal clock mode 100 83

External clock mode 109

External acquisition mode 92SCLK High Pulse Width (Note 5) t

Internal clock mode 40

External clock mode 109

External acquisition mode 92SCLK Low Pulse Width (Note 5) t

Internal clock mode 40

, maximum single-ended bipolar input range (±V

DD1

Internal reference 3 3.5

External reference 2.5 3

= 3.5MHz (50% duty cycle), external

CLK

4.75 5.25 V

2.70 5.25 V

0.9 2 mA

17.5 25 mA

0.2 1 mA

40 ns

0ns

40 ns

40 ns

0ns

), C

REF

40 ns

40 ns

40 ns

MAX1034/MAX1035

DOUT

mA

µs

ns

ns

_______________________________________________________________________________________ 5

8/4通道,±V

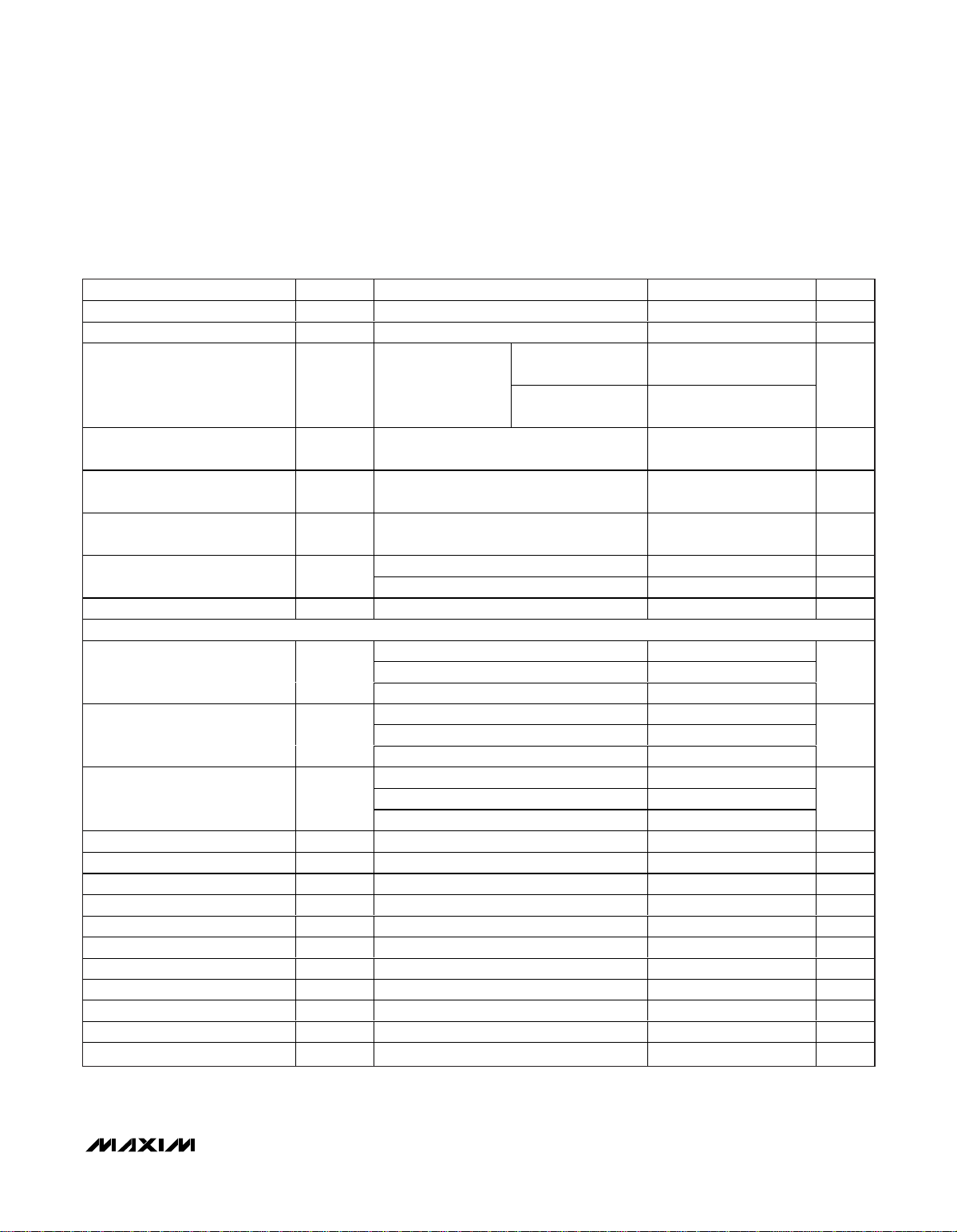

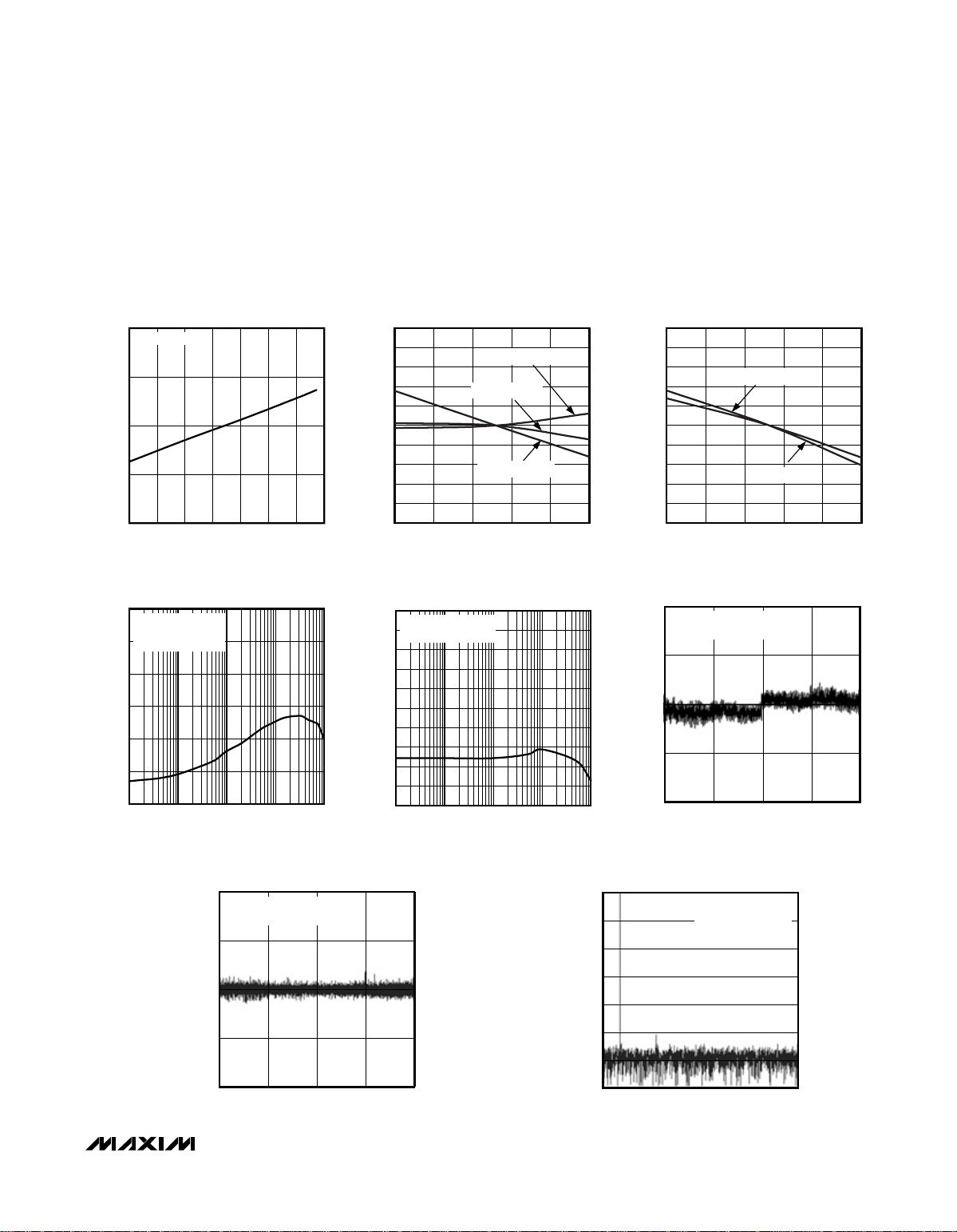

ANALOG SUPPLY CURRENT

vs. ANALOG SUPPLY VOLTAGE

MAX1034/35 toc01

AV

DD1

(V)

I

AVDD1

(mA)

5.155.054.954.85

2.35

2.40

2.45

2.50

2.55

2.60

2.30

4.75 5.25

TA = +85°C

TA = +25°C

TA = -40°C

EXTERNAL CLOCK MODE

PREAMPLIFIER SUPPLY CURRENT

vs. PREAMPLIFIER SUPPLY VOLTAGE

MAX1034/35 toc02

AV

DD2

(V)

I

AVDD2

(mA)

5.155.054.85 4.95

16

17

18

19

20

21

22

23

24

15

4.75 5.25

TA = +85°C

TA = +25°C

TA = -40°C

EXTERNAL CLOCK MODE

DIGITAL SUPPLY CURRENT

vs. DIGITAL SUPPLY VOLTAGE

MAX1034/35 toc03

DVDD (V)

I

DVDD

(mA)

5.155.054.954.85

0.70

0.75

0.80

0.85

0.90

0.65

4.75 5.25

TA = +85°C

TA = +25°C

TA = -40°C

EXTERNAL CLOCK MODE

REF

多量程输入、

串行14位ADC

ELECTRICAL CHARACTERISTICS (continued)

(AV

= AV

DD1

clock mode, V

= 50pF, C

Note 1: Parameter tested at AV

Note 2: See definitions in the Parameter Definitions section at the end of the data sheet.

Note 3: Guaranteed by correlation with single-ended measurements.

Note 4: To ensure external reference operation, V

must be below (AV

sition point between internal reference mode and external reference mode lies between the REFCAP buffer disable threshold

minimum and maximum values (Figures 17 and 18).

Note 5: The SCLK duty cycle can vary between 40% and 60%, as long as the t

= DVDD= DV

DD2

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, TA= -40°C to +85°C, unless otherwise noted. Typical values are at TA= +25°C.)

SSTRB

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

= AV

DD1

- 0.4V). Bypassing REFCAP with a 0.1µF or larger capacitor to AGND1 sets V

DD1

= DVDD= DV

DD2

REFCAP

= 5V.

DDO

must exceed (AV

, maximum single-ended bipolar input range (±V

DD1

- 0.1V). To ensure internal reference operation, V

DD1

and tCHtiming requirements are met.

CL

= 3.5MHz (50% duty cycle), external

CLK

REFCAP

REF

≈ 4.096V. The tran-

), C

MAX1034/MAX1035

_______________________________________________________________________典型工作特性

(AV

external clock mode, V

(±V

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, C

SSTRB

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

, maximum single-ended bipolar input range

DD1

= 50pF, unless otherwise noted.)

= 3.5MHz (50% duty cycle),

CLK

DOUT

REFCAP

6 _______________________________________________________________________________________

8/4通道,±V

I

(

A)

REF

多量程输入、

串行14位ADC

__________________________________________________________________典型工作特性 (续)

(AV

external clock mode, V

(±V

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, C

SSTRB

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

DD1

= 50pF, unless otherwise noted.)

= 3.5MHz (50% duty cycle),

CLK

, maximum single-ended bipolar input range

MAX1034/MAX1035

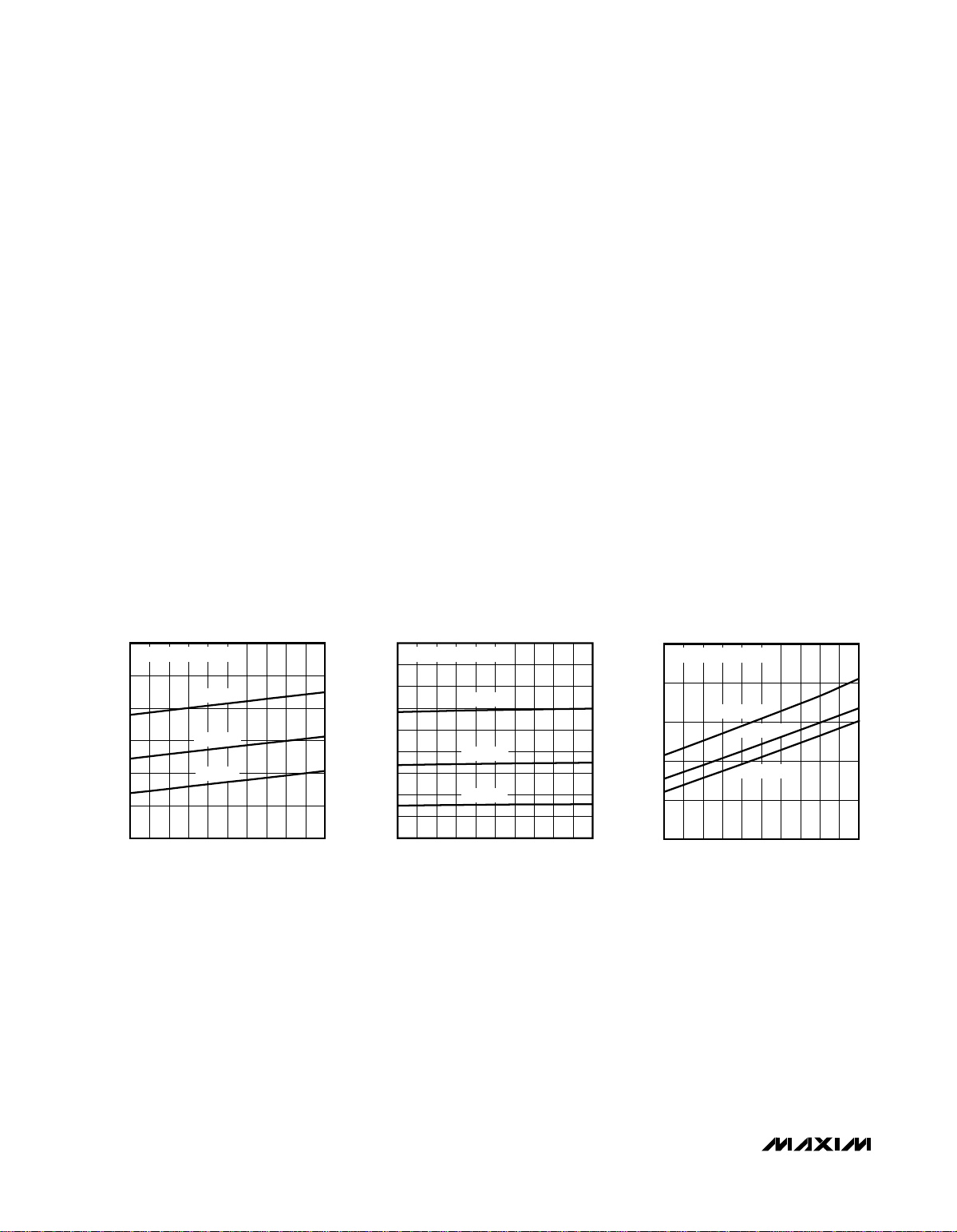

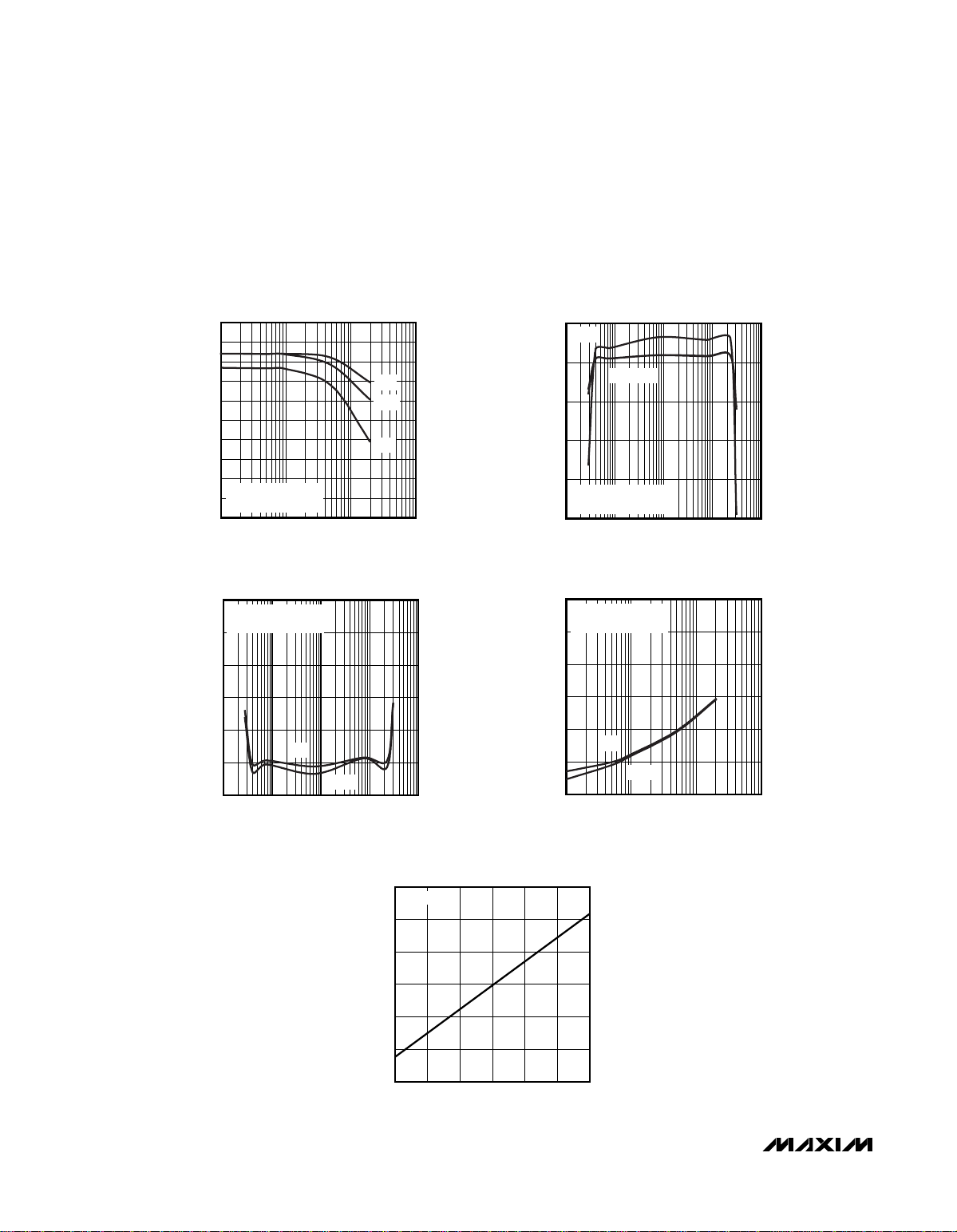

DIGITAL I/O SUPPLY CURRENT

vs. DIGITAL I/O SUPPLY VOLTAGE

0.28

EXTERNAL CLOCK MODE

0.26

0.24

0.22

TA = +85°C

0.20

(mA)

0.18

DVDDO

I

0.16

0.14

0.12

0.10

4.75 5.25

TA = +25°C

DV

DDO

TA = -40°C

(V)

PREAMPLIFIER SUPPLY CURRENT

vs. PREAMPLIFIER SUPPLY VOLTAGE

0.20

PARTIAL POWER-DOWN MODE

0.18

0.16

(mA)

TA = +25°C

AVDD2

I

0.14

0.12

0.10

4.75 5.25

TA = -40°C

AV

(V)

DD2

5.155.054.85 4.95

TA = +85°C

5.155.054.954.85

MAX1034/35 toc04

MAX1034/35 toc06

ANALOG SUPPLY CURRENT

vs. ANALOG SUPPLY VOLTAGE

0.55

PARTIAL POWER-DOWN MODE

0.53

TA = +85°C

0.51

(mA)

AVDD1

I

0.49

0.47

0.45

4.75 5.25

TA = +25°C

TA = -40°C

AV

DD1

(V)

DIGITAL SUPPLY CURRENT

vs. DIGITAL SUPPLY VOLTAGE

0.136

PARTIAL POWER-DOWN MODE

0.134

0.132

0.130

m

0.128

DVDD

0.126

0.124

0.122

0.120

4.75 5.25

TA = +85°C

TA = -40°C

TA = +25°C

DVDD (V)

MAX1034/35 toc05

5.155.054.954.85

MAX1034/35 toc07

5.154.85 5.054.95

_______________________________________________________________________________________ 7

8/4通道,±V

REF

多量程输入、

串行14位ADC

______________________________________________________________________典型工作特性 (续)

(AV

external clock mode, V

(±V

MAX1034/MAX1035

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

= 50pF, C

SSTRB

= 4.096V (external reference operation), REFCAP = AV

REF

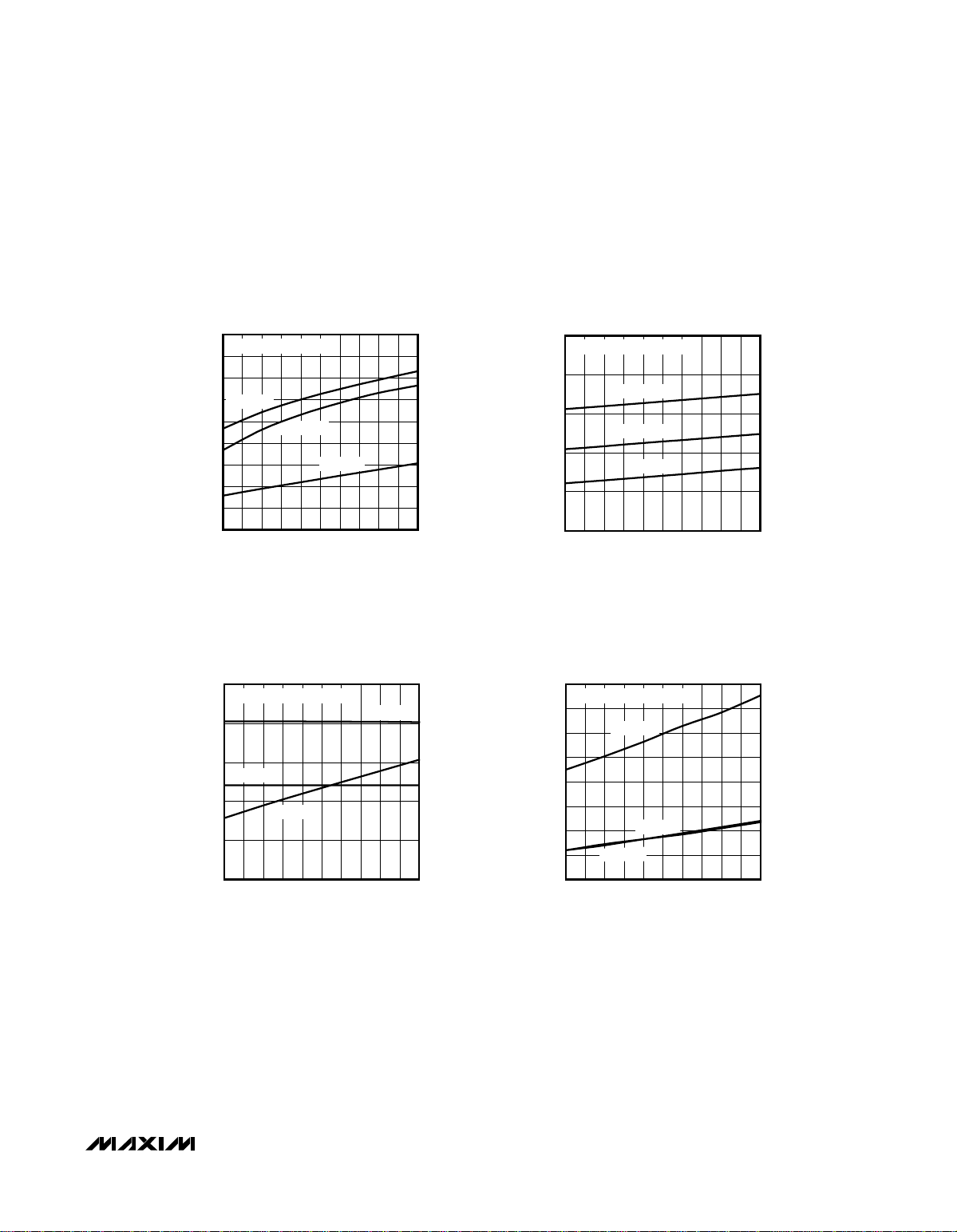

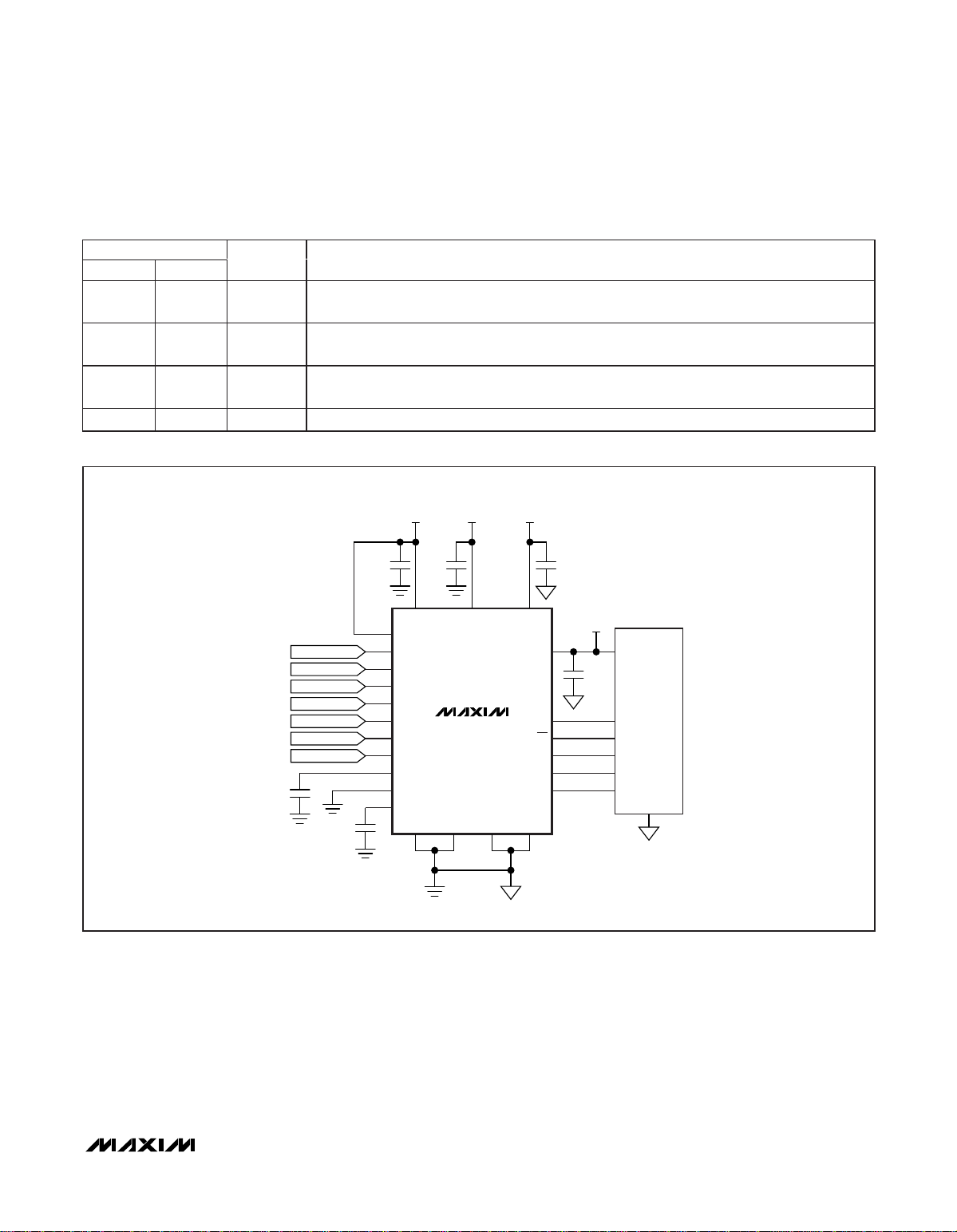

ANALOG SUPPLY CURRENT

3.0

EXTERNAL CLOCK MODE

2.5

2.0

PARTIAL

(mA)

POWER-DOWN MODE

1.5

AVDD1

I

1.0

0.5

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

DD1

= 50pF, unless otherwise noted.)

PREAMPLIFIER SUPPLY CURRENT

vs. CONVERSION RATE

25

f

CLK

20

EXTERNAL CLOCK MODE

FULL POWER-DOWN MODE,

15

PARTIAL POWER-DOWN MODE

(mA)

AVDD2

I

10

5

FULL

POWER-DOWN MODE

MAX1034/35 toc08

= 3.5MHz (50% duty cycle),

CLK

, maximum single-ended bipolar input range

vs. CONVERSION RATE

= 7.5MHz (NOTE 6)

MAX1034/35 toc09

(mA)

DVDDO

I

0

CONVERSION RATE (ksps)

DIGITAL I/O SUPPLY CURRENT

vs. CONVERSION RATE

0.6

f

= 7.5MHz (NOTE 6)

CLK

0.5

0.4

0.3

0.2

0.1

0

0

EXTERNAL CLOCK MODE

FULL POWER-DOWN MODE,

PARTIAL POWER-DOWN MODE

CONVERSION RATE (ksps)

150100500

200

MAX1034/35 toc11

20015010050

0

0

DIGITAL SUPPLY CURRENT

1.8

f

= 7.5MHz (NOTE 6)

CLK

1.6

1.4

EXTERNAL CLOCK MODE,

1.2

PARTIAL POWER-DOWN MODE

1.0

(mA)

0.8

DVDD

I

0.6

0.4

0.2

0

0

CONVERSION RATE (ksps)

vs. CONVERSION RATE

FULL POWER-DOWN MODE

15010050

CONVERSION RATE (ksps)

20015010050

MAX1034/35 toc10

200

Note 6: For partial power-down and full power-down modes, external clock mode was used for a burst of continuous samples.

Partial power-down or full power-down modes were entered thereafter. By using this method, the conversion rate was found

by averaging the number of conversions over the time starting from the first conversion to the end of the partial power-down

or full power-down modes.

8 _______________________________________________________________________________________

8/4通道,±V

)

REF

多量程输入、

串行14位ADC

______________________________________________________________________典型工作特性 (续)

(AV

external clock mode, V

(±V

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, C

SSTRB

DDO

EXTERNAL REFERENCE INPUT CURRENT

vs. EXTERNAL REFERENCE INPUT VOLTAGE

0.16

ALL MODES

0.15

0.14

0.13

EXTERNAL REFERENCE CURRENT (mA)

0.12

3.80 4.15

EXTERNAL REFERENCE VOLTAGE (V)

CHANNEL-TO-CHANNEL ISOLATION

vs. INPUT FREQUENCY

0

f

= 115ksps

SAMPLE

BIPOLAR RANGE

±V

REF

-20

CH0 TO CH2

-40

-60

ISOLATION (dB)

-80

-100

-120

1 10,000

FREQUENCY (kHz

100010010

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

, maximum single-ended bipolar input range

DD1

= 50pF, unless otherwise noted.)

GAIN DRIFT

0.10

0.08

0.06

MAX1034/35 toc12

0.04

0.02

0

-0.02

GAIN DRIFT (%)

-0.04

-0.06

-0.08

4.104.054.003.953.903.85

-0.10

-40 10-15 35 60 85

vs. TEMPERATURE

±V

BIPOLAR RANGE

REF

+V

/2 BIPOLAR

REF

±V

/4 BIPOLAR

REF

TEMPERATURE (°C)

MAX1034/35 toc13

OFFSET ERROR (mV)

COMMON-MODE REJECTION RATIO

vs. FREQUENCY

0

f

= 115ksps

SAMPLE

MAX1034/35 toc15

CMRR (dB)

-10

-20

-30

-40

-50

-60

-70

-80

-90

-100

BIPOLAR RANGE

±V

REF

1 10,000

100010010

MAX1034/35 toc16

INL (LSB)

= 3.5MHz (50% duty cycle),

CLK

OFFSET DRIFT

1.0

0.8

0.6

0.4

0.2

0

-0.2

-0.4

-0.6

-0.8

-1.0

-40 10-15 35 60 85

vs. TEMPERATURE

+V

/4 BIPOLAR RANGE

REF

±V

BIPOLAR

REF

TEMPERATURE (°C)

INTEGRAL NONLINEARITY

vs. DIGITAL OUTPUT CODE

1.0

f

= 115ksps

SAMPLE

BIPOLAR RANGE

±V

REF

0.5

0

-0.5

-1.0

0 81924096 12,288 16,383

DIGITAL OUTPUT CODE

MAX1034/MAX1035

MAX1034/35 toc14

MAX1034/35 toc17

DIFFERENTIAL NONLINEARITY

vs. DIGITAL OUTPUT CODE

1.0

f

= 115ksps

SAMPLE

BIPOLAR RANGE

±V

REF

0.5

0

DNL (LSB)

-0.5

-1.0

081924096 12,288 16,383

DIGITAL OUTPUT CODE

MAX1034/35 toc18

0

-20

-40

-60

-80

MAGNITUDE (dB)

-100

-120

-140

0203010 40 50

FFT AT 5kHz

f

SAMPLE

f

IN(SINE WAVE)

±V

REF

FREQUENCY (kHz)

= 115ksps

= 5kHz

BIPOLAR RANGE

_______________________________________________________________________________________ 9

MAX1034/35 toc19

8/4通道,±V

SNR, SINAD, ENOB vs. SAMPLE RATE

MAX1034/35 toc21

SAMPLE RATE (ksps)

SNR, SINAD (dB)

100101

20

40

60

80

100

0

0.1 1000

ENOB

SNR, SINAD

f

IN(SINE WAVE)

= 5kHz

±V

REF

BIPOLAR RANGE

10

11

12

13

14

9

ENOB (BITS)

-SFDR, THD vs. SAMPLE RATE

MAX1034/35 toc22

SAMPLE RATE (ksps)

-SFDR, THD (dB)

100101

-100

-80

-60

-40

-20

0

-120

0.1 1000

f

IN(SINE WAVE)

= 5kHz

±V

REF

BIPOLAR RANGE

THD

-SFDR

-SFDR, THD vs. ANALOG INPUT

FREQUENCY

MAX1034/35 toc23

FREQUENCY (kHz)

-SFDR, THD (dB)

10010

-100

-80

-60

-40

-20

0

-120

1 1000

f

SAMPLE

= 115ksps

±V

REF

BIPOLAR RANGE

THD

-SFDR

ANALOG INPUT CURRENT

vs. ANALOG INPUT VOLTAGE

MAX1034/35 toc24

ANALOG INPUT VOLTAGE (V)

ANALOG INPUT CURRENT (mA)

420-2-4

-0.5

-1.0

0

0.5

1.0

1.5

-1.5

-6 6

ALL MODES

REF

多量程输入、

串行14位ADC

_____________________________________________________________________典型工作特性 (续)

(AV

external clock mode, V

(±V

MAX1034/MAX1035

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

REF

= 50pF, C

SSTRB

= 4.096V (external reference operation), REFCAP = AV

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

= 50pF, unless otherwise noted.)

SNR, SINAD, ENOB

vs. ANALOG INPUT FREQUENCY

100

90

80

70

60

50

40

SNR, SINAD (dB)

30

20

f

= 115ksps

SAMPLE

10

0

BIPOLAR RANGE

±V

REF

11000

FREQUENCY (kHz)

10010

MAX1034/35 toc20

SNR

SINAD

ENOB

16

15

14

13

12

11

10

9

8

7

6

ENOB (BITS)

= 3.5MHz (50% duty cycle),

, maximum single-ended bipolar input range

DD1

CLK

10 ______________________________________________________________________________________

8/4通道,±V

FULL-POWER BANDWIDTH

MAX1034/35 toc26

FREQUENCY (kHz)

ATTENUATION (dB)

100010010

-50

-40

-30

-20

-10

0

-60

1 10,000

0

10,000

5000

20,000

15,000

35,000

30,000

25,000

40,000

81918190 8192 8193 8194 8195

NOISE HISTOGRAM

(CODE EDGE)

MAX1034/35 toc28

CODE

NUMBER OF HITS

65,534 SAMPLES

0

10,000

30,000

20,000

60,000

50,000

40,000

70,000

81918190 8192 8193 8194

NOISE HISTOGRAM

(CODE CENTER)

MAX1034/35 toc29

CODE

NUMBER OF HITS

65,534 SAMPLES

REF

多量程输入、

串行14位ADC

_____________________________________________________________________典型工作特性 (续)

(AV

external clock mode, V

(±V

DD1

REF

= AV

), C

DD2

DOUT

= DVDD= DV

= 4.096V (external reference operation), REFCAP = AV

REF

= 50pF, C

SSTRB

= 5V, AGND1 = DGND = DGNDO = AGND2 = AGND3 = 0, f

DDO

DD1

= 50pF, unless otherwise noted.)

= 3.5MHz (50% duty cycle),

CLK

, maximum single-ended bipolar input range

MAX1034/MAX1035

SMALL-SIGNAL BANDWIDTH

0

-5

-10

-15

ATTENUATION (dB)

-20

-25

-30

1 10,000

FREQUENCY (kHz)

REFERENCE VOLTAGE vs. TIME

MAX1034/35 toc25

100010010

4ms/div

MAX1034/35 toc27

1V/div

0V

______________________________________________________________________________________ 11

8/4通道,±V

REF

多量程输入、

串行14位ADC

___________________________________________________________________________引脚说明

引脚

MAX1034 MAX1035

12AV

2 3 CH0

3 4 CH1

4 5 CH2

5 6 CH3

6 — CH4

7 — CH5

MAX1034/MAX1035

8 — CH6

9 — CH7

10 7 CS

11 8 DIN

12 9 SSTRB

13 10 SCLK

14 11 DOUT

15 12 DGNDO

16 13 DGND

17 14 DV

18 15 DV

名称

DD1

DDO

DD

模拟供电电压1,将 AV

到AGND1。

模拟输入通道0。

模拟输入通道1。

模拟输入通道2。

模拟输入通道3。

模拟输入通道4。

模拟输入通道5。

模拟输入通道6。

模拟输入通道7。

低有效片选输入,当CS为低时,数据在SCLK 的上升沿由DIN同步移入器件。同时当CS为低时,

数据在SCLK 的下降沿从DOUT同步输出。当CS为高时,将忽略SCLK 和DIN的状态变化,DOUT

为高阻态。

串行数据输入。当CS为低时,数据在SCLK 的上升沿同步移入器件。当CS为高时,将忽略DIN

的状态变化。

转换状态指示。当采用内部时钟时,SSTRB的上升沿表示需要从器件读取的数据已经准备好。

当工作于外部时钟模式时,SSTRB始终保持低电平。不论CS为何状态,SSTRB都不会产生三态

输出,因此需要使用专门的I/O 线。

串行时钟输入。当CS为低时,SCLK将数据同步移入 DIN和移出DOUT。当CS为高时,将忽略

SCLK时钟变化。

串行数据输出。当CS为低时,数据在SCLK 的每个下降沿同步移出DOUT。当CS为高时,DOUT

为高阻态。

数字I/O 地。DGND、DGNDO、AGND3、AGND2和AGND1必须连到一起。

数字地。DGND、DGNDO、AGND3、AGND2和 AGND1必须连在一起。

数字I/O 电源电压输入。将DV

旁路至DGNDO。

数字电源电压输入。将DV

至DGND。

功能

与+4.75V 至+5.25V电源电压相连。使用一个0.1µF电容将AV

DD1

与+2.7V 至+5.25V电源电压相连。使用一个0.1µF电容将DV

DDO

与+4.75V 至+5.25V电源电压相连。使用一个0.1µF电容将DVDD旁路

DD

DD1

旁路

DDO

19 16 REFCAP

20 17 REF

12 ______________________________________________________________________________________

带隙电压旁路节点。采用外部基准时,将REFCAP 与AV

0.01µF电容将 REFCAP旁路到AGND1 (V

基准缓冲输出/ADC基准输入。采用外部基准时,应给 REF提供一个3.800V到4.136V的外部基准

电压。采用内部基准时,通过一个1µF 电容将REF旁路到AGND1,并且V

REFCAP

≈ 4.096V)。

相连。采用内部基准时,用一个

DD

= 4.096V ±1%。

REF

8/4通道,±V

REF

多量程输入、

串行14位ADC

_______________________________________________________________________引脚说明 (续)

引脚

MAX1034 MAX1035

21 18 AGND3

22 19 AV

23 20 AGND2

24 1 AGND1

名称

DD2

模拟信号地3。AGND3 是ADC的负基准电位。将AGND3与AGND1相连。DGND、DGNDO、

AGND3、AGND2和 AGND1必须连在一起。

模拟电源电压2。将 AV

到AGND2。

与+4.75V 至+5.25V电源电压相连。通过一个0.1µF电容将AV

DD2

模拟地2。从该模拟地流过的电流大约比 AGND1多5倍。DGND、DGNDO、AGND3、AGND2和

AGND1必须连接在一起。

模拟地1。DGND、DGNDO、AGND3、AGND2 和AGND1必须连接在一起。

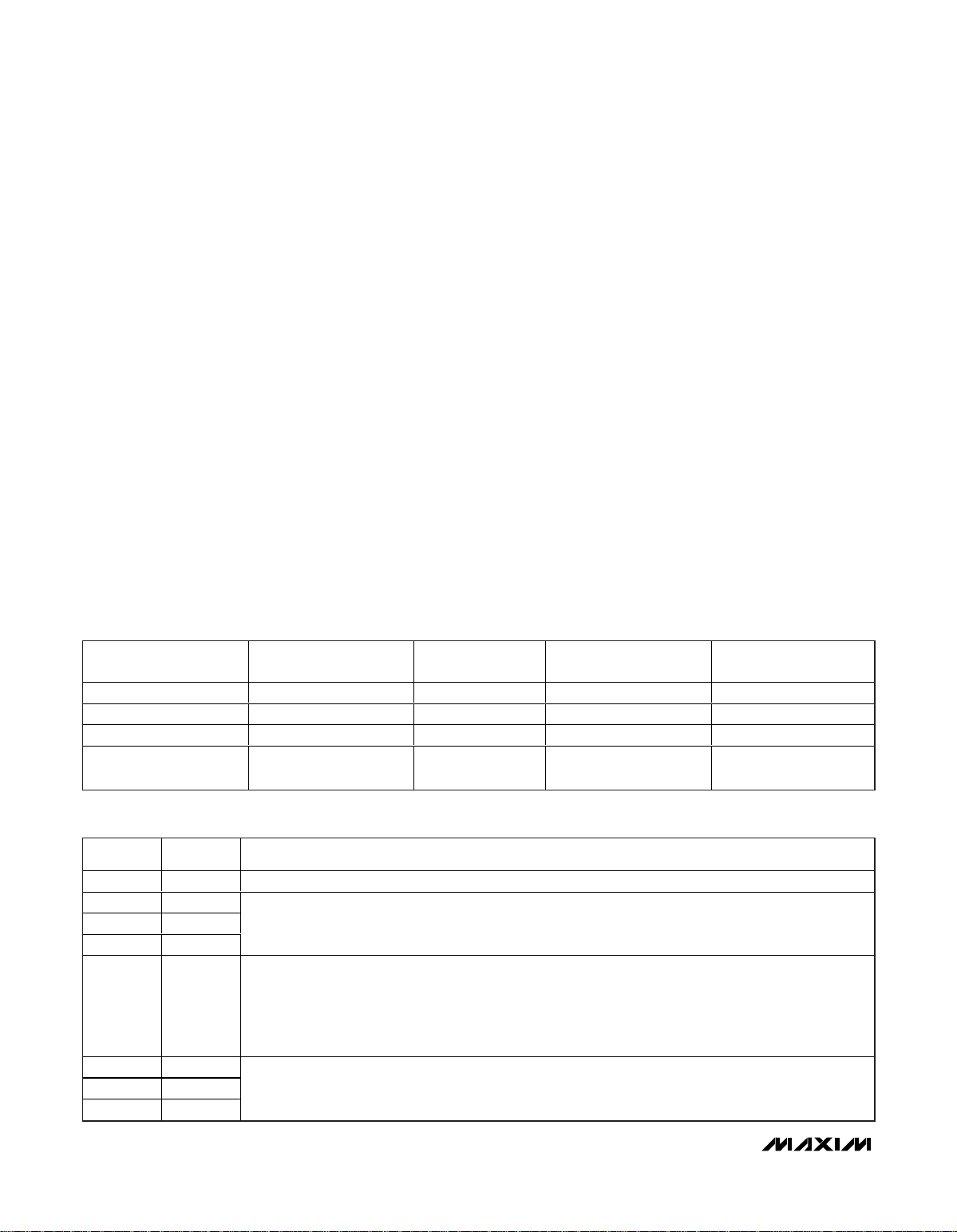

5.0V 5.0V 5.0V

0.1μF 0.1μF 0.1μF

1μF

4–20mA

PLC

ACCELERATION

PRESSURE

TEMPERATURE

WHEATESTONE

WHEATESTONE

0.1μF

AV

CHO

CH1

CH2

CH3

CH4

CH5

CH6

CH7

REF

AGND1

REFCAP

AGND2

DD2

AV

DD1

MAX1034

DV

DV

SCLK

SSTRB

DOUT

DGNDOAGND3 DGND

功能

旁路

DD2

DD

DDO

CS

DIN

3.3V

0.1μF

V

DD

MC68HCXX

μC

SCK

I/O

MOSI

I/O

MISO

V

SS

MAX1034/MAX1035

图1. 典型应用电路

________________________________详细说明

MAX1034/MAX1035多量程、低功耗、14位逐次逼近型

ADC采用+5V单电源供电,并具有独立的数字电源,允许

和2.7V至5.25V系统连接。这两款14 位 ADC 带有支持单端

和全差分输入的内部采样-保持 (T/H) 电路。进行单端信

______________________________________________________________________________________ 13

号转换时,有效模拟输入电压范围从地电位以下的-V

到地电位以上的+V

为 -2 x V

到+2 x V

REF

。允许的最大差分输入电压范围

REF

。数据转换可通过软件编程实现

REF

REF

多种通道配置和数据采集应用。微处理器 (µC) 很容易通

过SPI/QSPI/MICROWIRE兼容的串行接口控制转换器。

8/4通道,±V

REF

串行14位ADC

多量程输入、

MAX1034具有8路单端模拟输入通道或4路差分通道 (见

本数据资料最后部分给出的

方框图

)。MAX1035具有4路

单端模拟输入通道或2路差分通道。每一个模拟输入通道

均可通过软件独立编程设置为7种单端输入范围 (0至

+V

/2、-V

REF

±V

/2 和±V

REF

和 ±2 x V

/2至0、0至+V

REF

) 和3种差分输入范围 (±V

REF

)。此外,所有模拟输入通道均具有±6V故障

REF

REF

、-V

至0、±V

REF

REF

/2、±V

容限。空闲通道的故障状态不会影响其它通道的转换

结果。

为使工作环境保持低噪声,MAX1034和MAX1035为电路

的每一部分提供独立的电源。表1所示为4个独立电源。

MAX1034/MAX1035

采用独立的AV

DD1

、AV

、DVDD和DV

DD2

电源供电,

DDO

可获得最佳性能。另一种做法是在尽可能靠近器件的位

置将AV

DD1

、AV

和DVDD连接到一起,以方便电源连

DD2

接。同时在尽可能靠近器件的位置将AGND1、AGND2、

AGND3、DGND和DGNDO连接在一起。分别使用0.1µF

表1. MAX1034/MAX1035电源与旁路

POWER

SUPPLY/GROUND

DV

/DGNDO 2.7 to 5.25 0.2 Digital I/O 0.1µF to DGNDO

DDO

AV

/AGND2 4.75 to 5.25 17.5 Analog Circuitry 0.1µF to AGND2

DD2

AV

/AGND1 4.75 to 5.25 3.0 Analog Circuitry 0.1µF to AGND1

DD1

DVDD/DGND 4.75 to 5.25 0.9

SUPPLY VOLTAGE

RANGE (V)

电容将每一个供电电源旁路到各自对应的接地点 (表1)。

如果出现较大的低频噪声,则应增加一个10µF电容与

0.1µF旁路电容并联。

/4、

REF

REF

MAX1034/MAX1035 ADC采用全差分、逐次逼近寄存器

(SAR) 转换技术,并提供片上T/H模块,可将电压信号转

换成14位数字结果。器件支持单端和差分输入结构,并

可编程设置单极性和双极性信号范围。

电源

MAX1034/MAX1035具有开关电容T/H架构,允许模拟输

入信号以电荷的形式存储在采样电容上。各种工作模式

下的T/H时序和采样时间如图2、图 3 和图 4 所示。MAX1034/

MAX1035的模拟输入电路对取样电容的输入信号进行了

缓冲,使模拟输入电流和输入电压保持线性关系 (图5)。

TYPICAL SUPPLY

CURRENT (mA)

采样-保持电路

CIRCUIT SECTION BYPASSING

Digital Control Logic and

Memory

0.1µF to DGND

转换器工作

表2. 模拟输入配置字节

BIT

NUMBER

7 START Start Bit. The first logic 1 after CS goes low defines the beginning of the analog input configuration byte.

6C2

5C1

4C0

3 DIF/SGL

2R2

1R1

0R0

14 ______________________________________________________________________________________

NAME DESCRIPTION

Channel-Select Bits. SEL[2:0] select the analog input channel to be configured (Tables 4 and 5).

Differential or Single-Ended Configuration Bit. DIF/SGL = 0 configures the selected analog input channel

for single-ended operation. DIF/SGL = 1 configures the channel for differential operation. In single-ended

mode, input voltages are measured between the selected input channel and AGND1, as shown in

Table 4. In differential mode, the input voltages are measured between two input channels, as shown in

Table 5. Be aware that changing DIF/SGL adjusts the FSR, as shown in Table 6.

Input-Range-Select Bits. R[2:0] select the input voltage range, as shown in Table 6 and Figure 7.

8/4通道,±V

REF

多量程输入、

串行14位ADC

MAX1034/MAX1035

CS

1

2

3

SCLK

SSTRB

DIN S C2 C1 C0 0 0 0 0

ANALOG INPUT

TRACK AND HOLD*

DOUT

IMPEDANCE

HOLD TRACK HOLD

HIGH

*TRACK AND HOLD TIMING IS CONTROLLED BY SCLK.

4

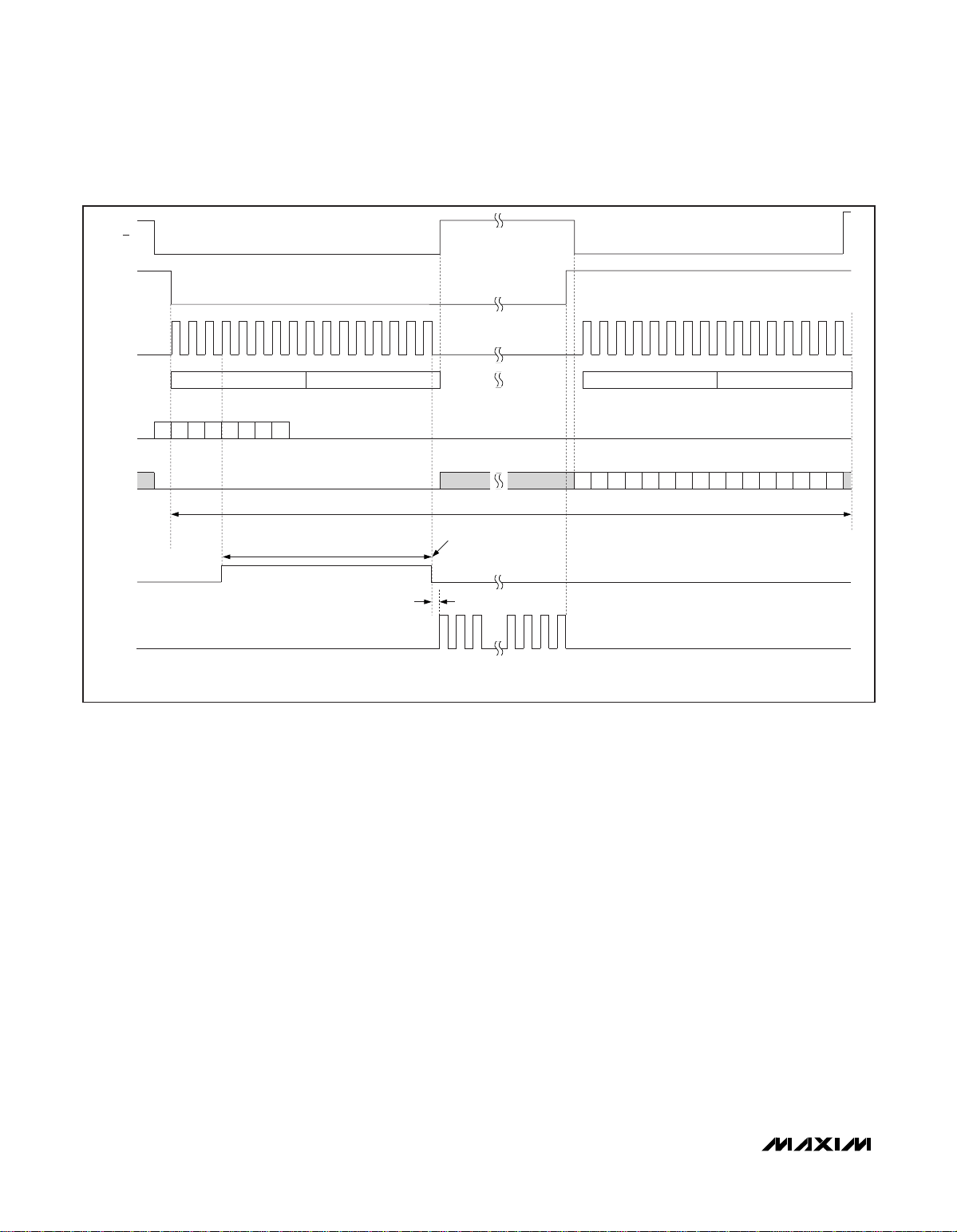

图2. 外部时钟模式 (模式0)

5

6

7

BYTE 1 BYTE 2 BYTE 3 BYTE 4

101112

8

9

t

ACQ

13

14

15

16

f

SAMPLE

1718192021

≈ f

/ 32

SCLK

SAMPLING INSTANT

B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 X X

22

23

24

252627

28

29

30

31

32

HIGH

IMPEDANCE

模拟输入电路

通过写相应的模拟输入配置字节 (表2),可将模拟输入单独

配置成差分或单端转换方式。模拟输入信号源必须能够

驱动 ADC的6kΩ 输入阻抗 (图6)。

图6给出了简化的模拟输入电路。模拟输入具有±6V故障

容限,并通过背向二极管提供保护。求和结点电压V

通道输入共模电压的函数:

R

1

⎛

V

⎜

SJ CM

⎝

RR

⎞

.

×++

⎟

⎠

+

12

2 375 1

⎛

V

⎜

⎝

R

1

⎛

⎜

⎝

+

RR

12

这样一来,在整个输入电压范围内,模拟输入阻抗相对

恒定,如图5所示。

单端转换内部以AGND1作为参考点 (表3和表4)。在差分

模式下,IN+和IN-根据表3和表5 进行选择。设置差分通

道时,差分对儿按照正通道的模拟配置字节来设置。例

如,要将CH2和CH3配置为量程为±V

______________________________________________________________________________________ 15

的差分转换输入

REF

,是

SJ

⎞

⎞

=

V

×

⎟

⎟

⎠

⎠

时,应将CH2的模拟配置字节设置成量程为±V

REF

的差分

转换方式 (1010 1100)。为启动CH2和CH3差分对儿转换,

发送命令1010 0000。

模拟输入带宽

MAX1034/MAX1035输入采样电路具有1.5MHz小信号带

宽。1.5MHz输入带宽使该系列器件能够数字化高速瞬变

信号。如

典型工作特性

中的-SFDR, THD vs. Analog Input

Frequency曲线所示,当需要数字化的信号频率超过15kHz

时,谐波失真将会加剧。

模拟输入范围和故障容限

如图7所示,可通过软件选择能够产生有效数字输出的单

端模拟输入电压范围。 DIF/

通道均可通过设置R[2:0] 控制位独立编程为7种单端输入

范围之一。

= 0时,每一个模拟输入

SGL

8/4通道,±V

REF

串行14位ADC

CS

SSTRB

多量程输入、

SCLK

DIN SC2C1C00000

MAX1034/MAX1035

DOUT

ANALOG INPUT

TRACK AND HOLD*

INTCLK**

123456789

BYTE 1 BYTE 2 BYTE 3 BYTE 4

HOLD

*TRACK AND HOLD TIMING IS CONTROLLED BY SCLK.

**INTCLK IS AN INTERNAL SIGNAL AND IS NOT ACCESSIBLE TO THE USER.

10111213141516

t

ACQ

TRACK HOLD

图3. 外部采样模式 (模式1)

图8说明了可软件选择的差分模拟输入电压范围,并能够

产生有效数字输出。在 DIF/

= 1时,每一个模拟输入

SGL

差分对儿均能通过设置 R[2:0] 控制位独立编程为3种差分

输入范围之一。

无论所指定的输入电压范围是多少,以及通道是否被选

择,每个模拟输入都具有±6V故障容限。而且无论器件

是否上电,模拟输入故障保护均有效。

f

SAMPLE

SAMPLING INSTANT

100ns to 400ns

123

171819202122232425262728293031

HIGH

B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 X X

17

f

≈ f

INTCLK

SCLK

/ 32 + f

≈ 4.5MHz

IMPEDANCE

/ 17

INTCLK

141516

对于超出FSR的任何电压,只要在±6V故障容限范围之内,

加到模拟输入通道后都将产生满量程输出电压结果。

箝位二极管的击穿电压门限超过6V,可在ESD和其它瞬

态冲击情况下保护MAX1034/MAX1035的模拟输入 (图6)。

器件正常工作时,箝位二极管不会导通,也不会在瞬态

冲击下限制电流。当工作环境具有潜在的高能量电压

和/或电流瞬变时,需要从外部对MAX1034/MAX1035提供

保护。

32

16 ______________________________________________________________________________________

SSTRB

8/4通道,±V

REF

多量程输入、

串行14位ADC

MAX1034/MAX1035

CS

SCLK

DIN S C2 C1 C0 0 0 0 0

DOUT

ANALOG INPUT

TRACK AND HOLD*

INTCLK**

1234567

HOLD HOLD

*TRACK AND HOLD TIMING IS CONTROLLED BY INTCLK, AND IS NOT ACCESSIBLE TO THE USER.

**INTCLK IS AN INTERNAL SIGNAL AND IS NOT ACCESSIBLE TO THE USER.

图4. 内部时钟模式 (模式2)

1.5

1.0

0.5

8

BYTE 1 BYTE 2 BYTE 3

HIGH IMPEDANCE

f

≈ f

/ 24 + f

/ 28

SCLK

INTCLK

252627

t

ACQ

TRACK

100ns to 400ns

123

SAMPLE

SAMPLING INSTANT

1011121314

≈ 4.5MHz

f

INTCLK

10111213141516

9

B13 B12 B11 B10 B9 B8 B7 B6 B5 B4 B3 B2 B1 B0 X X

28

MAX1034

17181920212223

R2

MAX1035

*R

SOURCE

ANALOG

SIGNAL

SOURCE

IN_+

R1

V

SJ

24

0

-0.5

ANALOG INPUT CURRENT (mA)

-1.0

-1.5

-6 6

ANALOG INPUT VOLTAGE (V)

图5. 模拟输入电流与输入电压的关系

______________________________________________________________________________________ 17

R2

*R

SOURCE

ANALOG

SIGNAL

SOURCE

IN_+

R1

V

SJ

420-2-4

*MINIMIZE R

TO AVOID GAIN ERROR AND DISTORTION.

SOURCE

图6. 简化的模拟输入电路

8/4通道,±V

REF

多量程输入、

串行14位ADC

表3. 输入数据字格式

DATA BIT

OPERATION

Conversion-Start Byte

(Tables 4 and 5)

Analog-Input Configuration Byte

(Table 2)

Mode-Control Byte

(Table 7)

表4. 单端模式 (DIF/SGL = 0) 下的通道选择

CHANNEL-SELECT BIT CHANNEL

MAX1034/MAX1035

C2 C1 C0 CH0 CH1 CH2 CH3 CH4 CH5 CH6 CH7 AGND1

000+ -

001 + -

010 + -

011 + -

100 + -

101 + -

110 +-

111 +-

D7

(START)

1C2C1C00000

1 C2 C1 C0 DIF/SGL R2 R1 R0

1M2M1M01000

D6 D5 D4 D3 D2 D1 D0

表5. 真差分模式 (DIF/SGL = 1) 下的通道选择

CHANNEL-SELECT BIT CHANNEL

C2 C1 C0 CH0 CH1 CH2 CH3 CH4 CH5 CH6 CH7 AGND1

000+-

0 0 1 RESERVED

010 +-

0 1 1 RESERVED

100 +-

1 0 1 RESERVED

110 +-

1 1 1 RESERVED

差分共模范围

MAX1034/MAX1035 的差分共模范围 (V

在-4.75V至+5.5V以内,以得到有效的转换结果。差分共

模范围定义如下:

CH CH

_ _

+

V

CMDR

18 ______________________________________________________________________________________

()

=

+

()

2

CMDR

−

) 必须保持

除了共模输入电压范围的限制外,每个独立的模拟输入

相对于AGND1还必须限制在±6V之内。

模拟输入配置字节中的量程范围选择位R[2:0] 决定了相应

通道的满量程范围 (表2和表6)。图9、图10和图11给出

了 MAX1034/MAX1035 工作在 FSR = V

V

和FSR = 2 x V

REF

压范围。阴影部分覆盖了支持整个FSR的有效共模电压

范围。

时分别对应的有效模拟输入电

REF

/ 2、FSR =

REF

8/4通道,±V

REF

多量程输入、

串行14位ADC

MAX1034/MAX1035

+V

REF

+V

REF

+3/4 V

REF

REF

FSR = V

101

REF

FSR = V

110

REF

FSR = 2 x V

111

+V

/2

REF

/4

+V

REF

0

(CH_) - AGND1 (V)

-V

/4

REF

/2

-V

REF

-3/4 V

REF

-V

REF

EACH INPUT IS FAULT TOLERANT TO ±6V.

/ 2

REF

/ 2

REF

FSR = V

001

FSR = V

/ 2

REF

FSR = V

010

011

INPUT RANGE SELECTION BITS, R[2:0]

REF

FSR = V

100

图7. 单端输入电压范围

数字接口

MAX1034/MAX1035具有SPI/QSPI和MICROWIRE兼容的串

行接口。MAX1034/MAX1035通过DIN、DOUT、SCLK、

和SSTRB可方便地与主机进行通信。SCLK速率可高达

CS

10MHz (内部时钟模式,模式2)、3.67MHz (外部时钟模式,

模式 0) 或4.39MHz (外部时钟模式,模式1)。主机 (通常

采用微控制器) 应该采用CPOL = 0、CPHA = 0的SPI传

输格式,时序图如图2、图3和图4所示。

数字接口用于完成以下功能:

• 选择单端或真差分输入通道配置。

• 选择单极性或双极性输入范围。

• 选择工作模式:

外部时钟 (模式0)

外部采样 (模式1)

内部时钟 (模式2)

复位 (模式4)

局部关断模式 (模式6)

完全关断模式 (模式7)

• 启动转换和读取结果。

+3/2 V

REF

+V

REF

+V

/2

REF

REF

0

FSR = V

(CH_+) - (CH_-) (V)

-V

/2

REF

-V

REF

-3/2 V

REF

-2 x V

REF

001

EACH INPUT IS FAULT TOLERANT TO ±6V.

REF

FSR = 2 x V

010

011

100

INPUT RANGE SELECTION BITS, R[2:0]

101

110

REF

FSR = 4 x V

111

图8. 差分输入电压范围

片选 (CS)

主机通过CS使能与MAX1034/MAX1035之间的通信。当

为低时,数据在SCLK的上升沿由DIN同步移入器件,

CS

并且数据在SCLK的下降沿从DOUT同步移出器件。当

CS

为高时,将忽略SCLK和DIN的状态变化,此时DOUT为

高阻态,所以允许其它外围设备共享DOUT线。由于

SSTRB永远都不会是高阻态,因此其它设备不能共享该

信号线。

转换状态指示 (SSTRB)

如图3和图4所示,SSTRB变高时表示ADC已经完成了一

次转换,并且主机可以读取已准备好的结果。SSTRB在

外部时钟模式下 (图2) 始终保持低电平,因此可以不连接。

SSTRB会被驱动为高电平或低电平,与CS的状态无关,

因此其它外部设备不能共享SSTRB。

______________________________________________________________________________________ 19

8/4通道,±V

REF

多量程输入、

串行14位ADC

表6. 量程范围选择位

DIF/SGL R2 R1 R0 MODE TRANSFER FUNCTION

0 0 0 0 No Range Change* —

Single-Ended

0001

0010

0011

MAX1034/MAX1035

0100

0101

REF

REF

REF

REF

REF

REF

REF

/ 2

/ 2

REF

/4 to +V

/2 to 0

REF

/2 to +V

to 0

Bipolar - V

Full-Scale Range (FSR) = V

Single-Ended

Unipolar -V

FSR = V

Single-Ended

Unipolar 0 to +V

FSR = V

Single-Ended

Bipolar -V

FSR = V

Single-Ended

Unipolar -V

FSR = V

/4

REF

/2

REF

/ 2

REF

/2

Figure 12

Figure 13

Figure 14

Figure 12

Figure 13

Single-Ended

0110

0111

1 0 0 0 No Range Change** —

1001

1 0 1 0 Reserved —

1 0 1 1 Reserved —

1100

1 1 0 1 Reserved —

1 1 1 0 Reserved —

1111

*

转换启动字节 (见表3)。

**

模式控制字节 (见表3)。

Unipolar 0 to +V

FSR = V

DEFAULT SETTING

Single-Ended

Bipolar -V

FSR = 2 x V

Differential

Bipolar -V

FSR = V

Differential

Bipolar -V

FSR = 2 x V

Differential

Bipolar -2 x V

FSR = 4 x V

REF

REF

REF

REF

REF

REF

REF

REF

REF

to +V

/2 to +V

to +V

to +2 x V

REF

REF

REF

REF

/2

REF

Figure 14

Figure 12

Figure 12

Figure 12

Figure 12

20 ______________________________________________________________________________________

1

2 4 096

.

LSB

FSR V

V

REF

N

=

×

×

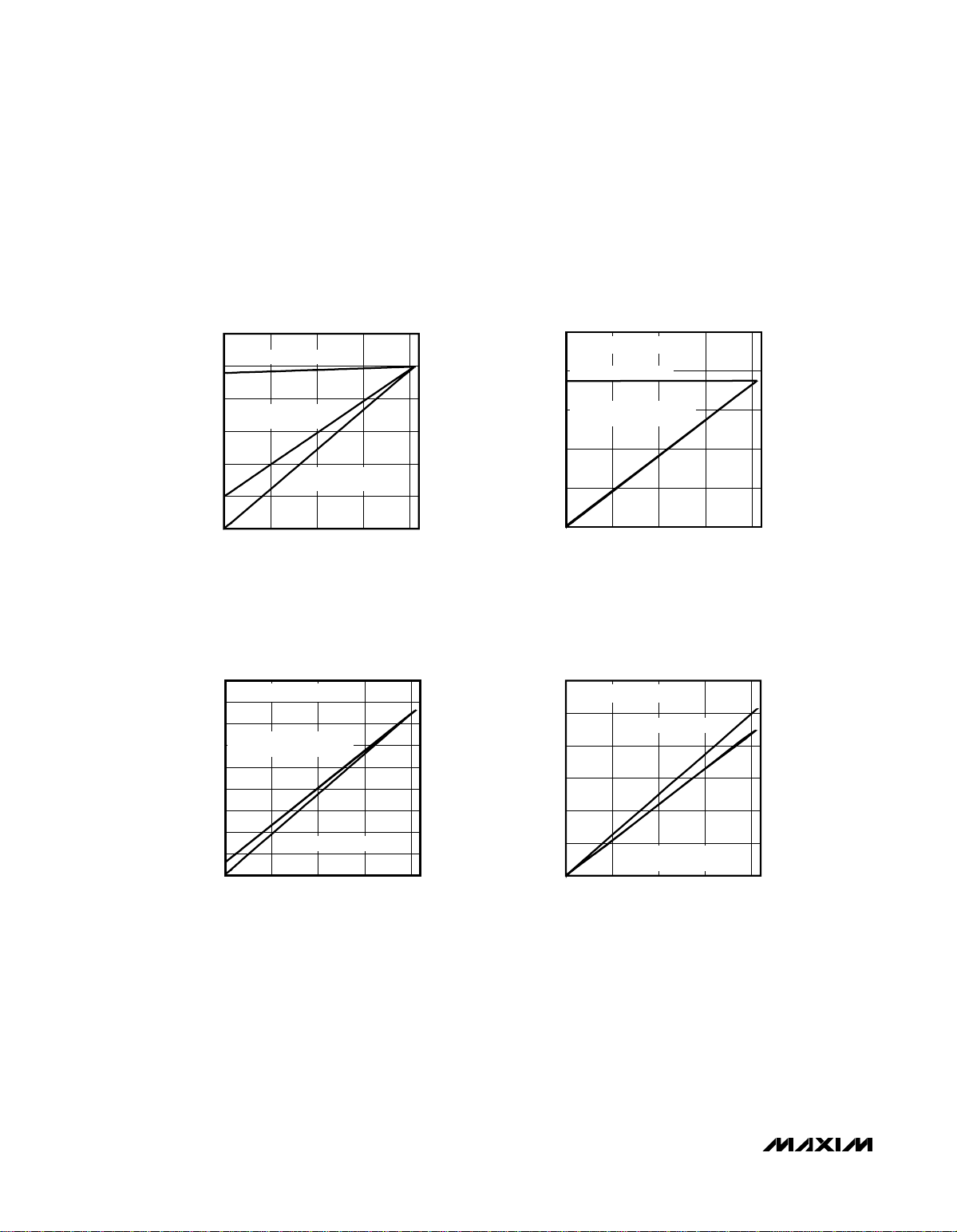

INPUT COMMON-MODE VOLTAGE RANGE

vs. OUTPUT VOLTAGE (FSR = V

6

REF

8/4通道,±V

REF

多量程输入、

串行14位ADC

MAX1034/MAX1035

)

INPUT COMMON-MODE VOLTAGE RANGE

vs. OUTPUT VOLTAGE (FSR = 2 x V

6

REF

)

4

2

0

-2

COMMON-MODE VOLTAGE (V)

-4

V

= 4.096V

V

REF

REF

REF

= 4.096V

-6

-8 8

INPUT VOLTAGE (V)

图9. 共模电压与输入电压的关系 (FSR =V

INPUT COMMON-MODE VOLTAGE RANGE

vs. OUTPUT VOLTAGE (FSR = 4 x V

6

4

2

0

-2

COMMON-MODE VOLTAGE (V)

-4

-6

-8 8

INPUT VOLTAGE (V)

图11. 共模电压与输入电压的关系 (FSR =4 x V

4

2

0

-2

COMMON-MODE VOLTAGE (V)

-4

V

= 4.096V

6420-2-4-6

)

)

REF

图10. 共模电压与输入电压的关系 (FSR =2 x V

在SCLK的下降沿,输出数据以偏移二进制码的格式从

-6

-8 8

INPUT VOLTAGE (V)

REF

6420-2-4-6

REF

输出数据格式

)

DOUT 同步输出,并且MSB在前 (B13)。关于输出二进制

码的信息,请参见

传输函数

一节以及图12、图13和图14。

配置模拟输入

每一个模拟输入都提供两个配置参数:

• 单端或真差分输入。

• 输入电压范围。

这些参数可用表2所示的模拟输入配置字节来进行配置。

6420-2-4-6

每一个模拟输入都有一个专门寄存器用于存储其输入配

置信息。图15所示的时序图说明了如何写模拟输入配置

REF

)

寄存器。图16给出了DOUT和SSTRB的时序。

起始位

如表3所示,使用3种输入数据字格式与MAX1034/MAX1035

进行通信。每一个输入数据字均由一个起始位开始。该

起始位定义为:CS为低时,同步移入DIN的第一个逻辑

高电平位,同时需符合下列条件之一:

• 器件未进行数据转换,且先前转换的所有数据均已从

DOUT移出。

• 器件配置为外部时钟模式 (模式0),且先前的转换结果

位B13–B1已经从DOUT移出。

• 器件配置为外部采集模式 (模式1),且先前的转换结果

位B13–B5已经从DOUT移出。

• 器件配置为内部时钟模式 (模式2),且先前的转换结果

位B13–B2已经从DOUT移出。

______________________________________________________________________________________ 21

传输函数

ADC的传输函数定义了模拟输入电压和数字输出代码之

间的关系。图12、图13和图14给出了MAX1034/MAX1035

的传输函数。该传输函数取决于下列因素:

• 模拟输入电压范围

• 单端或差分配置

• 基准电压

ADC传输函数坐标轴的单位通常采用最低有效位 (LSB)。

对于MAX1034/MAX1035,LSB采用下列公式进行计算:

其中N是位数 (N = 14),FSR为满量程范围 (见图 7和

图8)。

8/4通道,±V

REF

串行14位ADC

多量程输入、

3FFF

3FFE

3FFD

2001

2000

1FFF

BINARY OUTPUT CODE (LSB [hex])

0003

0002

0001

MAX1034/MAX1035

0000

-8,192 -8,190 0 +8,189 +8,191

INPUT VOLTAGE (LSB [DECIMAL])

FSR

1 LSB =

-1 +1

AGND1 (DIF/SGL = 0)

0V (DIF/SGL = 1)

FSR x V

REF

16,384 x 4.096V

FSR

图12. 理想的双极性传输函数,单端或差分输入

3FFF

3FFE

3FFD

2001

2000

1FFF

BINARY OUTPUT CODE (LSB [hex])

0003

0002

0001

0000

0 1 2 3 8,192 16,381 16,383

(AGND1)

INPUT VOLTAGE (LSB [DECIMAL])

FSR

1 LSB =

FSR x V

REF

16,384 x 4.096V

FSR

图14. 理想的单极性传输函数,单端输入,0 到+FSR

模式控制

MAX1034/MAX1035包含1个字节宽度的模式控制寄存器。

图15给出了如何使用模式控制字节,模式控制字节的格

式如表7所示。利用模式控制字节来选择转换方式,控制

MAX1034/MAX1035的功率模式。

3FFF

3FFE

3FFD

2001

2000

1FFF

BINARY OUTPUT CODE (LSB [hex])

0003

0002

0001

0000

0 1 2 3 8,192 16,381 16,383

INPUT VOLTAGE (LSB [DECIMAL])

FSR

1 LSB =

FSR x V

REF

16,384 x 4.096V

FSR

(AGND1)

图13. 理想的单极性传输函数,单端输入,-FSR 到0

选择转换方式

利用模式控制字节选择转换方式 (参见

模式控制

部分),

并使用转换启动命令 (见表3、图2、图3 和图 4) 来启动转

换。MAX1034/MAX1035采用下列三种方法之一将模拟信

号转换成数字信号:

• 外部时钟模式,模式0 (图2)

• 最高吞吐速率 (见

Electrical Characteristics

表)。

• 用户控制采样时间。

• 转换期间CS保持低电平。

• 在整个ADC转换期间和从DOUT读取数据过程中,

均由用户提供SCLK。

• 外部采集模式,模式1 (图3)

• 最低吞吐速率 (见

Electrical Characteristics

表)。

• 用户控制采样时间。

• 用户提供2个字节的SCLK,然后将CS驱动为高电

平,可在ADC转换期间减轻处理器的负担。

• 在SSTRB变高之后,用户提供2个字节的SCLK,

并读取DOUT数据。

• 内部时钟模式,模式2 (图4)

• 高吞吐速率 (见

Electrical Characteristics

表)。

• 内部时钟控制采样时间。

22 ______________________________________________________________________________________

t

CSS

CS

SCLK

DIN

DOUT

t

DS

t

DV

HIGH

IMPEDANCE

t

CL

18

START

SEL2

SEL1 SEL0 R2 R1

ANALOG INPUT CONFIGURATION BYTE

t

CP

t

DIF/SGL

CH

t

CSH

t

DH

R0

t

TR

图15. 模拟输入配置字节和模式控制字节的时序

• 用户提供1个字节的SCLK,然后将CS驱动为高电

平,可在ADC转换时减轻处理器的负担。

• 在SSTRB变高之后,用户提供2个字节的SCLK,

并读取DOUT数据。

外部时钟模式 (模式0)

MAX1034/MAX1035工作在外部时钟模式时,可获得最快

的吞吐速率。SCLK既控制模拟信号的采集,也控制模拟

信号的转换,便于精确控制采集模拟信号的时间。在

SCLK的第14个下降沿开始模拟输入采样 (图2)。

外部时钟模式下,由于采用SCLK驱动转换,为转换提供

时钟时SCLK频率应该保持恒定。最低的SCLK频率也能

够避免内部采样电容上的电压在转换期间发生跌落。

外部时钟模式下,SSTRB保持低电平,因此,如果MAX1034/

MAX1035一直工作在外部时钟模式下,SSTRB可以不接。

8/4通道,±V

REF

多量程输入、

串行14位ADC

t

CSPW

18

START

M2

M1 M0 1 0 0

MODE CONTROL BYTE

HIGH

IMPEDANCE

SSTRB

t

SSCS

CS

t

CSS

SCLK

t

DO

DOUT

NOTE: SSTRB AND CS REMAIN LOW IN EXTERNAL CLOCK MODE (MODE 0).

HIGH

IMPEDANCE

MSB

图16. DOUT 和SSTRB时

外部采集模式 (模式1)

采用外部采集模式时,吞吐速率最低。在外部采集模式

下,SCLK控制模拟信号的采集,便于精确控制采样模拟

信号的时间。内部时钟控制模拟输入电压的转换。在

SCLK的第16个下降沿进行模拟输入采样 (图3)。

0

HIGH

IMPEDANCE

MAX1034/MAX1035

表7. 模式控制字节

BIT NUMBER BIT NAME DESCRIPTION

7 START Start Bit. The first logic 1 after CS goes low defines the beginning of the mode-control byte.

6M2

5M1

4M0

3 1 Bit 3 must be a logic 1 for the mode-control byte.

2 0 Bit 2 must be a logic 0 for the mode-control byte.

1 0 Bit 1 must be a logic 0 for the mode-control byte.

0 0 Bit 0 must be a logic 0 for the mode-control byte.

______________________________________________________________________________________ 23

Mode-Control Bits. M[2:0] select the mode of operation as shown in Table 8.

8/4通道,±V

REF

多量程输入、

串行14位ADC

表8. 模式控制位M[2:0]

M2 M1 M0 MODE

0 0 0 External Clock (DEFAULT)

0 0 1 External Acquisition

0 1 0 Internal Clock

0 1 1 Reserved

1 0 0 Reset

1 0 1 Reserved

1 1 0 Partial Power-Down

1 1 1 Full Power-Down

对于外部采集模式,CS必须在开始的15个时钟周期内保

持低电平,然后在第16个时钟周期的下降沿或之后变为

MAX1034/MAX1035

高电平,如图3所示。要获得最佳性能,转换期间将DIN

和SCLK置为空闲状态。仔细进行电路板布局,使转换期

间DIN和SCLK的状态变化对转换结果的影响极小。

转换完成后,SSTRB变高,可拉低CS以读取转换结果。

在随后对应起始位的SCLK上升沿,SSTRB返回低电平。

内部时钟模式 (模式2)

内部时钟模式下,内部时钟控制模拟信号的采集和转换。

内部时钟在SCLK的第8个下降沿后的100ns到 400ns 之间启

动,速率大约为4.5MHz。在内部时钟信号的第11个下降

沿开始对模拟输入采样 (图4)。

对于内部时钟模式,CS在开始的7个SCLK时钟周期内必

须保持低电平,然后在第8个SCLK时钟周期的下降沿或

之后变为高电平。转换完成后,SSTRB变为高电平,可

以拉低CS并读取转换结果。在随后对应起始位的SCLK上

升沿,SSTRB返回低电平。

复位 (模式4)

如表 8所示,设置M[2:0] = 100时可将MAX1034/MAX1035

复位至缺省状态。缺省状态是:每一个通道都配置为

±V

、双极性、单端转换方式,并且采用外部时钟模式

REF

(模式0)。

局部关断模式 (模式6)

如表 8所示,设置M[2:0] = 110时,器件进入局部关断模

式。在局部关断模式下,除了基准电压产生电路和偏置

电源外,器件所有的模拟部分全部关断。

要退出局部关断模式,可发出下列模式控制字节之一来

改变模式 (见

• 外部时钟模式控制字节。

• 外部采集模式控制字节。

• 内部时钟模式控制字节。

• 复位字节。

• 完全关断模式控制字节。

这种作法可防止MAX1034/MAX1035在嘈杂的数字环境

下,由于CS干扰而错误地从局部关断模式退出。

当 M[2:0] = 111时,器件进入完全关断模式,总电源电流

下降到 1µ A (典型值)。在完全关断模式下,器件的所有

模拟部分全部关断。如果采用内部基准,从完全关断模

式退出时,需在启动转换之前预留10ms的恢复时间,以

保证内部基准电压稳定下来。

要退出完全关断模式,可发出下列模式控制字节之一来

改变该模式 (参见

• 外部时钟模式控制字节。

• 外部采集模式控制字节。

模式控制

模式控制

部分):

完全关断模式 (模式7)

部分):

24 ______________________________________________________________________________________

8/4通道,±V

REF

多量程输入、

串行14位ADC

• 内部时钟模式控制字节。

• 复位字节。

• 局部关断模式控制字节。

这种方法可防止MAX1034/MAX1035在嘈杂的数字环境

下,由于CS干扰而错误地退出完全关断模式。

上电复位

MAX1034/MAX1035上电后即进入采用外部时钟模式的正

常工作状态,所有电路都处于工作状态 (表7和表8)。每

一个模拟输入通道 (CH0–CH7) 均设置为单端转换模式,

输入范围为±V

REF

(表6)。

上电以后,应该先让电源稳定下来。在电源稳定之前,

不要启动转换。另外,当 C

= 1.0µ F和C

REF

REFCAP

=

0.1µF时,应为内部基准留出10ms的稳定时间。更大的基

准电容需要更长的稳定时间。

内部和外部基准

MAX1034/MAX1035可采用内部基准或外部基准。基准电

压影响 ADC的FSR (图12、图13和图14)。如果要求的基

准精度比内部基准更高,和/或多个转换器需要相同的基

准电压,则推荐使用外部基准。

内部基准

MAX1034/MAX1035内含一个4.096V带隙基准。该带隙基

准通过一个标称值为5kΩ 的电阻连接到REFCAP (图17)。

REFCAP上的电压经过缓冲,在REF上产生4.096V基准电

压。当采用内部基准时,应用0.1µF或者更大的电容将

REFCAP旁路到AGND1,同时用1.0µF或者更大的电容将

REF也旁路到AGND1。

外部基准

使用外部基准时,需将REFCAP连接到AV

基准和基准缓冲器。AV

与REFCAP相连时,REF变为

DD1

高阻抗输入,并接受外部基准电压。MAX1034/MAX1035

的外部基准电流取决于所提供的基准电压和工作模式 (参

见

典型工作特性

中的External Reference Input Current vs.

External Reference Input Voltage)。

以禁用内部

DD1

________________________________应用信息

降噪

进行多次额外采样并求取平均值 (过采样),可以消除转

换结果中的转换噪声影响。采样次数的平方根决定了性

能的改善程度。例如:存在2/3 LSB

2

换噪声时,必须进行16 (4

到1 LSB

P-P

。

= 16) 次采样才能将噪声减小

RMS

(4 LSB

P-P

) 的转

MAX1034/MAX1035

SAR

ADC

MAX1034

MAX1035

BANDGAP

REFERENCE

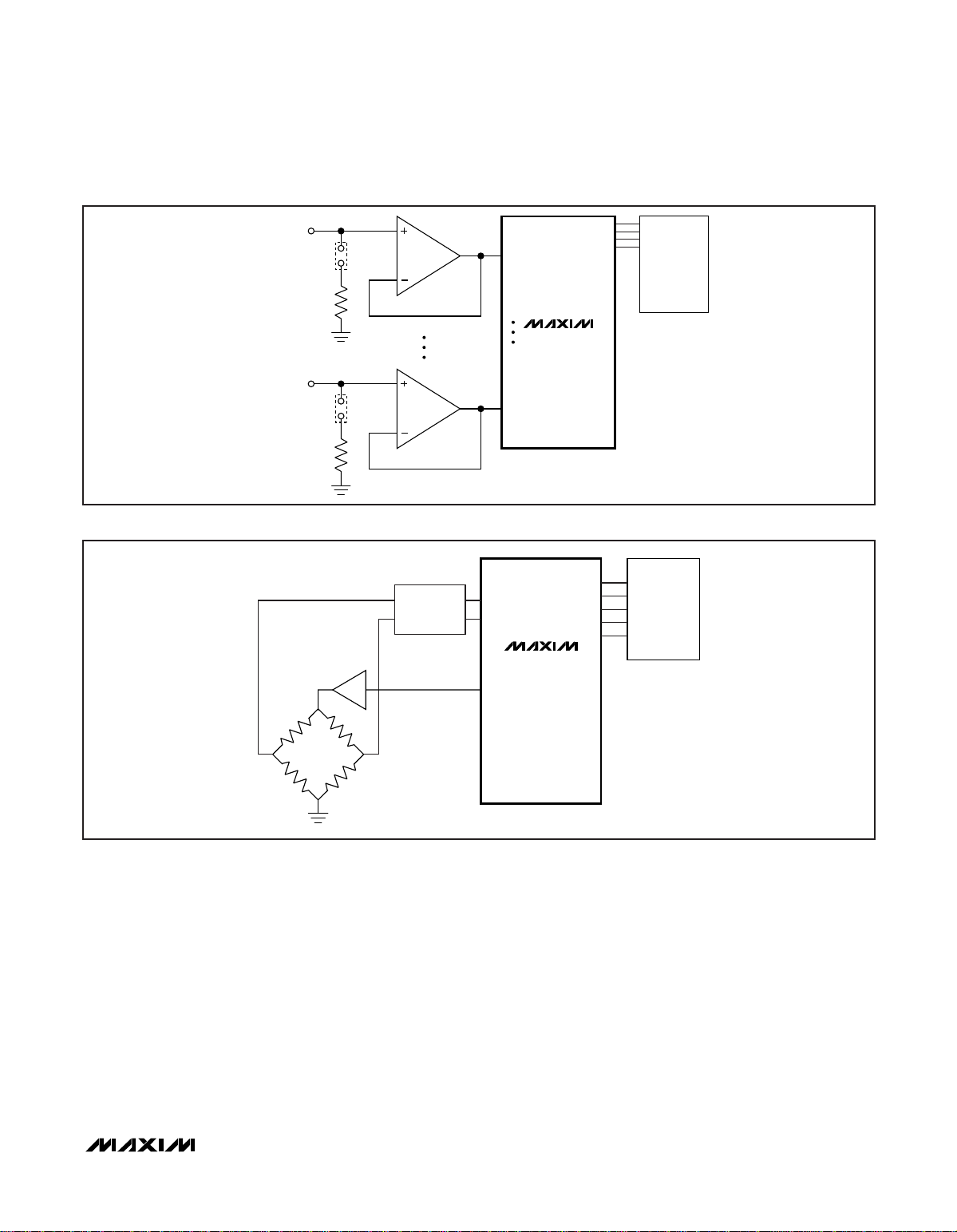

图17. 内部基准

与4–20mA信号接口

4.096V

REF

1x

5kΩ

4.096V

______________________________________________________________________________________ 25

REFCAP

V

RCTH

AGND1

REF

1.0μF

0.1μF

图19给出了一个MAX1034/MAX1035和4–20mA信号之间

的简单接口。4– 20mA信号可以用作一个二进制开关

(4mA表示逻辑低信号,20mA表示逻辑高信号),或者需

要精确传输 (4mA到20mA之间的电流代表中间模拟数

据)。对于二进制开关应用,可通过一个接地电阻将

4– 20mA 信号与MAX1034/MAX1035相连。例如:一个

200Ω电阻可将4– 20mA信号转换成0.8V到4V的信号。调

整该电阻值,以使该电阻与MAX1034/MAX1035源阻抗的

并联阻值为200Ω。在这种应用中,应选择单端0到V

量程范围 (R[2:0] = 011,表6)。对于需要精确测量4mA到

20mA连续模拟电流的应用,应使用一个缓冲器,以防止

MAX1034/MAX1035输入从4–20mA信号中分流。

REF

8/4通道,±V

REF

串行14位ADC

多量程输入、

V+

REF

4.096V

BANDGAP

4.096V

1x

5kΩ

SAR

ADC

MAX1034

MAX1035

MAX1034/MAX1035

图18. 外部基准工作电路

REFERENCE

电桥应用

转换1kHz信号时,MAX1034/MAX1035比电桥应用中可能

考虑的Σ-Δ转换器精度更高。MAX1034的输入阻抗与限

流电阻组合可能影响MAX1034的增益。在很多应用中,

这种误差是可以接受的。但如果应用不允许这种误差存

在,可对 MAX1034的输入进行缓冲 (图20)。电桥与低失

调差分放大器相连,放大器的输出连接至MAX1034/

MAX1035的真差分输入。较大的激励电压能够更充分地

利用±V

/2差分输入电压范围。选择的输入电压范围要

REF

和放大器输出匹配。选择合适的放大器时,应注意放大

器的失调和失调漂移误差。

动态调整输入范围

通过软件控制每一个通道的模拟输入范围,以及器件的

单极性端点交叠参数,允许用户动态改变一个通道的输

入范围,从而改善某些应用的性能。改变输入范围可在

更宽的输出电压范围内实现小的LSB步长。例如:在

-V

/2到0的量程范围和0到V

REF

时,一个LSB为:

VV

/

2

REF REF

, .

16 384 4 096

但输入电压范围的有效跨度为-V

)。

V

REF

/2的量程范围之间切换

REF

×

×

/2到+V

REF

/2 (FSR =

REF

1.0μF

REFCAP

V

RCTH

AGND1

REF

IN

OUT

1.0μF

MAX6341

AV

DD1

GND

布局,接地和旁路

为获得最佳系统性能,仔细考虑PC板的布局非常关键。

电路板应该有独立的模拟和数字地层,以确保数字和模

拟信号相互隔离。模拟和数字 (特别是时钟信号) 信号不

能彼此平行走线,也不要在器件封装底部走数字信号线。

图1给出了推荐的系统接地方式。在AGND1处建立一个模

拟接地点,而在DGND处建立一个数字接地点。将所有模

拟地星型连接至模拟接地点,将所有数字地星型连接到

数字接地点。然后将数字地层和模拟地层在单点连接到

一起。为使噪声最低,星型接地点至电源的地回路应该

为低阻通路,并应该尽可能的短。

AV

电源的高频噪声会降低ADC中高速比较器的性能。

DD1

使用一个0.1µ F的表面贴装陶瓷电容将AV

AGND1。旁路电容的连线应尽可能短。

________________________________参数定义

积分非线性 (INL)

INL是实际传输函数与一条直线的偏差值,该直线可以是

最佳拟合直线,也可以是消除失调和增益误差后两个端

点的连线。MAX1034/MAX1035的INL是采用端点连线方

法测量的。

DD1

旁路到

26 ______________________________________________________________________________________

图19. 4–20mA应用

4–20mA INPUT

4–20mA INPUT

200Ω

200Ω

8/4通道,±V

CH0

MAX1034

CH8

REF

多量程输入、

串行14位ADC

μC

MAX1034/MAX1035

LOW-OFFSET

DIFFERENTIAL

AMPLIFIER

BRIDGE

图20. 电桥应用

微分非线性 (DNL)

DNL是实际步长宽度和1个LSB理想值之间的差值。DNL

误差指标大于-1 LSB时可保证不失码和传输函数的单调性。

转换噪声

转换噪声是指出现在ADC传输函数代码跳变点的噪声。

若模拟输入恰好处于代码跳变点时进行转换,会导致输

出代码产生几个LSB的波动。

CH0

CH1

REF

MAX1034

MAX1035

μP

通道间隔离度

通道间隔离度表示每一个模拟输入与其它通道的隔离程

度。测量这些器件的通道间隔离度时,在所选的模拟输

入通道上施加接近满量程幅度的5kHz正弦波,同时在所

有未选通道上施加相同幅度、不同频率的正弦波。对选

定通道的输出进行FFT,确定未选定通道施加的信号所产

生的信号幅度和加至选定模拟输入通道的5kHz信号幅度

之比。该比值即为通道间隔离度,以dB为单位。

______________________________________________________________________________________ 27

8/4通道,±V

REF

串行14位ADC

多量程输入、

单极性失调误差

-FSR到0V

当一个零值模拟输入电压加到转换器输入时,数字输出

为全1 (0x3FFF)。理想情况下,0x3FFF到0x3FFE的跳变点

发生在 AGND1 - 0.5 LSB的位置。单极性失调误差是测得

的零值跳变点和理想零值跳变点之间的偏差,测试时所

有未选通道均接地。

0V到+FSR

当零值模拟输入电压加到转换器输入时,其数字输出为

全0 (0x0000)。理想情况下,0x0000到0x0001的跳变点出

现在 AGND1 + 0.5 LSB处。单极性失调误差是测得的零

值跳变点和理想零值跳变点的偏差值,测试时所有其它

MAX1034/MAX1035

未选通道均接地。

双极性失调误差

当一个零值模拟输入电压加到转换器输入时,其数字输

出为一个1和随后的全0 (0x2000)。理想情况下,0x1FFF

到0x2000的跳变点出现在 (2

调误差是指测得的中值跳变点和理想中值跳变点之间的

偏差值,测试时将未选通道接地。

当一个正极性满量程电压加到转换器输入时,其数字输

出为全1 (0x3FFF)。理想情况下,0x3FFE到0x3FFF的跳变

出现在低于满量程1.5 LSB处。增益误差是指消除失调误

差后测得的满量程跳变点和理想满量程跳变点之间的偏

差,测试时所有未选通道均接地。

单极性端点交叠是指在两个互补输入电压范围之间切换

时失调的变化量。例如,-V

应0x3FFF输出的输入电压,与0到+V

内对应0x0000输出的输入电压之差,就是单极性端点交

叠。MAX1034/MAX1035的单极性端点交叠为正值,这样

在相邻模拟输入电压范围之间切换时可防止信号丢失和

死区问题。

向ADC输入一个100mV

率,数字转换结果会降低,幅值降低-3dB时对应的频率

即为小信号带宽。

N-1

- 0.5) LSB处。双极性失

增益误差

单极性端点交叠

/2到0V输入电压范围内对

REF

/2输入电压范围

REF

小信号带宽

的正弦波时,逐步提高输入频

P-P

满功率带宽

向ADC输入一个幅值为满量程的95% 的正弦波,逐渐提

高输入频率,直到数字化转换结果的幅值降低-3dB,此时

对应的频率即为满功率带宽。

共模抑制比 (CMRR)

CMRR是一个器件对“共模”信号或加到两个输入端的信

号的抑制能力。共模信号可以是一个交流或直流信号,

也可以是二者的组合。CMR用分贝表示。共模抑制比是

差分信号增益与共模信号增益之比。CMRR仅用于差分

模式。

电源抑制比 (PSRR)

PSRR是指在固定输入电压下,输出电压变化量与电源电

压变化量的比值。对于MAX1034/MAX1035来说,AV

可以在4.75V到5.25V之间变化。PSRR用分贝表示,并且

采用下列公式进行计算:

PSRR dB

[ ] log

对于MAX1034/MAX1035,PSRR是在双极性模式下将模拟

输入接地测得的。

20

=×

⎛

⎜

VVVV

(. ) (. )

⎝

525 475

OUT OUT

−

VV

. .

525 475

−

DD1

⎞

⎟

⎠

孔径抖动

孔径抖动tAJ,是采样时刻变化量的统计分布 (图21)。

孔径延迟

孔径延迟tAD,是从SCLK下降沿到实际采样时刻的时间

延迟 (图21)。

信噪比 (SNR)

SNR是用信号RMS和噪声RMS的比值来计算的。噪声RMS

包括除了基波、前五次谐波和DC失调之外,奈奎斯特频

率的所有频谱成分。

信号与噪声 + 失真比 (SINAD)

SINAD由信号RMS和噪声加失真RMS的比值来计算。噪

声加失真RMS包括除了基波和DC失调之外,奈奎斯特频

率的所有频谱成分。

SINAD dB

( ) log=×

20

⎛

Signal

⎜

Noise

⎝

RMS

RMS

⎞

⎟

⎠

28 ______________________________________________________________________________________

⎝

⎠

8/4通道,±V

REF

多量程输入、

串行14位ADC

有效位 (ENOB)

ENOB表示ADC在指定输入频率和采样速率下的整体精

度。输入范围和ADC满量程范围相等时,ENOB可由以下

公式计算:

ENOB

⎛

=

⎜

⎝

SINAD

− 176

.

602

.

⎞

⎟

⎠

总谐波失真 (THD)

对于MAX1034/MAX1035,THD是输入信号前四次谐波分

量的RMS之和与基波自身之比。其表达式如下:

THD

log

=×

20

⎛

2

VVVV

2

⎜

⎜

2

+++

3

2

4

V

1

⎞

2

5

⎟

⎟

其中V1是基波幅值,V2到V5依次是2次到5次谐波分量的

幅值。

无杂散动态范围 (SFDR)

SFDR 是基波 RMS 值 (最大信号分量) 与第二大频谱分量

RMS值之比。

SCLK

(MODE 0)

SCLK

(MODE 1)

INTCLK

(MODE 2)

ANALOG INPUT

TRACK AND HOLD

图21. 孔径时序图

13

15

10

TRACK HOLD

14

16

11

t

AJ

t

AD

SAMPLE INSTANT

MAX1034/MAX1035

15

12

______________________________________________________________________________________ 29

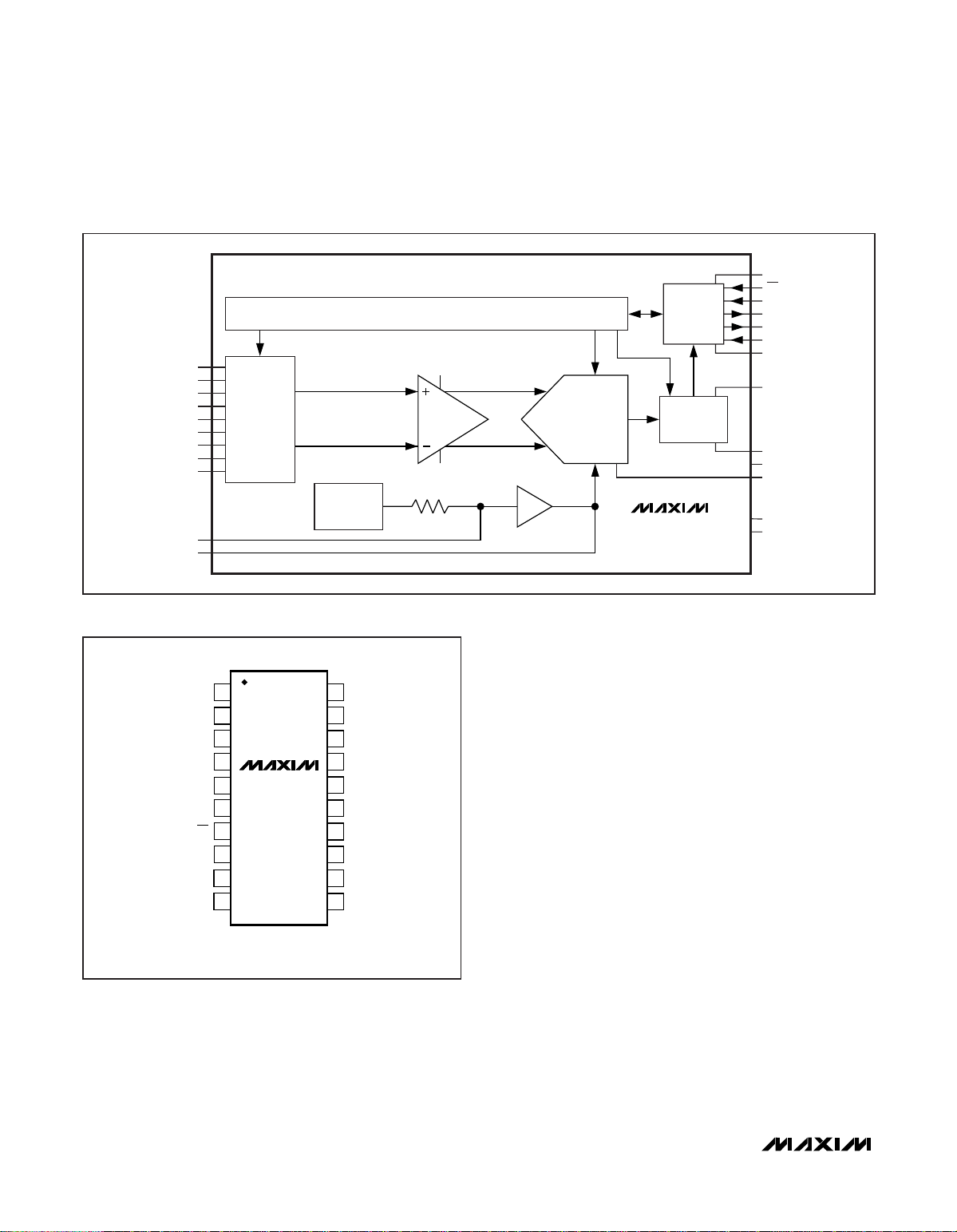

8/4通道,±V

MAX1034

CH0

CH1

CH2

CH3

CH4

CH5

CH6

CH7

AGND1

ANALOG

INPUT MUX

AND

MULTIRANGE

CIRCUITRY

PGA

AGND2

AV

DD2

4.096V

BANDGAP

REFERENCE

1x

5kΩ

IN

REF

REFCAP

REF

CONTROL LOGIC AND REGISTERS

FIFO

CLOCK

OUT

SAR

ADC

SERIAL I/O

AGND2

AV

DD2

AGND3

AV

DD1

DGND

DV

DD

DGNDO

SCLK

DOUT

SSTRB

DIN

CS

DV

DDO

20

19

18

17

16

15

14

13

1

2

3

4

5

6

7

8

AGND2

AV

DD2

AGND3

REFCH1

CH0

AV

DD1

AGND1

REFCAP

DV

DD

DV

DDO

DGNDDIN

CS

CH3

CH2

12

11

9

10

DGNDO

DOUTSCLK

SSTRB

MAX1035

TSSOP

TOP VIEW

REF

多量程输入、

串行14位ADC

_______________________________________________________________________________方框图

MAX1034/MAX1035

____________________________引脚配置 (续)

_________________________________芯片信息

TRANSISTOR COUNT: 28,210

PROCESS: BiCMOS

30 ______________________________________________________________________________________

8/4通道,±V

REF

多量程输入、

串行14位ADC

____________________________________________________________________________

(本数据资料提供的封装图可能不是最近的规格,如需最近的封装外型信息,请查询 www.maxim-ic.com.cn/packages。)

封装信息

MAX1034/MAX1035

TSSOP4.40mm.EPS

PACKAGE OUTLINE, TSSOP 4.40mm BODY

21-0066

1

G

1

MAXIM北京办事处

北京 8328信箱 邮政编码 100083

免费电话:800 810 0310

电话:010-6211 5199

传真:010-6211 5299

Maxim不对 Maxim产品以外的任何电路使用负责,也不提供其专利许可。Maxim保留在任何时间、没有任何通报的前提下修改产品资料和规格的权利。

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 ____________________ 31

© 2005 Maxim Integrated Products Printed USA

是

Maxim Integrated Products, Inc.

的注册商标。

Loading...

Loading...