Page 1

DS89C420 Ultra High

-

Speed

www.maxim

-

ic.com

Microcontroller User’s Guide

SECTION 1: INTRODUCTION

The Dallas Semiconductor DS89C420 is an 8051-compatible microcontroller that provides improved

performance and power consumption when compared to the original 8051 version. It retains instruction

set and object code compatibility with the 8051, yet performs the same operations in fewer clock cycles.

Consequently, greater throughput is possible for the same crystal speed. As an alternative, the DS89C420

can be run at a reduced frequency to save power. The more effic ient design allows a much slower crystal

speed to get the same results as an original 8051, using much less power.

The fundamental innovation of the DS89C420 is the use of only one clock per instruction cycle compared

with twelve for the original 8051. This results in up to 12 times improvement in performance over the

original 8051 architecture and up to 4 times improvement over other Dallas Semiconductor High-Speed

Microcontrollers. The DS89C420 provides several peripherals and features in addition to all of the

standard features of an 80C32. These include 16KB of on-chip flash memory, 1KB of on-chip RAM, 4

eight bit I/O ports, three 16-bit timer/counters, two on-chip UARTs, dual data pointers, an on-chip

watchdog timer, 5 levels of interrupt priority, and a crystal multiplier. The device provides 256 bytes of

RAM for variables and stack. 128 bytes can be reached using direct or indirect addressing and 128 using

only indirect addressing.

In addition to improved efficiency, the DS89C420 can operate at a maximum clock rate of 33 MHz.

Combined with the 12 times performance, this allows for a maximum performance of 33 MIPs. This

level of computing power is comparable to many 16-bit processors, but without the added expense and

complexity if implementing a 16-bit interface.

The DS89C420 incorporates a Power Management Mode which allows the device to dynamically vary

the internal clock speed from 1 clock per cycle (default) to 1024 clocks per cycle. Because power

consumption is directly proportional to clock speed, the device can reduce its operating frequency during

periods of little or no activity. This greatly reduces power consumption. The switch-back feature allows

the device to quickly return to highest speed operation upon receipt of an interrupt or serial port activity,

allowing the device to respond to external events while in Power Management Mode.

1 of 192 020602

Page 2

DS89C420 Ultra High-Speed Microcontroller User’s Guide

SECTION 2: ORDERING INFORMATION

The DS89C420 family follows the part numbering convention shown below. Note that not all

combinations of devices may be currently available. Contact a Maxim / Dallas Semiconductor Sales

Office for up to date details.

DS89C420-QCL

SPEED: L 33 MHz

TEMPERATURE: C 0 °C to 70 °C

N -40 °C to 85 °C

PACKAGE: M PDIP

Q PLCC

E Thin Quad Flat Pack (TQFP)

OPERATING VOLTAGE: 0 +5V

MEMORY TYPE: 9 Flash

2 of 192

Page 3

DS89C420 Ultra High-Speed Microcontroller User’s Guide

SECTION 3:ARCHITECTURE

The DS89C420 Architecture is based on the industry standard 87C52 and executes the standard 8051

instruction set. The core is an accumulator based architecture using internal registers for data storage and

peripheral control. This section provides a brief description of each architecture feature. Details

concerning the programming model, instruction set, and register description are provided in Section 4.

ALU

The ALU is responsible for math functions, comparisons, and general decision making in the DS89C420.

The ALU is not explicitly used by software. Instruction decoding prepares the ALU automatically and

passes it the appropriate data. The ALU primarily uses two special function registers (SFRs) as the

source and destination for all operations. These are the Accumulator and B register. The ALU also

provides status information in the Program Status Register. The SFRs are described below.

SPECIAL FUNCTION REGISTERS

All peripherals and operations that are not explicitly controlled by instructions in the DS89C420 are

controlled via Special Function Registers (SFRs). All SFRs are described in Section 4. The most

commonly used registers that are basic to the architecture are also described below.

Accumulator

The Accumulator is the primary register used in the DS89C420. It is a source and destination for many

operations involving math, data movement, and decisions. Although it can be bypassed, most high-speed

instructions require the use of the Accumulator (A or ACC) as one argument.

B Register

The B register is used as the second 8-bit argument in multiply and divide operations. When not used for

these purposes, the B register can be used as a general purpose register.

Program Status Word

The Program Status Word holds a selection of bit flags that include the Carry Flag, Auxiliary Carry Flag,

General Purpose Flag, Register Bank Select, Overflow Flag, and Parity Flag.

Data Pointer(s)

The Data Pointers (DPTR and DPTR1) are used to assign a memory address for the MOVX instructions.

This address can point to a data memory location, either on- or off-chip, or a memory mapped peripheral.

When moving data from one memory area to another or from memory to a memory mapped peripheral, a

pointer is needed for both the source and destination. The user can select the active pointer via a

dedicated SFR bit (Sel =DPS.0), or can activate an automatic toggling feature for altering the pointer

selection (TSL=DPS.5). An additional feature if selected, provides automatic incrementing or

decrementing of the current DPTR.

Stack Pointer

The Stack Pointer denotes the register location at the top of the Stack, which is the last used value. The

user can place the Stack anywhere in the scratchpad RAM by setting the Stack Pointer to the desired

location, although the lower bytes are normally used for working registers.

2 of 192

Page 4

DS89C420 Ultra High-Speed Microcontroller User’s Guide

I/O Ports

The DS89C420 offers four 8-bit I/O ports. Each I/O port is represent ed by an SFR location, and can be

written or read. The I/O port has a latch that contains the value written by software. In general, software

reads the state of external pins during a read operation.

Timer/Counters

Three 16-bit Timer/Counters are available in the DS89C420. Each timer is contained in two SFR

locations that can be written or read by software. The timers are controlled by other SFRs described in

Section 4.

UARTs

The DS89C420 provides two UARTs which are controlled and accessed by SFRs. Eac h UART has an

address that is used to read and write the UART. The same address is used for both read and write

operations, and the read and write operations are distinguished by the instruction. Each UART is

controlled by its own SFR control register.

SCRATCHPAD REGISTERS (RAM)

The High-Speed Core provides 256 bytes of Scratchpad RAM for general purpose data and variable

storage. The first 128 bytes are directly available to software. The second 128 are available through

indirect addressing discussed below. Selected portions of this RAM have other optional functions.

Stack

The stack is a RAM area that the DS89C420 uses to store return address information during Calls and

Interrupts. The user can also place variables on the stack when necessary. The Stack Pointer designates

the RAM location that is the top of the stack. Thus, depending on the value of the Stack Pointer, the

stack can be located anywhere in the 256 bytes of RAM. A common location would be in the upper 128

bytes of RAM, as these locations are accessible through indirect addressing only.

Working Registers

The first thirty-two bytes of the Scratchpad RAM can be used as four banks of eight Working Registers

for high speed data movement. Using four banks, software can quickly change cont ext by simply

changing to a different bank. In addition to the Accumulator, the Working Registers are commonly used

as data source or destination. Some of the Working Registers can also be used as pointers to other RAM

locations (indirect addressing).

PROGRAM COUNTER

The Program Counter (PC) is a 16-bit value that designates the next program address to be fetched. Onchip hardware automatically increments the PC value to move to the next ROM location.

ADDRESS/DATA BUS

The DS89C420 addresses a 64KB program and 64KB data memory area which resides in a combination

of internal and external memory. When external memory is accessed, Ports 0 and 2 are used as a

multiplexed address and data bus. The DS89C420 supports three external memory bus structures. The

non-page mode (traditional 8051) bus structure provides the address MSB on Port 2 and multiplexes Port

0 between address LSB and data. The page mode 1 bus structure uses Port 0 exclusively for data and

3 of 192

Page 5

DS89C420 Ultra High-Speed Microcontroller User’s Guide

multiplexes Port 2 between address MSB and address LSB. The page mode 2 bus structure uses Port 0

exclusively for address LSB and multiplexes Port 2 between address MSB and data. These addressing

modes are detailed later in the User Guide.

WATCHDOG TIMER

The Watchdog Timer provides a supervisory function for applications that cannot afford to run out of

control. The Watchdog Timer is a programmable free running timer. If allowed to reach the termination

of its count, if enabled, the Watchdog will reset the CPU. Software must prevent this by clearing or

resetting the Watchdog prior to its time-out.

POWER MONITOR

The DS89C420 incorporates a band -gap reference and analog circuitry to monitor the power supply

conditions. When VCC begins to drop out of tolerance, the Power Monitor will issue an optional ea rly

warning Power-fail interrupt. If power continues to fall, the Power Monitor will invoke a reset condition.

This will remain until power returns to normal operating voltage. The Power Monitor also functions on

power-up, holding the microcontroller in a reset state until power is stable.

INTERRUPTS

The DS89C420 is capable of evaluating thirteen interrupt sources simultaneously. Each interrupt has an

associated interrupt vector, flag, priority, and enable. These interrupts can be globally enabled or

disabled.

TIMING CONTROL

The DS89C420 provides an on-chip oscillator for use with an external crystal. This can be bypassed by

injecting a clock source into the XTAL 1 pin. The clock source is used to create machine cycle timing

(four clocks), ALE, PSEN, Watchdog, Timer, and serial baud rate timing. In addition, an on-chip ring

oscillator can be used to provide an approximately 10 MHz clock source. A frequency multiplier feature

is included which can be selected by SFR control to multiply the input clock source by either 2 or 4. This

allows lower frequency (and cost) crystals to be used while still allowing internal operation up to the full

33 MHz limit.

FLASH MEMORY

On-chip program memory is impemented in 16KB of Flash Memory. This can be programmed in system

with the standard 5 volt V

port (in-system) using a built-in program memory Loader (ROM Loader) or by a standard Flash or

EPROM programmer. Full programming details are given in Section 15.

The DS89C420 incorporates a Memory Management Unit (MMU) and other hardware to support any of

the three programming methods. The MMU controls program and data memory access, and provides

sequencing and timing controls for programming of the on-chip program memory. There is also a

separate Security Flash block which is used to support a standard three-level lock, a 64-byte encryption

array and other Flash options.

The full on-chip program memory range can be fetched by the processor automatically. Reset routines

and all interrupt vectors are located in the lower 128 bytes of the on-chip program memory area.

supply under the control of the user software (in-application), or via a serial

CC

4 of 192

Page 6

DS89C420 Ultra High-Speed Microcontroller User’s Guide

SECTION 4: PROGRAMMING MODEL

This section provides a programmer’s overview of the Ultra High-Speed Microcontroller core. It

includes information on the memory map, on-chip RAM, Special Function Registers (SFRs), and

instruction set. The programming model of the Ultra High-Speed Microcontroller is very similar to that

of the industry standard 80C52. The memory map is identical. It uses the same instruction set, with

improved instruction timing. Several new SFRs have been added.

MEMORY ORGANIZATION

The Ultra High-Speed Microcontroller, like the 8052, uses several distinct memory areas. These areas

include Registers, program memory, and data memory. Registers serve to control on-chip peripherals and

as RAM. Note that registers (on-chip RAM) are separate from data memory. Registers are divided into

three categories including directly addressed on-chip RAM, indirectly addressed on-chip RAM, and

Special Function Registers. The program and data memory areas are discussed under Memory Map. The

Registers are discussed under Register Map.

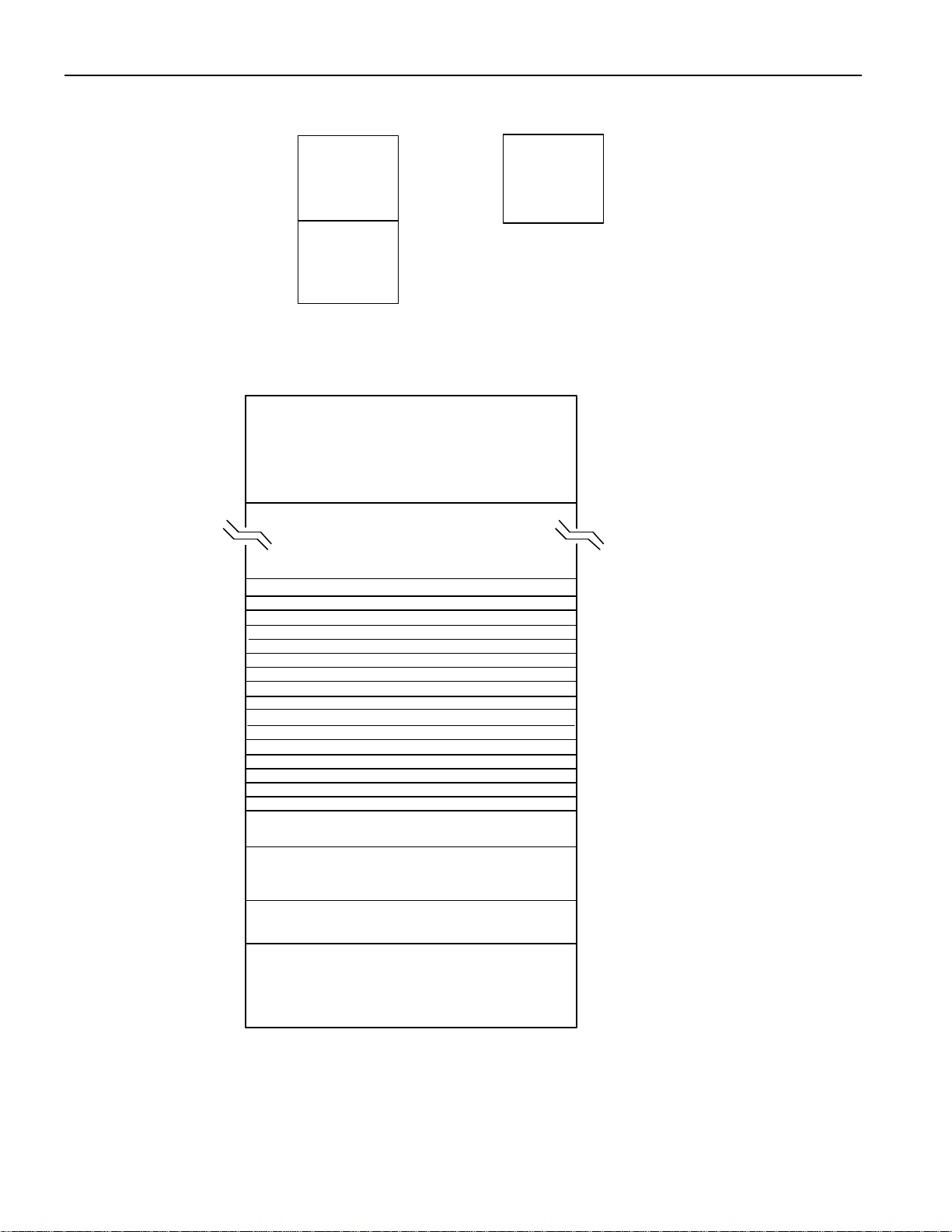

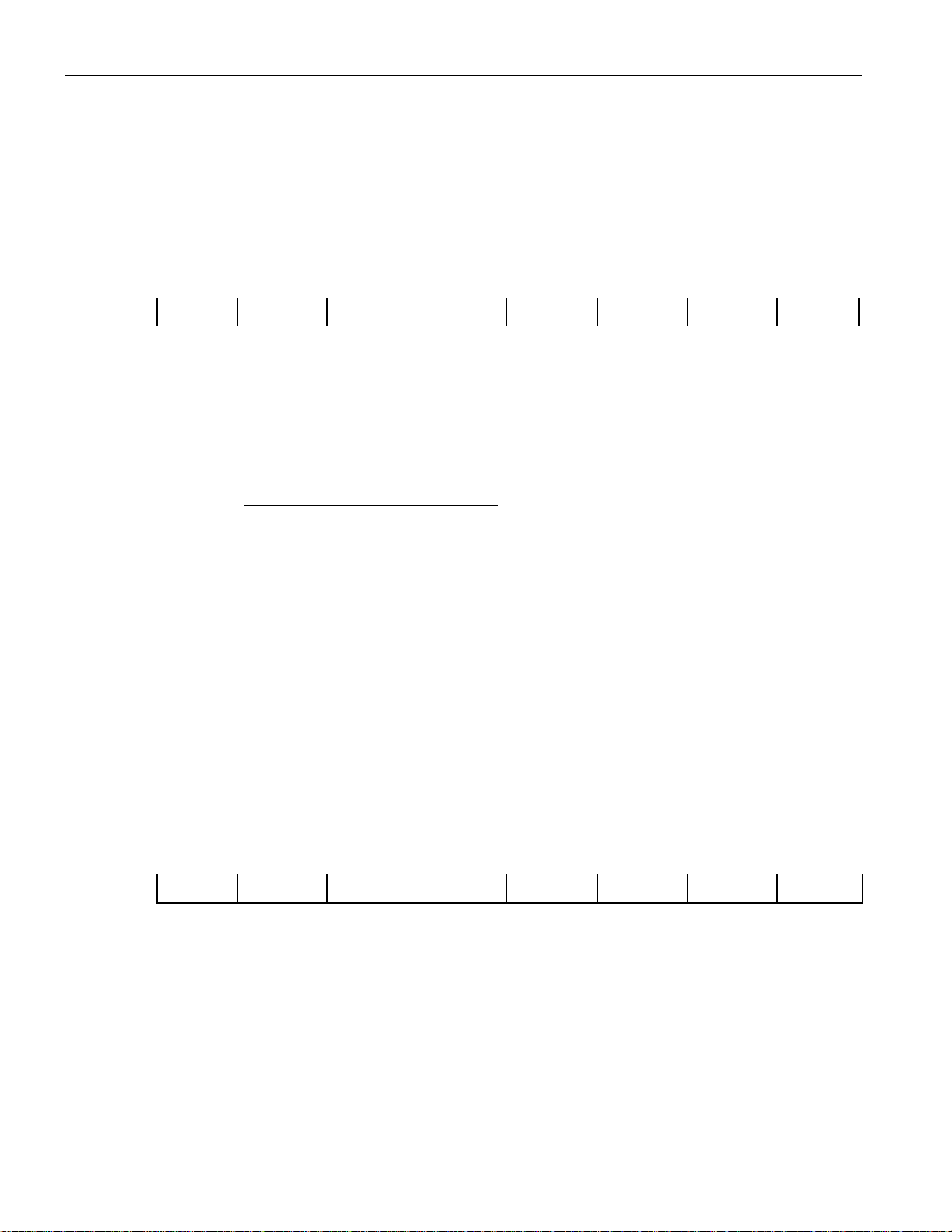

MEMORY MAP

The Ultra High-Speed Microcontroller uses a memory addressing scheme that separates program memory

from data memory. Each area is 64KB beginning at address 0000h and ending at FFFFh as shown in

Figure 4-1. The program and data segments can overlap since they are accessed in different ways.

Program memory is fetched by the microcontroller automatically. These addresses are never written by

software. In fact, there are no instructions that allow the program area to be written. There is one

instruction (MOVC) that is used to explicitly read the program area. This is commonly used to read lookup tables. The data memory area is accessed explicitly using the MOVX instruction. This instruction

provides multiple ways of specifying the target address. It is used to access the 64KB of data memory.

The address and data range of devices with on-chip program and data memory overlap the 64K memory

space. When on-chip memory is enabled, accessing memory in the on-chip range will cause the device to

access internal memory. Memory accesses beyond the internal range will be addressed externally via

ports 0 and 2.

The ROMSIZE feature allows software to dynamically configure the maximum address of on-chip

program memory. This allows the device to act as a bootstrap loader for an external Flash or Nonvolatile

SRAM. Secondly, this method can also be used to increase the amount of available program memory

from 64KB to 80KB without bank switching. For more information on this feature, please consult

Section 6.

Program and data memory can also be increased beyond the 64KB limit using bank switching techniques.

This is described in Application Note 81, Memory Expansion with the High-Speed Microcontroller

family.

REGISTER MAP

The Register Map is illustrated in Figure 4-2. It is entirely separate from the program and data memory

areas mentioned above. A separate class of instructions is used to access the registers. There are 256

potential register location values. In practice, the Ultra High-Speed Microcontroller has 256 bytes of

Scratchpad RAM and up to 128 Special Function Registers (SFRs). This is possible since the upper 128

Scratchpad RAM locations can only be accessed indirectly. That is, the contents of a Working Register

(R0 or R1) or the stack pointer (described below) will designate the RAM location. A direct reference to

one of the lower 128 addresses (0-7Fh) will access the Scratchpad RAM. A direct reference to one of the

5 of 192

Page 7

DS89C420 Ultra High-Speed Microcontroller User’s Guide

PROGRAM

DATA

upper 128 addresses (80h - FFh) must be an SFR access. In contrast, indirect references can access the

entire Scratchpad RAM range (0h-FFh).

Scratchpad RAM is available for general purpose data storage. It is commonly used in place of off-chip

RAM when the total data contents are small. When off-chip RAM is needed, the Scratchpad area will

still provide the fastest general purpose access. Within the 256 bytes of RAM, there are several special

purpose areas. These are described as follows:

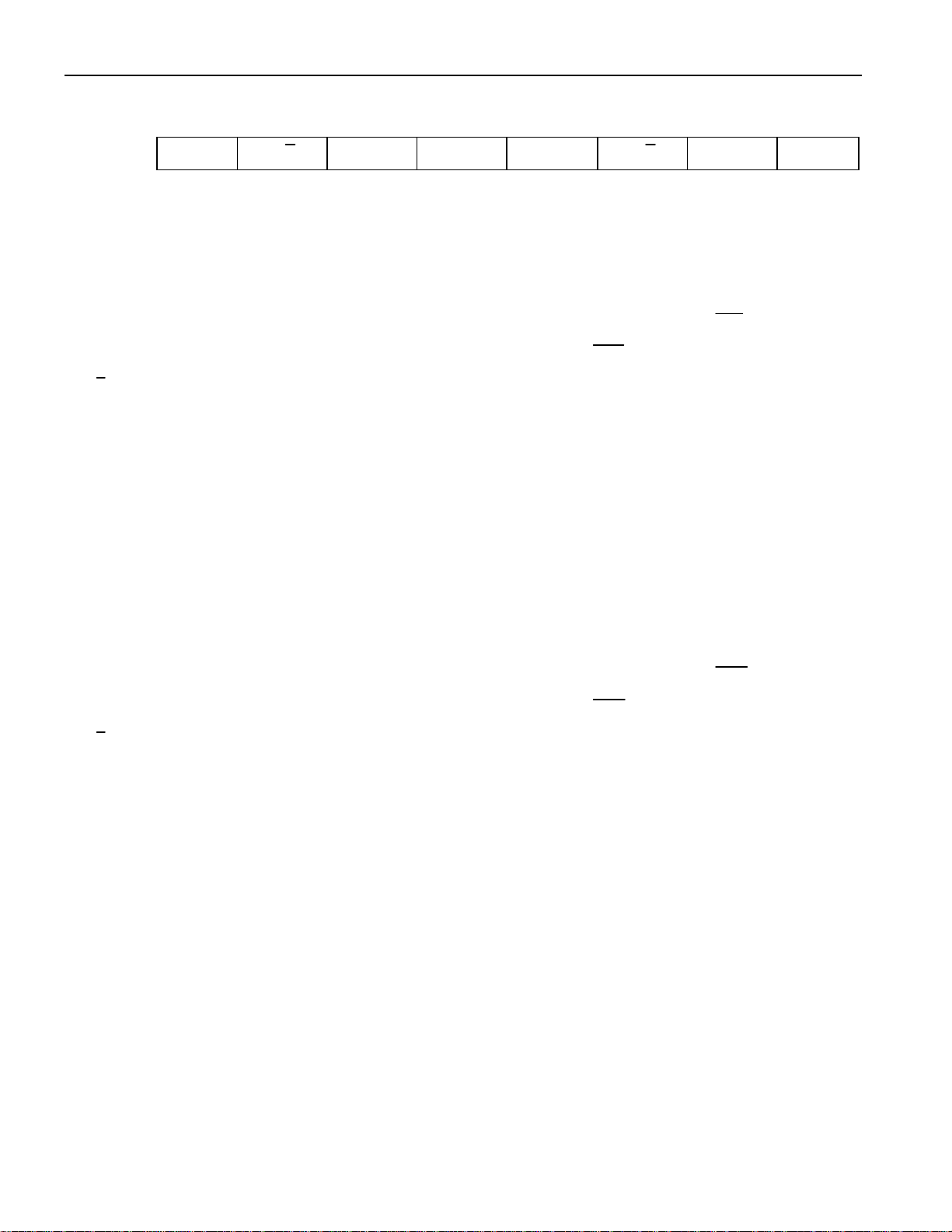

Bit Addressable Locations

In addition to direct register access, some individual bits are also accessible. These are individually

addressable bits in both the RAM and SFR area. In the Scratchpad RAM area, registers 20h to 2Fh are

bit addressable. This provides 128 (16 * 8) individual bits available to software. A bit access is

distinguished from a full register access by the type of instruction. Addressing modes are discussed later

in this section. In the SFR area, any register location ending in a 0 or 8 is bit addressable. Figure 4-3

shows details of the on-chip RAM addressing including the locations of individual RAM bits.

Working Registers

As part of the lower 128 bytes of RAM, there are four banks of Working Registers (8 bytes each). The

Working registers are general purpose RAM locations that can be addressed in a special way. They are

designated R0 through R7. Since there are four ba nks, the currently selected bank will be used by any

instruction using R0-R7. This allows software to change context by simply switching banks. This is

controlled via the Program Status Word register in the SFR area described below. The Working Registers

also allow their contents to be used for indirect addressing of the upper 128 bytes of RAM. Thus an

instruction can designate the value stored in R0 (for example) to address the upper RAM. This value

might be the result of another calculation.

Stack

Another use of the Scratchpad area is for the programmer’s stack. This area is selected using the Stack

Pointer (SP;81h) SFR. Whenever a call or interrupt is invoked, the return address is placed on the Stack.

It also is available to the programmer for variables, etc. since the Stack can be moved, there is no fixed

location within the RAM designated as Stack. The Stack Pointer will default to 07h on reset. The user

can then move it as needed. A convenient location would be the upper RAM area (>7Fh) since this is

only available indirectly. The SP will point to the last used value. Therefore, the next value placed on

the Stack is put at SP + 1. Each PUSH or CALL will increment the SP by the appropriate value. Each

POP or RET will decrement as well.

MEMORY MAP Figure 4-1

0000h

MEMORY

MEMORY

64K FFFFh

6 of 192

Page 8

DS89C420 Ultra High-Speed Microcontroller User’s Guide

FFh

DIRECT

INDIRECT

DIRECT

REGISTER MAP Figure 4-2

FFh

RAM

7Fh

255

128

SPECIAL

FUNCTION

REGISTERS

FFh

7Fh

0000h

RAM

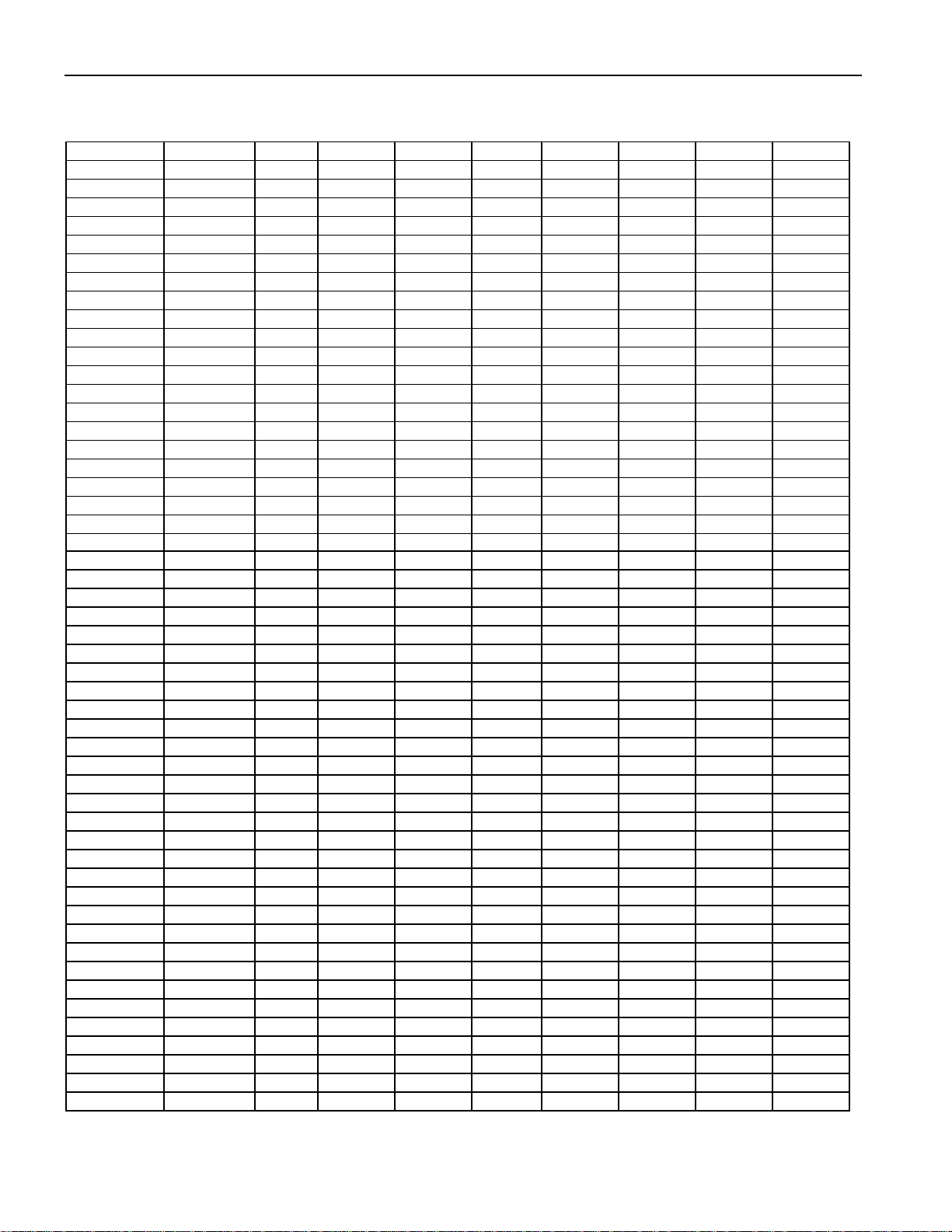

SCRATCHPAD REGISTER ADDRESSING Figure 4-3

INDIRECT RAM

7Fh

DIRECT RAM

2Fh 7F 7E 7D 7C 7B 7A 79 78

2Eh 77 76 75 74 73 72 71 70

2Dh 6F 6E 6D 6C 6B 6A 69 68

2Ch 67 66 65 64 63 62 61 60

2Bh 5F 5E 5D 5C 5B 5A 59 58

2Ah 57 56 55 54 53 52 51 50

29h 4F 4E 4D 4C 4B 4A 49 48

28h 47 46 45 44 43 42 41 40

27h 3F 3E 3D 3C 3B 3A 39 38

26h 37 36 35 34 333 32 31 30

25h 2F 2E 2D 2C 2B 2A 29 28

24h 27 26 25 24 23 22 21 20

23h 1F 1E 1D 1C 1B 1A 19 18

22h 17 16 15 14 13 12 11 10

21h 0F 0E 0D 0C 0B 0A 09 08

20h 07 06 05 04 03 02 01 00

1Fh

BANK 3

18h

17h

BANK 2

10h

0Fh

BANK 1

08h

07h

BANK 0

00h

MSB LSB

7 of 192

Page 9

DS89C420 Ultra High-Speed Microcontroller User’s Guide

ADDRESSING MODES

The Ultra High-Speed Microcontroller uses the standard 8051 instruction set which is supported by a

wide range of third party assemblers and compilers. Like the 8051, the Ultra High-Speed Microcontroller

uses three memory areas. These are program memory, data memory, and Registers. The program and data

areas are 64KB each. They extend from 0000h to FFFFh. The register areas are located between 00h and

FFh, but do not overlap with the program and data segments. This is because the Ultra High-Speed

Microcontroller uses different modes of addressing to reach each memory segment. These modes are

described below.

Program memory is the area from which all instructions are fetched. It is inherently read only. This is

because the 8051 instruction set provides no instructions that write to this area. Read/write access is for

data memory and Registers only. No special action is required to fetch from program memory. Each

instruction fetch will be performed automatically by the on-chip CPU. In versions that contain on chip

memory, the hardware will decide whether the fetch is on-chip or off-chip based on the address. Explicit

addressing modes are needed for the data memory and register areas. These modes determine which

register area is accessed or if off-chip data memory is used.

The Ultra High-Speed Microcontroller supports eight addressing modes. They are:

Register Addressing

Direct Addressing

Register Indirect Addressing

Immediate Addressing

Register Indirect Addressing with Displacement

Relative Addressing

Page Addressing

Extended Ad dressing

Five of the eight are used to address operands. The remainder are used for program control and

branching. When writing assembly language instructions that use arguments, the convention is

destination, source. Each mode of addressing is summarized below. Note that many instructions (such as

ADD) have multiple addressing modes available.

8 of 192

Page 10

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Register Addressing

Register Addressing is used for operands that are located in one of the eight Working Registers (R7 -R0).

The eight Working Registers can be located in one of four Working Register banks found in the lower 32

bytes of Scratchpad RAM, as determined by the current register bank select bits. A register bank is

selected using two bits in the Program Status Word (PSW;D0h). This addressing mode is powerful, since

it uses the active bank without knowing which bank is selected. Thus one instruction can have multiple

uses by simply switching banks. Register Addressing is also a high-speed instruction, requiring only one

machine cycle. Two examples of Register Addressing are provided below.

ADD A, R4 ;Add register R4 to Accumulator

INC R2 ;Increment the value in register R2

In the first case, the value in R4 is the source of the operation. In the later, R2 is the destination. These

instructions do not consider the absolute address of the register. They will act on whichever bank has

been selected.

Any Working Register may also be accessed by Direct Addressing, described below. To do this, the

absolute address must be specified.

Direct Addressing

Direct Addressing is the mode used to access the entire lower 128 bytes of Scratchpad RAM and the SFR

area. It is commonly used to move the value in one register to another. Two examples are shown below.

MOV 72h, 74h ;Move the value in register 74 to

;register 72.

MOV 90h, 20h ;Move the value in register 20 to

;the SFR at 90h (Port 1)

Note that there is no instruction difference between a RAM access and an SFR access. The SFRs are

simply register locations above 7Fh.

Direct Addressing also extends to bit addressing. There is a group of instructions that explicitly use bits.

The address information provided to such an instruction is the bit location, rather than the register

address. Registers between 20h and 2Fh contain bits that are individually addressable. SFRs that end in

0 or 8 are bit addressable. An example of Direct Bit Addressing is as follows.

SETB 00h ;Set bit 00 in the RAM. This is the

;LSb of the register at address 20h

;as shown earlier in this section.

MOV C, 0B7h ;Move the contents of bit B7 to the

;Carry flag. Bit B7 is the MSb of

;register B0 (Port 3).

9 of 192

Page 11

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Register Indirect Addressing

This mode is used to access the Scratchpad RAM locations above 7Fh. It can also be used to reach the

lower RAM (0h - 7Fh) if needed. The address is supplied by the contents of the Working Register

specified in the instruction. Thus one instruction can be used to reach many values by altering the

contents of the designated Working Register. Note that in general, only R0 and R1 can be used as

pointers. An example of Register Indirect Addressing is as follows.

ANL A, @R0 ;Logical AND the Accumulator

;with the contents of the register

;pointed to by the value stored in R0.

This mode is also used for Stack manipulation. This is becaus e all Stack references are directed by the

value in the Stack Pointer register. The Push and Pop instructions use this method of addressing. An

example is as follows.

PUSH A ;Saves the contents of the

;accumulator on the stack.

Register Indirect Addressing is used for all off-chip data memory accesses. These involve the MOVX

instruction. The pointer registers can be R0, R1, DPTR0 and DPTR1. Both R0 and R1 reside in the

Working Register area of the Scratchpad RAM. They can be used to reference a 256 byte area of off-chip

data memory. When using this type of addressing, the upper address byte is supplied by the value in the

Port 2 latch. This value must be selected by software prior to the MOVX instruction. An example is as

follows.

MOVX @R0, A ;Write the value in the accumulator

;to the address pointed to by R0 in

;the page pointed to by P2.

The 16-bit Data pointers (DPTRs) can be used as an absolute off-chip reference. This gives access to the

entire 64KB data memory map. An example is as follows.

MOVX @DPTR, A ;Write the value in the accumulator

;to the address referenced by the

;selected data pointer.

Immediate Addressing

Immediate Addressing is used when one of the operands is predetermined and coded into the software.

This mode is commonly used to initialize SFRs and to mask particular bits without affecting others. An

example is as follows.

ORL A, #40h ;Logical OR the Accumulator with 40h.

10 of 192

Page 12

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Register Indirect with Displacement

Register Indirect Addressing with Displacement is used to access data in lookup tables in program

memory space. The location is created using a base address with an index. The base address can be

either the PC or the DPTR. The index is the accumulator. The result is stored in the accumulator. An

example is as follows.

MOVC A, @A +DPTR ;Load the accumulator with the contents

of program memory

;pointed to by the contents of the DPTR

plus the value in

;the accumulator.

Relative Addressing

Relative Addressing is used to determine a destination address for Conditional branch. Each of these

instructions includes an 8-bit value that contains a two’s complement address offset (–127 to +128) which

is added to the PC to determine the destination address. This destination is branched to when the tested

condition is true. The PC points to the program memory location immediately following the branch

instruction when the offset is added. If the tested condition is not true, the next instruction is performed.

An example is as follows.

JZ $–20 ;Branch to the l ocation (PC+2)–20

;if the contents of the accumulator = 0.

Page Addressing

Page Addressing is used by the Branching instructions to specify a destination address within the same

2KB block as the next contiguous instruction. The full 16-bit address is calculated by taking the five

highest order bits for the next instruction (PC+2) and concatenating them with the lowest order 11 bit

field contained in the current instruction. An example is as follows.

0870h ACALL 100h ;Call to the subroutine at address 100h

plus the

;current page address.

In this example, the current page address is 800h, so the destination address is 900h.

Extended Addressing

Extended Addressing is used by the Branching instructions to specify a 16-bit destination address within

the 64KB address space. The destination address is fixed in software as an absolute value. An example

is as follows.

LJMP 0F732h ;Jump to address 0F732h.

11 of 192

Page 13

DS89C420 Ultra High-Speed Microcontroller User’s Guide

PROGRAM STATUS FLAGS

All Program Status Flags are contained in the Program Status Word at SFR location D0h. It contains

flags that reflect the status of the CPU and the result of selected operations. The flags are summarized

below. The following table shows the instructions that affect each flag.

Bit Description :

PSW.7 C

Carry Set when the previous operation resulted in a carry (during addition) or a

borrow (during subtraction), otherwise cleared.

PSW.6 AC

Auxiliary Carry Set when the previous operation resulted in a carry (during addition) or a

borrow (during subtraction) from the high orde r nibble. Otherwise cleared.

PSW.2 OV

Overflow For addition, set when a carry was generated into a high order bit (bit 6 or

bit 7), but not a carry out of the same high order bit. For subtraction, OV

set if a borrow is needed into a high order bit (b it 6 or bit 7), but not into the

other high order bit. For multiplication, OV is set when the product

exceeds FFh. For division, OV is always cleared.

PSW.0 P

Parity Set to logic 1 to indicate an odd number of ones in the accumulator (odd

parity). Cleared for an even number of ones. This produces even parity.

All of these bits are cleared to a logic 0 for all resets.

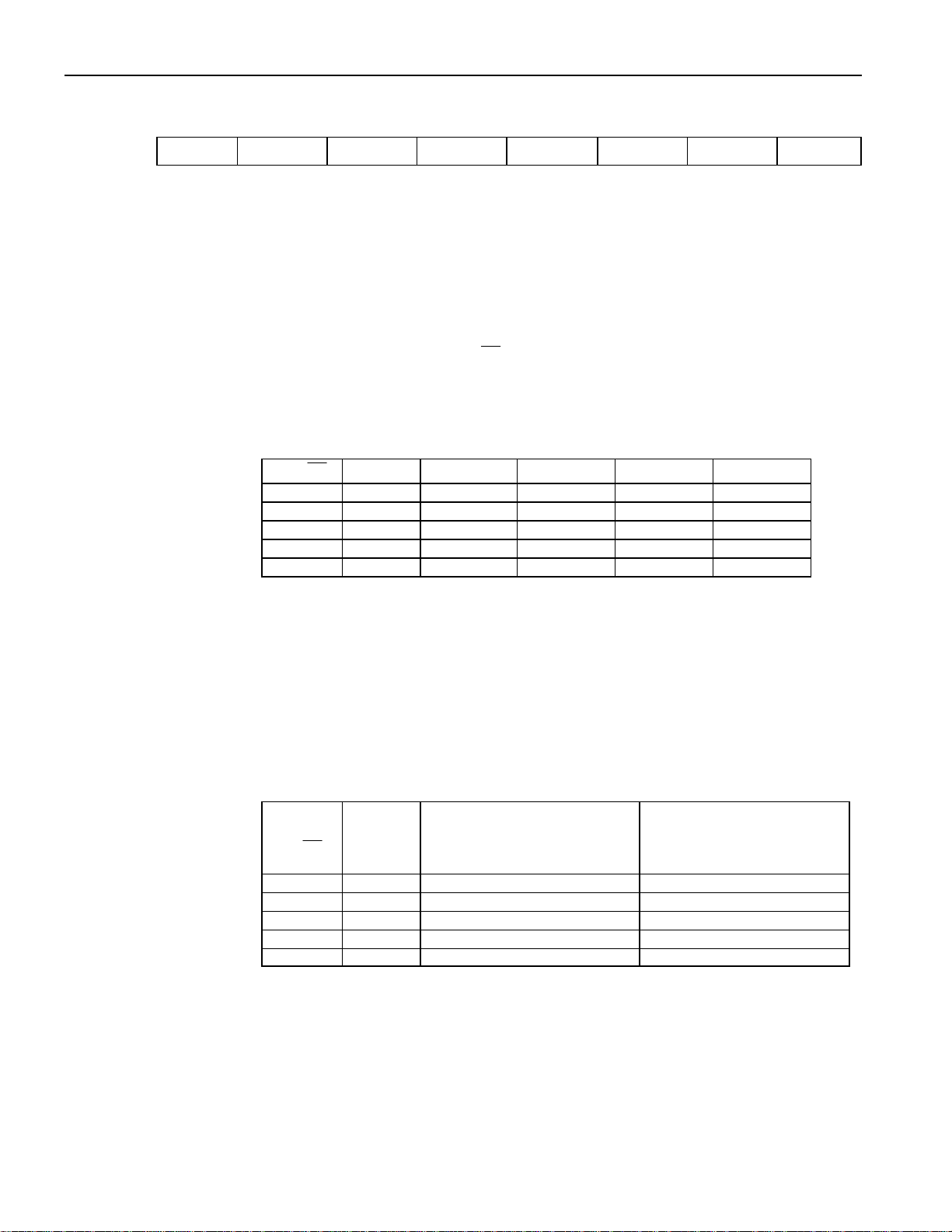

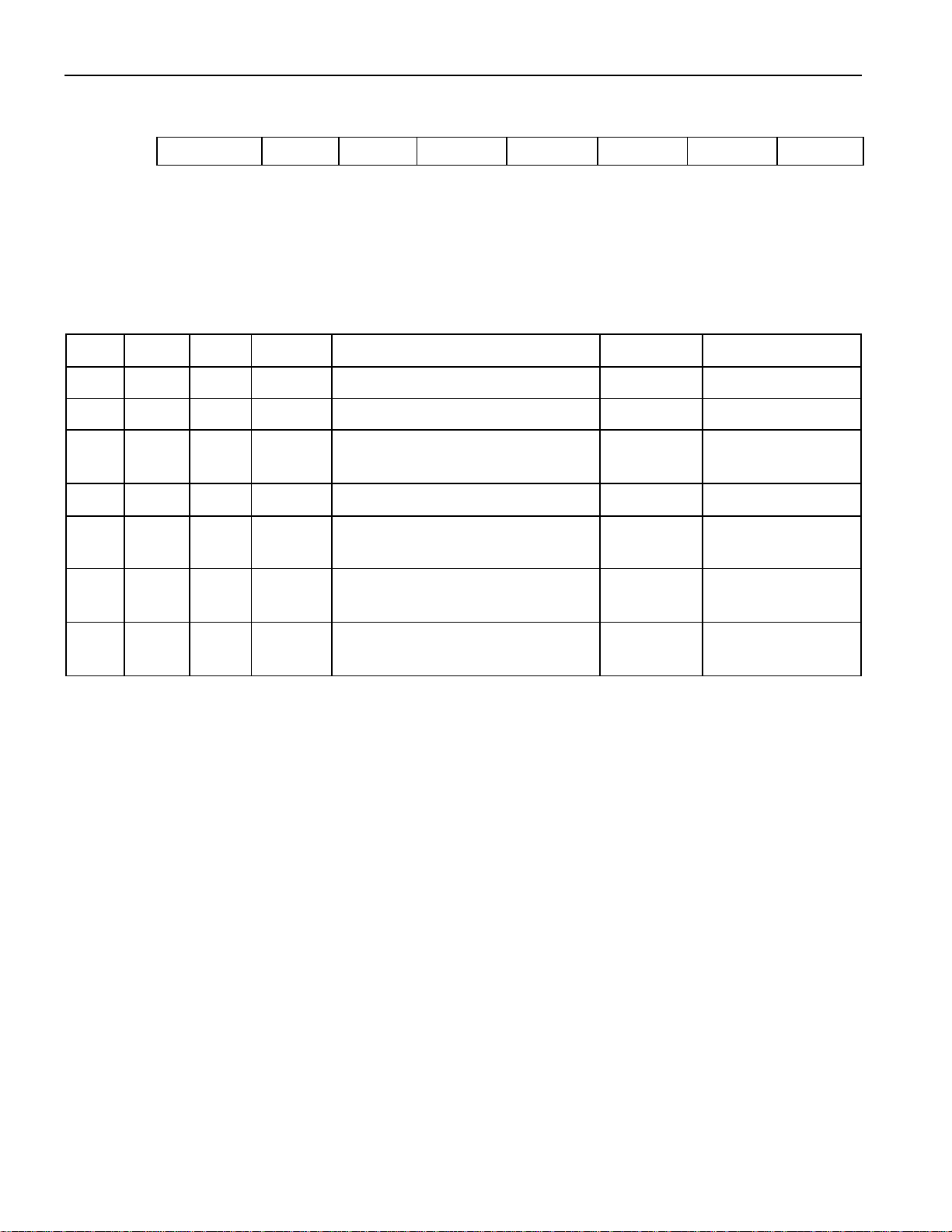

INSTRUCTIONS THAT AFFECT FLAG SETTINGS Table 4-1

INSTRUCTION FLAGS INSTRUCTION FLAGS

C OV AC C OV AC

ADD X X X CLR C 0

ADDC X X X CPL C X

SUBB X X X ANL C, bit X

MUL 0 X

DIV 0 X

DA X

RRC X MOV C, bit X

RLC X CJNE X

SETB C 1

ANL C, bit

ORL C, bit

ORL C, bit

X indicates the modification is according to the result of the instruction.

X

X

X

12 of 192

Page 14

DS89C420 Ultra High-Speed Microcontroller User’s Guide

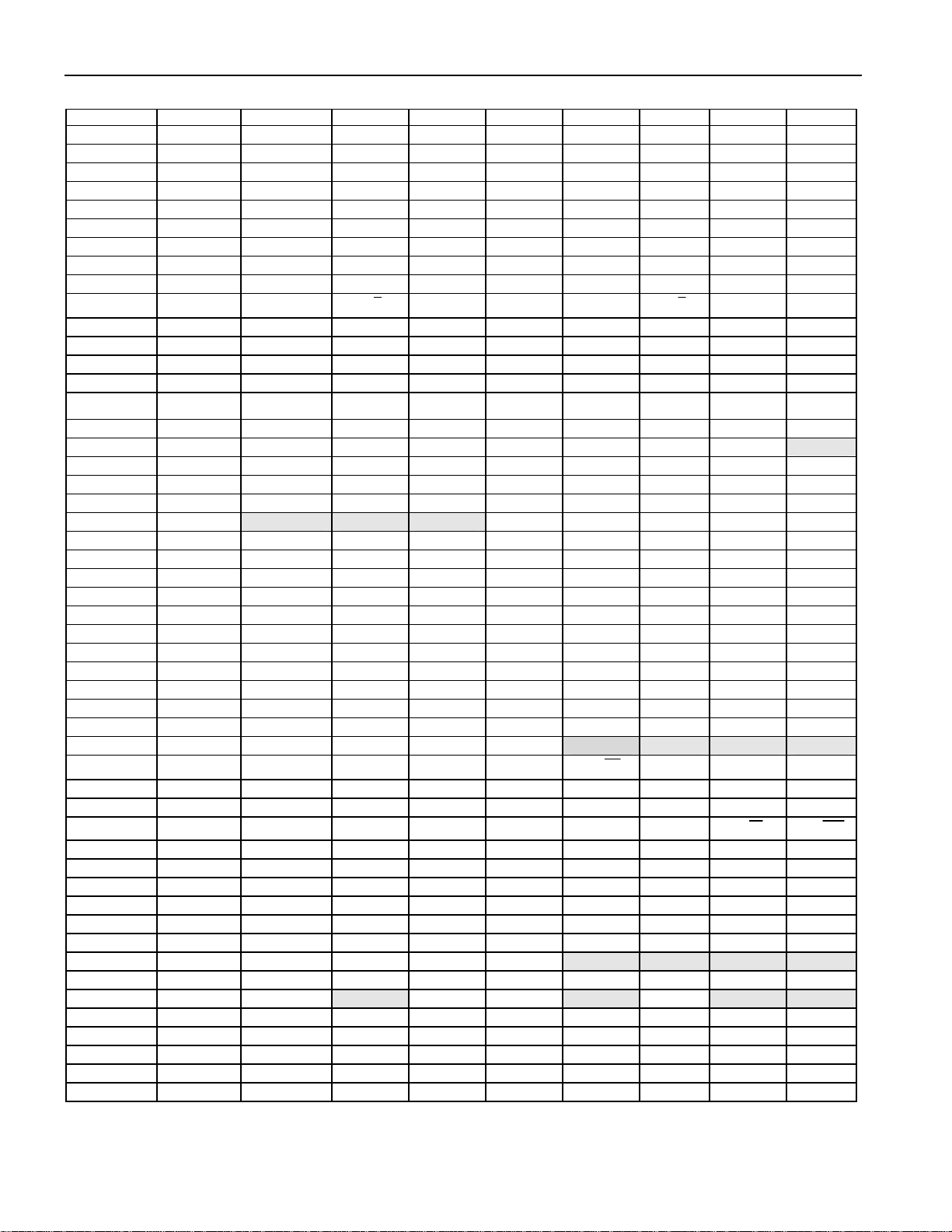

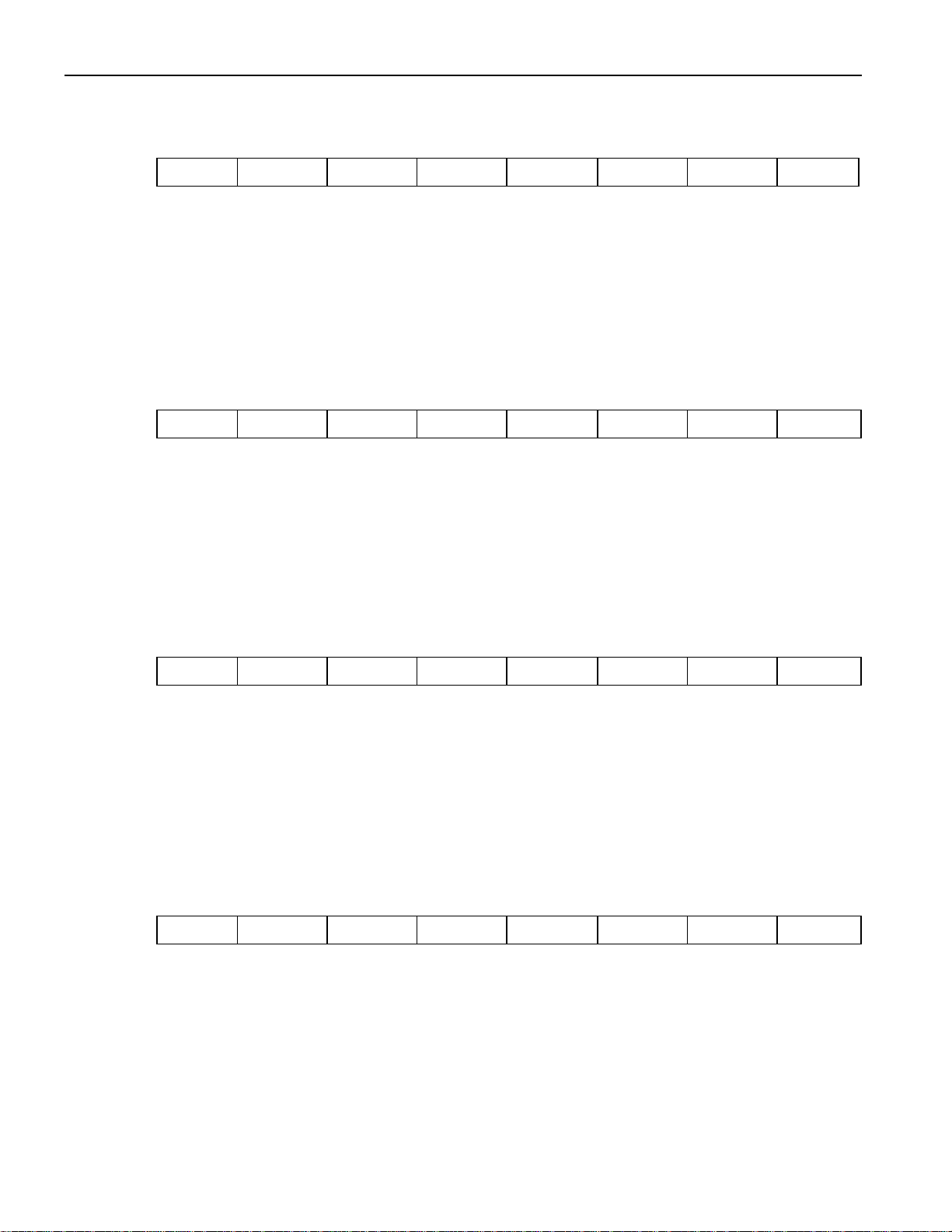

SPECIAL FUNCTION REGISTERS

The DS89C420, like the 8051, uses Special Function Registers (SFRs) to control peripherals and modes.

In many cases, an SFR will control individual functions or report status on individual functions. The

SFRs reside in register locations 80h-FFh and are reached using direc t addressing. SFRs that end in 0 or

8 are bit addressable.

All standard SFR locations from the original 8051 are duplicated in the DS89C420, with several

additions. Tables are provided to illustrate the locations of the SFRs for the DS89C420 device and t he

default reset conditions of all SFR bits. Detailed descriptions of each Special Function Register follow.

13 of 192

Page 15

DS89C420 Ultra High-Speed Microcontroller User’s Guide

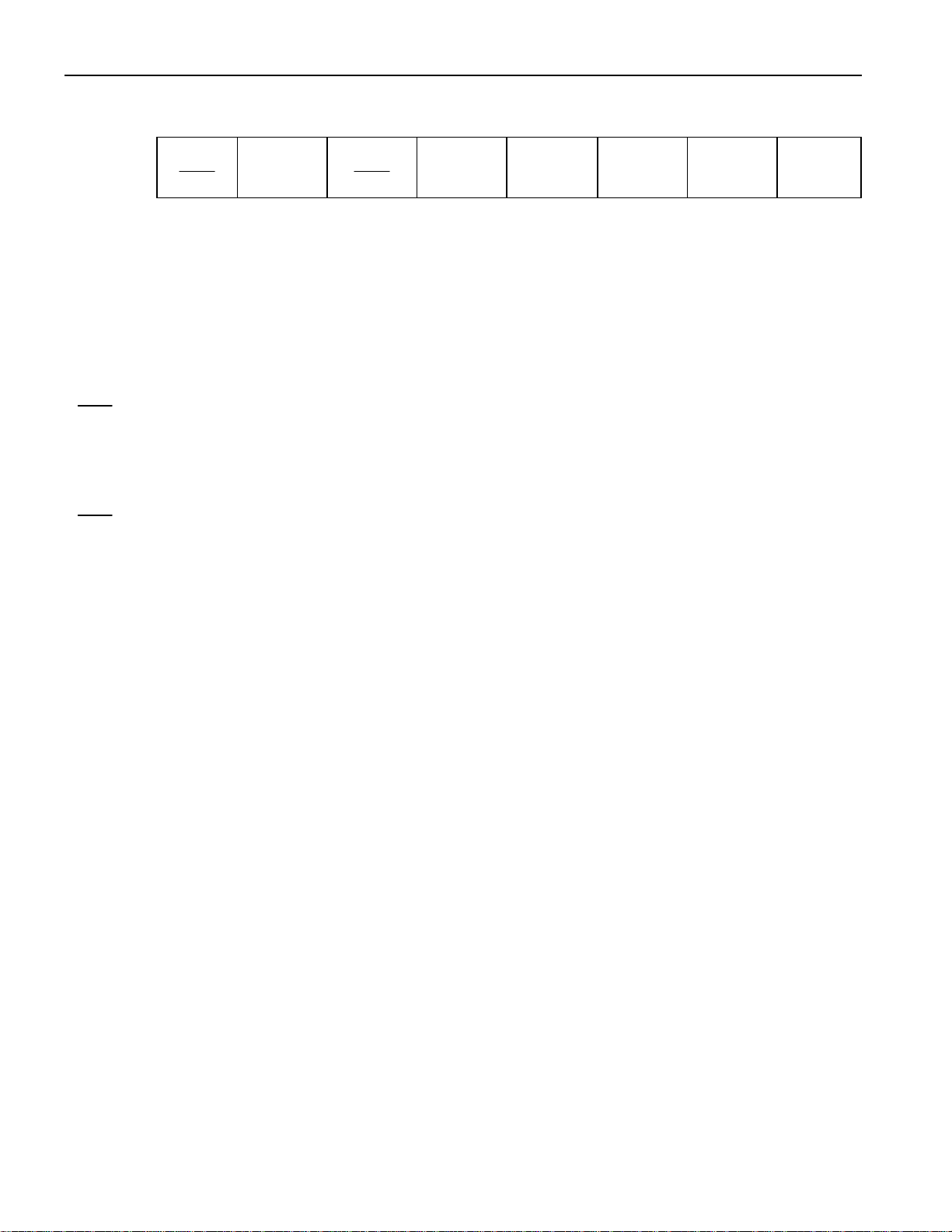

DS89C420 SPECIAL FUNCTION REGISTER LOCATIONS

REGISTER ADDRESS BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

P0 80h P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

SP 81h

DPL 82h

DPH 83h

DPL1 84h

DPH1 85h

DPS 86h ID1 ID0 TSL AID - - - SEL

PCON 87h SMOD_0 SMOD0 OFDF OFDE GF1 GF0 STOP IDLE

TCON 88h TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TMOD 89h GATE

TL0 8Ah

TL1 8Bh

TH0 8Ch

TH1 8Dh

CKCON 8Eh WD1 WD0 T2M T1M T0M MD2 MD1 MD0

P1 90h P1.7 P1.6 P1.5 P1.4 P1.3 P1.2 P1.1 P1.0

EXIF 91h IE5 IE4 IE3 IE2 CKRY RGMD RGSL BGS

CKMOD 96h

SCON0 98h SM0/FE_0 SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0

SBUF0 99h

ACON 9Dh PAGEE PAGES1 PAGES0

P2 A0h P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

IE A8h EA ES1 ET2 ES0 ET1 EX1 ET0 EX0

SADDR0 A9h

SADDR1 AAh

P3 B0h P3.7 P3.6 P3.5 P3.4 P3.3 P3.2 P3.1 P3.0

IP1 B1h - MPS1 MPT2 MPS0 MPT1 MPX1 MPT0 MPX0

IP0 B8h - LPS1 LPT2 LPS0 LPT1 LPX1 LPT0 LPX0

SADEN0 B9h

SADEN1 BAh

SCON1 C0h SM0/FE_1 SM1_1 SM2_1 REN_1 TB8_1 RB8_1 TI_1 RI_1

SBUF1 C1h

ROMSIZE C2h PRAME RMS2 RMS1 RMS0

PMR C4h CD1 CD0 SWB CTM

STATUS C5h PIS2 PIS1 PIS0 - SPTA1 SPRA1 SPTA0 SPRA0

TA C7h

T2CON

T2MOD C9h - - - - - - T2OE DCEN

RCAP2L CAh

RCAP2H CBh

TL2 CCh

TH2 CDh

PSW D0h CY AC F0 RS1 RS0 OV F1 P

FCNTL D5h FBUSY FERR FC3 FC2 FC1 FC0

FDATA D6h

WDCON D8h SMOD_1 POR EPFI PFI WDIF WTRF EWT RWT

ACC E0h

EIE E8h - - - EWDI EX5 EX4 EX3 EX2

B F0h

EIP1 F1h MPWDI MPX5 MPX4 MPX3 MPX2

EIP0 F8h - - - LPWDI LPX5 LPX4 LPX3 LPX2

C8h

TF2 EXF2 RCLK TCLK EXEN2 TR2 C/ T2 CP/ RL2

C/ T

T2MH T1MH T0MH

Shaded bits are Timed Access protected

M1 M0 GATE

4X/ 2X

C/ T

ALEON DME1 DME0

M1 M0

14 of 192

Page 16

DS89C420 Ultra High-Speed Microcontroller User’s Guide

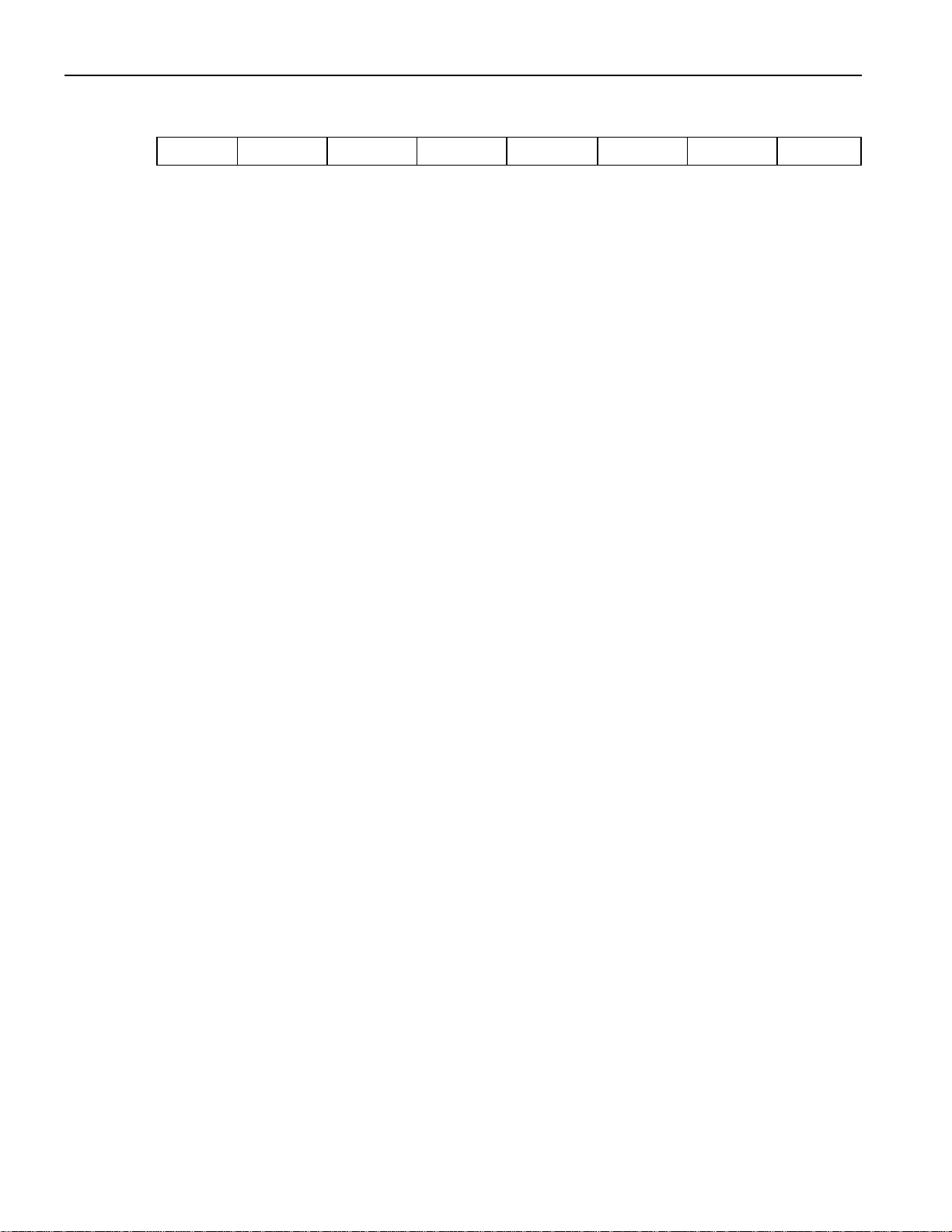

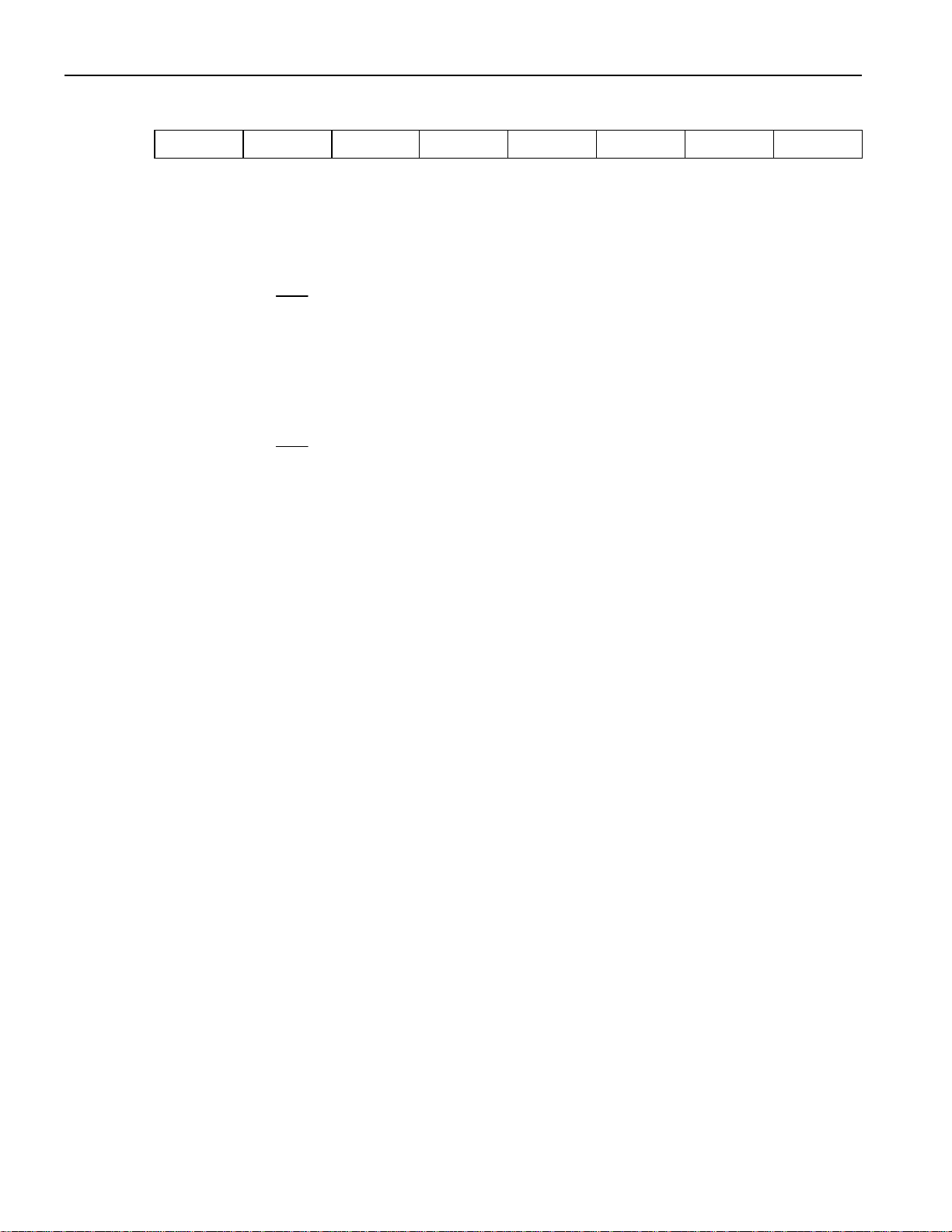

DS89C420 SPECIAL FUNCTION REGISTER RESET

VALUES

REGISTER ADDRESS BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

P0 80h 1 1 1 1 1 1 1 1

SP 81h 0 0 0 0 0 1 1 1

DPL 82h 0 0 0 0 0 0 0 0

DPH 83h 0 0 0 0 0 0 0 0

DPL1 84h 0 0 0 0 0 0 0 0

DPH1 85h 0 0 0 0 0 0 0 0

DPS 86h 0 0 0 0 0 1 0 0

PCON 87h 0 0 Special Special 0 0 0 0

TCON 88h 0 0 0 0 0 0 0 0

TMOD 89h 0 0 0 0 0 0 0 0

TL0 8Ah 0 0 0 0 0 0 0 0

TL1 8Bh 0 0 0 0 0 0 0 0

TH0 8Ch 0 0 0 0 0 0 0 0

TH1 8Dh 0 0 0 0 0 0 0 0

CKCON 8Eh 0 0 0 0 0 0 0 1

P1 90h 1 1 1 1 1 1 1 1

EXIF 91h 0 0 0 0 Special Special Special 0

CKMOD 96h 1 1 0 0 0 1 1 1

SCON0 98h 0 0 0 0 0 0 0 0

SBUF0 99h 0 0 0 0 0 0 0 0

ACON 9Dh 0 0 0 1 1 1 1 1

P2 A0h 1 1 1 1 1 1 1 1

IE A8h 0 0 0 0 0 0 0 0

SADDR0 A9h 0 0 0 0 0 0 0 0

SADDR1 AAh 0 0 0 0 0 0 0 0

P3 B0h 1 1 1 1 1 1 1 1

IP1 B1h 1 0 0 0 0 0 0 0

IP0 B8h 1 0 0 0 0 0 0 0

SADEN0 B9h 0 0 0 0 0 0 0 0

SADEN1 BAh 0 0 0 0 0 0 0 0

SCON1 C0h 0 0 0 0 0 0 0 0

SBUF1 C1h 0 0 0 0 0 0 0 0

ROMSIZE C2h 1 1 1 1 0 1 0 1

PMR C4h 1 0 0 0 0 0 0 0

STATUS C5h 0 0 0 1 0 0 0 0

TA C7h 1 1 1 1 1 1 1 1

T2CON C8h 0 0 0 0 0 0 0 0

T2MOD C9h 1 1 1 1 1 1 0 0

RCAP2L CAh 0 0 0 0 0 0 0 0

RCAP2H CBh 0 0 0 0 0 0 0 0

TL2 CCh 0 0 0 0 0 0 0 0

TH2 CDh 0 0 0 0 0 0 0 0

PSW D0h 0 0 0 0 0 0 0 0

FCNTL D5h 1 0 1 1 0 0 0 0

FDATA D6h 0 0 0 0 0 0 0 0

WDCON D8h 0 Special 0 Special 0 Special Special 0

ACC E0h 0 0 0 0 0 0 0 0

EIE E8h 1 1 1 0 0 0 0 0

B F0h 0 0 0 0 0 0 0 0

EIP1 F1h 1 1 1 0 0 0 0 0

EIP0 F8h 1 1 1 0 0 0 0 0

15 of 192

Page 17

DS89C420 Ultra High-Speed Microcontroller User’s Guide

SPECIAL FUNCTION REGISTERS

Most of the unique features of the Ultra High-Speed Microcontroller family are controlled by bits in

special function registers (SFRs) located in unused locations in the 8051 SFR map. This allows for

increased functionality while maintaining complete instruction set compatibility.

The description for each bit indicates its read and write access, as well as its state after a power on reset.

Port 0 (P0)

7 6 5 4 3 2 1 0

SFR 80h P0.7 P0.6 P0.5 P0.4 P0.3 P0.2 P0.1 P0.0

P0.7-0

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Port 0. This port functions according to the table below where PAGEE =

ACON.7 and PAGES = ACON.6-5

PAGEE PAGES Port0 Function

0 xx General Purpose I/0 (code execution < ROMSIZE.2-0)

0 xx Multiplexed Address LSB / Data (code execution > ROMSIZE.2-0)

1 00, 01, 10 Data

1 11 Address LSB

When serving as general purpose I/O, the port is open-drain and requires pullups. Writing a ‘1’ to one of the bits of this register configures the associated

port0 pin as an input. All read operations, with the exception of Read-ModifyWrite instructions, will leave the port latch unchange d. During external memory

addressing and data memory write cycles, the port has high and low drive

capability. During external memory data read cycles, the port will be held in a

high impedance state.

Stack Pointer (SP)

7 6 5 4 3 2 1 0

SFR 81h SP.7 SP.6 SP.5 SP.4 SP.3 SP.2 SP.1 SP.0

SP.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Stack Pointer. This stack pointer is written by software to identify the location

where the stack will begin. The stack pointer is incremented before every PUSH

operation and is decremented following every POP operation. This register

defaults to 07h after reset.

16 of 192

Page 18

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Data Pointer Low 0 (DPL)

7 6 5 4 3 2 1 0

SFR 82h PDL.7 PDL.6 PDL.5 PDL.4 PDL.3 PDL.2 PDL.1 PDL.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

DPL.7-0

Bits 7-0

Data Pointer Low 0. This register is the low byte of the standard 80C32 16-bit

data pointer. DPL and DPH are used to point to non-scratchpad data RAM.

Data Pointer High 0 (DPH)

7 6 5 4 3 2 1 0

SFR 83h DPH.7 DPH.6 DPH.5 DPH.4 DPH.3 DPH.2 DPH.1 DPH.0

DPH.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Data Pointer High 0. This register is the high byte of the standard 80C32 16-bit

data pointer. DPL and DPH are used to point to non-scratchpad data RAM.

Data Pointer Low 1 (DPL1)

7 6 5 4 3 2 1 0

SFR 84h DPL1.7 DPL1.6 DPL1.5 DPL1.4 DPL1.3 DPL1.2 DPL1.1 DL1H.0

DPL1.7-0

Bits 7-0

Data Pointer High 1 (DPH1)

7 6 5 4 3 2 1 0

SFR 85h DPH1.7 DPH1.6 DPH1.5 DPH1.4 DPH1.3 DPH1.2 DPH1.1 DPH1.0

DPH1.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Data Pointer Low 1. This register is the low byte of the auxiliary 16-bit data

pointer. When the SEL bit (DPS.0) is set, DPL1 and DPH1 are used in place of

DPL and DPH during DPTR operations.

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Data Pointer High 1. This register is the high byte of the auxiliary 16-bit data

pointer. When the SEL bit (DPS.0) is set, DPL1 and DPH1 are used in place of

DPL and DPH during DPTR operations.

17 of 192

Page 19

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Data Pointer Select (DPS)

7 6 5 4 3 2 1 0

SFR 86h ID1 ID0 TSL AID - - - SEL

ID1

Bit 7

RW-0 RW-0 RW-0 R-0 R-0 R-1 R-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Increment / Decrement Select for DPTR1. This bit determines the effect of

the INC DPTR instruction on DPTR1 when selected (SEL=1) as the active data

pointer.

0 = INC DPTR increments DPTR1 (default)

1 = INC DPTR decrements DPTR1

ID0

Bit 6

TSL

Bit 5

AID

Bit 4

Increment / Decrement Select for DPTR. This bit determines the effect of the

INC DPTR instruction on DPTR when selected (SEL=0) as the active data

pointer.

0 = INC DPTR increments DPTR (default)

1 = INC DPTR decrements DPTR

Toggle Select. When clear (=0), DPTR related instructions do not affect the

SEL bit. When set (=1), the SEL bit is toggled following execution of any of the

below DPTR related instructions:

INC DPTR

MOV DPTR, #data16

MOVC A, @A+DPTR

MOVX A, @DPTR

MOVX @DPTR, A

Auto Increment/Decrement Enable. When set, the active data pointer is

automatically incremented or decremented (as determined by ID1, ID0 bit

settings) following execution of any of the below DPTR related instructions:

MOVC A, @A+DPTR

MOVX A, @DPTR

MOVX @DPTR, A

Bits 3-1

SEL

Bit 0

Reserved. These bits will read 010b.

Data Pointer Select. This bit selects the active data pointer.

0 = Instructions that use the DPTR will use DPL and DPH.

1= Instructions that use the DPTR will use DPL1 and DPH1.

18 of 192

Page 20

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Power Control (PCON)

7 6 5 4 3 2 1 0

SFR 87h SMOD_0 SMOD0 OFDF OFDE GF1 GF0 STOP IDLE

RW-0 RW-0 RW-0* RW-0* RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset, *=see description

SMOD_0

Bit 7

SMOD0

Bit 6

OFDF

Bit 5

OFDE

Bit 4

Serial Port 0 Baud Rate Doubler Enable. This bit enables/disables the

serial baud rate doubling function for Serial Port 0.

0 = Serial Port 0 baud rate will be that defined by baud rate generation

equation.

1 = Serial Port 0 baud rate will be double that defined by baud rate generation

equation.

Framing Error Detection Enable. When clear (=0), SCON1.7 and

SCON0.7 serve as mode select bit SM0 for the respective Serial Ports.

When set (=1), SCON1.7 and SCON0.7 report whether a Framing Error has

been detected.

Oscillator Fail Detect Flag. When OFDE=1, this flag will be set if a reset

condition is generated due to oscillator failure. This bit is cleared on a

Power On Reset and is unchanged by other reset sources. This bit must be

cleared by software.

Oscillator Fail Detect Enable. When set (=1), the oscillator fail detect circuitry

and flag generation are enabled. An oscillator fail detection will occur if the

crystal oscillator falls below ~20 KHz. An oscillator fail detection will not occur

if the oscillator is halted through software setting of the STOP bit (PCON.1) or

when running from the internal ring oscillator source. When clear (=0), the

oscillator fail detect circuitry is disabled.

GF1

Bit 3

GF0

Bit 2

STOP

Bit 1

General Purpose User Flag 1. This is a general purpose flag for software

control.

General Purpose User Flag 0. This is a general purpose flag for software

control.

Stop Mode Select. Setting this bit will stop program execution, halt the CPU

oscillator, and internal timers, and place the CPU in a low-power mode. This bit

will always be read as a 0. Setting both the STOP bit and the IDLE bit will

cause the device to enter Stop Mode, however doing this is not advised.

IDLE

Bit 0

Idle Mode Select. Setting this bit will stop program execution but leave the

CPU oscillator, timers, serial ports, and interrupts active. This bit will always be

read as a 0. Setting both the STOP bit and the IDLE bit will cause the device to

enter Stop Mode, however doing this is not advised.

19 of 192

Page 21

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Timer/Counter Control (TCON)

7 6 5 4 3 2 1 0

SFR 88h TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0

TF1

Bit 7

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 1 Overflow Flag. This bit indicates when Timer 1 overflows its

maximum count as defined by the current mode. This bit can be cleared by

software and is automatically cleared when the CPU vectors to the Timer

1 interrupt service routine.

0 = No Timer 1 overflow has been detected.

1 = Timer 1 has overflowed its maximum count.

TR1

Bit 6

TF0

Bit 5

TR0

Bit 4

IE1

Bit 3

IT1

Bit 2

Timer 1 Run Control. This bit enables/disables the operation of Timer 1.

0 = Timer 1 is halted.

1 = Timer 1 is enabled.

Timer 0 Overflow Flag. This bit indicates when Timer 0 overflows its

maximum count as defined by the current mode. This bit can be cleared by

software and is automatically cleared when the CPU vectors to the Timer 0

interrupt service routine or by software.

0 = No Timer 0 overflow has been detected.

1 = Timer 0 has overflowed its maximum count.

Timer 0 Run Control. This bit enables/disables the operation of Timer 0.

0 = Timer 0 is halted.

1 = Timer 0 is enabled.

Interrupt 1 Edge Detect. This bit is set when an edge/level of the type defined

by IT1 is detected. If IT1=1, this bit will remain set until cleared in software or

the start of the External Interrupt 1 service routine. If IT1=0, this bit will

inversely reflect the state of the INT1 pin.

Interrupt 1 Type Select. This bit selects whether the INT1 pin will detect edge

or level triggered interrupts.

0 = INT1 is level triggered.

1 = INT1 is edge triggered.

IE0

Bit 1

Interrupt 0 Edge Detect. This bit is set when an edge/level of the type defined

by IT0 is detected. If IT0 =1, this bit will remain set until cleared in software or

the start of the External Interrupt 0 service routine. If IT0=0, this bit will

inversely reflect the state of the INT0 pin

IT0

Bit 0

Interrupt 0 Type Select. This bit selects whether the INT0 pin will detect edge

or level triggered interrupts.

0 = INT0 is level triggered.

1 = INT0 is edge triggered.

20 of 192

Page 22

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Timer Mode Control (TMOD)

7 6 5 4 3 2 1 0

SFR 89h GATE

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

GATE

Bit 7

C/T

Bit 6

M1, M0

Bits 5-4

C/ T

M1 M0 GATE

C/ T

M1 M0

Timer 1 Gate Control. This bit enable/disables the ability of Timer 1 to

increment.

0 = Timer 1 will clock when TR1=1, regardless of the state of INT.

1 = Timer 1 will clock only when TR1=1 and INT1=1.

Timer 1 Counter/Timer Select.

0 = Timer 1 is incremented by internal clocks.

1 = Timer 1 is incremented by pulses on T1 when TR1 (TCON.6) is 1.

Timer 1 Mode Select. These bits select the operating mode of Timer 1.

M1 M0 Mode

0 0 Mode 0: 8 bits with 5-bit prescale

0 1 Mode 1: 16 bits

1 0 Mode 2: 8 bits with auto-reload

1 1 Mode 3: Timer 1 is halted, but holds its count

GATE

Bit 3

C/T

Bit 2

M1, M0

Bits 1-0

Timer 0 Gate Control. This bit enables/disables that ability of Timer 0 to

increment.

0 = Timer 0 will clock when TR0=1, regardless of the state of INT0.

1 = Timer 0 will clock only when TR0=1 and INT0=1.

Timer 0 Counter/Timer Select.

0 = Timer incremented by internal clocks.

1 = Timer 1 is incremented by pulses on T0 when TR0 (TCON.4) is 1.

Timer 0 Mode Select. These bits select the operating mode of Timer 0.

When Timer 0 is in mode 3, TL0 is started/stopped by TR0 and TH0 is

started/stopped by TR1. Run control from Timer 1 is then provided via the

Timer 1 mode selection.

M1 M0 Mode

0 0 Mode 0: 8 bits with 5-bit prescale

0 1 Mode 1: 16 bits

1 0 Mode 2: 8 bits with auto-reload

1 1 Mode 3: Timer 0 is two 8 bit counters.

21 of 192

Page 23

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Timer 0 LSB (TL0)

7 6 5 4 3 2 1 0

SFR 8Ah TL0.7 TL0.6 TL0.5 TL0.4 TL0.3 TL0.2 TL0.1 TL0.0

TL0.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 0 LSB. This register contains the least significant byte of Timer 0.

Timer 1 LSB (TL1)

7 6 5 4 3 2 1 0

SFR 8Bh TL1.7 TL1.6 TL1.5 TL1.4 TL1.3 TL1.2 TL1.1 TL1.0

TL1.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 1 LSB. This register contains the leas t significant byte of Timer 1.

Timer 0 MSB (TH0)

7 6 5 4 3 2 1 0

SFR 8Ch TH0.7 TH0.6 TH0.5 TH0.4 TH0.3 TH0.2 TH0.1 TH0.0

TH0.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 0 MSB. This register contains the most significant byte of Timer 0.

Timer 1 MSB (TH1)

7 6 5 4 3 2 1 0

SFR 8Dh TH1.7 TH1.6 TH1.5 TH1.4 TH1.3 TH1.2 TH1.1 TH1.0

TH1.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 1 MSB. This register contains the most significant byte of Timer 1.

22 of 192

Page 24

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Clock Control (CKCON)

7 6 5 4 3 2 1 0

SFR 8Eh WD1 WD0 T2M T1M T0M MD2 MD1 MD0

WD1, WD0

Bits 7-6

T2M

Bit 5

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-1

R=Unrestricted Re ad, W=Unrestricted Write, -n=Value after Reset

Watchdog Timer Mode Select 1-0. These bits determine the watchdog timer

time-out period for the watchdog timer. The timer divides the crystal (or

external oscillator) frequency by a progra mmable value as shown below. The

divider value is expressed in crystal (oscillator) cycles. The settings of the

system clock control bits X2/X4 (PMR.3) and CD1:0 (PMR.7-6) will affect the

clock input to the watchdog timer and therefore its time-out period as shown

below. All Watchdog Timer reset time-outs follow the setting of the interrupt

flag by 512 system clocks.

Watchdog Interrupt Flag Time-Out Periods (in oscillator clocks)

CD1:0 WD1:0=00 WD1:0=01 WD1:0=10 WD1:0=11

X2/X4

1 00 2

0 00 2

X 01 2

X 10 2

X 11 2

15

16

17

17

27

18

2

19

2

20

2

220 223 226

30

2

21

2

22

2

23

2

33

2

24

2

25

2

26

2

36

2

Timer 2 Clock Select. This bit controls the input clock that drives Timer 2.

This bit has no effect when the timer is in baud rate generator or clock output

modes. See table below.

T1M

Bit 4

T0M

Bit 3

Timer 1 Clock Select. This bit controls the input clock that drives Timer 1.

See table below.

Timer 0 Clock Select. This bit controls the input clock that drives Timer 0.

See table below.

Timer Operation (in oscillator clocks)

X2/X4

1 00 12 1 0.25

0 00 12 2 0.5

X 01 12 4 1

X 10 12 4 1

X 11 3072 1024 1024

CD1:0

Oscillator clocks per Timer

(0,1,2) clock

TxMH,TxM =

00 01 1x

Oscillator clocks per Timer2

clock (baud rate gen)

T2MH, T2M =

xx

2

2

2

2

2048

23 of 192

Page 25

MD2, MD1, MD0

Bits 2-0

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Stretch MOVX Select 2-0. These bits select the time by which external MOVX

cycles are to be stretched. This allows slower memory or peripherals to be

accessed without using ports or manual software intervention. The RD or WR

strobe will be stretched by the specified interval, which will be transparent to the

software except for the increased time to execute to MOVX instruction. All

internal MOVX instructions are executed at the 2 machine cycle rate (0 stretch)

independent of these bit settings.

24 of 192

Page 26

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Port 1 (P1)

7 6 5 4 3 2 1 0

SFR 90h P1.7

INT5

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

P1.7-0

Bits 7-0

INT5

Bit 7

INT4

Bit 6

INT3

Bit 5

INT2

Bit 4

P1.6

INT4

P1.5

INT3

P1.4

INT2

P1.3

TXD1

P1.2

RXD1

P1.1

T2EX

P1.0

T2

General Purpose I/O Port 1. This register functions as a general purpose I/O

port. In addition, all the pins have an alternative function listed below. Each of

the functions is controlled by several other SFRs. The associated Port 1 latch bit

must contain a logic one before the pin can be used in its alternate function

capacity.

External Interrupt 5. A falling edge on this pin will cause an external interrupt

5 if enabled.

External Interrupt 4. A rising edge on this pin will cause an external interrupt

4 if enabled.

External Interrupt 3. A falling edge on this pin will cause an external interrupt

3 if enabled.

External Interrupt 2. A rising edge on this pin will cause an external interrupt

2 if enabled.

TXD1

Bit 3

RXD1

Bit 2

T2EX

Bit 1

T2

Bit 0

Serial Port 1 Transmit. This pin transmits the serial port 1 data in serial port

modes 1, 2, 3 and emits the synchronizing clock in serial port mode 0.

Serial Port 1 Receive. This pin receives the serial port 1 data in serial port

modes 1, 2, 3 and is a bi-directional data transfer pin in serial port mode 0.

Timer 2 Capture/Reload Trigger. A 1 to 0 transition on this pin will cause the

value in the T2 registers to be transferred into the capture registers if enabled by

EXEN2 (T2CON.3). When in auto–reload mode, a 1 to 0 transition on this pin

will reload the timer 2 registers with the value in RCAP2L and RCAP2H if

enabled by EXEN2 (T2CON.3).

Timer 2 External Input. A 1 to 0 transition on this pin will cause timer 2

increment or decrement depending on the timer configuration.

25 of 192

Page 27

DS89C420 Ultra High-Speed Microcontroller User’s Guide

External Interrupt Flag (EXIF)

7 6 5 4 3 2 1 0

SFR 91h IE5 IE4 IE3 IE2 CKRY RGMD RGSL BGS

R=Unrestricted Read, W=Unrestricted Write, T=Timed Access Write Only, -n=Value after Reset,

IE5

Bit 7

RW-0 RW-0 RW-0 RW-0 R-* R-* RW-* RT-0

*=See description

External Interrupt 5 Flag. This bit will be set when a falling edge is detected

on INT5. This bit must be cleared manually by software. Setting this bit in

software will cause an interrupt if enabled.

IE4

Bit 6

IE3

Bit 5

IE2

Bit 4

CKRY

Bit 3

RGMD

Bit 2

External Interrupt 4 Flag. This bit will be set when a rising edge is detected on

INT4. This bit must be cleared manually by software. Setting this bit in software

will cause an interrupt if enabled.

External Interrupt 3 Flag. This bit will be set when a falling edge is detected

on INT3. This bit must be cleared manually by software. Setting this bit in

software will cause an interrupt if enabled.

External Interrupt 2 Flag. This bit will be set when a rising edge is detected on

INT2. This bit must be cleared manually by software. Setting this bit in software

will cause an interrupt if enabled.

Clock Ready This bit indicates the status of the start-up period for the crystal

oscillator or crystal multiplier warm-up period. This bit is cleared after a reset or

when exiting STOP mode. It is also cleared when the clock multiplier is enabled

(setting of PMR.4 =1). Once CKRY is cleared, a 65536 clock count must take

place before CKRY is set and the lockout preventing modification of CD1:C D0

is removed. Once CKRY is set (=1), the clock multiplier may then be selected as

the clock source or switchover from the ring oscillator to the crystal oscillator

can occur.

Ring Mode Status. This status bit indicates the current clock source for the

device. This bit is cleared to 0 after a power-on reset, and unchanged by all

other forms of reset.

0 = Device is operating from the external crystal or oscillator.

1 = Device is operating from the ring oscillator.

26 of 192

Page 28

RGSL

Bit 1

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Ring Oscillator Select. When set (=1), this bit enables operation using the onchip ring oscillator as the clock source until the oscillator warm-up period has

completed (CKRY=1). Using the ring oscillator to resume from Stop mode

allows almost instantaneous start-up. This bit is cleared to 0 after a power-on

reset, and unchanged by all other forms of reset.

0 = Device operation will be held until completion of the crystal oscillator

warm-up delay period.

1 = The device will begin operating from the ring oscillator and switch over to

the crystal oscillator upon completion of the warm-up delay period.

BGS

Bit 0

Band-gap Select. This bit enables/disables the band -gap reference during Stop

mode. Disabling the band-gap reference provides significant power savings in

Stop mode, but sacrifices the ability to perform a power fail interrupt or powerfail reset while stopped. This bit can only be modified with a Timed Access

procedure.

0 = The band-gap reference is disabled in Stop mode but will function during

normal operation.

1 = The band-gap reference will operate in Stop mode.

27 of 192

Page 29

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Timer and Serial Port Clock Mode Register (CKMOD)

7 6 5 4 3 2 1 0

SFR 96h - - T2MH T1MH T0MH - - -

T2MH

Bit 5

RW-1 RW-1 RW-0 RW-0 RW-0 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Timer 2 Clock Mode High Speed Select. When set (=1), the system clock will

be used as the input clock for Timer 2 and the T2M bit (CKCON.5) setting will

be ignored. When clear (=0), the input clock for Timer 2 will be selected using

the T2M bit.

T1MH

Bit 4

T0MH

Bit 3

Timer 1 Clock Mode High Speed Select. When set (=1), the system clock will

be used as the input clock for Timer 2 and the T1M bit (CKCON.4) setting will

be ignored. When clear (=0), the input clock for Timer 2 will be selected using

the T1M bit.

Timer 0 Clock Mode High Speed Select. When set (=1), the system clock will

be used as the input clock for Timer 2 and the T0M bit (CKCON.3) setting will

be ignored. When clear (=0), the input clock for Timer 2 will be selected using

the T0M bit.

28 of 192

Page 30

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Serial Port 0 Control (SCON0)

7 6 5 4 3 2 1 0

SFR 98h SM0/FE_0 SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0

SM0-2

Bits 7-5

SM0 SM1 SM2 MODE FUNCTION LENGTH PERIOD

0 0 0 0 Synchronous 8 bits See PMR register

0 0 1 0 Synchronous 8 bits See PMR register

0 1 X 1 Asynchronous 10 bits Timer 1 or 2 baud

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Serial Port Mode These bits control the mode of serial port 0. In addition the

SM0 and SM2_0 bits have secondary functions as shown below.

rate equation

1 0 0 2 Asynchronous 11 bits

1 0 1 2 Asynchronous w/ Multiprocessor

11 bits

See PMR register

See PMR register

Communication

1 1 0 3 Asynchronous 11 bits Timer 1 or 2 baud

rate equation

1 1 1 3 Asynchronous w/ Multiprocessor

Communication

SM0/FE_0

Bit 7

Framing Error Flag. When SMOD0 (PCON.6)=0, this bit is used as a mode

select bit (SM0) for serial port 0. When SMOD0 (PCON.6)=1, this bit becomes a

11 bits Timer 1 or 2 baud

rate equation

framing error (FE) bit, which reports detection of an invalid stop bit. When used

as FE, this bit must be cleared in software. Once the SMOD0 bit is set,

modifications to this bit will not affect the serial port mode settings. Although

accessed from the same register, internally the data for bits SM0 and FE are

stored in different physical locations.

SM1_0

No alternate function.

Bit 6

SM2_0

Bit 5

Multiple CPU Communications. The function of this bit is dependent on the

serial port 0 mode.

Mode 0: Selects period for synchronous serial port 0 data transfers.

Mode 1: When set, reception is ignored (RI_0 is not set) if invalid stop bit

received.

Mode 2/3: When this bit is set, multiprocessor communications are enabled in

m odes 2 and 3. This will prevent the RI_0 bit from being set, and an interrupt

being asserted, if the 9th bit received is not 1.

29 of 192

Page 31

REN_0

Bit 4

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Receiver Enable. This bit enable/disables the serial port 0 receiver shift

register.

0 = Serial port 0 reception disabled.

1= Serial port 0 receiver enabled (modes 1, 2, 3). Initiate synchronous reception

(mode 0).

TB8_0

Bit 3

RB8_0

Bit 2

TI_0

Bit 1

RI_0

Bit 0

9th Transmission Bit State. This bit defines the state of the 9th transmission bit

in serial port 0 modes 2 and 3.

9th Received Bit State. This bit identifies that state of the 9th reception bit of

received data in serial port 0 modes 2 and 3. In serial port mode 1, when

SM2_0=0, RB8_0 is the state of the stop bit. RB8_0 is not used in mode 0.

Transmitter Interrupt Flag. This bit indicates that data in the serial port 0

buffer has been completely shifted out. In serial port mode 0, TI_0 is set at the

end of the 8th data bit. In all other modes, this bit is set at the end of the last data

bit. This bit must be manually cleared by software.

Receiver Interrupt Flag. This bit indicates that a byte of data has been

received in the serial port 0 buffer. In serial port mode 0, RI_0 is set at the end of

the 8th bit. In serial port mode 1, RI_0 is set after the last sample of the incoming

stop bit subject to the state of SM2_0. In modes 2 and 3, RI_0 is set after the last

sample of RB8_0. This bit must be manually cleared by software.

Serial Data Buffer 0 (SBUF0)

7 6 5 4 3 2 1 0

SFR 99h SBUF0.7 SBUF0.6 SBUF0.5 SBUF0.4 SBUF0.3 SBUF0.2 SBUF0.1 SBUF0.0

SBUF0.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Serial Data Buffer 0. Data for serial port 0 is read from or written to this

location. The serial transmit and receive buffers are separate registers, but both

are addressed at this location.

30 of 192

Page 32

DS89C420 Ultra High-Speed Microcontroller User’s Guide

bus operations as configured by the page mode select bits PAGES1, PAGES0.

Address Control (ACON)

7 6 5 4 3 2 1 0

SFR 9Dh PAGEE PAGES1 PAGES0 - - - - -

R=Unrestricted Read, W=Unrestricted Write, T=Timed Access Write Only, -n=Value after Reset

PAGEE

Bits 7

PAGES1, PAGES0

Bits 6-5

RT-0 RT-0 RT-0 R-1 R-1 R-1 R-1 R-1

Page Mode Enable. When set (=1), page mode access is enabled for external

When clear (=0), external bus operations default to the standard 8051 expanded

bus configuration.

Page Mode Select. If PAGEE=1, these bits select the page mode

configuration that will be followed for external bus operations. The four

possible configurations are summarized in the table below. Mode 1 results

in Port 0 serving as the data bus and Port 2 being the multiplexed address

MSB/LSB. Mode 2 results in Port 0 being used strictly for address LSB

and Port 2 being multiplexed between address MSB and data.

Bits 4-0 Reserved. Read data will be ‘1’.

31 of 192

Page 33

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Port 2 (P2)

7 6 5 4 3 2 1 0

SFR A0h P2.7 P2.6 P2.5 P2.4 P2.3 P2.2 P2.1 P2.0

P2.7-0

Bits 7-0

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Port 2. This port functions according to the table below where PAGEE =

ACON.7 and PAGES = ACON.6-5

PAGEE PAGES Port2 Function

0 xx General Purpose I/0 (code execution < ROMSIZE.2-0)

0 xx Address MSB (code execution > ROMSIZE.2-0)

1 00, 01, 10 Multiplexed Address MSB/LSB

1 11 Multiplexed Address MSB / Data

Writing a ‘1’ to an SFR bit configures the associated port pin as an input. All

read operations, with the exception of Read-Modify-Write instructions, will

leave the port latch unchanged. During external memory addressing and data

memory write cycles, the port has high and low drive capability. During

external memory data read cycles, the port will be held in a high impedance

state.

32 of 192

Page 34

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Interrupt Enable (IE)

7 6 5 4 3 2 1 0

SFR A8h EA ES1 ET2 ES0 ET1 EX1 ET0 EX0

EA

Bit 7

ES1

Bit 6

ET2

Bit 5

ES0

Bit 4

ET1

Bit 3

EX1

Bit 2

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Global Interrupt Enable. This bit controls the global masking of all interrupts

except Power-Fail Interrupt, which is enabled by the EPFI bit (WDCON.5).

0 = Disable all interrupt sources. This bit overrides individual interrupt mask

settings.

1 = Enable all individual interrupt masks. Individual interrupts will occur if

enabled.

Enable Serial Port 1 Interrupt. This bit controls the masking of the serial port

1 interrupt.

0 = Disable all serial port 1 interrupts.

1 = Enable interrupt requests generated by the RI_1 (SCON1.0) or TI_1

(SCON1.1) flags.

Enable Timer 2 Interrupt. This bit controls the masking of the Timer 2

interrupt.

0 = Disable all Timer 2 interrupts.

1 = Enable interrupt requests generated by the TF2 flag (T2CON.7).

Enable Serial Port 0 Interrupt. This bit controls the masking of the serial port

0 interrupt.

0 = Disable all serial port 0 interrupts.

1 = Enable interrupt requests generated by the RI_0 (SCON0.0) or TI_0

(SCON0.1) flags.

Enable Timer 1 Interrupt. This bit controls the masking of the Timer 1

interrupt.

0 = Disable all Timer 1 interrupts.

1 = Enable all interrupt requests generated by the TF1 flag (TCON.7).

Enable External Interrupt 1. This bit controls the masking of external

interrupt 1.

0 = Disable external interrupt 1.

1 = Enable all interrupt requests generated by the INT0 pin.

ET0

Bit 1

Enable Timer 0 Interrupt. This bit controls the masking of the Timer 0

interrupt.

0 = Disable all Timer 0 interrupts.

1 = Enable all interrupt requests generated by the TF0 flag (TCON.5).

EX0

Bit 0

Enable External Interrupt 0. This bit controls the masking of external

interrupt 0.

0 = Disable external interrupt 0.

1 = Enable all interrupt requests generated by the INT0 pin.

33 of 192

Page 35

DS89C420 Ultra High-Speed Microcontroller User’s Guide

RD

Slave Address Register 0 (SADDR0)

7 6 5 4 3 2 1 0

SFR A9h SADDR0.7 SADDR0.6 SADDR0.5 SADDR0.4 SADDR0.3 SADDR0.2 SADDR0.1 SADDR0.0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

SADDR0.7-0

Bits 7-0

Slave Address Register 0. This register is programmed with the given or

broadcast address assigned to serial port 0.

Slave Address Register 1 (SADDR1)

7 6 5 4 3 2 1 0

SFR AAh SADDR1.7 SADDR1.6 SADDR1.5 SADDR1.4 SADDR1.3 SADDR1.2 SADDR1.1 SADDR1.0

SADDR1.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Slave Address Register 1. This register is programmed with the given or

broadcast address assigned to serial port 1.

Port 3 (P3)

7 6 5 4 3 2 1 0

SFR B0h P3.7

RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1 RW-1

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

P3.7-0

Bits 7-0

RD

Bit 7

WR

Bit 6

T1

Bit 5

P3.6

WR

P3.5

T1

P3.4

T0

P3.3

INT1

P3.2

INT0

P3.1

TXD0

Purpose I/O Port 3. This register functions as a general purpose I/O port. In

addition, all the pins have an alternative function listed below. Each of the

functions is controlled by several other SFRs. The associated Port 3 latch bit

must contain a logic one before the pin can be used in its alternate function

capacity.

External Data Memory Read Strobe. This pin provides an active low read

strobe to an external memory device.

External Data Memory Write Strobe. This pin provides an active low write

strobe to an external memory device.

Timer/Counter External Input. A 1 to 0 transition on this pin will increment

Timer 1.

P3.0

RXD0

T0

Bit 4

Counter External Input. A 1 to 0 transition on this pin will increment Timer 0.

34 of 192

Page 36

INT1

Bit 3

DS89C420 Ultra High-Speed Microcontroller User’s Guide

External Interrupt 1. A falling edge/low level on this pin will cause an

external interrupt 1 if enabled.

INT0

Bit 2

TXD0

Bit 1

RXD0

Bit 0

External Interrupt 0. A falling edge/low level on this pin will cause an

external interrupt 0 if enabled.

Serial Port 0 Transmit. This pin transmits the serial port 0 data in serial port

modes 1, 2, 3 and emits the synchronizing clock in serial port mode 0.

Serial Port 0 Receive. This pin receives the serial port 0 data in serial port

modes 1, 2, 3 and is a bi-directional data transfer pin in serial port mode 0.

35 of 192

Page 37

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Interrupt Priority 1 (IP1)

7 6 5 4 3 2 1 0

SFR B1h - MPS1 MPT2 MPS0 MPT1 MPX1 MPT0 MPX0

Bit 7

R-1 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Reserved. Read data will be ‘1’..

MPS1

Bit 6

MPT2

Bit 5

MPS0

Bit 4

MPT1

Bit 3

MPX1

Bit 2

MPT0

Bit 1

MPX0

Bit 0

Most Significant Priority Select Bit for Serial Port 1 Interrupt. This is the

most significant bit of the bit pair MPS1, LPS1 (IP0.6) which des ignate priority

level for the serial port 1 interrupt.

Most Significant Priority Select Bit for Timer 2 Interrupt. This is the most

significant bit of the bit pair MPT2, LPT2 (IP0.5) which designate priority level

for the timer 2 interrupt.

Most Significant Priority Select Bit for Serial Port 0 Interrupt. This is the

most significant bit of the bit pair MPS0, LPS0 (IP0.4) which designate priority

level for the serial port 0 interrupt

Most Significant Priority Select Bit for Timer 1 Interrupt.. This is the most

significant bit of the bit pair MPT1, LPT1 (IP0.3) which designate priority level

for the timer 1 interrupt.

Most Significant Priority Select Bit for External Interrupt 1. This is the most

significant bit of the bit pair MPX1, LPX1 (IP0.2) which designate priority level

for external interrupt 1

Most Significant Priority Select Bit for Timer 0 Interrupt. This is the most

significant bit of the bit pair MPT0, LPT0 (IP0.1) which designate prior ity level

for the timer 0 interrupt

Most Significant Priority Select Bit for External Interrupt 0. This is the

most significant bit of the bit pair MPX0, LPX0 (IP0.0) which designate priority

level for external interrupt 0.

Interrupt priority level for the above sources is assigned using one bit from

register IP1 (B1h) and one bit from IP0 (B8h). The bit from IP1 serves as the

most significant bit and the bit from IP0 serves as the least significant bit in

forming a 2-bit binary number. This number represents the priority level.

Higher priority interrupts, when enabled, take precedence over lower priority

sources. The power fail warning interrupt source is assigned Priority Level 4.

MP (IP1.x) LP (IP0.x) Priority Level

0 0 0 (natural priority)

0 1 1

1 0 2

1 1 3 (high priority)

36 of 192

Page 38

DS89C420 Ultra High-Speed Microcontroller User’s Guide

Interrupt Priority 0 (IP0)

7 6 5 4 3 2 1 0

SFR B8h - LPS1 LPT2 LPS0 LPT1 LPX1 LPT0 LPX0

Bit 7

R-1 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Reserved. Read data will be ‘1’.

LPS1

Bit 6

LPT2

Bit 5

LPS0

Bit 4

LPT1

Bit 3

LPX1

Bit 2

LPT0

Bit 1

LPX0

Bit 0

Least Significant Priority Select Bit for Serial Port 1 Interrupt. LPS1 is the

least significant bit of the bit pair MPS1 (IP1.6), LPS1 which designate priority

level for the serial port 1 interrupt.

Least Significant Priority Select Bit for Timer 2 Interrupt. LPT2 is the least

significant bit of the bit pair MPT2 (IP1.5), LPT2 which designate priority level

for the timer 2 interrupt.

Least Significant Priority Select Bit for Serial Port 0 Interrupt. MPS0 is the

least significant bit of the bit pair MPS0 (IP1.4), LPS0 which designate priority

level for the serial port 0 interrupt

Least Significant Priority Select Bit for Timer 1 Interrupt.. MPT1 is the least

significant bit of the bit pair MPT1 (IP1.3), LPT1 which designate priority level

for the timer 1 interrupt.

Least Significant Priority Select Bit for External Interrupt 1. MPX1 is the

least significant bit of the bit pair MPX1 (IP1.2), LPX1 which designate priority

level for external interrupt 1

Least Significant Priority Select Bit for Timer 0 Interrupt. MPT0 is the least

significant bit of the bit pair MPT0 (IP1.1), LPT0 which designate priority level

for the timer 0 interrupt

Least Significant Priority Select Bit for External Interrupt 0. MPX0 is the

least significant bit of the bit pair MPX0 (IP1.0), LPX0 which designate priority

level for external interrupt 0.

MP (IP1.x) LP (IP0.x) Priority Level

0 0 0 (natural priority)

0 1 1

1 0 2

1 1 3 (high priority)

37 of 192

Page 39

DS89C420 Ultra High-Speed Microcontroller User’s Guide

n comparing serial port 0 addresses for automatic address recognition.

Slave Address Mask Enable Register 0 (SADEN0)

7 6 5 4 3 2 1 0

SFR B9h SADEN0.7 SADEN0.6 SADEN0.5 SADEN0.4 SADEN0.3 SADEN0.2 SADEN0.1 SADEN0.0

SADEN0.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Slave Address Mask Enable Register 0. This register functions as a mask

whe

When a bit in this register is set, the corresponding bit location in the SADDR0

register will be exactly compared with the incoming serial port 0 data to

determine if a receiver interrupt should be generated. When a bit in this register

is cleared, the corresponding bit in the SADDR0 register becomes a don‘t care

and is not compared against the incoming data. All incoming data will generate

a receiver interrupt when this register is cleared.

Slave Address Mask Enable Register 1 (SADEN1)

7 6 5 4 3 2 1 0

SFR BAh SADEN1.7 SADEN1.6 SADEN1.5 SADEN1.4 SADEN1.3 SADEN1.2 SADEN1.1 SADEN1.0

SADEN1.7-0

Bits 7-0

RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0 RW-0

R=Unrestricted Read, W=Unrestricted Write, -n=Value after Reset

Slave Address Mask Enable Register 1. This register functions as a mask

when comparing serial port 1 addresses for automatic address recognition. When

a bit in this register is set, the corresponding bit location in the SADDR1 register