Page 1

r

www.maxim-ic.com

GENERAL DESCRIPTION

The DS80C400 network microcontroller offers the highest

integration available in an 8051 device. Peripherals include

a 10/100 Ethernet MAC, three serial ports, a CAN 2.0B

controller, 1-Wire

To enable access to the network, a full applicationaccessible TCP IPv4/6 network stack and OS are provided

in ROM. The network stack supports up to 32 simultaneous

TCP connections and can transfer up to 5Mbps through the

Ethernet MAC. Its maximum system-clock frequency of

75MHz results in a minimum instruction cycle time of 54ns.

Access to large program or data memory areas is

simplified with a 24-bit addressing scheme that supports up

to 16MB of contiguous memory.

To accelerate data transfers between the microcontroller

and memory, the DS80C400 provides four data pointers,

each of which can be configured to automatically increment

or decrement upon execution of certain data pointer-related

instructions. The DS80C400’s hardware math accelerator

further increases the speed of 32-bit and 16-bit multiply

and divide operations as well as high-speed shift,

normalization, and accumulate functions.

The High-Speed Microcontroller User’s Guide and the High-Speed

Microcontroller User’s Guide: DS80C400 Supplement should be

used in conjunction with this data sheet. Download both at:

www.maxim-ic.com/microcontrollers

®

Master, and 64 I/O pins.

.

APPLICATIONS

Industrial Control/Automation

Environmental Monitoring

Network Sensors Remote Data Collection

Vending

Home/Office Automation

Data Converters (Serial-to-

Ethernet, CAN-toEthernet)

Equipment

Transaction/Payment

Terminals

ORDERING INFORMATION

PART TEMP RANGE

DS80C400-FNY -40°C to +85°C 75MHz 100 LQFP

1-Wire is a registered trademark of Dallas Semiconductor.

Magic Packet is a trademark of Advanced Micro Devices, Inc.

DeviceNet is a trademark of Open DeviceNet Vendor Association, Inc.

MAX CLOCK

SPEED

PINPACKAGE

DS80C400

Network Microcontrolle

FEATURES

§ High-Performance Architecture

Single 8051 Instruction Cycle in 54ns

DC to 75MHz Clock Rate

Flat 16MB Address Space

Four Data Pointers with Auto-Increment/

Decrement and Select-Accelerate Data Movement

16/32-Bit Math Accelerator

§ Multitiered Networking and I/O

10/100 Ethernet Media Access Controller (MAC)

CAN 2.0B Controller

1-Wire Net Controller

Three Full-Duplex Hardware Serial Ports

Up to Eight Bidirectional 8-Bit Ports (64 Digital I/O

Pins)

§ Robust ROM Firmware

Supports Network Boot Over Ethernet Using DHCP

and TFTP

Full, Application-Accessible TCP/IP Network Stack

Supports IPv4 and IPv6

Implements UDP, TCP, DHCP, ICMP, and IGMP

Preemptive, Priority-Based Task Scheduler

MAC Address can Optionally be Acquired from IEEE-

Registered DS2502-E48

§ 10/100 Ethernet Mac

Flexible IEEE 802.3 MII (10/100Mbps) and ENDEC

(10Mbps) Interfaces Allow Selection of PHY

Low-Power Operation

Ultra-Low-Power Sleep Mode with Magic Packet

and Wake-Up Frame Detection

8kB On-Chip Tx/Rx Packet Data Memory with Buffer

Control Unit Reduces Load on CPU

Half- or Full-Duplex Operation with Flow Control

Multicast/Broadcast Address Filtering with VLAN

Support

§ Full-Function CAN 2.0B Controller

15 Message Centers

Supports Standard (11-Bit) and Extended (29-Bit)

Identifiers and Global Masks

Media Byte Filtering to Support DeviceNet

Higher Layer CAN Protocols

Auto-Baud Mode and SIESTA Low-Power Mode

§ Integrated Primary System Logic

16 Total Interrupt Sources with Six External

Four 16-Bit Timer/Counters

2x/4x Clock Multiplier Reduces Electromagnetic

Interference (EMI)

Programmable Watchdog Timer

Oscillator-Fail Detection

Programmable IrDA Clock

Features continued on page 32.

Pin Configuration appears at end of data sheet.

™

™

, SDS, and

Note: Some revisions of this device may incorporate deviations from published specifications known as errata. Multiple revisions of any device

may be simultaneously available through various sales channels. For information about device errata, click here: www.maxim-ic.com/errata

1 of 96

REV: 102103

.

Page 2

DS80C400 Network Microcontroller

ABSOLUTE MAXIMUM RATINGS

Voltage Range on Any Input Pin Relative to Ground -0.5V to +5.5V

Voltage Range on Any Output Pin Relative to Ground -0.5V to (V

Voltage Range on V

Voltage Range on V

Relative to Ground -0.5V to +3.6V

CC3

Relative to Ground -0.3V to +2.0V

CC1

+ 0.5)V

CC3

Operating Temperature Range -40°C to +85°C

Junction Temperature +150°C max

Storage Temperature Range -55°C to +160°C

Soldering Temperature See IPC/JEDEC J-STD-020A

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only,

and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is

not implied. Exposure to absolute maximum rating conditions for extended periods can affect device reliability.

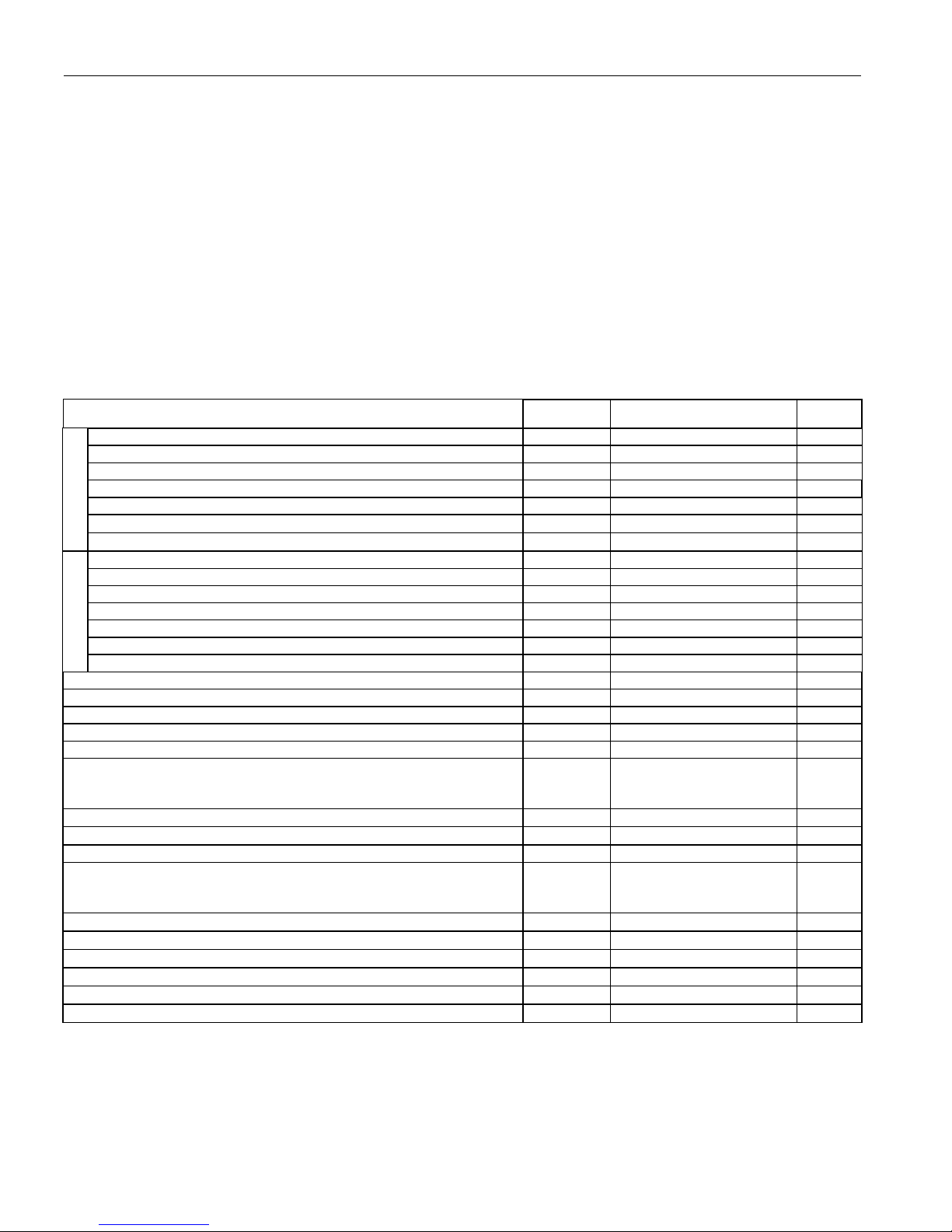

DC ELECTRICAL CHARACTERISTICS (Note 1)

(V

= 3.0V to 3.6V, V

CC3

Supply Voltage (V

Power-Fail Warning (V

Power-Fail Reset Voltage (V

Active Mode Current (V

VCC3

Idle Mode Current (V

Stop Mode Current (V

Stop Mode Current, Bandgap Enabled (V

Supply Voltage (V

Power-Fail Warning (V

Power-Fail Reset Voltage (V

Active Mode Current (V

VCC1

Idle Mode Current (V

Stop Mode Current (V

Stop Mode Current, Bandgap Enabled (V

Input Low Level V

Input Low Level for XTAL1, RST, OW V

Input High Level V

Input High Level for XTAL1, RST, OW V

Output Low Current for Port 1, 3–7 at VOL = 0.4V I

Output Low Current for Port 0, 2, TX_EN, TXD[3:0], MDC, MDIO,

RSTOL, ALE, PSEN, and Ports 3–7 (when used as any of the following:

A21–A0, WR, RD, CE0-7, PCE0-3) at V

Output Low Current for OW, OWSTP at VOL= 0.4V

Output High Current for Port 1, 3–7 at VOH = V

Output High Current for Port 1, 3–7 at VOH= V

Output High Current for Port 0, 2, TX_EN, TXD[3:0], MDC, MDIO,

RSTOL, ALE, PSEN, and Ports 3–7 (when used as any of the following:

A21–A0, WR, RD, CE0-7, PCE0-3) at V

Input Low Current for Port 1–7 at 0.4V (Note 10) IIL -50 -20 -10

Logic 1-to-0 Transition Current for Port 1, 3–7 (Note 11) ITL -650 -400

Input Leakage Current, Port 0 Bus Mode, VIL = 0.8V (Note 12) I

Input Leakage Current, Port 0 Bus Mode, VIH = 2.0V (Note 12) I

Input Leakage Current, Input Mode (Note 13) IL -15 0 15

RST Pulldown Resistance R

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: The user should note that this part is tested and guaranteed to operate down to V

thresholds for those supplies, V

supply is greater than the guaranteed minimum operating voltage, that reset threshold should be considered the minimum operating

point since execution ceases once the part enters the reset state. When the reset threshold for a given supply is lower than the

guaranteed minimum operating voltage, there exists a range of voltages for either supply, (V

3.0V), where the processor’s operation is not guaranteed, and the reset trip point has not been reached. This should not be an issue in

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

PARAMETER SYMBOL MIN TYP MAX UNITS

) (Note 2) V

CC3

) (Note 3) V

CC3

) (Note 3) V

CC3

) (Note 4) I

CC3

) (Note 4) I

CC3

) (Not 4) I

CC3

) (Note 4) I

CC3

) (Note 2) V

CC1

) (Note 5) V

CC1

) (Note 5) V

CC1

) (Note 4) I

CC1

) (Note 4) I

CC1

) (Note 4) I

CC1

) (Note 4) I

CC1

= 0.4V (Note 6)

OL

- 0.4V (Note 7) I

CC3

- 0.4V (Note 8) I

CC3

= V

OH

- 0.4V (Notes 6, 9)

CC3

3.0 3.3 3.6 V

CC3

2.85 3.00 3.15 V

PFW3

2.76 2.90 3.05 V

RST3

16 35 mA

CC3

7 15 mA

IDLE3

1 10

STOP3

100 150

SPBG3

1.62 1.8 1.98 V

CC1

1.52 1.60 1.68 V

PFW1

1.47 1.55 1.63 V

RST1

27 50 mA

CC1

20 40 mA

IDLE1

0.2 10 mA

STOP1

0.2 10 mA

SPBG1

0.8 V

IL1

1.0 V

IL2

2.0 V

IH1

2.4 V

IH2

6 10 mA

OL1

12 20 mA

I

OL2

10 16 mA

I

OL3

-75 -50

OH1

-8 -4 mA

OH2

I

-16 -8 mA

OH3

mA

mA

mA

mA

mA

20 50 200

TH0

-200 -50 -20

TL0

mA

mA

mA

RST3

and V

50 100 200

RST

= 3.0V and V

respectively, may be above or below those points. When the reset threshold for a given

RST1

CC3

RST3

< V

= 1.62V, while the reset

CC1

< 1.62V) or (V

CC3

RST1

< V

kW

CC1

2 of 96

<

Page 3

DS80C400 Network Microcontroller

most applications, but should be considered when proper operation must be maintained at all times. For these applications, it may be

desirable to use a more accurate external reset.

Note 3: While the specifications for V

PFW3

and V

overlap, the design of the hardware makes it such that this is not possible. Within the ranges

RST3

given, there is a guaranteed separation between these two voltages.

Note 4: Current measured with 75MHz clock source on XTAL1, V

= 3.6V, V

CC3

= 2.0V, EA and RST = 0V, Port0 = V

CC1

, all other pins

CC3

disconnected.

Note 5: While the specifications for V

PFW1

and V

overlap, the design of the hardware makes it such that this is not possible. Within the ranges

RST1

given, there will be a guaranteed separation between these two voltages.

Note 6: Certain pins exhibit stronger drive capability when being used to address external memory. These pins and associated memory

interface function (in parentheses) are as follows: Port 3.6-3.7 (WR, RD), Port 4 (CE0-3, A16-A19), Port 5.4-5.7 (PCE0-3), Port 6.0-6.5

(CE4-7, A20, A21), Port 7 (demultiplexed mode A0-A7).

Note 7: This measurement reflects the weak I/O pullup state that persists following the momentary strong 0 to 1 port pin drive (V

pin state can be achieved by applying RST = V

CC3.

). This I/O

OH2

Note 8: The measurement reflects the momentary strong port pin drive during a 0-to-1 transition in I/O mode. During this period, a one shot

circuit drives the ports hard for two clock cycles. A weak pullup device (V

) remains in effect following the strong two-clock cycle

OH1

drive. If a port 4 or 6 pin is functioning in memory mode with pin state of 0 and the SFR bit contains a 1, changing the pin to an I/O

mode (by writing to P4CNT, for example) does not enable the two-cycle strong pullup.

Note 9: Port 3 pins 3.6 (WR) and 3.7(RD) have a stronger than normal pullup drive for only one system clock period following the transition of

either WR or RD from a 0 to a 1.

Note 10: This is the current required from an external circuit to hold a logic low level on an I/O pin while the corresponding port latch bit is set to

1. This is only the current required to hold the low level; transitions from 1 to 0 on an I/O pin also have to overcome the transition

current.

Note 11: Following the 0 to 1 one-shot timeout, ports in I/O mode source transition current when being pulled down externally. It reaches a

maximum at approximately 2V.

Note 12: During external addressing mode, weak latches are used to maintain the previously driven state on the pin until such time that the Port

0 pin is driven by an external memory source.

Note 13: The OW pin (when configured to output a 1) at V

CRS, COL, MDIO) at V

= 3.6V.

IN

= 5.5V, EA, MUX, and all MII inputs (TXCLk, RXCLk, RX_DV, RX_ER, RXD[3:0],

IN

AC ELECTRICAL CHARACTERISTICS (MULTIPLEXED ADDRESS/DATA BUS)

(Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL

External Crystal Frequency 4 40

Clock Multiplier 4X Mode

External Clock Oscillator Frequency DC 75

Clock Mutliplier 2X Mode 16 37.5

Clock Multiplier 4X Mode

ALE Pulse Width 15.0 t

Port 0 Instruction Address Valid to ALE Low t

Address Hold After ALE Low t

ALE Low to Valid Instruction In t

ALE Low to PSEN Low

PSEN Pulse Width

PSEN Low to Valid Instruction In

Input Instruction Hold After PSEN

Input Instruction Float After PSEN

Port 0 Address to Valid Instruction In t

Port 2, 4, 6 Address or Port 4 CE to Valid

Instruction In

PSEN Low to Address Float

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: All parameters apply to both commercial and industrial temperature operation, unless otherwise noted.

Note 3: t

Note 4: The precalculated 75MHz MIN/MAX timing specifications assume an exact 50% duty cycle.

Note 5: All signals guaranteed with load capacitance of 80pF except Port 0, Port 2, ALE, PSEN, RD, and WR with 100pF. The following signals,

Note 6: For high-frequency operation, special attention should be paid to the float times of the interfaced memory devices so as to avoid bus

Note 7: References to the XTAL, XTAL1 or CLK signal in timing diagrams is to assist in determining the relative occurrence of events, not for

, t

CLCH

, t

CHCL

CLCL

External Clock Oscillator (XTAL1) Characteristics table.

when configured for memory interface, are also characterized with 100pF loading: Port 4 (CE0-3, A16–A19), Port 5.4–5.7 ( PCE0-3),

Port 6.0–6.5 (CE4-7, A20, A21), Port 7 (demultiplexed mode A0–A7).

contention.

determing absolute signal timing with respect to the external clock.

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

75MHz VARIABLE CLOCK

MIN MAX MIN MAX

1 / t

CLK

16 37.5 Clock Mutliplier 2X Mode

11 18.75

1 / t

CLK

11 18.75

+ t

CLCL

1.7 t

LHLL

4.7 t

AVLL

14.3 2t

LLAX

3.7 t

t

LLIV

21.7 2t

t

LLPL

9.7 2t

t

PLPH

0 0 ns

t

PLIV

8.3 t

t

PXIX

21.0 3t

AVIV0

27.7 3t

t

AVIV2

0 0 ns

t

PLAZ

CHCL

CLCH

CLCH

- 5 ns

CHCL

- 5 ns

- 2 ns

+ t

CLCL

- 3 ns

- 5 ns

CLCL

CLCL

CLCL

CLCL

+ t

CLCL

are time periods associated with the internal system clock and are related to the external clock (t

3 of 96

UNITS

MHz

MHz

- 19 ns

CLCH

-17 ns

- 5 ns

- 19 ns

- 19 ns

CLCH

) as defined in the

CLK

Page 4

DS80C400 Network Microcontroller

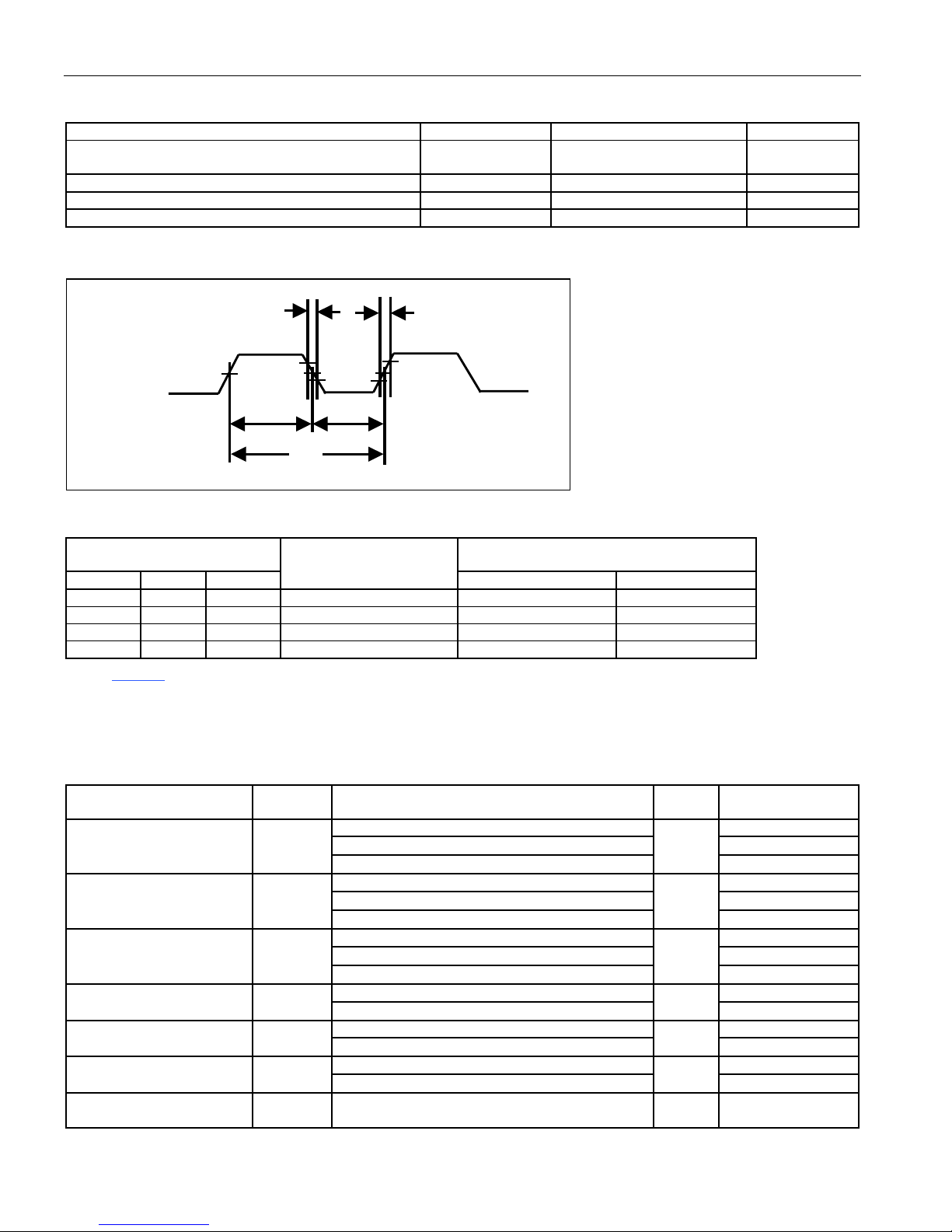

EXTERNAL CLOCK OSCILLATOR (XTAL1) CHARACTERISTICS

PARAMETER SYMBOL MIN MAX UNITS

Clock Oscillator Period t

Clock Symmetry at 0.5 x V

t

CC3

CLK

0.45 t

CH

See External Clock

Oscillator Frequency

0.55 t

CLK

ns

CLK

Clock Rise Time tCR 3 ns

Clock Fall Time tCF 3 ns

EXTERNAL CLOCK DRIVE

t

CF

tCR

XTAL1

t

CH

tCL

t

CLK

SYSTEM CLOCK TIME PERIODS (t

SYSTEM CLOCK SELECTION

4X/2X

CD1 CD0

1 0 0 t

0 0 0 t

X 1 0 t

X 1 1 256 t

Note 1: Figure 20 shows a detailed description and illustration of the system clock selection.

Note 2: When an external clock oscillator is used in conjunction with the default system clock selection (CD1:CD0 = 10b), the

minimum/maximum system clock high (t

SYSTEM CLOCK

PERIOD t

/ 4 0.45 (t

CLK

/ 2 0.45 (t

CLK

0.45 t

CLK

CLK

) and system clock low (t

CHCL

CLCL

, t

CHCL

, t

CLCH

SYSTEM CLOCK HIGH (t

CLCL

SYSTEM CLOCK LOW (t

MIN MAX

0.45 (256 t

) periods are directly related to clock oscillator duty cycle.

CLCH

)

/ 4) 0.55 (t

CLK

/ 2) 0.55 (t

CLK

0.55 t

CLK

0.55 (256 t

CLK)

CHCL

) AND

CLCH

CLK

CLK

)

CLK

/ 4)

/ 2)

CLK)

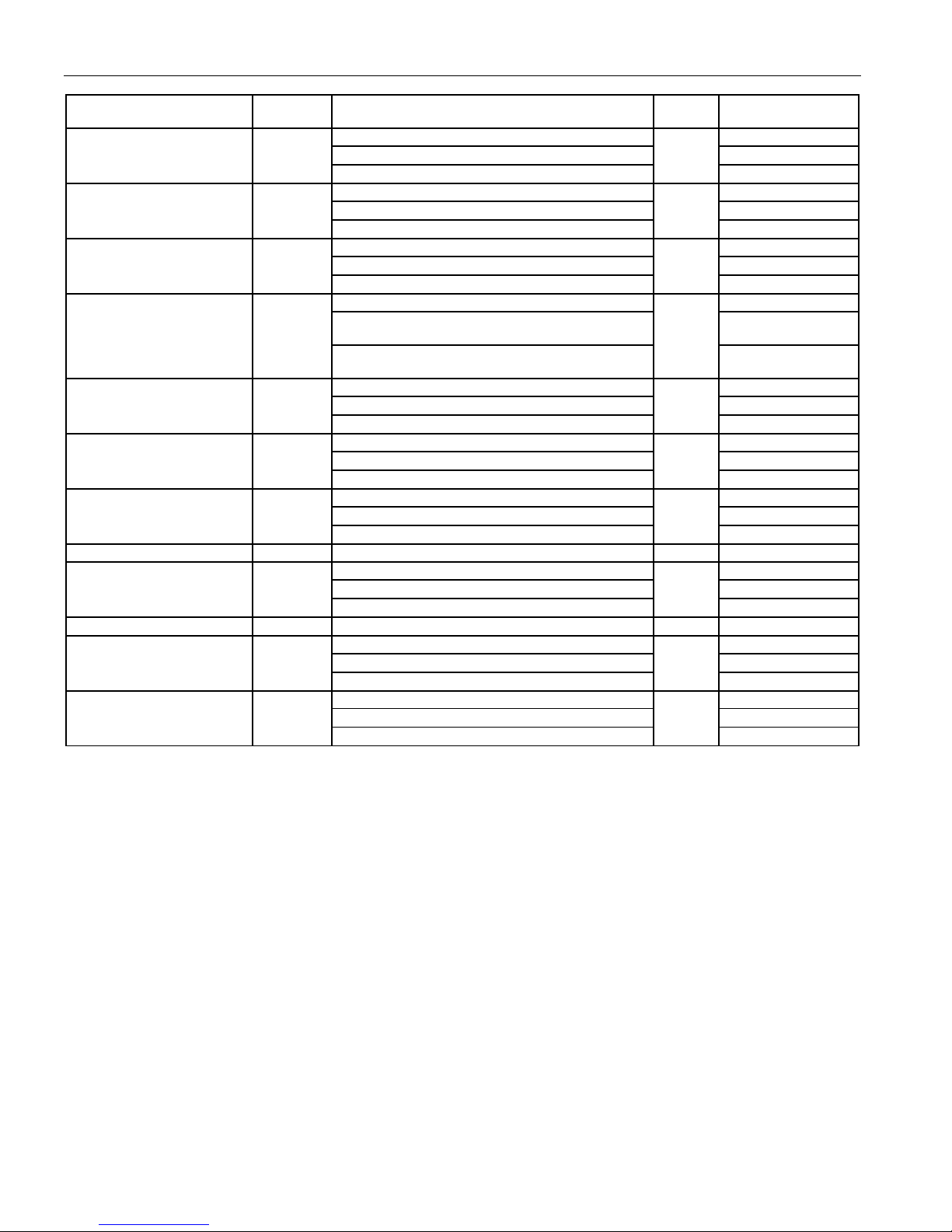

MOVX CHARACTERISTICS (MULTIPLEXED ADDRESS/DATA BUS) (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL MIN MAX UNITS

MOVX ALE Pulse Width t

Port 0 MOVX Address Valid

to ALE Low

Port 0 MOVX Address Hold

after ALE Low

RD Pulse Width (P3.7 or

PSEN)

WR Pulse Width (P3.6)

RD (P3.7 or PSEN) Low to

Valid Data In

Data Hold After RD (P3.7 or

PSEN) High

= 1.8V ±10%, TA = -40 °C to +85°C.)

CC1

t

+ t

CLCL

LHLL2

2t

6t

t

CHCL

t

AVLL2

t

CLCL

5t

t

5t

2t

(4 x C

2t

(4 x C

CLCH

t

CLCL

t

LLAX2

and t

LLAX3

t

RLRH

t

WLWH

t

RLDV

-2 ns

t

RHDX

- 5 CST = 0

CHCL

- 5

CLCL

- 5

CLCL

- 5 CST = 0

- 6

- 6

CLCL

- 2 CST = 0

- 2

- 2

CLCL

- 5 CST = 0

CLCL

) t

ST

CLCL

ST

- 3

CLCL

- 5 CST = 0

) t

- 3

CLCL

2t

(4 x C

STRETCH VALUES

C

ns

1£ C

4 £ C

ns

1£ C

4 £ C

ns

1£ C

4 £ C

ns

ns

- 17 CST = 0

CLCL

ST

) t

CLCL

- 17

ns

1 £ C

1 £ C

1 £ C

(MD2:0)

ST

ST

ST

ST

ST

ST

ST

ST

ST

ST

£ 3

£ 7

£ 3

£ 7

£3

£ 7

£ 7

£ 7

£ 7

4 of 96

Page 5

DS80C400 Network Microcontroller

PARAMETER SYMBOL MIN MAX UNITS

Data Float After RD (P3.7 or

PSEN) High

t

RHDZ

t

2t

6t

2t

ALE Low to Valid Data In t

LLDV

(4 x CST + 1) t

(4 x CST + 5) t

Port 0 Address to Valid Data

In

t

AVDV0

3t

(4 x CST + 2)t

(4 x CST + 10)t

3t

Port 2, 4, 6 Address, Port 4

CE, or Port 5 PCE to Valid

t

AVDV2

Data In

ALE Low to (RD or PSEN) or

WR Low

Port 0 Address to (RD or

PSEN) or WR Low

Port 2, 4 Address, Port 4 CE,

Port 5 PCE, to (RD or PSEN)

or WR Low

Data Valid to WR Transition

Data Hold After WR High

RD Low to Address Float

(RD or PSEN) or WR High to

ALE

t

LLWL

t

AVWL0

t

t

AVWL2

2t

10t

0 ns

t

QVWX

t

WHQX

(Note 2)

t

RLAZ

t

WHLH

(RD or PSEN) or WR High to

Port 4 CE or Port 5 PCE

High

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: For a MOVX read operation, on the falling edge of ALE, Port 0 is held by a weak latch until overdriven by external memory.

Note 3: All parameters apply to both commercial and industrial temperature operation, unless otherwise noted.

Note 4: CST is the stretch cycle value as determined by the MD2, MD1, and MD0 bits of the CKCON register. t

periods associated with the internal system clock and are related to the external clock. See the System Clock Time Periods table.

Note 5: All signals characterized with load capacitance of 80pF except Port 0, Port 2, ALE, PSEN, RD, and WR with 100pF. The following

signals, when configured for memory interface, are also characterized with 100pF loading: Port 4 (CE0-3, A16–A19), Port 5.4–5.7

(PCE0-3), Port 6.0–6.5 (CE4-7, A20, A21), Port 7 (demultiplexed mode A0–A7).

Note 6: References to the XTAL, XTAL1, or CLK signal in timing diagrams are to assist in determining the relative occurrence of events, not for

determing absolute signal timing with respect to the external clock.

t

WHLH2

t

5t

t

- 3 t

CLCH

t

- 3 t

CLCL

5t

- 3 5t

CLCL

t

- 5 CST = 0

CLCL

2t

- 6

CLCL

10t

- 6

CLCL

+ t

CLCL

CLCL

CLCL

2

6t

t

CLCL

- 5 CST = 0

CLCH

+ t

- 5

CLCH

+ t

- 5

CLCH

- 4 CST = 0

- 7

CLCL

- 7

CLCL

0 7 CST = 0

t

- 3 t

CLCL

5t

- 3 5t

CLCL

t

-5 t

CHCL

+ t

+ t

CHCL

CHCL

- 5 t

- 5 5t

CLCL

CLCL

(4 x C

(4 x C

ST

CLCL

CLCL

- 5 CST = 0

CLCL

- 5

CLCL

- 5

CLCL

+ t

CLCL

CLCL

ST

+ 2)t

- 19 CST = 0

CLCH

- 19

CLCL

- 19

CLCL

- 19 CST = 0

CLCL

- 19

CLCL

- 19

CLCL

+ t

- 19 CST = 0

CLCH

+ t

CLCL

CLCH

19

+ 10)t

CLCL

+ t

CLCH

ns

ns

ns

ns

-

20

+ 6 CST = 0

CLCH

CLCL

CLCL

+ 6

+ 6

ns

ns

ns

ns

+ 4

CLCL

+ 4

CLCL

+ 13 CST = 0

CHCL

+ t

+ 13

CHCL

+ t

+ 13

CHCL

ns

ns

STRETCH VALUES

(MD2:0)

C

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

1£ CST £ 3

4 £ CST £ 7

£ 3

1 £ C

ST

£ 7

4 £ C

ST

£ 3

1 £ C

ST

£ 7

4 £ C

ST

£ 3

1 £ C

ST

£ 7

4 £ C

ST

£ 3

1 £ C

ST

£ 7

4 £ C

ST

£ 7

0£ C

ST

£ 3

1 £ C

ST

£ 7

4 £ C

ST

£ 3

1 £ C

ST

£ 7

4 £ C

ST

, t

, t

CLCL

CLCH

are time

CHCL

5 of 96

Page 6

DS80C400 Network Microcontroller

6 of 96

Page 7

DS80C400 Network Microcontroller

7 of 96

Page 8

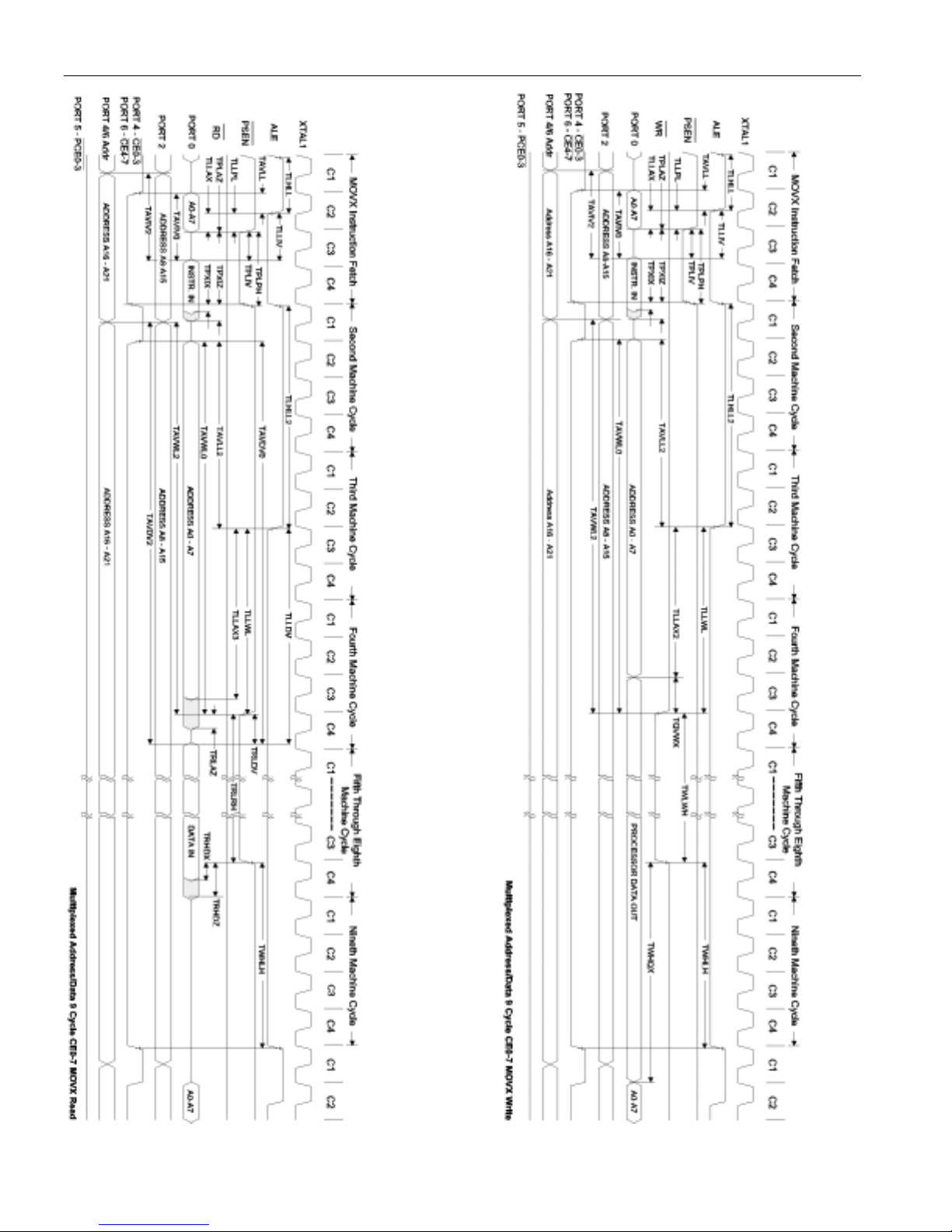

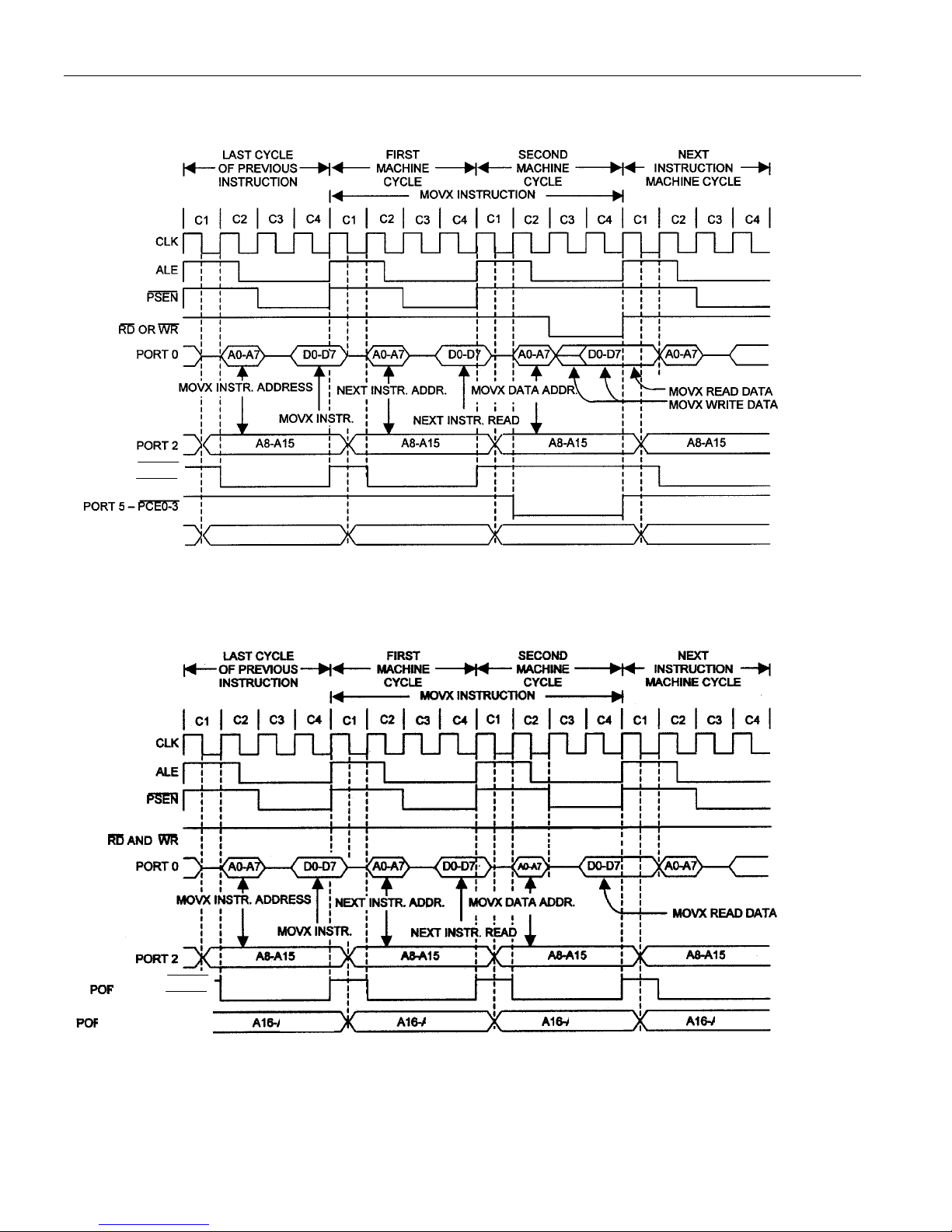

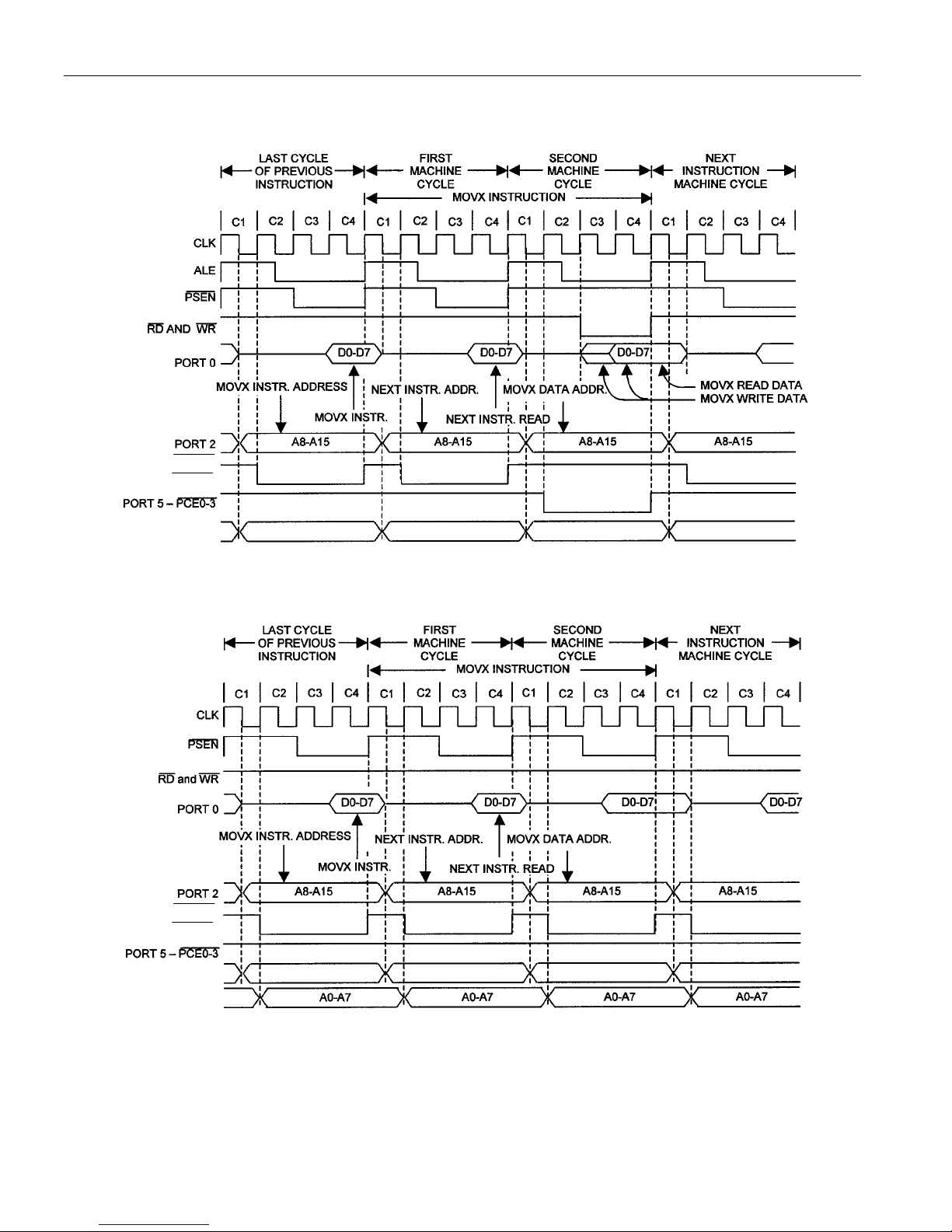

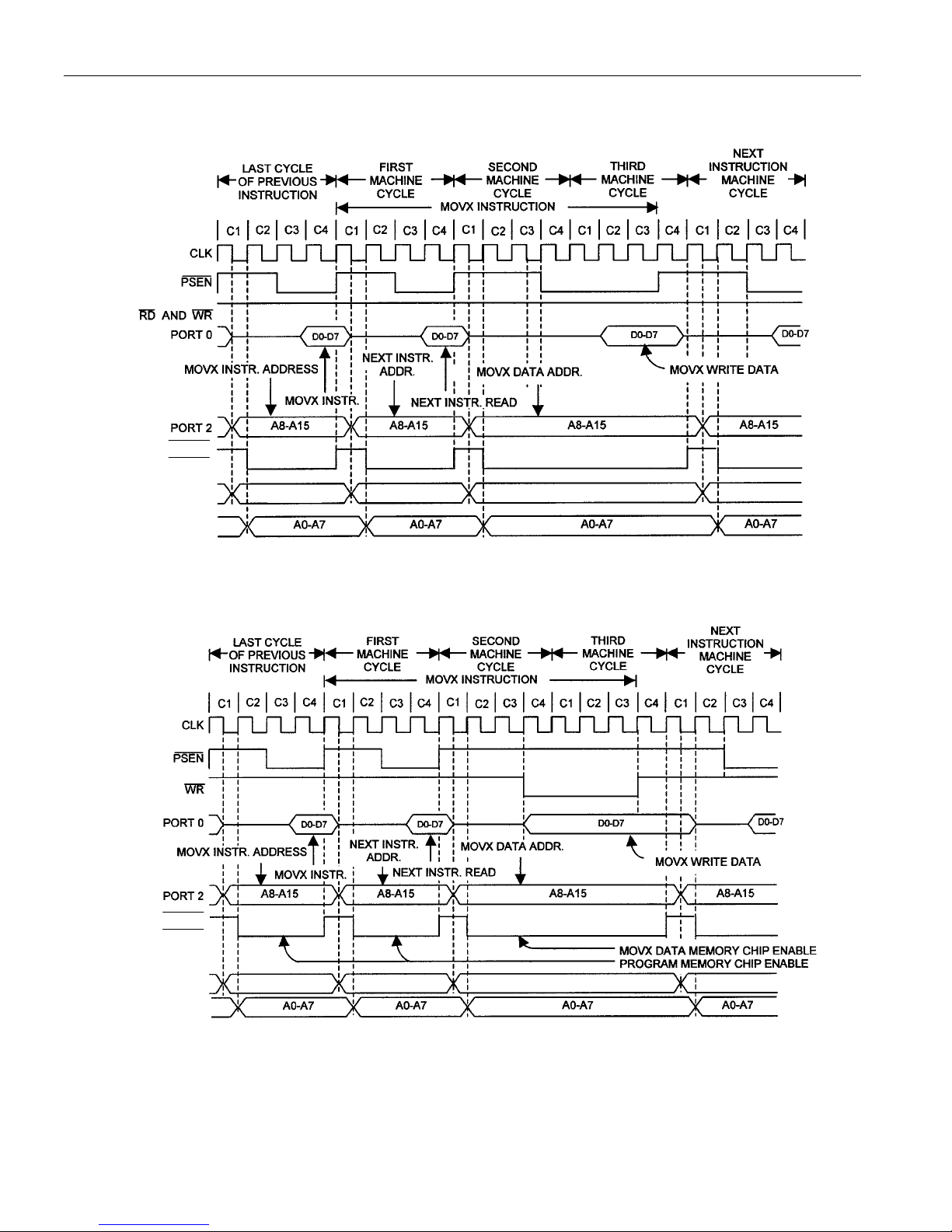

MULTIPLEXED, 2-CYCLE DATA MEMORY PCE0-3 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

DS80C400 Network Microcontroller

PORT 4/6 ADDRESS

A16 -A21

-

A16 -A21 A16 -A21

MULTIPLEXED, 2-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21

A16 -A21 A16 -A21

A16 -A21

8 of 96

Page 9

DS80C400 Network Microcontroller

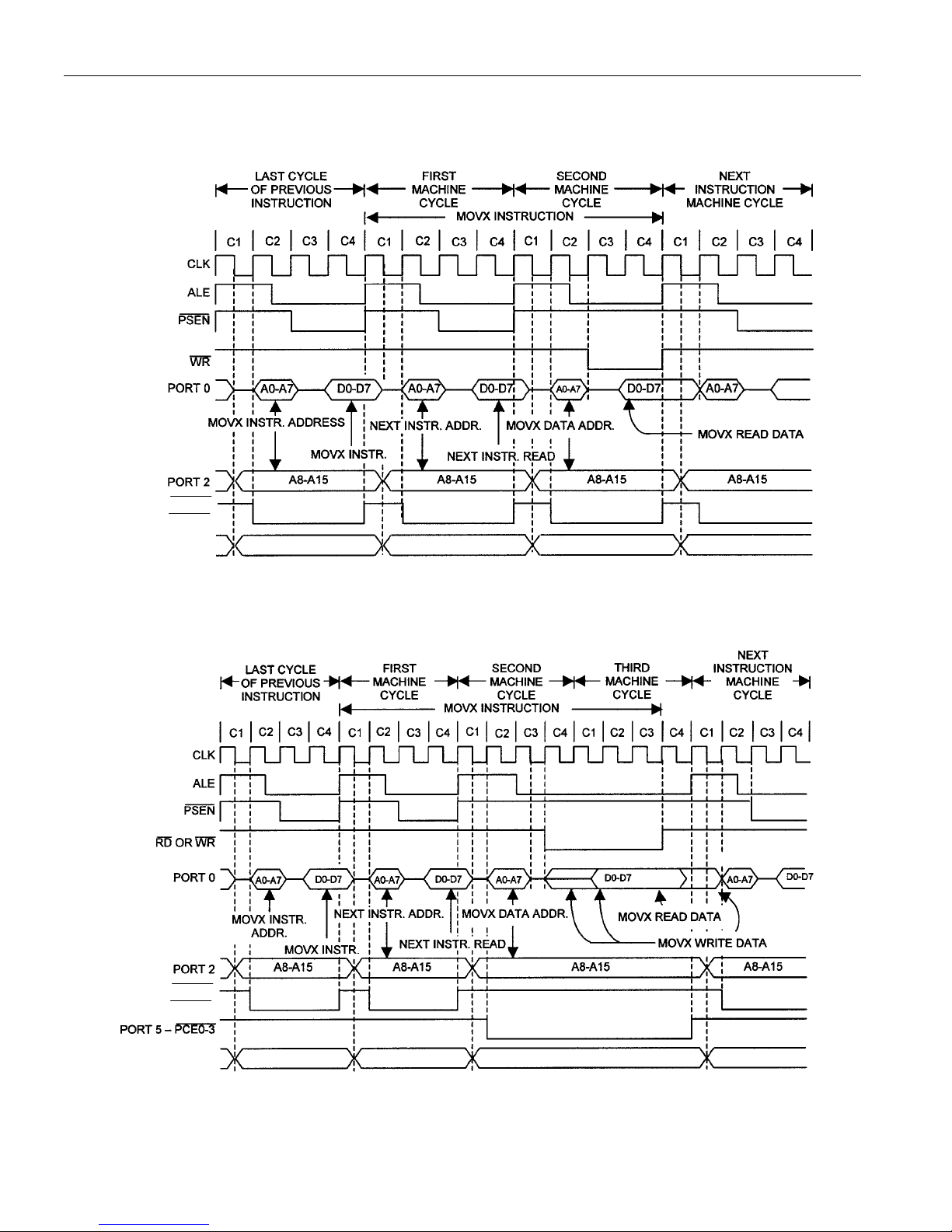

MULTIPLEXED, 2-CYCLE DATA MEMORY CE0-7 WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21

A16 -A21

A16 -A21

MULTIPLEXED, 3-CYCLE DATA MEMORY PCE0-3 READ OR WRITE

A16 -A21

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21

A16 -A21

A16 -A21 A16 -A21

9 of 96

Page 10

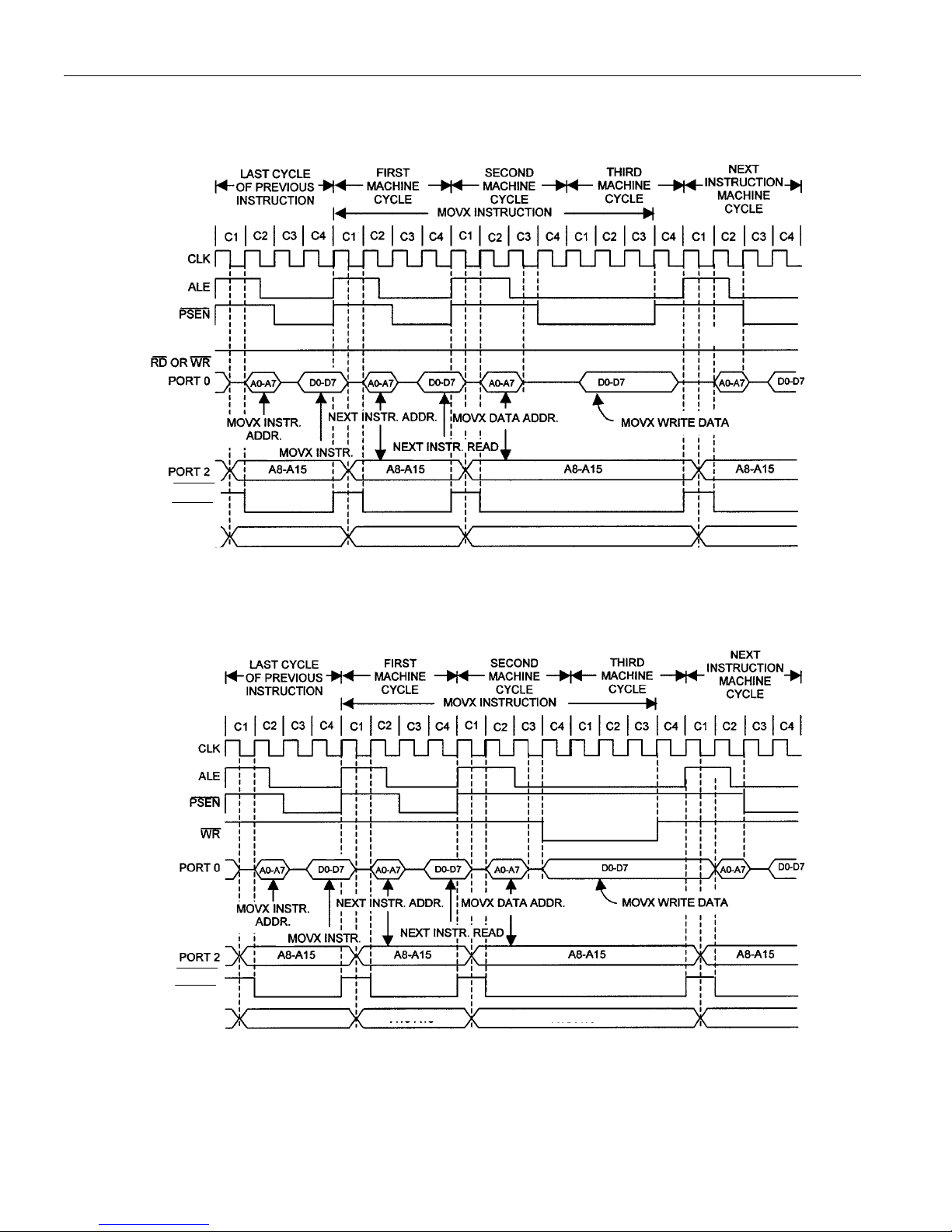

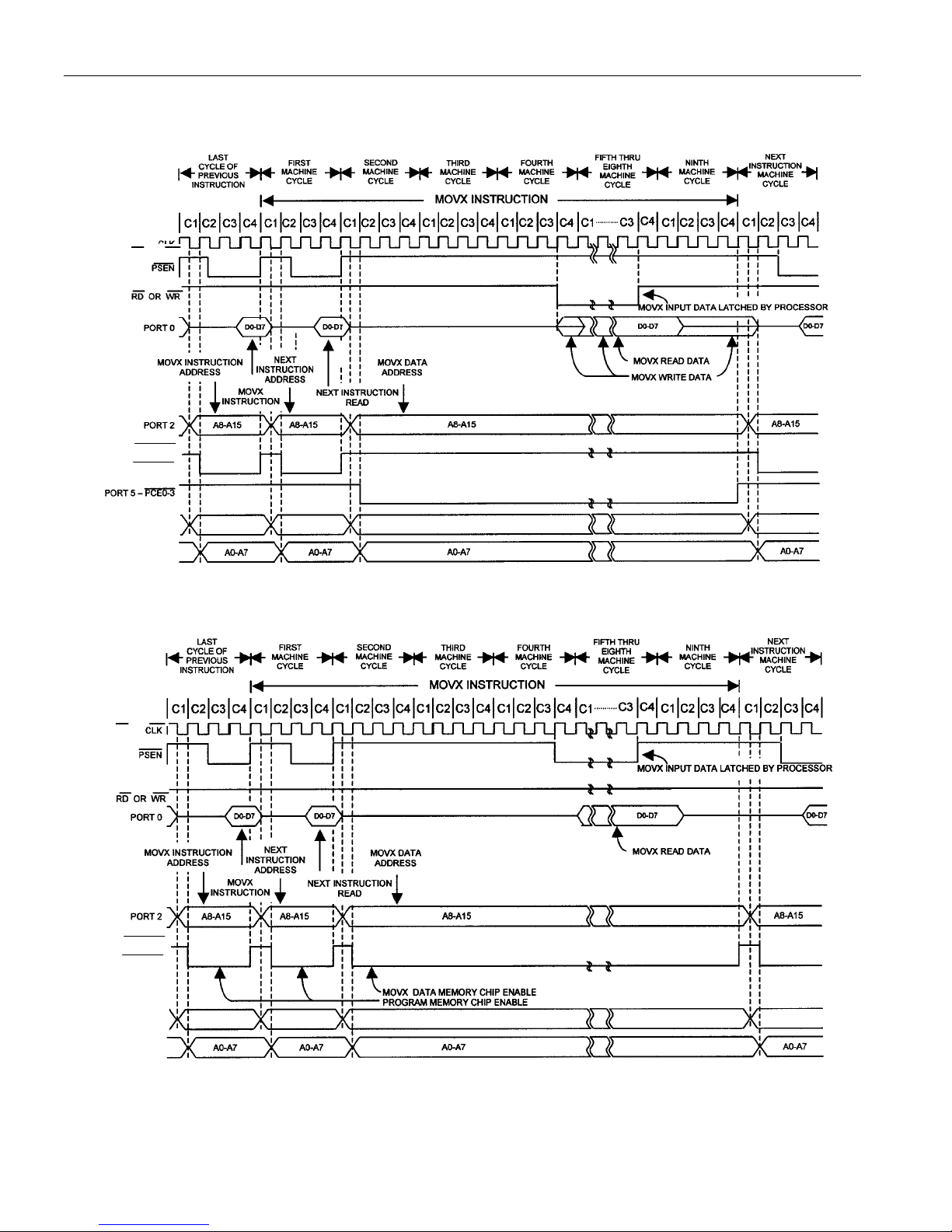

MULTIPLEXED, 3-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21 A16 -A21

A16 -A21

MULTIPLEXED, 3-CYCLE DATA MEMORY CE0-7 WRITE

DS80C400 Network Microcontroller

A16 -A21

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

-

-

10 of 96

-

A16 -A21

Page 11

DS80C400 Network Microcontroller

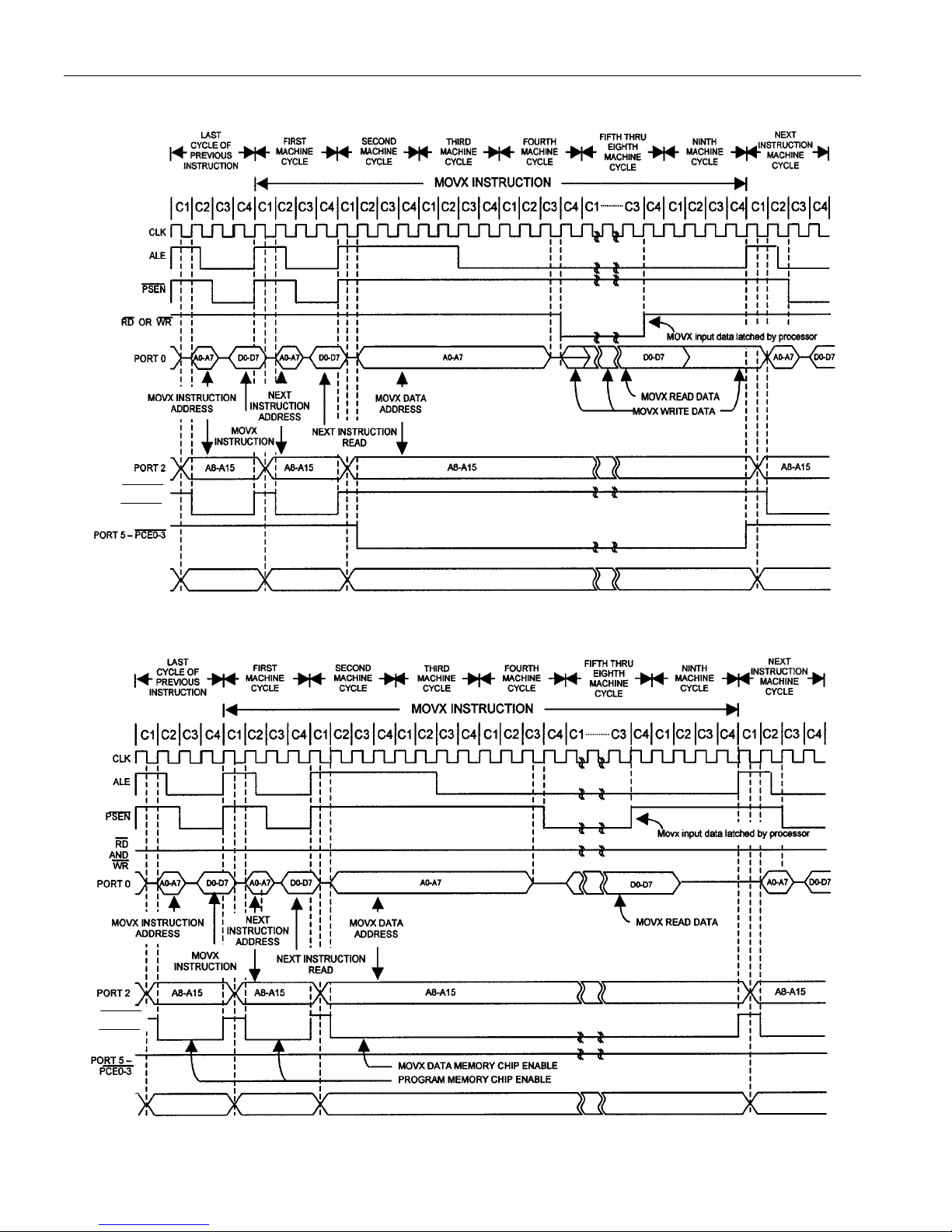

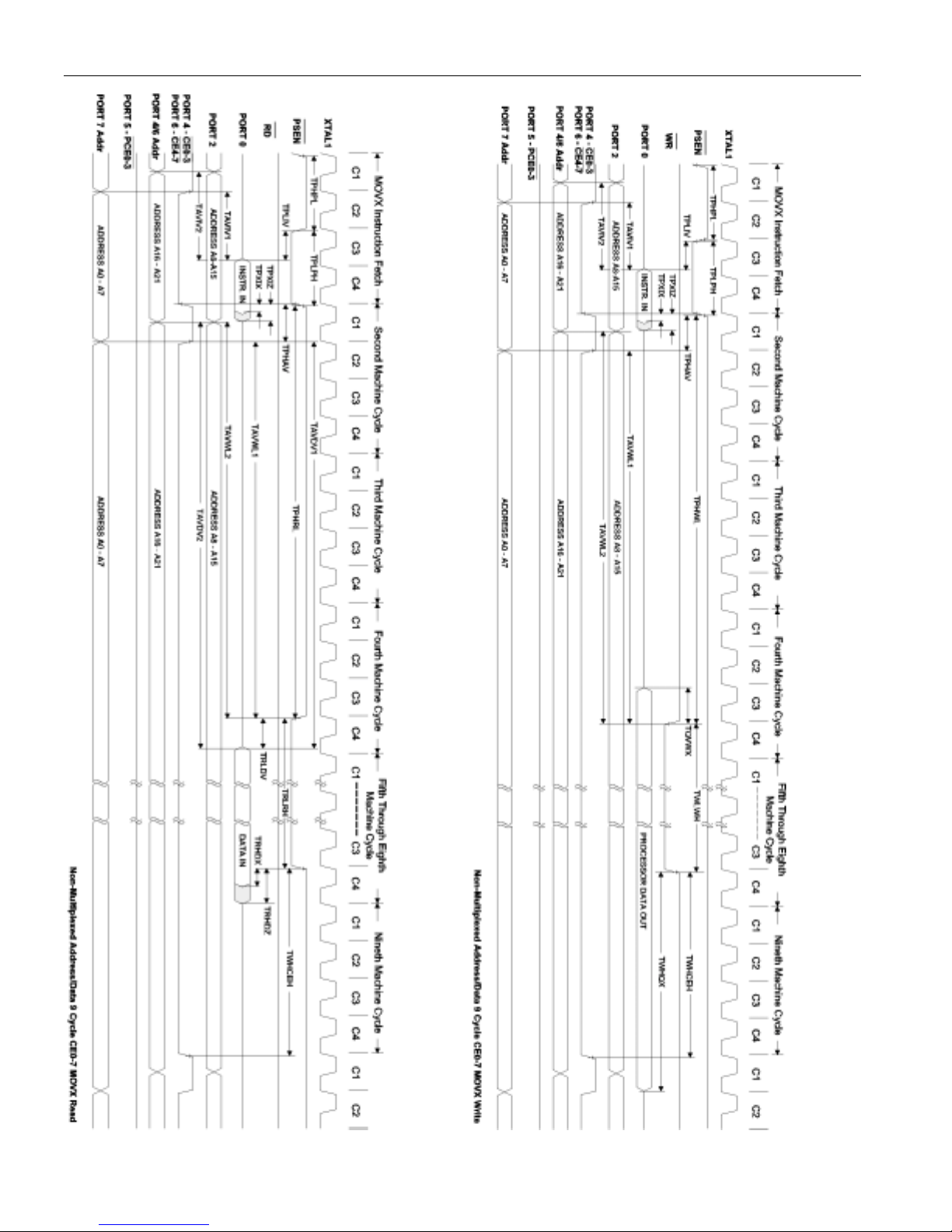

MULTIPLEXED, 9-CYCLE DATA MEMORY PCE0-3 READ OR WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21 A16 -A21 A16 -A21

MULTIPLEXED, 9-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

A16 -A21

PORT 4/6

ADDRESS

A16 -A21 A16 -A21 A16 -A21

A16 -A21

11 of 96

Page 12

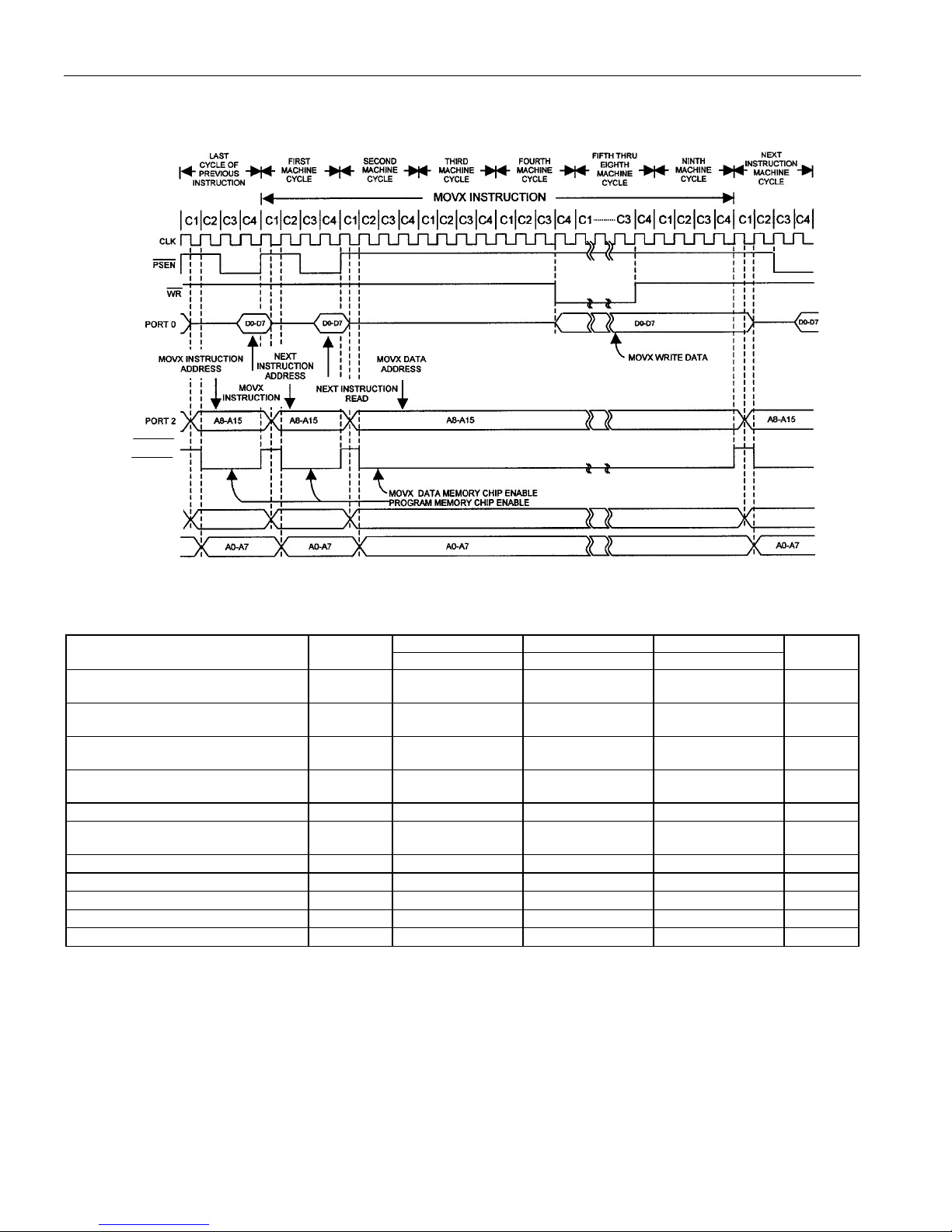

MULTIPLEXED, 9-CYCLE DATA MEMORY CE0-7 WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

DS80C400 Network Microcontroller

PORT 4/6

ADDRESS

A16 -A21

A16 -A21 A16 -A21

A16 -A21

12 of 96

Page 13

DS80C400 Network Microcontroller

ELECTRICAL CHARACTERISTICS (NONMULTIPLEXED ADDRESS/DATA BUS)

(Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL

External Crystal Frequency 4 40

Clock Mutliplier 2X Mode 16 37.5

Clock Multiplier 4X Mode

External Oscillator Frequency DC 75

Clock Mutliplier 2X Mode 16 37.5

Clock Multiplier 4X Mode

PSEN Pulse Width

PSEN Low to Valid Instruction In

Input Instruction Hold After PSEN

Input Instruction Float After PSEN

Port 7 Address to Valid Instruction In t

Port 2, 4, 6 Address or Port 4 CE to Valid

Instruction In

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: All parameters apply to both commercial and industrial temperature operation, unless otherwise noted.

Note 3: t

Note 4: The precalculated 75MHz min/max timing specifications assume an exact 50% duty cycle.

Note 5: All signals characterized with load capacitance of 80pF except Port 0, Port 2, ALE, PSEN, RD, and WR with 100pF. The following

Note 6: References to the XTAL, XTAL1, or CLK signal in timing diagrams is to assist in determining the relative occurrence of events, not for

, t

CLCL

the System Clock Time Periods table.

, t

CLCH

CHCL

signals, when configured for memory interface, are also characterized with 100pF loading: Port 4 (CE0-3, A16–A19), Port 5.4–5.7

(PCE0-3), Port 6.0–6.5 (CE4-7, A20, A21), Port 7 (demultiplexed mode A0–A7).

determing absolute signal timing with respect to the external clock.

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

75MHz VARIABLE CLOCK

MIN MAX MIN MAX

1 / t

CLK

11 18.75

1 / t

CLK

11 18.75

21.7 2t

t

PLPH

9.7 2t

t

PLIV

0 0 ns

t

PXIX

t

PXIZ

21.0 3t

AVIV1

27.7 3t

t

AVIV2

are time periods associated with the internal system clock and are related to the external clock (t

- 5 ns

CLCL

CLCL

See MOVX

Characteristics

CLCL

+ t

CLCL

CLCH

UNITS

MHz

MHz

- 17 ns

ns

- 19 ns

- 19 ns

) as defined in the

CLK

13 of 96

Page 14

DS80C400 Network Microcontroller

MOVX CHARACTERISTICS (NONMULTIPLEXED ADDRESS/DATA BUS) (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL MIN MAX UNITS

Input Instruction Float After PSEN

PSEN High to Data Address, Port 4 CE,

Port 5 PCE Valid

RD Pulse Width (P3.7 or PSEN)

WR Pulse Width (P3.6)

RD (P3.7 or PSEN) Low to Valid Data In

Data Hold After RD (P3.7 or PSEN) High

Data Float After RD (P3.7 or PSEN) High

PSEN High to WR Low

PSEN High to (RD or PSEN) Low

Port 7 Address to Valid Data In t

Port 2, 4, 6 Address, Port 4 CE or Port 5

PCE to Valid Data In

Port 7 Address to (RD or PSEN) or WR

Low

Port 2, 4, 6 Address, Port 4 CE or Port 5

PCE to (RD or PSEN) or WR Low

Data Valid to WR Transition

Data Hold After WR High

(RD or PSEN) or WR High to Port 4 CE

or Port 5 PCE High

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: All parameters apply to both commercial and industrial temperature operation unless otherwise noted.

Note 3: CST is the stretch cycle value as determined by the MD2, MD1, and MD0 bits of the CKCON register. t

Note 4: All signals characterized with load capacitance of 80pF except Port 0, Port 2, ALE, PSEN, RD, and WR with 100pF. The following

Note 5: References to the XTAL or CLK signal in timing diagrams is to assist in determining the relative occurrence of events, not for determing

associated with the internal system clock and are related to the external clock. See the System Clock Time Periods table.

signals, when configured for memory interface, are also characterized with 100pF loading: Port 4 (CE0-3, A16–A19), Port 5.4–5.7

(PCE0-3), Port 6.0–6.5 (CE4-7, A20, A2), Port 7 (demultiplexed mode A0–A7).

absolute signal timing with respect to the external clock.

= 1.8V +±10%, TA = -40°C to +85°C.)

CC1

t

PXIZ

t

t

PHAV

t

RLRH

t

WLWH

t

RLDV

-2 ns

t

RHDX

t

RHDZ

2t

(4 x C

2t

(4 x C

2t

t

PHWL

3t

11t

2t

t

PHRL

3t

11t

AVDV1

t

AVDV2

t

t

AVWL1

2t

10t

t

CLCL

2t

t

AVWL2

0 ns

t

QVWX

10t

CLCL

CLCL

t

t

WHQX

2

6t

t

t

WHCEH

t

5t

CLCL

CLCL

14 of 96

CST (MD2:0)

2t

3t

11t

- 3 ns

CHCL

- 5 CST =0

CLCL

) t

ST

CLCL

ST)tCLCL

- 3

CLCL

- 5 CST =0

- 3

2t

(4 x C

t

2t

6t

- 3 CST = 0

CLCL

- 3

CLCL

- 3

CLCL

- 3 CST = 0

CLCL

- 3

CLCL

- 3

CLCL

3t

(4 x CST + 2)t

3t

- 5 CST = 0

CLCL

- 5

CLCL

- 5

CLCL

+ t

- 5 CST = 0

CLCH

+ t

- 5

CLCH

+ t

- 5

CLCH

- 4 CST = 0

CLCL

- 7

CLCL

- 7

CLCL

- 5 t

CHCL

+ t

- 5 t

CHCL

+ t

-5 5t

CHCL

(4 x C

CLCL

(4 x C

(4 x C

CLCL

CLCL

- 5 CST = 0

CLCL

CLCL

CLCL

- 5

- 5

ns

ns

ns

- 17 CST = 0

CLCL

- 17

ST)tCLCL

- 5 CST = 0

CLCL

- 5

CLCL

- 5

CLCL

ns

ns

ns

ns

- 19 CST = 0

CLCL

- 19

+ 10)t

ST

CLCL

CLCL

-

ns

19

+ t

- 19 CST = 0

CLCH

ST

t

CLCH

ST

t

CLCH

+ 2)t

+ 10)t

- 19

- 19

CLCL

CLCL

+

ns

+

ns

ns

ns

+ 13 CST = 0

CHCL

CLCL

ns

, t

, t

CLCH

are time periods

CHCL

+ t

+ t

CHCL

CHCL

+12

+12

STRETCH

VALUES

£ 3

1£ C

ST

£ 7

4 £ C

ST

£ 7

1 £ C

ST

1 £ C

£ 7

ST

1 £ C

£ 7

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

£ 3

1£ C

ST

4 £ C

£ 7

ST

£ 3

1£ C

ST

£ 7

4 £ C

ST

1£ CST £ 3

£ 7

4 £ C

ST

£ 3

1 £ C

ST

4 £ C

£ 7

ST

£ 3

1 £ C

ST

4 £ C

£ 7

ST

£ 3

1 £ C

ST

4 £ C

£ 7

ST

£ 3

1 £ C

ST

4 £ C

£ 7

ST

Page 15

DS80C400 Network Microcontroller

15 of 96

Page 16

DS80C400 Network Microcontroller

l

16 of 96

Page 17

DS80C400 Network Microcontroller

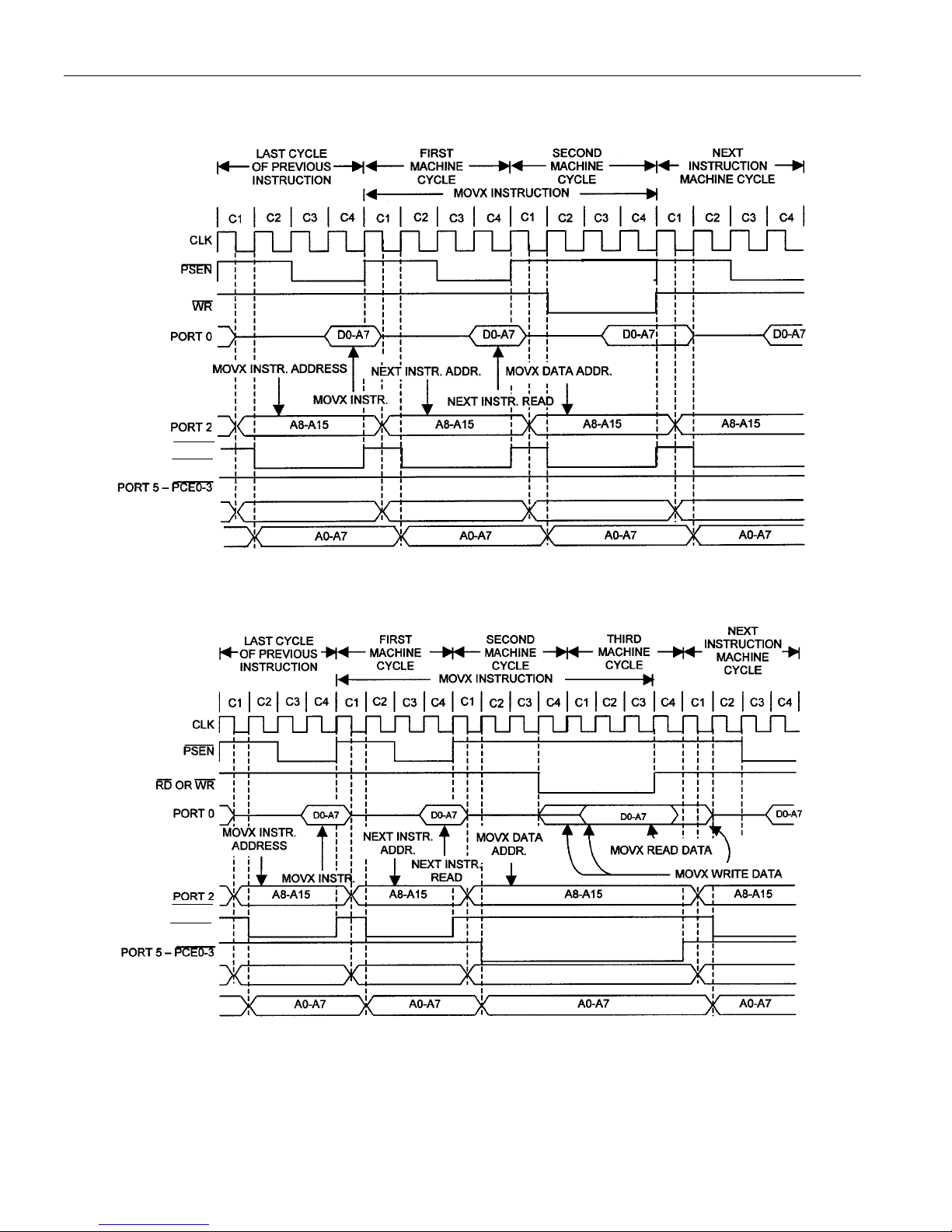

NONMULTIPLEXED, 2-CYCLE DATA MEMORY PCE0-3 READ OR WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

-

A16 -A21

A16 -A21 A16 -A21

NONMULTIPLEXED, 2-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21

PORT 7

A16 -A21

A16 -A21 A16 -A21

17 of 96

Page 18

NONMULTIPLEXED, 2-CYCLE DATA MEMORY CE0-7 WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

DS80C400 Network Microcontroller

PORT 4/6 ADDRESS

PORT 7

A16 -A21

A16 -A21 A16 -A21

NONMULTIPLEXED, 3-CYCLE DATA MEMORY PCE0-3 READ OR WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

A16 -A21

PORT 4/6 ADDRESS

PORT 7

A16 -A21

A16 -A21

18 of 96

A16 -A21

A16 -A21

Page 19

NONMULTIPLEXED, 3-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

A16 -A21

A16 -A21 A16 -A21

DS80C400 Network Microcontroller

A16 -A21

PORT 7

NONMULTIPLEXED, 3-CYCLE DATA MEMORY CE0-7 WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

PORT 7

A16 -A21 A16 -A21 A16 -A21 A16 -A21

19 of 96

Page 20

DS80C400 Network Microcontroller

7

NONMULTIPLEXED, 9-CYCLE DATA MEMORY PCE0-3 READ OR WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

PORT 4/6 ADDRESS

PORT

A16 -A21

A16 -A21

-

NONMULTIPLEXED, 9-CYCLE DATA MEMORY CE0-7 READ

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

-

PORT 4/6 ADDRESS

PORT 7

A16 -A21

A16 -A21 A16 -A21

A16 -A21

20 of 96

Page 21

NONMULTIPLEXED, 9-CYCLE DATA MEMORY CE0-7 WRITE

PORT 4 – 3CE0 -

PORT 6 – 7-CE4

DS80C400 Network Microcontroller

PORT 4/6 ADDRESS

PORT 7

A16 -A21 A16 -A21

A16 -A21 A16 -A21

OW PIN TIMING CHARACTERISTICS (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL

Transmit Reset Pulse Low Time

(Note 2)

Transmit Reset Pulse High Time

(Note 2)

Wait Time for Transmit of Presence

Pulse (Notes 2, 3)

Wait Time for Absence of Presence

Pulse (Notes 2, 4)

Presence Pulse Width (Note 2) t

Presence Pulse Sampling Time

(Note 2)

Read/Write Data Time Slot t

Low Time for Write 1 t

Low Time for Write 0 t

Write Data Sampling Time t

Read Data Sampling Time t

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: In PMM mode, the master pulls the line low after the first 15ms for the remainder of the standard speed 1-Wire routine.

Note 3: This parameter quantifies the wait time for the slave devices to respond to the reset pulse and is dependent on the slave device timing.

Note 4: This parameter quantifies the wait time for the case when no presence pulse detected.

Note 5: The maximum timing figures shown apply only when an exact 1-Wire clock frequency can be achieved from the microcontroller input

.

clock

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

STANDARD OVERDRIVE LONGLINE

MIN MAX MIN MAX MIN MAX

500.8 626 50.4 63 500.8 626

t

RSTL

t

508.8 636 59.2 74 508.8 636

RSTH

15 60 2 6 15 60

t

PDH

60 75 6.4 8 60 75

t

PDHCNT

60 240 8 24 60 240

PDL

24 31 2.4 4 30.4 38

t

PDS

68.8 86 12 15 68.8 86

SLOT

4.8 6 0.8 1 7.2 9

LOW1

62.4 78 8 10 62.4 78

LOW0

15 60 2 6 25 60

WDV

12 15 1.6 2 20 25

RDV

UNITS

ms

ms

ms

ms

ms

ms

ms

ms

ms

ms

ms

21 of 96

Page 22

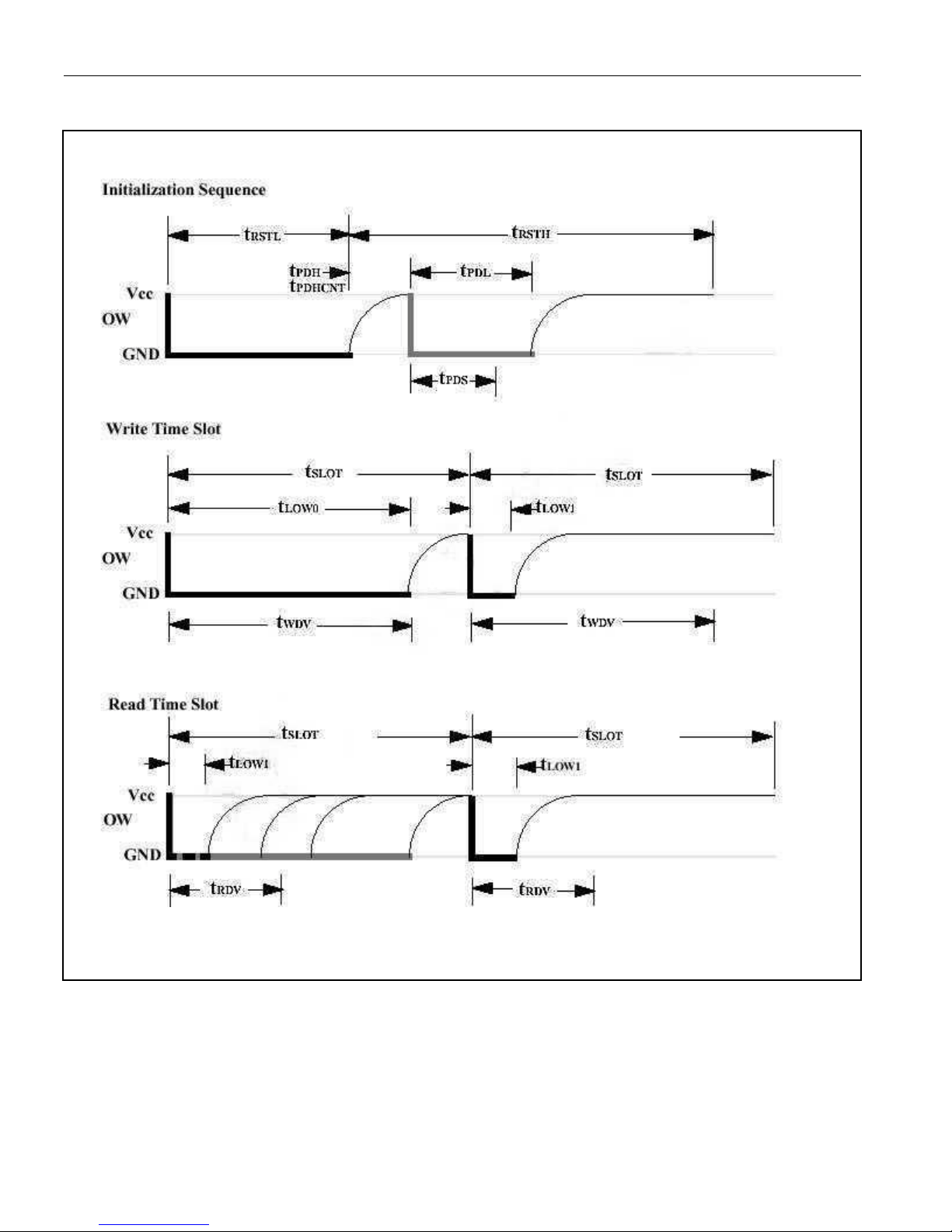

OW PIN TIMING

DS80C400 Network Microcontroller

22 of 96

Page 23

DS80C400 Network Microcontroller

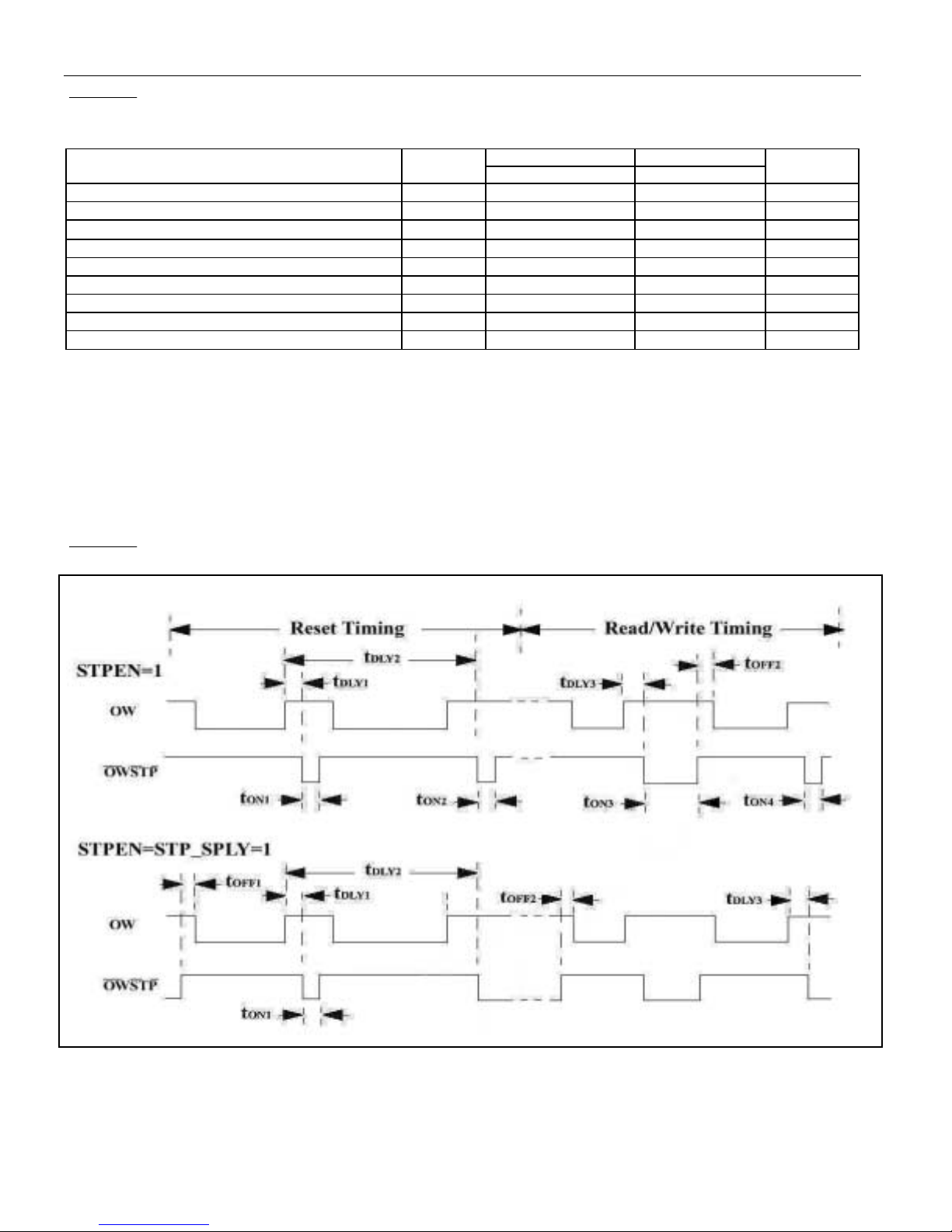

OWSTP PIN TIMING CHARACTERISTICS (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL

Active Time for Presence Detect t

Active Time for Presence Detect Recovery t

Active Time for Write 1 Recovery (Notes 2, 3) t

Active Time for Write 0 Recovery (Notes 2, 3) t

Delay Time for Presence Detect t

Delay Time for Presence Detect Recovery (Note 4) t

Delay Time for Write 1/Write 0 Recovery t

Turn-Off Time for 1-Wire Reset t

Turn-Off Time for Write 1/Write 0 (Note 5) t

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

Note 2: There is no OWSTP timing difference for sending out and receiving bits within a byte. The difference comes when the last bit of the byte

Note 3: When performing a read versus a write time slot, the master provides the same active time for write 1 and write 0. However, the

Note 4: This parameter is the time delay until the master begins to monitor the OW pin level. If the line is already high, then OWSTP is enabled.

Note 5: The very first bit in a byte has an extended turn-off time of 4ms because of the order of states that the 1-Wire master state machine

has been completely sent. At this point, the signal is either enabled continuously until the next reset or time slot begins, or enabled only

for active time write 1 or write 0.

Schmitt-triggered input from the OW line is sensed every 1ms for a high value. If OW is high, the OWSTP signal is enabled. If the OW

line is low, the OWSTP signal remains disabled until a high state is sensed. In all write time slots, a high is sensed immediately.

If not, it waits to enable OWSTP until the next state machine clock (1ms or 50ns) after the OW line recovers.

must go through.

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

ON1

ON2

ON3

ON4

DLY1

DLY2

DLY3

OFF1

OFF2

STANDARD OVERDRIVE

MIN MAX MIN MAX

6.4 8 0.8 1

8 10 8 10

51.2 64 7.2 9

6.4 8 0.8 1

0.8 1 0.8 1

399.2 499 31.2 39

0.8 1 0.8 1

1.6 2 1.6 2

0.8 1 0.8 1

UNITS

ms

ms

ms

ms

ms

ms

ms

ms

ms

OWSTP PIN TIMING

23 of 96

Page 24

DS80C400 Network Microcontroller

ETHERNET MII INTERFACE TIMING CHARACTERISTICS (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL

TXClk Duty Cycle t

TXD, TX_EN Data Setup to TXClk t

TXD, TX_EN Data Hold from TXClk t

RXClk Pulse Width t

RXClk to RXD, RX_DV, RX_ER Valid t

MDC Period t

MDC to Input Data Valid t

MDIO Output Data Setup to MDC t

MDIO Output Data Hold from MDC t

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

MII INTERFACE TIMING

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

14 26 140 260 ns

TDC

10 25 ns

TSU

2 2 ns

THD

14 26 140 260 ns

RDC

10 30 190 210 ns

RDV

400 400 ns

MCLCL

300 300 ns

MDV

10 10 ns

MOS

10 10 ns

MOH

100Mbps 10Mbps

MIN MAX MIN MAX

UNITS

24 of 96

Page 25

DS80C400 Network Microcontroller

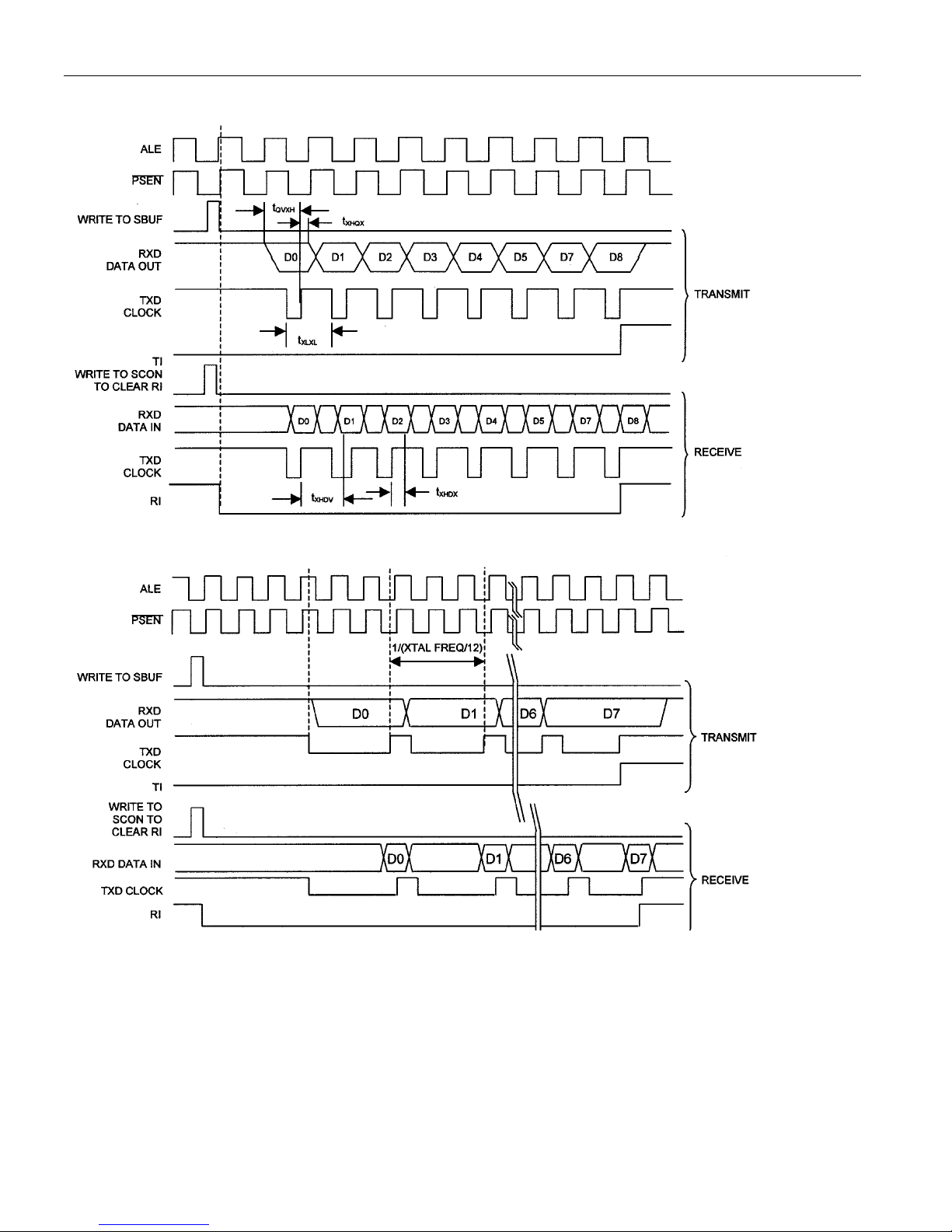

SERIAL PORT MODE 0 TIMING CHARACTERISTICS (Note 1)

(V

= 3.0V to 3.6V, V

CC3

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

= 1.8V ±10%, TA = -40°C to +85°C.)

CC1

SM2 = 0:12 clocks per cycle 12 t

Serial Port Clock Cycle Time t

XLXL

SM2 = 1:4 clocks per cycle 4 t

Output Data Setup to Clock

Rising

Output Data Hold from Clock

Rising

t

QVXH

t

XHQX

SM2 = 0:12 clocks per cycle

SM2 = 1:4 clocks per cycle

SM2 = 0:12 clocks per cycle

SM2 = 1:4 clocks per cycle

Input Data Hold After Clock

Rising

t

XHDX

SM2 = 0:12 clocks per cycle 0

SM2 = 1:4 clocks per cycle 0

SM2 = 0:12 clocks per cycle

t

Data Valid

Note 1: Specifications to -40°C are guaranteed by design and not production tested.

XHDV

SM2 = 1:4 clocks per cycle

10 t

3 t

CLCL

10

CLCL

10

CLCL

ns

CLCL

-

-

-

2 t

CLCL

10

-

t

CLCL

ns

ns

10

ns

-

11 t

CLCL

3 t

20 Clock Rising Edge to Input

CLCL

-

ns

20

25 of 96

Page 26

SERIAL PORT 0 (SYNCHRONOUS MODE)

DS80C400 Network Microcontroller

HIGH-SPEED OPERATION, TXD CLK = SYSCLK/4 (SM2 = 1)

TRADITIONAL 8051 OPERATION, TXD CLOCK = XTAL/12 (SM2 = 0)

26 of 96

Page 27

DS80C400 Network Microcontroller

POWER CYCLE TIMING CHARACTERISTICS

PARAMETER SYMBOL MIN TYP MAX UNITS

Crystal Startup Time (Note 1) t

Power-On Reset Delay (Note 2) t

Note 1: Startup time for crystals varies with load capacitance and manufacturer. Time shown is for an 11.0592MHz crystal manufactured by Fox

Note 2: Reset delay is a synchronous counter of crystal oscillations during crystal startup. Counting begins when the level on the XTAL1 input

Electronics.

meets the V

criteria. At 40MHz, this time is approximately 1.64ms.

IH2

POWER CYCLE TIMING

1.8 ms

CSU

65,536 t

POR

CLCK

27 of 96

Page 28

X

A

MANAGEMENT

I/O

BLOCK DIAGRAM

DS80C400 Network Microcontroller

OW

OWSTP

P1.0–P1.7

P0.0–P0.7

MDC MDIO

MII I/O (15)

P3.0–P3.7

1-WIRE

CONTROLLER

MII

MII

BUFFER CONTROL UNIT

PORT 3

PORT LATCH

PORT LATCH

SRAM

9kk x 8

B

ACCUMULATOR

DATA BUS

PORT 1

ONE’S COMP.

PSW

SERIAL

PORT 0

PORT 1

TIMER 2

PORT 7

PORT LATCH

STACK

MATH

ADDER

ACCELERATOR

POINTER

256 x 8

SFRs/ SRAM

ROM

BOOT

TIMED

ACCESS

LOGIC

INTERRUPT

64k x 8

ADDRESS BUS

PORT LATCH

SERIAL

PORT 2

PORT 2

P2.0–P2.7 P7.0–P7.7

SERIAL

PORT 0

TIMER 0

TIMER 1

CAN

SRAM

TIMER 3

PORT LATCH

PORT 5

P5.0–P5.7

256 x 8

DPTR0

DPTR1

DPTR2

DPTR3

CAN 0

COUNTER

PROGRAM

CONTROLLER

(1)

CC1

V

POWER

CC

V

(4)

CC3

V

OSCILLATOR-

FAIL DETECT

RESET

MONITOR

(4)

SS

V

CONTROL

RST

RSTOL

WATCHDOG

REGISTER

INTRUCTION

MEMORY

CONTROL

CLOCK AND

E

MU

ALE

PSEN

OSCILLATOR

XTAL1

XTAL2

PORT 6

PORT LATCH

PORT 4

PORT LATCH

P6.0–P6.7

P4.0– 4.7

28 of 96

Page 29

PIN DESCRIPTION

PIN NAME FUNCTION

70 V

12, 36, 62,

87

13, 39, 63,

88

CC1

V

CC3

V

SS

68 ALE

67

69

40

PSEN

EA

MUX

97 RST

98

RSTOL

37 XTAL2

38 XTAL1

86 AD0/D0

85 AD1/D1

84 AD2/D2

83 AD3/D3

82 AD4/D4

81 AD5/D5

80 AD6/D6

79 AD7/D7

89 P1.0

90 P1.1

91 P1.2

92 P1.3

93 P1.4

94 P1.5

95 P1.6

96 P1.7

66

A8

65 A9

64 A10

61 A11

60 A12

+1.8V Core Supply Voltage

+3.3V I/O Supply Voltage

Digital Circuit Ground

Address Latch Enable, Output. When the MUX pin is low, this pin outputs a clock to latch the external address

LSB from the multiplexed address/data bus on Port 0. This signal is commonly connected to the latch enable of

an external transparent latch. ALE has a pulse width of 1.5 XTAL1 cycles and a period of four XTAL1 cycles.

When the MUX pin is high, the pin toggles continuously if the ALEOFF bit is cleared. ALE is forced high when

the device is in a reset condition or if the ALEOFF bit is set while the MUX pin is high.

Program Store Enable, Output. This signal is the chip enable for external program or merged program/data

memory. PSEN provides an active-low pulse and is driven high when external memory is not being accessed.

External Access Enable, Input. Connect to GND to use external program memory. Connect to V

internal ROM.

Multiplex/Demultiplex Select, Input. This pin selects if the address/data bus operates in multiplexed (MUX =

0) or demultiplexed (MUX = 1) mode. The MUX pin is sampled only on a power-on reset.

Reset, Input. The RST input pin contains a Schmitt voltage input to recognize external active-high reset inputs.

The pin also employs an internal pulldown resistor to allow for a combination of wired-OR external-reset

sources. An RC circuit is not required for power-up, as the device provides this function internally.

Reset Output Low, Output. This active-low signal is asserted when the microcontroller has entered reset

through the RST pin; during crystal warm-up period following power-on or stop mode; during a watchdog timer

reset; during an oscillator failure (if OFDE = 1); whenever V

DS80C400 to an external PHY, do not connect the RSTOL to the reset of the PHY. Doing so may disable the

Ethernet transmit.

XTAL1, XTAL2. Crystal oscillator pins support fundamental mode, parallel resonant, AT cut crystals. XTAL1 is

the input if an external clock source is used in place of a crystal. XTAL2 is the output of the crystal amplifier.

AD0–7 (Port 0), I/O. When the MUX pin is connected low, Port 0 is the multiplexed address/data bus. While

ALE is high, the LSB of a memory address is presented. While ALE falls, the port transitions to a bidirectional

data bus. When the MUX pin is connected high, Port 0 functions as the bidirectional data bus. Port 0 cannot be

modified by software. The reset condition of Port 0 pins is high. No pullup resistors are needed.

Port Alternate Function

P0.0 AD0/D0 (Address)/Data 0

P0.1 AD1/D1 (Address)/Data 1

P0.2 AD2/D2 (Address)/Data 2

P0.3 AD3/D3 (Address)/Data 3

P0.4 AD4/D4 (Address)/Data 4

P0.5 AD5/D5 (Address)/Data 5

P0.6 AD6/D6 (Address)/Data 6

P0.7 AD7/D7 (Address)/Data 7

Port 1, I/O. Port 1 can function as either an 8-bit, bidirectional I/O port or as an alternate interface for internal

resources. The reset condition of Port 1 is all bits at logic 1 through a weak pullup. The logic 1 state also serves

as an input mode, since external circuits writing to the port can override the weak pullup. When software clears

any port pin to 0, a strong pulldown is activated that remains on until either a 1 is written to the port pin or a

reset occurs. Writing a 1 after the port has been at 0 activates a strong transition driver, followed by a weaker

sustaining pullup. Once the momentary strong driver turns off, the port once again becomes the output (and

input) high state.

Port Alternate Function

P1.0 T2 External I/O for Timer/Counter 2

P1.1 T2EX Timer/Counter 2 Capture/Reload Trigger

P1.2 RXD1 Serial Port 1 Receive

P1.3 TXD1 Serial Port 1 Transmit

P1.4 INT2 External Interrupt 2 (Positive Edge Detect)

P1.5 INT3 External Interrupt 3 (Negative Edge Detect)

P1.6 INT4 External Interrupt 4 (Positive Edge Detect)

P1.7 INT5 External Interrupt 5 (Negative Edge Detect)

A15–A8 (Port 2), Output. Port 2 serves as the MSB for external addressing. The port automatically asserts the

address MSB during external ROM and RAM access. Although the Port 2 SFR exists, the SFR value never

appears on the pins (due to memory access). Therefore, accessing the Port 2 SFR is only useful for MOVX A,

@Ri or MOVX @Ri, A instructions, which use the Port 2 SFR as the external address MSB.

Port Alternate Function

P2.0 A8 Program/Data Memory Address 8

P2.1 A9 Program/Data Memory Address 9

CC1

DS80C400 Network Microcontroller

CC

£ V

or V

£ V

RST1

CC3

. When connecting the

RST3

to use

29 of 96

Page 30

PIN NAME FUNCTION

59 A13

58 A14

57 A15

20 P3.0

21 P3.1

22 P3.2

23 P3.3

24 P3.4

25 P3.5

26 P3.6

27 P3.7

48 P4.0

47 P4.1

46 P4.2

45 P4.3

44 P4.4

43 P4.5

42 P4.6

41 P4.7

35 P5.0

34 P5.1

33 P5.2

32 P5.3

31 P5.4

30 P5.5

29 P5.6

28 P5.7

56 P6.0

55 P6.1

54 P6.2

53 P6.3

52 P6.4

P2.2 A10 Program/Data Memory Address 10

P2.3 A11 Program/Data Memory Address 11

P2.4 A12 Program/Data Memory Address 12

P2.5 A13 Program/Data Memory Address 13

P2.6 A14 Program/Data Memory Address 14

P2.7 A15 Program/Data Memory Address 15

Port 3, I/O. Port 3 functions as an 8-bit, bidirectional I/O port, and as an alternate interface for several resources

found on the traditional 8051. The reset condition of Port 3 is all bits at logic 1 through a weak pullup. The logic

1 state also serves as an input mode, since external circuits writing to the port can override the weak pullup.

When software clears any port pin to 0, the device activates a strong pulldown that remains on until either a 1 is

written to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong transition

driver, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again

becomes the output (and input) high state.

Port Alternate Function

P3.0 RXD0 Serial Port 0 Receive

P3.1 TXD0 Serial Port 0 Transmit

P3.2 INT0 External Interrupt 0

P3.3 INT1 External Interrupt 1

P3.4 T0 Timer 0 External Input

P3.5 T1/CLKO Timer 1 External Input/External Clock Output

P3.6 WR External Data Memory Write Strobe

P3.7 RD External Data Memory Read Strobe

Port 4, I/O. Port 4 can function as an 8-bit, bidirectional I/O port, and as the source for external address and

chip-enable signals for program and data memory. Port pins are configured as I/O or memory signals through

the P4CNT register. The reset condition of Port 4 is all bits at logic 1 through a weak pullup. The logic 1 state

also serves as an input mode, since external circuits writing to the port can override the weak pullup. When

software clears any port pin to 0, the device activates a strong pulldown that remains on until either a 1 is written

to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong transition driver,

followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again

becomes the output (and input) high state.

Port Alternate Function

P4.0 CE0 Program Memory Chip Enable 0

P4.1 CE1 Program Memory Chip Enable 1

P4.2 CE2 Program Memory Chip Enable 2

P4.3 CE3 Program Memory Chip Enable 3

P4.4 A16 Program/Data Memory Address 16

P4.5 A17 Program/Data Memory Address 17

P4.6 A18 Program/Data Memory Address 18

P4.7 A19 Program/Data Memory Address 19

Port 5, I/O. Port 5 can function as an 8-bit, bidirectional I/O port, the CAN interface, Timer 3 input, and/or as

peripheral-enable signals. The reset condition of Port 5 is all bits at logic 1 through a weak pullup. The logic 1

state also serves as an input mode, since external circuits writing to the port can override the weak pullup.

When software clears any port pin to 0, the device activates a strong pulldown that remains on until either a 1 is

written to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong transition

driver, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again

becomes the output (and input) high state.

Port Alternate Function

P5.0 C0TX CAN0 Transmit Output

P5.1 C0RX CAN0 Receive Input

P5.2 T3 Timer 3 External Input

P5.3 None

P5.4 PCE0 Peripheral Chip Enable 0

P5.5 PCE1 Peripheral Chip Enable 1

P5.6 PCE2 Peripheral Chip Enable 2

P5.7 PCE3 Peripheral Chip Enable 3

Port 6, I/O. Port 6 can function as an 8-bit, bidirectional I/O port, as program and data memory address/chipenable signals, and/or a third serial port. The reset condition of Port 6 is all bits at logic 1 through a weak pullup.

The logic 1 state also serves as an input mode, since external circuits writing to the port can override the weak

pullup. When software clears any port pin to 0, the device activates a strong pulldown that remains on until

either a 1 is written to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong

transition driver, followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port

once again becomes the output (and input) high state.

Port Alternate Function

P6.0 CE4 Program Memory Chip Enable 4

DS80C400 Network Microcontroller

30 of 96

Page 31

g

PIN NAME FUNCTION

51 P6.5

50 P6.6

49 P6.7

78 A0

77 A1

76 A2

75 A3

74 A4

73 A5

72 A6

71 A7

8 TXClk

7 TX_EN

3 TXD.3

4 TXD.2

5 TXD.1

6 TXD.0

10 RXClk

11 RX_DV

9 RX_ER

17 RXD.3

16 RXD.2

15 RXD.1

14 RXD.0

1 CRS

2 COL

18 MDC

P6.1 CE5 Program Memory Chip Enable 5

P6.2 CE6 Program Memory Chip Enable 6

P6.3 CE7 Program Memory Chip Enable 7

P6.4 A20 Program/Data Memory Address 20

P6.5 A21 Program/Data Memory Address 21

P6.6 RXD2 Serial Port 2 Receive

P6.7 TXD2 Serial Port 2 Transmit

Port 7, I/O. Port 7 can function as either an 8-bit, bidirectional I/O port or the nonmultiplexed A0–A7 signals

(when the MUX pin = 1). The reset condition of Port 7 is all bits at logic 1 through a weak pullup. The logic 1

state also serves as an input mode, since external circuits writing to the port can override the weak pullup.

When software clears any port pin to 0, a strong pulldown is activated that remains on until either a 1 is written

to the port pin or a reset occurs. Writing a 1 after the port has been at 0 activates a strong transition driver,

followed by a weaker sustaining pullup. Once the momentary strong driver turns off, the port once again

becomes the output (and input) high state.

Port Alternate Function

P7.0 A0 Program/Data Memory Address 0

P7.1 A1 Program/Data Memory Address 1

P7.2 A2 Program/Data Memory Address 2

P7.3 A3 Program/Data Memory Address 3

P7.4 A4 Program/Data Memory Address 4

P7.5 A5 Program/Data Memory Address 5

P7.6 A6 Program/Data Memory Address 6

P7.7 A7 Program/Data Memory Address 7

Transmit Clock, Input. The transmit clock is a continuous clock sourced from the Ethernet PHY controller. It is

used to provide timing reference for transferring of TX_EN and TXD[3:0] signals from the MAC to the external

Ethernet PHY controller. The input clock frequency of TXClk should be 25MHz for 100Mbps operation and

2.5MHz for 10Mbps operation. For ENDEC operation, TXClk serves the same function, but the input clock

frequency should be 10MHz.

Transmit Enable, Output. The transmit enable is an active-high output and is synchronous with respect to the

TXClk signal. TX_EN is used to indicate valid nibbles of data for transmission on the MII pins TXD.3–TXD.0.

TX_EN is asserted with the first nibble of the preamble and remains asserted while all nibbles to be transmitted

are presented on the TXD.3–TXD.0 pins. TX_EN negates prior to the first TXClk following the final nibble of the

frame. TX_EN serves the same function for ENDEC operation.

Transmit Data, Output. The transmit data outputs provide 4-bit nibbles of data for transmission over the MII.

The transmit data is synchronous with respect to the TXClk signal. For each TXClk period when TX_EN is

asserted, TXD.3–TXD.0 provides the data for transmission to the Ethernet PHY controller. When TX_EN is

deasserted, the TXD data should be ignored. For ENDEC operation, only TXD.0 is used for transmission of

frames.

Receive Clock, Input. The receive clock is a continuous clock sourced from the Ethernet PHY controller. It is

used to provide timing reference for transferring of RX_DV, RX_ER, and RXD[3:0] signals from the external

Ethernet PHY controller to the MAC. The input clock frequency of RXClk should be 25MHz for 100Mbps

operation and 2.5MHz for 10Mbps operation. For ENDEC operation, RXClk serves the same function, but the

input clock frequency should be 10MHz.

Receive Data Valid, Input. The receive data valid is an active-high input from the external Ethernet PHY

controller and is synchronous with respect to the RXClk signal. RX_DV is used to indicate valid nibbles of data

for reception on the MII pins RXD.3–RXD.0. RX_DV is asserted continuously from the first nibble of the frame

through the final nibble. RX_DV negates prior to the first RXClk following the final nibble. RX_DV serves the

same function for ENDEC operation.

Receive Error, Input. The receive error is an active-high input from the external Ethernet PHY controller and is

synchronous with respect to the RXClk signal. RX_ER is used to indicate to the MAC that an error (e.g., a

coding error, or any error detectable by the PHY) was detected somewhere in the frame presently being

transmitted by the PHY. RX_ER has no effect on the MAC while RX_DV is deasserted. RX_ER should be low

for ENDEC operation.

Receive Data, Input. The receive data inputs provide 4-bit nibbles of data for reception over the MII. The

receive data is synchronous with respect to the RXClk signal. For each RXClk period when RX_DV is asserted,

RXD.3–RXD.0 have the data to be received by the MAC. When RX_DV is deasserted, the RXD data should be

ignored. For ENDEC operation, only RXD.0 is used for reception of frames.

Carrier Sense, Input. The carrier sense signal is an active-high input and should be asserted by the external

Ethernet PHY controller when either the transmit or receive medium is not idle. CRS should be deasserted by

the PHY when the transmit and receive mediums are idle. The PHY should ensure that the CRS signal remains

asserted throughout the duration of a collision condition. The transitions on the CRS signal need not be

synchronous to TXClk or RXClk. CRS serves the same function for ENDEC operation.

Collision Detect, Input. The collision detect signal is an active-high input and should be asserted by the

external Ethernet PHY controller upon detection of a collision on the medium. The PHY should ensure that COL

remains asserted while the collision condition persists. The transitions on the COL signal need not be

synchronous to TXClk or RXClk. The COL signal is ignored by the MAC when operating in full-duplex mode.

COL serves the same function for ENDEC operation.

MII Management Clock, Output. The MII management clock is generated by the MAC for use by the external

Ethernet PHY controller as a timin

referenced for transferring information on the MDIO pin. MDC is a periodic

31 of 96

DS80C400 Network Microcontroller

Page 32

DS80C400 Network Microcontroller

PIN NAME FUNCTION

signal that has no maximum high or low times. The minimum high and low times are 160ns each. The minimum

period for MDC is 400ns independent of the period of TXClk and RXClk.

MII Management Input/Output. The MII management I/O is the data pin for serial communication with the

19 MDIO

99 OW

100

OWSTP

external Ethernet PHY controller. In a read cycle, data is driven by the PHY to the MAC synchronously with

respect to the MDC clock. In a write cycle, data from the MAC is output to the external PHY synchronously with

respect to the MDC clock.

1-Wire Data, I/O. The 1-Wire data pin is an open-drain, bidirectional data bus for the 1-Wire Bus Master.

External 1-Wire slave devices are connected to this pin. This pin must be pulled high by an external resistor,

normally 2.2kW.

Strong Pullup Enable, Output. This 1-Wire pin is an open-drain active-low output used to enable an external

strong pullup for the 1-Wire bus. This pin must be pulled high by an external resistor, normally 10kW. This

functionality helps recovery times when the 1-Wire bus is operated in overdrive and long-line standard

communication modes. It can optionally be enabled while the bus master is in the idle state for slave devices

requiring sustained high-current operation.

FEATURES (continued)

§ Advanced Power Management

Energy Saving 1.8V Core

3.3V I/O Operation, 5V Tolerant

Power-Management, Idle, and Stop Mode

Operations with Switchback Feature

Ethernet and CAN Shutdown Control for Power

Conservation

Early Warning Power-Fail Interrupt

Power-Fail Reset

§ Enhanced Memory Architecture

Selectable 8/10-Bit Stack Pointer for High-Level

Language Support

1kB Additional On-Chip SRAM Usable as

Stack/Data Memory

16-Bit/24-Bit Paged/24-Bit Contiguous Modes

Selectable Multiplexed/Nonmultiplexed External

Memory Interface

Merged Program/Data Memory Space Allows In-

System Programming

Defaults to True 8051-Memory Compatibility

DETAILED DESCRIPTION

The DS80C400 network microcontroller offers the highest integration available in an 8051 device. Peripherals

include a 10/100 Ethernet MAC, three serial ports, a CAN 2.0B controller, 1-Wire Master, and 64 I/O pins. To

enable access to the network, a full application-accessible TCP IPv4/6 network stack and OS are provided in ROM.

The network stack supports up to 32 simultaneous TCP connections and can transfer up to 5Mbps through the

Ethernet MAC. Its maximum system-clock frequency of 75MHz results in a minimum instruction cycle time of 54ns.

Access to large program or data memory areas is simplified with a 24-bit addressing scheme that supports up to

16MB of contiguous memory. To accelerate data transfers between the microcontroller and memory, the

DS80C400 provides four data pointers, each of which can be configured to automatically increment or decrement

upon execution of certain data pointer-related instructions. The DS80C400’s hardware math accelerator further

increases the speed of 32-bit and 16-bit multiply and divide operations as well as high-speed shift, normalization,

and accumulate functions.

With extensive networking and I/O capabilities, the DS80C400 is equipped to serve as a central controller in a

multitiered network. The 10/100 Ethernet media access controller (MAC) enables the DS80C400 to access and

communicate over the Internet. While maintaining a presence on the Internet, the microcontroller can actively

control lower tier networks with dedicated on-chip hardware. These hardware resources include a full CAN 2.0B

controller, a 1-Wire net controller, three full-duplex serial ports, and eight 8-bit ports (up to 64 digital I/O pins).

Instant connectivity and networking support are provided through an embedded 64kB ROM. This ROM contains

firmware to perform a network boot over an Ethernet connection using DHCP in conjunction with TFTP. The ROM

firmware realizes a full, application-accessible TCP/IP stack, supporting both IPv4 and IPv6, and implements UDP,

TCP, DHCP, ICMP, and IGMP. In addition, a priority-based, preemptive task scheduler is also included. The

firmware has been structured so that a MAC address can optionally be acquired from an IEEE-registered DS2502E48.

The 10/100 Ethernet MAC featured on the DS80C400 complies with both the IEEE 802.3 MII and ENDEC PHY

interface standards. The MII interface supports 10/100Mbps bus operation, while the ENDEC interface supports

10Mbps operation. The MAC has been designed for low-power standard operation and can optionally be placed

into an ultra-low-power sleep mode, to be awakened manually or by detection of a Magic Packet or wake-up frame.

Incorporating a buffer control unit reduces the burden of Ethernet traffic on the CPU. This unit, after initial

32 of 96

Page 33

DS80C400 Network Microcontroller

configuration through an SFR interface, manages all Tx/Rx packet activity and status reporting through an on-chip

8kB SRAM. To further reduce host (DS80C400) software intervention, the MAC can be set up to generate a

hardware interrupt following each transmit or receive status report. The DS80C400 MAC can be operated in halfduplex or full-duplex mode with flow control, and provides multicast/broadcast-address filtering modes as well as

VLAN tag-recognition capability.

The DS80C400 features a full-function CAN 2.0B controller. This controller provides 15 total message centers, 14

of which can be configured as either transmit or receive buffers and one that can serve as a receive double buffer.

The device supports standard 11-bit or 29-extended message identifiers, and offers two separate 8-bit media

masks and media arbitration fields to support the use of higher-level CAN protocols such as DeviceNet and SDS. A

special auto-baud mode allows the CAN controller to quickly determine required bus timing when inserted into a

new network. A SIESTA sleep mode has been made available for times when the CAN controller can be placed

into a power-saving mode.

The DS80C400 has resources that far exceed those normally provided on a standard 8-bit microcontroller. Many

functions, which might exist as peripheral circuits to a microcontroller, have been integrated into the DS80C400.

Some of the integrated functions of the DS80C400 include 16 interrupt sources (six external), four timer/counters, a

programmable watchdog timer, a programmable IrDA output clock, an oscillator-fail detection circuit, and an

internal 2X/4X clock multiplier. This frequency multiplier allows the microcontroller to operate at full speed with a

reduced crystal frequency, reducing EMI.

Advanced power-management support positions the DS80C400 for portable and power-conscious applications.

The low-voltage microcontroller core runs from a 1.8V supply while the I/O remains 5V tolerant, operating from a

3.3V supply. A power-management mode (PMM) allows software to switch from the standard machine cycle rate of

4 clocks per cycle to 1024 clocks per cycle. For example, 40MHz standard operation has a machine cycle rate of

10MHz. In PMM, at the same external clock speed, software can select a 39kHz machine cycle rate, considerably

reducing power consumption. The microcontroller can be configured to automatically switch back from PMM to the

faster mode in response to external interrupts or serial port activity. The DS80C400 provides the ability to place the

CPU into an idle state or an ultra-low-power stop-mode state. As protection against brownout and power-fail

conditions, the microcontroller is capable of issuing an early warning power-fail interrupt and can generate a powerfail reset.

Defaulting to true 8051-memory compatibility, the microcontroller is most powerful when taking advantage of its

enhanced memory architecture. The DS80C400 has a selectable 10-bit stack pointer that can address up to 1kB of

on-chip SRAM stack space for increased code efficiency. It can be operated in a 24-bit paged or 24-bit contiguous

address mode, giving access to a much larger address range than the standard 16-bit address mode. Support for

merged program and data memory access allows in-system programming, and it can be configured to internally

demultiplex data and the lowest address byte, thereby eliminating the need for an external latch and potentially

allowing the use of slower memory devices.

80C32 COMPATIBILITY

The DS80C400 is a CMOS 80C32-compatible microcontroller designed for high performance. Every effort has

been made to keep the core device familiar to 80C32 users while adding many enhanced features. The DS80C400

provides the same timer/counter resources, full duplex serial port, 256 Bytes of scratchpad RAM, and I/O ports as

the standard 80C32. Timers default to 12 oscillator clocks per tick operation to keep timing compatible with original

8051 systems. New hardware functions are accessed using special function registers (SFRs) that do not overlap

with standard 80C32 locations. All instructions perform exactly the same functions as their 8051 counterparts. Their

effect on bits, flags, and other status functions is identical. Because the device runs the standard 8051 instruction

set, in general, software written for existing 80C32-based systems work on the DS80C400. The primary exceptions

are related to timing-critical issues, since the high-performance core of the microcontroller executes instructions

much faster than the original, both in absolute and relative number of clocks.

The relative time of two DS80C400 instructions might differ from the traditional 8051. For example, in the original

architecture the “MOVX A, @DPTR” instruction and the “MOV direct, direct” instruction required the same amount

of time: two machine cycles or 24 oscillator cycles. In its default configuration (machine cycle = 4 oscillator cycles),

the DS80C400 executes the “MOVX A, @DPTR” instruction in as little as two machine cycles or 8 oscillator cycles,

but the “MOV direct, direct” uses three machine cycles or 12 oscillator cycles. While both are faster than their

original counterparts, they now have different execution times. Examine the timing of each instruction for familiarity

33 of 96

Page 34

DS80C400 Network Microcontroller

with the changes. Note that a machine cycle now requires just 4 clocks, and provides one ALE pulse per cycle.

Most instructions require only one or two cycles, but some require as many as four or five. Refer to the High-Speed

Microcontroller User’s Guide and High-Speed Microcontroller User’s Guide: DS80C400 Supplement for individual

instruction-timing details and for calculating the absolute timing of software loops. Also remember that the

counter/timers default to run at the traditional 12 clocks per increment. This means that timer-based events still

occur at the standard intervals, but that code now executes at a higher speed relative to the timers. Timers

optionally can be configured to run at the faster 4 clocks per increment to take advantage of faster controller

operation.

Memory interfacing can be performed identically to the standard 80C32. The high-speed nature of the DS80C400

core slightly changes the interface timing, and designers are advised to consult the timing diagrams in this data

sheet for more information.

This data sheet provides only a summary and overview of the DS80C400. Detailed descriptions are available in the

corresponding user’s guide. This data sheet assumes a familiarity with the architecture of the standard 80C32. In

addition to the basic features of that device, the DS80C400 incorporates many new features.

PERFORMANCE OVERVIEW

The DS80C400’s higher performance comes not just from increasing the clock frequency but from a more efficient

design. This updated core removes the dummy memory cycles that are present in a standard, 12 clock-permachine cycle 8051. In the DS80C400, a machine cycle requires only 4 clocks. Thus the fastest instruction, 1

machine cycle in duration, executes three times faster for the same crystal frequency. The majority of instructions

on the DS80C400 experience a 3-to-1 speed improvement, while a few execute between 1.5 and 2.4 times faster.

One instruction, INC DPTR, actually executes in fewer machine cycles (1 machine cycle vs. 2 machine cycles

originally required), thus it sees a 6X throughput improvement over the original 8051. Regardless of specific

performance improvements, all instructions are faster than the original 8051.

Improvement of individual programs depend on the actual mix of instructions used. Speed-sensitive applications

should make the most use of instructions that are at least three times faster. However, given the large number of 3to-1 improved op codes, dramatic speed improvements are likely for any arbitrary combination of instructions. The

core architectural improvements and the submicron-CMOS design result in a peak instruction cycle of 54ns (18.75

million instructions per second, i.e., MIPS). To further increase performance, auto-increment/decrement and autotoggle enhancements have been implemented for the quad data pointer to allow the user to eliminate wasted

instructions when moving blocks of memory.

SPECIAL FUNCTION REGISTERS (SFRS)

SFRs control most special features of the microcontroller. They allow the device to have many new features but

use the standard 8051 instruction set. When writing software to use a new feature, an equate statement defines the

SFR to the assembler or compiler. This is the only change needed to access the new function. The DS80C400

duplicates the SFRs contained in the standard 80C32. Table 1

High-Speed Microcontroller User’s Guide: DS80C400 Supplement contains a full description of all SFRs.

shows the register addresses and bit locations. The

34 of 96

Page 35

DS80C400 Network Microcontroller

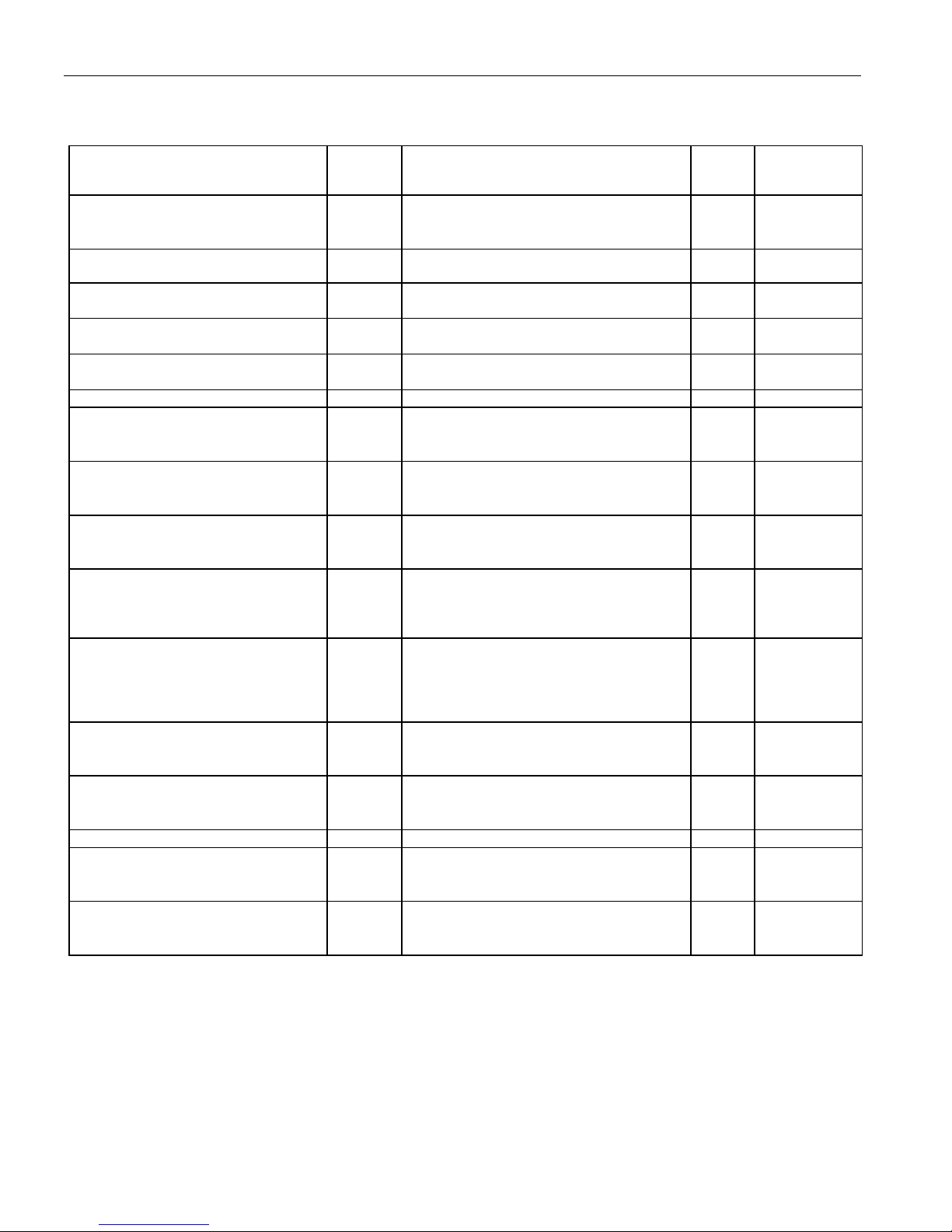

Table 1. SFR Addresses and Bit Locations

REGISTER BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 ADDRESS

P4 P4.7/A19 P4.6/A18 P4.5/A17 P4.4/A16 P4.3/CE3 P4.2/CE2 P4.1/CE1 P4.0/CE0 80h

SP 81h

DPL 82h

DPH 83h

DPL1 84h

DPH1 85h

DPS ID1 ID0 TSL AID SEL1 — — SEL0 86h

PCON SMOD_0 SMOD0 OFDF OFDE GF1 GF0 STOP IDLE 87h

TCON TF1 TR1 TF0 TR0 IE1 IT1 IE0 IT0 88h

TMOD GATE

TL0 8Ah

TL1 8Bh

TH0 8Ch

TH1 8Dh

CKCON WD1 WD0 T2M T1M T0M MD2 MD1 MD0 8Eh

P1 P1.7/INT5 P1.6/INT4 P1.5/INT3 P1.4/INT2 P1.3/TXD P1.2/RXD1 P1.1/T2EX P1.0/T2 90h

EXIF IE5 IE4 IE3 IE2 CKRY RGMD RGSL BGS 91h

P4CNT — — P4CNT.5 P4CNT.4 P4CNT.3 P4CNT.2 P4CNT.1 P4CNT.0 92h

DPX 93h

DPX1 95h

C0RMS0 96h

C0RMS1 97h

SCON0 SM0/FE_0 SM1_0 SM2_0 REN_0 TB8_0 RB8_0 TI_0 RI_0 98h

SBUF0 99h

ESP — — — — — — ESP.1 ESP.0 9Bh

AP 9Ch

ACON — — MROM BPME BROM SA AM1 AM0 9Dh

C0TMA0 9Eh

C0TMA1 9Fh

P2 P2.7/A15 P2.6/A14 P2.5/A13 P2.4/A12 P2.3/A11 P2.2/A10 P2.1/A9 P2.0/A8 A0h

P5 P5.7/PCE3 P5.6/PCE2 P5.5/PCE1 P5.4/PCE0 P5.3 P5.2/T3 P5.1/C0RX P5.0/C0TX A1h

P5CNT — CAN0BA — — C0_I/O P5CNT.2 P5CNT.1 P5CNT.0 A2h

C0C ERIE STIE PDE SIESTA CRST AUTOB ERCS SWINT A3h

C0S BSS EC96/128 WKS RXS TXS ER2 ER1 ER0 A4h

C0IR INTIN7 INTIN6 INTIN5 INTIN4 INTIN3 INTIN2 INTIN1 INTIN0 A5h

C0TE A6h

C0RE A7h

IE EA ES1 ET2 ES0 ET1 EX1 ET0 EX0 A8h

SADDR0 A9h

SADDR1 AAh

C0M1C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ABh

C0M2C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ACh

C0M3C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP ADh

C0M4C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP AEh

C0M5C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP AFh

P3 P3.7/RD P3.6/WR P3.5/T1 P3.4/T0 P3.3/INT1 P3.2/INT0 P3.1/TXD0 P3.0/RXD0 B0h

P6 P6.7/TXD2 P6.6/RXD2 P6.5/A21 P6.4/A20 P6.3/CE7 P6.2/CE6 P6.1/CE5 P6.0/CE4 B1h

P6CNT — — P6CNT.5 P6CNT.4 P6CNT.3 P6CNT.2 P6CNT.1 P6CNT.0 B2h

C0M6C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B3h

C0M7C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B4h

C0M8C MSRDY ETI ERI INTRQ EXTRQ MTRQ ROW/TIH DTUP B5h

C/T

M1 M0 GATE

C/T

M1 M0 89h

35 of 96

Page 36

DS80C400 Network Microcontroller

REGISTER BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0 ADDRESS