Page 1

www.maxim-ic.com.cn

概述

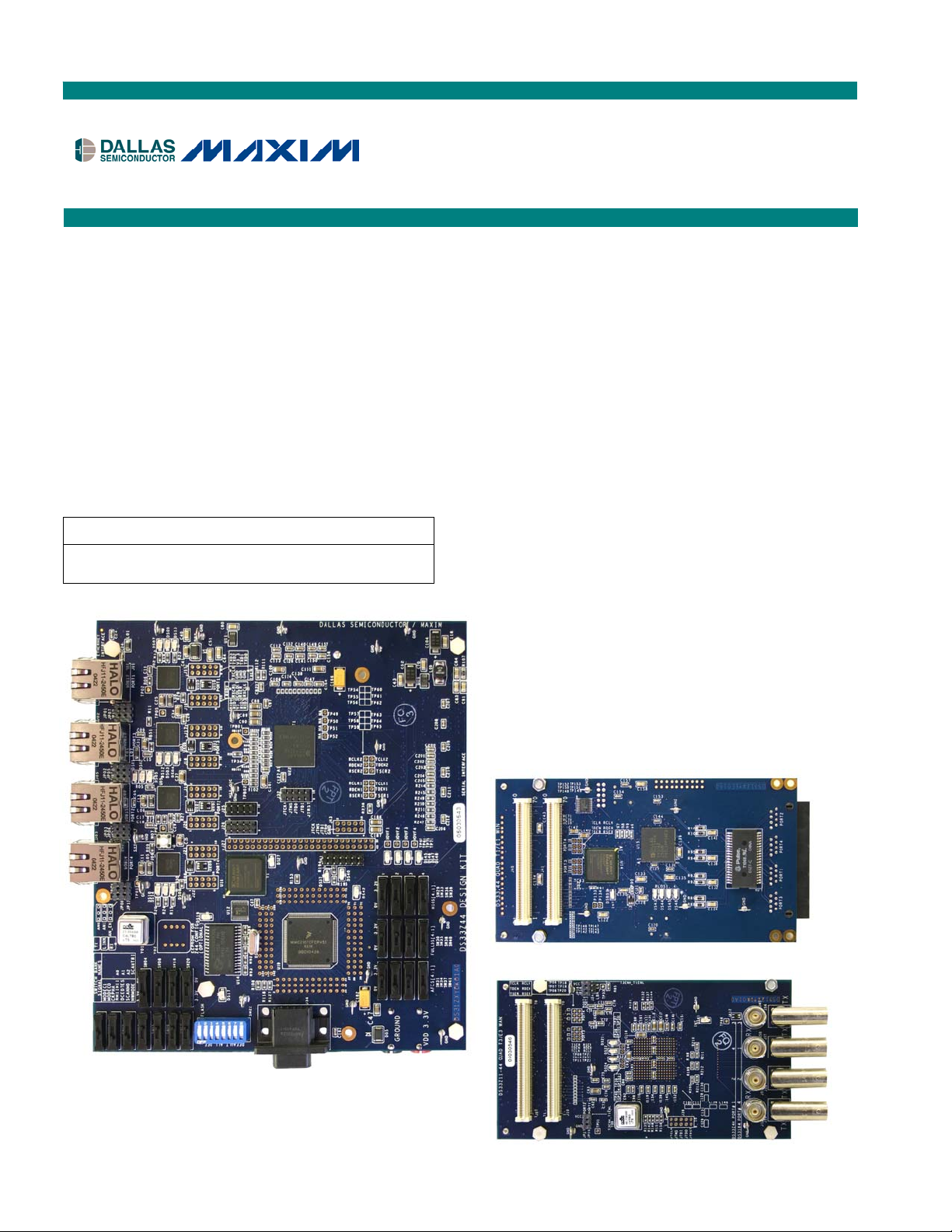

DS33Z44 开发板是使用方便的评估板,用于评估以太

网在串行链路上的传输器件 DS33Z44。DS33Z44DK

的串行链路由子卡提供。串行子卡包括接口、变压器

以及网络接口。Dallas 的 ChipView 软件随开发板一起

提供,可在基于 Windows®的 PC 上访问配置寄存器

和状态寄存器。板载 LED 用于指示接收信号丢失、队

列溢出、以太网链路、Tx/Rx 和中断状态。

Windows是Microsoft Corp.

的注册商标。

定购信息

PART DESCRIPTION

DS33Z44DK

DS33Z44 demo card, T3/E3, T1/E1

transceiver resource card included

DS33Z44DK

以太网传输开发套件

特性

演示 DS33Z44 以太网传输芯片组的主要功能

包括两块子卡:一块 DS21458 T1/E1 SCT 和一块

DS3174 T3/E3 SCT,提供变压器、BNC 和 RJ48

网络连接器以及终端匹配

提供硬件和软件模式支持

板载 MMC2107 处理器和 ChipView 软件允许访

问 DS33Z44 的寄存器组

所有 DS33Z44 接口引脚便于与外部数据源/接收

器连接

LED 指示信号丢失、队列溢出、以太网链路、

Tx/Rx 以及中断状态

丝网印制标记清晰标识与所有连接器、跳线和

LED 相关的信号

开发套件内容

• DS33Z44DK 主板

• 具有 DS21458 T1/E1 SCT 的 4 端口串口卡

• 具有 DS3174 T3/E3 SCT 的 4 端口串口卡

• CD_ROM

o ChipView 软件和手册

o DS33Z44DK 数据资料

o 配置文件

1 of 59 REV: 110106

Page 2

DS33Z44DK

目录表

概述..............................................................................................................................................1

定购信息.......................................................................................................................................1

开发套件内容 ...............................................................................................................................1

元件清单.......................................................................................................................................3

PCB勘误表.................................................................................................................................10

文件位置.....................................................................................................................................10

基本操作.....................................................................................................................................11

开发板供电 ............................................................................................................................................ 11

概要

..................................................................................................................................................................... 11

基本的DS33Z44 初始化(用于所有的快速设置)...................................................................................... 11

快速配置

快速配置

快速配置

#1 (Device Driver + CPLD

#2 (DS3174 T3E3)...............................................................................................................................12

#3 (DS21458 T1E1)............................................................................................................................. 12

环回

)........................................................................................................... 11

配置开关和跳线..........................................................................................................................13

地址映射(所有板卡)....................................................................................................................15

DS33Z44 信息............................................................................................................................15

DS33Z44DK信息 .......................................................................................................................15

技术支持.....................................................................................................................................15

文档版本历史 .............................................................................................................................15

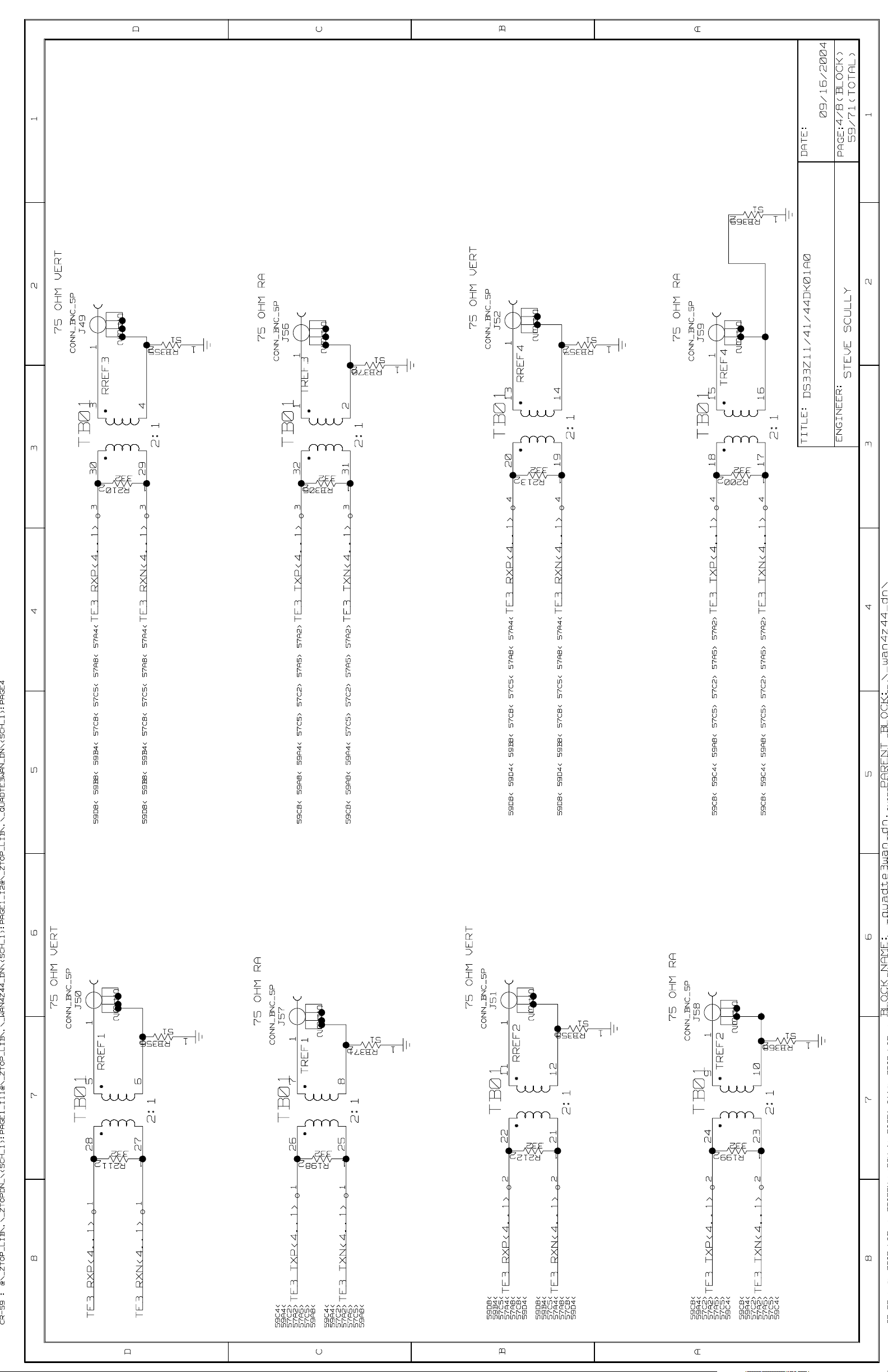

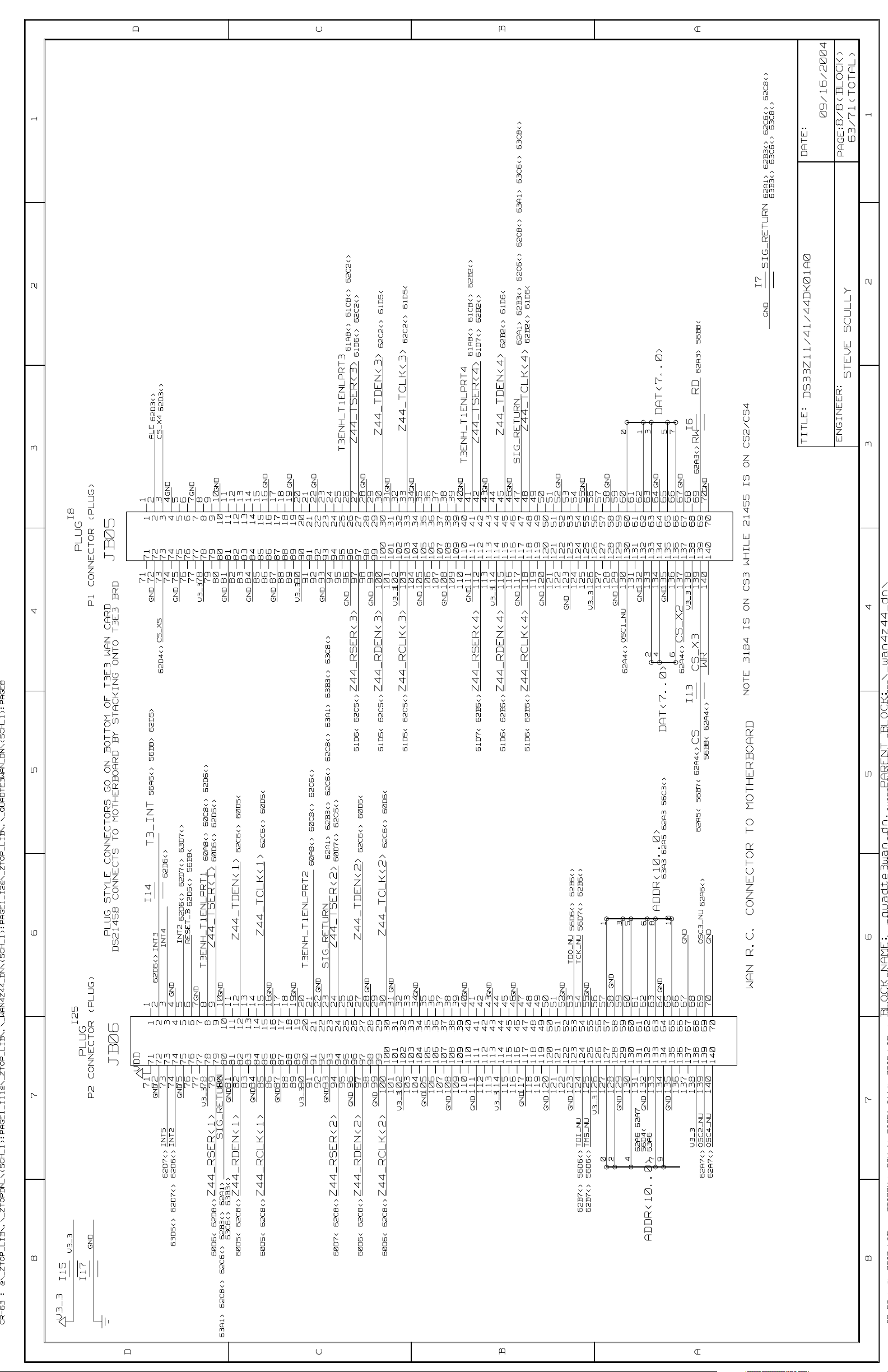

原理图 ........................................................................................................................................16

图片列表

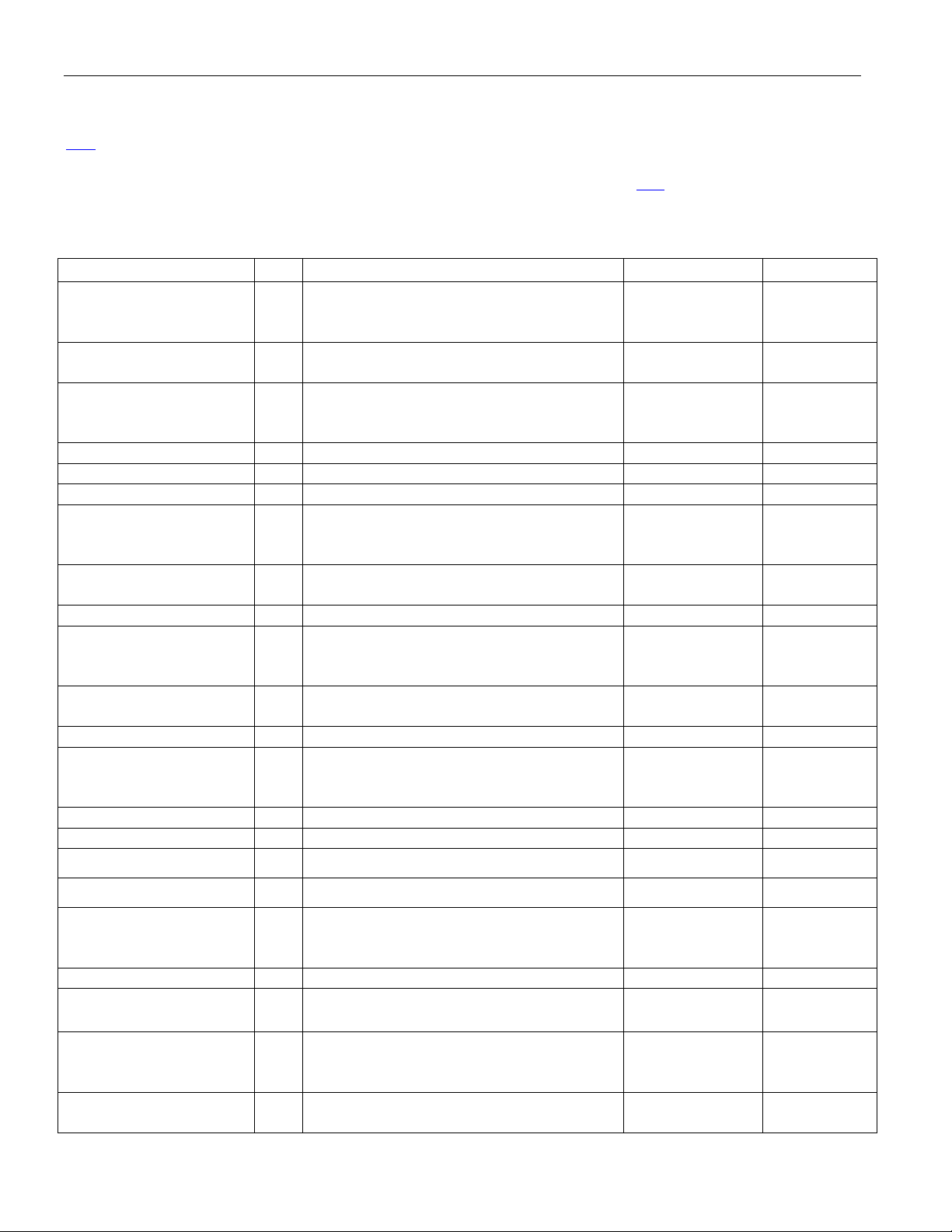

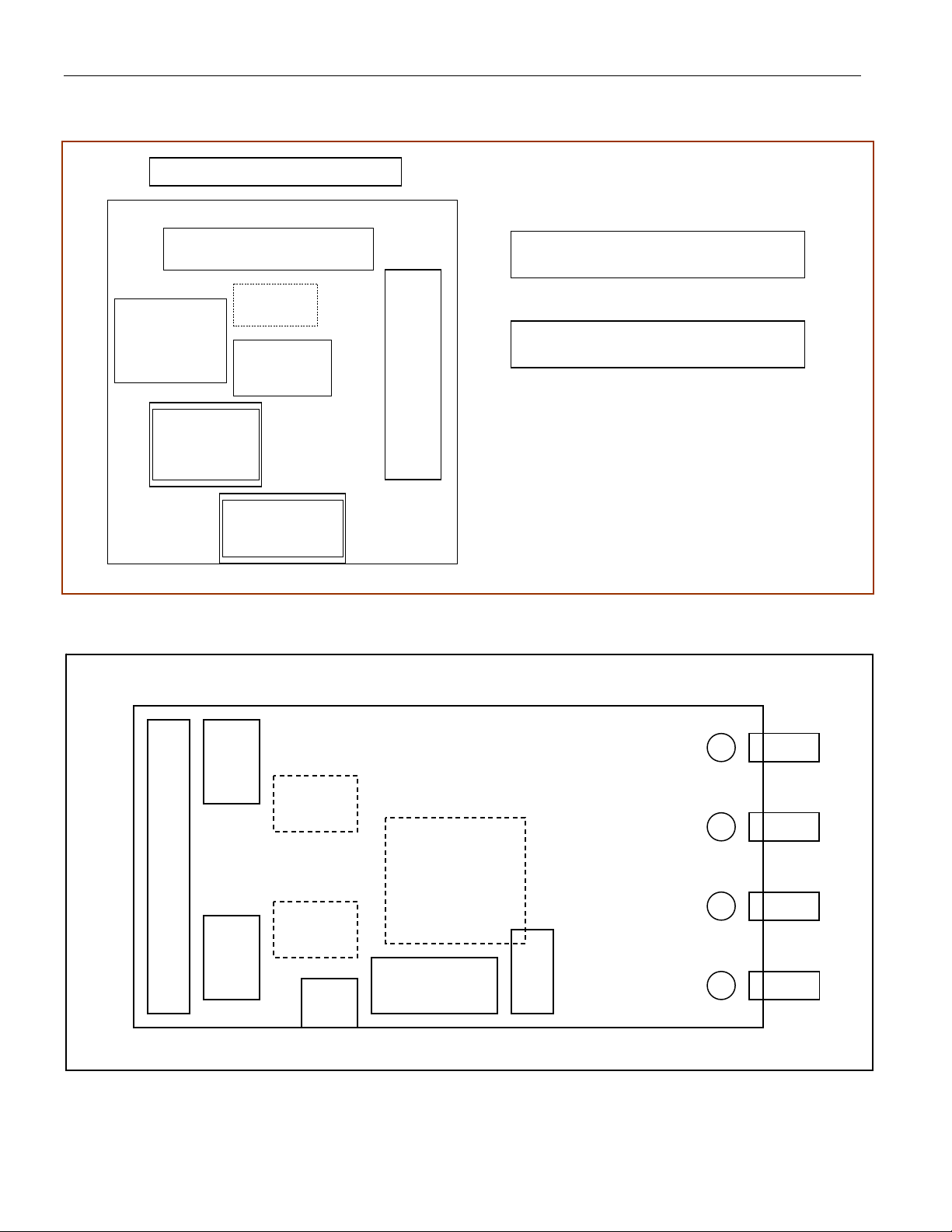

图 1. 系统平面图 .......................................................................................................................................................... 8

图 2. DS3174 子卡平面图............................................................................................................................................. 8

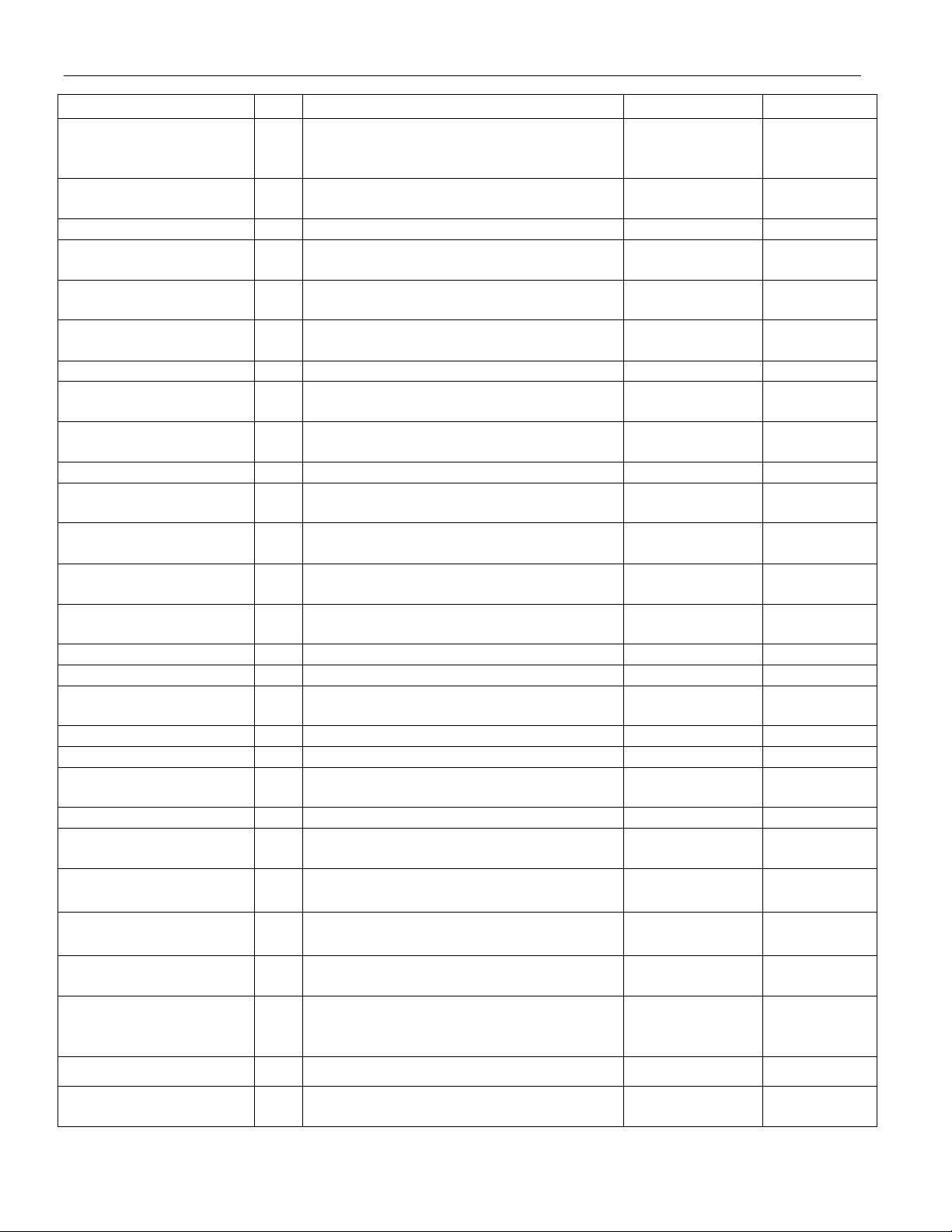

图 3. DS21458 子卡平面图........................................................................................................................................... 9

表格清单

表 1. 元件清单(未显示去耦电容) .................................................................................................................................. 3

表 2. 主板PCB配置..................................................................................................................................................... 13

表 3. DS3174 串行子卡跳线设置................................................................................................................................14

表 4. 卡地址映射概述 ................................................................................................................................................. 15

2 of 59

Page 3

DS33Z44DK

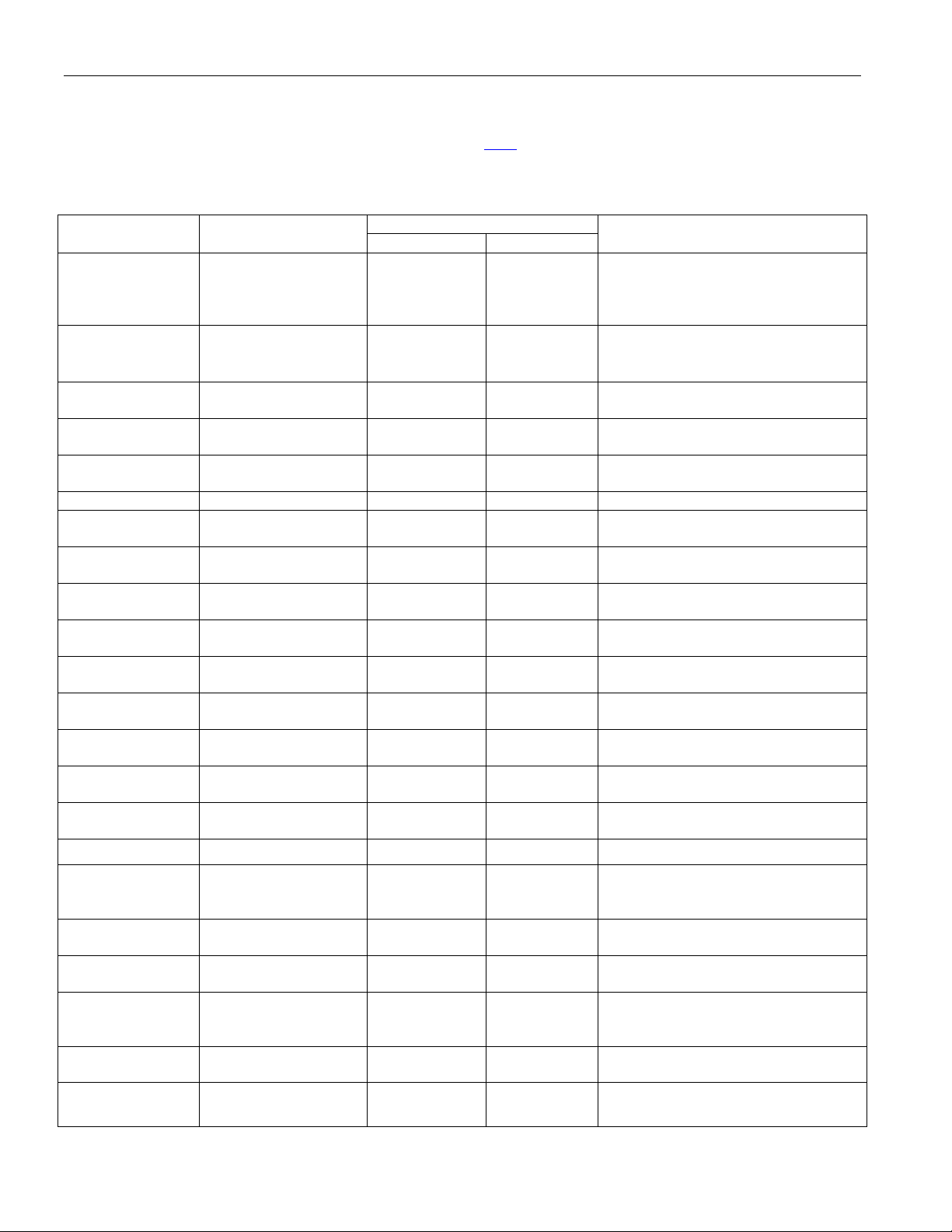

元件清单

表 1给出了DS33Z44 和DS33Z11/DS33Z41 开发板及其子卡的元件清单。其BOM给出了 5 块电路板的元件清单,这

些电路板是DS33Z11DK、DS33Z44DK、DS21458RC、DS3174RC和DS2155-DS21348-DS3170RC。各器件标号

仅使用一次。例如,U18 仅出现在DS33Z11DK上,而不再用于其他电路板。请参考

表 2。

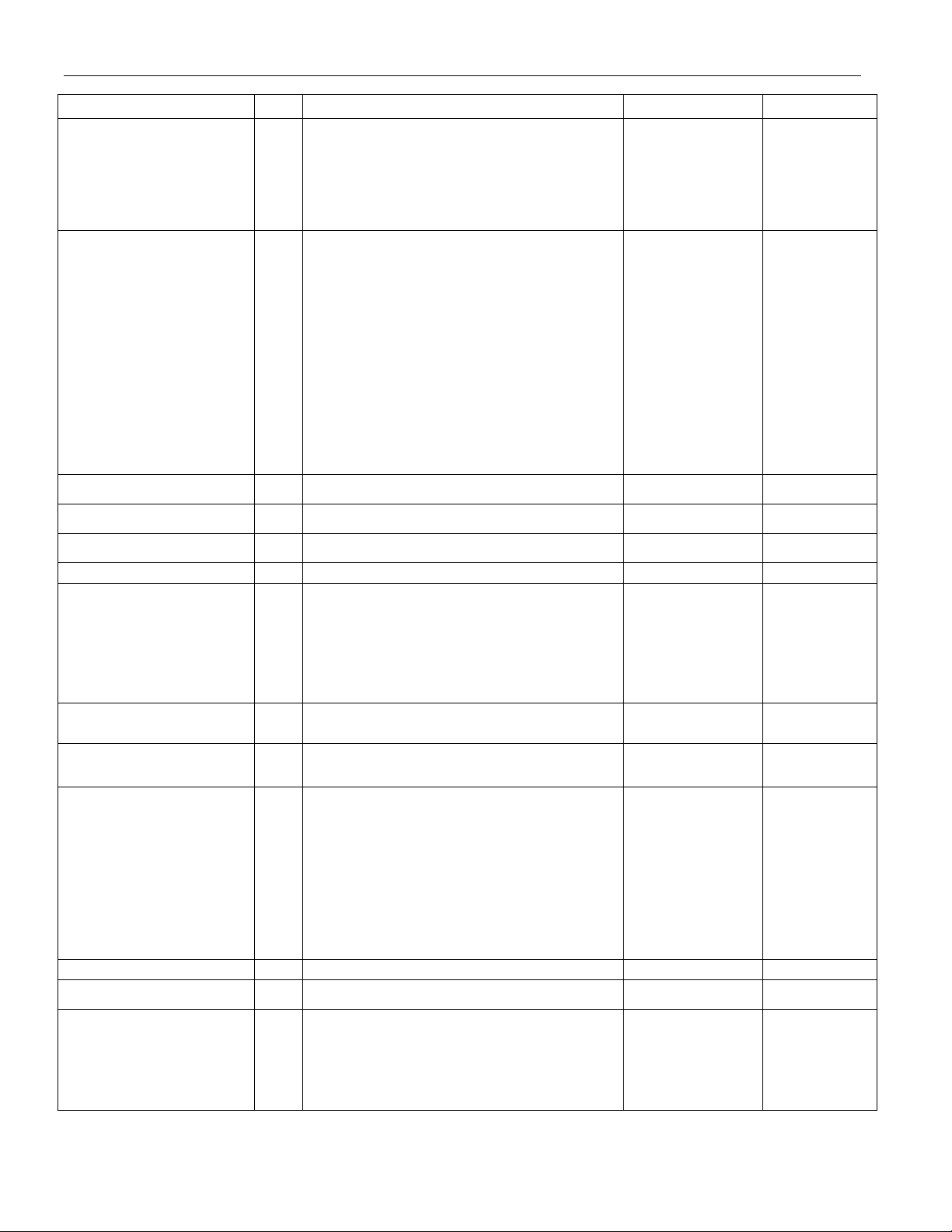

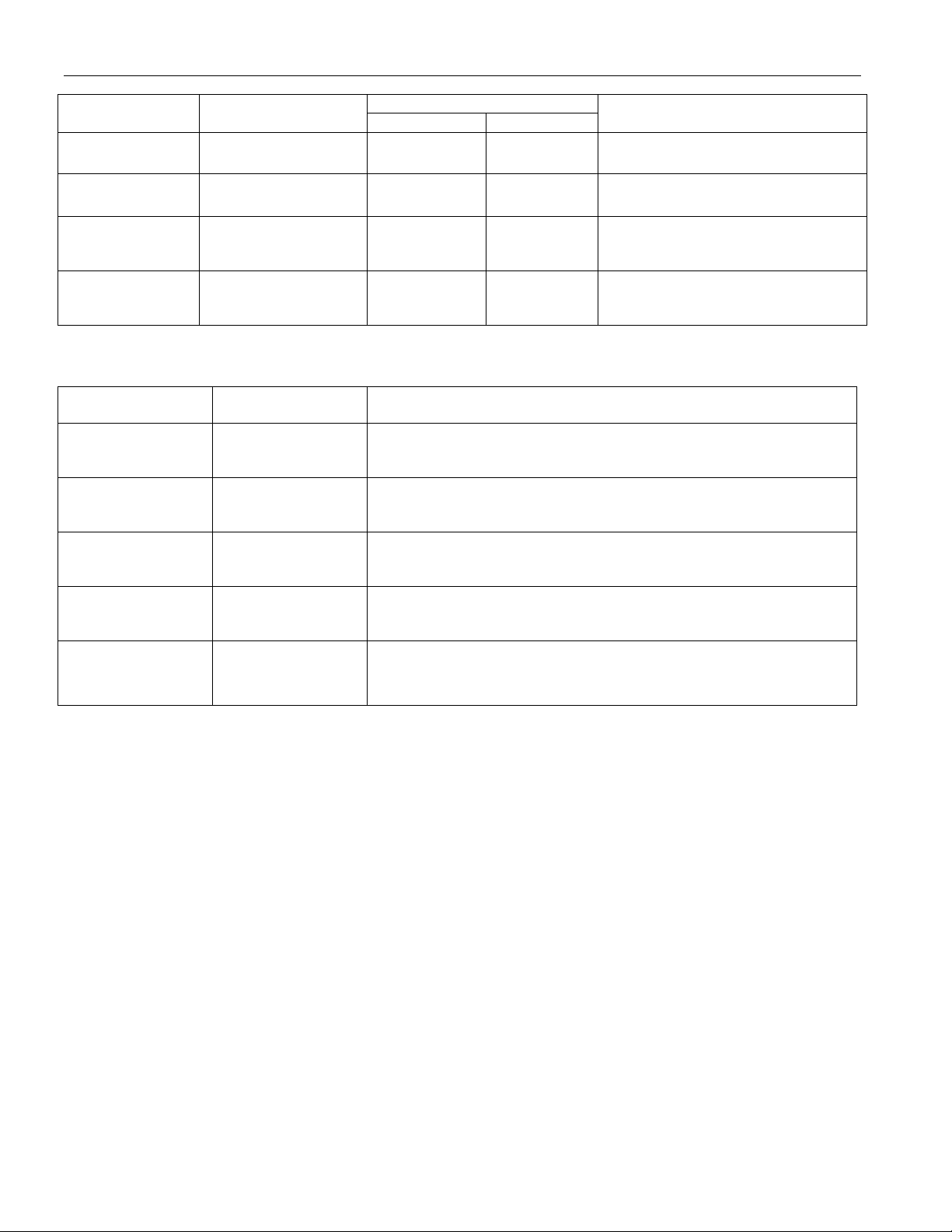

表1. 元件清单(未显示去耦电容)

DESIGNATION QTY DESCRIPTION SUPPLIER PART

U18 1

U20 1

U22 1

U23 1 DS3/E3 SCT, 11X11 CSBGA, 100 PIN Dallas Semiconductor DS3170

U24 1 T1/E1/J1 XCVR 100P QFP 0-70C Dallas Semiconductor DS2156L

U25 1 3.3V LIU Dallas Semiconductor DS21348

UB08 1

U01, U09 2

U07, U11 2

U13, UB01 2

U21, UB07 2

U31, UB06, UB11 3

C11, C13, C16, C25, C27, C31–

C35, C37, C41, C47, CB10,

CB63, CB114, CB128, CB164,

CB496

CB390, CB391, CB395, CB396 4 1206 CERAM 0.1uF 25V 10% Panasonic ECJ-3VB1E104K

D01–D03, D05, DB03–DB05 7 SCHOTTKY DIODE, 1 AMP 40 VOLT International Rectifier 10BQ040

DS01, DS07, DS10–DS12,

DS17, DS20

DS02, DS03, DS09, DS14,

DS15

DS04–DS06, DS08, DS13,

DS16, DS18, DS27, DS28,

DS35, DS37, DS38, DS40

DS19, DS43 2 LED, GREEN, SMD Panasonic LN1351C

DS21–DS26, DS30, DS32–

DS34, DS36, DS39, DS41,

DS42, DS44–DS48

GND_TP01–GND_TP07,

GND_TP09-–GND_TP44,

GND_TP46–GND_TP68,

GND_TPB01–GND_TPB10

H1–H8, H17–H19 8

19 1206 CERAM 10uF 10V 20% Panasonic ECJ-3YB1A106M

7 LED, AMBER, SMD Panasonic LN1451C

5 L_LED, GREEN, SMD Panasonic LN1351C

13 LED, RED, SMD Panasonic LN1251C

19 L_LED, RED, SMD Panasonic LN1251C

76 STANDARD GROUND CLIP KEYSTONE 4954

ELITE 10/100 ETHERNET TRANSPORT OVER

SERIAL LINK 14X14 CSBGA 169 PIN

3.3V T1.E1.J1 QUAD TRANSCEIVER 0-70C 256P

BGA

QUAD 10/100 ETHERNET EXTENSION TO WAN

17X17 PBGA 256 PIN

QUAD TRIPLE DUAL SINGLE ATM PACKET PHYS

FOR DS3 E3 STS1 0-70C 400P BGA

SOIC 8PIN STEP-UP DC-DC CONVERTER 0.5A

LIMIT

8-Pin μMAX/SOIC 1.8V or Adj

MICROPROCESSOR VOLTAGE MONITOR, 2.93V

RESET, 4PIN SOT143

Dual RS-232 transceivers with 3.3V/5V internal

capacitors

8-Pin μMAX/SOIC 2.5V or Adj

KIT, 4-40 HARDWARE, .50 NYLON STANDOFF AND

NYLON HEX-NUT

Dallas Semiconductor DS33Z11

Dallas Semiconductor DS21458

Dallas Semiconductor DS33Z44

Dallas Semiconductor DS3184

Maxim MAX1675EUA

Maxim MAX1792EUA18

Maxim MAX811SEUS-T

MAXIM NA

Maxim MAX1792EUA25

NA Lab Stock

3 of 59

Page 4

DS33Z44DK

DESIGNATION QTY DESCRIPTION SUPPLIER PART

KIT, 4-40 HARDWARE, 1.12 NYLON STANDOFF

H9–H16 16

J01–J05 5 CONNECTOR, FASTJACK SINGLE, 8 PIN Halo Electronics HFJ11-2450E

J06, J41 2 100 MIL 2*7 POS JUMPER NA Lab Stock

J07–J12 6

J13–J22 10

J23, J29, J32, J38, J39, J43,

J44, J47, JB07

J24, J30, J31, J33 4 100 MIL 2 POS JUMPER NA Lab Stock

J25, J26, J45, J46 4 TERMINAL STRIP, 10 PIN, DUAL ROW, VERT NA Lab Stock

9

AND NYLON HEX-NUT (1.12 STANDOFF PN =

4807K-ND)

RECEPTACLE, SMD, 140 PIN, .8MM, 2 ROW

VERTICAL

L_TERMINAL STRIP, 10 PIN, DUAL ROW, VERT DO

NOT POPLUATE

L_TERMINAL STRIP, SHROUDED, 10 PIN, DUAL

ROW, VERT

NA Lab Stock

AMP 5-179010-6

NA Lab Stock

3M Electronics 2510-6002UB

J27, J42 2

J28, J36 2 L_CONN, DB9 RA, LONG CASE AMP 747459-1

J48, J54, JB01 3 SOCKET, BANANA PLUG, HORIZONTAL, BLACK Mouser Electronics 164-6218

J49–J52 4 CONNECTOR BNC 75 OHM VERTICAL 5PIN Cambridge CP-BNCPC-004

J53, JB02, JB08 3 SOCKET, BANANA PLUG, HORIZONTAL, RED Mouser Electronics 164-6219

J55, JB11 2 L_RJ48 8 PIN SINGLE PORT CONNECTOR MOLEX 15-43-8588

J56–J59, J61, J63 6 CONNECTOR BNC 75 OHM RA 5PIN Trompetor UCBJR220

J60, J62, J64, J65 4 CONNECTOR BNC RA 5PIN Trompetor UCBJR220

JB05, JB06, JB09, JB10, JB13,

JB14

JB12 1 RA RJ45 8PIN 4PORT JACK MOL 43223-8140

JP01–JP19 19 100 MIL 3 POS JUMPER NA NA

L01, L03–L08, LB01, LB02 9 FERRITE 3A 100 OHM AT 100 MHZ 1206 SMD Steward HI1206N101R-00

L02, L09 2 INDUCTOR 22.0uH 2PIN SMT 20% Coiltronics UP1B-220

L10 1 XFMR 1-2CT XMIT, 1-1CT RCV, 40P WIDE SOIC Pulse T1068

R01, R02, RB10, RB11, RB18,

RB19, RB22, RB23, RB26,

RB27

R03, R04, RB12, RB13, RB20,

RB21, RB24, RB25, RB28,

RB29

R05, R06, R08, R09, R11 5

R07, R12, R16, R79, R160,

R244, R248, R250, R251,

R254, R255, RB126, RB143,

RB147, RB150, RB157

R10, R107 2 RES 1206 5.6 Ohm 1/8W 5% Panasonic

R132, R137, R142, R144,

R156, RB194, RB208, RB227

6 PLUG, SMD, 140 PIN, .8MM, 2 ROW VERTICAL AMP 179031-6

10 RES 0603 54.9 Ohm 1/16W 1% Panasonic ERJ-3EKF54R9V

10 RES 0603 49.9 Ohm 1/16W 1% Panasonic ERJ-3EKF49R9V

16 RES 0603 1.0K Ohm 1/16W 5% Panasonic ERJ-3GEYJ102V

8 L_RES 0603 0 Ohm 1/16W 1% AVX CJ10-000F

CONN 50 PIN, 2 ROW, POSTS VERT,

MOTHERBOARD FOOTPRINT

RES 0603 10.0K Ohm 1/16W 1% - Must be 1%

tolerance

SAMTEC TSW-125-07-T-D

Panasonic ERJ-3EKF1002V

ERJ8GEYJ5R6V

4 of 59

Page 5

DS33Z44DK

DESIGNATION QTY DESCRIPTION SUPPLIER PART

R13–R15, R18–R20, R22, R23,

R29, R30, RB01, RB03, RB07,

RB09, RB15–RB17, RB30–

RB32, RB34–RB38, RB41,

RB44, RB47, RB48, RB50–

RB52, B55, RB60, RB62, RB72,

RB73, RB75, RB80, RB82

R17, R21, R25–R28, R31, R55,

R57–R59, R71, R74–R76, R83,

R96–R102, R105, R106, R109,

R111, R112, R115–R117,

R120, R122–R126, R128,

R133, R134, R140, R141,

RB61, RB96, RB97, RB99,

RB100, RB102–RB110, RB112,

RB114–RB119, RB121,

RB123–RB125, RB127, RB128,

RB130, RB131, RB133,

RB135–RB138, RB145, RB148,

RB149, RB160, RB161, RB164,

RB165, RB167–RB171,

RB173–RB181, RB184, RB187,

RB311, RB320, RB335, RB339,

RB359

R171, R172, R174, R175,

R190, R191, R240, R241

R198–R200, R210–R213,

RB306, RB325, RB326

R201–R208, RB321–RB324,

RB327–RB330

R239, RB349 2 RES 0805 51.1 Ohm 1/10W 1% Panasonic ERJ-6ENF51R1V

R24, R114, R197, RB14, RB33,

RB40, RB42, RB43, RB49,

RB53, RB54, RB57–RB59,

RB71, RB77, RB78, RB152–

RB156, RB221, RB234, RB251,

RB284, RB304, RB331, RB332,

RB342, RB344, RB350, RB354,

RB360

R242, R243, RB144, RB166,

RB355–RB358, RB368–RB371

R32, R70, R78, R161, R176,

R194, R195, R237, R238,

RB129, RB134, RB146, RB193

R33–R54, R60–R69, R72, R73,

R131, R136, R143, R147,

R150, R154, R158, R163,

R166, R169, R173, R178–

R189, R215–R228, RB89–

RB95, RB101, RB188–RB191,

RB196–RB199, RB202–RB205,

RB210–RB213, RB216–RB219,

RB223–RB226, RB230–RB233,

RB239–RB242, RB244–RB249,

RB252–RB260, RB265–RB268,

RB270-RB282, RB289–RB297

R56, R90 2 RES 0603 1.0M Ohm 1/16W 5% Panasonic ERJ-3GEYJ105V

R77, RB159 2 L_RES 1206 0 Ohm 1/8W 5% Panasonic

R80, R81, R84, R87, R89, R91–

R93, R95, R108, R110, R118,

R127, R152, R153, R196,

R209, R214, R229–R236,

RB200, RB237, RB238, RB263,

RB264, RB286, RB287, RB300,

RB301, RB333, RB364

40 RES 0603 5.1K Ohm 1/16W 5% Panasonic ERJ-3GEYJ512V

104 RES 0603 30 Ohm 1/16W Panasonic ERJ-3GEYJ300V

8 L_RES 0805 0.0 Ohm 1/10W 5% Panasonic

10 RES 0603 332 Ohm 1/16W 1% Panasonic ERJ-3EKF3320V

16 RES 1206 0 Ohm 1/8W 5% Panasonic

34 L_RES 0603 330 Ohm 1/16W 5% Panasonic ERJ-3GEYJ331V

12 RES 0603 51 Ohm 1/16W 5% Panasonic ERJ-3GEYJ510V

13 RES 0603 330 Ohm 1/16W 5% Panasonic ERJ-3GEYJ331V

152 RES 0402 30 Ohm 1/16W 5% Panasonic ERJ-2GEJ300X

37 RES 0603 10K Ohm 1/16W 5% Panasonic ERJ-3GEYJ103V

ERJ6GEY0R00V

ERJ8GEYJ0R00V

ERJ8GEYJ0R00V

5 of 59

Page 6

DS33Z44DK

DESIGNATION QTY DESCRIPTION SUPPLIER PART

R85, R88, R94, R104, R113,

RB02, RB04–RB06, RB08,

RB39, RB45, RB46, RB56,

RB63–RB70, RB76, RB83,

RB98, RB183, RB185, RB192,

RB209, RB228, RB302, RB303,

RB305, RB338, RB340, RB341,

RB346–RB348, RB351–RB353,

RB361–RB363, RB365–RB367

R86, R103, R119, R121, R129,

R130, R135, R138, R139,

R145, R146, R149, R151,

R157, R162, R164, R167,

R168, R170, R177, R192,

R193, R245-R247, R249, R252,

R253, R256, R257, RB74,

RB79, RB132, RB139-RB141,

RB151, RB162, RB163, RB172,

RB182, RB186, RB206, RB207,

RB214, RB215, RB220, RB222,

RB229, RB235, RB236, RB243,

RB250, RB261, RB262, RB269,

RB308–RB310, RB343, RB345

RB201, RB285 2 RES 0805 330 Ohm 1/10W 5% Panasonic ERJ-6GEYJ331V

RB283 1

RB298, RB299, RB312–RB319,

RB336, RB337

RB81, RB84–RB88, RB111,

RB113, RB120, RB122

SW01–SW05, SW08–SW21,

SW24–SW26, SW29–SW31,

SW33–SW44

48 RES 0603 2.0K Ohm 1/16W 5% Panasonic ERJ-3GEYJ202V

61 L_RES 0603 10K Ohm 1/16W 5% Panasonic ERJ-3GEYJ103V

RES 0603 10K Ohm 1/10W 5% - SEE SPECIAL

INSTRUCTIONS

12 RES 0805 61.9 Ohm 1/10W 1% Panasonic ERJ-6ENF61R9V

10 RES 0603 DO NOT POPULATE NA NA

37 L_SWITCH, SP3T SLIDE, 4PIN TH Tyco 3-1437575-3

Panasonic

603_ERJ3GEYJ103V

SW06, SW22 2 L_SWITH 8POS 16PIN DIP LOW PROFILE AMP 435668-7

SW07, SW23 2 SWITCH MOM 4PIN SINGLE POLE Panasonic EVQPAE04M

SW27, SW28, SW32 3 L_DIPSWITCH, 10 POS AMP 435668-9

T01, T03 2 XFMR 16P SMT Pulse TX1099

T02, TB01 2 XFMR, OCTAL T3/E3, 1 TO 2, SMT 32 PIN Pulse T3049

TP01–TP78, TPB01, TPB02 80 TESTPOINT, 1 PLATED HOLE, DO NOT STUFF NA NA

U02–U06 5

U08, U12, U29 3 1MBit Flash based config mem Avnet XCF01SV020C

U10 1 XILINX SPARTAN xc200 2.5V FPGA,256 PIN BGA Xilinx

U14, U26, U30, UB05 4 CYPRESS SRAM, LAB STOCK NA NA

U15, U19 2 mmc2107 processor Motorola MMC2107

U16, U27 2 XILINX SPARTAN 2.5V FPGA,256 PIN BGA Xilinx

U17, U28, U32 3 10 pin res pack, 10K ohm NA NA

UB02, UB03, UB04 3 100 PIN CPLD XILINX

UB09, UB10 2

IC, DsPHYTER11-SINGLE 10/100 ETHERNET

TRANSCEIVER, 65 PIN LLP

SYNCHRONOUS DRAM, 1MEGX32X4 BANKS,

TSOP 86 PIN

National

Semiconductor

Micron

DP83847ALQA5

6A

XC2S2005FG256C

XC2S505FG256C

XC95144XL10TQ100C

MT48LC4M32B2

TG-7

6 of 59

Page 7

DS33Z44DK

DESIGNATION QTY DESCRIPTION SUPPLIER PART

UX01–UX12, UXB02–UXB04,

UXB06–UXB08

UXB01, UXB05 2 HIGH SPEED INVERTER Fairchild NC7SZ86

X01, X02 2 XTAL LOW PROFILE 8.0MHZ ECL EC1-8.000M

Y01, Y09 2

Y02, Y13 2

Y03 1 OSCILLATOR, CRYSTAL CLOCK, 3.3V - 2.048 MHZ SaRonix

Y05, Y06 2

Y07 1 OSCILLATOR, CRYSTAL CLOCK, 3.3V - 44.736 MHZ SaRonix

Y08 1 OSCILLATOR, CRYSTAL CLOCK, 5.0V - 44.736 MHZ SaRonix

YB02 1

18 HIGH SPEED BUFFER Fairchild NC7SZ86

OSCILLATOR, CRYSTAL CLOCK, 3.3V - 25.000

MHZ, Low Jitter required for PHY

SPI SERIAL EEPROM 16K 8 PIN DIP 2.7V NEEDS

SOCKET

OSCILLATOR, CRYSTAL CLOCK, 3.3V - 100.000

MHZ

L_OSCILLATOR, CRYSTAL CLOCK, 3.3V - 2.048

MHZ

SaRonix

Atmel

SaRonix

SaRonix

NTH089AA3-

25.000

AT25160A-10PI-

2.7

NTH039A3-

2.0480

NTH089A3-

100.0000

NTH089AA3-

44.736

NTH089AA-

44.736

NTH039A3-

2.0480

7 of 59

Page 8

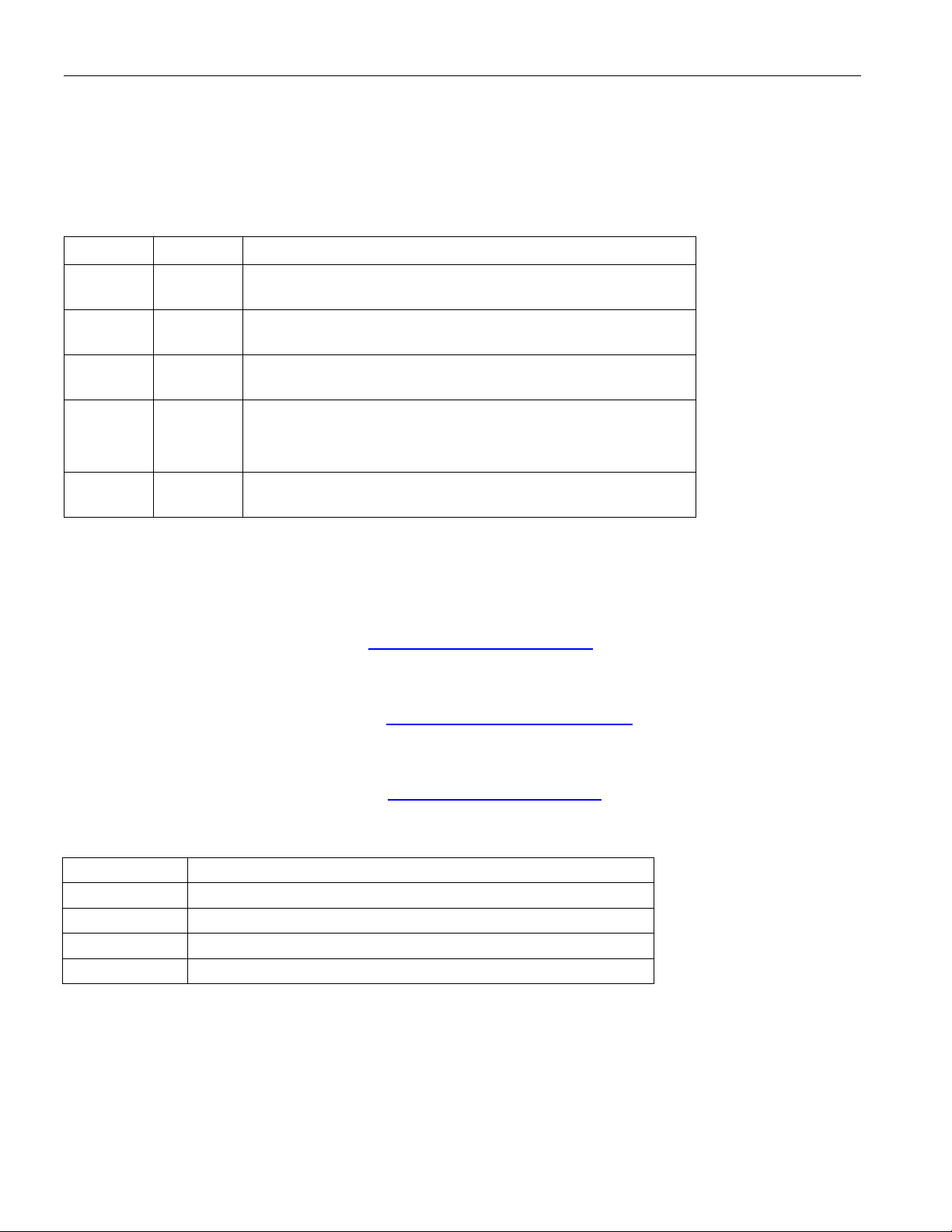

图1. 系统平面图

ETHERNET PHYs,

MAGNETIC,

LEDS, AND

JUMPERS

HARDWARE

MODE SWITCHES

FOR DS33Z44

DS33Z44 MAINBOARD

LEDS AND TESTPOINTS

SDRAM

DS33Z44

MICROPROCESSOR

AND SERIAL PORT

(57600-8-N-1)

DS33Z44DK

DS21458 RESOURCE CARD

(DETAIL PROVIDED BELOW)

DS3184 RESOURCE CARD

(DETAIL PROVIDED BELOW)

SERIAL INTERFACE

2 X 140 PIN CONNECTORS

图2. DS3174 子卡平面图

+ JUMPERS

TEST POINTS

140 PIN CONNECTORS (2 TOP, 2 BOTTOM)

JUMPERS

CPLD

(MUX)

CPLD

(MUX)

OSC

DS3174

QUAD-PORT

T3/E3

TRANSCEIVER

LOOPBACK

JUMPER

DS3174 PORT 3

LAN PORT 3

BNC Tx Rx

DS3174 PORT 1

LAN PORT 4

DS3174 PORT 2

LAN PORT 2

JTAG

DS3174 PORT 4

LAN PORT 1

8 of 59

Page 9

DS33Z44DK

J

G

TRANSFORMER

DS3174 四端口T3/E3 的PCB平面图在

设置为三态/使能。电路板方向如

还增加了一个 2 引脚跳线 JP24 以允许环回。安装短路器后,该电路板通过 CPLD 实现环回;DS33Z44 发送的所有

通信数据将送回 Z44,在 CPLD 环回模式,DS3174 发出的信息将被忽略。

四端口 T3/E3 板用于连接 DS33Z11 或 DS33Z44 主板。四端口 T3/E3 板可与四端口 T1/E1 板配合使用,以这种方式

使用时,四端口 T1/E1 板安装在四端口 T3/E3 板的下方。这样 T3/E3 板上的跳线可分别控制两块电路板的各端口为

三态或使能状态。

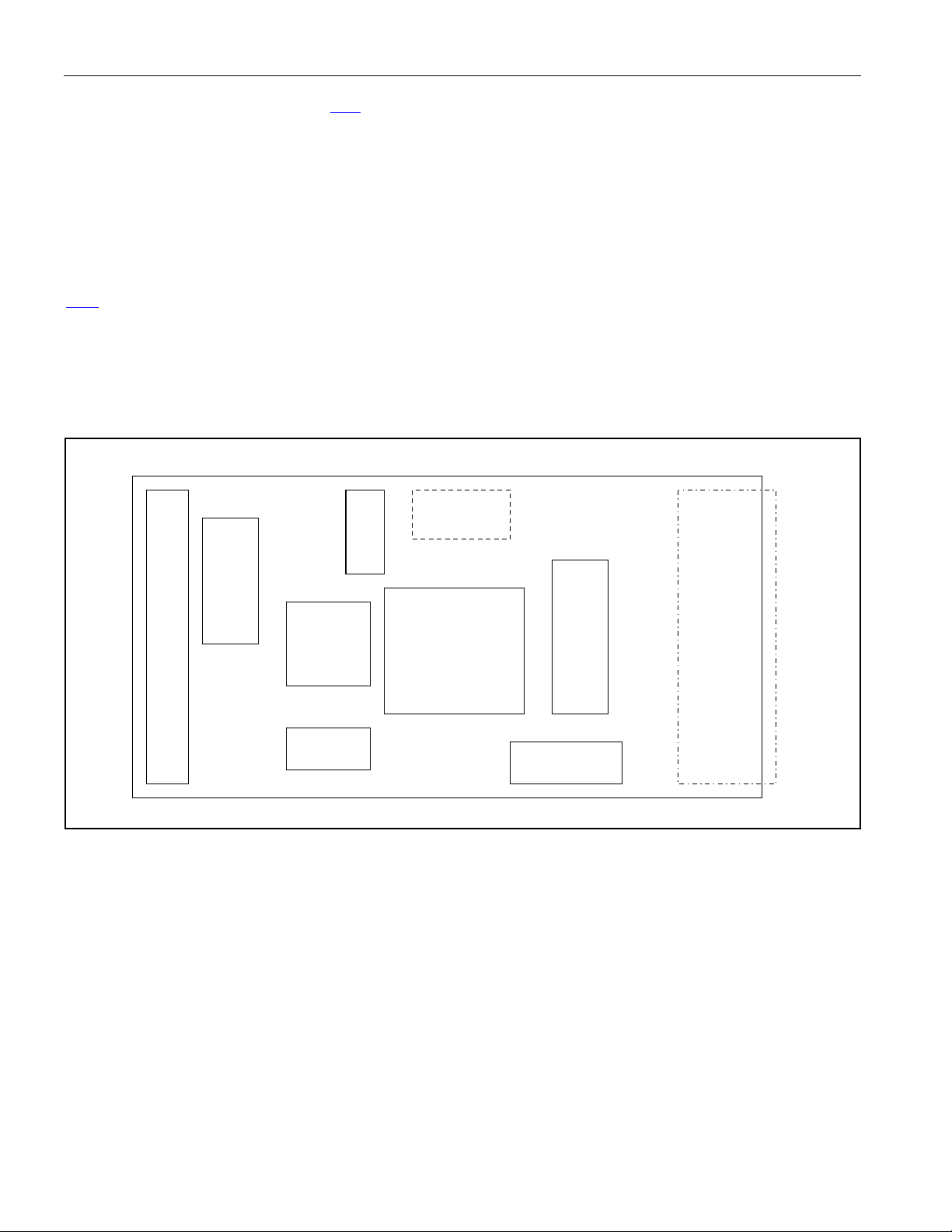

图 3给出了DS21458 四端口T1/E1 PCB的平面图。当前的配置是采用板载 2.048MHz振荡器作为MCLK1 振荡器。

WAN卡上提供port 3 和port 4 的测试点,主板上提供port 1 和 2 的测试点。

四端口 T1/E1 板可与四端口 T3/E3 板配合使用。以这种方式使用时,四端口 T1/E1 板安装在四端口 T3/E3 板的下

方。这样 T3/E3 板上的跳线可分别控制两块电路板的各端口为三态或使能状态。

图 2中给出。JP16、JP17、JP18 和JP19 为 3 引脚跳针,用于将T3/E3 端口

图 2所示时,各跳线上部的两个引脚短接可使能T3/E3 通信。

图3. DS21458 子卡平面图

TEST POINTS

140 PIN CONNECTORS

INT LED

FPGA

TA

OSC

MCLK1, 2

DS21458

QUAD-PORT

T1/E1

TRANSCEIVER

QUAD

RLOS LEDS

PORT 2

PORT 4

PORT 1

QUAD-PORT RJ45

PORT 3

9 of 59

Page 10

DS33Z44DK

PCB 勘误表

• 串联子卡配置开关SW27、SW28 和SW32 的VCC和地的丝印标号方向有错。需用粘性标签加以修正。

• 四端口 T1E1 卡的 JTAG 连接器的信号描述有误。需用粘性标签加以修正。

• 在 PCB 布局中变压器初级位于错误的一侧(由此产生 2:1 的绕线而非 1:2)。原理图对此进行了修正,PCB/装配图

纠正了这个错误。

文件位置

该开发板依靠几个支持文件,由CD 光盘提供并且作为一个zip 文件可从Maxim 网站获得www.maxim-

ic.com.cn/DS33Z44DK。

所有位置都相对于 CD/zip 文件的顶层目录。

• DS33Z44 的寄存器定义文件和配置文件:

o .\cfg_demo_gui\DS33Z44_cfg_demo_gui\DS33Z44.def

o .\DS33Z44_cfg_demo_gui\SU_LI_PORT4.def (def files for port 3, 2, 1 not shown)

o .\DS33Z44_cfg_demo_gui\basic_config.mfg

• DS21458 的寄存器定义文件和配置文件:

o .\DS33Z44_cfg_demo_gui\Qt1e1_DS21458\DS21458RC.def

o .\DS33Z44_cfg_demo_gui\Qt1e1_DS21458\DS21458RC_FPGA.def

o .\DS33Z44_cfg_demo_gui\Qt1e1_DS21458\e1_gapclk_crc4_hdb3_nocas.ini

o .\DS33Z44_cfg_demo_gui\Qt1e1_DS21458\gapclk_DS21458_T1_ESF_LBO0.ini

• DS3174 的寄存器定义文件和配置文件:

o .\DS33Z44_cfg_demo_gui\Qt3e3_DS3184\ds3184_evbrd_reduced.def

o ….. 14 other low level def files ….

o .\DS33Z44_cfg_demo_gui\Qt3e3_DS3184\84_t3_sct_needscoaxlb.mfg

10 of 59

Page 11

DS33Z44DK

基本操作

开发板供电

• 将子卡插入主板。

• 给 PCB 上的 3.3V 和 GND 香蕉插头连接电源,启动时系统会消耗约 1A 电流。

• 将开关设置为

• 左上排:除 MODEC0 为高外,全低

• 右上排:A2、A1、A0 在中间位置,SCANTRI 为低

• 下排:全高(AFCS、FULLDS、H1OS)

概要

• 上电后,处理器 FPGA 的状态指示 LED (绿色的 DS19)被点亮,中断指示 LED (红色的 DS42)被点亮。

DS33Z44 的队列溢出指示 LED (红色的 DS45、DS46、DS47、DS48)不会点亮。如果连接有以太网则 PHY

LINK LED (绿色的 DS02、DS03、DS14)将被点亮。

接下来为几个基本的系统初始化。

基本的 DS33Z44 初始化 (用于所有的快速设置)

本章节介绍配置 Z44 的四种基本方法。这些初始化中的任意方法都可参考下面的例子快速设置:

1. 上电后,板载器件驱动为 DS33Z44 及其串行子卡提供基本的配置。这将使能以太网端口与串行端口之间的

通信。更多详细信息请参考器件驱动文档。器件驱动操作依赖于跳线设置,详细资料在表 2 中列出。

2. 基于寄存器的配置。运行ChipView.exe并选择Register View。在提示定义文件时,选择名为DS33Z44.def的

文件。加载定义文件后,转到文件菜单并选择

择名为 4Portsbasic_config.mfg的文件。

3. 硬件模式。按照开发板供电章节所述对开关进行设置,然后进行以下改动:HWMODE←3.3V,A0←3.3V,

A1←3.3V,A2←0V。这可将端口设置为 LSB 在前,加扰关闭,封装 HDLC。此后数据将从以太网端口传送

至串口。在这种模式下,不传送广播帧(例如 ping)。

4. DK 提供 EEPROM 模式,但是超出了本手册的范围。

快速配置

• 在串行子卡上安装跳线 24。跳线JP16–JP19 必须为高。这将使卡进入CPLD回环并按照表 3所述使能所有四个端

• 按照前面章节所述完成硬件配置和 DS33Z44 的一个基本配置。

• 使用附带的电缆,将以太网连接器连接至通用 PC 或网络测试设备。这将使链接 LED 点亮。

• 此后,发送给 DS33Z44 的任何数据包都将被重复发回。输入包(例如:ping)将使 RX LED 闪烁。之后 TX LED

• 要配合使用器件驱动,请从下拉菜单中选择:

#1 (Device Driver + CPLD

口。

会闪烁。

• Tools→Plugins→Load Plugins。在询问 DLL 是否已注册时选择是

• Select Tools→Plugins→DS33Z44/11/41 Device Driver Demo

• 一个名叫‘Zchip Configuration’的程序弹出。

• 通过选择 File→Load Settings (在 ‘Zchip Configuration’ 程序中)为 GUI 预加载基本的配置。选择名为

‘basic_Config.eset’的文件

表 2 (带有简短描述)所述的软件模式。

File→Memory Config File→Load .MFG file。出现提示后,选

环回

)

11 of 59

Page 12

DS33Z44DK

快速配置

• 在DS3174 串行子卡上安装跳线J24。跳线JP16–JP19 应设置为高。这将使卡进入DS3174 模式并按照表 3所述

• 按照前文所述完成硬件配置和 DS33Z44 的一个基本配置。

• 使用附带的电缆,将以太网连接器连接至通用 PC 或网络测试设备。这将使链接 LED 点亮。

• 运行ChipView.exe (如果它已被打开,则退出会话)并选择Register View。在提示定义文件时,选择名为

• 在 DS3174 的网络侧安装回环连接器。

• 此后,发送给 DS33Z44 的任何数据包将被重复发回。输入数据包(例如:ping)将使 RX LED 闪烁,之后 TX LED

快速配置

• 按照前文所述完成硬件配置和 DS33Z44 的一个基本配置。

• 使用附带的电缆,将以太网连接器连接至通用 PC 或网络测试设备。这将使链接 LED 点亮。

• 运行ChipView.exe (如果它已被打开,则退出会话)并选择Register View。在提示定义文件时,选择名为

• 在 DS21458 的网络侧安装环回连接器;RLOS LED 将熄灭。

• 此后,发送给 DS33Z44 的任何数据包将被重复发回。输入数据包(例如:ping)将使 RX LED 闪烁,之后 TX LED

#2 (DS3174 T3E3)

使能所有四个端口。

ds3184_evbrd_reduced.def 的文件。加载定义文件后,转至文件菜单选择

File→

Load .MFG file。出现提示后,选择名为 84_t3_sct_needscoaxlb.mfg的文件。

也闪烁。

#3 (DS21458 T1E1)

DS21458.def的文件。加载定义文件后,转至文件菜单选择

名为e1_gapclk_crc4_hdb3_nocas.ini的文件。

也闪烁。

File→Reg Ini File→Load Ini File。出现提示后,选择

File→Memory Config

12 of 59

Page 13

DS33Z44DK

配置开关和跳线

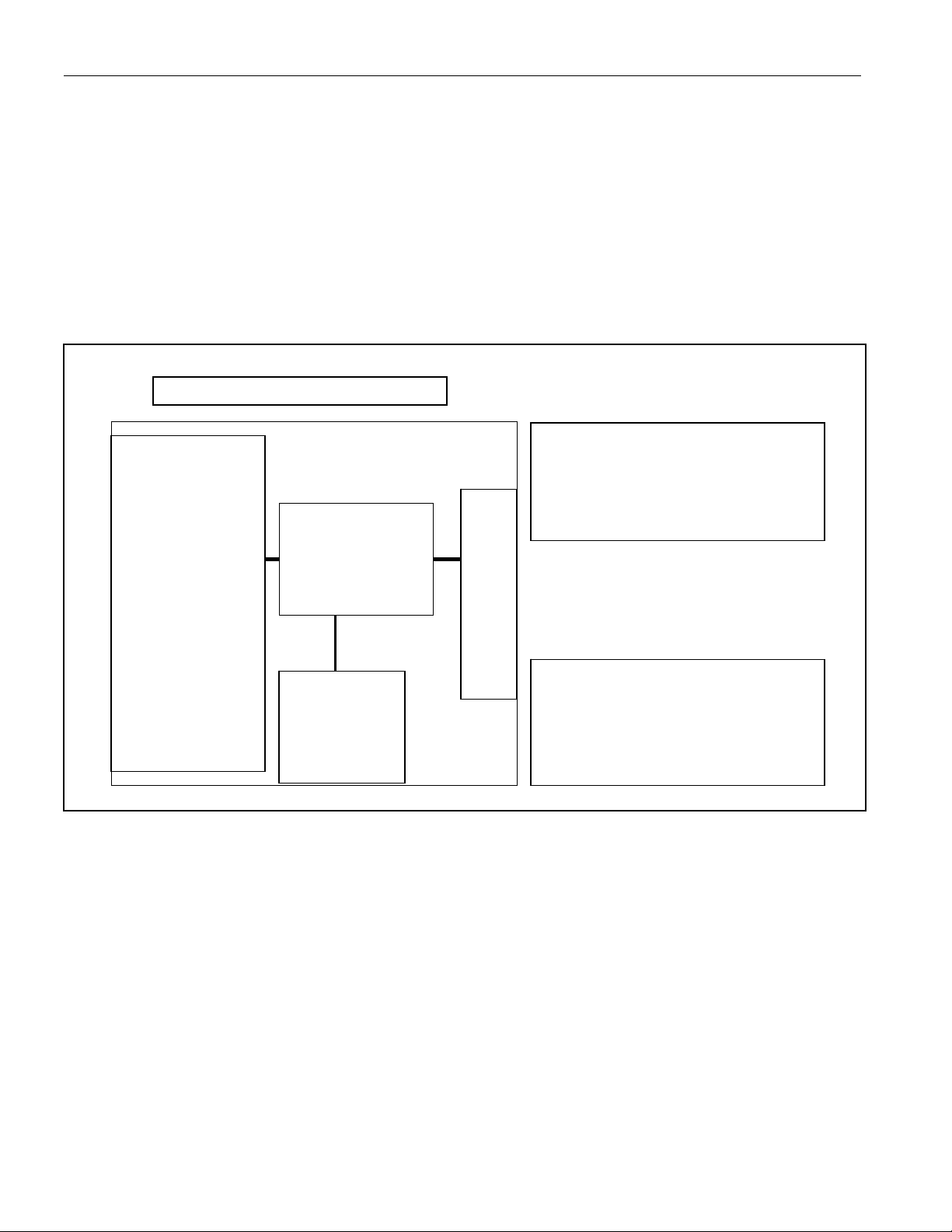

DS33Z44DK具有数个配置开关、香蕉插头、振荡器和跳线。表 2按照在PCB上出现的顺序(从左到右,从上至下),

提供了这些信号的描述。

表2. 主板 PCB 配置

SILKSCREEN

REFERENCE

J25.9 + J25.10 Reserved Not Installed —

J25.7 + J25.8 Enable device driver User decision —

J25.5 + J25.6 Enable callbacks User decision —

GROUND

(banana plug)

VDD 3.3V

(banana plug)

OnCe BDM — — Debug connector for processor

DCEDTES

(3pos switch)

RMIIMII

(3pos switch)

CKPHA

(3pos switch)

MODEC0

(3pos switch)

MODEC1

(3pos switch)

HWMODE

(3pos switch)

SCANMO

(3pos switch)

SCANTRI

(3pos switch)

….testpoints…. DS33Z44 testpoints — —

Z-RESET (button) DS33Z44 reset — — System reset

A2, A1, A0

(3pos switches)

SDRAM CLOCK

MII CLOCK PHY MII clock Installed Installed

spi_cs, spi_ck,

spi_miso,

spi_mosi

FUNCTION

Power supply ground — —

Power supply VDD — —

DS33Z44 mode pin;

DTE/DCE selection

DS33Z44 mode pin Low Low High for RMII, low for MII

DS33Z44 mode pin Low Low

DS33Z44 mode pin High Low Software mode selected

DS33Z44 mode pin Low Low Software mode selected

DS33Z44 mode pin Low Low

DS33Z44 mode pin Low Low Set low for normal operation

DS33Z44 mode pin Low Low Set low for normal operation

DS33Z44/SPI pins Mid position Mid position

DS33Z44 SDRAM

clock

— — — SPI signals (for EEPROM memory)

BASIC SETTING

SW MODE HW MODE

Low Low Low for DTE

Installed Installed

DESCRIPTION

This jumper is not for use with the

DS33Z44 design kit. Pin J25.10 has

been removed to prevent accidental

installation.

When installed the device driver will

con 图 the DS33Z44 and the

Transceiver during power-up.

When installed the driver will

respond to interrupts.

System Ground. Always connected

to power supply.

System VDD. Always connected to

power supply.

SPI EEPROM hardware mode

configuration switch

Hardware/software mode (software

mode selected)

Processor bus, JTAG and LAN side

testpoints for Zchip

Address pin/EEPROM config switch.

Set to mid position to allow

connection to processor.

100MHz oscillator to drive SDRAM

clock

25MHz oscillator to drive SDRAM

clock

….testpoints….. DS33Z44 testpoints — — DS33Z44 serial port testpoints

AFCS

(1 per port)

DS33Z44 mode pin HW mode only High Set high to enable auto flow control.

13 of 59

Page 14

SILKSCREEN

REFERENCE

FULLDS

(1 per port)

H10S

(1 per port)

GROUND/VDD

(banana plug)

VDD 3.3V

(banana plug)

FUNCTION

DS33Z44 mode pin HW mode only High Set high to enable full duplex.

DS33Z44 mode pin HW mode only High Set high to confg for 100Mb.

Power supply

ground/3.3V

Power supply VDD — —

表3. DS3174 串行子卡跳线设置

BASIC SETTING

SW MODE HW MODE

— —

DS33Z44DK

DESCRIPTION

Redundant connection to system

power. Use plugs at either top or

bottom of board.

Redundant connection to system

power. Use plugs at either top or

bottom of board.

JUMPER

SETTINGS

JP16

JP17

JP18

JP19

J243 CPLD loopback

MODE COMMENT

Port 4 tri-state

(at CPLD)

Port 2 tri-state

(at CPLD)

Port 3 tri-state

(at CPLD)

Port 1 tri-state

(at CPLD)

When the middle pin of this 3 position jumper is set to VCC, the

CPLD passes traffic from the DS3174 to the DS33Z44. When the pin

is set low, the CPLD tri-states this port.

When the middle pin of this 3 position jumper is set to VCC, the

CPLD passes traffic from the DS3174 to the DS33Z44. When the pin

is set low, the CPLD tri-states this port.

When the middle pin of this 3 position jumper is set to VCC, the

CPLD passes traffic from the DS3174 to the DS33Z44. When the pin

is set low, the CPLD tri-states this port.

When the middle pin of this 3 position jumper is set to VCC, the

CPLD passes traffic from the DS3174 to the DS33Z44. When the pin

is set low, the CPLD tri-states this port.

CPLD loopback makes the following connections:

Zrser ← Ztser, Ztden ← 3.3V, Zrden ← 3.3V,

Ztclki ← OscY03, Zrclki ← OscY03

14 of 59

Page 15

DS33Z44DK

地址映射(所有板卡)

Motorola 子卡地址空间起始于 0x81000000。下面给出的所有偏移都是相对于子卡地址空间(在前文中给出)的起始

值。

表4. 子卡地址映射概述

OFFSET DEVICE DESCRIPTION

0X0000 to

0X0087

0X1000 to

0X1FFF

0X2000 to

0X2FFF

0X4000 to

0X4010

0X3000 to

0X3FFF

DS33Z44、DS21458 和 DS3174 内的寄存器可方便的使用基于主机的 ChipView 用户界面软件和之前提到的定义文

件来进行修改。

FPGA Processor board identification

DS33Z44 DS33Z44. Uses CS_X1.

DS21458 T1E1 DS21458 resource card. Uses CS_X2.

FPGA on DS21458 resource card. Used to facilitate IBO mode.

FPGA

DS3174 T3E3 resource card. Uses CS_X3.

Default configuration of FPGA is compatible with non-IBO mode

functionality. The FPGA settings do not require modification for

use with the DS33Z44.

DS33Z44 信息

关于DS33Z44 的更多信息,请参考我们网站www.maxim-ic.com.cn/DS33Z44提供的DS33Z44 数据资料。

DS33Z44DK 信息

关于DS33Z44DK的更多信息,请参考我们网站www.maxim-ic.com.cn/DS33Z44DK.提供的DS33Z44DK数据资料。

技术支持

若需进一步的技术支持,请将您的问题e-mail至telecom.support@dalsemi.com (English only)。

文档版本历史

版本日期 说明

032305

042205

051105

110106

第一版 DS33Z44DK 数据资料发布。

基本的

更新

增加新的 PCB 勘误。

更新原理图。

DS33Z44

初始化

章节;增加

15 of 59

快速配置

#1 步骤

。

Page 16

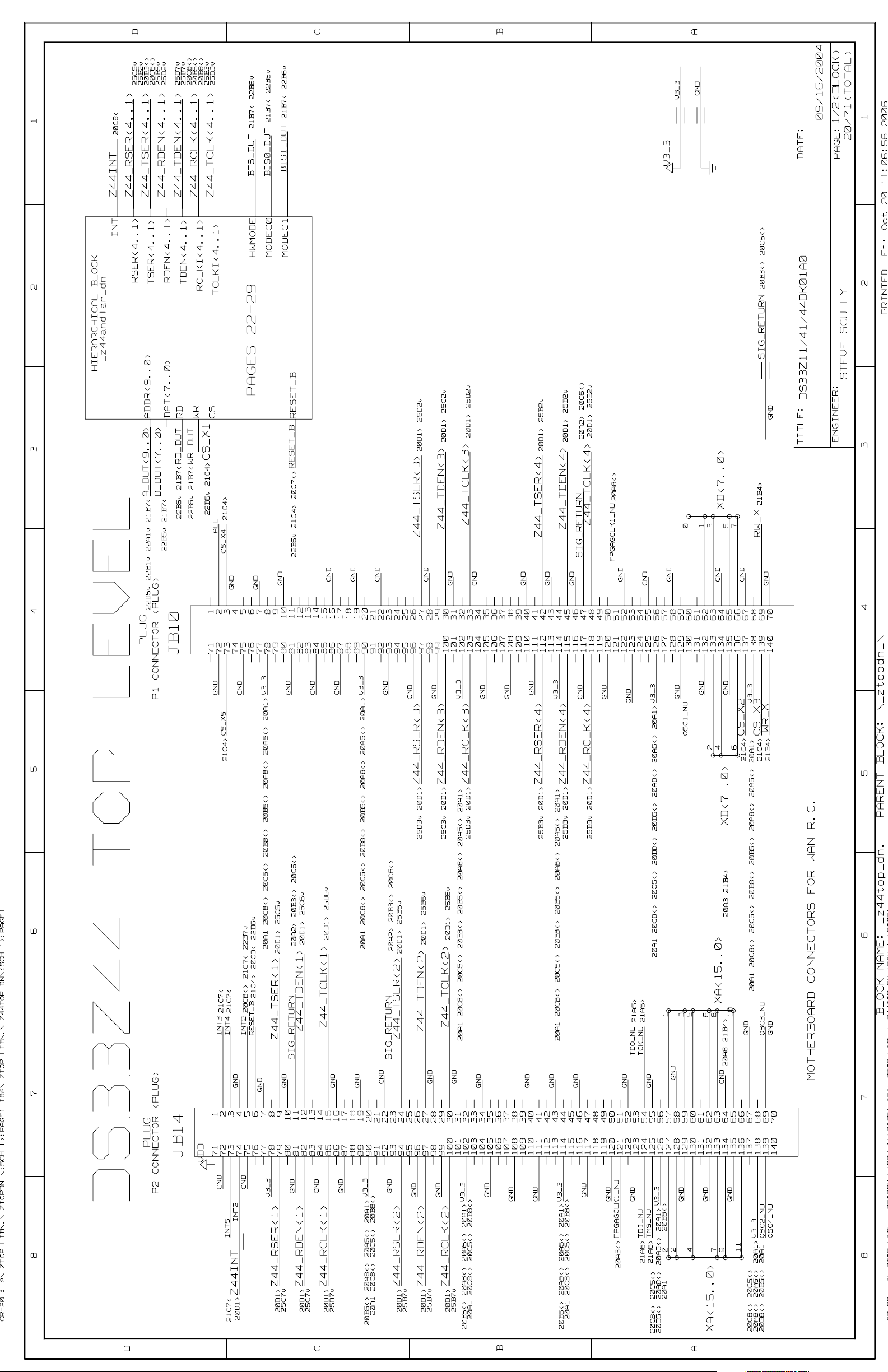

DS33Z44DK

2 X 140 PIN CONNECTORS

原理图

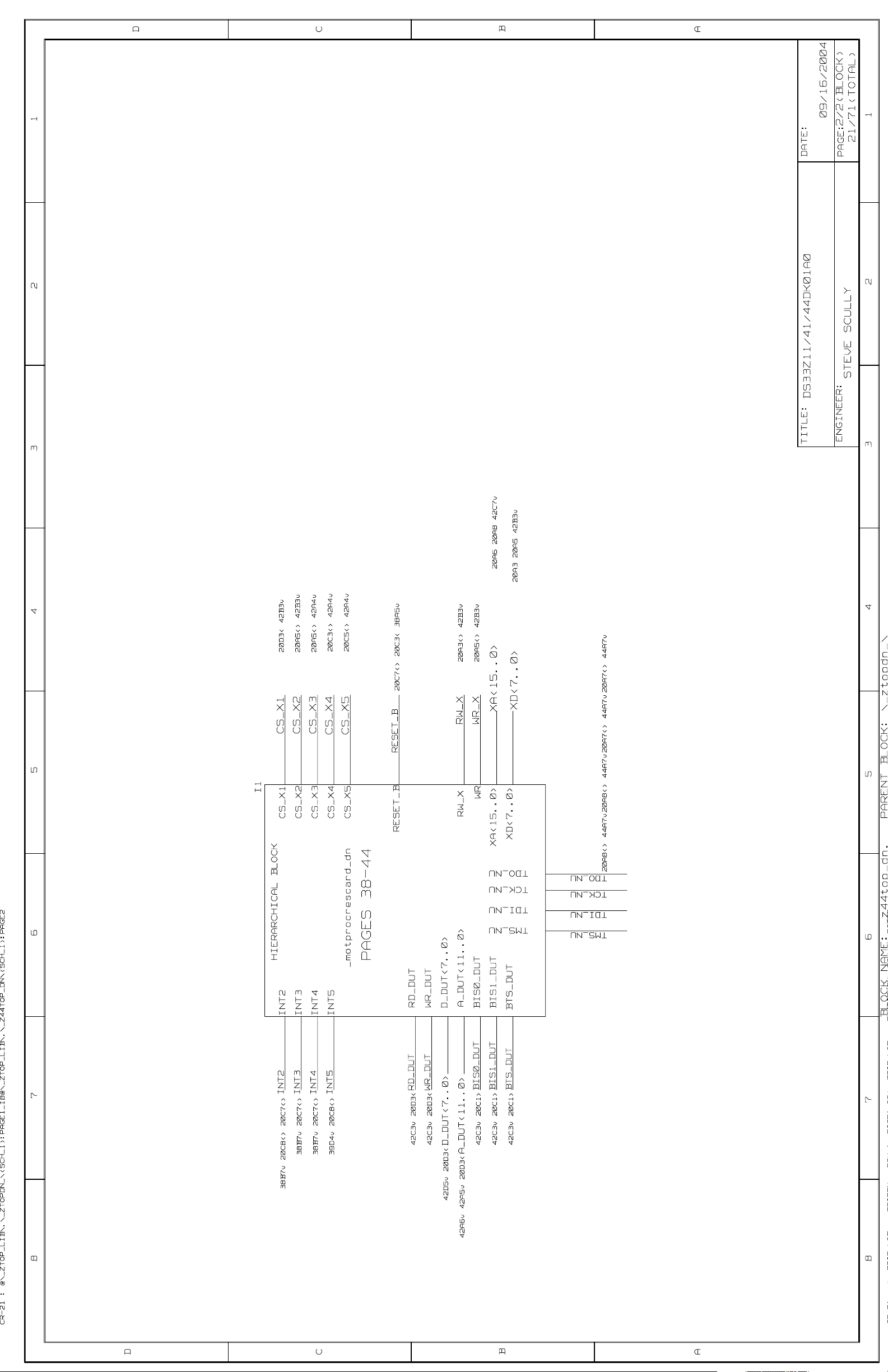

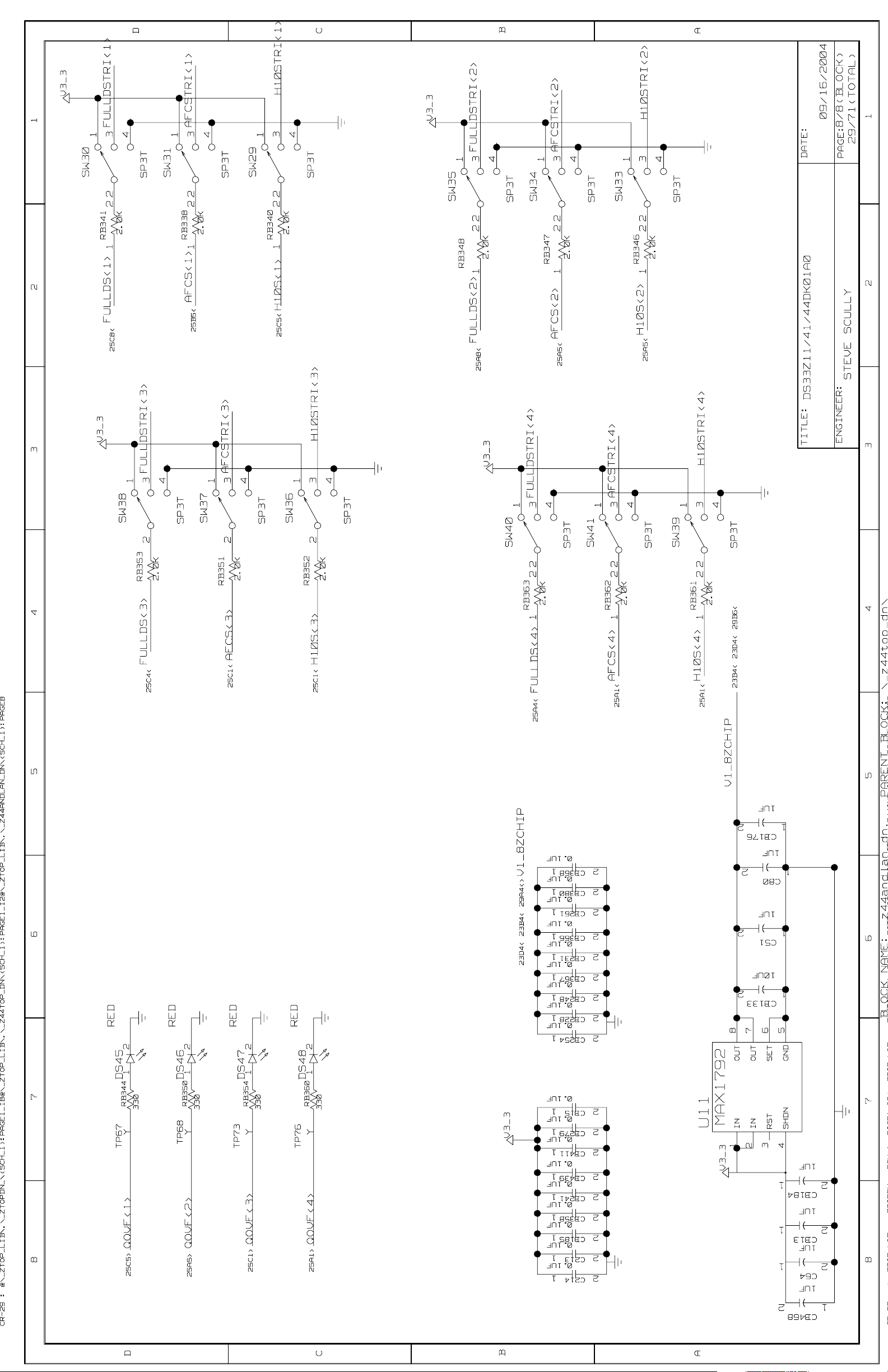

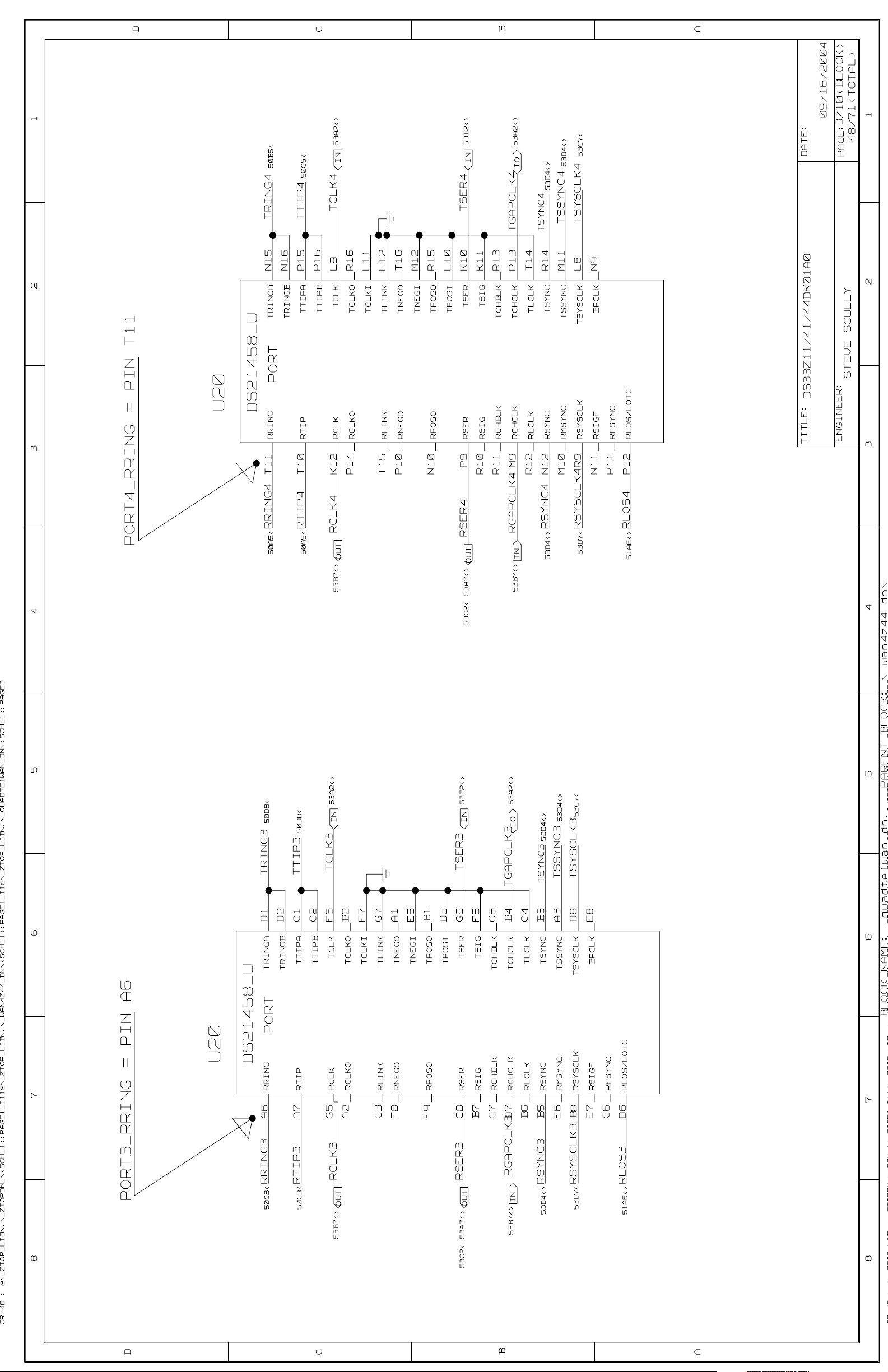

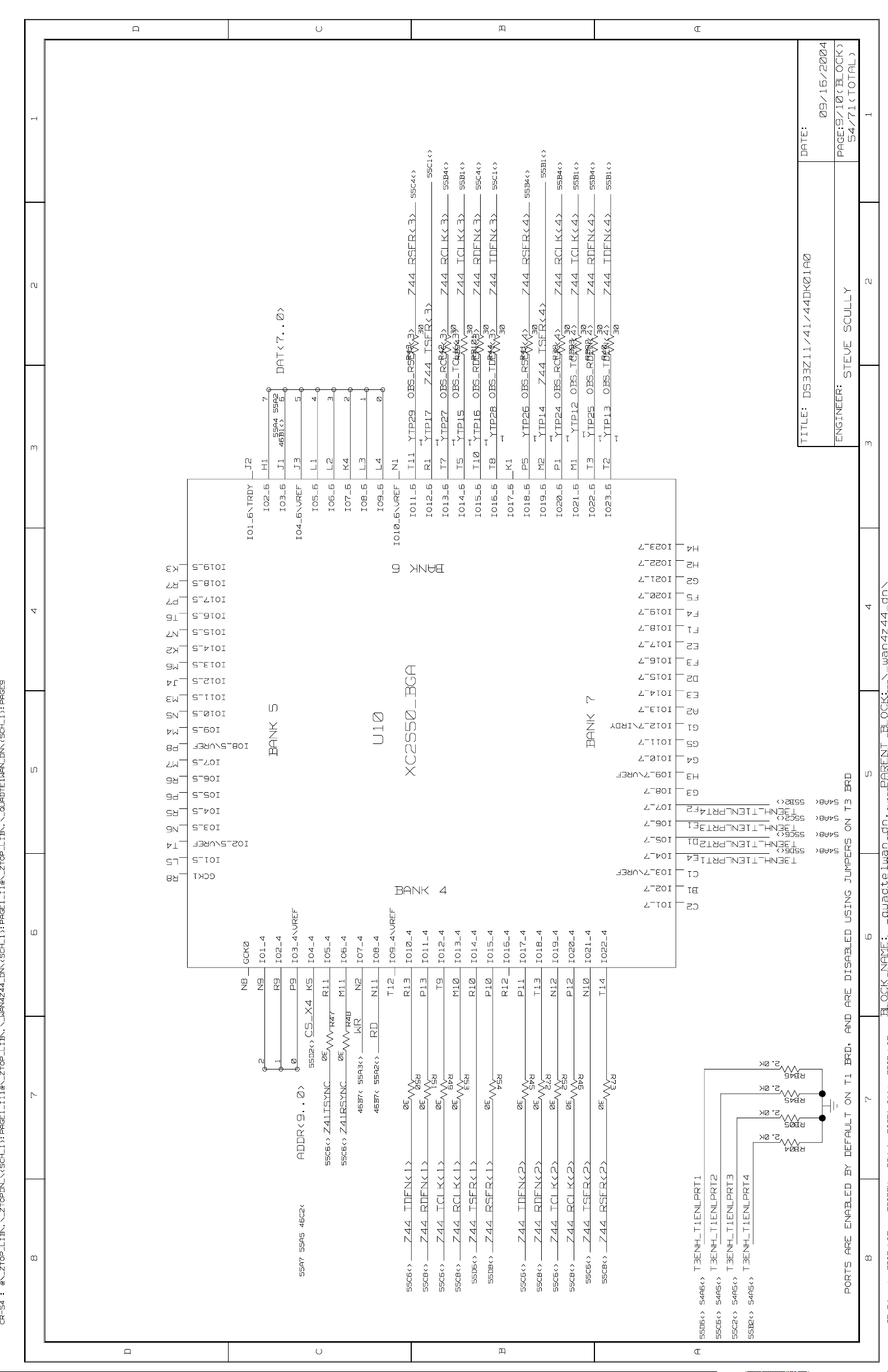

DS33Z44DK 的原理图在后续页中给出。由于采用了层次化原理图,以下说明也按顺序进行。主板由六个分层模块组

成:处理器模块,DS33Z44 模块,以及作为嵌套模块、包含在 DS33Z44 模块中的四个以太网模块。各串口卡

(DS21458 和 DS3174)由单层模块组成,连接至主板上的 140 引脚卡入式 AV 总线。

除V

和地之外,各层内的信号都为本地信号。输入端口和输出端口连接器可使分层模块内部的信号能作为分层模块

CC

符号的引脚来访问。这样一来,模块可以像普通元件一样用线连接在一起。下面再一次给出了带有各功能模块原理

图页码的系统框图。

这里未给出该系统中包含的其他分层模块(主要是单端口串口卡和 DS33Z11 主板)。由于这一点,页码将不连续并且

相对于总的页数将会有一些间断。但是,任何给定分层模块内部的页码是连续的。

DS33Z44 MAINBOARD TOP LEVEL

PHY SYMBOLS ON

PAGES 26-27

PORT 1 ETHERNET

PHY

SCHEMATIC

PAGES 30-31

PORT 3 ETHERNET

PHY

SCHEMATIC

PAGES 36-37

PORT 2 ETHERNET

PHY

SCHEMATIC

PAGES 32-33

DS33Z44 BLOCK

PAGE 20 SYMBOL

SCHEMATIC

PAGES 22-29

µP BLOCK

PAGE 21 SYMBOL

SCHEMATIC

PAGES 38-44

SCHEMATIC

PAGES 46-55

SERIAL INTERFACE

SCHEMATIC

PAGES 56-63

DS21458 RESOURCE CARD

DS3184 RESOURCE CARD

Maxim/Dallas Semiconductor不对Maxim/Dallas Semiconductor

没有任何通报的前提下修改产品资料和规格的权利。

Maxim Integrated Products, 120 San Gabriel D rive, Sunnyvale, CA 94086 408-737-7600

Maxim 标志是 Maxim Integrated Products, Inc.的注册商标。Dallas 标志是 Dallas Semiconductor Corp.的注册商标

16 of 59

产品以外的任何电路使用负责,也不提供其专利许可。

© 2006 Maxim Integrated Products • Printed USA

Maxim/Dallas Semiconductor

保留在任何时间、

。

Page 17

D

20B 5<>

20B 8<>

20C 8<>

25B 3v

25B 7v

25D 7v

20B 3<>

20C 6<>

25B 2v

25B 5v

25C 5v

25D 2v

1

20C8<

Z44INT

Z44_RSER<4..1>

Z44_RDEN<4..1>

Z44_TSER<4..1>

25D 3v

22B 6v

22B 6v

22B 6v

21B7<

21B7<

21B7<

GND

V3_ 3

09/16/2004

1

1/2(BLOCK)

20/71(TOTAL)

BIS1_DUT

BIS0_DUT

BTS_DUT

Z44_TCLK<4..1>

Z44_TDEN<4..1>

Z44_RCLK<4..1>

V3_3

DATE:

PAGE:

INT

HWMODE

MODEC1

MODEC0

RDEN<4..1>

2

RSER<4..1>

TDEN<4..1>

TSER<4..1>

RCLKI<4..1>

TCLKI<4..1>

20C 6<>

20B3<>

2

_z44andlan_dn

HIERARCHICAL BLOCK

PAGES 22-29

25D 2v

DAT<7..0>

ADDR<9..0>

CS

WR

RD

RESET_B

3

CS_X1

WR_DUT

RD_DUT

21C4>

21B7<

21B7<

A_DUT<9..0 >

D_DUT<7..0 >

22B 6v

22B 6v

22B 6v

21B7<

21B7<

22B 5v

22A 1v22B1 v22D5v

4

21C4>

ALE

CS_ X4

GND

GND

3

1

6

5

4

2

RESET_B

20C 7<>

21C4>

22B 6v

GND

7

8

9

11

10

GND

14

13

12

159016

172219

GND

GND

18

20

23

21

PLUG

73

71

72

JB10

7478777675

79

818384

80

87

85

82

86

92

932491

89

88

94

959997

25C 2v

25D 2v

20D1>

20D1>

20D1>

Z44_TCLK<3>

Z44_TDEN<3>

Z44_TSER<3>

GND

GND

GND

35

3230333134

36

262725

29

28

101

100

102

98

96

37

104

105

106

107

103

25B 2v

20D1>

Z44_TSER<4>

GND

GND

39

38

40

42

41

43

110

109

111

108

112

113

25B 2v

20D1>

Z44_TDEN<4>

SIG_RETURN

GND

46474954525051

45

44

114

115

116

25B 2v

20C 6<>

20D1>

20A2>

20A 8<>

Z44_TCLK<4>

FPGAGC LK1 _NU

GND

GND

48

118

117

5358565557

123

120

119

122

121

125

124

0

GND

596260

129

128

127

126

XD<7..0>

3

1

5

GND

61

64

63

134

132

133

131

130

SIG_RETURN

STEVE SCULLY

DS33Z11/41/44DK01A0

GND

TITLE:

21B4>

7

ENGINEER:

3

RW_X

GND

GND

70

66

65

69

68

67

135

136

140

139

138

137

45

GND

P1 CONNECTOR (PLUG)

GND

20A1>

CS_ X5

21C4>

20A1>

GND

GND

GND

V3_ 3

GND

V3_ 3

GND

GND

GND

V3_ 3

GND

GND

GND

V3_ 3

GND

GND

V3_ 3

GND

20A1>

GND

GND

OSC 1_N U

2

V3_ 3

WR_X

CS_X3

CS_X2

6

4

21B4>

21C4>

21C4>

20A1>

56

Z44_RSER<3>

20D1>

Z44_RCLK<3>

Z44_RDEN<3>

20D1>

20D1>

20A1>

Z44_RSER<4>

20A 8<> 2 0A5<>

20D1>

20D1>

20D1>

20A1>

20A 5<>

Z44_RCLK<4>

Z44_RDEN<4>

XD<7..0>

25D 3v

25C 3v

25D 3v

20C6<>

20C 5<> 2 0B8<> 2 0B5 <> 20A8 <> 20 A5<>

25D 6v

25C 6v

20B 3<>

25C 5v

20C8<>

22B 6v

20A1

22B 7v

20D1>

20C3<21C4 >

21C7<

20D1>

20D1>

20A2>

20C 6<>20B 3<>

20C 5<> 2 0B8<> 2 0B5 <> 20A8 <> 20 A5<>

25B 6v

25B 6v

25B 5v

20D1>

20A1 20C8<>

20D1>

20A2>

20D1>

20C 5<> 2 0B8<> 2 0B5 <> 20A8 <> 20 A5<>

25B 3v

20B8<> 20B5<>

20C 8<> 2 0C5<>

20A1

20C 5<> 2 0B8<> 2 0B5 <> 20A8 <> 20 A5<>

20B5<> 20A8<>

21B4>

20A 3

6

20C 8<> 2 0C5<> 2 0B8 <>

20A1

25B 3v

25B 3v

XA<15..0>

20C 8<>

21C7<

21C7<

Z44_TCLK<1>

INT3

INT4

INT2

RESET_ B

GND

7

1

2

GND

3

7

6

5

4

Z44_TDEN<1>

Z44_TSER<1>

SIG_RETURN

GND

8

9

11

10

GND

GND

14

13

12

159016

172219

18

Z44_TSER<2>

SIG_RETURN

GND

20

24

23

21

Z44_TCLK<2>

Z44_TDEN<2>

262725

20A1 20C8<>

GND

GND

GND

35

3230333134

36

39

38

29

28

37

20A1 20C8<>

GND

GND

GND

40

41

42

44

43

46474954525051

48

45

21A5>

TDO _NU

TCK _NU

GND

5358565557

21A5>

3

1

5

GND

GND

10

8

6

GND

OSC 3_N U

21B4>

20A 8

GND

GND

MOTHERBOARD CONNECTORS FOR WAN R.C.

7

596260

61

65

64

63

70

66

69

68

67

PLUG

P2 CONNECTOR (PLUG)

DS33Z44 TOP LEVEL

JB14

73

71

72

VDD

7478777675

GND

GND

INT2

INT5

79

818384

80

82

GND

V3_ 3

87

85

86

GND

GND

92

93

91

89

88

GND

V3_ 3

20A1>

94

959997

96

GND

98

GND

104

105

101

100

103

102

GND

V3_ 3

20A1>

8

Z44_RDEN<2>

Z44INT

20D1>

21C7<

D

Z44_RSER<1>

25D 7v

20D1>

25C 7v

20D1>

25C 7v

20D1>

C C

Z44_RCLK<1>

Z44_RDEN<1>

Z44_RSER<2>

20C 8<> 2 0C5<> 2 0B8 <>

25B 7v

20D1>

20A1

20B 5<> 2 0A8<> 2 0A5 <>

Z44_RCLK<2>

20C 8<> 2 0C5<> 2 0B8 <>

20A 8<> 2 0A5<>

25B 7v

20D1>

25B 7v

20D1>

20A1

20B5<>

110

109

106

107

108

GND

114

111

115

118

117

116

112

113

GND

V3_ 3

GND

20A1>

20C 8<> 2 0C5<> 2 0B8 <>

20A 8<> 2 0A5<>

20A1

20B5<>

123

120

119

122

121

124

GND

GND

TMS _NU

TDI _NU

FPGAGC LK1 _NU

21A6>

21A6>

20A 3<>

129

128

127

126

125

GND

V3_ 3

20B 8<>

20A1>

402

20A 5<>

20A1

20C8<> 20C5<>

20B5<> 20A8<>

B B

134

132

135

133

136

140

139

138

131

130

GND

7

XA<15..0>

137

GND

OSC 4_N U

OSC 2_N U

V3_ 3

11

9

20A1

20C8<> 20C5<>

20B8<> 20B5<>

20A8<> 20A5<> 20A1>

8

A A

Page 18

D

1

09/16/2004

1

2/2(BLOCK)

21/71(TOTAL)

DATE:

2

PAGE:

2

STEVE SCULLY

DS33Z11/41/44DK01A0

3

TITLE:

ENGINEER:

3

20A 6 20 A8 4 2C7v

20A 3 20 A5 4 2B3v

4

42B 3v

42B 3v

20C 3<> 42A 4v

20A 5<>

20D3<

20A 5<> 42A 4v

CS_X1

CS_X2

20C 5<> 42A 4v

CS_X3

CS_X4

CS_X5

20C3< 38A5v

20C 7<>

20A 5<> 42B 3v

20A 3<> 42B 3v

20A 7<> 44A 7v20A 7<> 44A 7v20A 8<>20A 8<> 44A 7v

XD<7..0>

XA<15..0>

WR_X

RW_X

45

RESET_B

56

I1

CS_X1

CS_X2

CS_X3

CS_X5

CS_X4

RESET_B

WR

RW_X

XD<7..0>

XA<15..0>

TDO_NU

TCK_NU

TDI_NU

TMS_NU

44A 7v

TDO_NU

TCK_NU

TDI_NU

TMS_NU

6

HIERARCHICAL BLOCK

INT2

INT3

INT4

INT5

INT4

INT5

INT3

7

INT2

20C 7<>

20C 7<>20C8<>

38B7v

20C 8<>

20C 7<>

38B7v

39D4v

38B7v

8

PAGES 38-44

_motprocrescard_dn

RD_DUT

RD_DUT

A_DUT<11..0>

WR_DUT

D_DUT<7..0>

BIS0_DUT

BIS1_DUT

BTS_DUT

BTS_DUT

BIS1_DUT

WR_DUT

BIS0_DUT

7

20C1>

20C1>

20D3<

20D3<

42C 3v

42C 3v

20C1>

42C 3v

42C 3v

42C 3v

D_DUT<7..0>

A_DUT<11..0>

20D3<

20D3<

42D 5v

42A 5v42 A6v

8

D

C C

B B

A A

Page 19

D

10K

V3_3

RB74

10K

1

RB79

3

7

8

4

22C4<

20D3^

0

IN

V3_3

4

GND

WP*

VCC

HOLD*

SW04

2.7V

2

Y02

SI

SO

SCK

CS*

1

6

2

5

ZMISO

ZSPISCK

ZMOSI

22C 4<>

ZSPICS

22A6>

22C 4<>

22B 4<>

AT25160A_U

SP3T

SW08

ZADDR0

22D4<

ZADDR1

ADDR<9..0>

1

4

22C4<

2

09/16/2004

1

1/8(BLOCK)

22/71(TOTAL)

4

SP3T

SW18

SP3T

DATE:

PAGE:

ZADDR2

2

22C4<

STEVE SCULLY

DS33Z11/41/44DK01A0

3

TITLE:

V3_3

22B1<

20D 3^

IN

ADDR<9..0>

22A 2<>

22B 2<>

22B 2<>

4

ZADDR0

ZADDR1

3

ZADDR2

7

8

645

0

9

ZMOSI

3

1

2

ZMISO

ZSPISCK

6

5

4

20D 3^

DAT<7..0>

IO

7

J32

TMS _NU

TCK _NU

TDI _NU

TDO _NU

10

65

4

2

1

8

6108

412

3

7

5

9

3

7

9

ENGINEER:

3

45

CONN_10P

A7

A6

A1

A<0>

B2

B1

A<1>

C2

A2

A<2>

A<4>

A<3>

C3

A4

B3

A3

A<5>

A<6>

A<8>

A<7>

56

A5

B4

A<9>

22C2<

D<0>/MOSI

B5

D<3>

22C2<

22C2>

D<1>/MISO

D<2>/SPICK

C5

B7

B6

D<4>

C6

D<7>

D<5>

D<6>

CKPHA

F6

SCAN MODE

SCAN ENABLE

CKPHA

E8

SCANMOD

E7

28B4<

28C4<

28B4<

JTCLK

JTMS

JTDO

JTDI

JTRST

22D6<

22D6<

22D6<

22D6<

22D 6<>

SCANEN

RMIIMIIS

22A5<>

22A5<>

22A5<>

22A5<>

22A5<>

JTRST

E6

JTCLK

D4

JTDO

E5

JTDI

E4

JTMS

F7

JTRST

JTCLK

JTDO

JTDI

JTAG

U22

JTMS

DS33Z44_U1

MII/RMII

SDRAM CONTROL

MICRO PORT/SPI MASTER PORT

C4

DCEDTES

MODEC<1>

MODEC<0>

HWMODE

RST*

WR*/RW*

RD*/DS*

SPI_CS*

CS*

INT*

RMIIMIIS

A15

DCEDTES

D7

MODEC1

D6

MODEC0

D5

HWMODE

D8

RESET_B

E2

WR

E1

RD

E13

ZSPICS

D1

CS

D3

INT

OUT

OUT

OUT

OUT

28C4<

28D2<

28D4<

20C2^

28D2<

20C2^

28D4<

20C2^

IN

20D3^

IN

20D3^

22C2<

IN

20D3^

20D2^ 22A6<>

20D 2^

22A7>

6

INT

11

NC7SZ8 6_U

BUFFER

MDC

REF_CLKO

REF_CLK

MDIO

SBA<0>

SDMASK<0>

SBA<1>

SDMASK<1>

SDMASK<3>

SDMASK<2>

SYSCLKI

SDCLKO

SDCS*

SWE*

SCAS*

SRAS*

7

R8

C15

TPB02

1

RB181

8

REF_CLK

28A4<

F10

B15

F11

TPB01

TP34

11

R99

RB161

MDC

MDIO

27B6>

27B6>

R9

RB246

RB230

SD_BA1

SD_BA0

24B4<

24B4<

M7

T8

T11

R147

RB239

R166

SD_DQM1

SD_DQM0

SD_DQM2

24C4<

24C4<

24C4<

P8

N11

RB217

SD_DQM3

24C4<

T7

RB226

R158

SD_CS

SD_CLKO

24C4<

24C3<

N7

T15

RB219

SD_CLKI

28D5<

R7

P15

RB282

R163

SD_RAS

SD_CAS

SD_WE

24C4<

24C4<

24C4<

UNMARKED RESISTORS ARE 30 OHM

4

UXB07

7

22

RED

DS42

330

RB332

1

8

V3_3

REF_CLKO

27B3> 26B6> 26B3>

27B3> 26B6> 26B3>

D

C C

B B

A A

Page 20

D

1

09/16/2004

1

2/8(BLOCK)

23/71(TOTAL)

DATE:

2

3

1

2

0

RB267

RB249

R173

4

RB280

RB268

RB265

7

9

8

6

5

R169

RB281

RB248

RB241

11

10

121413

RB233

RB247

RB242

RB213

RB240

16

17

19

15

RB279

RB197

18

20

R143

RB189

RB198

RB202

R136

23

22

21

R13 1

RB204

RB188

26

25

24

RB199

RB203

SD_DQ<31..0>

24D 7

PAGE:

2

STEVE SCULLY

DS33Z11/41/44DK01A0

N15

P13

P14

R14

R13

T14

T12

T13

P12

N12

R12

P4

N5

N4

M5

M3

P7

R6

T6

T5

R5

T4

P5

R4

3

M6N6P6

TITLE:

ENGINEER:

3

SDATA<0>

SDATA<1>

G12

F13

E14

K12

M14

L13

N3

4

P2

A14

V1_8ZCHIP

M4

F4

29A 4<>

E3

D2

C1

29B6< 23B4<

H10

H9

56

V3_3

H8

H7

H6

H5

H4

H3

G10

G9

G8

G7

1.8VDD13

1.8VDD12

1.8VDD11

1.8VDD10

1.8VDD9

1.8VDD8

1.8VDD7

1.8VDD6

1.8VDD5

1.8VDD4

1.8VDD3

1.8VDD2

1.8VDD1

V3_3

1.8VDD0

3.3VDD15

3.3VDD14

3.3VDD13

3.3VDD12

3.3VDD11

3.3VDD10

3.3VDD9

3.3VDD8

3.3VDD7

3.3VDD6

3.3VDD5

3.3VDD4

10UF

SDATA<2>

SDATA<3>

SDATA<4>

SDATA<5>

SDATA<6>

SDATA<7>

SDATA<9>

SDATA<8>

SDATA<10>

SDATA<11>

SDATA<12>

SDATA<13>

SDATA<14>

SDATA<15>

SDATA<16>

SDATA<17>

SDATA<18>

SDATA<19>

SDATA<20>

SDATA<21>

SDATA<22>

SDATA<23>

SDATA<24>

SDATA<25>

CB115

10UF

CB202

10UF

CB495

10UF

CB361

10UF

CB492

10UF

CB402

10UF

CB446

10UF

CB335

10UF

CB469

0.1UF

1

1

1

1

1

1

1

1

1

1

1

1

2

CB421

0.1UF

2

CB301

0.1UF

2

CB423

0.1UF

2

CB323

0.1UF

2

CB298

0.1UF

2

CB315

0.1UF

2

CB312

0.1UF

2

CB47

0.1UF

2

CB240

0.1UF

2

C184

0.1UF

2

CB289

470UF

2

CB26

I182

NA

DS33Z44

U22

PWR/GND

DS33Z44_U1

SDRAM CONTROL

V1_8ZCHIP

29A 4<>

29B6< 23D4<

470UF

1

1

1

1

1

1

1

1

1

1

1

1

1

2

CB211

0.1UF

2

CB387

0.1UF

2

CB247

0.1UF

2

CB255

0.1UF

2

CB256

0.1UF

2

CB178

0.1UF

2

CB246

0.1UF

2

CB227

0.1UF

2

CB177

0.1UF

2

CB386

0.1UF

2

C102

0.1UF

2

CB162

0.1UF

2

CB400

10UF

C90

10UF

CB408

10UF

CB417

10UF

C101

10UF

C88

10UF

C89

10UF

CB381

SDATA<26>

UNMARKED RESISTORS ARE 30 OHM

SDATA<27>

N13

SDATA<28>

M13

SDATA<29>

L12

SDATA<30>

M12

SDATA<31>

M11

VSS24

L9

VSS23

L8

VSS22

L7

VSS21

L6

VSS20

L5

VSS19

L4

VSS18

L3

VSS17

K10

VSS16

K9

VSS15

K8

VSS14

K7

VSS13

K6

VSS12

M10

VSS11

L10

VSS10

K4

VSS9

K3

VSS8

J10

VSS7

J9

VSS6

J8

VSS5

J7

VSS4

K5

RB212

RB191

RB211

RB210

RB218

27

28

29

31

45

UNMARKED RESISTORS ARE 30 OHMS

6

3.3VDD3

3.3VDD2

3.3VDD1

3.3VDD0

SDA<0>

G3

G4

G5

G6

T10

R10

R150

RB196

7

1

0

SDA<3>

SDA<4>

SDA<5>

SDA<6>

SDA<7>

SDA<8>

SDA<10>

SDA<11>

NC1

NC2

NC3

SDA<1>

SDA<2>

M8

N9

M9

R11

P11

RB190

RB223

RB216

N10

RB205

RB224

RB231

SDA<9>

P9

N8

P10

RB232

RB225

RB266

F3

T9

TP51

1111

R154

NC4

G1

F9

F8

TP52

TP50

TP49

VSS2

VSS0

J4

J3

VSS3

VSS1

J6

J5

7

3

4

2

7

6

5

10

11

9

8

J53

J48

B

A

BLACK

1

2

RED

CONN_B ANANA_ 2P

B

A

1

CONN_B ANANA_ 2P

2

V3_3

SD_A<11..0>

8

8

24A3>

D

C C

B B

A A

Page 21

D

1

09/16/2004

1

3/8(BLOCK)

24/71(TOTAL)

DATE:

2

PAGE:

2

STEVE SCULLY

DS33Z11/41/44DK01A0

3

V3_3

23C 8

TITLE:

ENGINEER:

3

22B8<

22C8<

22C8<

22C8<

22C8<

22B8<

22B8<

22B8<

22C8<

22C8<

22C8<

SD_A<11..0>

SD_CLKO

FROM Z11 SYSCLKO

SD_BA0

SD_DQM3

SD_DQM2

SD_DQM1

SD_DQM0

SD_RAS

SD_CAS

SD_WE

SD_CS

18

4

682067

CLK

V3_3

3

9

35

41

49

55

56

75

81

VDDQ1

VDDQ2

VDDQ3

VDDQ4

VDDQ5

VDDQ6

VDDQ7

VDDQ8

17

CKE

CS*

WE*

CAS*

16

19

RAS*

71

28

59

22

BA<0>

DQM<3>

DQM<2>

DQM<1>

DQM<0>

0

SD_BA1

23

25

A<0>

BA<1>

1

266027

A<1>

3

4

2

616362

A<4>

A<2>

A<3>

7

9

8

6

5

A<7>

A<5>

A<6>

656466

A<8>

10

11

24

21

A<9>

A<11>

A<10>

VSSQ1

6

VSSQ2

12

VSSQ3

32

VSSQ4

38

VSSQ5

46

VSSQ6

52

VSSQ7

78

VSSQ8

84

45

1

15

29

43

0

1

SD_DQ<31..0>

7

23A 2

2

4

VDD1

VDD2

VDD3

VDD4

DQ<0>

DQ<1>

DQ<3>

DQ<2>

DQ<4>

DQ<5>

7

8

5

2

10

11

3

6

5

4

DQ<8>

DQ<7>

DQ<6>

13

74

7

8

DQ<11>

DQ<10>

DQ<9>

76

77

79

11

10

9

DQ<12>

808382

12

UB09

MT48LC4M32B2_TSOP_U

DQ<15>

DQ<13>

DQ<14>

85

15

14

13

SYNCHRONOUS DRAM

MT48LC4M32B2 - 1 MEG X 32 X 4 BANKS

DQ<28>

DQ<27>

DQ<26>

DQ<24>

DQ<22>

DQ<21>

DQ<19>

DQ<20>

DQ<18>

DQ<17>

DQ<16>

31

33

343736

18

17

16

39

40

19

22

21

20

DQ<25>

DQ<23>

42

474548

50

51

28

27

26

25

24

23

VSS1

44

VSS2

58

VSS3

72

VSS4

86

DQ<31>

DQ<30>

DQ<29>

31

56

30

54

6

53

29

7

8

D

C C

B B

A A

8

Page 22

D

1

20D 2^

20D 2^

27D8<

27D8<

27D8<

IN

OUT

TXD0<3>

TSER<3>

30

RB311

TXD1<3>30TXD2<3>30TXD3<3>30TX_EN<3>

30

27D8<

30

TDEN<3>

R97

R123

RB187

RB169

RB170

27D5>

27D8<

27C8<26D5>

29C 8<>

29C4<

29C4<

RX_CLK<3>

TX_CLK<3>

H10S<3>

QOVF<3>

AFCS<3>

20D 2^

20D 2^

27D4<

27D4<

27D4<

IN

OUT

TXD0<4>

TSER<4>

30

RB320

TXD1<4>30TXD2<4>30TXD3<4>30TX_EN<4>

30

27D4<

30

TDEN<4>

R126

RB171

RB167

RB168

R124

27D2>

27D4<

27C4<

29C 8<>

29A4<

29A4<

RX_CLK<4>

TX_CLK<4>

H10S<4>

QOVF<4>

AFCS<4>

09/16/2004

DATE:

2

H13

M2

P3

M1

F15

TSER

TXD0

TDEN/TBSYNC

H14

G14

TXD1

TXD3

TXD2

H16

G16

E15

TX_EN

RX_CLK

TX_CLK

J11

F12

B8

H10S

QOVF

AFCS

R2R3R1

TSER

TDEN/TBSYNC

D16

B16

C16

TXD1

TXD0

TXD2

A16

A13

G13

E16

TXD3

TX_EN

RX_CLK

TX_CLK

C12

B12

A8

H10S

QOVF

AFCS

1

4/8(BLOCK)

25/71(TOTAL)

PAGE:

2

STEVE SCULLY

DS33Z11/41/44DK01A0

PORT

3

U22

DS33Z44_U1

U22

RSER

RCLKI TCLKI

RDEN/RBSYNC

RXD0

RXD1

RXDV

RX_CRS/CRS_DV

RX_ERR

COL_DET

RXD2

RXD3

FULLDS

DS33Z44_U1

PORT

TITLE:

RSER

RCLKI TCLKI

RDEN/RBSYNC

RXD0

RXD1

RXDV

RX_CRS/CRS_DV

RX_ERR

COL_DET

RXD2

RXD3

FULLDS

ENGINEER:

3

T1

T2

N1

P1

N2

RCLKI<3> TCLKI<3>

RSER<3>

4

56

REV01A0 SCHEMATIC SYMBOL (AND PCB) FOR Z44 HAD ERRORS

TXD/RXD PINS FOR PHY CONNECTION WERE INCORRECT

CORRECT PINOUT SHOWN AT BO TT OM OF PAGE

PORT3 PIN N2

IN

IN

20D 2^

20D 2^ 20D 2^

IN

30

RB335

J14

G15

RDEN<3>

RXD0<3>

RXD1<3>

IN

27D5>

27D5>

20D 2^

20D 2^

OUT

20D 2^

26D8<

IO

TXD0<1>

TSER<1>

30

R105

R122

TDEN<1>

K11

J12

J13

RXD2<3>

27D5>

26D8<

TXD1<1>

30

R96

M15

RXDV<3>

RXD3<3>

RX_CRS<3>

27C5>

27C5>

27D5>

26C8<

26D8<

26D8<

TX_EN<1>

TXD3<1>

TXD2<1>

30

30

R115

R98

H11

G11

RX_ERR<3>

H12

COL_DET<3>

FULLDS<3>

PORT4 PIN T3

27C5>

27C5>

29D4<

29D2<

29C2<

29D 8<>

26D8<

26D5>

H10S<1>

AFCS<1>

QOVF<1>

30

RX_CLK<1>

TX_CLK<1>

T3

RCLKI<4> TCLKI<4>

INIOIN

20D 2^ 20D 2^

A12

F16

D14

F14

D15

C14

B14

C13

B13

RSER<4>

RDEN<4>

RXD0<4>

RXD1<4>

RXDV<4>

RXD2<4>

RXD3<4>

RX_CRS<4>

RX_ERR<4>

COL_DET<4>

FULLDS<4>

45

IN

27D2>

27D2>

27D2>

27D2>

27C2>

27C2>

27C2>

27C2>

29B4<

20D 2^

20D 2^

26D2>

20D 2^

26D5<

26D5<

26D5<

20D 2^

20D 2^

OUT

IN

IO

TXD0<2>

TSER<2>

30

TCLKI<2>

RB339

30

RB164

TDEN<2>

RB165

TXD3<2>

TXD2<2>

TXD1<2>

30

30

RB121

RB180

26D5<

26C5<

26D5<

TX_CLK<2>

TX_EN<2>

30

30

RB179

29D 8<>

29A2<

29B2<

RX_CLK<2>

H10S<2>

QOVF<2>

AFCS<2>

TP65

TP64

TP63

C10

B10

B9

F2

F1

TSER

C9

F5

TXD1

TXD0

TDEN/TBSYNC

E10D9E9

TXD3

TXD2

TX_EN

C7A9A11

H10S

QOVF

AFCS

RX_CLK

TX_CLK

PORT

DS33Z44_U1

7

U22

RCLKI TCLKI

RDEN/RBSYNC

RXD0

RXD1

RSER

H2

H1

G2

TP57

B11

TP59

TP58

RXD2

E11

D11

C11

RX_CRS/CRS_DV

RX_ERR

COL_DET

RXD3

RXDV

E12

D12

D10

FULLDS

A10

D13

PORT1 PIN G2

RXD0<1>

RXD1<1>

8

RCLKI<1> TCLKI<1>

RDEN<1>

RSER<1>

26D5>

26D5>

INININ

RXDV<1>

RXD2<1>

26D5>

RX_ERR<1>

26C5>

26C5>

26C5>

RX_CRS<1>

RXD3<1>

FULLDS<1>

COL_DET<1>

26C5>

29D2<

U22

DS33Z44_U1

PORT2 PIN L2

TP61

TP60

TP62

L11

L16

L14

L15

R15

J2K2J1

TSER

R16

TXD1

TXD0

TXD2

TDEN/TBSYNC

M16

N14

TXD3

TX_EN

RX_CLK

TX_CLK

PORT

RCLKI TCLKI

RDEN/RBSYNC

RXD0

RXD1

RSER

L1

K1

L2

TP54

TP56

TP55

RCLKI<2>

RSER<2>

RDEN<2>

INIOIN

IN

20D 2^

20D 2^

20D 2^

RXD2

K16

H15

K14

K13

RXD0<2>

RXD1<2>

RXD2<2>

RXD3<2>

26D2>

26D2>

26D2>

RX_CRS/CRS_DV

RXD3

26D2>

RX_ERR

RXDV

K15

T16

N16

RXDV<2>

RX_CRS<2>

RX_ERR<2>

26C2>

26C2>

26C2>

J16

C8

H10S

QOVF

AFCS

PORT1 RXD0--RXD3 B11 ,C11,D11,E11

PORT4 RXD0--RXD3 B13,C13,B14,C14

PORT3 RXD0--RXD3 G15,J14,J13,J12

PORT2 RXD0--RXD3 K13,K14,H15,K16

COL_DET

FULLDS

J15

P16

6

7

FULLDS<2>

COL_DET<2>

29B2<

26C2>

8

PORT4 TXD0--TXD3 B16,C16,D16,E16

PORT3 TXD0--TXD3 F15,G14,H13,H14

PORT2 TXD0--TXD3 R15,R16,L15,N14

20D 2^

20D 2^ 20D 2^

20D 2^

D

C C

B B

A A

PORT1 TXD0--TXD3 B9, C9, D9, E9

Page 23

D

1

32A7v

32A7v25A8<

32A7v25A8<

32A7v25A8<

32A7v25B8<

32A7v25A8<

25A 5<>

32A7v25A8<

32A7v25A8<

32A7v25A8<

32C7v30C7v26B7<22A6<27C7>27C3>

0.1UF

1

1

2

C04

10UF

CB02

10UF

CB01

10UF

CB03

CHASSI S

1

09/16/2004

DATE:

1

5/8(BLOCK)

26/71(TOTAL)

PAGE:

CHASSIS GND FOR PHY

2

RX_CLK<2>

RX_ERR<2>

RXD3<2>

RXD1<2>

RXD0<2>

RXD2<2>

RXD3

RXD2

RXD1

RXD0

RX_CRS<2>

RXDV<2>

COL_DET<2>

RXDV

RX_CLK

RX_ERR

RX_CRS

COL_DET

MII_CLK

32C7v

30C5v

28A4< 30C5v32C5v22C8<27B6>27B3>26B6>

32C5v22C8<27B6>

20C 3^

27B3>26B6>

L01

100O100MZH

2

LB02

100O100MZH

2

V3_3

MII_CLK<2>

2

STEVE SCULLY

DS33Z11/41/44DK01A0

MDC

MDIO

3

MDC

MDIO

TITLE:

ENGINEER:

3

RESET_B

RESET_B

V3_3

_mii_wan_dn

HIERARCHICAL BLOCKHIERARCHICAL BLOCK

RB33

R22

TX_CLK

TXD0

TXD1

TXD3

TXD2

TX_EN

LED_DPLX_ADD0

LED_COL_ADD1

LED_RX_ADD4

LED_TX_ADD3

LED_GDLINK_ADD2

R18

5.1K

RB34

5.1K

330

5.1K

2

DS02

1

4

LED_DPLX_A0<2>

TXD1<2>

TXD0<2>

32A5v 25B5<

TXD3<2>

TXD2<2>

32A5v 25A5<

32A5v 25A5<

TX_CLK<2>

TX_EN<2>

25A 5<>

32A5v 25A5<

32A5v 25A5<

32A5v

LED_GDLINK_A2< 2>

LED_DPLX_A0<2>

LED_COL_A1<2>

LED_RX_A4<2>

LED_TX_A3<2>

26A 4<>

26A 4<>

26A 4<>

32C5v 26C5<

LED_COL_A1<2>

LED_GDLINK_A2< 2>

32C5v 26C5<

32C5v 26C5<

RB14

330

RB15

5.1K

AMBER

2

DS01

1

RB42

330

R14

RED

5.1K

2

DS05

1

45

LED_TX_A3<2>

32C5v 26C5<

56

32C5v 26B4<

32C5v 26B4<

32C5v

32C5v

32C5v

30A7v

30A7v25C8<

30A7v25C8<

30A7v25C8<

30A7v25C8<

30A7v25C8<

30A7v25C8<

25C 5<>

30A7v25C8<

30A7v

25C8<

30C5v32C5v22C8<27B6>

COL_DET<1>

RXD0<1>

RXD1<1>

RXD2<1>

RXD3<1>

RX_CLK<1>

RXD3

RXD2

RXD1

RXD0

RX_CLK

7

_mii_wan_dn

RXDV<1>

RX_CRS<1>

RX_ERR<1>

27B3>26B3> 30C5v32C5v22C8<27B6>27B3>26B3>30C7v28A4<

6

RXDV

RX_ERR

RX_CRS

COL_DET

MII_CLK

MDC

MDIO

RESET_B

MII_CLK<1>

MDC

MDIO

IN

RESET_B

V3_3

7

PAGES 30-31 PAGES 32-33

RB58

RB75

RB80

5.1K

5.1K

TX_CLK

TXD0

TXD1

TXD3

TXD2

TX_EN

LED_DPLX_ADD0

LED_COL_ADD1

LED_RX_ADD4

LED_TX_ADD3

LED_GDLINK_ADD2

R19

330

5.1K

2

GREEN GREEN

DS09

1

RB49

330

R13

5.1K

AMBER

2

DS07

1

RB7 1

330

R23

5.1K

2

RED

DS13

1

LED_DPLX_A0<1>

LED_COL_A1<1>

8

TXD2<1>

TXD3<1>

TX_CLK<1>

TXD1<1>

TXD0<1>

30A5v 25C5<

30A5v 25C5<

30A5v 25C5<

30A5v 25C5<

D

TX_EN<1>

30C5v 26C8<

30C5v 26C8<

25C 5<>

LED_DPLX_A0<1>

30A5v 25C5<

30A5v

LED_TX_A3<1>

LED_COL_A1<1>

LED_GDLINK_A2< 1>

LED_RX_A4<1>

C C

B B

LED_GDLINK_A2< 1>

30C5v 26C8<

A A

LED_TX_A3<1>

LED_RX_A4<1> LED_RX_A4<2>

8

30C5v 26C8<

30C5v 26C8< 32C5v 26C5<

Page 24

D

1

09/16/2004

1

6/8(BLOCK)

27/71(TOTAL)

DATE:

34A7v

34A7v25 A4<

34A7v25B4<

34A7v25B4<

34A7v25A4<

34A7v25A4<

25A 1<>

2

RXD0<4>

RXD1<4>

RXD2<4>

RXD3<4>

RX_CLK<4>

RX_CRS<4>

RXD3

RXD2

RXD1

RXD0

RX_CLK

RX_CRS

34A7v25 A4<

34A7v25 A4<

34A7v25A4<

RXDV<4>

RX_ERR<4>

COL_DET<4>

RXDV

RX_ERR

COL_DET

MII_CLK

34C7v36C7 v26B7<22A6<

34C7v28 A4< 36C5v34C5v22 C8<27B6>26B6>26B3>

36C5v34C5v22C8<27B6>

20C 3^

27C7>26B3>

26B6>26B3>

MII_CLK<4>

PAGE:

2

STEVE SCULLY

MDC

MDIO

3

RESET_B

RESET_B

MDC

MDIO

DS33Z11/41/44DK01A0

TITLE:

ENGINEER:

3

V3_3

_mii_wan_dn

HIERARCHICAL BLOCK

TXD0

TXD1

TXD2

PAGES 34-35

R24

330

R30

R29

5.1K

5.1K

TX_CLK

TXD3

TX_EN

LED_DPLX_ADD0

LED_COL_ADD1

LED_RX_ADD4

LED_TX_ADD3

LED_GDLINK_ADD2

1

RB73

5.1K

2

DS14

GREEN

RB59

330

R20

5.1K

AMBER

2

DS10

1

RB53

330

R15

5.1K

RED

2

DS08

1

4

LED_DPLX_A0<4>

LED_COL_A1<4>

TXD2<4>

TXD3<4>

TX_CLK<4>

TXD1<4>

TXD0<4>

34A5v 25A1<

34A5v 25A1<

34A5v 25B1<

34A5v 25B1<

56

36A7v25C4<

36A7v25C4<

36A7v25C4<

36A7v25C4<

RXD0<3>

RXD1<3>

RXD3<3>

RXD2<3>

TX_EN<4>

25A 1<>

LED_DPLX_A0<4>

34A5v 25A1<

34A5v

34C5v 27B4<

36A7v

36A7v25C4<

25C 1<>

RX_CRS<3>

RX_CLK<3>

36A7v25 C4<

36A7v25 C4<

36A7v25C4<

RX_ERR<3>

COL_DET<3>

RXDV<3>

LED_TX_A3<4>

LED_COL_A1<4>

LED_GDLINK_A2< 4>

LED_RX_A4<4>

27A 4<>

27A 4<>

27A 4<>

34C5v 27B4<

34C5v

34C5v

34C5v

36C7v28A4<

36C5v34C5v22C8<27B3>

34C5v 27C5<

34C5v 27C5<

LED_GDLINK_A2< 4>

34C5v 27C5<

LED_TX_A3<4>

34C5v 27C5<

34C5v 27C5<

45

26B6>26B3> 36C5v34C5v22C8<27B3>26B6>26B3>

RXD3

RXD2

RXD1

RXD0

RX_CLK

RX_CRS

7

HIERARCHICAL BLOCK

TXD0

TXD1

_mii_wan_dn

PAGES 36-37

TXD3

TXD2

TX_CLK

8

TXD2<3>

TXD3<3>

TXD1<3>

TXD0<3>

36A5v 25C1<

36A5v 25C1<

36A5v 25C1<

36A5v 25C1<

TX_EN<3>

TX_CLK<3>

25C 1<>

36A5v 25C1<

36A5v

D

RXDV

RX_ERR

TX_EN

COL_DET

MII_CLK

MDC

MDIO

RESET_B

LED_RX_ADD4

LED_DPLX_ADD0

LED_COL_ADD1

LED_TX_ADD3

LED_GDLINK_ADD2

RESET_B

MII_CLK<3>

MDC

MDIO

V3_3

V3_3

RB40

RB82

RB5 1

5.1K

5.1K

LED_DPLX_A0<3>

LED_COL_A1<3>

RB32

330

5.1K

2

GREEN

DS03

1

RB77

330

RB62

5.1K

2

AMBER

DS12

1

LED_TX_A3<3>

RB43

330

RB36

5.1K

RED

2

DS04

1

LED_RX_A4<3> LED_RX_A4<4>

LED_GDLINK_A2< 3>

36C5v 27C8<

36C5v 27C8<

36C5v 27C8<

LED_TX_A3<3>

LED_COL_A1<3>

LED_DPLX_A0<3>

36C5v

36C5v

27B8<

27B8<

LED_RX_A4<3>

LED_GDLINK_A2< 3>

C C

B B

36C5v 27C8<

A A

36C5v 27C8<

6

7

8

Page 25

D

V3_3

1

MODEC0TRI

3

1

4

DCEDTESTRI

3

1

4

09/16/2004

1

7/8(BLOCK)

28/71(TOTAL)

DATE:

SW02

2

2

RB06

2.0K

1

2

MODEC0

22A6>

20C 2^

SW09

SP3T

SP3T

2

2

RB56

2.0K

1

(HELPS PCB NETLIST)

SIGNAME_TRI DOES NOT

DCEDTES

22A6<

CONNECT ANYWHERE

PAGE:

2

STEVE SCULLY

DS33Z11/41/44DK01A0

V3_3

3

HWMODETRI

3

1

4

MODEC1TRI

3

1

4

RMIIMIISTRI

3

1

4

SCANMODTRI

3

1

4

SCANENTRI

3

1

4

CKPHATRI

3

1

4

TITLE:

ENGINEER:

3

SW21

2

2

RB98

2.0K

1

4

HWMODE

22A6>

20C 2^

56

SW01

SP3T

2

2

RB02

2.0K

1

MODEC1

22A6>

20C 2^

22B8<

SW05

SP3T

2

2

RB39

2.0K

1

RMIIMIIS

22A6<

SW19

SP3T

SP3T

2

2

RB76

2.0K

1

SW20

2

2

RB83

2.0K

1

SCANEN

SCANMOD

22A5<

22A5<

SW03

SP3T

RB08

CKPHA

SP3T

2

2

26B6>

27B6>

26B2>

27B2>

2.0K

22D 8<>

1

MII_CLK<3>

MII_CLK<1>

MII_CLK<2>

MII_CLK<4>

REF_CLK

45

30

30

30

30

30

22A5<

R25

R17

R100

RB6 1

R116

V3_3

8

VCC

OSC

Y01

1

GND OUT

25.000MHZ_3.3V

1

4 5

SD_CLKI

3030

R11 1

4

UXB03

BUFFER

NC7SZ8 6_U

1

OSC100MHZ

V3_3

R112

6

8

7

VCC

100.000MHZ_3.3V

OSC

Y05

1

GND OUT

7

1

4 5

GND

V3_ 3

8

V3_3

D

C C

B B

A A

8

Page 26

D

V3_3

1

2

FULLDSTRI<1>

3

1

4

SW30

SP3T

2

2

2.0K

RB341

1

AFCSTRI<1>

3

1

4

SW31

SP3T

2

2

2.0K

RB338

1

AFCS<1>

H10STRI<1>

V3_3

3

1

4

FULLDSTRI<2>

3

1

4

SW29

2

2

SP3T

SW35

SP3T

2

2.0K

RB340

2

AFCSTRI<2>

3

1

4

SW34

SP3T

2

2

H10STRI<2>

3

1

4

SW33

SP3T

2

2

09/16/2004

DATE:

1

8/8(BLOCK)

29/71(TOTAL)

PAGE:

1

2.0K

RB348

1

2.0K

RB347

1

2.0K

RB346

1

2

H10S<1>

FULLDS<1>

25B5<

25C8<

25C5<

FULLDS<2>

25A8<

AFCS<2>

25A5<

H10S<2>

25A5<

STEVE SCULLY

DS33Z11/41/44DK01A0

3

4

V3_3

FULLDSTRI<3>

3

1

4

SW38

SP3T

2

2.0K

RB353

FULLDS<3>

25C4<

AFCSTRI<3>

3

1

4

SW37

SP3T

2

2.0K

RB351

AFCS<3>

25C1<

H10STRI<3>

V3_3

3

1

4

FULLDSTRI<4>

3

1

4

SW36

2

SP3T

SW40

SP3T

2

2.0K

RB352

2

2.0K

RB363

1

AFCSTRI<4>

3

1

4

SW41

SP3T

2

2

2.0K

RB362

1

H10STRI<4>

3

1

4

SW39

SP3T

2

2

2.0K

RB361

1

29B6<23D4<23B4<

TITLE:

ENGINEER:

3

45

H10S<3>

AFCS<4>

25C1<

FULLDS<4>

25A1<

25A4<

H10S<4>

25A1<

56

V1_8ZCHIP

1UF

2

0.1UF

V3_3

MAX1792

2

2

2

8

OUT

IN

1

1

V1_8ZCHIP

1

29A 4<>

1

1

1

23D4< 23B4<

1

1

1

RED

2

1

DS45

7

RB344

330

RED

2

1

DS46

RB350

330

RED

2

1

DS47

RB354

330

RED

2

1

DS48

RB360

330

1

1

1

TP67

TP68

TP73

TP76

V3_3

1

1

1

1

1

QOVF<1>

8

25C5>

QOVF<2>

25A5>

QOVF<3>

25C1>

QOVF<4>

1

25A1>

1

2

CB368

0.1UF

2

CB380

0.1UF

2

CB261

0.1UF

2

CB366

0.1UF

2

CB231

0.1UF

2

CB367

0.1UF

2

CB248

0.1UF

2

CB228

0.1UF

2

CB254

0.1UF

2

CB15

0.1UF

2

CB279

0.1UF

2

CB411

0.1UF

2

CB439

0.1UF

2

CB241

0.1UF

2

CB358

0.1UF

2

CB185

0.1UF

2

C213

0.1UF

2

C214

U11

1

CB176

1UF

1

C80

1UF

1

C51

10UF

6

1

CB133

7

5

6

OUT

SET

GND

7

IN

SHDN

RST

3

4

2

1UF

1

1

1

2

2

CB184

1UF

2

CB13

1UF

2

8

C64

1UF

1

CB468

D

C C

B B

A A

Page 27

D

1

1

1

AN_V3_3

1

1

L08

100O100MZH

2

1

2

1

1

1

1

V3_3

1

1

0.1UF

2

CB73

0.1UF

2

CB81

10UF

2

C25

10UF

2

CB10

10UF

CB87

10UF

CB292

0.1UF

2

CB40

0.1UF

2

CB72

0.1UF

2

C18

0.1UF

2

CB291

0.1UF

2

CB284

0.1UF

2

CB221

3

09/16/2004

DATE:

DS33Z11/41/44DK01A0

TITLE:

1

1/2(BLOCK)

30/71(TOTAL)

PAGE:

2

STEVE SCULLY

ENGINEER:

3

V3_3

4

LEDS NEED TO BE ATTACHED

OUTSIDE OF MODUL E DUE TO

STRAP ADAPTING OPTION OF DP83847

AN_EN

IO

IO

IO

IO

IO

26C 6^

IN

IO

AN1

JP12

3

3

3

1

2

JP07

1

2

JP01

1

2

31C8<

26D 8^

31C8<

31C8<

31C8<

V3_3

26D 8^

IN

26D 8^

26D 8^

IN

IN

IN

45

AN0

MDC

RB09

RB30

RB37

5.1K

5.1K

LED_TX_ADD3

MDIO

56

30

R10 1

24

25

LED_COL_ADD1

LED_DPLX_ADD0

22

23

LED_RX_ADD4

TP02

1

LED_GDLINK_ADD2

18

19

21

20

5.1K

15

16

17

J15

MDC

MDIO

V3_3

63

59

57

AN_V3_3

14

56

28

34

13

12

9

8

5

4

VDD3

VDD2

VDD1

LED_COL/PHYAD1

LED_DPLX/PHYAD0

LED_GDLNK/PHYAD2

LED_SPEED

LED_RX/PHYAD4

LED_TX/PHYAD3

VDD/ANA_VDD

VDD/IO_VDD2

VDD/IO_VDD1

RESERVED9

RESERVED8

U02

CONTROL

RESERVED7

RESERVED6

DP83847_U1

RESERVED5

RESERVED4

RESERVED3

7

AN_1

AN_0

AN_EN

GND5

65

GND4

64

GND3

62

GND2

60

GND1

58

RESERVED18

61

RESERVED17

55

RESERVED16

54

RESERVED15

53

RESERVED14

52

RESERVED13

51

RESERVED12

50

TXD2

TXD3

4

2

412

3

3

1

TX_CLK

OUT

31C5<

31C4<

26D 8^

26C 6^

OUT

OUT

RXDV

RX_CRS

4

2

412

65

6108

5

31B5<

26C 6^

OUT

COL_DET

65

6108

TXD0

TXD1

10

8

7

9

7

9

CONN_10P

TX_EN

IN

26C 6^

31C8<

26C 8^

31C6<>

OUT

OUT

RX_CLK

RX_ERR

10

8

6

7

3

7

5

X1

464248

X2C1RESET*

RESERVED11

RESERVED10

44

47

RESERVED1

RESERVED2

1

2

RBIAS

3

49

J16

3

1

9

7

9

CONN_10P

RBIAS

RXD0

RXD1

RXD2

MII_CLK

C1PIN

0.1UF

1

8

COMPONETS FOR

C1 AND RBIAS M UST

BE PLACED CLO SE TO PI N

10UF

1

R06

2

CB104

2

C41

D

RESET_B

10.0K

IN

IN

26C 6^

26C 7^

OUT

OUT

26D 6^

V3_3

31B8<

26D 6^

31B8<

C C

B B

RXD3

0.2 BETWEEN CONNECTO RS.

ALLOW USE OF A DIFFERENT PHY CARD IF DESIRED. PLACEMENT SHOULD ALLOW

ON Z44 CARD ALL 4 PORTS MUST BE PLACED WITH EQUAL SPACING AND A COMMON CENTER LINE

TESTPOINTS (SHOWN ABOVE) MUST BE PLACED THE SAME FOR EACH PORT TO

PLACEMENT NOTE:

OUT

OUT

26D 6^

26D 6^

31B8<

31B8<

A A

8

Page 28

D

9

CHASSI S

1

J1

J2

J3

SH1

SYM_1

J01

2

P1

P4

P3

P2

J6

J4,5

P5

P6

10

CHASSI S

09/16/2004

SH2

J7,8

P8

DATE:

1

2/2(BLOCK)

31/71(TOTAL)

PAGE:

2