Page 1

General Description

The DS2775–DS2778 report available capacity for

rechargeable lithium-ion (Li+) and Li+ polymer (Li-Poly)

batteries in mAh and as a percentage of full. Safe operation is ensured by the integrated Li+ protector. The

DS2776/DS2778 support SHA-1-based challengeresponse authentication in addition to all other DS2775/

DS2777 features.

Precision measurements of voltage, temperature, and

current, along with a cell characteristics table and

application parameters, are used for capacity estimation calculations. The capacity registers report a conservative estimate of the amount of charge that can be

removed given the current temperature, discharge rate,

stored charge, and application parameters.

The DS2775–DS2778 operate from +4.0V to +9.2V for

direct integration into battery packs with two Li+ or LiPoly cells.

In addition to nonvolatile storage for cell compensation

and application parameters, the DS2775–DS2778 offer

16 bytes of EEPROM for use by the host system and/or

pack manufacturer to store battery lot and date tracking

information. The EEPROM can also be used for nonvolatile storage of system and/or battery usage statistics. A Maxim 1-Wire

®

(DS2775/DS2776) or 2-wire

(DS2777/DS2778) interface provides serial communication to access measurement and capacity data registers, control registers, and user memory. The

DS2776/DS2778 use the SHA-1 hash algorithm in a

challenge-response pack authentication protocol for

battery-pack verification.

Applications

Low-Cost Notebooks

UMPCs

DSLR Cameras

Video Cameras

Commercial and Military Radios

Portable Medical Equipment

Features

♦ High-Side nFET Drivers and Protection Circuitry

♦ Precision Voltage, Temperature, and Current

Measurement System

♦ Cell-Capacity Estimation from Coulomb Count,

Discharge Rate, Temperature, and Cell

Characteristics

♦ Estimates Cell Aging Between Learn Cycles

♦ Uses Low-Cost Sense Resistor

♦ Allows Calibration of Gain and Temperature

Coefficient

♦ Programmable Thresholds for Overvoltage and

Overcurrent

♦ Pack Authentication Using SHA-1 Algorithm

(DS2776/DS2778)

♦ 32-Byte Parameter EEPROM

♦ 16-Byte User EEPROM

♦ Maxim 1-Wire Interface with 64-Bit Unique ID

(DS2775/DS2776)

♦ 2-Wire Interface with 64-Bit Unique ID

(DS2777/DS2778)

♦ 3mm x 5mm, 14-Pin TDFN Lead-Free Package

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

________________________________________________________________

Maxim Integrated Products

1

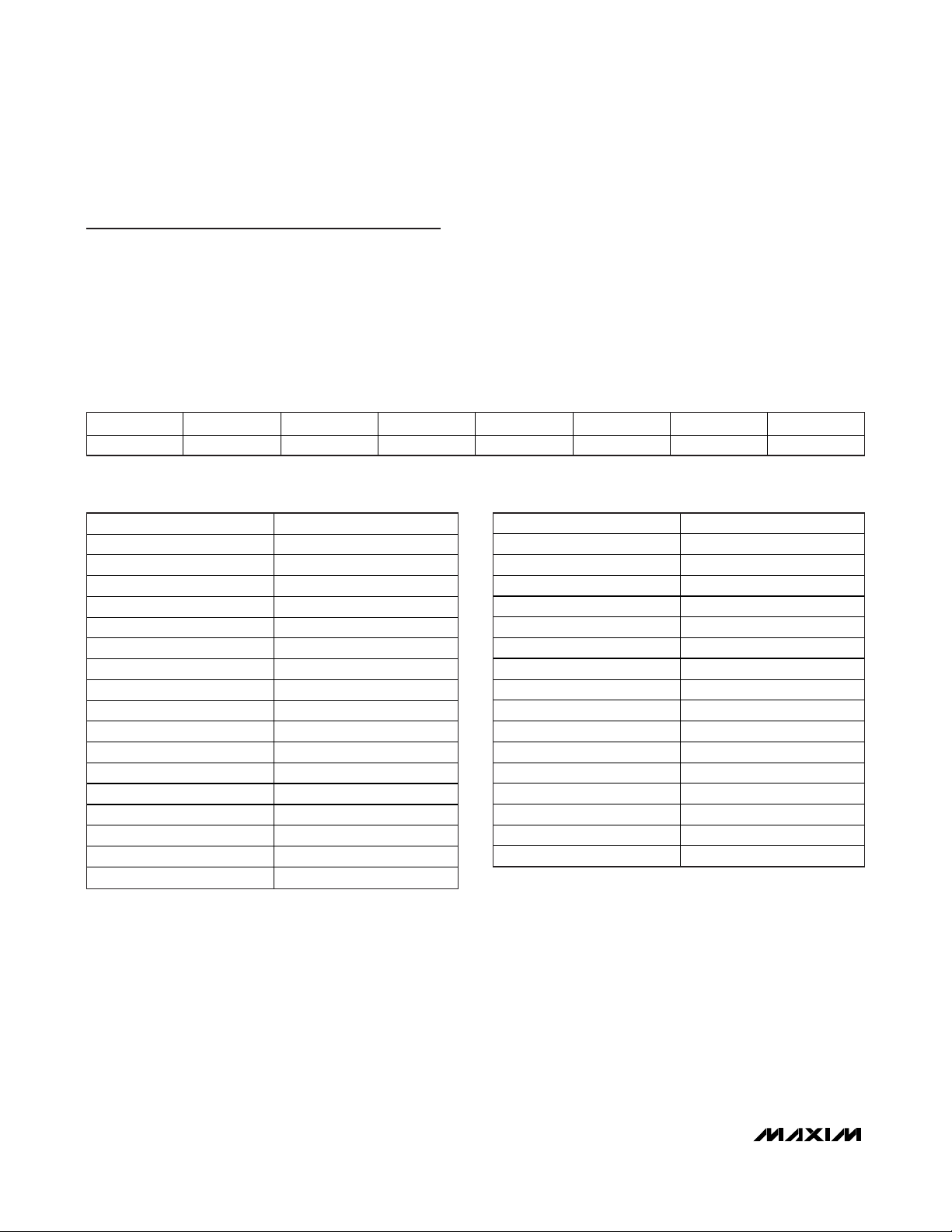

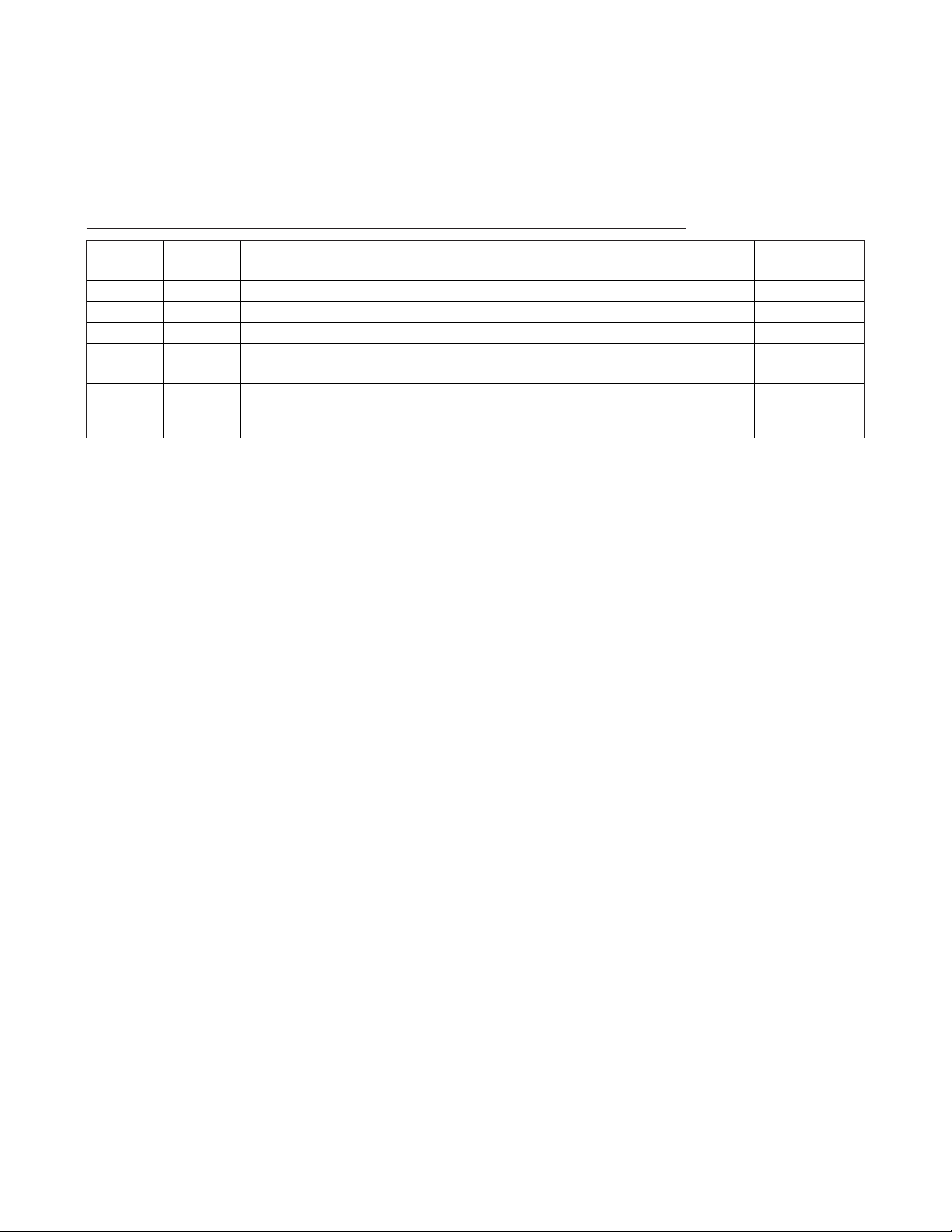

Ordering Information

19-4688; Rev 4; 6/11

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642,

or visit Maxim’s website at www.maxim-ic.com.

PART PIN-PACKAGE TOP MARK

DS2775G+ 14 TDFN-EP* D2775

DS2775G+T& R 14 TDFN-EP* D2775

DS2776G+ 14 TDFN-EP* D2776

DS776G+T&R 14 TDFN-EP* D2776

DS2777G+ 14 TDFN-EP* D2777

DS2777G+T& R 14 TDFN-EP* D2777

DS2778G+ 14 TDFN-EP* D2778

DS2778G+T& R 14 TDFN-EP* D2778

Note: All devices are specified over the -20°C to +70°C operating temperature range.

+

Denotes a lead(Pb)-free/RoHS-compliant package.

T&R = Tape and reel.

*

EP = Exposed pad.

Selector Guide appears at end of data sheet.

1-Wire is a registered trademark of Maxim Integrated Products, Inc.

Page 2

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

2 _______________________________________________________________________________________

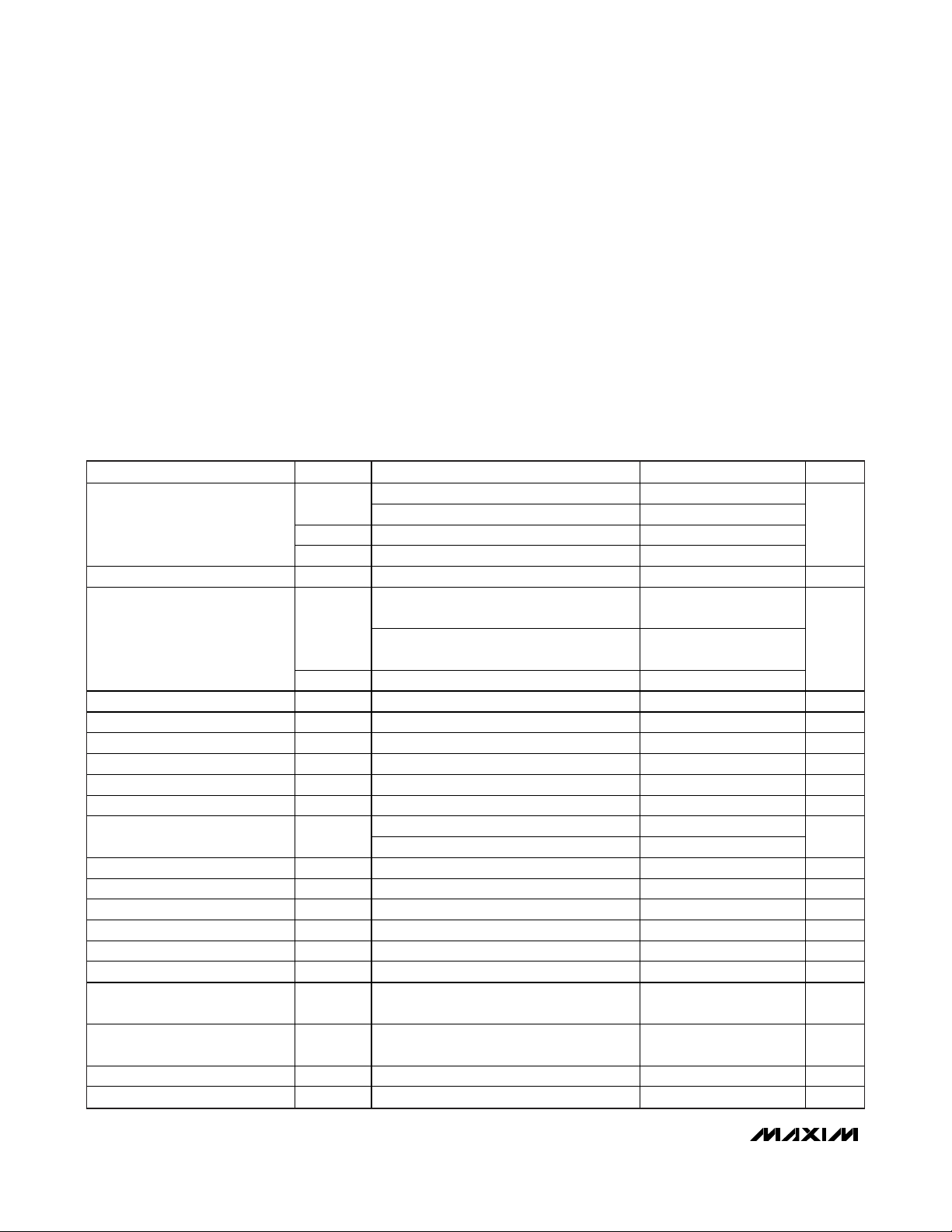

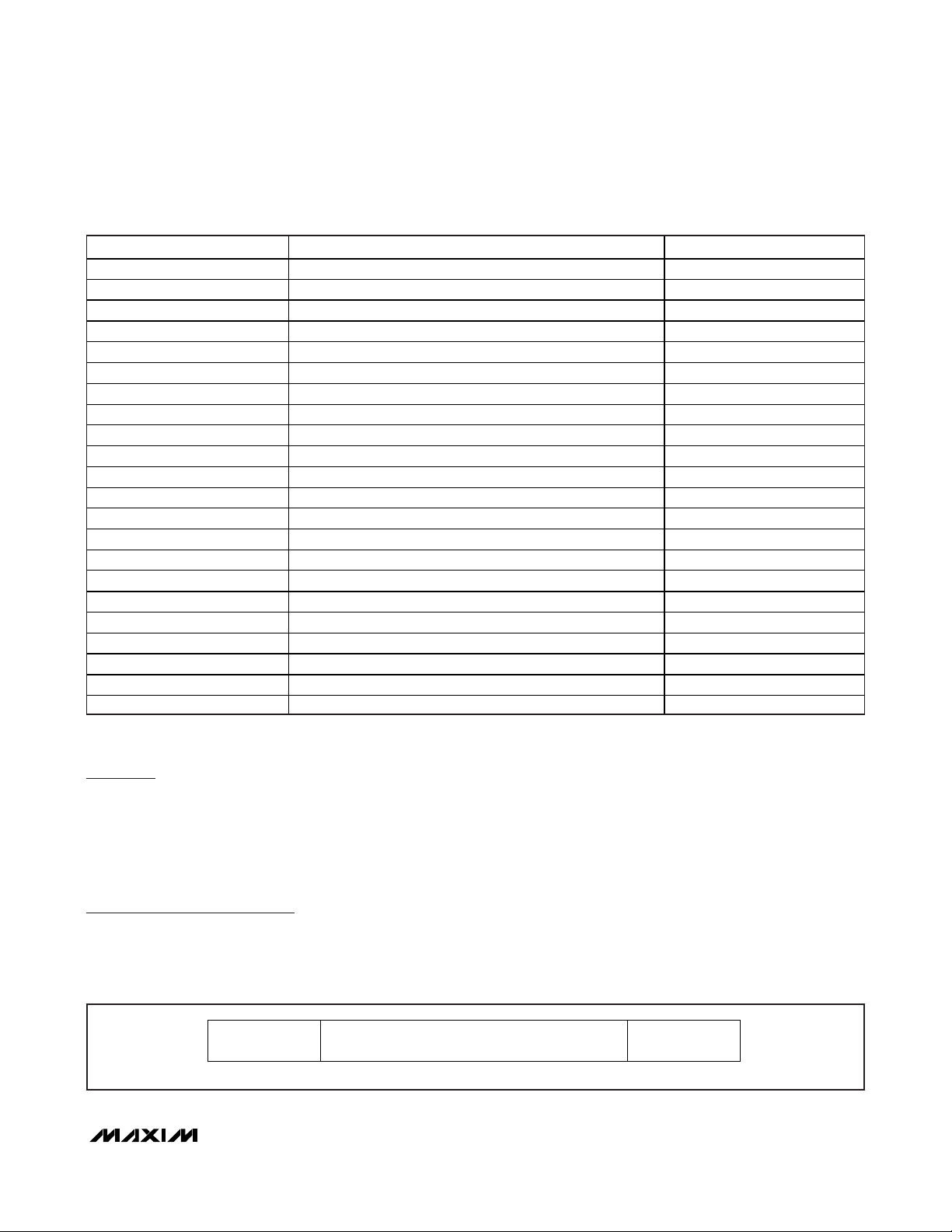

ABSOLUTE MAXIMUM RATINGS

ELECTRICAL CHARACTERISTICS

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C, unless otherwise noted. Typical values are at TA= +25°C.)

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional

operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to

absolute maximum rating conditions for extended periods may affect device reliability.

Voltage Range on PLS, CP, CC, DC Pins

Relative to V

SS

.....................................................-0.3V to +18V

Voltage Range on V

DD

, V

IN1

, V

IN2

, SRC Pins

Relative to VSS....................................................-0.3V to +9.2V

Voltage Range on All Other Pins Relative to V

SS

..-0.3V to +6.0V

Continuous Sink Current, PIO, DQ......................................20mA

Continuous Sink Current, CC, DC.......................................10mA

Operating Temperature Range ...........................-20°C to +70°C

Storage Temperature Range .............................-55°C to +125°C

Lead Temperature (soldering, 10s) .................................+300°C

Soldering Temperature (reflow) .......................................+260°C

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

I

DD0

Supply Current

Temperature Accuracy T

I

DD1

I

DD2

ERR

Voltage Accuracy

Input Resistance (V

Current Resolut ion I

Current Ful l Scale I

Current Gain Error I

Current Offset I

Accumulated Current Offset q

Time-Base Error t

CP Output Voltage (VCP - V

CP Startup Time t

Output High: CC, DC V

Output Low: CC V

Output Low: DC V

IN1

, V

) 15 M

IN2

LSB

FS

GERR

OERR

OERR

ERR

) VGS I

SRC

SCP

OHCP IOH

OLCC IOL

OLDC IOL

DQ, PIO Voltage Range -0.3 +5.5 V

DQ, PIO, SDA, SCL Input

Logic-High

DQ, PIO, SDA, SCL Input

Logic-Low

V

V

OVD Input Logic-High V

OVD Input Logic-Low V

Sleep mode, TA +50°C 3 5

Sleep mode, TA> +50°C 10

Active mode 80 135

Active mode during SHA-1 computation 120 300

-3 +3 °C

2.0V V

IN1

4.6V, 0°C T

2.0V V

4.6V, T

2.0V V

IN1

= +25°C

A

IN1

1.56 μV

-51.2 +51.2 mV

-1 +1 % FS

0°C TA +70°C (Note 1) -9.375 9.375 μVh

0°C TA +70°C (Note 1) -255 0 μVh/Day

0°C TA +50°C -2 +2

-3 +3

= 0.9μA 4.4 4.7 5 V

OUT

CE = 0, DE = 0, CCP = 0.1μF, acti ve mode 200 ms

= 100μA (Note 2) VCP - 0.4 V

= 100μA V

= 100μA V

1.5 V

IH

0.6 V

IL

V

IH

V

IL

4.6V, 2.0V (V

+50°C

A

4.6V, 2.0V (V

4.6V, 2.0V (V

IN2

- V

IN2

IN2

)

IN1

– V

)

IN1

- V

) 4.6V -50 +50

IN1

-35 +35

-22 22

- 0.2 V

BAT

SRC

SRC

SS

+ 0.1 V

+ 0.1 V

+ 0.2 V

μA

mV

%

Page 3

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

_______________________________________________________________________________________ 3

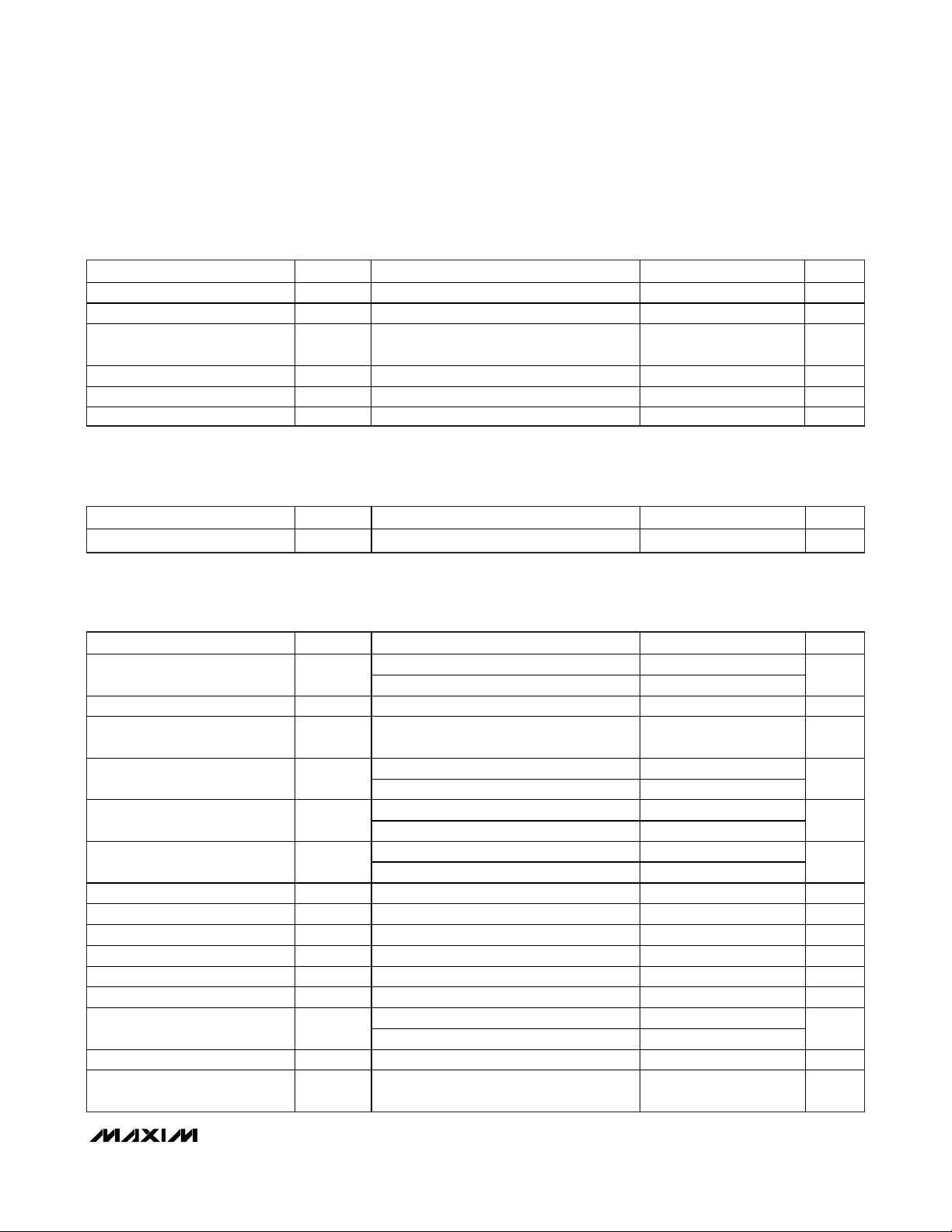

ELECTRICAL CHARACTERISTICS (continued)

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C, unless otherwise noted. Typical values are at TA= +25°C.)

SHA-1 COMPUTATION TIMING (DS2776/DS2778 ONLY)

(VDD= +4.0V to +9.2V, TA= 0°C to +70°C, unless otherwise noted. Typical values are at TA= +25°C.)

ELECTRICAL CHARACTERISTICS: PROTECTION CIRCUIT

(VDD= +4.0V to +9.2V, TA= 0°C to +50°C, unless otherwise noted. Typical values are at TA= +25°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

DQ, PIO, SDA Output Logic-Low V

DQ, PIO Pullup Current I

DQ, PIO, SDA, SCL Pulldown

Current

DQ Input Capacitance C

DQ Sleep Timeout t

PIO, DQ Wake Debounce t

OL

PU

I

PD

DQ

SLEEP

WDB

IOL = 4mA 0.4 V

Sleep mode, V

Active mode, V

50 pF

DQ < VIL 2 9 s

Sleep mode 100 ms

= (VDD - 0.4V) 30 100 200 nA

PIN

= 0.4V 30 100 200 nA

PIN

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Computation Time t

COMP

30 m s

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Overvoltage Detect V

Charge-Enable Voltage V

Undervoltage Detect V

Overcurrent Detect: Charge V

Overcurrent Detect: Discharge V

Short-Circuit Current Detect V

Overvoltage Delay t

Undervoltage Delay t

Overcurrent Delay t

Short-Circuit Delay t

Charger-Detect Hysteresis V

Test Threshold V

Test Current I

PLS Pulldown Current I

Recovery Current I

OV

CE

UV

COC

DOC

SC

OVD

UVD

OCD

SCD

CD

TST

PPD

RC

VOV = 1110111b 4.438 4.473 4.508

VOV = 1100011b 4.242 4.277 4.312

Relative to VOV -100 mV

Programmable in Control register 0x60h,

UV[1:0] = 10

OC = 11b -60 -75 -90

OC = 00b -12.5 -25 -38

OC = 11b 80 100 120

OC = 00b 25 38 50

SC =1b 240 300 360

SC = 0b 120 150 180

(Note 3) 600 1400 ms

(Note 3) 600 1400 ms

8 10 12 ms

80 120 160 μs

VUV condition 50 mV

COC, DOC condition 0.4 1.0 1.2 V

TP

DOC condition 20 40 80

COC condition -45 -60 -95

Sleep mode 200 400 630 μA

VUV condition, max: V

min: V

= 4.2V, VDD = 2V

PLS

= 15V, VDD = 1.4V;

PLS

2.415 2.450 2.485 V

3.3 8 13 mA

V

mV

mV

mV

μA

Page 4

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

4 _______________________________________________________________________________________

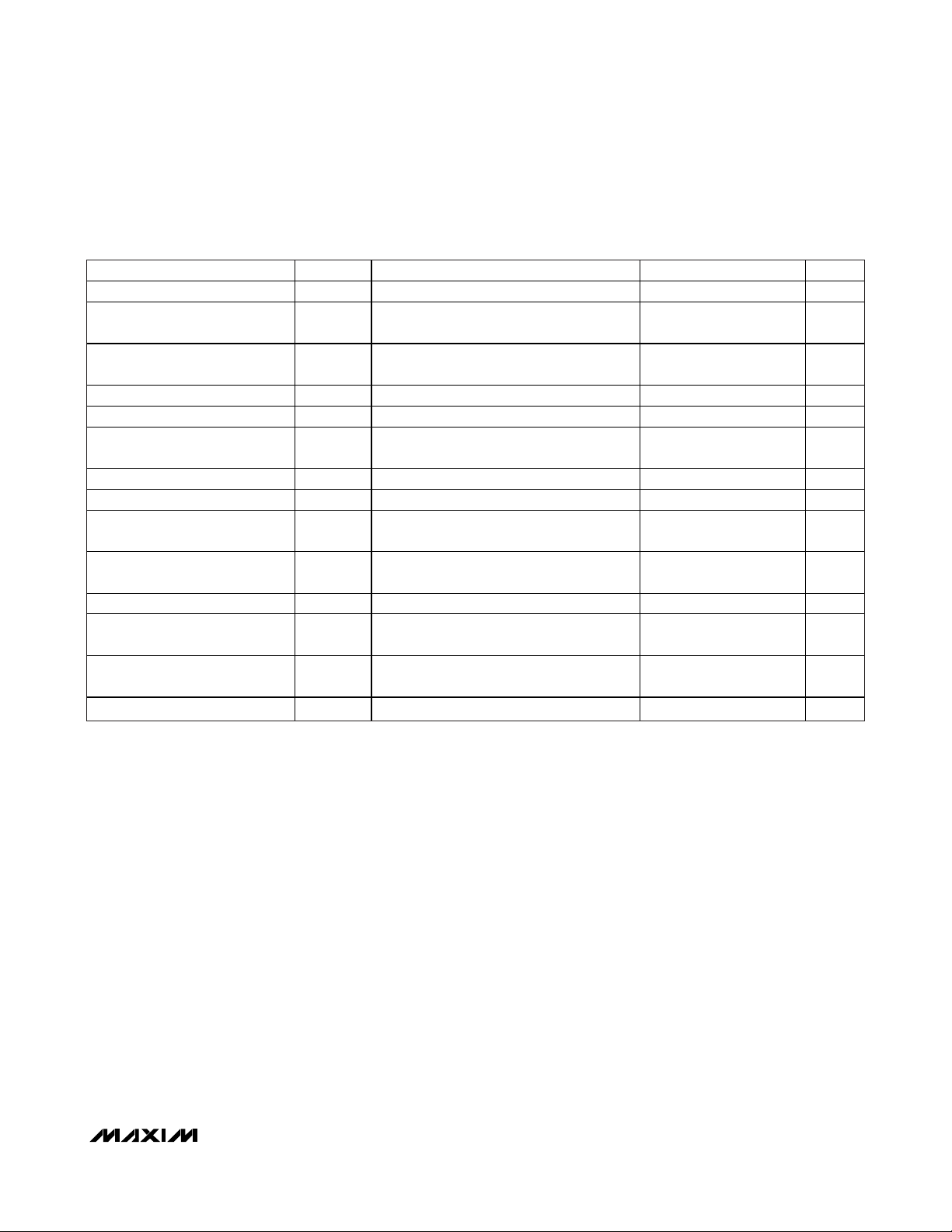

EEPROM RELIABILITY SPECIFICATION

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C, unless otherwise noted.)

ELECTRICAL CHARACTERISTICS: 1-Wire INTERFACE, STANDARD (DS2775/DS2776 ONLY)

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C.)

ELECTRICAL CHARACTERISTICS: 1-Wire INTERFACE, OVERDRIVE (DS2775/DS2776 ONLY)

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C.)

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

EEPROM Copy Time t

EEPROM Copy Endurance N

EEC

EEC

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

Time Slot t

Recovery Time t

Write-Zero Low Time t

Write-One Low Time t

Read Data Valid t

Reset Time High t

Reset Time Low t

Presence-Detect High t

Presence-Detect Low t

SLOT

REC

LOW0

LOW1

RDV

RSTH

RSTL

PDH

PDL

10 ms

TA = +50°C 50,000 Cycles

60 120 μs

1 μs

60 120 μs

1 15 μs

15 μs

480 μs

480 960 μs

15 60 μs

60 240 μs

Time Slot t

Recovery Time t

Write-Zero Low Time t

Write-One Low Time t

Read Data Valid t

Reset Time High t

Reset Time Low t

Presence-Detect High t

Presence-Detect Low t

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SLOT

REC

LOW0

LOW1

RDV

RSTH

RSTL

PDH

PDL

6 16 μs

1 μs

6 16 μs

1 2 μs

2 μs

48 μs

48 80 μs

2 6 μs

8 24 μs

Page 5

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

_______________________________________________________________________________________ 5

ELECTRICAL CHARACTERISTICS: 2-WIRE INTERFACE (DS2777/DS2778 ONLY)

(VDD= +4.0V to +9.2V, TA= -20°C to +70°C.)

Note 1: Accumulation bias and offset bias registers set to 00h. NBEN bit set to 0.

Note 2: Measurement made with V

SRC

= +8V, VGSdriven with external +4.5V supply.

Note 3: Overvoltage (OV) and undervoltage (UV) delays (t

OVD

, t

UVD

) are reduced to zero seconds if the OV or UV condition is

detected within 100ms of entering active mode.

Note 4: Timing must be fast enough to prevent the DS2777/DS2778 from entering sleep mode due to bus low for period > t

SLEEP

.

Note 5: f

SCL

must meet the minimum clock low time plus the rise/fall times.

Note 6: The maximum t

HD:DAT

need only be met if the device does not stretch the low period (t

LOW

) of the SCL signal.

Note 7: This device internally provides a hold time of at least 75ns for the SDA signal (referred to the V

IHMIN

of the SCL signal) to

bridge the undefined region of the falling edge of SCL.

Note 8: Filters on SDA and SCL suppress noise spikes at the input buffers and delay the sampling instant.

Note 9: C

B

is total capacitance of one bus line in pF.

PARAMETER SYMBOL CONDITIONS MIN TYP MAX UNITS

SCL Clock Frequency f

Bus-Free Time Between a STOP

and START Condition

Hold Time (Repeated) START

Condition

Low Period of SCL Clock t

High Period of SCL Clock t

Setup Time for a Repeated

START Condition

Data Hold Time t

Data Setup Time t

Rise Time of Both SDA and SCL

Signals

Fal l Time of Both SDA and SCL

Signals

Setup Time for STOP Condition t

Spike Pulse Widths Suppressed

by Input Filter

Capacitive Load for Each Bus

Line

SCL, SDA Input Capacitance C

(Note 4) 0 400 kHz

SCL

t

1.3 μs

BUF

t

(Note 5) 0.6 μs

HD: STA

1.3 μs

LOW

0.6 μs

HIGH

t

0.6 μs

SU:STA

(Notes 6, 7) 0 0.9 μs

HD:DAT

(Note 6) 100 ns

SU:DAT

t

R

t

F

0.6 μs

SU:STO

(Note 8) 0 50 ns

t

SP

C

(Note 9) 400 pF

B

60 pF

BIN

20 +

0.1C

20 +

0.1C

300 ns

B

300 ns

B

Page 6

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

6 _______________________________________________________________________________________

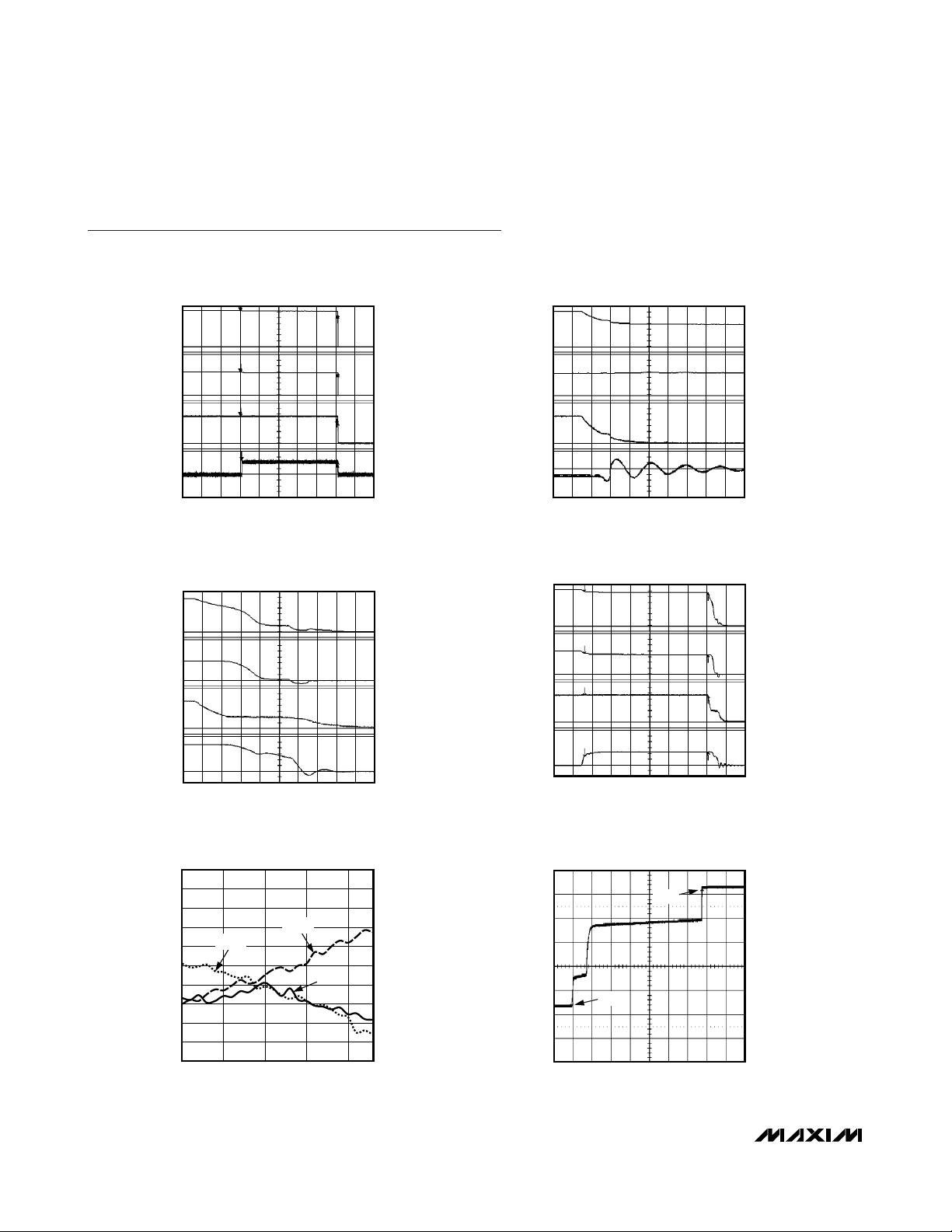

Typical Operating Characteristics

(TA = +25°C, unless otherwise noted.)

DISCHARGE-OVERCURRENT

PROTECTION DELAY

DS2775/6/7/8 toc01

DC FET

GATE

2V/div

2V/div

0V

0V

0V

0V

1V/div

20mV/div

DC FET

SOURCE

V

GS

V

SNS

25mΩ

SENSE RESISTOR

WITH DISCHARGEOVERCURRENT

THRESHOLD = 38mV

TIME (ms)

18

161412108642020

CC FET GATE TURN-OFF DURING

CHARGE-OVERCURRENT EVENT

DS2775/6/7/8 toc02

CC FET

GATE

2V/div

2V/div

0V

0V

0V

0V

1V/div

20mV/div

CC FET

SOURCE

V

GS

CC FET

V

SNS

25mΩ

SENSE RESISTOR

WITH CHARGEOVERCURRENT

THRESHOLD = 25mV

TIME (μs)

45

403530252015105050

DC FET GATE TURN-OFF DURING

SHORT-CIRCUIT EVENT

DS2775/6/7/8 toc03

DC FET

GATE

2V/div

0V

0V

0V

0V

2V/div

1V/div

50mV/div

DC FET

SOURCE

V

GS

DC FET

V

SNS

25mΩ

SENSE RESISTOR

WITH SHORT-CIRCUIT

THRESHOLD = 150mV

TIME (μs)

18

161412108642020

SHORT-CIRCUIT PROTECTION

DELAY

DS2775/6/7/8 toc04

DC FET

GATE

2V/div

0V

0V

0V

0V

2V/div

1V/div

100mV/div

DC FET

SOURCE

V

GS

DC FET

V

SNS

25mΩ

SENSE RESISTOR

WITH SHORT-CIRCUIT

THRESHOLD = 150mV

TIME (μs)

180

160140120100806040200 200

VOLTAGE MEASUREMENT

ACCURACY

DS2775/6/7/8 toc05

V

INX

(V)

ACCURACY (mV)

4321

2

4

6

8

10

12

14

16

18

20

0

0

+70°C

-20°C

+25°C

CHARGE-PUMP STARTUP EXITING SLEEP

MODE (V

DD

= 8V NO LOAD ON PK+)

DS2775/6/7/8 toc06

TIME (ms)

VOLTAGE (V)

908010 20 30 50 6040 70

0

2

3

4

5

6

7

8

-2

0 100

2.75V

12.6V

Page 7

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

_______________________________________________________________________________________

7

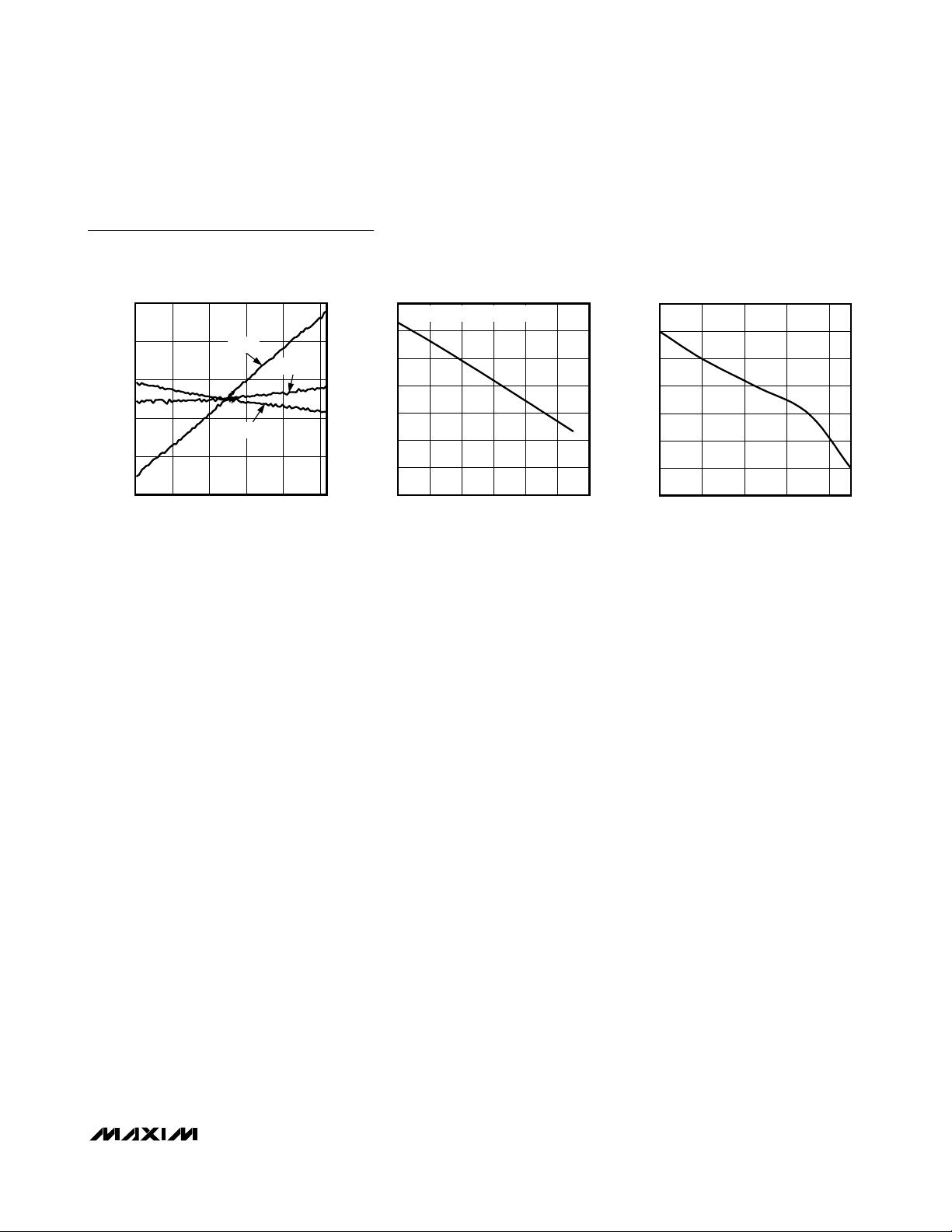

Typical Operating Characteristics (continued)

(TA = +25°C, unless otherwise noted.)

CURRENT MEASUREMENT

ACCURACY

125

75

25

-25

ACCURACY (μV)

-75

-125

-0.052

-20°C

+25°C

+70°C

V

(mV)

SNS

0.0480.0280.008-0.012-0.032

CURRENT MEASUREMENT OFFSET

vs. TEMPERATURE

2

1

0

-1

-2

LSB (1.5625μV)

-3

-4

-5

-20

TEMPERATURE (°C)

DS2775/6/7/8 toc07

(mA)

RC

I

IRC vs. V

7

1kΩ RESISTOR FROM PLS TO PK+

6

5

4

3

2

1

0

06

DD

DS2775/6/7/8 toc08

54321

VDD (V)

DS2775/6/7/8 toc09

6040200

Page 8

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

8 _______________________________________________________________________________________

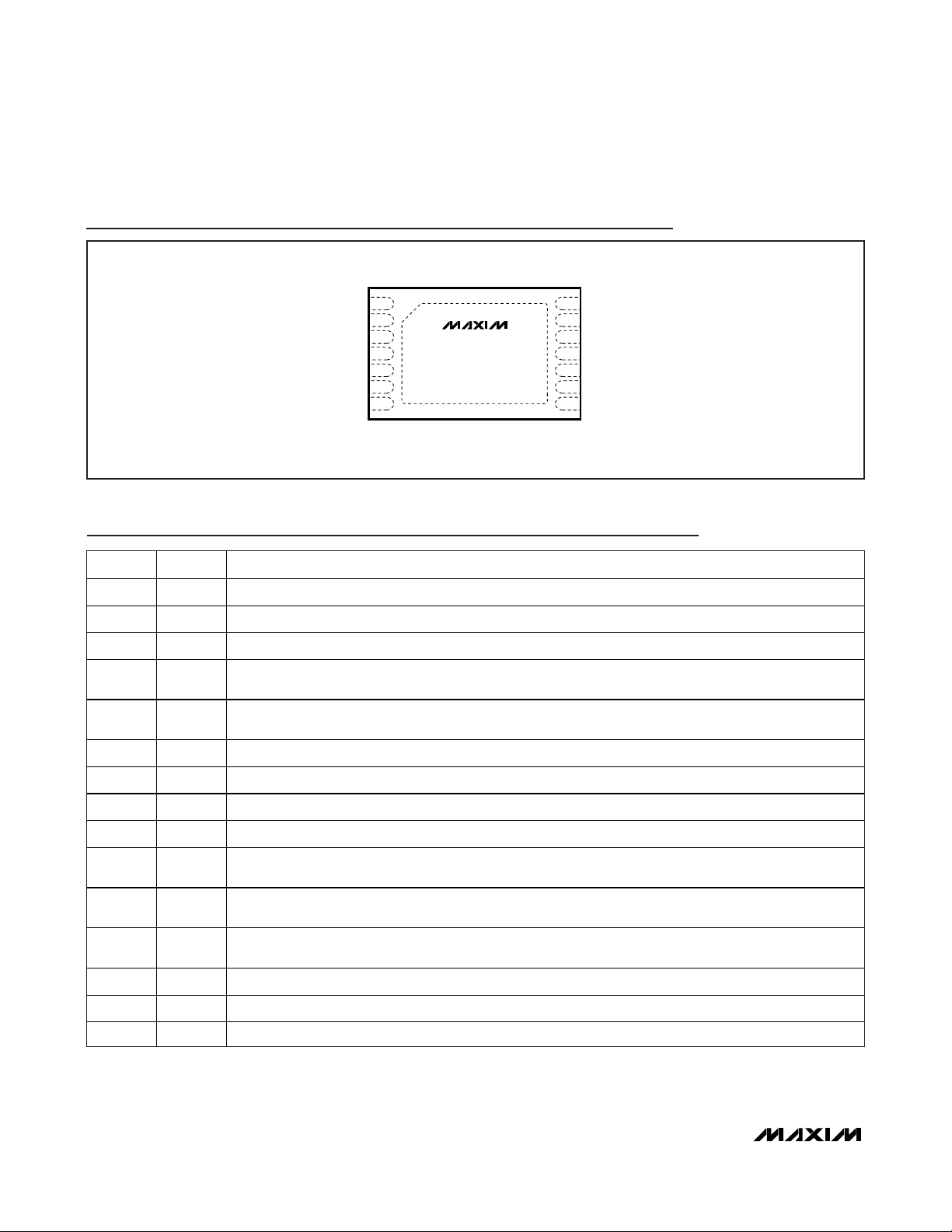

Pin Description

×

Pin Configuration

TOP VIEW

1CC

+

2V

DD

3DC

4V

IN2

5V

IN1

6VB

7V

SS

PIN NAME FUNCTION

1 CC Charge Control. Charge FET control output.

2 VDD Chip-Supply Input. Bypa ss with 0.1μF to VSS.

3 DC Discharge Control. Discharge FET control output.

4 V

5 V

6 VB Regulated Operating Voltage. B ypas s with 0.1μF to VSS.

Battery Voltage Sense Input 2. Connect to highest voltage potential positive cell terminal through

IN2

decoupl ing network.

Battery Voltage Sense Input 1. Connect to lowe st voltage potential po sit ive cel l terminal through

IN1

decoupl ing network.

DS2775

DS2776

DS2777

DS2778

TDFN

(3mm

5mm)

EP

14 CP

13 SRC

12 SCL/OVD

11 SDA/DQ

10 PLS

9 PIO

8 SNS

7 VSS Device Ground. Chip ground and battery-side sense resistor input.

8 SNS Sense Resistor Connection. Pack-side sense resistor sense input.

9 PIO Programmable I/O. Can be configured as wake input.

10 PLS

11 SDA/DQ

12 SCL/OVD

13 SRC Protection MOSFET Source Connection. U sed a s a reference for the charge pump.

14 CP Charge Pump Output. Generates gate drive voltage for protection FETs. Bypass with 0.47μF to SRC.

— EP Exposed Pad. Connect to ground or leave unconnected.

Pack Plus Terminal Sense Input. Used to detect the removal of short-circuit, discharge overcurrent, and

charge overcurrent condition s.

Data Input/Output. Serial data I/O, includes weak pulldown to detect system disconnect and can be

configured as wa ke input for 1-Wire devices.

Serial Clock Input/Overdrive Select. Communication clock for 2-wire devices/overdrive select pin for

1-Wire devices.

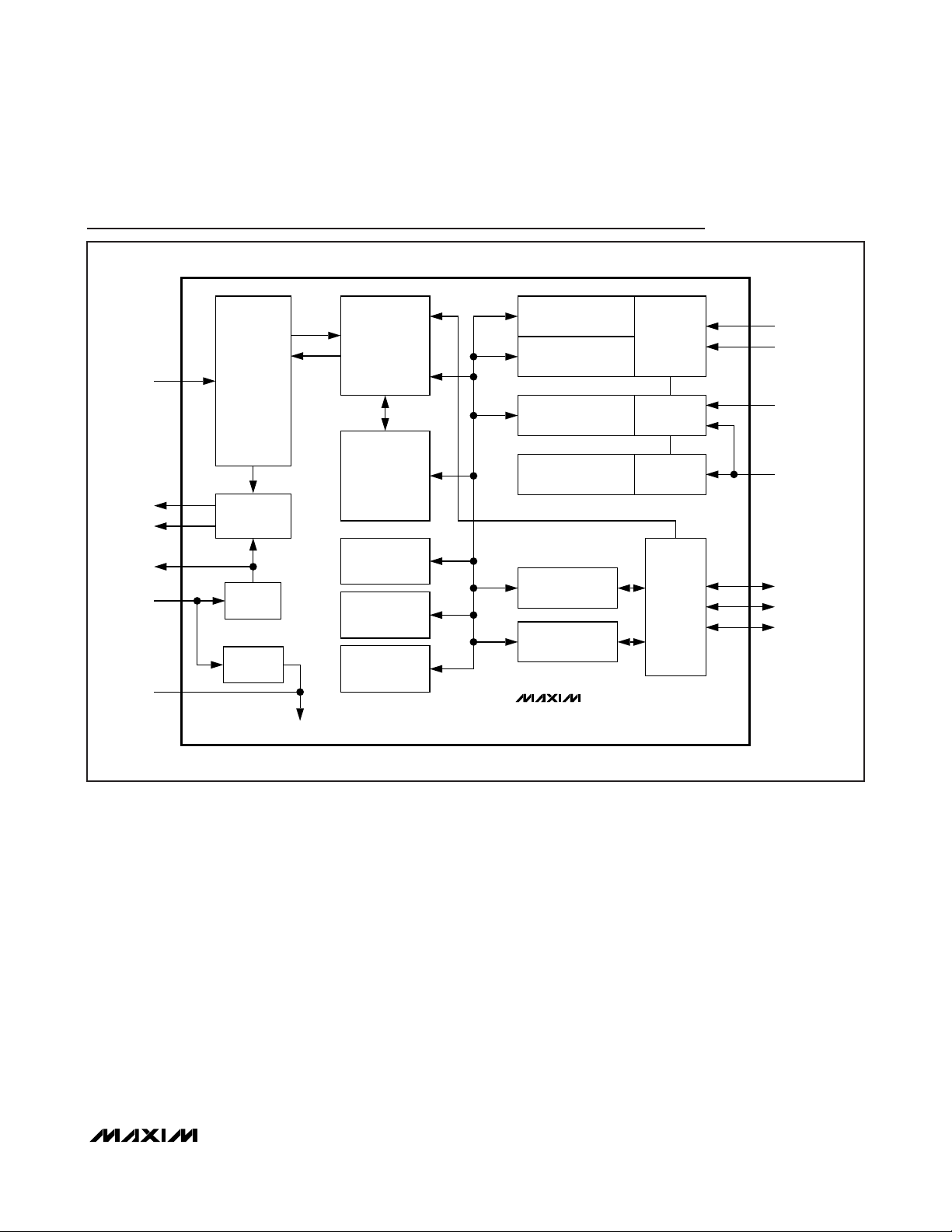

Page 9

DS2775/DS2776/DS2777/DS2778

Block Diagram

FuelPack is a trademark of Maxim Integrated Products, Inc.

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

_______________________________________________________________________________________ 9

PLS

CC

DC

CP

V

VOLTAGE

POWER-MODE

CONTROL

Li+

PROTECTOR

FuelPack™

ALGORITHM

FET DRIVERS

CONTROL AND

STATUS REGISTERS

DD

VB

CHARGE

PUMP

VOLTAGE

REGULATOR

VB INTERNAL

32-BYTE

PARAMETER

EEPROM

16-BYTE USER

EEPROM

TEMPERATURE

CURRENT

PRECISION ANALOG

OSCILLATOR

PIO LOGIC

COMMUNICATION

INTERFACE

DS2775–DS2778

10-BIT + SIGN

ADC/MUX

15-BIT + SIGN

ADC

VREF

PIN

DRIVERS

AND

POWER

SWITCH

CONTROL

V

IN2

V

IN1

SNS

V

SS

SDA/DQ

SCL/OVD

PIO

Page 10

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

10 ______________________________________________________________________________________

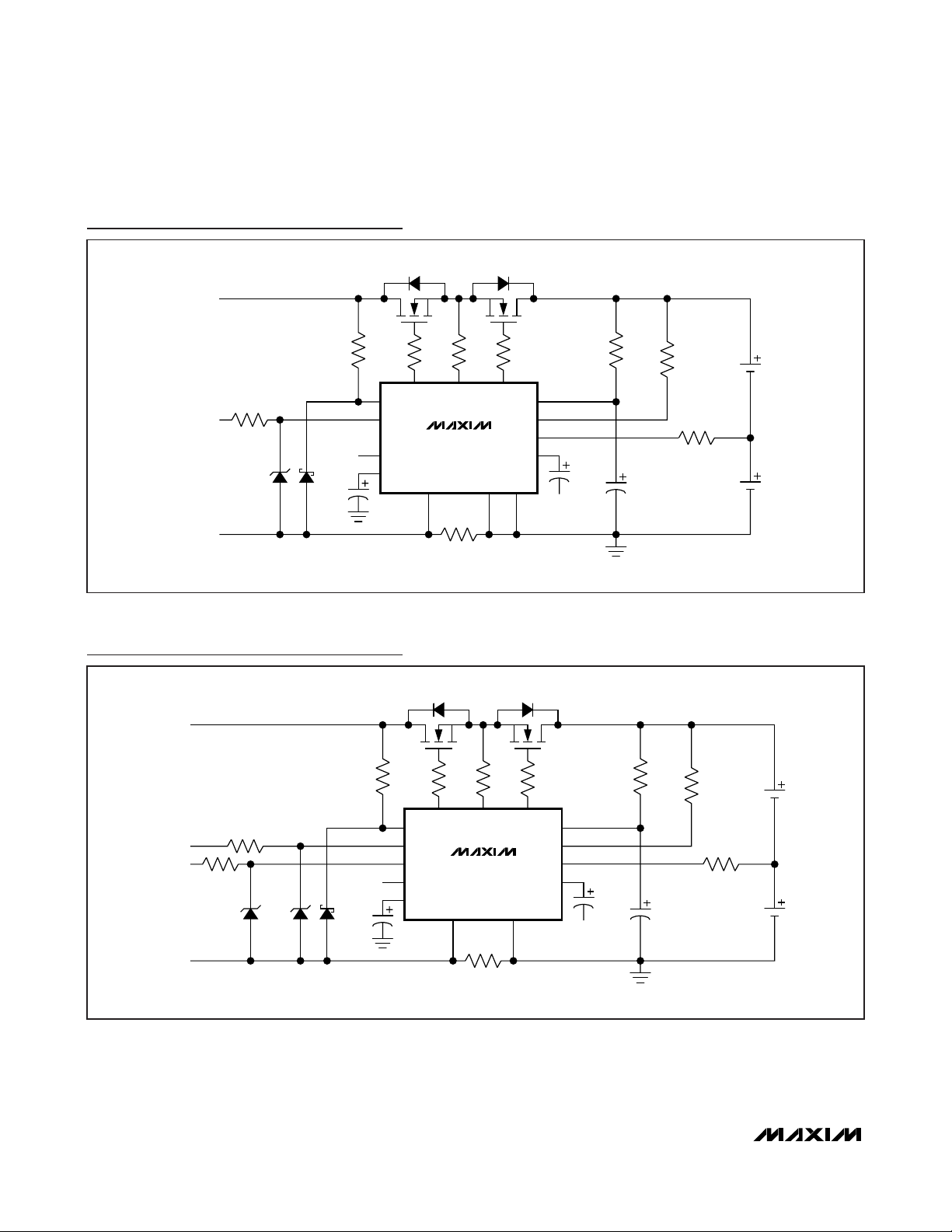

DS2775/DS2776 Typical Application Circuit

DS2777/DS2778 Typical Application Circuit

PK+

1kΩ 150Ω

150Ω

DATA

5.1V

0.1μF

PK-

1kΩ

CC SRC DC

PLS

DQ

DS2775

PIO

VB

DS2776

R

SNS

1kΩ470Ω

V

DD

V

IN2

V

IN1

CP

V

OVDSNS

SS

SRC

PK+

1kΩ 150Ω

1kΩ

1kΩ470Ω

0.47μF

1kΩ

1kΩ

0.1μF

1kΩ

CC SRC DC

SDA

SCL

PK-

150Ω

150Ω

PLS

SDA

SCL

PIO

5.1V5.1V

0.1μF

VB

SNS

DS2777

DS2778

R

SNS

V

DD

V

IN2

V

IN1

CP

SRC

0.47μF

0.1μF

V

SS

1kΩ

Page 11

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 11

Detailed Description

The DS2775–DS2778 function as an accurate fuel

gauge, Li+ protector, and SHA-1-based authentication

token (SHA-1-based authentication available only on

the DS2776/DS2778). The fuel gauge provides accurate estimates of remaining capacity and reports timely

voltage, temperature, and current measurement data.

Capacity estimates are calculated from a piecewise linear model of the battery performance over load and

temperature along with system parameters for charge

and end-of-discharge conditions. The algorithm parameters are user programmable and can be modified

within the pack. Critical capacity and aging data are

periodically saved to EEPROM in case of short-circuit

or deep-depletion events.

The Li+ protection function ensures safe, high-performance operation. nFET protection switches are driven

with a charge pump that maintains gate drive as the

cell voltage decreases. The high-side topology preserves the ground path for serial communication while

eliminating the parasitic charge path formed when the

fuel-gauge IC is located inside the protection FETs in a

low-side configuration. The thresholds for overvoltage,

undervoltage, overcurrent, and short-circuit current are

user programmable for customization to each cell and

application.

The 32-bit-wide SHA-1 engine with 64-bit secret and

64-bit challenge words resists brute force and other

attacks with financial-level HMAC security. The challenge of managing secrets in the supply chain is

addressed with the compute next secret feature. The

unique serial number or ROM ID can be used to assign

a unique secret to each battery.

Power Modes

The DS2775–DS2778 have two power modes: active

and sleep. On initial power-up, the DS2775–DS2778

default to active mode. In active mode, the DS2775–

DS2778 are fully functional with measurements and

capacity estimation registers continuously updated.

The protector circuit monitors battery pack, cell voltages, and battery current for safe conditions. The protection FET gate drivers are enabled when conditions

are deemed safe. Also, the SHA-1 authentication function is available in active mode. When an SHA-1 computation is performed, the supply current increases to

I

DD2

for t

SHA

. In sleep mode, the DS2775–DS2778 con-

serve power by disabling measurement and capacity

estimation functions, but preserve register contents.

Gate drive to the protection FETs is disabled in sleep;

the SHA-1 authentication feature is not operational.

The IC enters sleep mode under two different conditions: bus low and undervoltage. An enable bit makes

entry into sleep optional for each condition. Sleep mode

is not entered if a charger is connected (V

PLS

> VDD+

V

CD

) or if a charge current of 1.6mV/R

SNS

measured

from SNS to V

SS

. The DS2775–DS2778 exit sleep mode

upon charger connection or a low-to-high transition on

any communication line. The bus-low condition, where

all communication lines are low for t

SLEEP

, indicates

pack removal or system shutdown in which the bus

pullup voltage, V

PULLUP

, is not present. The power

mode (PMOD) bit must be set to enter sleep when a

bus-low condition occurs. After the DS2775–DS2778

enter sleep due to a bus-low condition, it is assumed

that no charge or discharge current flows and that

coulomb counting is unnecessary.

The second condition to enter sleep is an undervoltage

condition, which reduces battery drain due to the

DS2775–DS2778 supply current and prevents overdischarging the cell. The DS2775–DS2778 transition to

sleep mode if the V

IN1

or V

IN2

voltage is less than V

UV

and the undervoltage enable (UVEN) bit is set. The

communication bus must be in a static state, that is,

with DQ (SDA and SCL for 2-wire) either high or low for

t

SLEEP

. The DS2775–DS2778 transition from sleep

mode to active mode when DQ (SDA and SCL for

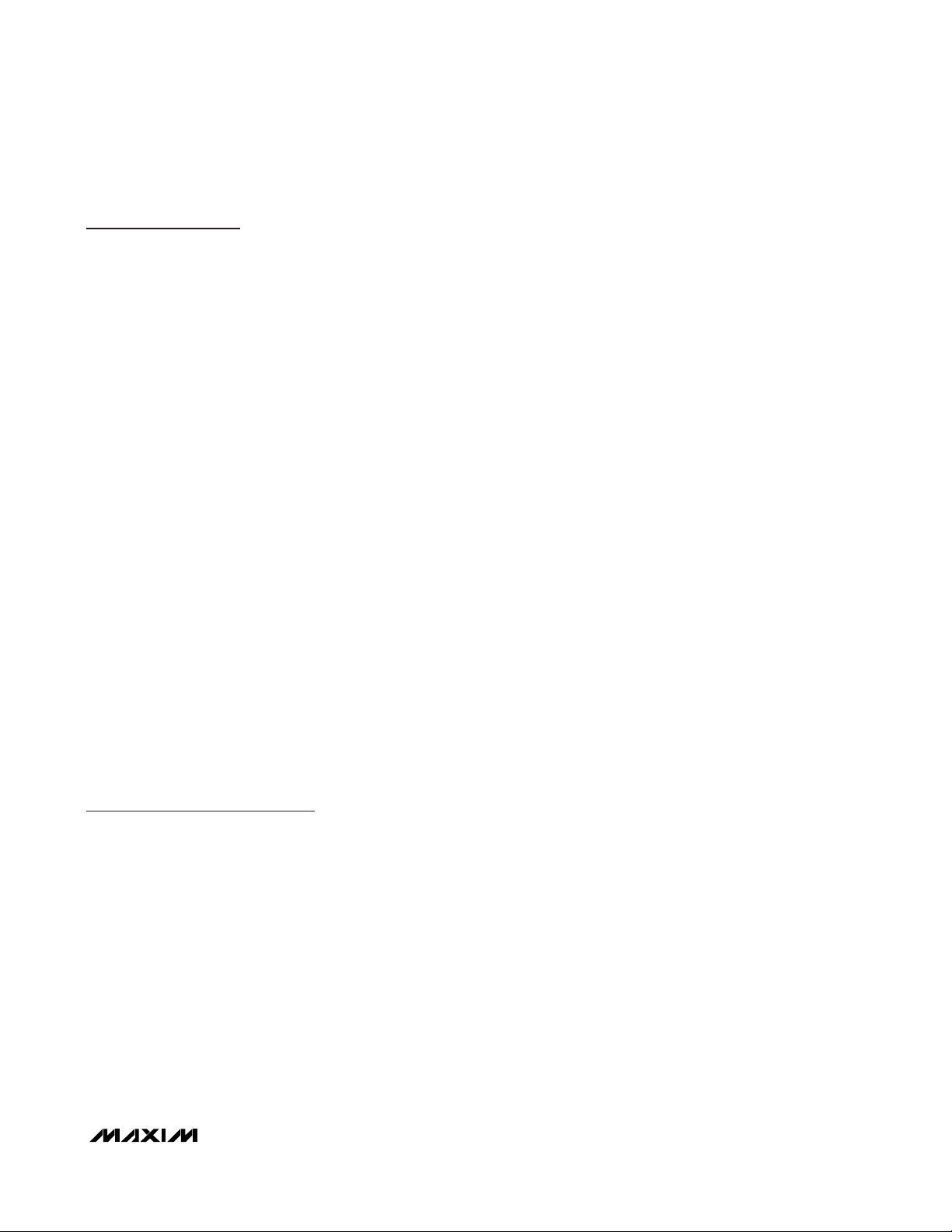

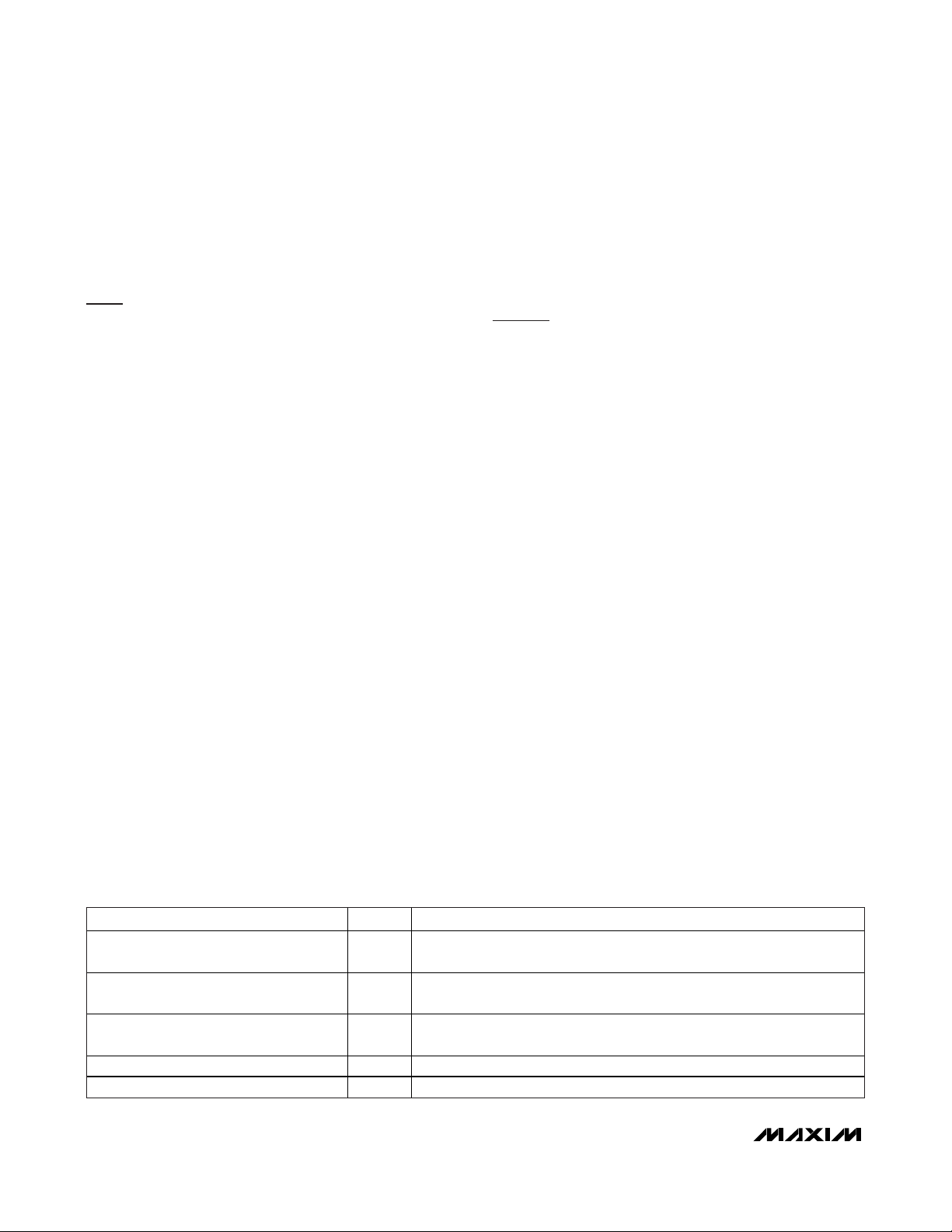

2-wire) changes logic state. See Figures 1 and 2 for

more information on sleep-mode state.

The DS2775–DS2778 have a “power switch” capability

for waking the device and enabling the protection FETs

when the host system is powered down. A simple dry

contact switch on the PIO pin or DQ pin can be used to

wake up the battery pack. The power-switch function is

enabled using the PSPIO and PSDQ configuration bits

in the Control register.

When PSPIO or PSDQ are set and sleep mode is

entered through the PMOD condition*, the PIO and DQ

pins pull high, respectively. Sleep mode is exited upon

the detection of a low-going transition on PIO or DQ.

PIO has a 100ms debounce period to filter out glitches

that can be caused when a sleeping battery is inserted

into a system.

*

The “power switch” feature is disabled if sleep mode is

entered because of a UV condition.

Page 12

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

12 ______________________________________________________________________________________

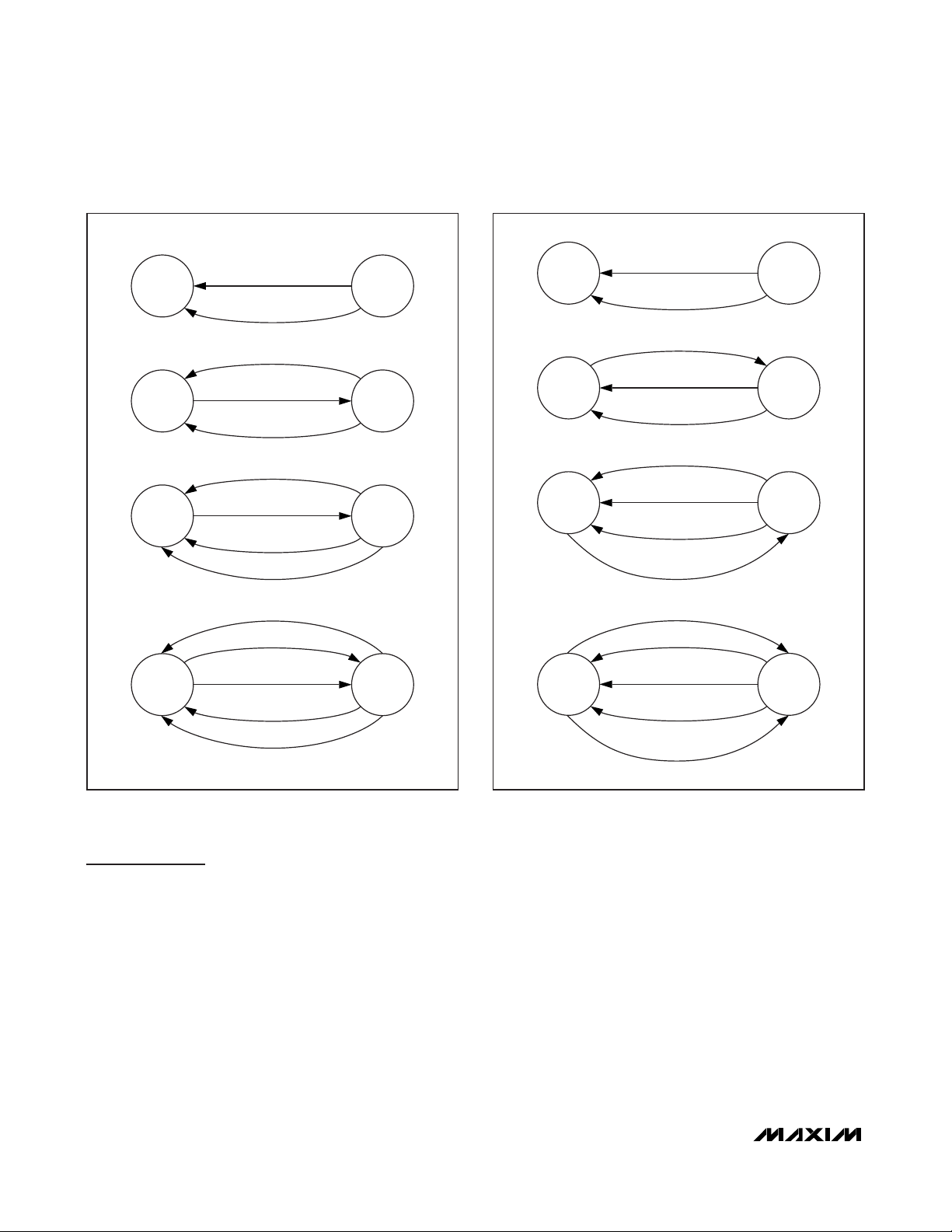

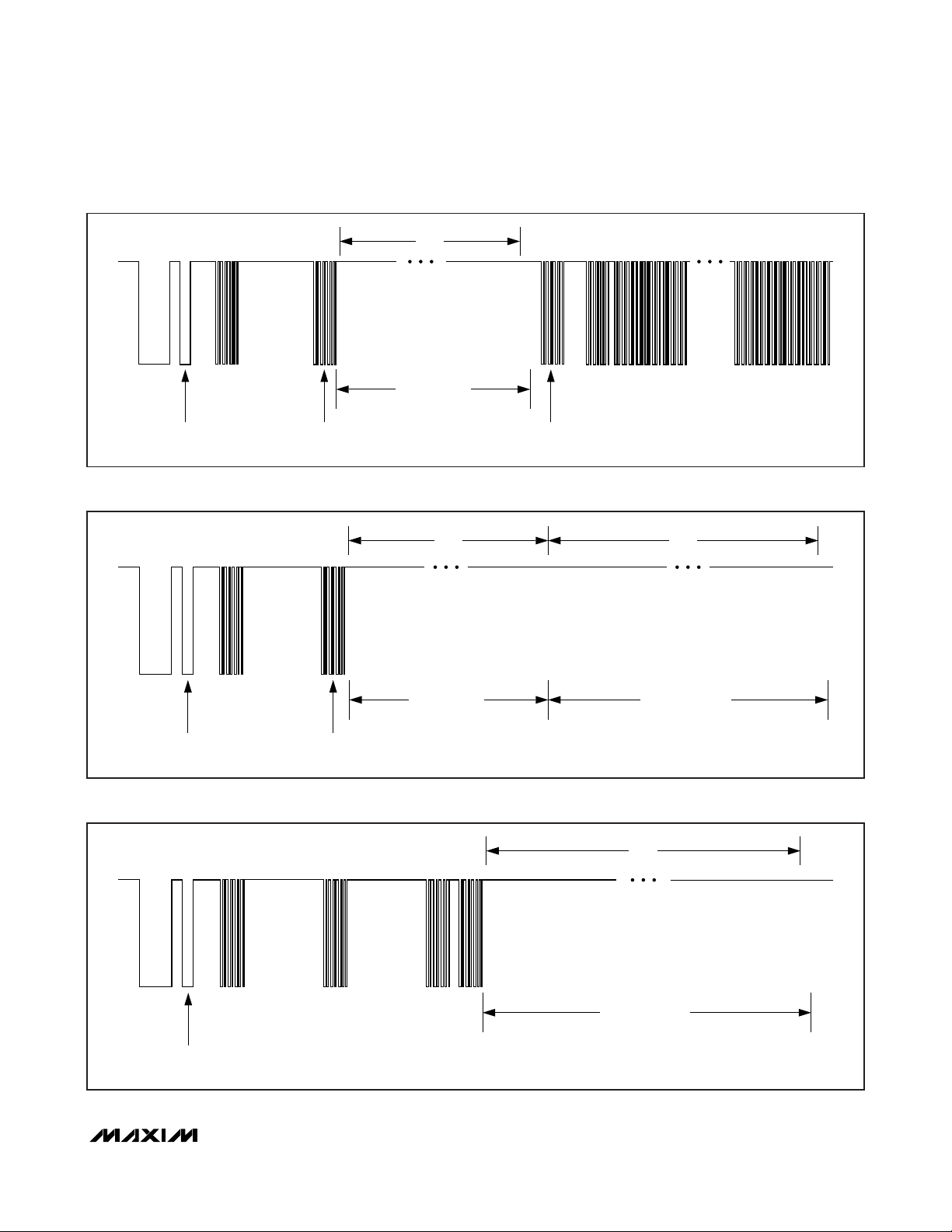

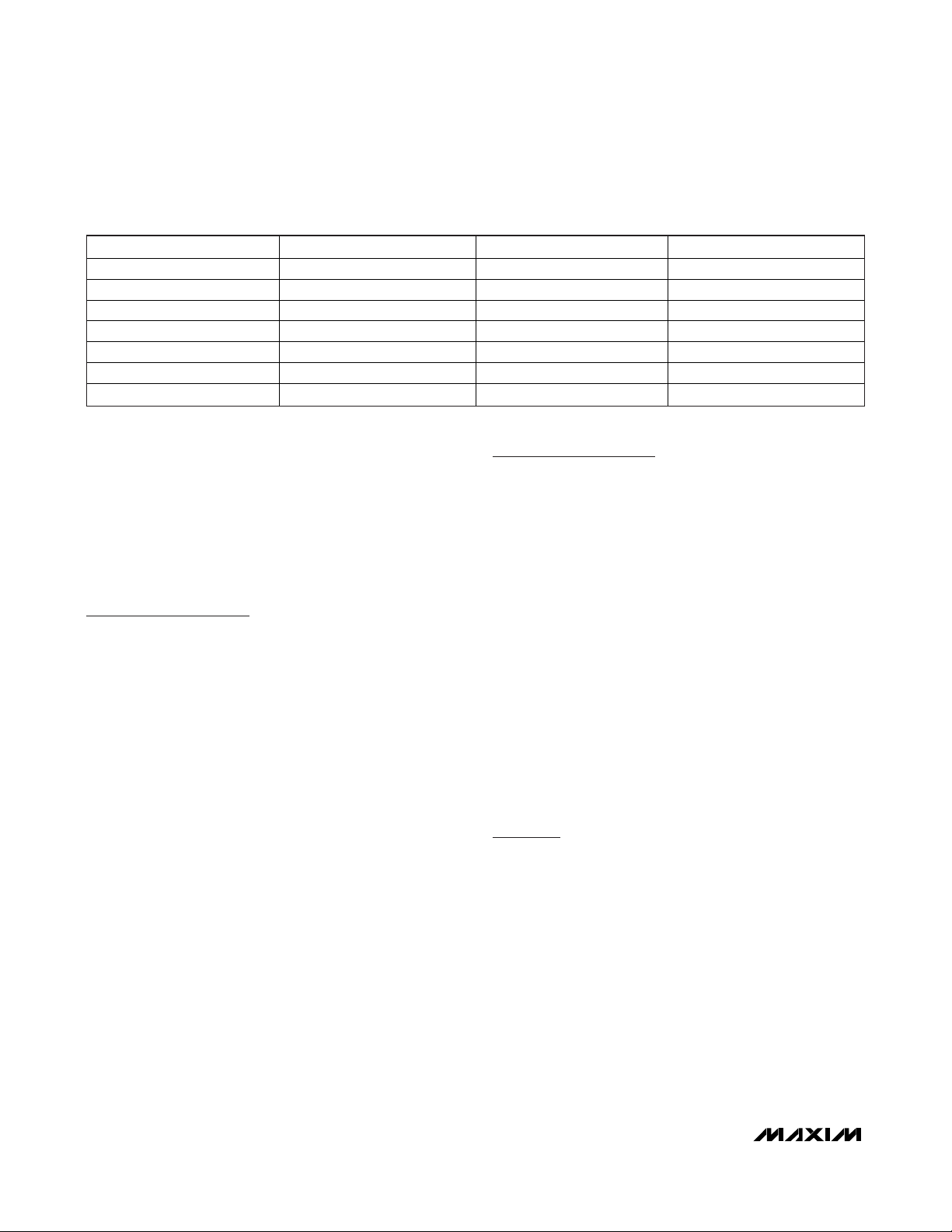

Li+ Protection Circuitry

During active mode, the DS2775–DS2778 constantly

monitor SNS, V

IN1

, V

IN2

, and PLS to protect the battery

from overvoltage (overcharge), undervoltage (overdischarge), and excessive charge and discharge currents

(overcurrent, short circuit). Table 1 summarizes the

conditions that activate the protection circuit, the

response of the DS2775–DS2778, and the thresholds

that release the DS2775–DS2778 from a protection

state. Figure 3 shows Li+ protection circuitry example

waveforms.

Overvoltage (OV)

If either of the voltages on (V

IN2

- V

IN1

) or (V

IN1

- VSS)

exceeds the overvoltage threshold, VOV, for a period

longer than overvoltage delay, t

OVD

, the CC pin is driven low to shut off the external charge FET. The DC output remains high during overvoltage to allow

discharging. When (V

IN2

- V

IN1

) and (V

IN1

- VSS) falls

below the charge-enable threshold, VCE, the

DS2775–DS2778 turn the charge FET on by driving CC

high. The DS2775–DS2778 drive CC high before

[(V

IN2-VIN1

) and (V

IN1

- VSS)] < VCEif a discharge

condition persists with V

SNS

≥ 1.2mV and [(V

IN2

- V

IN1

)

and (V

IN1

- VSS)] < VOV.

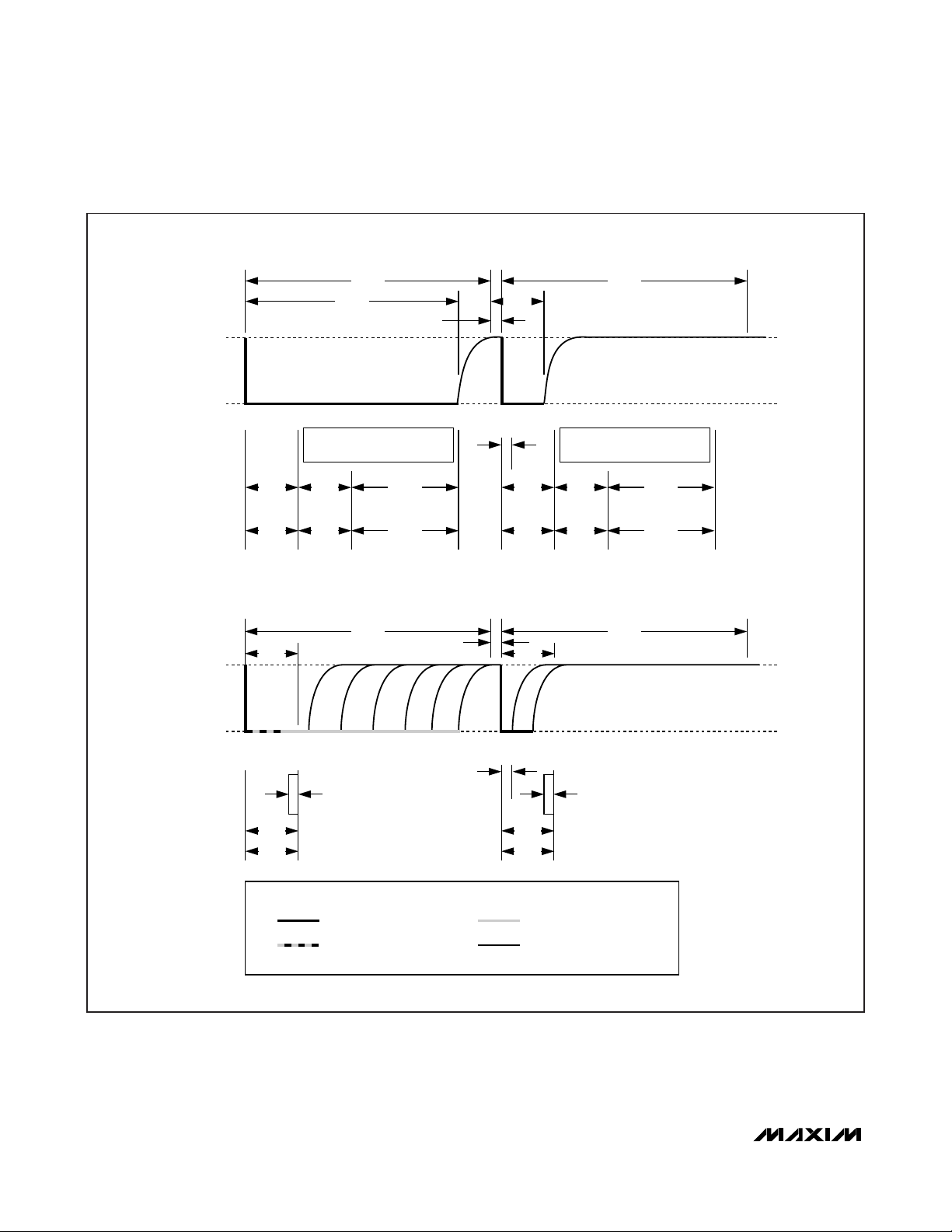

ACTIVE

PMOD = 0

UVEN = 0

SLEEP

PSPIO = 0

PSDQ = 0

RISING EDGE ON DQ

CHARGER DETECT

PULL DQ LOW

CHARGER DETECT

ACTIVE

PMOD = 0

UVEN = 1

SLEEP

PSPIO = 0

PSDQ = 1

V

IN1

OR V

IN2

< V

UV

PULL PIO LOW

RISING EDGE ON DQ

CHARGER DETECT

ACTIVE

PMOD = 1

UVEN = 0

SLEEP

PSPIO = 1

PSDQ = 0

PULL DQ LOW FOR t

SLEEP

PULL DQ LOW FOR t

SLEEP

PULL DQ LOW

PULL PIO LOW

CHARGER DETECT

ACTIVE

PMOD = 1

UVEN = 1

SLEEP

PSPIO = 1

PSDQ = 1

V

IN1

OR V

IN2

< V

UV

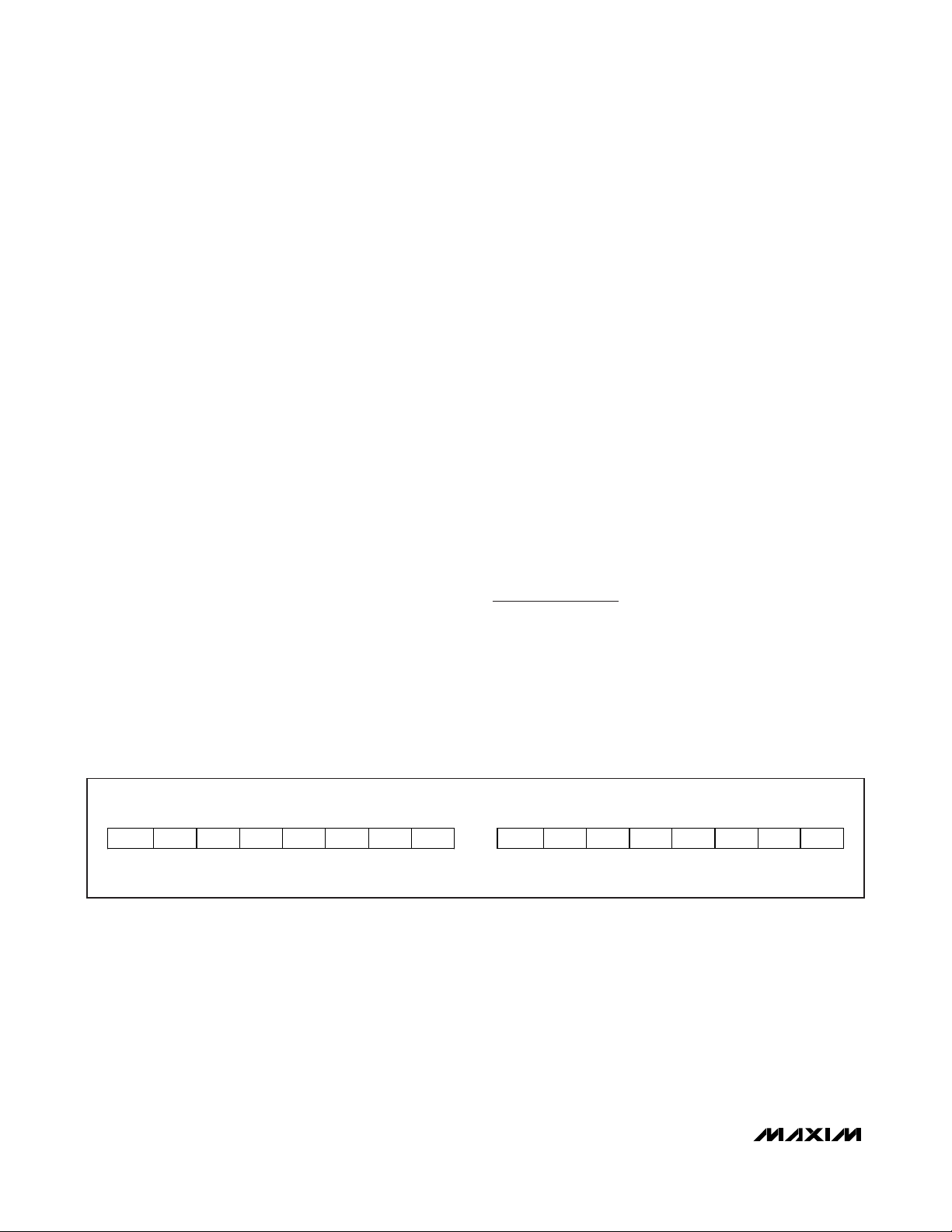

Figure 1. Sleep-Mode State Diagram for DS2775/DS2776

ACTIVE

PMOD = 0

UVEN = 0

SLEEP

PSPIO = 0

PSDQ = X

RISING EDGE ON SDA OR SCL

CHARGER DETECT

V

IN1

OR V

IN2

< V

UV

CHARGER DETECT

ACTIVE

PMOD = 0

UVEN = 1

SLEEP

PSPIO = 0

PSDQ = X

RISING EDGE ON SDA OR SCL

PULL PIO LOW

CHARGER DETECT

PULL SDA AND SCL LOW

FOR t

SLEEP

ACTIVE

PMOD = 1

UVEN = 0

SLEEP

PSPIO = 1

PSDQ = X

RISING EDGE ON SDA OR SCL

PULL SDA AND SCL LOW

FOR t

SLEEP

PULL PIO LOW

CHARGER DETECT

V

IN1

OR V

IN2

< V

UV

ACTIVE

PMOD = 1

UVEN = 1

SLEEP

PSPIO = 1

PSDQ = X

RISING EDGE ON SDA OR SCL

Figure 2. Sleep-Mode State Diagram for DS2777/DS2778

Page 13

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 13

Table 1. Li+ Protection Conditions and DS2775/DS2776 Responses

Note 1: V

CELL

is defined as (V

IN1

- VSS) or (V

IN2

- V

IN1

).

Note 2: Sleep mode is only entered if UVEN = 1.

Note 3: If V

CELL

< VUVwhen a charger connection is detected, release is delayed until V

CELL

≥

V

UV

. The recovery charge path pro-

vides an internal current limit (I

RC

) to safely charge the battery.

Note 4: With test current I

PPD

flowing from PLS to VSS(pulldown on PLS) enabled.

Note 5: With test current I

TST

flowing from VDDto PLS (pullup on PLS).

V

OV

V

CE

V

UV

V

IN

V

SNS

-V

COC

0

V

DOC

V

SC

t

OVD

t

OVD

t

OCD

t

UVD

t

UVD

t

OCD

t

SCO

DISCHARGE

CHARGE

POWER

MODE

ACTIVE

SLEEP*

*IF UVEN = 1.

CC

DC

V

OHCC

V

CP

V

DD

V

CP

V

PLS

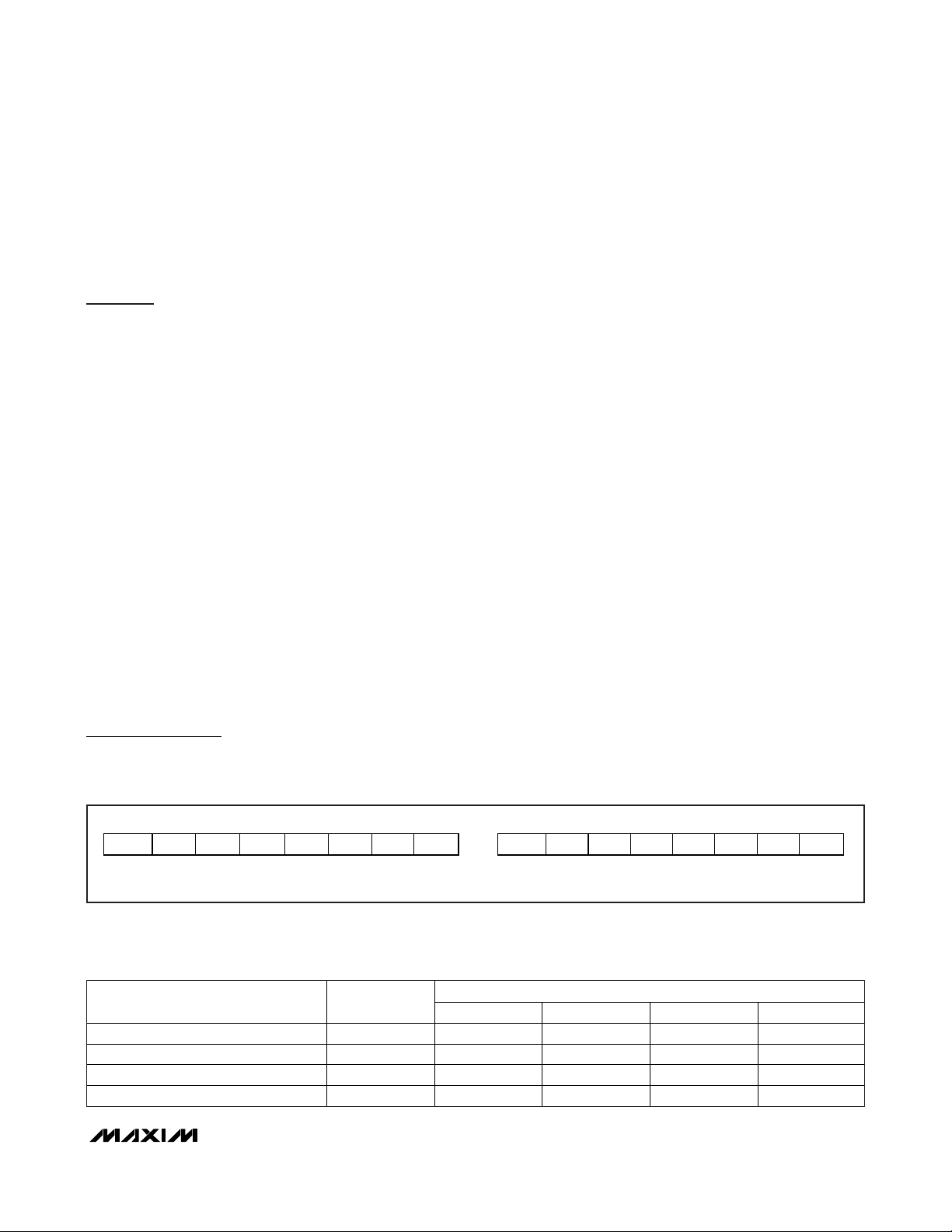

Figure 3. Li+ Protection Circuitry Example Waveforms

ACTIVATION

CC Off

OVD

UVD

CC Off, DC Off

OCD

DC Off

OCD

DC Off V

SCD

CC Off, DC Off,

Sleep Mode (Note 2)

CONDITION

Overvoltage (OV) (Note 1) V

Undervoltage (UV) (Note 1) V

Overcurrent, Charge (COC) V

Overcurrent, Discharge

(DOC)

Short Circuit (SC) V

THRESHOLD DELAY RESPONSE

> VOV t

CELL

< VUV t

CELL

< V

SNS

COC

V

> V

SNS

DOC

> VSC t

SNS

t

t

RELEASE THRESHOLD

< VCE or

CELL

1.2mV and both

< VOV) (Note 1)

(charger connected)

> VUV and

CELL

V

PLS

Both V

(V

SNS

V

CELL

> V

IN2

or (both V

UVEN = 0) (Note 3)

V

< VDD – V

PLS

TP

(charger removed) (Note 4)

> VDD – V

V

PLS

TP

(load removed) (Note 5)

> VDD – VTP (Note 5)

PLS

Page 14

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

14 ______________________________________________________________________________________

Undervoltage (UV)

If the average of the voltages on (V

IN2

- V

IN1

) or

(V

IN1

- VSS) drops below the undervoltage threshold,

VUV, for a period longer than undervoltage delay, t

UVD

,

the DS2775–DS2778 shut off the charge and discharge

FETs. If UVEN is set, the DS2775–DS2778 also enter

sleep mode. When a charger is detected and V

PLS

>

V

IN2

, the DS2775–DS2778 provide a current-limited

recovery charge path (IRC) from PLS to VDDto gently

charge severely depleted cells. The recovery charge

path is enabled when 0 ≤ [(V

IN2

- V

IN1

) and (V

IN1

-

V

SS

)] < VCE. The FETs remain off until (V

IN2

- V

IN1

) and

(V

IN1

- VSS) exceed VUV.

Overcurrent, Charge Direction (COC)

Charge current develops a negative voltage on V

SNS

with respect to VSS. If V

SNS

is less than the charge

overcurrent threshold, V

COC

, for a period longer than

overcurrent delay, t

OCD

, the DS2775–DS2778 shut off

both external FETs. The charge current path is not reestablished until the voltage on the PLS pin drops

below (VDD- VTP). The DS2775–DS2778 provide a test

current of value I

PPD

from PLS to VSS, pulling PLS

down, in order to detect the removal of the offending

charge current source.

Overcurrent, Discharge Direction (DOC)

Discharge current develops a positive voltage on V

SNS

with respect to VSS. If V

SNS

exceeds the discharge

overcurrent threshold, V

DOC

, for a period longer than

t

OCD

, the DS2775–DS2778 shut off the external discharge FET. The discharge current path is not reestablished until the voltage on PLS rises above (VDD- VTP).

The DS2775–DS2778 provide a test current of value

I

TST

from V

DD

to PLS, pulling PLS up, in order to detect

the removal of the offending low-impedance load.

Short Circuit (SC)

If V

SNS

exceeds short-circuit threshold, VSC, for a

period longer than short-circuit delay, t

SCD

, the

DS2775–DS2778 shut off the external discharge FET.

The discharge current path is not reestablished until

the voltage on PLS rises above (VDD- VTP). The

DS2775–DS2778 provide a test current of value I

TST

from VDDto PLS, pulling PLS up, in order to detect the

removal of the short circuit.

All the protection conditions described are logic

ANDed to affect the CC and DC outputs.

CC = (overvoltage) AND (undervoltage) AND

(overcurrent, charge direction) AND (Protection register

bit CE = 0)

DC = (undervoltage) AND (overcurrent, either direction)

AND (short circuit) AND (Protection register bit

DE = 0)

Voltage Measurements

Cell voltages are measured every 440ms. The lowest

potential cell, V

IN1

, is measured with respect to VSS.

The highest potential cell, V

IN2

, is measured with

respect to V

IN1

. Battery voltages are measured with a

range of -5V to +4.9951V and a resolution of 4.8828mV

and placed in the Result register in two’s complement

form. Voltages above the maximum register value are

reported as 7FE0h.

MSB - ADDRESS 0Ch, V

IN1

- V

SS

LSB - ADDRESS 0Dh, V

IN1

- V

SS

MSB - ADDRESS 1Ch, V

IN2

- V

IN1

LSB - ADDRESS 1Dh, V

IN2

- V

IN1

S 29 28 27 26 25 24 2

3

22 21 20 X X X X X

MSb LSb MSb LSb

“S”: SIGN BIT(S), “X”: RESERVED UNITS: 4.883mV

Figure 4. Voltage Register Format

Page 15

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 15

Temperature Measurement

The DS2775–DS2778 use an integrated temperature

sensor to measure battery temperature with a resolution

of 0.125°C. Temperature measurements are updated

every 440ms and placed in the Temperature register in

two’s complement form.

Current Measurement

In active mode, the DS2775–DS2778 continuously measure the current flow into and out of the battery by measuring the voltage drop across a low-value current-sense

resistor, R

SNS

. The voltage-sense range between SNS

and V

SS

is ±51.2mV with a least significant bit (LSb) of

1.5625µV. The input linearly converts peak signal amplitudes up to 102.4mV as long as the continuous signal

level (average over the conversion cycle period) does

not exceed ±51.2mV. The ADC samples the input differentially at 18.6kHz and updates the Current register at

the completion of each conversion cycle (3.52s). Charge

currents above the maximum register value are reported

as 7FFFh. Discharge currents below the minimum register value are reported as 8000h.

The Average Current register reports an average current level over the preceding 28.16s. The register value

is updated every 28.16s in two’s complement form and

represents an average of the eight preceding Current

register values.

MSB—ADDRESS 0Ah LSB—ADDRESS 0Bh

S 2

9

28 27 26 25 24 2

3

22 21 20 X X X X X

MSb LSb MSb LSb

“S”: SIGN BIT(S), “X”: RESERVED UNITS: 0.125°C

Figure 5. Temperature Register Format

MSB—ADDRESS 0Eh LSB—ADDRESS 0Fh

S 2

14

213 212 211 210 29 2

8

27 26 25 24 23 22 21 2

0

MSb LSb MSb LSb

“S”: SIGN BIT(S)

UNITS: 1.5625μV/R

SNS

Figure 6. Current Register Format

MSB—ADDRESS 08h LSB—ADDRESS 09h

S 2

14

213 212 211 210 29 2

8

27 26 25 24 23 22 21 2

0

MSb LSb MSb LSb

“S”: SIGN BIT(S)

UNITS: 1.5625μV/R

SNS

Figure 7. Average Current Register Format

Page 16

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

16 ______________________________________________________________________________________

Current Offset Correction

Every 1024th conversion, the ADC measures its input

offset to facilitate offset correction. Offset correction

occurs approximately once per hour. The resulting correction factor is applied to the subsequent 1023 measurements. During the offset correction conversion, the

ADC does not measure the sense resistor signal. A

maximum error of 1/1024 in the Accumulated Current

register (ACR) is possible; however, to reduce the error,

the current measurement made just prior to the offset

conversion is retained in the Current register and is

substituted for the dropped current measurement in the

current accumulation process. Therefore the accumulated current error due to offset correction is typically

much less than 1/1024.

Current Offset Bias

The current offset bias value (COB) allows a programmable offset value to be added to raw current measurements. The result of the raw current measurement plus

COB is displayed as the current measurement result in

the Current register and is used for current accumulation. COB can be used to correct for a static offset error

or can be used to intentionally skew the current results

and therefore the current accumulation. Read and write

access is allowed to COB. Whenever the COB is written, the new value is applied to all subsequent current

measurements. COB can be programmed in 1.56µV

steps to any value between -199.7µV and +198.1µV.

The COBR value is stored as a two’s complement value

in volatile memory and must be initialized through the

interface on power-up. The factory default value is 00h.

Current Blanking

The current blanking feature modifies current measurement result prior to being accumulated in the ACR.

Current blanking occurs conditionally when a current

measurement (raw current and COBR) falls in one of

two defined ranges. The first range prevents charge

currents less than 100µV from being accumulated. The

second range prevents discharge currents less than

25µV in magnitude from being accumulated. Charge

current blanking is always performed; however, discharge current blanking must be enabled by setting the

NBEN bit in the Control register. See the

Control

Register Format

description for additional information.

Current Measurement Gain

The DS2775–DS2778’s current measurement gain can

be adjusted through the RSGAIN register, which is factory calibrated to meet the data sheet specified accuracy.

RSGAIN is user accessible and can be reprogrammed

after module or pack manufacture to improve the current

measurement accuracy. Adjusting RSGAIN can correct

for variation in an external sense resistor’s nominal value

and allows the use of low-cost, nonprecision currentsense resistors. RSGAIN is an 11-bit value stored in 2

bytes of the parameter EEPROM memory block. The

RSGAIN value adjusts the gain from 0 to 1.999 in steps

of 0.001 (precisely 2–10). The user must use caution

when programming RSGAIN to ensure accurate current

measurement. When shipped from the factory, the gain

calibration value is stored in two separate locations in the

parameter EEPROM block, RSGAIN, which is reprogrammable and FRSGAIN, which is read-only. RSGAIN determines the gain used in the current measurement. The

ADDRESS 7Bh

S 2

6

25 24 23 22 21 2

0

MSb LSb

“S”: SIGN BIT(S)

UNITS: 1.56μV/R

SNS

Figure 8. Current Offset Bias Register Format

MSB—ADDRESS 78h LSB—ADDRESS 79h

X SC0 OC1 OC0 X 2

0

2-1 2

-2

2-3 2-4 2-5 2-6 2-7 2-8 2-9 2

-10

MSb LSb MSb LSb

“X”: RESERVED UNITS: 2–10

Figure 9. RSGAIN Register

Page 17

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 17

FRSGAIN value is provided to preserve the factory calibration value only and is not used to calibrate the current

measurement. The 16-bit FRSGAIN value is readable

from addresses B0h and B1h.

Sense-Resistor Temperature

Compensation

The DS2775–DS2778 can temperature compensate the

current-sense resistor to correct for variation in a sense

resistor’s value over temperature. The DS2775–DS2778

are factory programmed with the sense-resistor temperature coefficient, RSTC, set to zero, which turns off the

temperature compensation function. RSTC is user

accessible and can be reprogrammed after module or

pack manufacture to improve the current accuracy

when using a high-temperature coefficient currentsense resistor. RSTC is an 8-bit value stored in the

parameter EEPROM memory block. The RSTC value

sets the temperature coefficient from 0 to +7782ppm/°C

in steps of 30.5ppm/°C. The user must program RSTC

cautiously to ensure accurate current measurement.

Temperature compensation adjustments are made when

the Temperature register crosses 0.5°C boundaries. The

temperature compensation is most effective with the

resistor placed as close as possible to the VSSterminal

to optimize thermal coupling of the resistor to the on-chip

temperature sensor. If the current shunt is constructed

with a copper PCB trace, run the trace under the

DS2775–DS2778 package whenever possible.

Current Accumulation

Current measurements are internally summed, or accumulated, at the completion of each conversion period

with the results displayed in the Accumulated Current

register (ACR). The accuracy of the ACR is dependent

on both the current measurement and the conversion

time base. The ACR has a range of 0 to +409.6mVh

with an LSb of 6.25µVh. Additional registers hold fractional results of each accumulation to avoid truncation

errors. The fractional result bits are not user accessible.

Accumulation of charge current above the maximum

register value is reported at the maximum value; conversely, accumulation of discharge current below the

minimum register value is reported at the minimum

value.

Charge currents (positive Current register values) less

than 100µV are not accumulated in order to mask the

effect of accumulating small positive offset errors over

long periods. This effect limits the minimum charge current, for coulomb counting purposes, to 5mA for R

SNS

= 0.020Ω and 20mA for R

SNS

= 0.005Ω (see Table 2 for

more details).

Read and write access is allowed to the ACR. The

ACR must be written most significant byte (MSB) first,

then LSB. Whenever the ACR is written, the fractional

accumulation result bits are cleared. The write must

be completed in 3.5s. A write to the ACR forces the

ADC to perform an offset correction conversion and

update the internal offset correction factor. The current measurement and accumulation begin with the

second conversion following a write to the ACR. To

preserve the ACR value in case of power loss, the

ACR value is backed up to EEPROM. The ACR value

is recovered from EEPROM on power-up. See the

Memory Map

for specific address location and back-

up frequency.

Table 2. Resolution and Range vs. Sense Resistor

MSB—ADDRESS 10h LSB—ADDRESS 11h

2

15

214 213 212 211 210 29 2

8

27 26 25 24 23 22 21 2

0

MSb LSb MSb LSb

UNITS: 6.25μV/R

SNS

Figure 10. Accumulated Current Register Format

R

TYPE OF RESOLUTION/RANGE VSS - V

Current Resolution 1.5625μV 78.13μA 104.2μA 156.3μA 312.5μA

Current Range ±51.2mV ±2.56A ±3.41A ±5.12A ±10.2A

ACR Resolution 6.25μVh 312.5μAh 416.7μAh 625μAh 1.250mAh

ACR Range ±409.6mVh ±20.48Ah ±27.30Ah ±40.96Ah ±81.92Ah

SNS

20m 15m 10m 5m

SNS

Page 18

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

18 ______________________________________________________________________________________

Accumulation Bias

In some designs a systematic error or an application

preference requires the application of an arbitrary bias

to the current accumulation process. The Current

Accumulation Bias register (CAB) allows a user-programmed constant positive or negative polarity bias to

be included in the current accumulation process. The

value in CAB can be used to estimate battery currents

that do not flow through the sense resistor, estimate

battery self-discharge, or estimate current levels below

the current measurement resolution. The user-programmed two’s complement value, with bit weighting

the same as the current register, is added to the ACR

once per current conversion cycle. CAB is loaded on

power-up from EEPROM memory.

Cycle Counter

The cycle counter is an absolute count of the cumulative discharge cycles. This register is intended to act as

a “cell odometer.” The LSb is two cycles, which allows

a maximum count of 510 discharge cycles. The register

does not loop. Once the maximum value is reached,

the register is clamped. This register is read and write

accessible while the parameter EEPROM memory block

(block 1) is unlocked. The Cycle Count register

becomes read-only once the EEPROM block is locked.

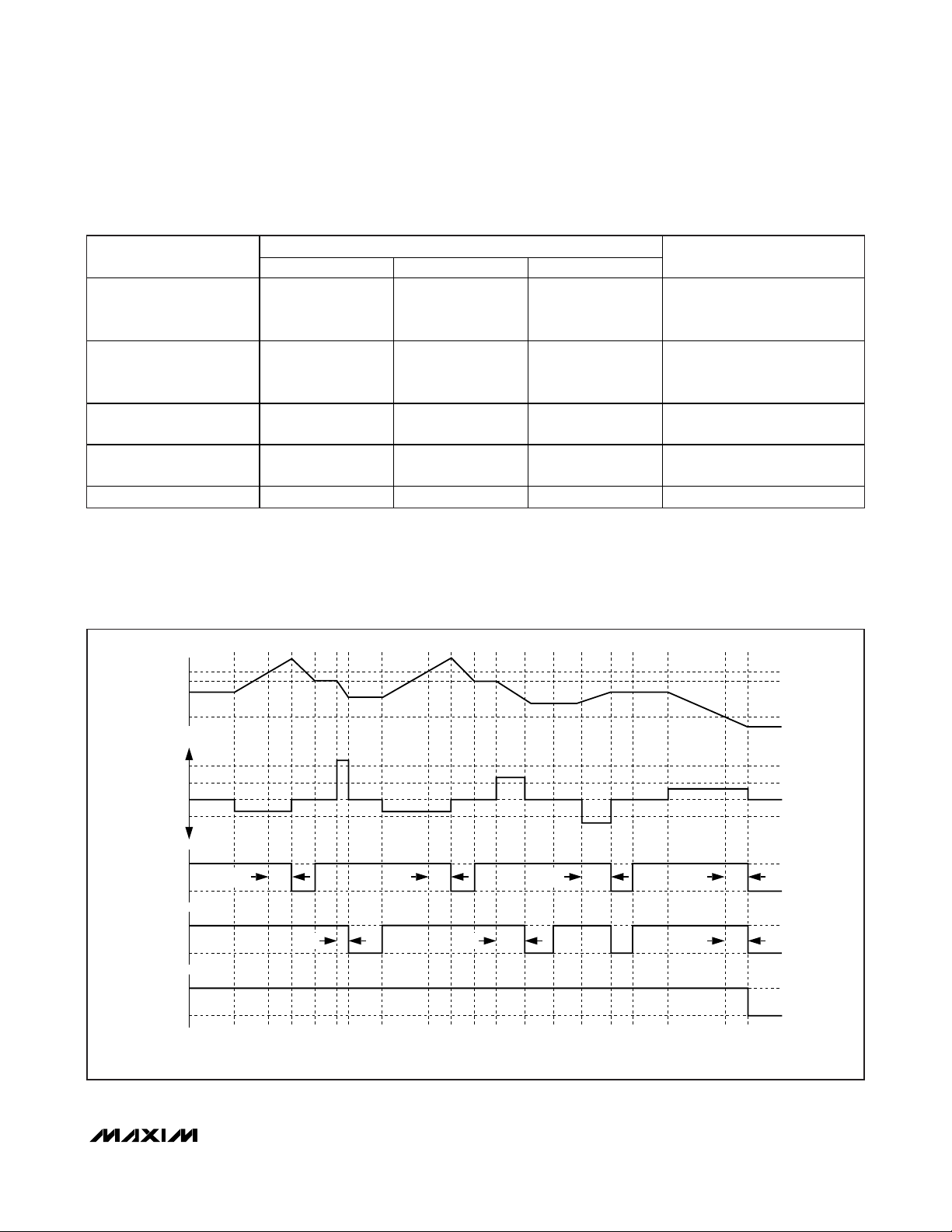

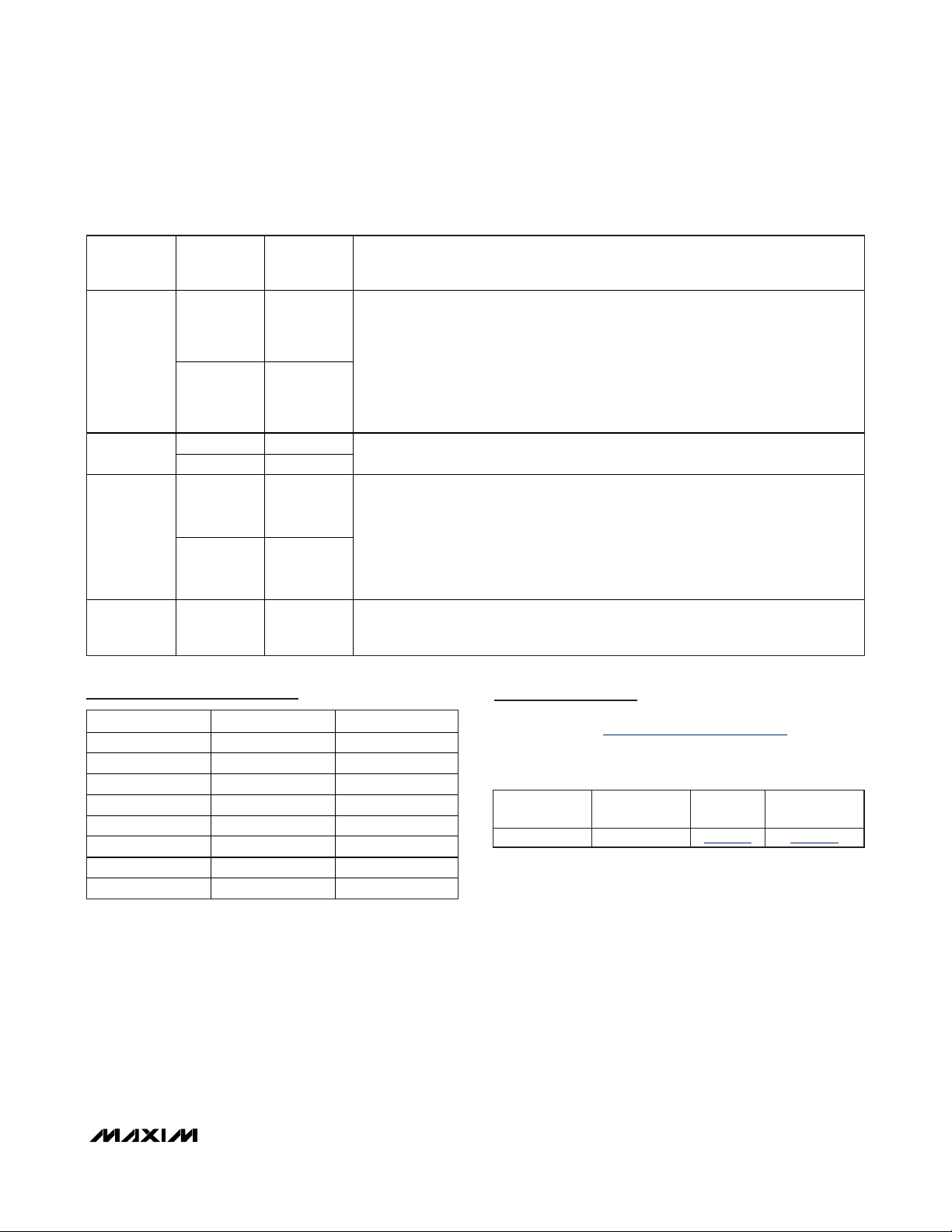

Capacity Estimation Algorithm

Remaining capacity estimation uses real-time measured values and stored parameters describing the cell

characteristics and application operating limits. Figure

13 describes the algorithm inputs and outputs.

Modeling Cell Characteristics

To achieve reasonable accuracy in estimating remaining capacity, the cell performance characteristics over

temperature, load current, and charge-termination point

must be considered. Since the behavior of Li+ cells is

nonlinear, these characteristics must be included in the

capacity estimation to achieve an acceptable level of

accuracy in the capacity estimation. The FuelPack

method used in the DS2775–DS2778 is described in

general in Application Note 131:

Lithium-Ion Cell Fuel

Gauging with Maxim Battery Monitor ICs.

To facilitate

efficient implementation in hardware, a modified version

of the method outlined in Application Note 131 is used

to store cell characteristics in the DS2775–DS2778. Full

and empty points are retrieved in a lookup process that

retraces a piecewise linear model consisting of three

model curves named full, active empty, and standby

empty. Each model curve is constructed with five line

segments, numbered 1 through 5. Above +40°C, the

segment 5 model curves extend infinitely with zero

slope, approximating the nearly flat change in capacity

of Li+ cells at temperatures above +40°C. Segment 4 of

each model curves originates at +40°C on its upper end

and extends downward in temperature to the junction

with segment 3. Segment 3 joins with segment 2, which

in turn joins with segment 1. Segment 1 of each model

curve extends from the junction with segment 2 to infinitely colder temperatures. The three junctions or breakpoints that join the segments (labeled TBP12, TBP23,

and TBP34 in Figure 14) are programmable in 1°C

increments from -128°C to +40°C. The slope or derivative for segments 1, 2, 3, and 4 are also programmable

over a range of 0 to 15,555ppm in steps of 61ppm.

ADDRESS 61h

S 2

6

25 24 23 22 21 2

0

MSb LSb

“S”: SIGN BIT(S)

UNITS: 6.25μV/R

SNS

Figure 11. Current Accumulation Bias Register Format

ADDRESS 1Eh

2

7

26 25 24 23 22 21 2

0

MSb LSb

UNITS: 2 cycle s

Figure 12. Cycle Counter Register Format

Page 19

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 19

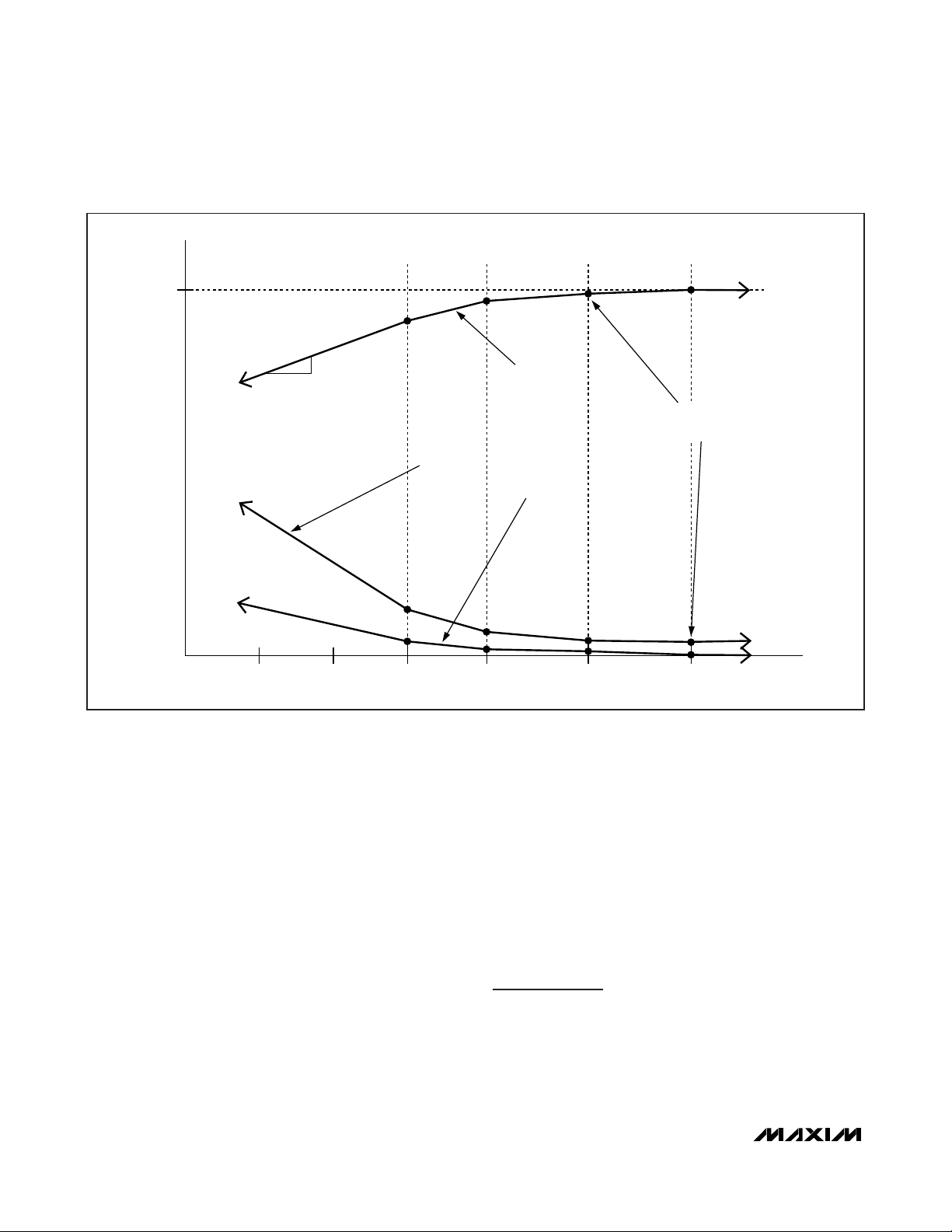

Figure 13. Top-Level Algorithm Diagram

Full

The full curve defines how the full point of a given cell

depends on temperature for a given charge termination. The application’s charge termination method

should be used to determine the table values. The

DS2775–DS2778 reconstruct the full line from cell characteristic table values to determine the full capacity of

the battery at each temperature. Reconstruction occurs

in one-degree temperature increments.

Active Empty

The active-empty curve defines the variation of the

active-empty point over temperature. The active-empty

point is defined as the minimum voltage required for

system operation at a discharge rate based on a highlevel load current (one that is sustained during a highpower operating mode). This load current is

programmed as the active-empty current (IAE), and

should be a 3.5s average value to correspond to values

VOLTAGE (R) FULL FULL(T) (R)

TEMPERATURE (R)

CURRENT (R)

ACCUMULATED

CURRENT (ACR) (RW)

AVERAGE CURRENT (R)

CELL MODEL PARAMETERS

(EEPROM)

AGING CAPACITY (AC)

(2 BYTES EE)

AGE SCALAR (AS)

(1 BYTE EE)

SENSE-RESISTOR PRIME (RSNSP)

(1 BYTE EE)

CHARGE VOLTAGE (VCHG)

(1 BYTE EE)

MINIMUM CHARGE CURRENT (IMIN)

(1 BYTE EE)

CAPACITY LOOKUP

AVAILABLE CAPACITY CALCULATION

ACR HOUSEKEEPING

AGE ESTIMATOR

LEARN FUNCTION

ACTIVE EMPTY AE(T) (R)

STANDBY EMPTY SE(T) (R)

REMAINING ACTIVE-ABSOLUTE

CAPACITY (RAAC) mAh (R)

REMAINING STANDBY-ABSOLUTE

CAPACITY (RSAC) mAh (R)

REMAINING ACTIVE-RELATIVE

CAPACITY (RARC) % (R)

REMAINING STANDBY-RELATIVE

CAPACITY (RSRC) % (R)

USER MEMORY (EEPROM)

16 BYTES

CYCLE COUNTER (EEPROM)

ACTIVE-EMPTY VOLTAGE (VAE)

(1 BYTE EE)

ACTIVE-EMPTY CURRENT (IAE)

(1 BYTE EE)

Page 20

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

20 ______________________________________________________________________________________

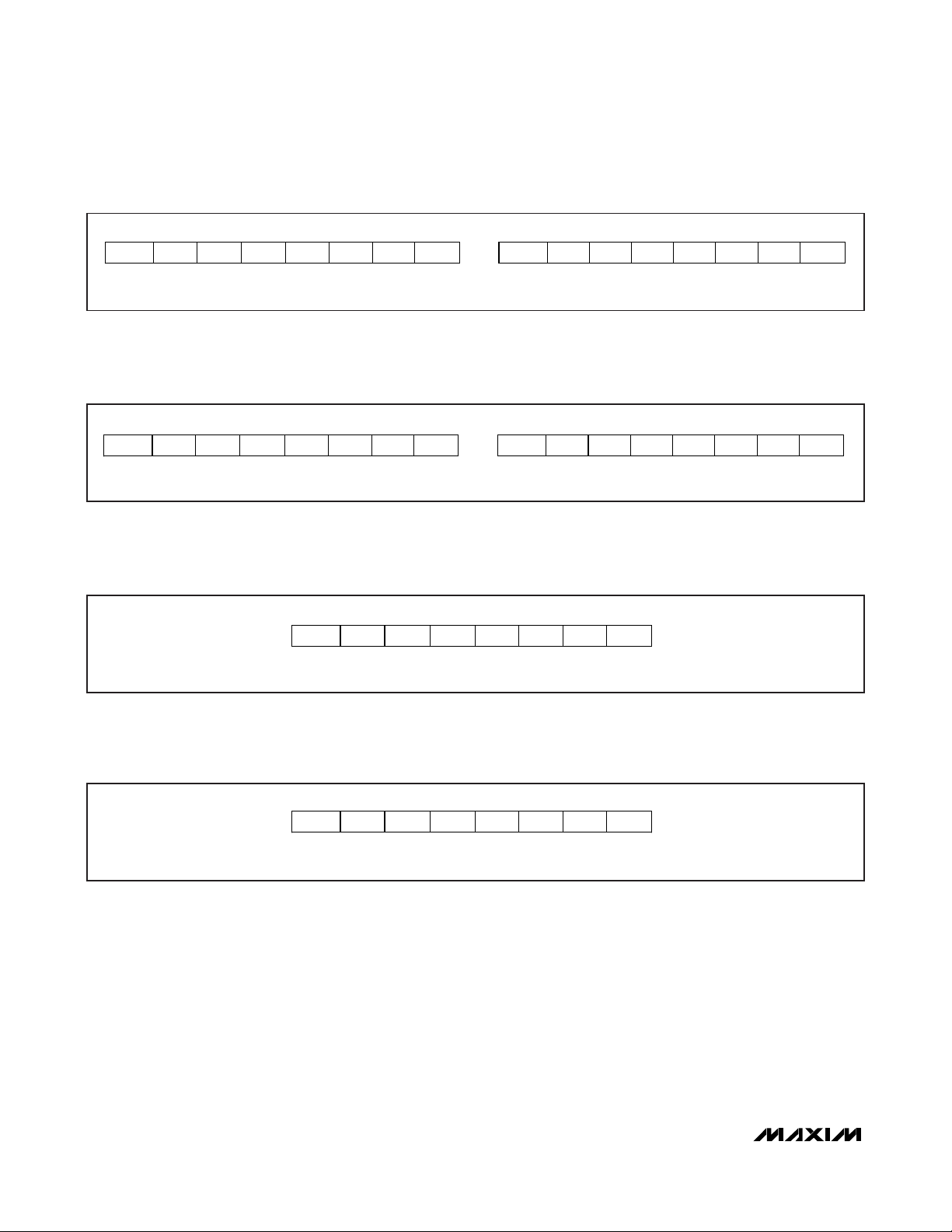

Figure 14. Cell Model Example Diagram

read from the Current register. The specified minimum

voltage, or active-empty voltage (VAE), should be a

110ms average value to correspond to the values read

from the voltage register. The VAE value represents the

average of the two cell’s voltages, V

IN1

and V

IN2

. The

DS2775–DS2778 reconstruct the active-empty line from

the cell characteristic table to determine the activeempty capacity of the battery at each temperature.

Reconstruction occurs in one-degree temperature

increments.

Standby Empty

The standby-empty curve defines the variation of the

standby-empty point over temperature. The standbyempty point is defined as the minimum voltage required

for standby operation at a discharge rate dictated by

the application standby current. In typical handheld

applications, standby empty represents the point that

the battery can no longer support DRAM refresh and

thus the standby voltage is set by the minimum DRAM

voltage-supply requirements. In other applications,

standby empty can represent the point that the battery

can no longer support a subset of the full application

operation, such as games or organizer functions. The

standby-load current and voltage are used for determining the cell characteristics but are not programmed

into the DS2775–DS2778. The DS2775–DS2778 reconstruct the standby-empty line from the cell characteristic table to determine the standby-empty capacity of

the battery at each temperature. Reconstruction occurs

in one-degree temperature increments.

Cell Model Construction

The model is constructed with all points normalized to

the fully charged state at +40°C. All values are stored in

the cell parameter EEPROM block. The +40°C full value

is stored in µVh with an LSb of 6.25µVh. The +40°C

active-empty value is stored as a percentage of +40°C

100%

SEGMENT 1

DERIVATIVE

(ppm/°C)

SEGMENT 2

ACTIVE

EMPTY

SEGMENT 3 SEGMENT 4

FULL

CHARACTERIZATION DATA

STANDBY

EMPTY

SEGMENT 5

CELL

CELL

CHARACTERIZATION

+40°CTBP34TBP23TBP12

Page 21

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 21

full with a resolution of 2

-10

. Standby empty at +40°C is,

by definition, zero and therefore no storage is required.

The slopes (derivatives) of the four segments for each

model curve are stored in the cell parameter EEPROM

block as ppm/°C. The breakpoint temperatures of each

segment are stored there also (refer to Application Note

3584:

Storing Battery Fuel Gauge Parameters in

DS2780

for more details on how values are stored). An

example of data stored in this manner is shown in

Table 3.

Application Parameters

In addition to cell model characteristics, several application parameters are needed to detect the full and

empty points, as well as calculate results in mAh units.

Sense Resistor Prime (RSNSP)

RSNSP stores the value of the sense resistor for use in

computing the absolute capacity results. The value is

stored as a 1-byte conductance value with units of

mhos (1/Ω). RSNSP supports resistor values of 1Ω to

3.922mΩ. RSNSP is located in the parameter EEPROM

block.

RSNSP = 1/R

SNS

(units of mhos; 1/Ω)

Charge Voltage (VCHG)

VCHG stores the charge voltage threshold used to

detect a fully charged state. The voltage is stored as a

1-byte value with units of 19.5mV and can range from 0

to 4.978V. VCHG should be set marginally less than the

average cell voltage at the end of the charge cycle to

ensure reliable charge termination detection. VCHG is

located in the parameter EEPROM block.

TEMPERATURE

CELL MODEL

PARAMETERS

(EEPROM)

LOOKUP

FUNCTION

FULL(T)

AE(T)

SE(T)

Figure 15. Lookup Function Diagram

Table 3. Example Cell Characterization Table (Normalized to +40°C)

Manufacturer’s Rated Cell Capacity: 1000mAh

Charge Voltage: 4.2V Termination Current: 50mA

Active Empty (V): 3.0V Standby Empty (I): 300mA

Sense Resistor: 0.020

SEGMENT BREAKPOINTS

TBP12 = -12°C

TBP23 = 0°C

TBP34 = 18°C

CALCULATED VALUE

Full 1051 3601 3113 1163 854

Active Empty 2380 1099 671 305

Standby Empty 1404 427 244 183

+40°C NOMINAL

(mAh)

SEGMENT 1

(ppm/°C)

SEGMENT 2

(ppm/°C)

SEGMENT 3

(ppm/°C)

SEGMENT 4

(ppm/°C)

Page 22

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

22 ______________________________________________________________________________________

Minimum Charge Current (IMIN)

IMIN stores the charge-current threshold used to detect

a fully charged state. It is stored as a 1-byte value with

units of 50µV (IMIN x R

SNS

) and can range from 0 to

12.75mV. Assuming R

SNS

= 20mΩ, IMIN can be programmed from 0 to 637.5mA in 2.5mA steps. IMIN

should be set marginally greater than the charge current at the end of the charge cycle to ensure reliable

charge termination detection. IMIN is located in the

parameter EEPROM block.

Active-Empty Voltage (VAE)

VAE stores the voltage threshold used to detect the

active-empty point. The value is stored in 1 byte with

units of 19.5mV and can range from 0 to 4.978V. VAE is

stored as an average of the cell’s voltages. VAE is located in the parameter EEPROM block. See the

Modeling

Cell Characteristics

section for more information.

Active-Empty Current (IAE)

IAE stores the discharge-current threshold used to

detect the active-empty point. The unsigned value represents the magnitude of the discharge current and is

stored in 1 byte with units of 200µV and can range from

0 to 51.2mV. Assuming R

SNS

= 20mΩ, IAE can be programmed from 0 to 2550mA in 10mA steps. IAE is located in the parameter EEPROM block. See the

Modeling

Cell Characteristics

section for more information.

Aging Capacity (AC)

AC stores the rated cell capacity, which is used to estimate the decrease in battery capacity that occurs during normal use. The value is stored in 2 bytes in the

same units as the ACR (6.25µVh). When set to the manufacturer’s rated cell capacity, the aging estimation rate

is approximately 2.4% per 100 cycles of equivalent full

capacity discharges. Partial discharge cycles are

added to form equivalent full capacity discharges. The

default aging estimation results in 88% capacity after

500 equivalent cycles. The aging estimation rate can

be adjusted by setting the AC to a value other than the

cell manufacturer’s rating. Setting AC to a lower value

accelerates the aging estimation rate. Setting AC to a

higher value retards the aging estimation rate. The AC

is located in the parameter EEPROM block.

Age Scalar (AS)

AS adjusts the cell capacity estimation results downward to compensate for aging. The AS is a 1-byte value

that has a range of 49.2% to 100%. The LSb is weighted at 0.78% (precisely 2-7). A value of 100% (128 decimal or 80h) represents an unaged battery. A value of

95% is recommended as the starting AS value at the

time of pack manufacture to allow the learning of a larger capacity on batteries that have an initial capacity

greater than the rated cell capacity programmed in the

cell characteristic table. The AS is modified by aging

estimation introduced under aging capacity and by the

learn function.

Batteries are typically considered worn out when the full

capacity reaches 80% of the rated capacity; therefore,

the AS value is not required to range to 0%. It is

clamped to 50% (64 decimal or 40h). If a value of 50%

is read from the AS, the host should prompt the user to

initiate a learning cycle.

The host system has read and write access to the AS;

however, caution should be exercised when writing it to

ensure that the cumulative aging estimate is not overwritten with an incorrect value. The AS is automatically

saved to EEPROM. The EEPROM value is recalled on

power-up.

Capacity Estimation Operation

Cycle-Count-Based Aging Estimation

As previously discussed, the AS register value is

adjusted occasionally based on cumulative discharge.

As the ACR register decrements during each discharge

cycle, an internal counter is incremented until equal to

32 times the AC. The AS is then decremented by one,

resulting in a decrease of the scaled full battery capacity by 0.78% (approximately 2.4% per 100 cycles). The

internal counter is reset in the event of a learn cycle.

See the

Aging Capacity (AC)

section for recommenda-

tions on customizing the age estimation rate.

Learn Function

Because Li+ cells exhibit charge efficiencies near unity,

the charge delivered to a Li+ cell from a known empty

point to a known full point is a dependable measure of

the cell’s capacity. A continuous charge from empty to

full results in a learn cycle. First, the active-empty point

must be detected. The learn flag (LEARNF) is set at this

point. Then, once charging starts, the charge must continue uninterrupted until the battery is charged to full.

Upon detecting full, the LEARNF is cleared, the chargeto-full (CHGTF) flag is set, and the AS is adjusted

according to the learned capacity of the cell.

Full capacity estimation based on the learn function is

more accurate than the cycle-count-based estimation

introduced under aging capacity. The learn function

reflects the current performance of the cell. Cyclecount-based estimation is an approximation derived

from the manufacturer’s recommendation for a typical

cell. Therefore, the internal counter used for cycle-

Page 23

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 23

count-based estimation is reset after a learn cycle. The

cycle-count-based estimation is used only in the

absence of a learn cycle.

ACR Housekeeping

The ACR value is adjusted occasionally to maintain the

coulomb count within the model curve boundaries. When

the battery is charged to full (CHGTF set), the ACR is set

equal to the age-scaled full lookup value at the present

temperature. If a learn cycle is in progress, correction of

the ACR value occurs after the AS is updated. When an

empty condition is detected (LEARNF and/or AEF set),

the ACR adjustment is conditional:

• If the AEF is set and the LEARNF is not set, the

active-empty point was not detected. The battery is

likely below the active-empty capacity of the model.

The ACR is set to the active-empty model value at

present temperature only if it is greater than the

active-empty model value at present temperature.

• If the AEF is set, the LEARNF is not set, and the ACR

is below the active-empty model value at present

temperature, the ACR is not updated.

• If the LEARNF is set, the battery is at the active-

empty point and the ACR is set to the active-empty

model value.

Full Detect

Full detection occurs when the average of V

IN1

and

V

IN2

voltage registers remain continuously above the

charge voltage (VCHG) threshold for the duration of two

average current (IAVG) readings, and both IAVG readings are below terminating current (IMIN). The two consecutive IAVG readings must also be positive and

nonzero (>16 LSB). This ensures that removing the battery from the charger does not result in a false detection of full. Full detect sets the charge to full (CHGTF)

bit in the Status register.

Active-Empty Point Detect

Active-empty point detection occurs when the average

of V

IN1

and V

IN2

voltage registers drops below the VAE

threshold and the two previous current readings are

above IAE. This captures the event of the battery reaching the active-empty point. Note that the two previous

current readings must be negative and greater in magnitude than IAE (i.e., a larger discharge current than

specified by the IAE threshold). Qualifying the voltage

level with the discharge rate ensures that the activeempty point is not detected at loads much lighter than

those used to construct the model. Also, the activeempty point must not be detected when a deep discharge at a very light load is followed by a load greater

than IAE. Either case would cause a learn cycle on the

following charge to include part of the standby capacity

in the measurement of the active capacity. Activeempty point detection sets the learn flag (LEARNF) bit

in the Status register.

Note: Do not confuse the active-empty point with the

active-empty flag. The active-empty flag is set only

when the VAE threshold is passed.

Result Registers

The DS2775–DS2778 process measurement and cell

characteristics on a 3.5s interval and yield seven result

registers. The result registers are sufficient for direct

display to the user in most applications. The host system can produce customized values for system use or

user display by combining measurement, result, and

user EEPROM values.

FULL(T)

The full capacity of the battery at the present temperature is reported normalized to the +40°C full value. This

15-bit value reflects the cell model full value at the

given temperature. The FULL(T) register reports values

between 100% and 50% with a resolution of 61ppm

(precisely 2

-14

). Though the register format permits values greater than 100%, the register value is clamped to

a maximum value of 100%.

Active Empty, AE(T)

The active-empty capacity of the battery at the present

temperature is reported normalized to the +40°C full

value. This 13-bit value reflects the cell model activeempty value at the given temperature. The AE(T) register reports values between 0% and 49.8% with a

resolution of 61ppm (precisely 2

-14

).

Standby Empty, SE(T)

The standby-empty capacity of the battery at the present temperature is reported normalized to the +40°C

full value. This 13-bit value reflects the cell model

standby-empty value at the current temperature. The

SE(T) register reports values between 0% and 49.8%

with a resolution of 61ppm (precisely 2

-14

).

Page 24

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

24 ______________________________________________________________________________________

The RAAC register reports the capacity available under the current temperature conditions to the the active-empty

point in absolute units of milliamps/hour (mAh). RAAC is 16 bits.

The RSAC register reports the remaining battery capacity available under the current temperature conditions to the

standby-empty point capacity in absolute units of milliamps/hour (mAh). RSAC is 16 bits.

The RARC register reports the remaining battery capacity available under the current temperature conditions to the

active-empty point in relative units of percent (%). RARC is 8 bits.

The RSRC register reports the remaining battery capacity available under the current temperature conditions to the

standby-empty point capacity in relative units of percent (%). RSRC is 8 bits.

Calculation of Results

RAAC [mAh] = (ACR[mVh] - AE(T) x FULL40[mVh]) x RSNSP [mhos]*

RSAC [mAh] = (ACR[mVh] - SE(T) x FULL40[mVh]) x RSNSP [mhos]*

RARC [%] = 100% x (ACR[mVh] - AE(T) x FULL40[mVh])/{(AS x FULL(T) - AE(T)) x FULL40[mVh]}

RSRC [%] = 100% x (ACR[mVh] - SE(T) x FULL40[mVh])/{(AS x FULL(T) - SE(T)) x FULL40[mVh]}

*

RSNSP = 1/R

SNS

MSB—ADDRESS 02h LSB—ADDRESS 03h

2

15

214 213 212 211 210 29 2

8

27 26 25 24 23 22 21 2

0

MSb LSb MSb LSb

UNITS: 1.6mAh

Figure 16. Remaining Active Absolute Capacity (RAAC) [mAh]

MSB—ADDRESS 04h LSB—ADDRESS 05h

2

15

214 213 212 211 210 29 2

8

27 26 25 24 23 22 21 2

0

MSb LSb MSb LSb

UNITS: 1.6mAh

Figure 17. Remaining Standby Absolute Capacity (RSAC) [mAh]

MSB– ADDRESS 06h

2

15

214 213 212 211 210 29 2

8

MSb LSb

UNITS: 1%

Figure 18. Remaining Active Relative Capacity (RARC) [%]

MSB– ADDRESS 07h

2

15

214 213 212 211 210 29 2

8

MSb LSb

UNITS: 1%

Figure 19. Remaining Standby Relative Capacity (RSRC) [%]

Page 25

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 25

Protection, Status, and Control Registers

Protection Register Format

The Protection register reports events detected by the Li+ safety circuit on bits [3:2]. Bits 0 and 1 are used to disable

the charge and discharge FET gate drivers. Bits [3:2] are set by internal hardware only. Bits 2 and 3 are cleared by

hardware only. Bits 0 and 1 are set on power-up and a transition from sleep to active modes. While in active mode,

these bits can be cleared to disable the FET gate drive of either or both FETs. Setting these bits only turns on the

FETs if there are no protection faults.

Protection Register (00h)

Bits 7 to 4: Reserved.

Bit 3: Charge Control Flag (CC). CC indicates the logic state of the CC pin driver. The CC flag is set to indicate CC

high and is cleared to indicate CC low. The CC flag is read-only.

Bit 2: Discharge Control Flag (DC). DC indicates the logic state of the DC pin driver. DC flag is set to indicate DC

high and is cleared to indicate DC low. DC flag is read-only.

Bit 1: Charge-Enable Bit (CE). CE must be set to allow the CC pin to drive the charge FET to the on state. CE acts

as an enable input to the safety circuit. If all safety conditions are met and CE is set, the CC pin drives to VCP. If CE

is cleared, the CC pin is driven low to disable the charge FET. The power-up default state of CE is 1.

Bit 0: Discharge-Enable Bit (DE). DE must be set to allow the DC pin to drive the discharge FET to the on state. DE

acts as an enable input to the safety circuit. If all safety conditions are met and DE is set, the DC pin drives to VCP. If

DE is cleared, the DC pin is driven low to disable the discharge FET. The power-up default state of DE is 1.

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

X X X X CC DC CE DE

Page 26

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

26 ______________________________________________________________________________________

Status Register Format

The Status register contains bits that report the device status. All bits are set internally. The CHGTF, AEF, SEF, and

LEARNF bits are read-only.

Status Register (01h)

Bit 7: Charge-Termination Flag (CHGTF). CHGTF is set to indicate that the average of the voltages on V

IN1

and

V

IN2

and the Average Current register values have persisted above the VCHG and below the IMIN thresholds sufficiently long enough to detect a fully charged condition. CHGTF is cleared when RARC is less than 90%. CHGTF is

read-only.

Bit 6: Active-Empty Flag (AEF). AEF is set to indicate that the battery is at or below the active-empty point. AEF is

set when the average of the voltages on V

IN1

and V

IN2

is less than the VAE threshold. AEF is cleared when RARC is

greater than 5%. AEF is read-only.

Bit 5: Standby-Empty Flag (SEF). SEF is set to indicate RSRC is less than 10%. SEF is cleared when RSRC is

greater than 15%. SEF is read-only.

Bit 4: Learn Flag (LEARNF). LEARNF indicates that the current-charge cycle can be used to learn the battery

capacity. LEARNF is set when the active-empty point is detected. This occurs when the average of the voltages on

V

IN1

and V

IN2

drops below the VAE threshold and the two previous current register values were negative and

greater in magnitude than the IAE threshold. See the

Active-Empty Point Detect

section for additional information.

LEARNF is cleared when any of the following occur:

1) Learn cycle completes (CHGTF set).

2) Current register value becomes negative indicating discharge current flow.

3) ACR = 0.

4) ACR value is written or recalled from EEPROM.

5) Sleep mode is entered.

LEARNF is read-only.

Bit 3 to 0: Reserved.

BIT 7 BIT 6 BIT 5 BIT 4 BIT 3 BIT 2 BIT 1 BIT 0

CHGTF AEF SEF LEARNF X X X X

Page 27

DS2775/DS2776/DS2777/DS2778

2-Cell, Stand-Alone, Li+ Fuel-Gauge IC with

Protector and Optional SHA-1 Authentication

______________________________________________________________________________________ 27

Control Register Format

All Control register bits are read and write accessible. The Control register is recalled from parameter EEPROM

memory at power-up. Register bit values can be modified in shadow RAM after power-up. Power-up default values

are saved by using the Copy Data command.

Control Register (60h)

Bit 7: Negative Blanking Enable (NBEN). A value of 1 enables blanking of negative current values up to 25µV. A

value of 0 disables blanking of negative currents. The power-up default of NBEN = 0.

Bit 6: Undervoltage Enable (UVEN). A value of 1 allows the DS2775–DS2778 to enter sleep mode when the average of the voltages on V

IN1

and V

IN2

is less than VUVand DQ is stable at either logic level for t

SLEEP

. A value of 0