Page 1

K

r

查询DS21458DK供应商

www.maxim-ic.com

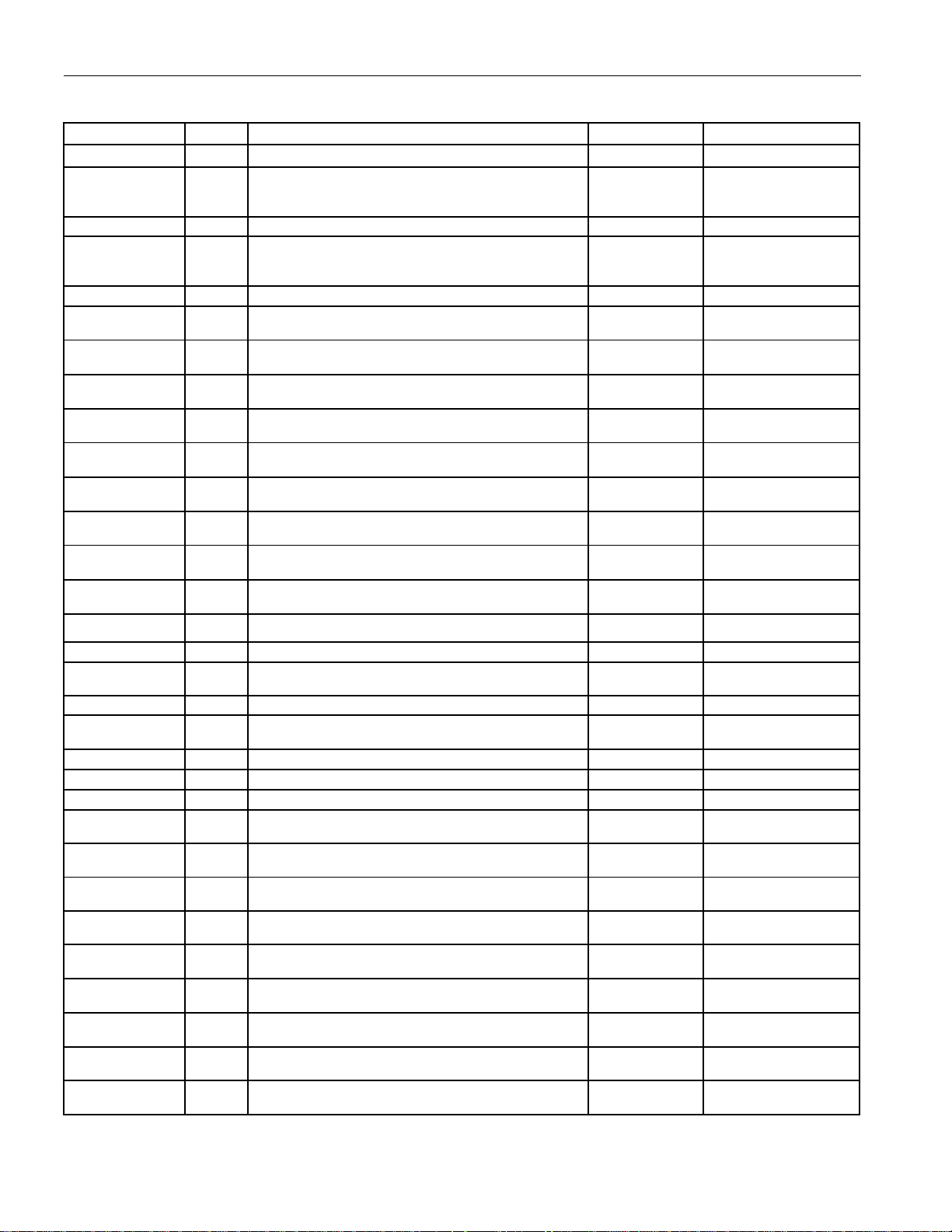

GENERAL DESCRIPTION

The DS21458DK is an easy-to-use evaluation board

for the DS21458 quad T1/E1/J1 transceiver. The

DS21458DK is intended to be used as a daughter

card with the DK101 motherboard or the DK2000

motherboard. The DS21458DK comes complete with

a DS21458 quad SCT, transformers, termination

resistors, configuration switches, line-protection

circuitry, network connectors, and motherboard

connectors. The DK101/DK2000 motherboard and

Dallas’ ChipView software give point-and-click

access to configuration and status registers from a

Windows-based PC. On-board LEDs indicate

receive loss-of-signal and interrupt status. An onboard FPGA contains mux logic to connect framer

ports to one another or to the DK2000 in a variety of

configurations.

Each DS21458DK is shipped with a free DK101

motherboard. For complex applications, the DK2000

high-performance demo kit motherboard can be

purchased separately.

Windows is a registered trademark of Microsoft Corp.

DESIGN KIT CONTENTS

DS21458DK Design Kit Daughter Card

DK101 Low-Cost Motherboard

CD ROM

ChipView Software

DS21458DK Data Sheet

DK101 Data Sheet

DS21458 Data Sheet

DS21458D

Quad T1/E1/J1 Transceive

Design Kit Daughter Card

FEATURES

Demonstrates Key Functions of DS21458 Quad

T1/E1/J1 Transceiver

Includes DS21458 Quad LIU, Transformers,

BNC and RJ45 Network Connectors, and

Termination Passives

Compatible with DK101 and DK2000 Demo Kit

Motherboards

DK101/DK2000 and ChipView Software Provide

Point-and-Click Access to the DS21458 Register

Set

All Equipment-Side Framer Pins are Easily

Accessible for External Data Source/Sink

Memory-Mapped FPGA Provides Flexible

Clock/Data/Sync Connections Among Framer

Ports and DK2000 Motherboard

LEDs for Loss-of-Signal and Interrupt Status

Easy-to-Read Silk Screen Labels Identify the

Signals Associated with all Connectors, Jumpers,

and LEDs

Network Interface Protection for Overvoltage and

Overcurrent Events

ORDERING INFORMATION

PART DESCRIPTION

DS21458DK

DS21458 Design Kit Daughter Card

(with included DK101 Motherboard)

1 of 32 REV: 012506

Page 2

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

COMPONENT LIST

DESIGNATION QTY DESCRIPTION SUPPLIER PART

C1–C8 8

C9, C10, C12,

C18, C22–C33,

C35, C38–C43

C11, C13–C15 4

C16, C17, C19–

C21, C34, C36,

C45, C46

C37, C44 2

CH1 1 Quad-port choke

DS1 1 LED, red, SMD Panasonic LN1251C

DS2–DS6 5 LED, green, SMD Panasonic LN1351C

F1–F16 16 1.25A, 250V fuses, SMT Teccor F1250T

J1 1 10-pin connectors, dual row, vertical Digi-Key S2012-05-ND

J2–J9 8 5-pin BNC connectors, vertical Cambridge CP-BNCPC-004

J10 1

J11, J12 2 50-pin sockets, SMD, dual row, vertical Samtec TFM-125-02-S-D-LC

J13 1

J14 1 1Mbit flash-based configuration memory Xilinx XCF01SV020C

PRT1–PRT4 4 6-pin through-hole slide switches DPDT Tyco SSA22

R1, R2, R4, R26,

R39, R41, R45

R3, R27 2

R5–R12, R14–

R21, R48

R13, R47 2 Not populated Panasonic Not populated

R22–R25 4

R29–R36 8

R40, R42–R44,

R46, R49

T1 1

U1 1

U2 1

U3 1

U4 1

Z1–Z8 8

Z9–Z16 8

Z17–Z32 16

0.22µF, 50V ceramic capacitors

23

0.1µF 10%, 16V ceramic capacitors (0603)

0.1µF 10%, 25V ceramic capacitors (1206)

9

1µF 10%, 16V ceramic capacitors (1206)

10µF 20%, 10V ceramic capacitors (1206)

8-pin, 4-port jack

Right-angle RJ45

12-pin connector, dual row, vertical

Not populated

7

10kΩ 5%, 1/10W resistors (0805)

1.0kΩ 5%, 1/10W resistors (0805)

17

0Ω 5%, 1/8W resistors (1206)

51.1Ω 5%, 1/10W resistors (0805)

61.9Ω 1%, 1/8W resistors (1206)

6

330Ω 5%, 1/10W MF resistors (0805)

SMT 32-pin octal T1/E1 transformer,

transmit/receive, 1:2

2.5V FPGA Spartan (Xilinx)

144-pin TQFP

3.3V T1/E1/J1 quad transceiver

0°C to +70°C, 256-pin BGA

1M PROM for FPGA

44-pin TQFP

8-pin µMAX, SO

2.5V or Adj

50A, 6V Sidactor

DO214 SMD

500A, 25V Sidactor

DO214 SMD

500A, 170V Sidactor

DO214 SMD

2 of 32

Panasonic PCF1152CT-ND

Phycomp 06032R104K7B20D

Panasonic ECJ-3VB1E104K

Panasonic ECJ-3YB1C105K

Panasonic ECJ-3YB1A106M

Pulse

Engineering

Molex 43223-8140

Digi-Key S2012-06-ND

Panasonic ERJ-6GEYJ103V

Panasonic ERJ-6GEYJ102V

Panasonic ERJ-8GEYJ0R00V

Panasonic ERJ-6GEY51R1V

Panasonic ERJ-8ENF61R9V

Panasonic ERA-6GEY331V

Pulse

Engineering

Xilinx XC2S50-5TQ144C

Dallas

Semiconductor

Xilinx Not populated

Maxim MAX1792EUA25

Teccor P0080SAMC

Teccor P0300SCMC

Teccor P1800SCMC

T8132

TX1473

DS21458

Page 3

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

r

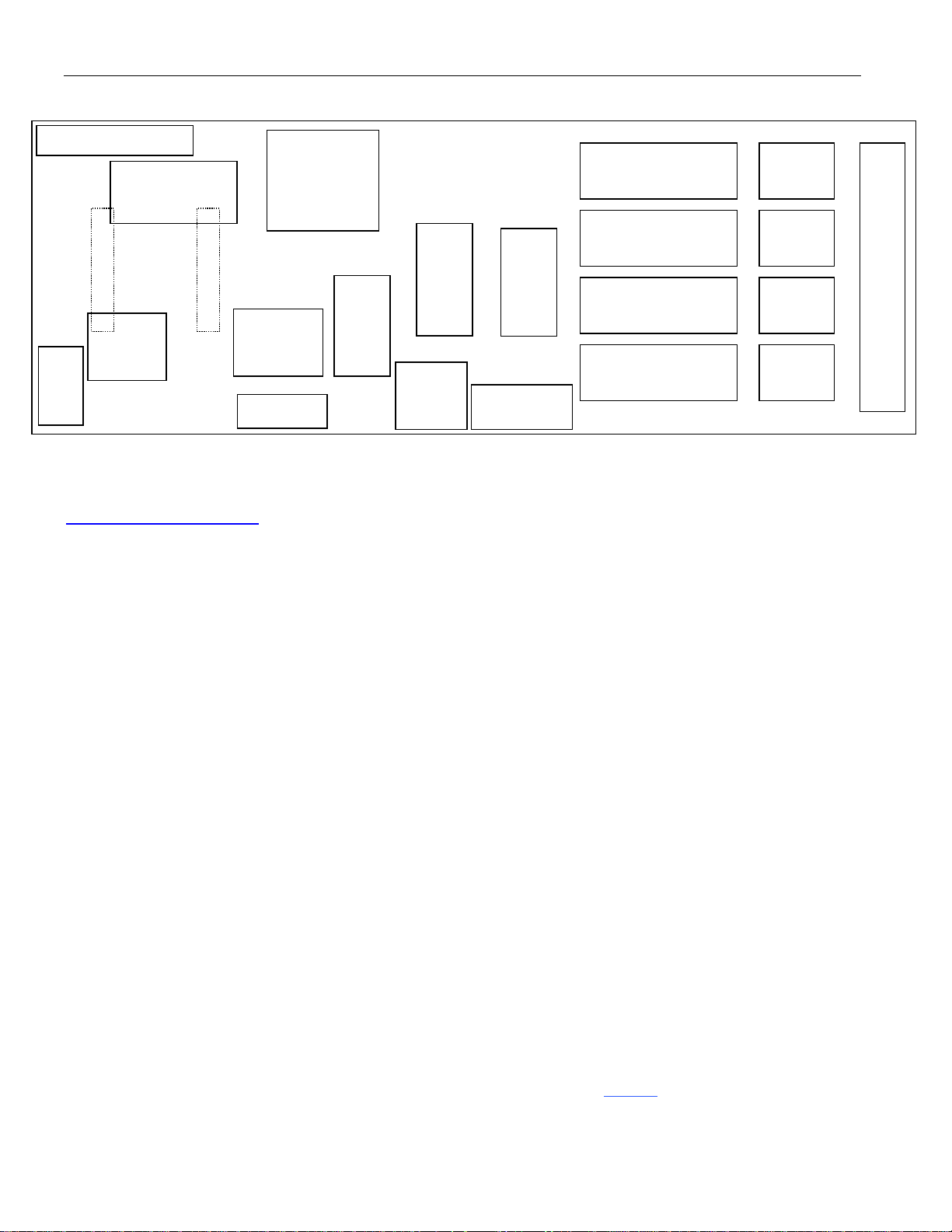

BOARD FLOORPLAN

RLOS 4-1 LEDs

Dallas

Semiconducto

DS21458

IMPEDANCE

MATCHING/

LINE

PROTECTION

LINE

PROTECTION

PORT 4

PROTECTION

PORT 3

LINE

BNC

PORT

4

BNC

PORT

3

CPU INTERFACE

FPGA

INT LED

CPU INTERFACE

FPGA

STATUS

LED

JTAG

TEST

PCM BUS

QUAD PORT

FPGA

CONFIG

PROM

TRANSFORMER

CHOKE

QUAD PORT

2.5V FPGA

SUPPLY

LINE

PROTECTION

PORT 2

LINE

PROTECTION

PORT 1

BNC

PORT

2

BNC

PORT

1

BASIC CONFIGURATION

This design kit relies upon several supporting files, which are available for downloading on our website at

www.maxim-ic.com/telecom

Hardware Configuration

Using the DK101 Processor Board:

· Connect the daughter card to the DK101 processor board.

· Supply 3.3V to the banana-plug receptacles marked GND and VCC_3.3V. (The external 5V connector is

unused. Additionally, the TIM 5V supply headers are unused.)

· All processor board DIP switch settings should be in the ON position with exception of the flash programming

switch, which should be OFF.

· From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If

the default installation options were used, click the Start button on the Windows toolbar and select Programs ®

ChipView ® ChipView.

Using the DK2000 Processor Board:

· Connect the daughter card to the DK2000 processor board.

· Connect J1 to the power supply that is delivered with the kit. Alternately, a PC power supply may be connected

to connector J2.

· From the Programs menu, launch the host application named ChipView.EXE. Run the ChipView application. If

the default installation options were used, click the Start button on the Windows toolbar and select Programs ®

ChipView ® ChipView.

General

· Upon power-up, the RLOS LEDs (green) will not be lit, the INT LED (red) will not be lit, but the FPGA Status

LED (green) will be lit.

· When operating in E1 mode, slide SW1–SW4 to E1 Mode (grounding the BNC shell). When operating in T1

mode, slide SW1–SW4 to T1 Mode.

Miscellaneous

· Clock frequencies and certain pin bias levels are provided by a register-mapped FPGA that is on the DS21458

daughter card.

· The definition file for this FPGA is named DS21458DC_FPGA.def. See Table 2

definitions. A drop-down menu on the top of the screen allows for switching between definition files.

· All files referenced above are available for download as described in the Basic Configuration section.

. See the DS21458DK QuickView data sheet for these files.

for the FPGA Register Map

3 of 32

RJ45 x 4

Page 4

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Quick Setup (Demo Mode)

· The PC will load ChipView offering a choice among DEMO MODE, REGISTER VIEW, and TERMINAL MODE.

Select Demo Mode.

· The program will request a configuration file. Select among the displayed files, which are

DS2155_E1_DSNCOM_DRVR.cfg or DS2155_T1_DSNCOM_DRVR.cfg.

· The Demo Mode screen will appear. Upon external loopback the RLOS indicators will turn green.

·

Note: Demo Mode interacts with the device driver, which resides in the DK101/DK2000 firmware. The current

implementation of this driver is for one device. As such, the demo mode will only interact with Port 1. With

minor changes, the device driver is extendible to N devices.

Quick Setup (Register View)

· The PC will load ChipView offering a choice among DEMO MODE, REGISTER VIEW, and TERMINAL MODE.

Select Register View.

· The program will request a definition file. Select DS21458DC_FPGA.def through the Links section. This will

also load DS21458DC.def.

· The Register View Screen will appear, showing the register names, acronyms, and values for the DS21458.

· Predefined Register settings for several functions are available as initialization files.

- INI files are loaded by selecting the menu F

- Load the INI file DS21458_T1_BERT_ESF.ini.

- After loading the INI file, the following may be observed:

o The RLOS LEDs turns green upon external loopback.

o All four ports of the DS21458 begin transmitting a Daly pattern. When external loopback is applied, the

BERT bit count registers BBC1 to BBC3 and BEC1 to BEC3 may be updated by clearing and setting

BC1.LC and clicking the ‘Read All’ button.

ile®Reg Ini File®Load Ini File.

4 of 32

Page 5

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

ADDRESS MAP

DK101 daughter card address space begins at 0x81000000

DK2000 daughter card address space begins at:

0x30000000 for slot 0

0x40000000 for slot 1

0x50000000 for slot 2

0x60000000 for slot 3

All offsets given below are relative to the beginning of the daughter card address space (shown above).

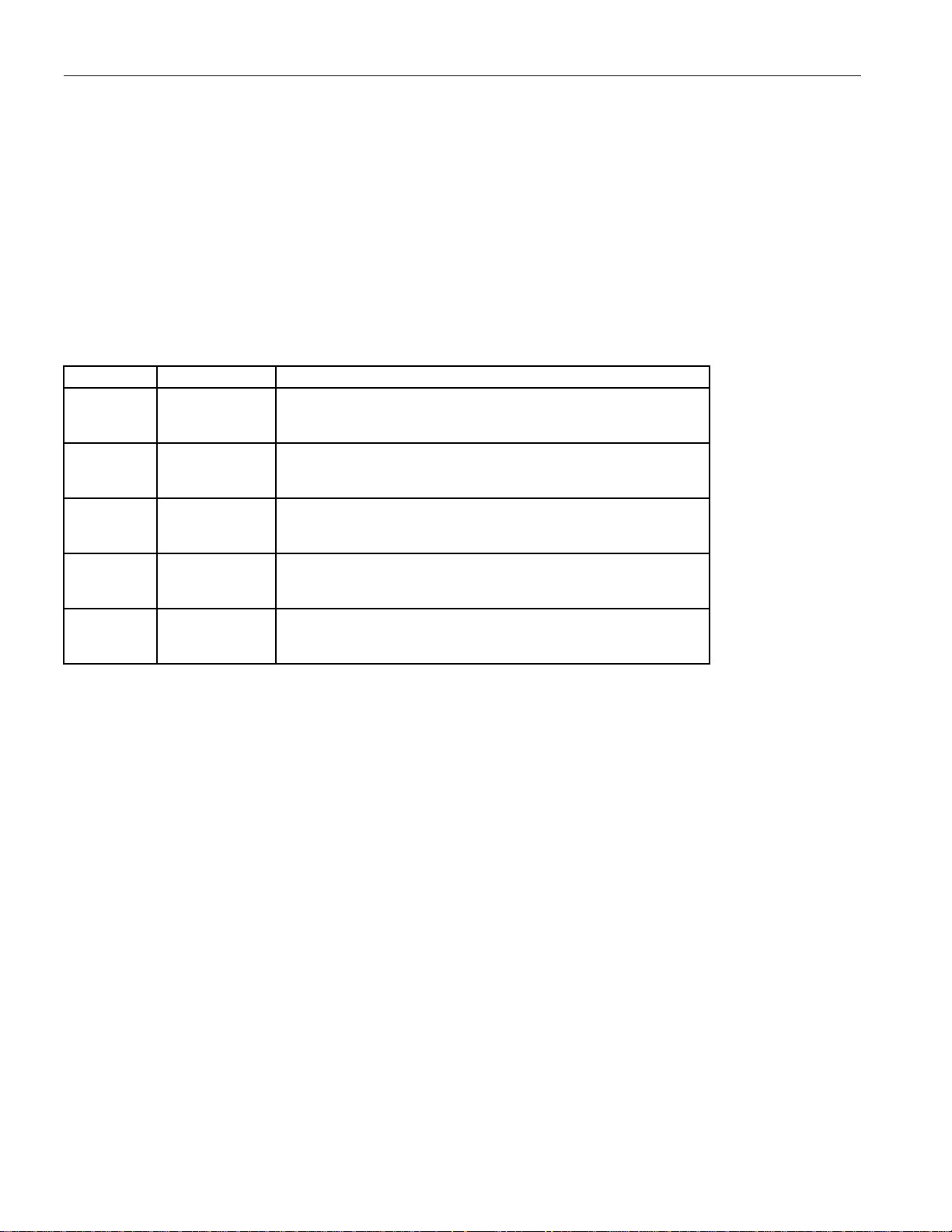

Table 1. Daughter Card Address Map

OFFSET DEVICE DESCRIPTION

0X0000

to

0X0015

0X1000

to

0X10ff

0X1100

to

0X11ff

0X1200

to

0X12ff

0X1300

to

0X13ff

Registers in the FPGA can be easily modified using the ChipView host-based user-interface software along with

the definition file named “DS21458DC_FPGA.def.”

FPGA Board identification and clock/signal routing

T1/E1/J1

Transceiver #1

T1/E1/J1

Transceiver #2

T1/E1/J1

Transceiver #3

T1/E1/J1

Transceiver #4

DS21458 T1/E1/J1 transceiver, port 1

DS21458 T1/E1/J1 transceiver, port 2

DS21458 T1/E1/J1 transceiver, port 3

DS21458 T1/E1/J1 transceiver, port 4

5 of 32

Page 6

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

FPGA REGISTER MAP

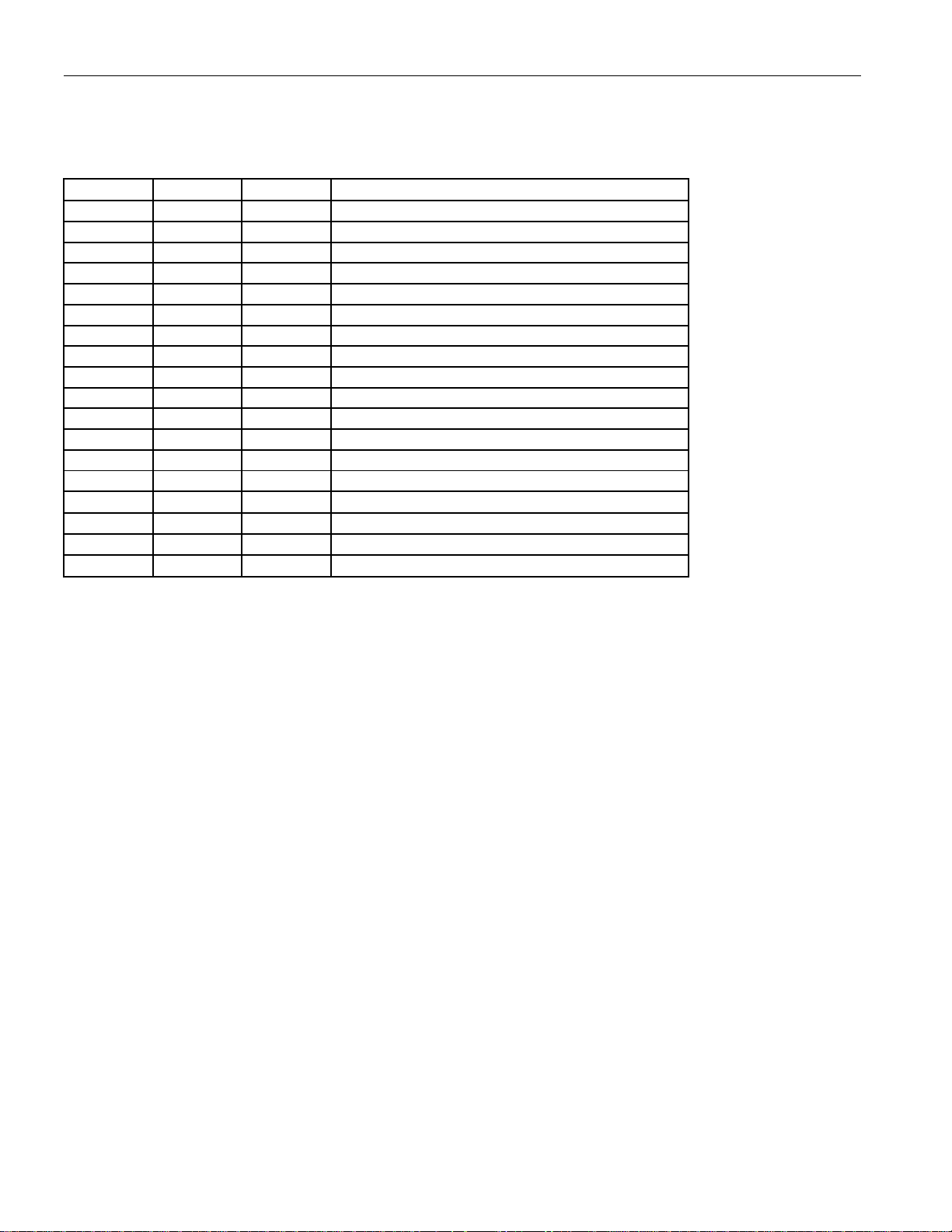

Table 2. FPGA Register Map

OFFSET NAME TYPE DESCRIPTION

0X0000 BID Read Only BOARD ID

0X0002 XBIDH Read Only HIGH NIBBLE EXTENDED BOARD ID

0X0003 XBIDM Read Only MIDDLE NIBBLE EXTENDED BOARD ID

0X0004 XBIDL Read Only LOW NIBBLE EXTENDED BOARD ID

0X0005 BREV Read Only BOARD FAB REVISION

0X0006 AREV Read Only BOARD ASSEMBLY REVISION

0X0007 PREV Read Only PLD REVISION

0X0011 MCSR Control DS21458 MCLK Pin Source

0X0012 TCSR Control DS21458 TCLK Pin Source

0X0013 SYSCLKT Control DS21458 TSYSCLK Pin Setting

0X0014 SYSCLKR Control DS21458 RSYSCLK Pin Setting

0X0015 SYNC1 Control DS21458 TSYNC Source

0X0016 SYNC2 Control DS21458 TSSYNC Source

0X0017 SYNC3 Control DS21458 RSYNC Source

0X0018 TSERS Control TSER Source

0X0019 PRSER Control PCM RSER Source

0X001A PSYNC Control PCM RSYNC/TSYNC Source

0X001B PCLK Control PCM RCLK/TCLK Source

ID REGISTERS

BID: BOARD ID (Offset = 0X0000)

BID is read only with a value of 0xD.

XBIDH: HIGH NIBBLE EXTENDED BOARD ID (Offset = 0X0002)

XBIDH is read only with a value of 0x0.

XBIDM: MIDDLE NIBBLE EXTENDED BOARD ID (Offset = 0X0003)

XBIDM is read only with a value of 0x1.

XBIDL: LOW NIBBLE EXTENDED BOARD ID (Offset = 0X0004)

XBIDL is read only with a value of 0x6.

BREV: BOARD FAB REVISION (Offset = 0X0005)

BREV is read only and displays the current fab revision.

AREV: BOARD ASSEMBLY REVISION (Offset = 0X0006)

AREV is read only and displays the current assembly revision.

PREV: PLD REVISION (Offset = 0X0007)

PREV is read only and displays the current PLD firmware revision.

6 of 32

Page 7

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

CONTROL REGISTERS

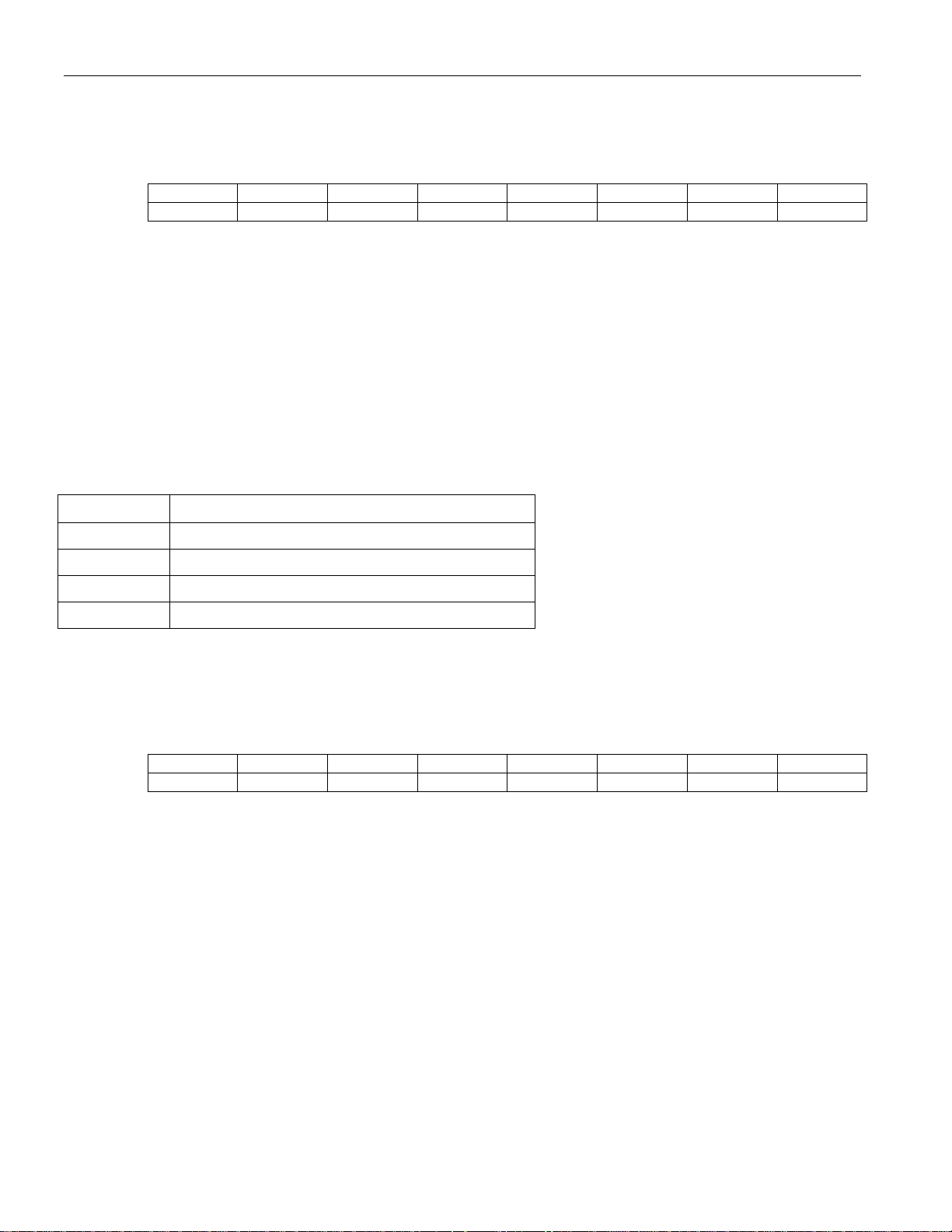

Register Name: MCSR

Register Description: DS21458 MCLK Pin Source

Register Offset: 0x0011

Bit # 7 6 5 4 3 2 1 0

Name — — — — — — MSRCB MSRCA

Default — — — — — — 1 1

Bit 0: DS21458 Port 1 and 3 MCLK Source (MSRCA)

0 = Connect MCLK 1 (controls port 1 and 3) to the 1.544MHz clock

1 = Connect MCLK 1 (controls port 1 and 3) to the 2.048MHz clock

Bit 1: DS21458 Port 2 and 4 MCLK Source (MSRCA)

0 = Connect MCLK 2 (controls port 2 and 4) to the 1.544MHz clock

1 = Connect MCLK 2 (controls port 2 and 4) to the 2.048MHz clock

Register Name: TCSR

Register Description: DS21458 TCLK Pin Source

Register Offset: 0x0012

Bit # 7 6 5 4 3 2 1 0

Name T4S1 T4S0 T3S1 T3S0 T2S1 T2S0 T1S1 T1S0

Default 0 0 0 0 0 0 0 0

Bit 0 to 1: DS21458 Port 1 TCLK Source (T1S0, T1S1)

The source for TCLK 1 is Defined as shown in Table 3.

Bit 2 to 3: DS21458 Port 2 TCLK Source (T2S0, T2S1)

The source for TCLK 2 is Defined as shown in Table 3.

Bit 4 to 5: DS21458 Port 3 TCLK Source (T3S0, T3S1)

The source for TCLK 3 is Defined as shown in Table 3.

Bit 6 to 7: DS21458 Port 4 TCLK Source (T4S0, T4S1)

The source for TCLK 3 is Defined as shown in Table 3.

Table 3. TCLKx Source Definition

TxS1, TxS0 TCLK CONNECTION

00 Drive TCLKX with the 1.544MHz clock

01 Drive TCLKX with the 2.048MHz clock

10 Drive TCLKX with RCLKX

11 N/A

7 of 32

Page 8

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: SYSCLKT

Register Description: DS21458 TSYSCLK Pin Setting

Register Offset: 0x0013

Bit # 7 6 5 4 3 2 1 0

Name R4S1 R4S0 R3S1 R3S0 R2S1 R2S0 R1S1 R1S0

Default 0 0 0 0 0 0 0 0

Bit 0 to 1: DS21458 Port 1 TSYSCLK Source (R1S0, R1S1)

The source for TSYSCLK 1 is Defined as shown in Table 4.

Bit 2 to 3: DS21458 Port 2 TSYSCLK Source (R2S0, R2S1)

The source for TSYSCLK 2 is Defined as shown in Table 4.

Bit 4 to 5: DS21458 Port 3 TSYSCLK Source (R3S0, R3S1)

The source for TSYSCLK 3 is Defined as shown in Table 4.

Bit 6 to 7: DS21458 Port 4 TSYSCLK Source (R4S0, R4S1)

The source for TSYSCLK 4 is Defined as shown in Table 4.

Table 4. TSYSCLKx Source Definition

RxS1, RxS0 TSYSCLKX CONNECTION

00 Drive TSYSCLKX with the 1.544MHz clock

01 Drive TSYSCLKX with the 2.048MHz clock

10 Drive TSYSCLK

with 8.192MHz clock

X

11 Drive TSYSCLKX with DS21458 PortX BPCLK

8 of 32

Page 9

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: SYSCLKR

Register Description: DS21458 RSYSCLK Pin Setting

Register Offset: 0x0014

Bit # 7 6 5 4 3 2 1 0

Name T4S1 T4S0 T3S1 T3S0 T2S1 T2S0 T1S1 T1S0

Default 0 0 0 0 0 0 0 0

Bit 0 to 1: DS21458 Port 1 RSYSCLK Source (T1S0, T1S1)

The source for RSYSCLK 1 is Defined as shown in Table 5.

Bit 2 to 3: DS21458 Port 2 RSYSCLK Source (T2S0, T2S1)

The source for RSYSCLK 2 is Defined as shown in Table 5.

Bit 4 to 5: DS21458 Port 3 RSYSCLK Source (T3S0, T3S1)

The source for RSYSCLK 3 is Defined as shown in Table 5.

Bit 6 to 7: DS21458 Port 4 RSYSCLK Source (T4S0, T4S1)

The source for RSYSCLK 4 is Defined as shown in Table 5.

Table 5. RSYSCLKx Source Definition

TxS1, TxS0 RSYSCLKX CONNECTION

00 Drive RSYSCLKX with the 1.544MHz clock

01 Drive RSYSCLKX with the 2.048MHz clock

10 Drive RSYSCLK

with 8.192MHz clock

X

11 Drive RSYSCLKX with DS21458 PortX BPCLK

Register Name: SYNC1

Register Description: DS21458 TSYNC Pin Source

Register Offset: 0x0015

Bit # 7 6 5 4 3 2 1 0

Name — — — — T4SRC T3SRC T2SRC T1SRC

Default — — — — 0 0 0 0

Bit 0: DS21458 Port 1 TSYNC Source (T1SRC)

0 = TSYNC 1 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSYNC 1 with RSYNC 1

Bit 1: DS21458 Port 2 TSYNC Source (T2SRC)

0 = TSYNC 2 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSYNC 2 with RSYNC 2

Bit 2: DS21458 Port 3 TSYNC Source (T3SRC)

0 = TSYNC 3 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSYNC 3 with RSYNC 3

Bit 3: DS21458 Port 4 TSYNC Source (T4SRC)

0 = TSYNC 4 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSYNC 4 with RSYNC 4

Note: When driving TSYNCx with RSYNCx the corresponding DS21458 port should be configured such that

TSYNCx is an input (IOCR1.1 = 0) and RSYNCx is an output (IOCR1.4 = 0).

9 of 32

Page 10

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: SYNC2

Register Description: DS21458 TSSYNC Pin Source

Register Offset: 0x0016

Bit # 7 6 5 4 3 2 1 0

Name — — — — T4SRC T3SRC T2SRC T1SRC

Default — — — — 0 0 0 0

Bit 0: DS21458 Port 1 TSSYNC Source (T1SRC)

0 = Not using transmit-side elastic store, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSSYNC 1 with RSYNC 1

Bit 1: DS21458 Port 2 TSSYNC Source (T2SRC)

0 = Not using transmit-side elastic store, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSSYNC 2 with RSYNC 2

Bit 2: DS21458 Port 3 TSSYNC Source (T3SRC)

0 = Not using transmit-side elastic store, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSSYNC 3 with RSYNC 3

Bit 3: DS21458 Port 4 TSSYNC Source (T4Source)

0 = Not using transmit-side elastic store, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive TSSYNC 4 with RSYNC 4

Note: When driving TSSYNCx with RSYNCx the corresponding DS21458 port should be configured such that

RSYNCx is an output (IOCR1.4 = 0).

10 of 32

Page 11

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: SYNC3

Register Description: DS21458 RSYNC Pin Setting

Register Offset: 0x0017

Bit # 7 6 5 4 3 2 1 0

Name RSOR1 RSOR0 — — R4IO R3IO R2IO R1IO

Default 0 0 — — 0 0 0 0

Bit 0: DS21458 Port 1 RSYNC Setting (R1IO)

0 = RSYNC 1 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive RSYNC 1 with RSYNC

as shown in Table 6

X

Bit 1: DS21458 Port 2 RSYNC Setting (R2IO)

0 = RSYNC 2 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive RSYNC 2 with RSYNC

as shown in Table 6

X

Bit 2: DS21458 Port 3 RSYNC Setting (R3IO)

0 = RSYNC 3 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive RSYNC 4 with RSYNC

as shown in Table 6

X

Bit 3: DS21458 Port 4 RSYNC Setting (R4IO)

0 = RSYNC 4 is an output, tri-state corresponding FPGA driver pin (weak pulldown)

1 = Drive RSYNC 4 with RSYNC

as shown in Table 6

X

Note: When driving RSYNCy with RSYNCx the corresponding DS21458 port should be configured such that

RSYNCx is an output (IOCR1.4 = 0) and RSYNCy is an input (IOCR1.4 = 1).

Table 6. RSYNCx Function Definition

RSOR1, RSOR0 MASTER RSYNC DESIGNATION

00 RSYNC 1 is used to drive other RSYNC pins (providing RXIO = 1)

01 RSYNC 2 is used to drive other RSYNC pins (providing RXIO = 1)

10 RSYNC 3 is used to drive other RSYNC pins (providing RXIO = 1)

11 RSYNC 4 is used to drive other RSYNC pins (providing RXIO = 1)

11 of 32

Page 12

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: TSERS

Register Description: DS21458 TSER Pin Source

Register Offset: 0x0018

Bit # 7 6 5 4 3 2 1 0

Name T4S1 T4S0 T3S1 T3S0 T2S1 T2S0 T1S1 T1S0

Default 0 0 0 0 0 0 0 0

Bit 0 to 1: DS21458 Port 1 TSER Source (T1S0, T1S1)

The source for TSER 1 is Defined as shown in Table 7.

Bit 2 to 3: DS21458 Port 2 TSER Source (T2S0, T2S1)

The source for TSER 2 is Defined as shown in Table 7.

Bit 4 to 5: DS21458 Port 3 TSER Source (T3S0, T3S1)

The source for TSER 3 is Defined as shown in Table 7.

Bit 6 to 7: DS21458 Port 4 TSER Source (T4S0, T4S1)

The source for TSER 4 is Defined as shown in Table 7.

Table 7. TSERx Source Definition

TxS1, TxS0 TSERX CONNECTION

00 Tri-state TSERX (weak pulldown)

01 Drive TSERX with RSERX

10 Drive TSERX with PCM_TXD bus (DK2000 only)

11 N/A

Register Name: PRSER

Register Description: PCM RSER Source

Register Offset: 0x0019

Bit # 7 6 5 4 3 2 1 0

Name — — — — R1EN R1EN R1EN R1EN

Default — — — — 0 0 0 0

Bit 0 to 1: PCM RSER Source (R1EN)

0 = Do not drive DS21458 Port 1 RSER onto PCM_RSER

1 = Logically OR DS21458 Port 1 RSER with selected other RSER pins and drive onto PCM_RSER

Bit 2 to 3: DS21458 Port 2 TSER Source (T2S0, T2S1)

0 = Do not drive DS21458 Port 2 RSER onto PCM_RSER

1 = Logically OR DS21458 Port 2 RSER with selected other RSER pins and drive onto PCM_RSER

Bit 4 to 5: DS21458 Port 3 TSER Source (T3S0, T3S1)

0 = Do not drive DS21458 Port 3 RSER onto PCM_RSER

1 = Logically OR DS21458 Port 3 RSER with selected other RSER pins and drive onto PCM_RSER

Bit 6 to 7: DS21458 Port 4 TSER Source (T4S0, T4S1)

0 = Do not drive DS21458 Port 4 RSER onto PCM_RSER

1 = Logically OR DS21458 Port 4 RSER with selected other RSER pins and drive onto PCM_RSER

Note: PRSER register is for use with the DK2000 only.

12 of 32

Page 13

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: PSYNC

Register Description: PCM RSYNC/TSYNC Source

Register Offset: 0x001A

Bit # 7 6 5 4 3 2 1 0

Name — — T2SR T1SR — — R2SR R1SR

Default — — 0 0 — — 0 0

Bit 0 to 1: PCM_RSYNC Source

R2SR, R1SR PCM_RSYNC SOURCE

00 PCM_RSYNC is driven by DS21458 port 1 RSYNC

01 PCM_RSYNC is driven by DS21458 port 2 RSYNC

10 PCM_RSYNC is driven by DS21458 port 3 RSYNC

11 PCM_RSYNC is driven by DS21458 port 4 RSYNC

Bit 4 to 5: PCM_TSYNC Source

T2SR, T1SR PCM_TSYNC SOURCE

00 PCM_TSYNC is driven by DS21458 port 1 TSYNC

01 PCM_TSYNC is driven by DS21458 port 2 TSYNC

10 PCM_TSYNC is driven by DS21458 port 3 TSYNC

11 PCM_TSYNC is driven by DS21458 port 4 TSYNC

Note: PSYNC register is for use with the DK2000 only.

13 of 32

Page 14

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

Register Name: PCLK

Register Description: PCM RCLK/TCLK Source

Register Offset: 0x001B

Bit # 7 6 5 4 3 2 1 0

Name — TCM T2SR T1SR — RCM R2SR R1SR

Default —- 0 0 0 — 0 0 0

Bit 0 to 2: PCM_RCLK Source

RCM,R2SR, R1SR PCM_RCLK SOURCE

000 PCM_RCLK is driven by DS21458 port 1 RCLK

001 PCM_RCLK is driven by DS21458 port 2 RCLK

010 PCM_RCLK is driven by DS21458 port 3 RCLK

011 PCM_RCLK is driven by DS21458 port 4 RCLK

100 PCM_RCLK is driven by DS21458 port 1 BPCLK

101 PCM_RCLK is driven by DS21458 port 2 BPCLK

110 PCM_RCLK is driven by DS21458 port 3 BPCLK

111 PCM_RCLK is driven by DS21458 port 4 BPCLK

Bit 4 to 5: PCM_TCLK Source

TCM,T2SR, T1SR PCM_TCLK SOURCE

000 PCM_TCLK is driven by source used for DS21458 port 1 TCLK

001 PCM_TCLK is driven by source used for DS21458 port 2 TCLK

010 PCM_TCLK is driven by source used for DS21458 port 3 TCLK

011 PCM_TCLK is driven by source used for DS21458 port 4 TCLK

100 PCM_TCLK is driven by DS21458 port 1 BPCLK

101 PCM_TCLK is driven by DS21458 port 2 BPCLK

110 PCM_TCLK is driven by DS21458 port 3 BPCLK

111 PCM_TCLK is driven by DS21458 port 4 BPCLK

Note: PCLK register is for use with the DK2000 only.

14 of 32

Page 15

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

K

K

K

K

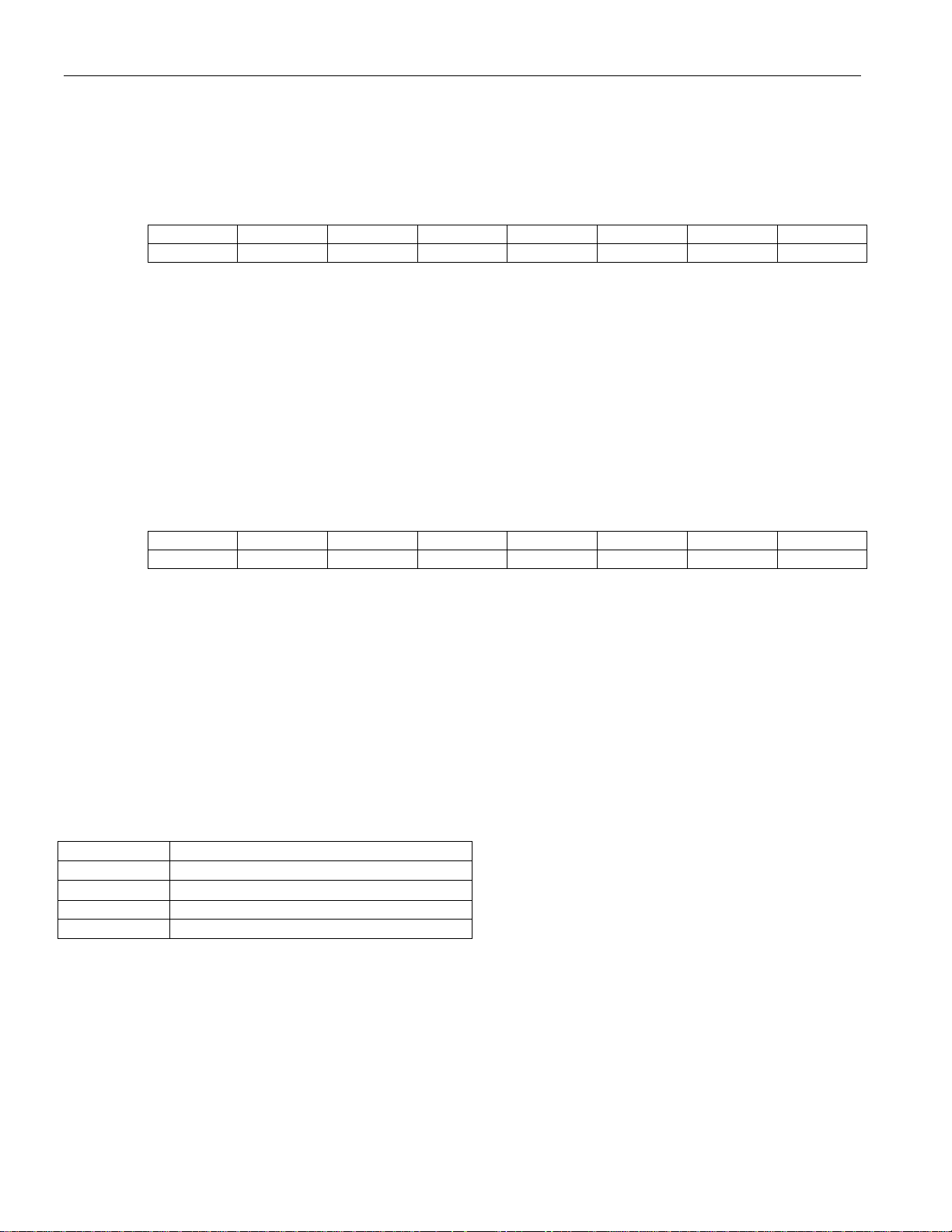

FPGA CONTROL EXAMPLES

Table 8. FPGA Configuration for Scenario #1 (Port 1, T1 Mode)

SCENARIO #1: DS21458 TO/FROM DK2000

DS21458

TSER

TCL

BPCL

TSYNC

RSER

RCL

BPCL

RSYNC

XO

DK2000

PCM_TXD

PCM_TCLK

PCM_TSYNC

PCM_RXD

PCM_RCLK

PCM_RSYNC

REGISTER SETTING COMMENT

MCSR 0X01 Drive DS21458 ports 1 and 3 MCLK with 2.048MHz

TCSR 0X00 Drive TCLK with 1.544MHz

SYSCLKT 0X00 Drive TSYSCLK with 1.544MHz

SYSCLKR 0X00 Drive RSYSCLK with 1.544MHz

SYNC1 0X00 Tri-state FPGA driver pin for DS21458 TSYNC1

SYNC2 0X01 Drive TSSYNC1 with RSYNC1

SYNC3 0X00 Tri-state FPGA driver pin for DS21458 RSYNC

TSERS 0X02 Drive DS21458 TSER1 with data from PCM bus

PRSER 0X01 Drive DS21458 RSER1 onto PCM bus

PSYNC 0X00

PCLK 0X44 PCM RCLK and TCLK are driven by port 1 BPCLK

PCM RSYNC and PCM TSYNC are provided by DS21458 port 1 RSYNC

and TSYNC (respectively)

15 of 32

Page 16

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

(

K

K

K

K

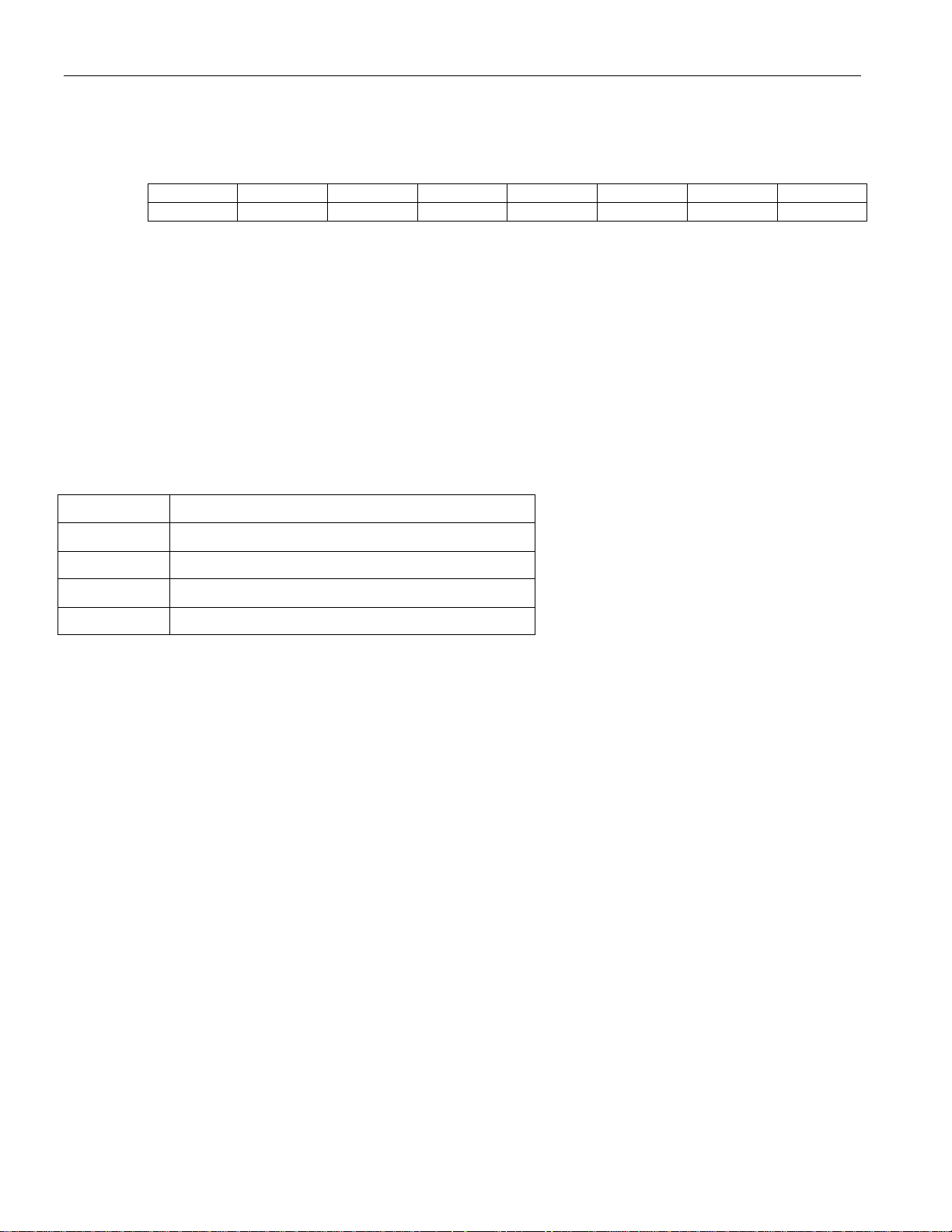

FPGA CONTROL EXAMPLES (continued)

Table 9. FPGA Configuration for Scenario #2 (Port 1, T1 Mode)

REGISTER SETTING COMMENT

MCSR 0X01 Drive DS21458 ports 1 and 3 MCLK with 2.048MHz

TCSR 0X02 Drive TCLK1 with RCLK1

SYSCLKT 0X00 Drive TSYSCLK with 1.544MHz

SYSCLKR 0X00 Drive RSYSCLK with 1.544MHz

SYNC1 0X01 Drive TSYNC1 with RSYNC1

SYNC2 0X01 Drive TSSYNC1 with RSYNC1

SYNC3 0X00 Tri-state FPGA driver pin for DS21458 RSYNC

TSERS 0X01 Drive DS21458 TSER1 with data from RSER1

PRSER N/A Unused

PSYNC N/A Unused

PCLK N/A Unused

SCENARIO #2: EXTERNAL REMOTE LOOPBACK

FULL BANDWIDTH, NOT JUST PAYLOAD)

DS21458

TSER

TCL

BPCL

TSYNC

RSER

RCL

BPCL

RSYNC

Table 10. DS21458 Partial Configuration for Scenario #2 (Port 1, T1 Mode)

REGISTER SETTING COMMENT

IOCR1

ESCR

CCR1

TSIO = 0;

RSIO = 0

TESE = 0;

RESE = 0

TCSS1 = 0;

TCSS2 = 0

TSYNC is an input, RSYNC is an output

Bypass Rx and Tx elastic stores

TCLK is driven by TCLK pin

16 of 32

Page 17

DS21458DK, Quad T1/E1/J1 Transceiver Design Kit Daughter Card

DS21458 INFORMATION

For more information about the DS21458, please consult the DS21458 data sheet available on our website at

www.maxim-ic.com/DS21458. Software downloads are also available for this design kit.

DS21458DK INFORMATION

For more information about the DS21458DK, including software downloads, please consult the DS21458DK data

sheet available on our website at www.maxim-ic.com/DS21458DK

.

TECHNICAL SUPPORT

For additional technical support, please e-mail your questions to telecom.support@dalsemi.com.

SCHEMATICS

The DS21458DK schematics are featured at the end of this document.

17 of 32

Maxim/Dallas Semiconductor cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim/Dallas Semiconductor product.

No circuit patent licenses are implied. Maxim/Dallas Semiconductor reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 2006 Maxim Integrated Products • Printed USA

The Maxim logo is a registered trademark of Maxim Integrated Products, Inc. The Dallas logo is a registered trademark of Dallas Semiconductor.

Page 18

Page 19

Page 20

Page 21

Page 22

Page 23

Page 24

Page 25

Page 26

Page 27

Page 28

Page 29

Page 30

Page 31

Page 32

Loading...

Loading...