www.maxim-ic.com.cn

概述

DS1990A序列号iButton®是一种坚固的数据载体,可

作为自动识别系统的电子注册号。数据通过 1-Wire®

协议传输,只需要一条信号引线和一个地回路。每个

DS1990A内包含工厂刻入的唯一 64 位注册号,可绝

对跟踪。坚固耐用的不锈钢

iButton封装具有极强的环

境适应能力,可防尘、防潮、防震。这种紧凑的纽扣

外形使其自动对准相应的探测头,易于人工操作。多

种附件使DS1990A可以灵活地安装在各种容器、塑料

盘、包装袋等物体表面。

应用

接入控制

工作流程跟踪

工具管理

库存管理

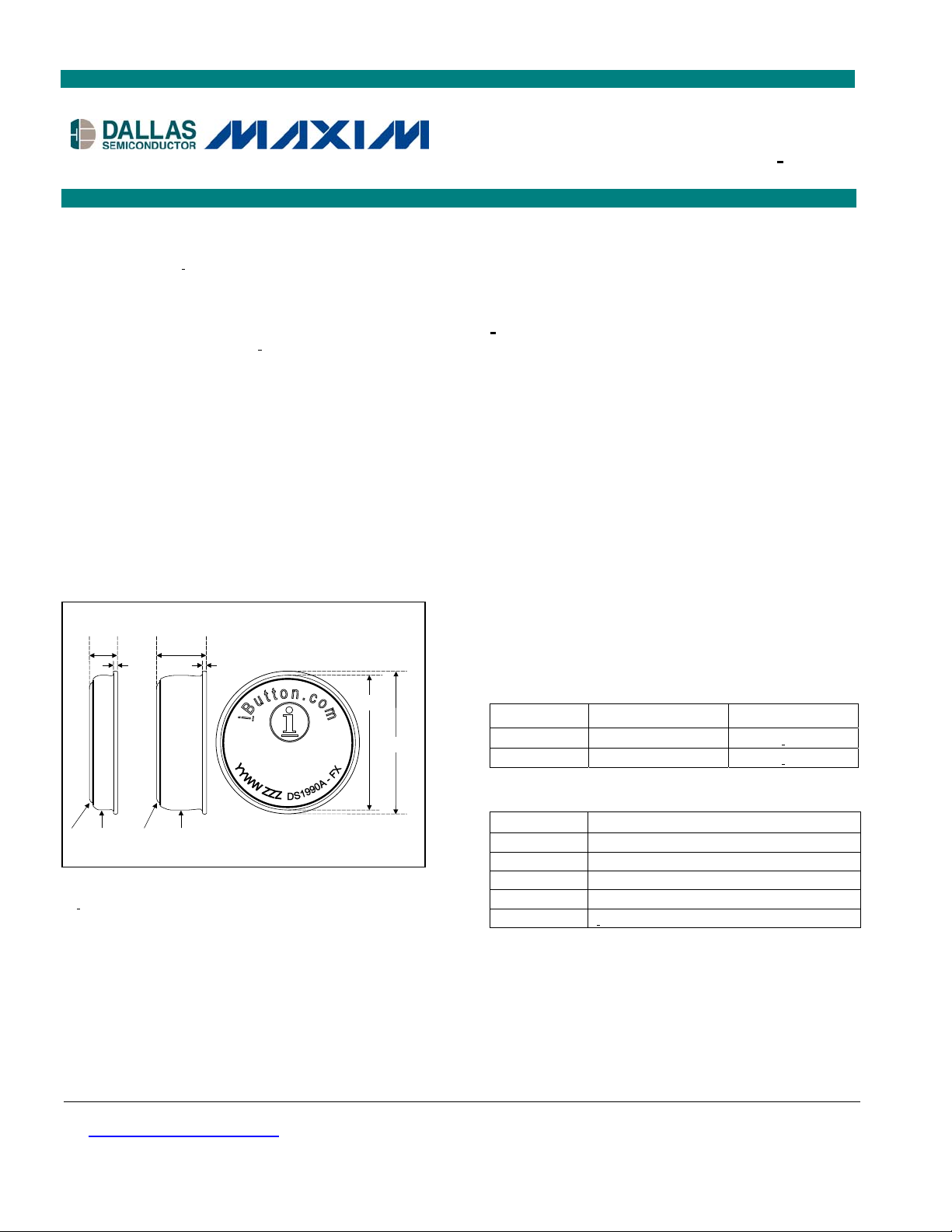

F3 和 F5 MicroCAN

尺寸

F3

IO

iButton, 1-Wire, 和MicroCAN是Dallas Semiconductor

标。

F5

3.10

0.51

地

尺寸

5.89

0.51

89 01

000000FBC52B

IO

地

所有尺寸单位为毫米。

商标

1-Wire

®

®

®

16.25

17.35

的注册商

DS1990A

序列号 i

特性

读取时间在 5ms 以内

工作范围:2.8V 至 6.0V, -40°C至+85°C

iButton共性

工厂刻入的 64 位注册号确保正确无误的器件选择

和绝对跟踪,不存在任何两个具有相同注册号的

器件。

内置多点控制器,适用于 1-Wire 网络。

短时间接触实现数字识别。

可以安装在某一物体上、并读取数据。

通过单线与主机进行数据通信,传输速率可达

16.3kbps,经济实惠。

纽扣外形使其可以自动对准杯状探测器。

注册号刻在耐用的不锈钢外壳上,能够经受恶劣

的环境。

安装时可以很容易地用自粘胶粘贴背面、固定其

边沿,或嵌装其环箍。

符合 UL#913 (第四版)标准;固有安全设备:经过 I

级、1 区、A、B、C组和指定 D区域场合的认

证。

定购信息

型号 温度范围 封装

DS1990A-F5

DS1990A-F3

常用附件

型号 说明

DS9096P 自粘胶垫

DS9101 多用途夹

DS9093RA 安装固定环

DS9093A 链扣

DS9092 iButton读取探头

-40°C 至+85°C

-40°C 至+85°C

Button

F5 iButton

F3 iButton

注:该器件的一些修订资料可能与已经发布的勘误表有所不同。任何器件有可能通过不同的销售途径同时提供多个版本。器件勘误表的信息可以从网

站:

http://www.maxim-ic.com.cn/errata

下载。

1 of 8 REV: 033005

DS1990A

物理规格

尺寸 参考机械图

DS1990A 重量 Ca. 2.5 克

安全性 符合 UL#913 (第四版)标准;固有安全设备:经过 I 级、1

区、A、B、C 组和指定 D 区域场合的认证。

极限参数

IO 至 GND 的电压

IO 吸入电流

结温

储存温度 -55°C 至+125°C

超出“极限参数”规定的范围会造成器件永久性损坏。这只是器件所能承受的极限值。在不超出极限参数的前提下,要使器件正常工作还需保证

不超出特性参数列表中的限定条件。如果器件长时间处于这些极限参数下会影响其可靠性。

-0.5V, +6.0V

20mA

+125°C

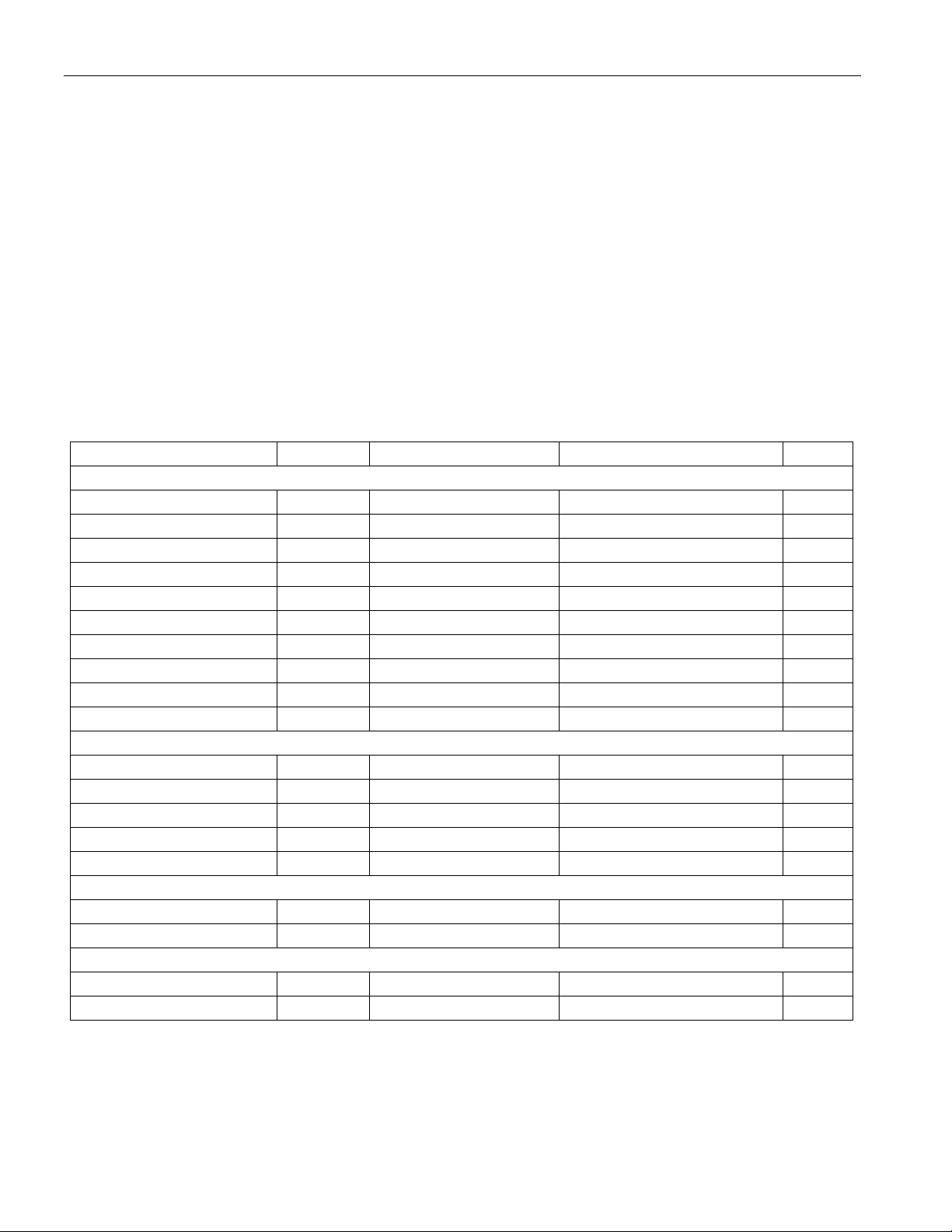

电气特性

(V

= 2.8V至 6.0V, TA = -40°C至+85°C.)

PUP

参数 符号 条件 最小值 典型值 最大值 单位

IO 引脚通用数据

1-Wire 上拉电阻

输入电容

输入负载电流

输入低电平电压

输入高电平电压

输出低电平电压 4mA

输出高电平电压

工作电荷

恢复时间

时隙持续时间

IO 引脚, 1-Wire 复位, 在线检测周期

复位低电平时间

复位高电平时间

在线检测高电平时间

在线检测低电平时间

在线检测采样时间

IO 引脚, 1-Wire 写

写 0 低电平时间

写 1 低电平时间

IO 引脚, 1-Wire 读

读低电平时间

读采样时间

R

C

V

V

V

V

Q

t

REC

t

SLOT

t

RSTL

t

RSTH

t

PDH

t

PDL

t

MSP

t

W0L

t

W1L

t

t

MSR

PUP

IO

I

L

IL

IH

OL

OH

OP

RL

(注 1, 2)

(注 3, 15)

(注 4)

(注 1, 5, 6)

(注 6, 7)

(注 6)

(注 6, 8)

(注 9, 15)

(注 1)

(注 1)

(注 1, 10)

(注 1, 11)

15 60 µs

(注 14)

(注 1)

(注 1)

(注 1, 12)

(注 1, 13)

(注 1, 13)

0.6 5

kΩ

100 800 pF

0.25 µA

0.8 V

2.2 V

0.4 V

V

PUP

V

30 nC

1 µs

61 µs

480 µs

480 µs

60 240 µs

60 75 µs

60 120 µs

1

1

t

RL

+ δ

15 µs

15 - ε

15 - δ

µs

µs

2 of 8

DS1990A

注 1: 系统要求。

注 2:

注 3: 首次上电时,

注 4: 输入负载接地。

注 5: 当主控制器驱动总线为低电平时,IO电压须低于或等于V

注 6: 所有电压以地为参考。

注 7: VIH是内部电源电压的函数。

注 8:

注 9: 5.0V上拉电压、5kΩ上拉电阻,t

注 10: 复位低电平时间 (t

注 11: 在达到复位高电平之前,不会产生额外的复位或通信序列。

注 12: ε表示上拉电路将IO电压从V

注 13: δ表示上拉电路将

注 14:

注 15: 仅由设计、仿真保证,未经过生产测试。

R

的范围仅由设计、仿真保证,未经过生产测试。产品测试是在固定R

PUP

器件数量和 1-Wire 恢复时间的函数。这里提供的数值对应于系统只包含一个器件和 1-Wire最小恢复时间。对于负载较重的系统,可

能需要

DS2480 中的有源上拉。

IO引脚的电容可能达到 800pF。如果IO引脚采用 5kΩ电阻上拉至V

操作。

。在一定的低电压条件下,V

线应答脉冲。

V

= 外部上拉电压。

PUP

≤ 120µs时,每 72 个时隙为 30nC。

SLOT

) 应该限制在最大 960µs,允许中断信令。与DS1994 并行使用时,更长的持续时间有可能屏蔽或隐蔽中断脉

冲。

在线应答脉冲确保仅出现在复位脉冲之后

RSTL

拉至VIH 所需要的时间。

IL

IO电压从VIL 拉至总线主控制器输入高电平门限所需要的时间。

(t

RSTL

ILMAX

)。

下进行的。所允许的最大上拉电阻是系统中的 1-Wire

PUP

,上电 5µs后,寄生电容将不会影响正常的通信

PUP

可能需要降至 0.5V,以确保正确的在

ILMAX

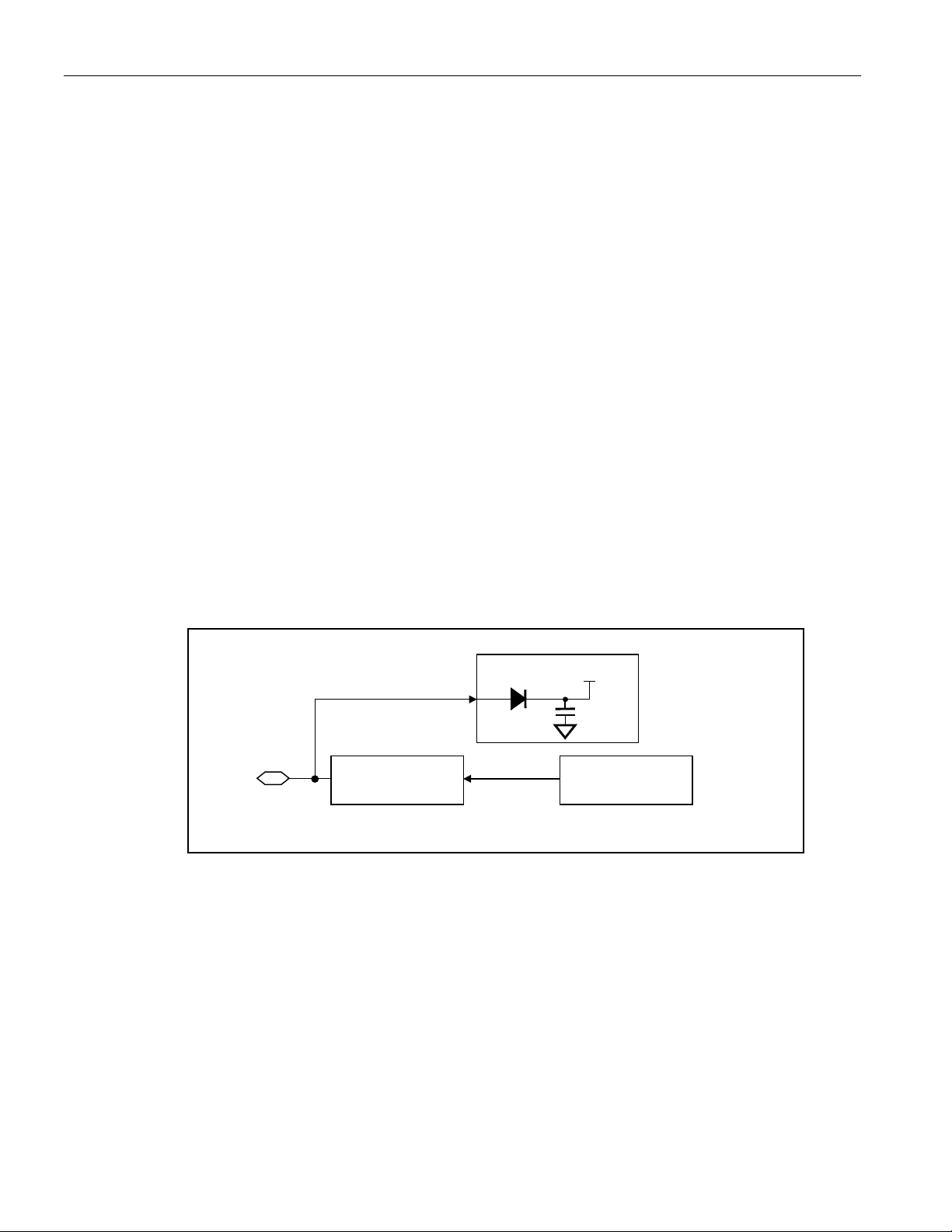

说明

图 1 给出了该器件的主要功能框图。DS1990A 从 IO 总线获取所需的能量,如寄生电源原理图所示。ROM 功能控制

单元包括 1-Wire 接口和逻辑电路,用于实现 ROM 功能命令,访问 64 位光刻 ROM。

图 1. DS1990A 原理框图

Parasite Power

IO

ROM

Function Control

64-bit

Lasered ROM

64 位光刻 ROM

每个 DS1990A包含唯一的 64 位ROM码,前 8 位是 1-Wire家族码,接下来的 48 位是唯一的序列号,最后 8 位是前

56 位的CRC校验码。详细内容请参考图 2。1-Wire CRC是由多项式发生器产生的,多项式发生器包括移位和“异

或”逻辑门电路,如图 3所示。多项式为:X

用笔记

27。

移位寄存器以 0 为起始位,然后是家族码(最低有效位),每次移入 1 位。移入第 8 位家族码后,开始移入序列

号。48 位序列号完全移入后,移位寄存器内所包含的值即为 CRC 校验码。移入 8 位 CRC 校验码,移位寄存器将全

部归 0。

8

+ X5 + X4 + 1。有关Dallas 1-Wire循环冗余校验的详细信息,请参考

应

3 of 8

图 2. 64 位光刻 ROM

MSB LSB

DS1990A

8 位

CRC 码

48 位序列号 8位家族码 (01H)

MSB LSB MSB LSB MSB LSB

图 3. 1-Wire CRC 发生器

POLYNOMIAL = X8 + X5 + X4 + 1

STAGE

0

X

st

1

1

X

nd

2

STAGE

STAGE

2

X

rd

3

STAGE

3

X

th

4

STAGE

4

X

th

5

STAGE

5

X

th

6

STAGE

6

X

INPUT DATA

th

7

STAGE

7

X

th

8

8

X

1-Wire 总线系统

1-Wire是在一条总线上连接一个主控制器(主机)和多个从机的系统。任何情况下,DS1990A都是从机器件,而总

线主控制器常由微控器或PC充任。对于一个小型系统配置,1-Wire通信信号可以在软件控制下由微控制器的一个端

口引脚产生。另外,也可以利用DS2480B 1-Wire线驱动器或串口适配器(DS9097U系列)实现。这种通信方式简化

了硬件设计,而且可以节省微处理器的资源,减轻其实时操作任务。有关总线系统的讨论我们分为三个主题:硬件

结构、处理流程和 1-Wire的信令(信号类型和时序)。1-Wire协议规定按照特定时隙中的总线状态进行总线操作,

以主控制器发送的同步脉冲的下降沿为起始状态,更详细的协议描述,请参考Book of DS19xx

iButton Standards第

四章。

硬件配置

1-Wire 总线仅定义了一条信号线,所以让总线上每个器件都在适当的时刻运行是非常重要。 为便于达到这一目的,

每一个接入 1-Wire 总线的器件都采用开漏连接或三态输出。DS1990A 的 1-Wire 端口为漏极开路输出,内部等效电

路如图 4 所示。多点总线在一条 1-Wire 总线上挂接了多个从机器件。1-Wire 总线的最高标准数据传输率为

16.3kbps。上拉电阻的阻值取决于网络规模和负载条件,对于大多数应用,可选择 2.2kΩ的上拉电阻。1-Wire 的空

闲状态为高电平,任何情况下需要暂停 1-Wire 操作时,总线必须置于空闲状态,以便随后恢复 1-Wire 操作。如果没

有进行上述操作,将总线置于低电平的时间超过 120µs,则总线上的一个或多个器件将被复位。

处理流程

DS1990A 在 1-Wire 总线上的数据访问命令流程如下所示:

初始化

ROM 功能命令

4 of 8

图 4. 硬件配置

SIMPLE BUS MASTER DS1990A 1-Wire PORT

RX

DS1990A

V

PUP

R

PUP

RXDATA

TX

Ω

TX

Open Drain

DS2480B BUS MASTER

HOST CPU

Serial

Port

serial in

serial out

Port Pin

RX = Receive

TX = Transmit

VDD

VPP

POL

RXD

TXD

GND

DS2480B

1-W

NC

100

MOSFET

+5V

To 1-Wire data

初始化

1-Wire 总线上所有的传输操作均由初始化序列开始。初始化序列由主机发出的复位脉冲(Reset Pulse)和从机发出

的在线应答脉冲(Presence Pulse)组成。在线应答脉冲使主机检测到 DS1990A 在总线上,并且已经准备就绪。详

细内容请参阅 1-Wire

信令

部分。

1-Wire ROM 功能命令

一旦主机检测到应答脉冲,就可以发出 DS1990A 支持的 ROM 功能命令。所有 ROM 功能命令的长度为 8 位。以下

列出了这些命令的简要介绍(流程图参见图 5)。

Read ROM [33h]

此命令允许总线主机读取 DS1990A 的 8 位家族码、唯一的 48 位序列码和 8 位 CRC 校验码。此命令仅在总线上只

有一个从机器件时可以使用。若总线上的从机超过一个,各器件同时发送数据时将会引发数据冲突(开漏输出将产

生“线与”的结果)。所得到的家族码和 48 位序列号将导致不匹配的 CRC。

Search ROM [F0h]

当一个系统启动初始化时,总线主机可能并不知道有哪些器件挂接在 1-Wire 总线上或不知道它们的注册号。利用总

线的“线或”特点,总线主机采用排除法可以识别总线上所有从机器件的注册号。获取注册号的每一位,从最低有

效位开始,总线主机都需要经过三个时隙。第一个时隙,每个参与搜索的从机器件发送一位其注册号的真实码;第

二个时隙,每个参与搜索的从机器件发送该位注册号的补码;第三个时隙,主机写其选择位的真实码。与主机写入

位不同的所有从机器件停止参与搜索操作。如果在前两个时隙中读取位为 0,总线主机可以获悉现有的从机器件存在

两种位状态(1 和 0)。总线主机选择写入位后,ROM 码“树”出现“分枝”。完成一次操作流程,总线主机可以

获得一个器件的注册号。有关其余器件的注册号识别,请参考应用笔记 187:1-Wire

实例介绍。

搜索算法,

其中还提供了一个

5 of 8

图 5. ROM 功能流程图

y

DS1990A

Bus Master TX

Reset Pulse

Bus Master TX ROM

Function Command

33h

Read ROM

Command ?

Y

DS1990A TX

Family Code

(1 Byte)

DS1990A TX

Serial Number

(6 Bytes)

DS1990A TX

Presence Puls e

N

DS1990A TX Bit 0

DS1990A TX Bit 0

N

DS1990A TX Bit 1

DS1990A TX Bit 1

N

F0h

Search ROM

Command ?

Y

Master TX Bit 0

Bit 0

Match ?

Master TX Bit 1

Bit 1

Match ?

N

Y

Y

DS1990A TX

CRC B

te

DS1990A

DS1990A

Master TX Bit 63

N

TX Bit 63

TX Bit 63

Bit 63

Match ?

Y

Match ROM [55h] / Skip ROM [CCh]

1-Wire ROM 功能的最小配置包括 Match ROM 和 Skip ROM。因为 DS1990A仅有一个 64 位 ROM 码,无其它附加

的存储空间,所以 Match ROM 和 Skip ROM 命令都不可使用。DS1990A 接收到一个它不支持的 ROM 功能命令

时,将保持“沉默”(不动作)。这样可以确保 DS1990A 与其它能够响应 Match ROM 或 Skip ROM 的 1-Wire 器

件共同挂接在一条多点总线上(例如 DS1990A 和 DS1994)。

6 of 8

DS1990A

ε

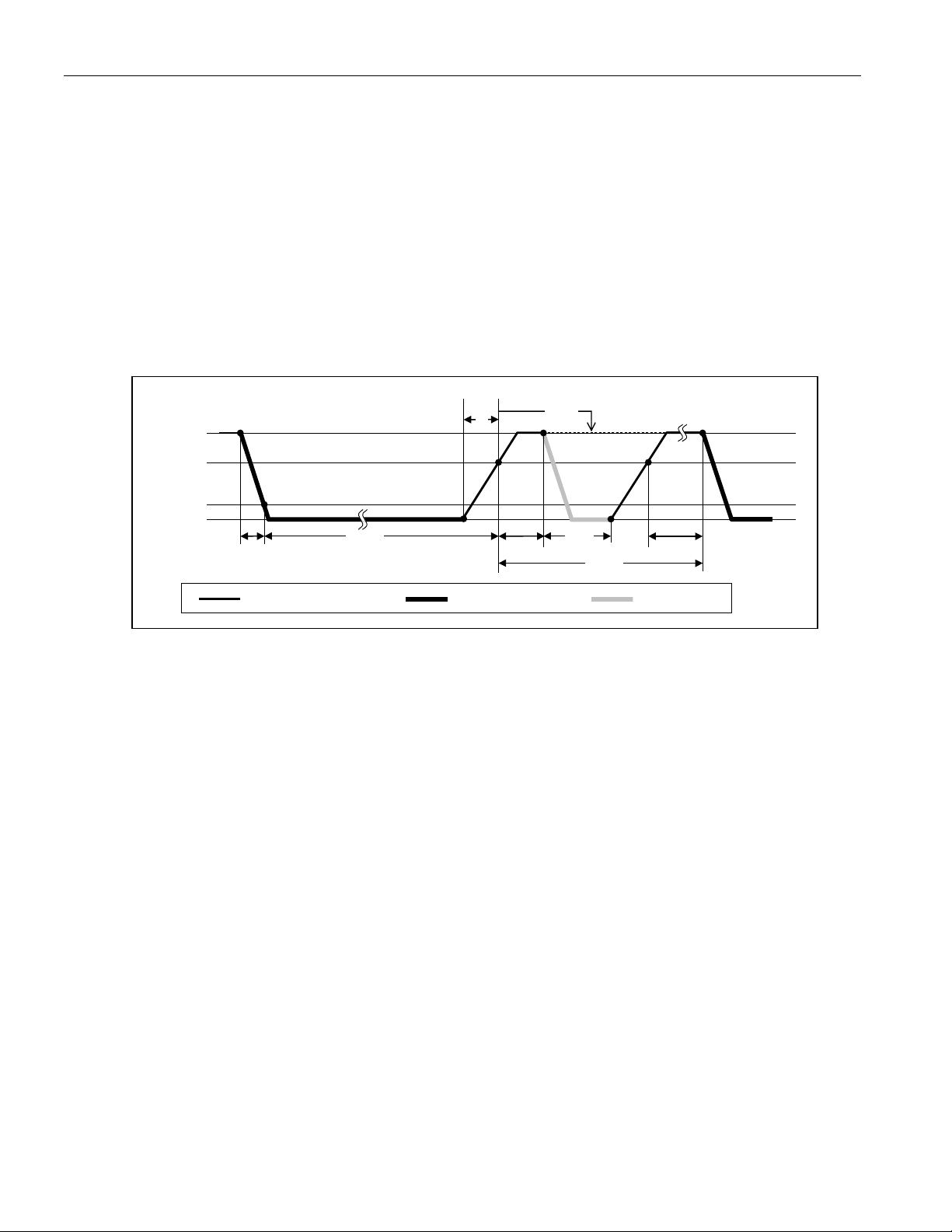

1-Wire 信令

DS1990A 需要严格的通信协议来确保数据的完整性,此协议在单线上定义了四种类型的信号:包括复位脉冲和在线

应答脉冲的复位过程、写 0(Write 0)、写 1(Write 1)和读数据(Read Data)。除了在线脉冲以外,其它类型的

信号都由总线主机启动。

从空闲到活动状态,1-Wire总线需要从V

V

以上。电压上升所需要的时间请参考图 6 中的ε,取决于上拉电阻(R

IHMIN

下降到V

PUP

以下;从活动状态到空闲,总线电压需要从V

ILMAX

)和 1-Wire网络的电容。

PUP

ILMAX

上升到

DS1990A进行任何通信都要进行初始化处理(如图 6 所示)。一个复位脉冲紧跟一个在线应答脉冲表明DS1990A就

+ t

绪,可接收ROM功能命令。如果总线主机在下降沿采用了摆率控制,则必须将总线拉低t

RSTL

,以对边沿进行补

F

偿。

图 6. 初始化流程“复位和在线应答脉冲”

MASTER TX “RESET PULSE” MASTER RX “PRESENCE PULSE”

t

t

PDH

MSP

t

PDL

t

RSTH

t

REC

V

V

V

PUP

IHMIN

ILMAX

0V

t

F

t

RSTL

RESISTOR MASTER DS1990A

主机释放总线后进入接收模式(RX)。此时 1-Wire总线电平被上拉电阻,或DS2480B驱动器等有源电路上拉至

V

。当电平高于V

PUP

应答脉冲,主机必须在t

时,DS1990A等待t

IHMIN

时间检测 1-Wire总线的逻辑电平。

MSP

,然后通过将总线电平拉低并保持t

PDH

,发送一个应答脉冲。为了检测

PDL

读/写时隙

与 DS1990A 的数据通信按时隙进行,每时隙传输一位。数据在写时隙由总线主机传输到从机。数据在读时隙由从机

传输到主机。图 7 说明了读时隙和写时隙的定义。

所有通信均从主机拉低数据线开始,当 1-Wire总线上的电压降至V

以下时,DS1990A启动内部定时发生器,在

ILMAX

写时隙确定何时采样数据线,在读时隙确定数据有效的时间。

主机到从机

对于写 1 时隙,数据线上的电压必须在写 1 的低电平时间t

电压在写 0 的低电平时间t

时间窗口内都不应超过V

。

t

REC

ILMAX

结束前必须保持在V

W0LMIN

。数据线上的电压超过V

ILMAX

IHMIN

以下。为了实现最可靠的通信,数据线上的电压在整个t

W1LMAX

结束前达到V

以上。对于写 0 时隙,数据线上的

IHMIN

后,DS1990A在进行下一个时隙前需要一段恢复时间

W0L

7 of 8

DS1990A

从机到主机

读数据时隙开始时与写 1 时隙类似。数据线上的电压在读低电平时间tRL结束前必须保持在V

口,应答 0 时,DS1990A开始拉低数据线,其内部定时发生器决定何时结束下拉,电压重新开始升高;应答 1 时,

DS1990A将不保持数据线的低电平,一旦t

结束,电压即开始上升。

RL

主机采样窗口(t

MSRMIN到tMSRMAX

主机必须在采样窗口内执行一次数据线读操作。为达到可靠通信,t

但不晚于t

的时间读取数据。从数据线读取数据后,主机必须等待直至t

MSRMAX

准备就绪前有足够的恢复时间t

)一方面由tRL + δ(上升时间)决定,另一方面由DS1990A内部定时发生器决定,

时间在允许范围内应尽量短,主机应该在接近

RL

结束,确保DS1990A在下一个时隙

SLOT

。

REC

ILMAX

以下。在t

时间窗

RL

图 7. 读/写时序图

Write-One Time Slot

t

W1L

ε

t

SLOT

V

IHMASTER

V

V

V

PUP

IHMIN

ILMAX

0V

t

F

Write-Zero Time Slot

V

PUP

V

IHMASTER

V

IHMIN

V

ILMAX

0V

t

F

Read-Data Time Slot

V

PUP

V

IHMASTER

V

IHMIN

V

ILMAX

0V

t

F

RESISTOR MASTER

t

W0L

RESISTOR MASTER

t

t

RL

MSR

Master

Sampling

Window

δ

t

SLOT

t

SLOT

t

REC

t

REC

RESISTOR MASTER DS1990A

8 of 8

Loading...

Loading...