Page 1

71M6521DE/DH/FE

Energy Meter ICs

DATA SHEET

19-5370; Rev 2; 11/11

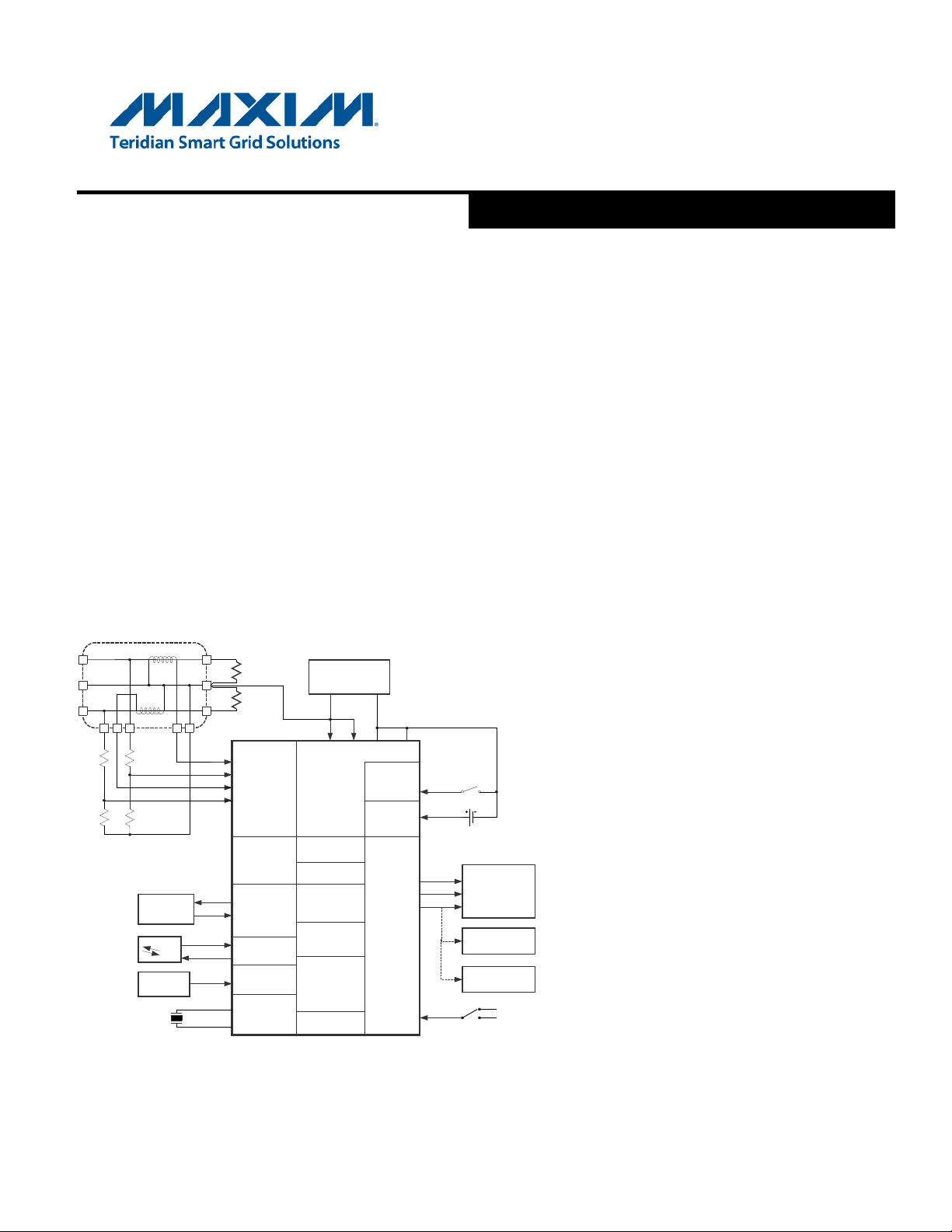

MPU

RTC

TIMERS

IA

VA

IB

XIN

XOUT

VREF

RX/DIO1

TX/DIO2

V1

TX

RX

COM0..3

V3.3A

V3.3

SYS

VBAT

V2.5

VBIAS

SEG0..18

GNDA GNDD

SEG 24..31/

DIO 4..11

SEG 34..37/

DIO 14..17

ICE

LOAD

88.88.8888

IIC or uWire

EEPROM

POWER

FAULT

AMR

TEST PULSES

COMPARATOR

SENSE

DRIVE/MOD

SERIAL PORTS

OSC/PLL

CONVERTER

DIO, PULSE

COMPUTE

ENGINE

FLASH

RAM

VOLTAGE REF

REGULATOR

POWER SUPPLY

TERIDIAN

71M6521

3.3V LCD

TEMP

SENSOR

32 kHz

A

NEUT

CT/SHUNT

07/25/2007

VB

B

LOAD

IR

PWR MODE

CONTROL

WAKE-UP

BATTERY

ICE_E GNDD

V3P3D

SEG 32,33,

38/ICE

Teridian is a trademark and Single Converter Technology is a registered

GENERAL DESCRIPTION

The Teridian™ 71M6521DE/DH/FE energy meter ICs are highly integrated

systems-on-a-chip (SoCs) with an MPU cor e, RTC, flash, and LCD dri ver.

The Single Converter Technology® with a 22-bit delta-sigma ADC, four

analog inputs, digital temperature compensation, precision voltage

reference, battery voltage monitor, and 32-bit computation engine (CE)

supports a wide range of residential metering applications with very few

low-cost external components. A 32kHz crystal time base for the entire

system and internal battery-backup support for RAM and RTC further

reduce system cost. The ICs support 2-wire, 3-wire, and 4-wire singlephase and dual-phase residential metering along with tamper-detection

mechanisms.

Maximum design flexibility is provided by multiple UARTs, I

MICROWIRE®, up to 18 DIO pins, and in-system programmable flash

memory, which can be updated with data or application code in operation.

A complete array of ICE and deve lopm ent tools , pr ogr am ming l ibr ar ies , and

reference designs enable rapid development and certification of TOU,

AMR, and prepay meters that comply with worldwide electricity metering

standards.

trademark of Maxim Integrated Products Inc.

MICROWIRE is a registered trademark of National Semiconductor Corp.

Rev 2 Page: 1 of 107

2

C,

FEATURES

• Up to 0.1% Wh Accuracy Over 2000:1 Current

Range

• Exceeds IEC 62053/ANSI C 12.20 Standards

• Voltage Reference < 40 ppm/°C (< 20ppm/°C for

71M6521DH)

• Four Sensor Inputs—V

• Low-Jitter Wh and VARh Pulse Test Outputs

(10kHz max)

• Pulse Count for Pulse Outputs

• Four-Quadrant Metering

• Tamper Detection

Neutral Current with CT or Shunt

• Line Frequency Count for RTC

• Digital Temperature Compensation

• Sag Detection for Phase A and B

• Independent 32-Bit Compute Engine

• 46-64Hz Line Frequency Range with Same

Calibration

• Phase Compensation (±7°)

• Battery backup for RTC and battery monitor

• Three Battery Modes with Wake-Up on Pushbutton

or Timer:

Brownout Mode (48µA)

LCD Mode (5.7µA)

Sleep Mode (2.9µA)

• Energy Display on Main Power Failure

• Wake-Up with Pushbutton

• 22-Bit Delta-Sigma ADC

• 8-Bit MPU (80515), 1 Clock Cycle per Instruction

with Integrated ICE for MPU Debug

• RTC with Temperature Compensation

• Auto-Calibration

• Hardware Watchdog Timer, Power-Fail Monitor

• LCD Driver (Up to 152 Pixels)

• Up to 18 General-Purpose I/O Pins

• 32kHz Time Base

• 16KB (6521DE/DH) or 32KB (6521FE) Flash with

Security

• 2KB MPU XRAM

• Two UARTs for IR and AMR

• Digital I/O Pins Compatible with 5V Inputs

• 64-Pin LQFP or 68-Pin QFN Package

• Lead(Pb)-Free Packages

Referenced

DD

Page 2

71M6521DE/DH/FE Data Sheet

Table of Contents

GENERAL DESCRIPTION ........................................................................................................................ 1

FEATURES ................................................................................................................................................ 1

HARDWARE DESCRIPTION ..................................................................................................................... 10

Hardware Overview ..................................................................................................................... 10

Analog Front End (AFE) ............................................................................................................... 10

Input Multiplexer ............................................................................................................ 10

A/D Converter (ADC) ..................................................................................................... 11

FIR Filter ........................................................................................................................ 11

Voltage References ....................................................................................................... 11

Temperature Sensor ...................................................................................................... 12

Battery Monitor .............................................................................................................. 13

Functional Description ................................................................................................... 13

Digital Computation Engine (CE) ................................................................................................. 13

Meter Equations ............................................................................................................ 14

Description ................................................................................................................................... 14

Real-Time Monitor ......................................................................................................... 15

Pulse Generator ............................................................................................................ 15

CE Functional Overview ................................................................................................ 15

80515 MPU Core ........................................................................................................... 17

Memory Organization .................................................................................................... 17

Special Function Registers (SFRs) ................................................................................ 19

Special Function Registers (Generic 80515 SFRs) ....................................................... 20

Special Function Registers Specific to the 71M6521DE/DH/FE .................................... 22

Instruction Set ................................................................................................................ 23

UART ............................................................................................................................. 23

Timers and Counters ..................................................................................................... 25

WD Timer (Software Watchdog Timer) .......................................................................... 28

Interrupts ....................................................................................................................... 30

On-Chip Resources ..................................................................................................................... 38

Oscillator ....................................................................................................................... 38

PLL and Internal Clocks ................................................................................................ 38

Real-Time Clock (RTC) ................................................................................................. 38

Temperature Sensor ...................................................................................................... 38

Physical Memory ........................................................................................................... 39

Optical Interface ............................................................................................................ 40

Digital I/O ....................................................................................................................... 40

LCD Drivers ................................................................................................................... 42

Battery Monitor .............................................................................................................. 42

EEPROM Interface ........................................................................................................ 43

Page: 2 of 107 Rev 2

Page 3

71M6521DE/DH/FE Data Sheet

Hardware Watchdog Timer ............................................................................................ 46

Program Security ........................................................................................................... 46

Test Ports ...................................................................................................................... 47

FUNCTIONAL DESCRIPTION ................................................................................................................... 48

Theory of Operation ..................................................................................................................... 48

System Timing Summary ............................................................................................................. 49

Battery Modes .............................................................................................................................. 50

MISSION ...................................................................................................................................... 51

BROWNOUT Mode ....................................................................................................... 51

LCD Mode ..................................................................................................................... 52

SLEEP Mode ................................................................................................................. 52

Fault and Reset Behavior ............................................................................................................ 57

Wake Up Behavior ....................................................................................................................... 57

Wake on PB................................................................................................................... 58

Wake on Timer .............................................................................................................. 58

Data Flow ..................................................................................................................................... 59

CE/MPU Communication ............................................................................................................. 59

APPLICATION INFORMATION ................................................................................................................. 60

Connection of Sensors (CT, Resistive Shunt) .............................................................................. 60

Distinction between 71M6521DE/71M6521FE and 71M6521DH Parts ....................................... 60

Temperature Measurement ......................................................................................................... 61

Temperature Compensation ........................................................................................................ 61

Temperature Compensation and Mains Frequency Stabilization for the RTC ............................. 64

Connecting 5 V Devices ............................................................................................................... 65

Connecting LCDs ......................................................................................................................... 66

Connecting I2C EEPROMs .......................................................................................................... 68

Connecting Three-Wire EEPROMs ............................................................................................. 69

UART0 (TX/RX) ........................................................................................................................... 69

Optical Interface ........................................................................................................................... 70

Connecting V1 and Reset Pins .................................................................................................... 70

Connecting the Emulator Port Pins .............................................................................................. 71

Crystal Oscillator .......................................................................................................................... 71

Flash Programming ..................................................................................................................... 72

MPU Firmware Library ................................................................................................................. 72

Meter Calibration ......................................................................................................................... 72

FIRMWARE INTERFACE .......................................................................................................................... 73

I/O RAM MAP – In Numerical Order ............................................................................................ 73

SFR MAP (SFRs Specific to the Teridian 80515) – In Numerical Order ...................................... 74

I/O RAM DESCRIPTION – Alphabetical Order ............................................................................ 75

CE Interface Description .............................................................................................................. 82

CE Program ................................................................................................................... 82

Rev 2 Page: 3 of 107

Page 4

71M6521DE/DH/FE Data Sheet

Formats ......................................................................................................................... 82

Constants ...................................................................................................................... 82

Environment .................................................................................................................. 82

CE Calculations ............................................................................................................. 83

CE STATUS .................................................................................................................. 83

CE TRANSFER VARIABLES ........................................................................................ 85

ELECTRICAL SPECIFICATIONS .............................................................................................................. 89

ABSOLUTE MAXIMUM RATINGS .............................................................................................. 89

RECOMMENDED EXTERNAL COMPONENTS ......................................................................... 90

RECOMMENDED OPERATING CONDITIONS .......................................................................... 90

PERFORMANCE SPECIFICATIONS .......................................................................................... 91

INPUT LOGIC LEVELS ................................................................................................. 91

OUTPUT LOGIC LEVELS ............................................................................................. 91

POWER-FAULT COMPARATOR .................................................................................. 91

BATTERY MONITOR .................................................................................................... 91

SUPPLY CURRENT ...................................................................................................... 92

V3P3D SWITCH ............................................................................................................ 92

2.5 V VOLTAGE REGULATOR ..................................................................................... 92

LOW POWER VOLTAGE REGULATOR ....................................................................... 92

CRYSTAL OSCILLATOR .............................................................................................. 93

VREF, VBIAS ................................................................................................................ 93

LCD DRIVERS .............................................................................................................. 94

ADC CONVERTER, V3P3A REFERENCED ................................................................. 94

TEMPERATURE SENSOR ........................................................................................... 95

TIMING SPECIFICATIONS ......................................................................................................... 96

RAM AND FLASH MEMORY ..................................................................................................................... 96

FLASH MEMORY TIMING ............................................................................................ 96

EEPROM INTERFACE .................................................................................................. 96

RESET and V1 .............................................................................................................. 96

RTC ............................................................................................................................... 96

TYPICAL PERFORMANCE DATA ................................................................................ 97

PACKAGE OUTLINE (LQFP 64) ................................................................................................. 98

PACKAGE OUTLINE (QFN 68) ................................................................................................... 98

PINOUT (LQFP-64) ..................................................................................................................... 100

PINOUT (QFN 68) ....................................................................................................................... 100

Recommended PCB Land Pattern for the QFN-68 Package ....................................................... 101

PIN DESCRIPTIONS ................................................................................................................... 102

Power/Ground Pins: ...................................................................................................... 102

Analog Pins: .................................................................................................................. 102

Digital Pins:.................................................................................................................... 103

I/O Equivalent Circuits: .................................................................................................. 104

Page: 4 of 107 Rev 2

Page 5

71M6521DE/DH/FE Data Sheet

ORDERING INFORMATION ...................................................................................................................... 105

REVISION HISTORY ................................................................................................................................. 106

Rev 2 Page: 5 of 107

Page 6

71M6521DE/DH/FE Data Sheet

List of Figures

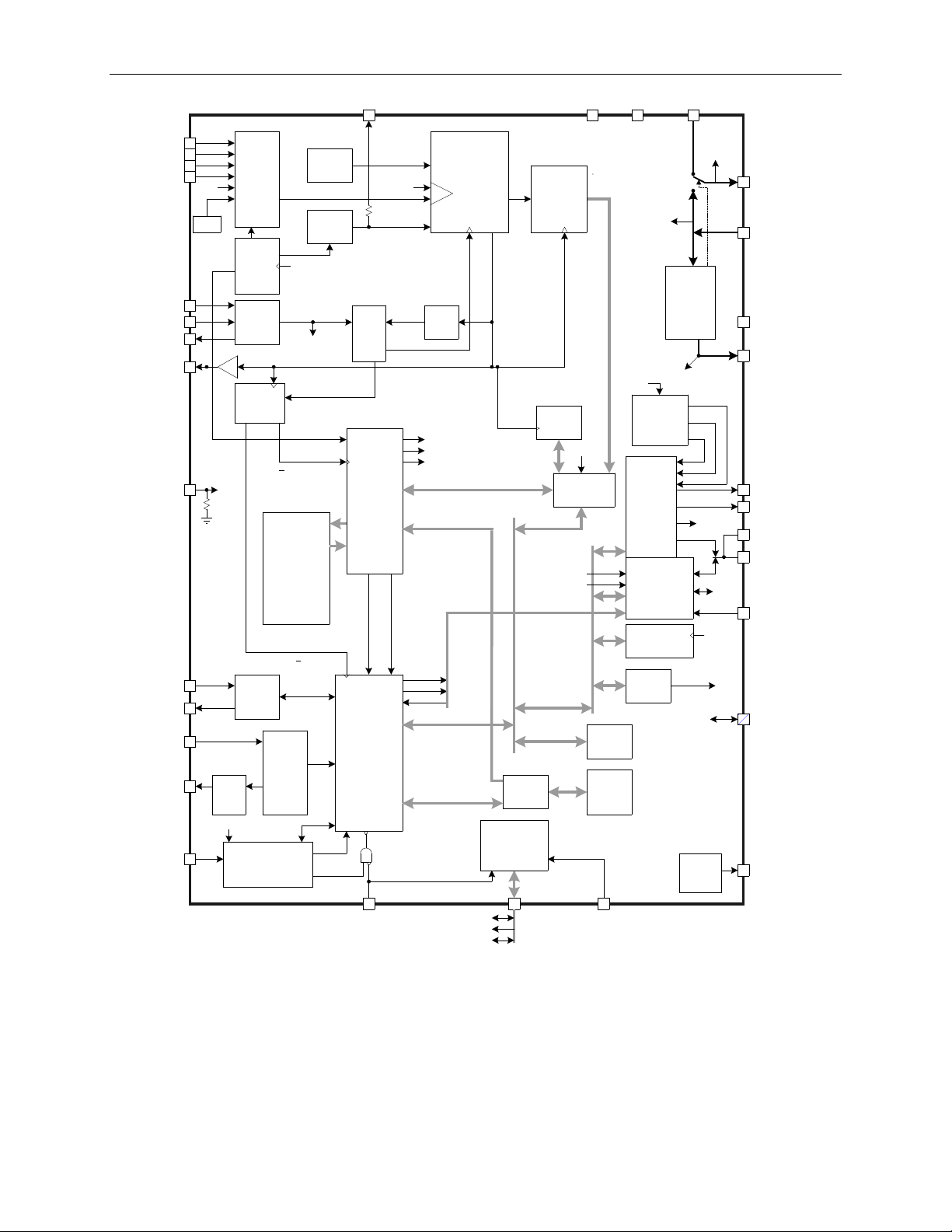

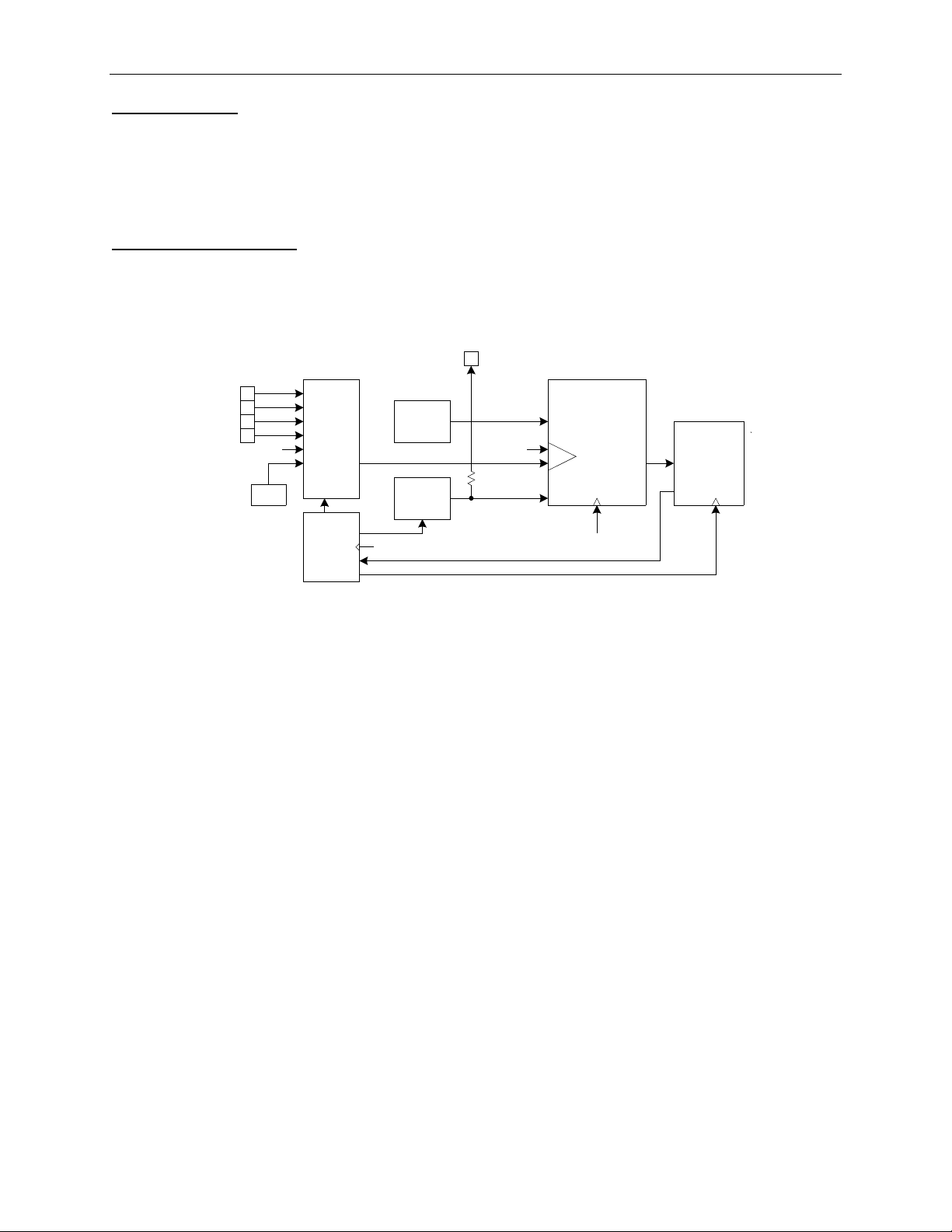

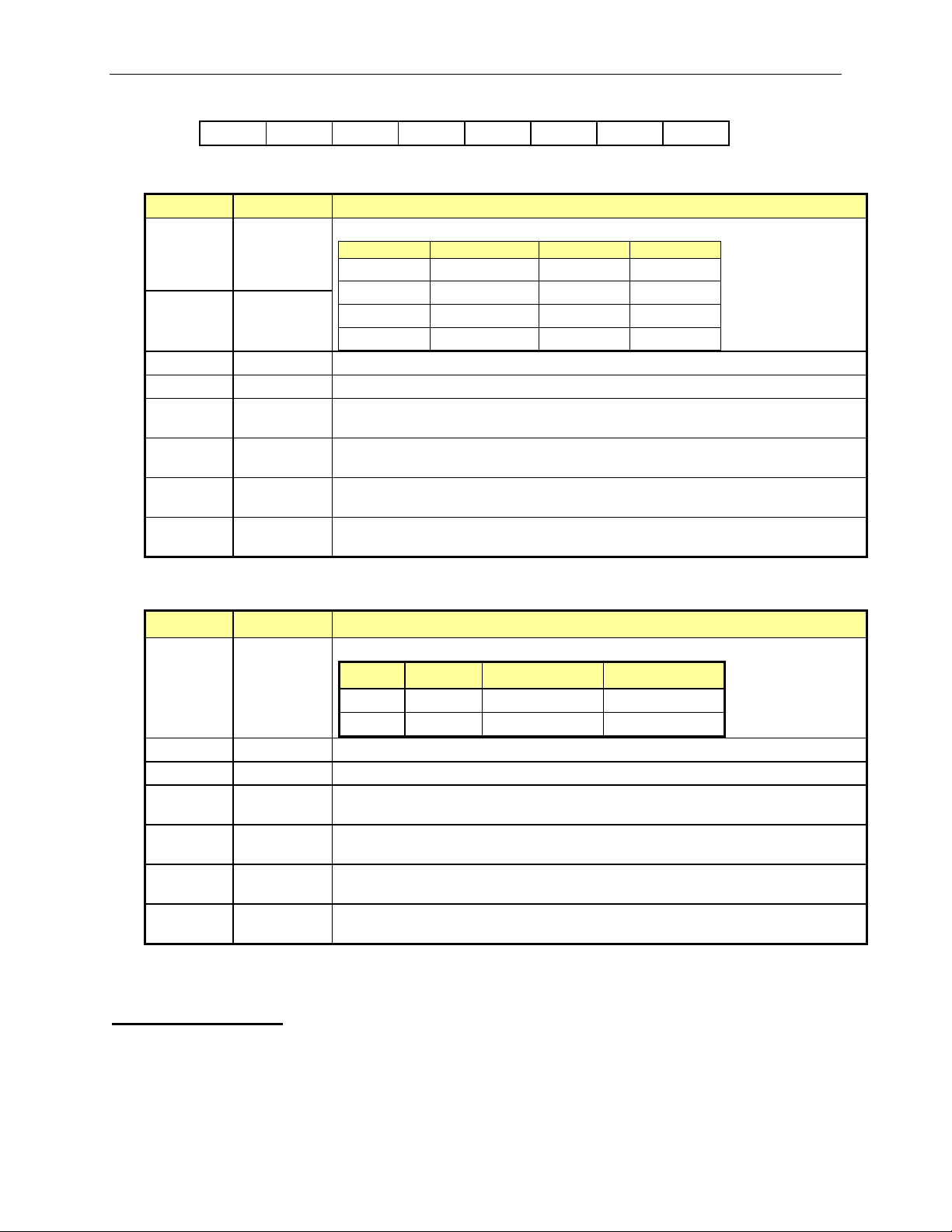

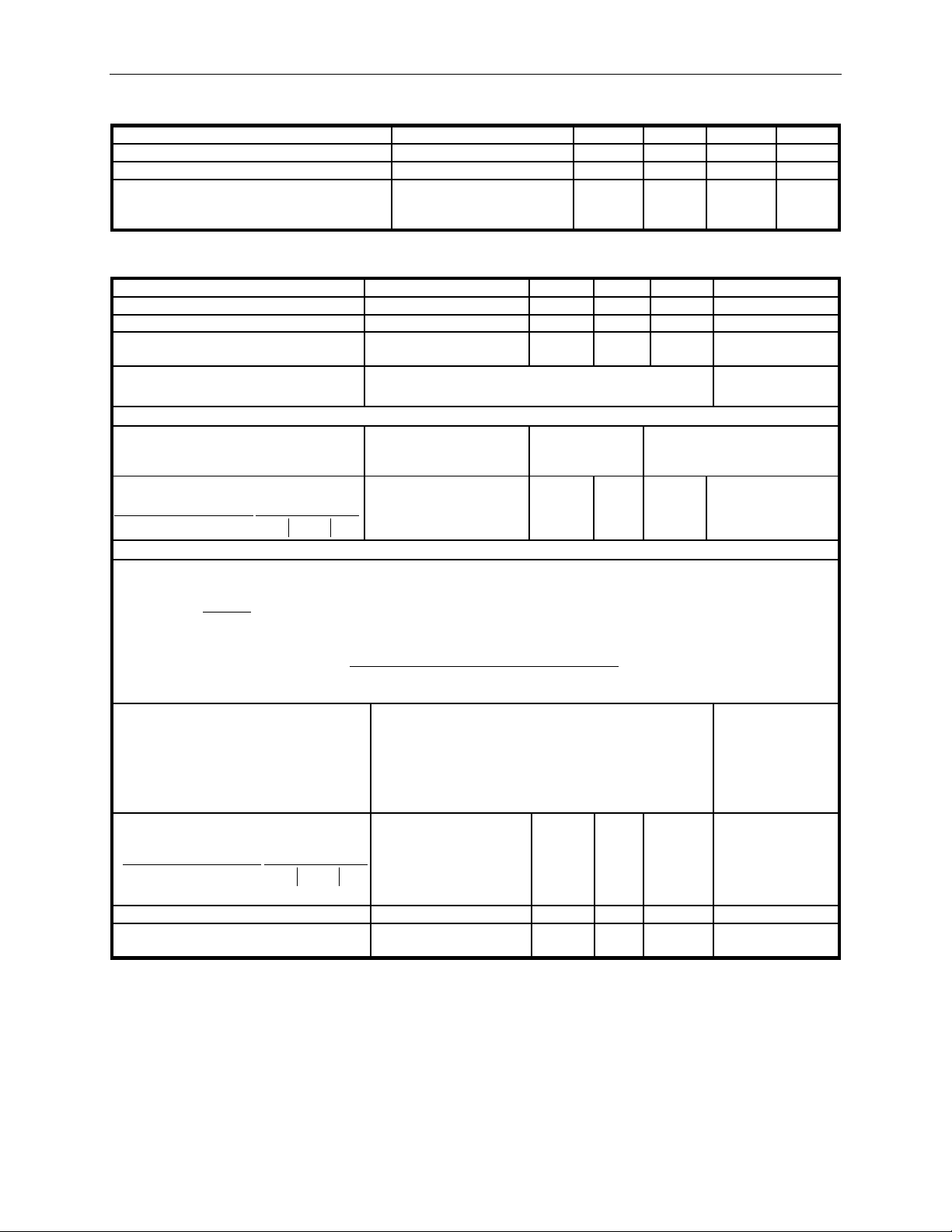

Figure 1: IC Functional Block Diagram .................................................................................................................................... 9

Figure 2: General Topology of a Chopped Amplifier ............................................................................................................. 11

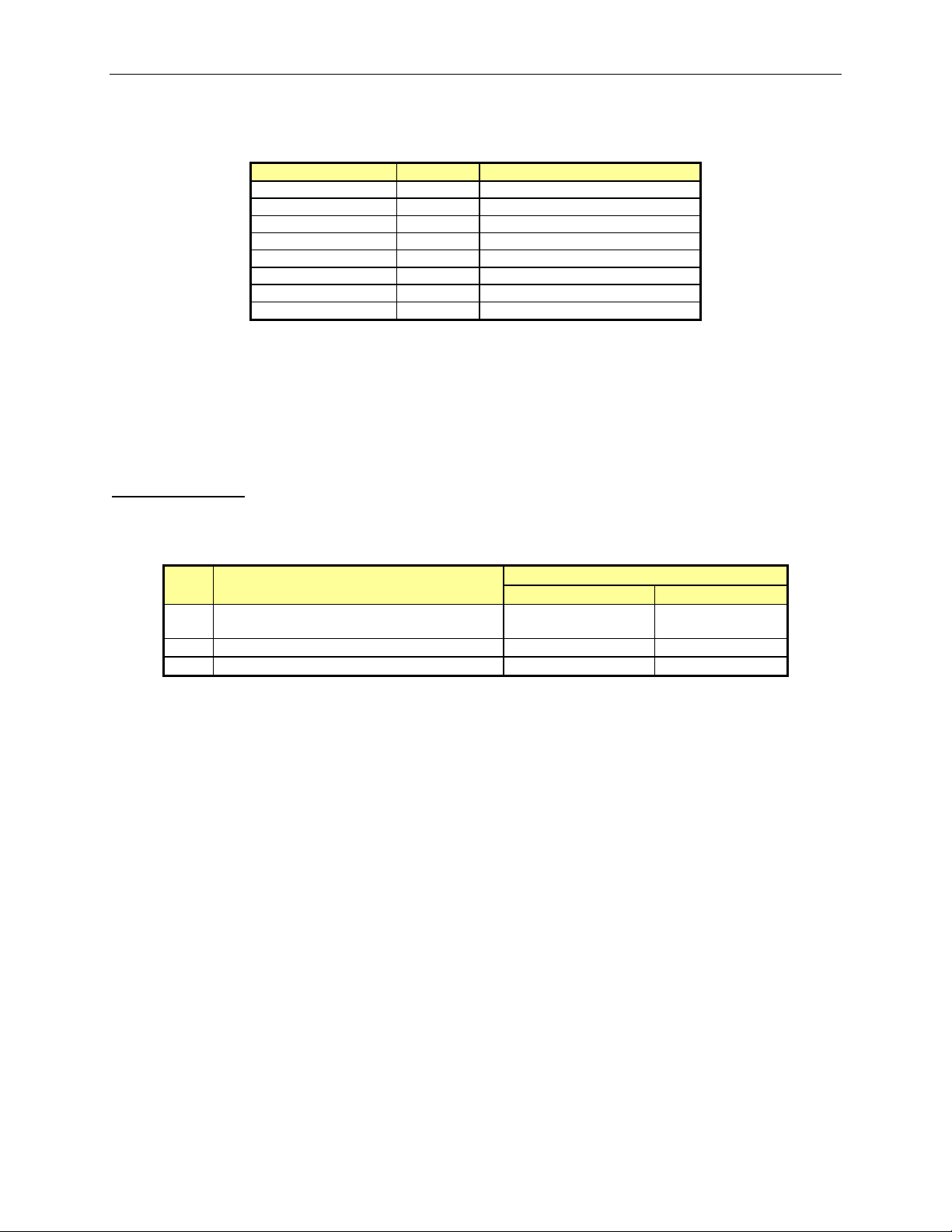

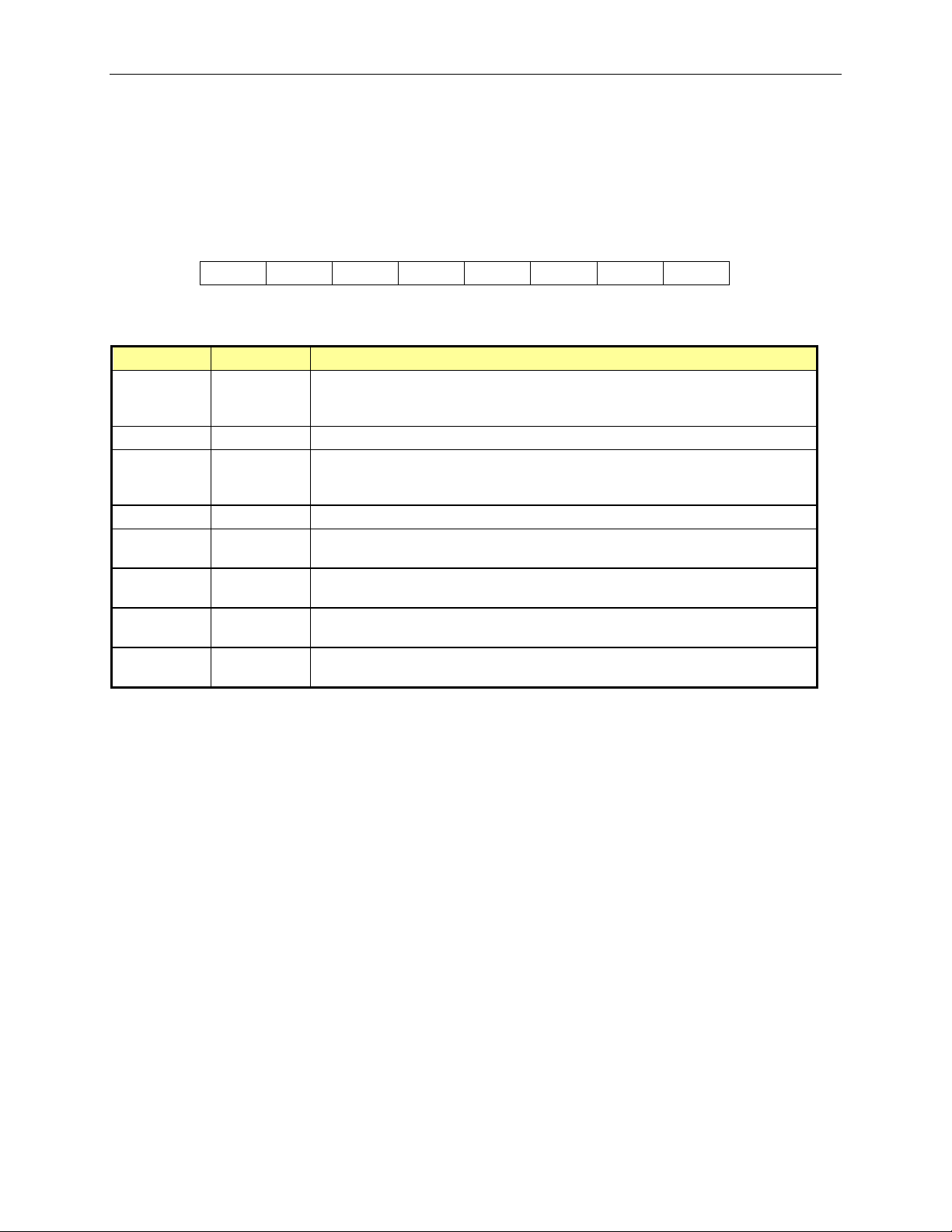

Figure 3: AFE Block Diagram................................................................................................................................................. 13

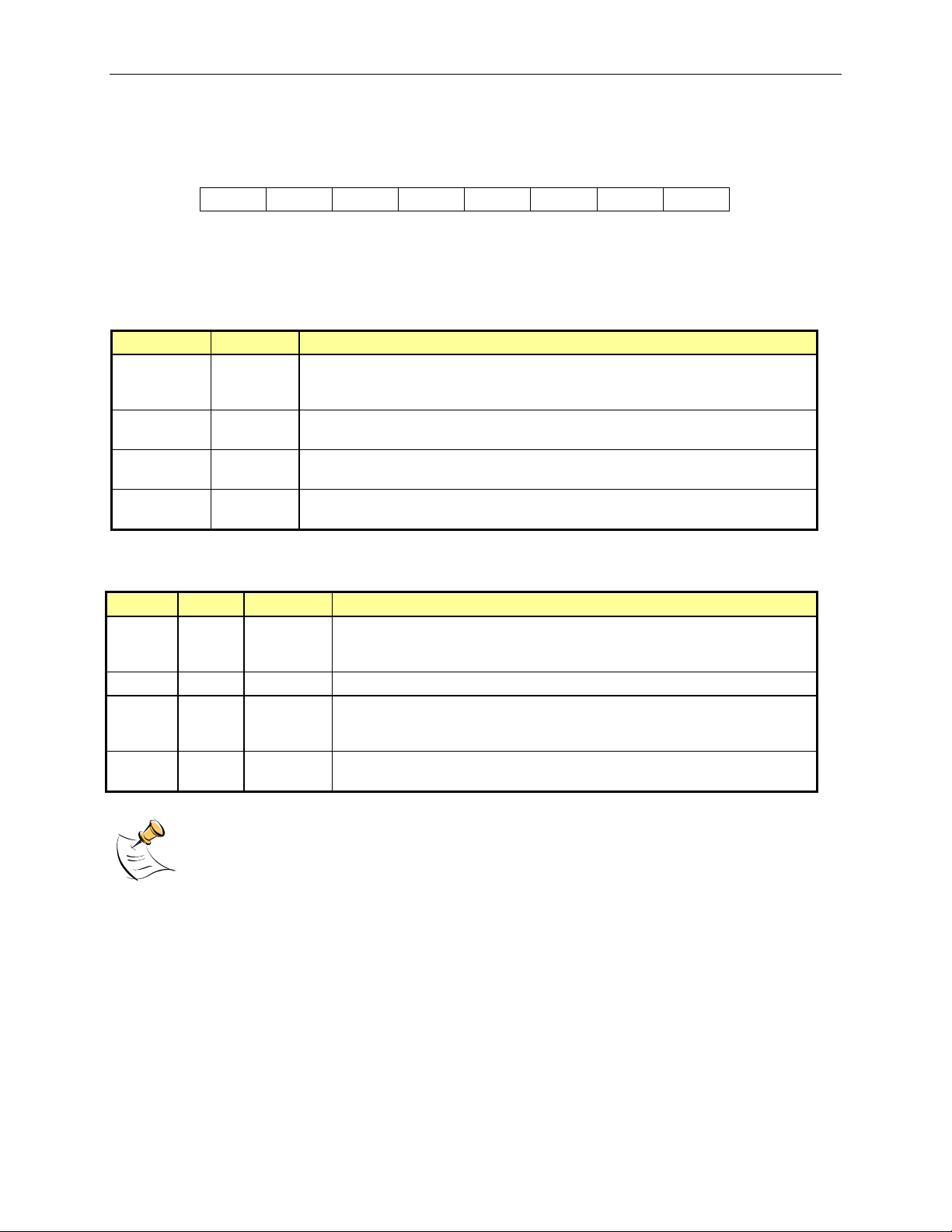

Figure 4: Samples from Multiplexer Cycle ............................................................................................................................ 16

Figure 5: Accumulation Interval ............................................................................................................................................ 16

Figure 6: Interrupt Structure ................................................................................................................................................. 37

Figure 7: Optical Interface .................................................................................................................................................... 40

Figure 8: Connecting an External Load to DIO Pins .............................................................................................................. 42

Figure 9: 3-Wire Interface. Write Command, HiZ=0. ............................................................................................................. 44

Figure 10: 3-Wire Interface. Write Command, HiZ=1 ............................................................................................................ 44

Figure 11: 3-Wire Interface. Read Command........................................................................................................................ 45

Figure 12: 3-Wire Interface. Write Command when CNT=0 .................................................................................................. 45

Figure 13: 3-Wire Interface. Write Command when HiZ=1 and WFR=1. .............................................................................. 45

Figure 14: Functions defined by V1 ...................................................................................................................................... 46

Figure 15: Voltage. Current, Momentary and Accumulated Energy ...................................................................................... 48

Figure 16: Timing Relationship between ADC MUX, Compute Engine, and Serial Transfers. ............................................... 49

Figure 17: RTM Output Format ............................................................................................................................................. 49

Figure 18: Operation Modes State Diagram .......................................................................................................................... 52

Figure 19: Functional Blocks in BROWNOUT Mode (inactive blocks grayed out) ................................................................. 53

Figure 20: Functional Blocks in LCD Mode (inactive blocks grayed out) .............................................................................. 54

Figure 21: Functional Blocks in SLEEP Mode (inactive blocks grayed out) .......................................................................... 55

Figure 22: Transition from BROWNOUT to MISSION Mode when System Power Returns .................................................. 56

Figure 23: Power-Up Timing with V3P3SYS and VBAT tied together ................................................................................... 56

Figure 24: Power-Up Timing with VBAT only ....................................................................................................................... 57

Figure 25: Wake Up Timing ................................................................................................................................................... 58

Figure 26: MPU/CE Data Flow ............................................................................................................................................... 59

Figure 27: MPU/CE Communication ..................................................................................................................................... 59

Figure 28: Resistive Voltage Divider (Left), Current Transformer (Right) ............................................................................ 60

Figure 29: Resistive Shunt .................................................................................................................................................... 60

Figure 30: Error Band for VREF over Temperature (Regular-Accuracy Parts) ...................................................................... 62

Figure 31: Error Band for VREF over Temperature (High-Accuracy Parts) ........................................................................... 63

Figure 32: Crystal Frequency over Temperature ................................................................................................................... 64

Figure 33: Crystal Compensation .......................................................................................................................................... 65

Figure 34: Connecting LCDs ................................................................................................................................................. 66

Figure 35: I2C EEPROM Connection ...................................................................................................................................... 68

Figure 36: Three-Wire EEPROM Connection ......................................................................................................................... 69

Figure 37: Connections for the RX Pin .................................................................................................................................. 69

Figure 38: Connection for Optical Components .................................................................................................................... 70

Figure 39: Voltage Divider for V1 .......................................................................................................................................... 70

Figure 40: External Components for RESET: Development Circuit (Left), Production Circuit (Right) .................................. 71

Figure 41: External Components for the Emulator Interface ................................................................................................. 71

Figure 42: Wh Accuracy, 0.1A to 200A at 240V/50Hz and Room Temperature .................................................................... 97

Figure 43: Meter Accuracy over Harmonics at 240V, 30A .................................................................................................... 97

Figure 44: Typical Meter Accuracy over Temperature Relative to 25°C (71M6521FE) ......................................................... 98

Page: 6 of 107 Rev 2

Page 7

71M6521DE/DH/FE Data Sheet

List of Tables

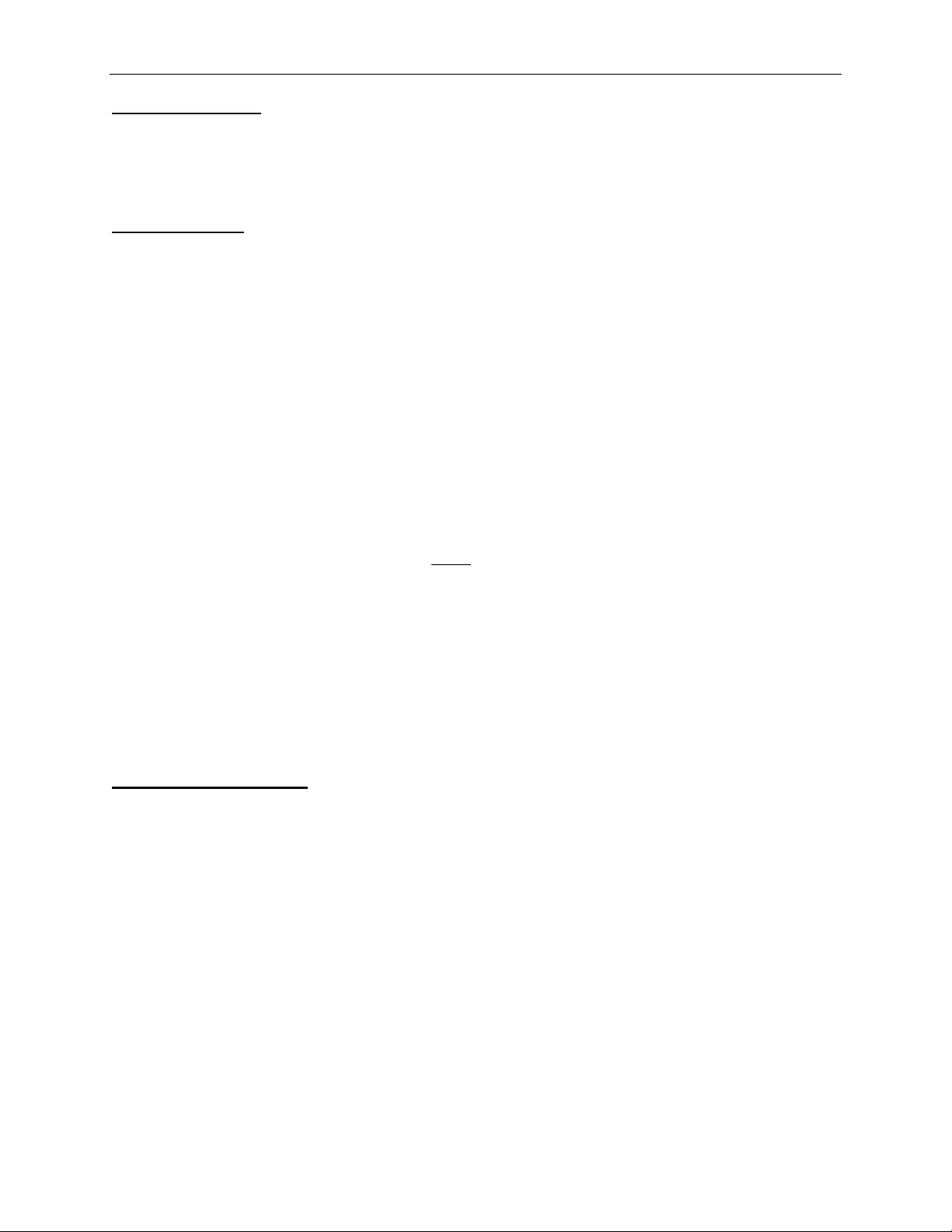

Table 1: Inputs Selected in Regular and Alternate Multiplexer Cycles .................................................................................. 11

Table 2: CE DRAM Locations for ADC Results ...................................................................................................................... 14

Table 3: Meter Equations. .................................................................................................................................................... 14

Table 4: Memory Map ........................................................................................................................................................... 17

Table 5: Stretch Memory Cycle Width .................................................................................................................................. 18

Table 6: Internal Data Memory Map ...................................................................................................................................... 19

Table 7: Special Function Registers Locations ..................................................................................................................... 19

Table 8: Special Function Registers Reset Values ................................................................................................................ 20

Table 9: PSW Register Flags ................................................................................................................................................. 21

Table 10: PSW Bit Functions................................................................................................................................................. 21

Table 11: Port Registers ....................................................................................................................................................... 22

Table 12: Special Function Registers .................................................................................................................................... 23

Table 13: Baud Rate Generation ............................................................................................................................................ 24

Table 14: UART Modes ......................................................................................................................................................... 24

Table 15: The S0CON Register ............................................................................................................................................. 24

Table 16: The S1CON register .............................................................................................................................................. 25

Table 17: The S0CON Bit Functions ..................................................................................................................................... 25

Table 18: The S1CON Bit Functions ..................................................................................................................................... 25

Table 19: The TCON Register .............................................................................................................................................. 26

Table 20: The TCON Register Bit Functions .......................................................................................................................... 26

Table 21: The TMOD Register .............................................................................................................................................. 27

Table 22: TMOD Register Bit Description ............................................................................................................................ 27

Table 23: Timers/Counters Mode Description ...................................................................................................................... 27

Table 24: Timer Modes ......................................................................................................................................................... 28

Table 25: The PCON Register .............................................................................................................................................. 28

Table 26: PCON Register Bit Description ............................................................................................................................. 28

Table 27: The IEN0 Register (see also Table 32) ................................................................................................................. 29

Table 28: The IEN0 Bit Functions (see also Table 32) .......................................................................................................... 29

Table 29: The IEN1 Register (see also Tables 30/31) .......................................................................................................... 29

Table 30: The IEN1 Bit Functions (see also Tables 30/31) ................................................................................................... 29

Table 31: The IP0 Register (see also Table 45) .................................................................................................................... 29

Table 32: The IP0 bit Functions (see also Table 45) ............................................................................................................. 30

Table 33: The WDTREL Register ......................................................................................................................................... 30

Table 34: The WDTREL Bit Functions .................................................................................................................................. 30

Table 35: The IEN0 Register ................................................................................................................................................ 31

Table 36: The IEN0 Bit Functions ......................................................................................................................................... 31

Table 37: The IEN1 Register ................................................................................................................................................ 31

Table 38: The IEN1 Bit Functions ......................................................................................................................................... 31

Table 39: The IEN2 Register ................................................................................................................................................ 32

Table 40: The IEN2 Bit Functions ......................................................................................................................................... 32

Table 41: The TCON Register .............................................................................................................................................. 32

Table 42: The TCON Bit Functions ....................................................................................................................................... 32

Table 43: The T2CON Bit Functions ..................................................................................................................................... 32

Table 44: The IRCON Register ............................................................................................................................................. 33

Table 45: The IRCON Bit Functions ..................................................................................................................................... 33

Table 46: External MPU Interrupts ........................................................................................................................................ 33

Table 47: Interrupt Enable and Flag Bits .............................................................................................................................. 34

Table 48: Priority Level Groups ............................................................................................................................................ 35

Table 49: The IP0 Register ................................................................................................................................................... 35

Table 50: The IP1 Register: .................................................................................................................................................. 35

Table 51: Priority Levels ....................................................................................................................................................... 35

Table 52: Interrupt Polling Sequence .................................................................................................................................... 36

Table 53: Interrupt Vectors ................................................................................................................................................... 36

Table 54: Data/Direction Registers and Internal Resources for DIO Pin Groups .................................................................. 41

Rev 2 Page: 7 of 107

Page 8

71M6521DE/DH/FE Data Sheet

Table 55: DIO_DIR Control Bit ............................................................................................................................................ 41

Table 56: Selectable Controls using the DIO_DIR Bits ........................................................................................................ 42

Table 57: EECTRL Status Bits ............................................................................................................................................. 43

Table 58: EECTRL bits for 3-wire interface ........................................................................................................................ 44

Table 59: TMUX[4:0] Selections .......................................................................................................................................... 47

Table 60: Available Circuit Functions (“—“ means “not active) ............................................................................................ 51

Table 62: VREF Definition for the High-Accuracy Parts ........................................................................................................ 62

Table 63: Frequency over Temperature................................................................................................................................. 64

Table 64: LCD and DIO Pin Assignment by LCD_NUM for the QFN-68 Package ................................................................ 67

Table 65: LCD and DIO Pin Assignment by LCD_NUM for the LQFP-64 Package .............................................................. 68

Page: 8 of 107 Rev 2

Page 9

71M6521DE/DH/FE Data Sheet

IA

VA

MUX

XIN

XOUT

VREF

CKADC

CKTEST/

SEG19

CE

32 bit Compute

Engine

MPU

(80515)

CE

CONTROL

OPT_RX/

DIO1

OPT_TX/

DIO2/

WPULSE/

VARPULSE

RESET

V1

EMULATOR

PORT

CE_BUSY

UART

TX

RX

XFER BUSY

COM0..3

VLC2

LCD DISPLAY

DRIVER

DATA

00-7F

PROG

000-7FF

DATA

0000-FFFF

PROG

0000-7FFF

00007FFF

MPU XRAM

(2KB)

0000-07FF

DIGITAL I/O

CONFIG

2000-20FF

I/O RAM

CE RAM

(0.5KB)

MEMORY SHARE

1000-11FF

RTCLK

RTCLK (32KHz)

MUX_SYNC

CKCE

CKMPU

CK32

CE_E

RTM_E

LCD_E

LCD_CLK

LCD_MODE

DIO

4.9MHz

<4.9MHz

4.9MHz

GNDD

V3P3A

V3P3D

VBAT

VOLT

REG

2.5V to logic

V2P5

MPU_DIV

SUM_CYCLES

PRE_SAMPS

EQU

CKOUT_E

32KHz

TMUXOUT

MPU_RSTZ

FAULTZ

WAKE

TMUX[4:0]

CONFIGURATION

PARAMETERS

GNDA

VBIAS

December 11, 2006

CROSS

CK_GEN

OSC

(32KHz)

CK32

CKOUT_E

MCK

PLL

VREF

VREF_DIS

DIV

ADC

MUX

CTRL

MUX_DIV

CHOP_E

EQU

STRT

IB

MUX

MUX

CKFIR

4.9MHz

RTM

SEG34/DIO14 ..

SEG37/DIO17

WPULSE

VARPULSE

WPULSE

VARPULSE

TEST

TEST

MODE

LCD_MODE

VLC1

VLC0

LCD_E

<4.9MHz

LCD_NUM

DIO_R

DIO_DIR

LCD_NUM

DIO_PV/PW

MUX_ALT

SEG24/DIO4 ..

SEG31/DIO11

SDCK

SDOUT

SDIN

E_RXTX/SEG38

E_TCLK/SEG33

E_RST/SEG32

FLASH

(16/32KB)

FLSH66ZT

V3P3A

FIR_LEN

FIR

SEG0..18

EEPROM

INTERFACE

DIO_EEX

CK_2X

ECK_DIS

V3P3D

LCD_GEN

X4MHZ

PB

RTC

RTC_INC_SEC

RTC_DEC_SEC

VB

VBIAS

MEMORY

SHARE

SEG32,33

SEG19,38

E_RXTX

E_TCLK

E_RST (Open Drain)

ICE_E

DIO1,2

VREF_CAL

∆Σ ADC

CONVERTER

+

-

VREF

ADC_E

RTM_0..3

CE_LCTN

PLS_MAXWIDTH

PLS_INTERVAL

PLS_INV

LCD_BLKMAP

LCD_SEG

LCD_Y

SLEEP

LCD_ONLY

V3P3SYS

TEST

MUX

DIO3,

DIO19/SEG39,

DIO20/SEG40,

DIO21/SEG41

(68 Pin Package Only)

V3P3D

TEMP

VBAT

VBAT

VBIAS

OPTICAL

COMP_STAT

POWER FAULT

OPT_TXE

OPT_TXINV

OPT_RXINV

OPT_RXDIS

MOD

OPT_TXMOD

OPT_FDC

CE_LCTN

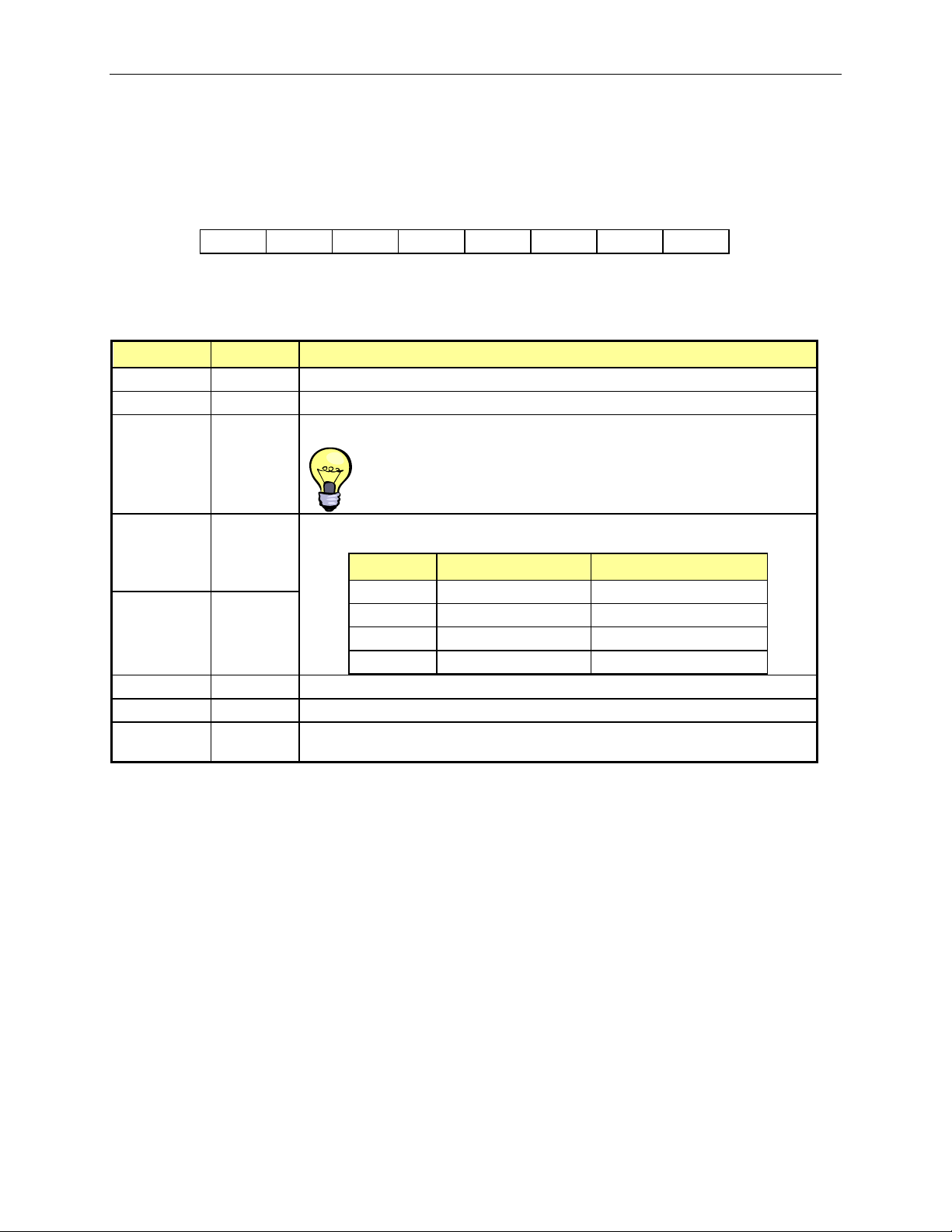

Figure 1: IC Functional Block Diagram

Rev 2 Page: 9 of 107

Page 10

71M6521DE/DH/FE Data Sheet

HARDWARE DESCRIPTION

Hardware Overview

The Teridian 71M6521DE/DH/FE single-chip energy meter integrates all primary functional blocks required to

implement a solid-state electricity meter. Included on chip are an analog front end (AFE), an independent digital

computation engine (CE), a n 8051-compatible microprocessor (MPU) whic h executes one instruction per c lock cycle

(80515), a voltage reference, a tem perature sensor, LC D drivers , RAM, flash memory, a real time clock (RT C), and a

variety of I/O pins. Various current sensor technologies are supported including Current Transformers (CT), and

Resistive Shunts.

In a typical application, the 32-bit compute engine (CE) of the 71M6521DE/DH/FE sequentially processes the

samples from the voltage input s on pins IA, VA, IB, VB and performs calcul ations to measure active energy (Wh),

reactive energy (VARh), A

MPU, processed further and output using the peripheral devices available to the MPU.

In addition to advanced measureme nt functions, the real time cloc k function a llows the 71M 6521DE/DH/FE to record

time of use (TOU) metering infor mation for multi-rate applic ations and to time-stamp tamper event s. Measurements

can be displayed on 3.3V LCD common ly used in low temperature environm ents. Flexible mapping of LCD display

segments will facilitate integrati on of existing custom LCD. Design trade-off bet ween number of LCD segments vs.

DIO pins can be implemented in software to accommodate various requirements.

In addition to the temperature-trimmed ultra-precision voltage reference, the on-chip digital temperature compensation mechanism includes a temper ature sens or and ass ociated cont rols f or correcti on of un wanted temperat ure

effects on measurement and RTC ac curacy, e.g. to meet the requirements of ANSI and IEC standar ds. Temper ature

dependent external compone nts such as cryst al oscillat or, c urrent tra nsfor mers (CT s), and their corres ponding signa l

conditioning circuits can be characterized and their correction factors can be programmed to produce electricity

meters with exceptional accuracy over the industrial temperature r ange.

The 71M6521DH is trimmed at +85°C in addition to the trim at room temperature, which provides a set of

individualized trim fuse values that enable temperature compensation with accuracy better than ±20 PPM/°C.

One of the two internal UARTs is ad apted t o supp ort an Inf rared LED with int ernal dr ive a nd sens e conf igurat ion, a nd

can also function as a standard UART. The optical output can be modulated at 38 kHz. This flexibility makes it

possible to implement AMR meters with an IR interface. A block diagra m of the IC is shown in Figure 1. A det ailed

description of various functional blocks follows.

The AFE of the 71M6521DE/DH/FE is composed of an input multiplexer , a delta-sigma A/D conv erter and a voltage

reference.

2

h, and V2h for four-quadrant metering. These measur ements are then accessed by the

Analog Front End (AFE)

Input Multiplexer

The input multiplexer supports up to four input signals that are applied to pins IA, VA, IB and VB of the device.

Additionally, using the altern ate mux selection, it has the ability to sel ect temperature and the battery voltage. The

multiplexer can be operated in two modes:

• During a normal multiplexer cycle, the signals from the IA, IB, VA, and VB pins are selected.

• During the alternate multiplexer c ycle, the temperature sig nal (TEMP) and the battery monitor are selected,

along with the signal sources sho wn i n Table 1. To prevent unnecessary drainage on the battery, the battery

monitor is enabled only with the BME bit (0x2020[6]) in the I/O RAM.

The alternate mux cycles are usu ally performed infrequently (e.g. every second) by the MPU. In order to prevent

disruption of the voltage track ing PLL and voltage allpass net works, VA is not replaced in the ALT mux sel ections.

Table 1 details the regular and alternative MUX sequences. M i s sing samples due to an ALT multiplexer sequence are

filled in by the CE.

Page: 10 of 107 Rev 2

Page 11

71M6521DE/DH/FE Data Sheet

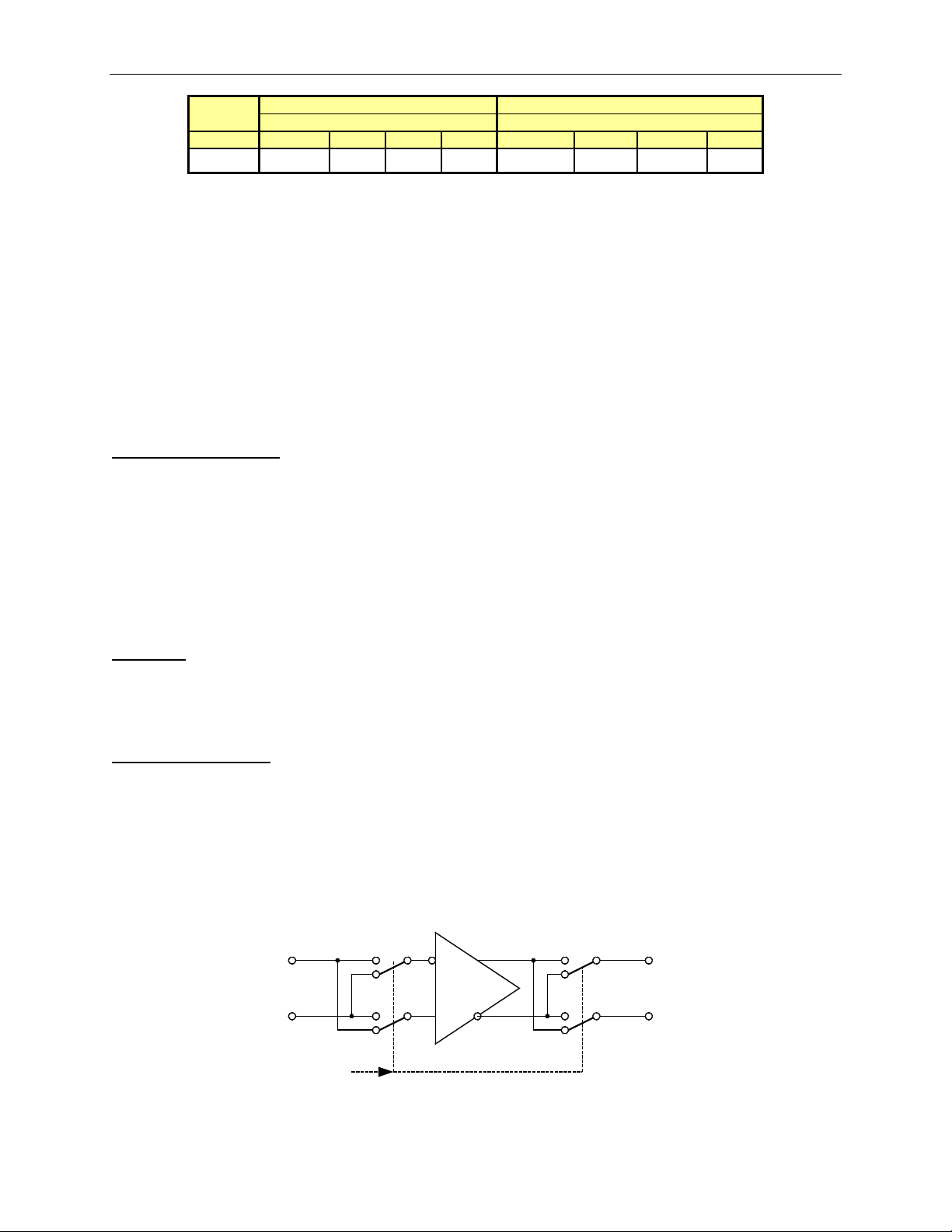

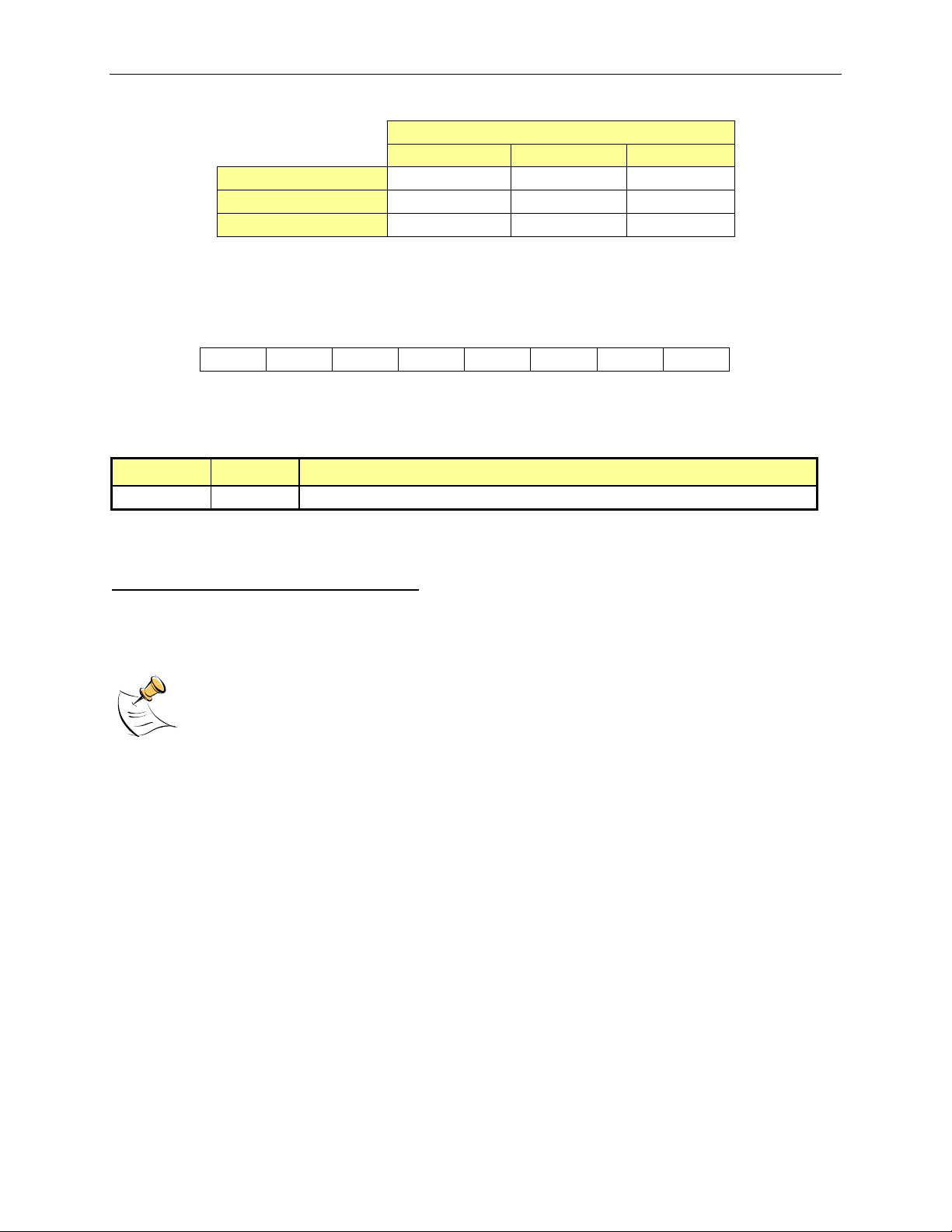

Regular MUX Sequence

ALT MUX Sequence

Mux State

Mux State

EQU

0 1 2 3 0 1 2

3

G

-

+V

inp

V

outp

V

outn

V

inn

CROSS

A

B

A

B

A

B

A

B

0, 1, 2 IA VA IB VB TEMP VA VBAT

VB

Table 1: Inputs Selected in Regular and Alternate Multiplexer Cycles

In a typical application, IA and IB are c onnected to current transf ormers that sense the current on each phase of the

line voltage. VA and VB are typically connected to voltage sensors thro ugh resistor dividers.

The multiplexer control circuit handles the s etting of the m ultiplexer. T he function of the c ontrol circuit i s governed by

the I/O RAM registers MUX_ALT, MUX_DIV and EQU. MUX_DIV controls the number of samples per cycle. It can

request 2, 3, or 4 multiplexer states per c ycle. Multiplexer states above 4 are reserve d and must not be used. The

multiplexer always starts at the beginning of its list and proceeds until MUX_DIV states have been converted.

The MUX_ALT bit requests an altern ative multiple xer frame. The bi t may be asserted o n any MPU cycle and may be

subsequently de-asserted on an y cycle including t he next one. A ris ing edge on MUX_ALT will cause t he multiplexer

control circuit to wait until the next multiplexer cycle and implement a single alternate cycle.

The multiple xer control circuit also controls the FIR filter initiation a nd the chopping of the ADC reference voltage,

VREF. The multiplexer control circuit is clocked by CK32, the 32768Hz c lock from the PLL bl ock, and launches with

each new pass of the CE program.

A/D Converter (ADC)

A single delta-sigma A/D conver ter digitiz es the vo ltage and c urrent inp uts to the 71M6521DE/DH/FE. The resolution

of the ADC is programmable using th e FIR_LEN regist er as shown in the I/O RAM section. ADC reso lution can be

selected to be 21 bits (FIR_LEN=0), or 22 bit s (FIR_LEN=1). Conversion tim e is t wo cycles of CK 32 with FIR_LEN = 0

and three cycles with FIR_LEN = 1.

In order to provide the maximum resolution, the ADC should be operated with FIR_LEN = 1. Accuracy and

timing specifications in this data sheet are based on FIR_LEN = 1.

Initiation of each ADC conversion is controll ed by th e multipl exer contro l circ uit as descri bed prev iousl y. At the end of

each ADC conversion, the FIR filter out put data is stored into the CE DRAM location de termined by the multiplexer

selection.

FIR Filter

The finite impulse response fi lter is an integral part of the ADC and it is optimized for u se with the multiplexer. The

purpose of the FIR filter is to decim ate the ADC out put to the desir ed resolut ion. At the e nd of each ADC conversion,

the output data is stored into the fixed CE DRAM location determined b y the multiplexer selec tion. FIR data is st ored

LSB justified, but shifted left by nine bits.

Voltage References

The device includes an on-chip precision bandgap voltage reference that incorporates auto-zero techniques. The

reference is trimmed to minimize errors caused by component mismatch and drift. T he result is a voltage o utput with

a predictable temperature coefficient.

The amplifier within the reference i s chopper stabilized, i.e. the polarit y can be switched by the MPU using the I/O

RAM register CHOP_E (0x2002[5:4]). T he two bits in the CHOP_E register enable the MPU to operate the ch opper

circuit in regular or inverted operation, or in “toggling” mode. When the chopper circuit is toggled in between

multiplexer cycles, DC offsets on the measured signals will automatically be averaged out.

The general topology of a chopped amplifier is given in Figure 2.

Rev 2 Page: 11 of 107

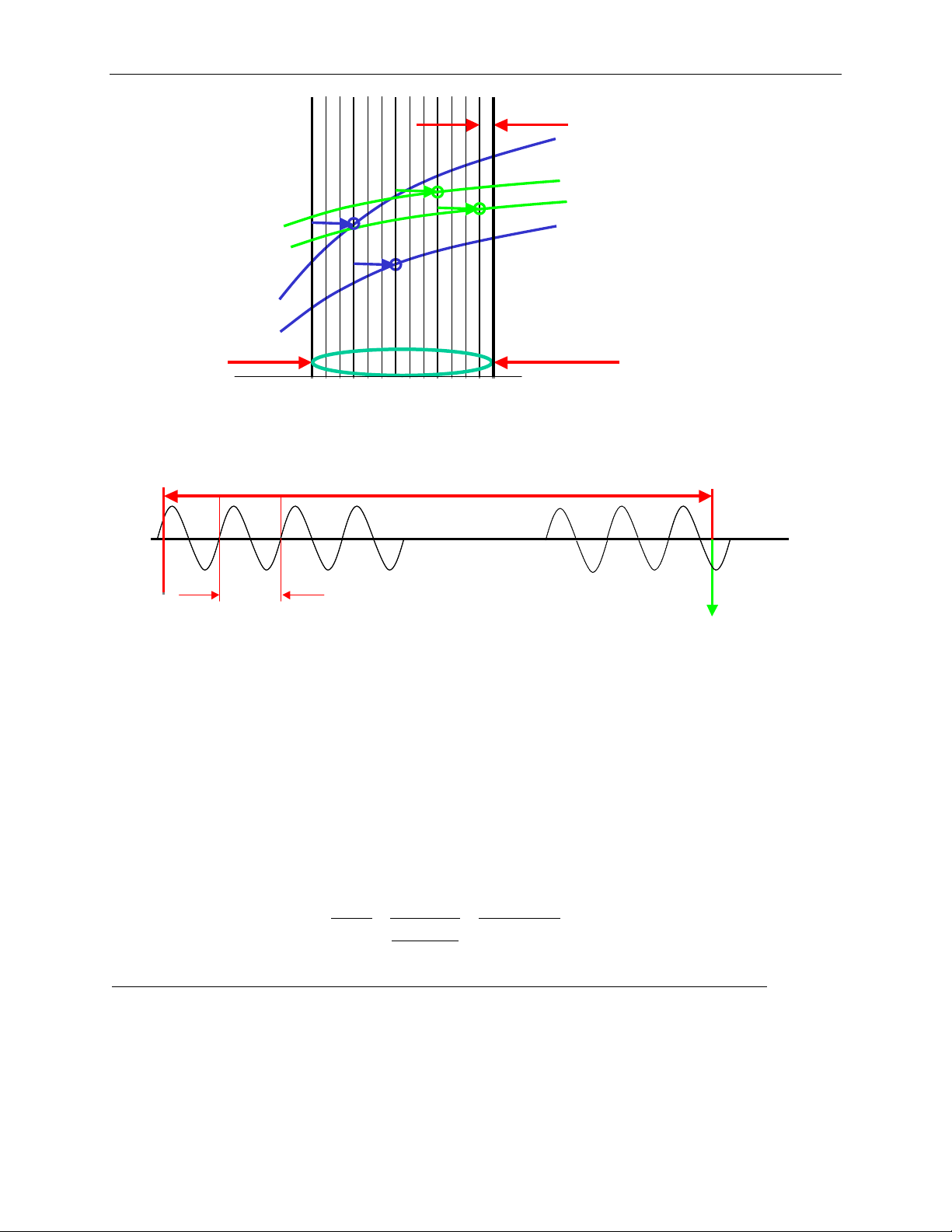

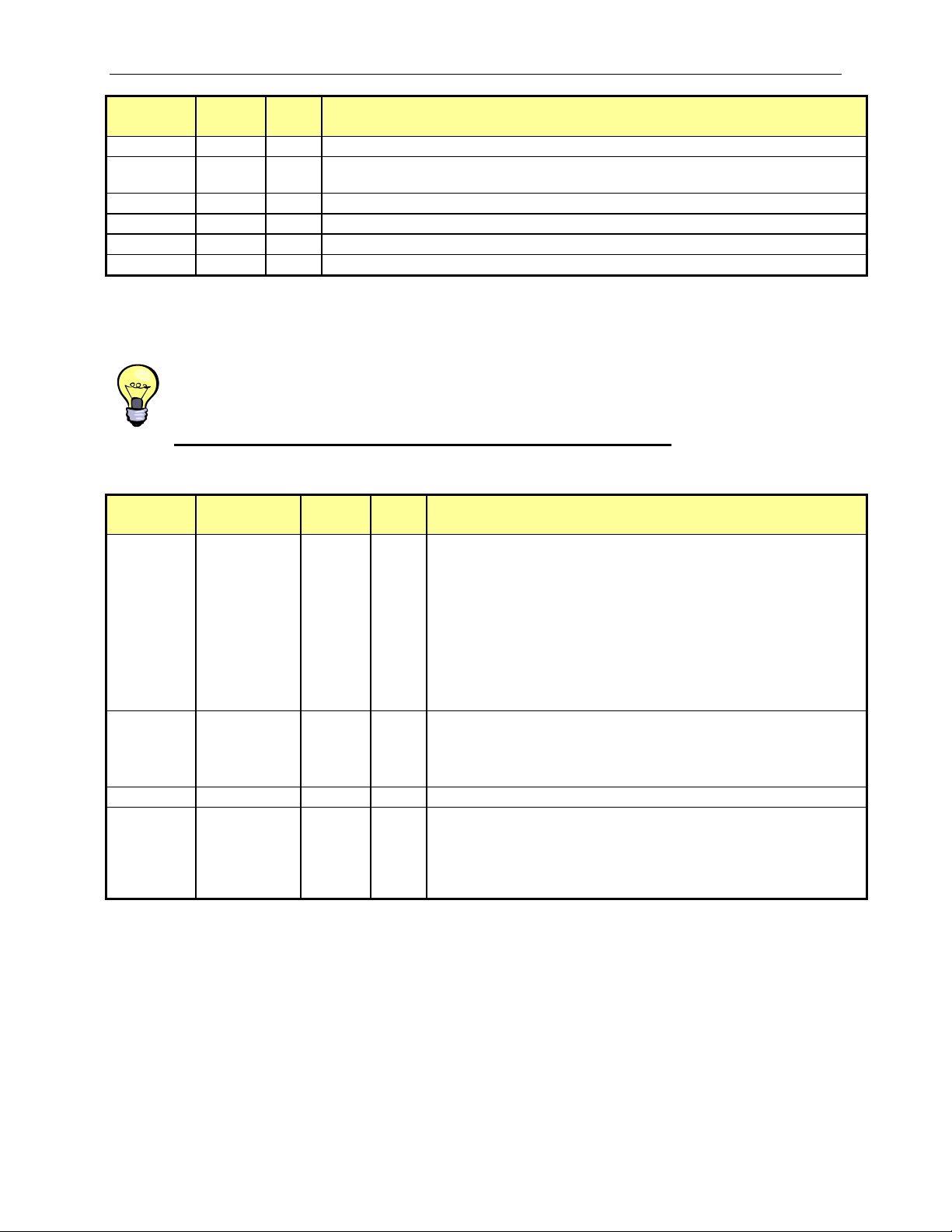

Figure 2: General Topology of a Chopped Amplifier

Page 12

71M6521DE/DH/FE Data Sheet

It is assumed that an offset voltage Voff appears at the positive amplifier input. With all switches, as controlled by

CROSS in the “A” position, the output v oltage is:

Voutp – Voutn = G (Vinp + Voff – Vinn) = G (Vinp – Vinn) + G Voff

With all switches set to the “B” position by applying the inverted CROSS signal, the output voltage is:

Voutn – Voutp = G (Vinn – Vinp + Voff) = G (Vinn – Vinp) + G Voff, or

Voutp – Voutn = G (Vinp – Vinn) - G Voff

Thus, when CROSS is toggled, e. g. after each multiplexer cycle, the offset will alternately appear on t he output as

positive and negative, which results in the offset effectively being eliminated, regardless of its pol ar i ty or magnitude.

When CROSS is high, the hooku p of the amplifier input devices is reversed. This preserves the ove rall polarity of

that amplifier gain; it inverts its input offset . By altern ately r eversing t he conn ection, the amplif ier’s offset i s averag ed

to zero. This removes the most s ignificant long-term drift mechanism in the voltag e reference. The CHOP_E bits

control the behavior of CROSS. The CRO SS signal will reverse the amplifi er connection in the voltage reference i n

order to negate the effects of its offset. On the first CK32 rising edge after the last mux state of its sequence, the mux

will wait one additional CK32 cycle before beginning a new frame. At the beginning of this cycle, the value of CROSS

will be updated according to the CHOP_E bits. The extra CK32 c ycle allows time for the chopped VREF to settle.

During this cycle, MUXSYNC is held high. The leading edge of muxs ync initiates a pass through the CE program

sequence. The beginning of the sequence is the serial readout of the 4 RTM words.

CHOP_E has 3 s tates: positiv e, reverse, and chop. In the ‘positive’ stat e, CROSS is held low. In t he ‘reverse’ state,

CROSS is held high. In t he ‘chop’ stat e, CROSS is toggled near t he end of eac h Mux Frame, as descri bed above. I t

is desirable that CROSS take on alt ernate values at the b eginning of each M ux cycle. For this reas on, if ‘chop’ stat e

is selected, CROSS will not toggle at the end of the last Mux cycle in a SUM cycle.

The internal bias voltage VBIAS (t ypically 1.6 V) is used by the ADC when measuring t he temperature and battery

monitor signals.

Temperature Sensor

The 71M6521DE/DH/FE includes an on-chip temperatur e sensor implemented as a bandgap reference. It is used t o

determine the die temperature The MPU may request an alternate multiplexer cycle containing the temperature

sensor output by asserting MUX_ALT.

The primary use of the temperature data is to determine the magnitude of compensation required to offset the

thermal drift in the system (see secti on titled “Temperature Compensation”).

Page: 12 of 107 Rev 2

Page 13

71M6521DE/DH/FE Data Sheet

IA

VA

MUX

VREF

4.9MHz

VBIAS

CROSS

CK32

VREF

VREF_DIS

MUX

CTRL

MUX_DIV

CHOP_E

EQU

IB

MUX

MUX_ALT

V3P3A

FIR_LEN

FIR

VB

VBIAS

VREF_CAL

∆Σ ADC

CONVERTER

+

-

VREF

ADC_E

TEMP

VBAT

FIR_DONE

FIR_START

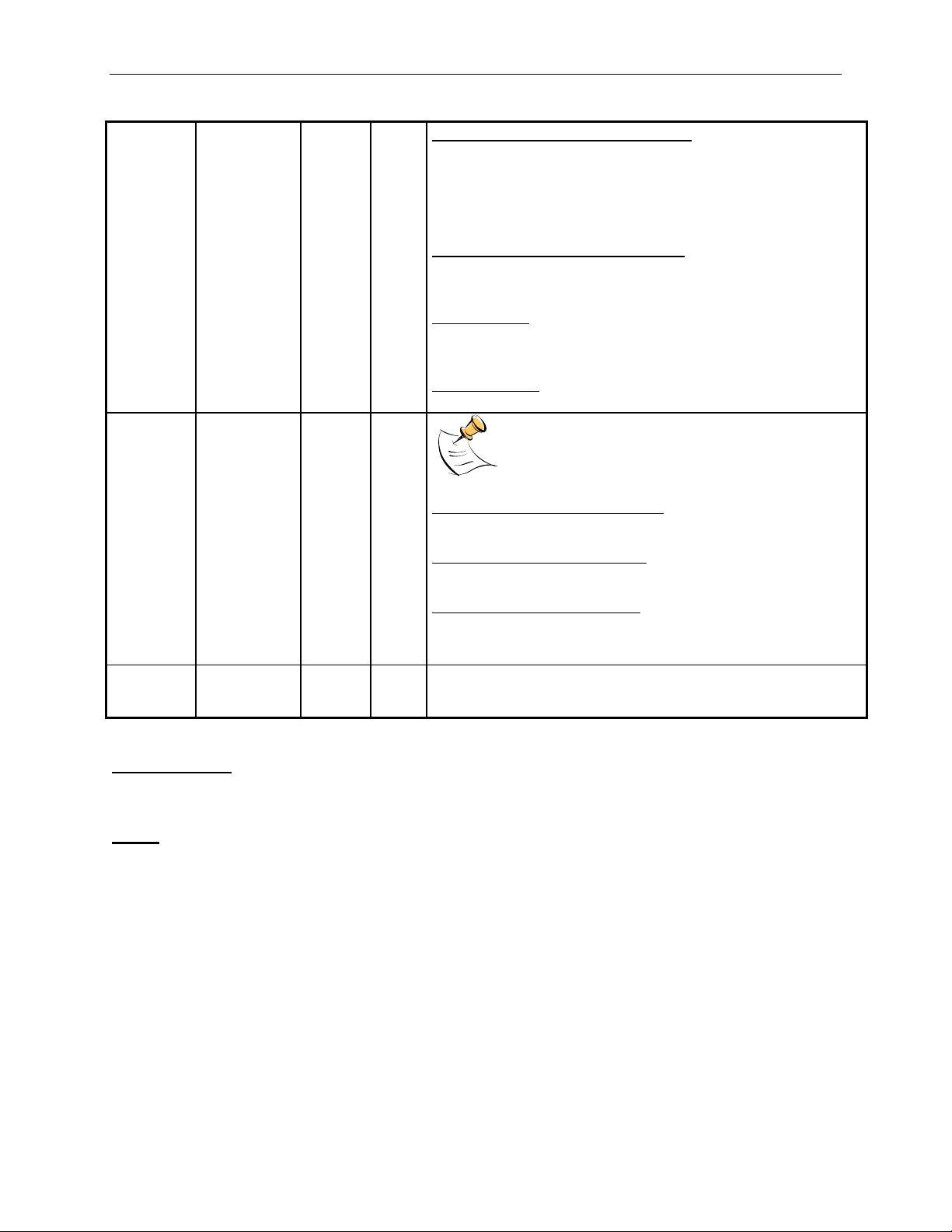

Battery Monitor

The battery voltage is measured by the ADC during alternative multiplexer frames if the BME (Battery Measure

Enable) bit in the I/O RAM is set. While BME is set, an on-chip 45kΩ load resistor is applied t o the battery, and a

scaled fraction of the batt ery voltage is a pplied to the ADC input. After ea ch alternative MUX frame, the result of the

ADC conversion is available at CE DRAM address 07. BME is ignored and assumed z ero when system power is not

available (V1 < VBIAS). See the Batter y Monitor section of the Electrical Spec ifications f or details regardin g the ADC

LSB size and the conversion accuracy.

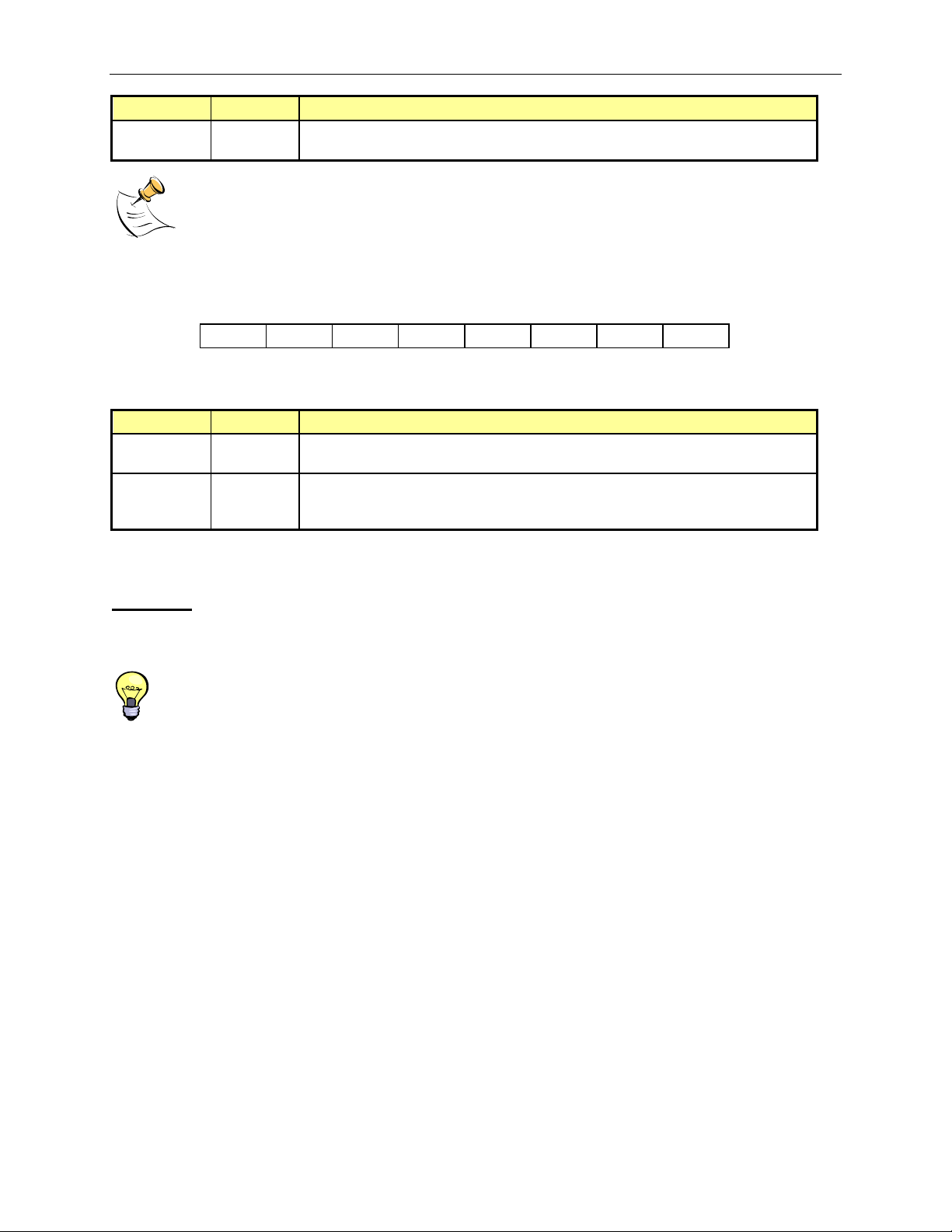

Functional Description

The AFE functions as a data acquisition system, controlled by the MPU. The main signals (IA, VA, IB, VB) are

sampled and the ADC counts obtained are stored in CE DRAM where they can be accessed by the CE and, if

necessary, by the MPU. Alternate m ultiplexer cycles are initiated less f requently by the MPU t o gather access to the

slow temperature and battery signal s .

Figure 3: AFE Block Diagram

Digital Computation Engine (CE)

The CE, a dedicated 32-bit signal process or, performs the precision com putations necessary to accur ately measure

energy. The CE calculations and proces ses include:

• Multiplication of each current s ample with its associated voltage sample to obtain the energ y per sample

(when multiplied with the const ant sample time).

• Frequency-insensitive dela y cancellation on all six channels (to com pensate for th e delay bet ween samples

caused by the multiplexing scheme).

• 90° phase shifter (for VAR calculations).

• Pulse generation.

• Monitoring of the input signal frequency (for frequency and phase inform ation).

• Monitoring of the input signal amplitude (for sag detection).

• Scaling of the processed samples b as ed on calibration coefficients.

The CE program resides in flash memory. Common access to flash memory by CE and MPU is controlled by a

memory share circuit. Each CE instr uction word is two bytes long. Allocated flash space for the CE program cann ot

exceed 1024 words (2KB). The CE program counter begins a pass through the CE code each time multiplexer state 0

begins. The code pass ends when a HALT instruction is executed. For proper operation, the code pass must be

completed before the multiplexer cycle ends (see System Timing Summary in the Functional Descriptio n S ection).

The CE program must begin on a 1Kbyte bo undary of the flash address. The I/O RA M register CE_LCTN[4:0]

defines which 1KB boundary contains the CE code. Thus, the first CE instruction is located at 1024*CE_LCTN[4:0].

The CE DRAM can be accessed by the FIR filter block, the RTM circuit, the CE, and the MPU. Assigned time slots

are reserved for FIR, RTM, and MPU, r es pectively, to prevent bus contention for CE DRAM data access. Holding registers are used to convert 8-bit wide MPU data to/from 32-bit wide CE DRAM data, and wait states are inserted as

needed, depending on the frequency of CKMPU.

Rev 2 Page: 13 of 107

Page 14

71M6521DE/DH/FE Data Sheet

ADDRESS (HEX)

NAME

DESCRIPTION

00

IA

Phase A current

01

VA

Phase A voltage

02

IB

Phase B current

03

VB

Phase B voltage

04

-

Not used

05

-

Not used

06

TEMP

Temperature

07

VBAT

Battery Voltage

Watt & VAR Formula

Element 0

Element 1

1 element, 2W 1φ with neutral current s ense

and tamper detection (VA connected to VB)

1

1 element, 3W 1φ

VA(IA-IB)/2

N/A

2

2 element, 4W 2φ

VA IA

VB IB

The CE DRAM contains 128 32-bit words. The MPU can read and write the CE DRAM as the primary means of data

communication between the two processors .

Table 2 shows the CE DRAM addresses allocated to analog inputs from the AF E .

Table 2: CE DRAM Locations for ADC Results

The CE of the 71M6521DE/DH/FE is aided by suppor t hardware that facilitates im plementation of equations, pulse

counters, and accumulators. This support hardware is controlle d through I/O RAM locations EQU (equation assist),

DIO_PV and DIO_PW (pulse count assist), and PRE_SAMPS and SUM_CYCLES (accumulation assist). PRE_SAMPS

and SUM_CYCLES support a dual level accumulation scheme where the first accumulator accumulate s results from

PRE_SAMPS samples an d the second accumulator acc umulates up to SUM_CYCLES of the first accumulator results.

The integration time for each ener gy output is PRE_SAMPS * SUM_CY CLES/2520.6 ( with MUX_DIV = 1). CE hardware

issues the XFER_BUSY interrupt when the accumulation is complet e.

Meter Equations

Compute Engine (CE) firmware a nd hardware for residential met er configurations implement the eq uations listed in

Table 3. The register EQU (l oc ated i n t he I/ O RAM) specif i es t he equat i on t o be use d b as ed o n the num ber of p has es

used for metering.

EQU

0

Description

VA IA VA IB

Table 3: Meter Equations.

Page: 14 of 107 Rev 2

Page 15

71M6521DE/DH/FE Data Sheet

Real-Time Monitor

The CE contains a Real-Time Monitor (RTM), which can be programmed through the UART to monitor four

selectable CE DRAM locations at f ull sample rate. The four monitored locations ar e serially output to t he TMUXOUT

pin via the digital output multi plexer at the beginning of each CE code pass. T he RTM can be enabled and disabled

with RTM_EN. The RT M output is clocked by CKTEST. E ach RTM word is clocked out in 35 c ycles and contains a

leading flag bit. See the Functional Description section for the RTM output format. RTM is low when not in us e.

Pulse Generator

The chip contains two pulse g enerator s that create l o w-jitt er puls es at a rat e set by either CE or MP U. T he func tion i s

distinguished by EXT_PULSE (a CE input vari able in CE DRAM):

• If EXT_PULSE = 1, APULSEW*WRATE and APULSER*WRATE control the pulse rate (external pulse

generation)

• If EXT_PULSE is 0, APULSEW is repl aced with WSUM_X and APULSER is replaced with VARSUM_X (internal

pulse generation).

The I/O RAM bits DIO_PV and DIO_PW, as described in the Digital I/O section, can be programmed to route

WPULSE to the output pin DIO6 and VAR PULSE to the o utput pi n DIO 7. Pulses c an als o be outp ut on O PT_T X (see

OPT_TXE[1:0] for details).

During each CE code pass, the hard ware stores exported sign bits in an 8-bit FIFO and outputs them at a spec ified

interval. This permits the CE c ode t o c alc ula t e al l of t he pu l se g en erat or o utput s at t he b eginni ng of its code p ass and

to rely on hardware to spread them over the MUX fr ame. The FIFO is reset at the beginning of each MUX frame.

PLS_INTERVAL controls the dela y to the first pulse update and the inter val between subsequent update s. Its LSB is

four CK_FIR cycles, or 4 * 203ns. If PLS_INTERVAL is zero, the FIFO is deactivated and the pulse outputs are

updated immediately. Thus, N

For use with the supplied standard Teridian CE code, PLS_INTERVAL is set to a fixed v alue of 81. PLS_INTERVAL is

specified so that all of the pulse updates are output before

On-chip hardware provides a maximum puls e width feat ure: PLS_MAXWIDTH[7:0] selects a maximum negativ e pulse

width to be ‘Nmax’ updates per multiplexer cycle according to the formula: Nmax = (2*PLS_MAXWIDTH+1). If

PLS_MAXWIDTH = 255, no width checking is performed.

Given that PLS_INTERVAL = 81, the maximum pulse width is determined by:

INTERVAL is 4*PLS_INTERVAL.

the MUX frame completes.

Maximum Pulse Width = (2 * PLS_MAXWIDTH +1) * 81*4*203ns = 65.9µs + PLS_MAXWIDTH * 131.5µs

If the pulse period correspon ding to the pulse rate exceeds the desired pulse width, a squar e wave with 50% dutycycle is generated.

The CE pulse output polarity is progr ammable to be either positiv e or negative. Pulse polarity may be i nverted with

PLS_INV. When this bit is set, the pulses are act i v e hi gh, rather than the more usual active low.

CE Functional Overview

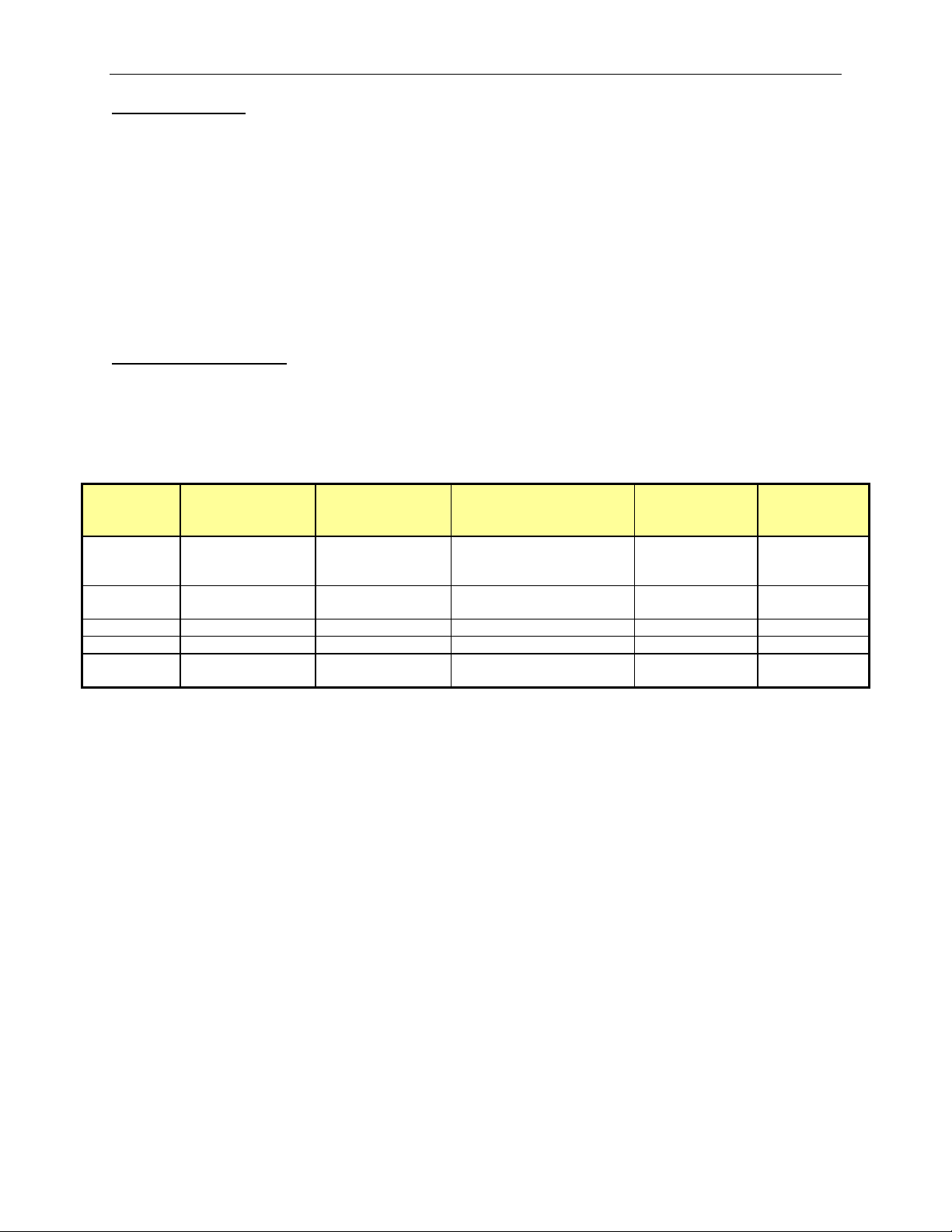

The ADC processes one sample per channel per multiplexer c ycle. Figure 4 shows the timin g of the samples taken

during one multiplexer cycle.

The number of samples processed during one accum ulatio n cycle is controlle d by the I /O RAM r egisters PRE_SAMPS

(0x2001[7:6]) and SUM_CYCLES (0x2001[5:0]). The integration time for each energy output is

PRE_SAMPS * SUM_CYCLES / 2520.6, where 2520.6 is the sample rate [Hz]

For example, PRE_SAMPS = 42 and SUM_CYCLES = 50 will establish 2100 samples per accumulation cycle.

PRE_SAMPS = 100 and SUM_CYCLES = 21 will result in the exact same accumulation cycle of 2100 samples or

833ms. After an accumulation c ycle is completed, the XFER_BUSY interrupt signals to the MPU that accumulated

data are available.

Rev 2 Page: 15 of 107

Page 16

71M6521DE/DH/FE Data Sheet

ms

Hz

Hz

f

N

S

ACC

75.999

62.2520

2520

13

32768

4260==⋅

==

τ

VA

IA

1/32768Hz =

30.518µs

13/327 68Hz = 397µs

per mux cycle

IB

VB

XFER_BUSY

Interrupt to MPU

20ms

833ms

Figure 4: Samples from Multiplexer Cycle

The end of each multiplexer c ycle is signaled to the MPU by the CE_BUSY interru pt. At the end of eac h multiplexer

cycle, status information, suc h as sag data and the digitized input signal , is available to the MPU.

Figure 5: Accumulation Interval

Figure 5 sho ws the accumula tion int erval r esultin g from PRE_SAMPS = 42 and SUM_CYCLES = 50, cons isting of 2100

samples of 397µs each, follo wed by the XFER_BUSY interrupt. The samplin g in this example is applied to a 50Hz

signal.

There is no correlation between the line signal frequency and the choice of PRE_SAMPS or SUM_CYCLES (even

though when SUM_CYCLES = 42 one set of SUM_CYCLES happens to sample a period of 16.6ms). Furthermore,

sampling does not have to start when the line voltage crosses the zero line, and the length of the accumulation

interval need not be an integer multiple of the signal cycles.

It is important to note that the length of the accumulation interval, as determined by N

SUM_CYCLES and PRE_SAMPS, is not an exact multiple of 1000ms. For example, if SUM_CYCLES = 60, and

PRE_SAMPS = 00 (42), the resulting accumulation i nterval is:

, the product of

ACC

This means that accurate time measurements should be based on the RTC, not t he ac cumulation interval.

Page: 16 of 107 Rev 2

Page 17

71M6521DE/DH/FE Data Sheet

Address

0000-7FFF

0000-1FFF

32K

8K

on 1K

boundary

0000-07FF

Static RAM

Volatile

MPU data XRAM,

0

2K

1000-11FF

Static RAM

Volatile

CE data

6

512

Configuration RAM

I/O RAM

80515 MPU Core

The 71M6521DE/DH/FE includes an 8051 5 MPU (8-bit, 8051-compatible) that processes most instruc tions in one

clock cycle. Using a 5 MHz clock results in a processing throughput of 5 MIPS. The 8051 5 architecture eliminates

redundant bus states and implement s parallel executi on of fetch and execution phases. Nor mally a machine cycle i s

aligned with a memory fetch, therefore, most of t he 1-byte instr uctions are perform ed in a single cycl e. This leads t o

an 8x performance (in average) improv ement (in term s of MIPS) over the Int el 8051 d evice r unning at the same cloc k

frequency.

Actual processor clocking speed can be adjusted to the total processing demand of the application (metering

calculations, AMR management, mem ory m anageme nt, L CD driv er managem ent a nd I/O m anagemen t) using t h e I/O

RAM register MPU_DIV[2:0].

Typical measurement and meterin g functions based on the results provided by the internal 32-bit compute engine

(CE) are available for the MPU as part of the Teridian standard library. A standard ANSI “C” 80515-application

programming interface library i s available to help reduce design cycle.

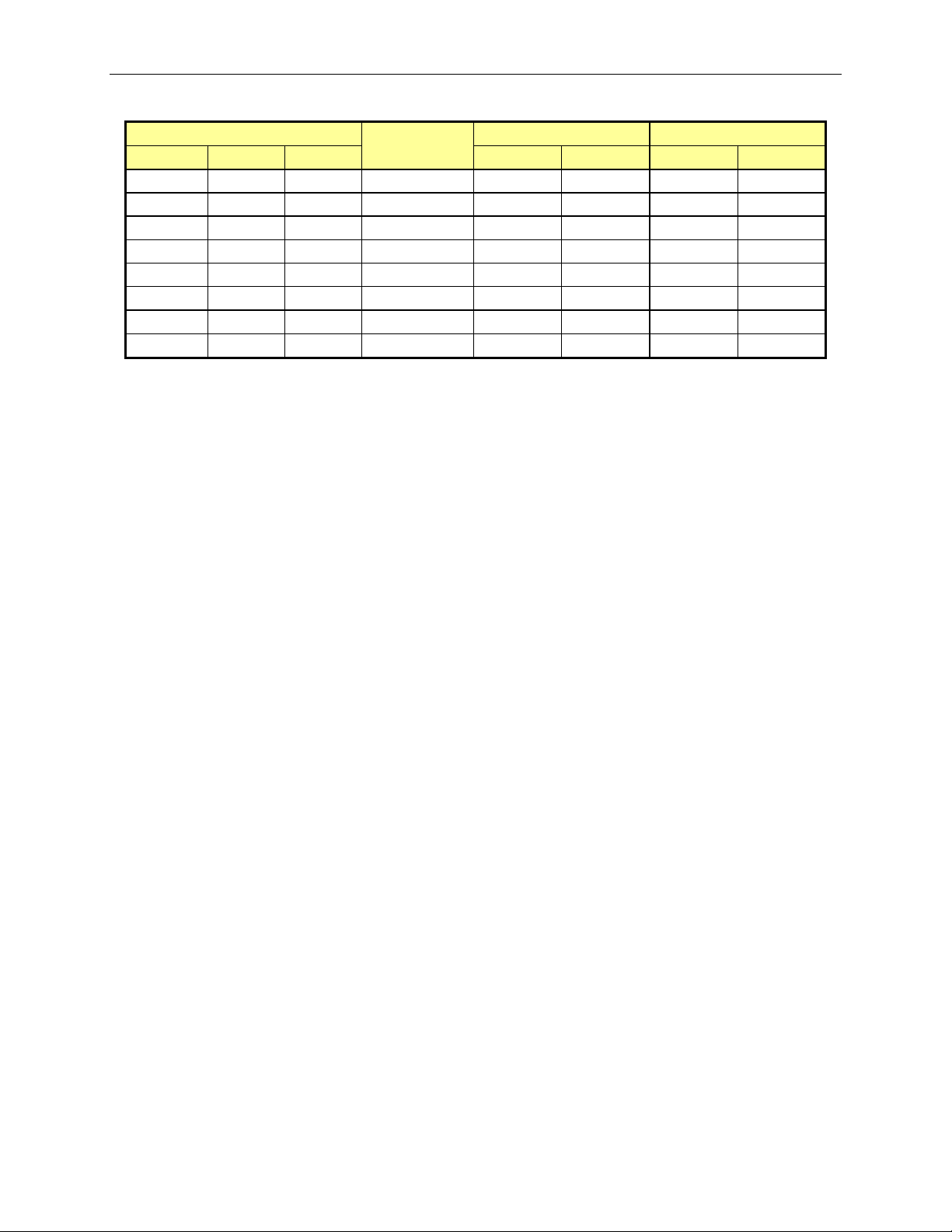

Memory Organization

The 80515 MPU core incorporates the Harvard architecture with separate code and data spaces.

Memory organization in the 80515 is simil ar to that of the industry standard 8051. There are three m emory areas:

Program memory (flash), external data memory (XRAM), physically consisting of XRAM, CE DRAM, and I/O RAM,

and internal data memory (Internal RAM). Table 4 shows the memory map .

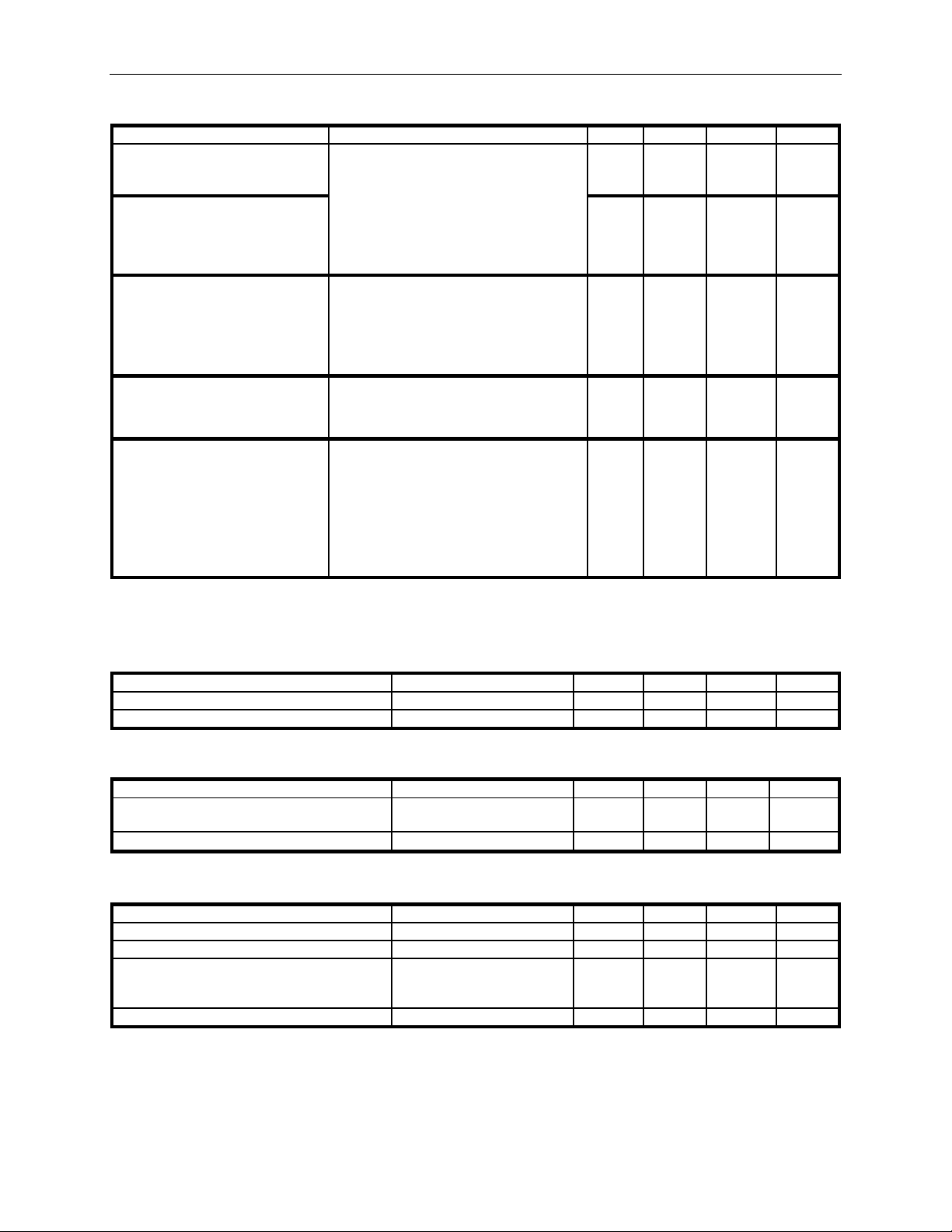

Memory

(hex)

0000-3FFF

2000-20FF St atic RAM Volatile

Internal and External Data Memory: Both internal and external data memory are physically located on the

71M6521DE/DH/FE IC. “External” data memory is only external to the 80515 MPU c or e.

Program Memory: The 80515 can theoretically address up to 64KB of program memory space from 0x0000 to

0xFFFF. Program memory is read when the M PU fetches instructions or performs a MOVC operation.

After reset, the MPU starts program e xecution fr om locatio n 0x0000. T he lo wer part of the program memor y includes

reset and interrupt vectors. T he interrupt vectors are spaced at 8-byte int ervals, starting from 0x0003.

External Data Memory: While the 80515 is capable of addressing up to 64KB of external dat a memory (0x0000 to

0xFFFF), only the memory ranges shown in Table 4: Memory Map

contain physical memory. The 80515 writes into e xternal data memor y when t he MPU executes a MOV X @Ri,A o r

MOVX @DPTR,A instruction. The MPU reads external data memory by executing a MOVX A,@Ri or MOVX

A,@DPTR instruction (SFR USR2 provides the upper 8 bytes for the MOVX A,@R i instruction).

Clock Stretching: MOVX instructions can acc ess fast or slo w external RA M and external peripherals. T he three lo w

order bits of the CKCON register def ine the stretch memor y cycles. Setting all th e CKCON stretch bits to one al lows

access to very slow external RAM or external peripherals.

Table 5 shows how the sig na l s of th e E xter n al M em or y Int e rf ace ch an ge w hen s tr etch values are set from 0 to 7. T he

widths of the signals are counted in MPU clo ck cycles. The post-reset state of the CKCO N regis ter , which is in bold in

the table, performs the MOVX instructions with a stretch value equal to 1.

Technology

Flash Memory Non-volatile

Flash Memory Non-volatile CE program 0 2K

Memory Typ e Typical Usage

MPU Program and non-

volatile data

Table 4: Memory Map

Wait States

(at 5MHz)

0

0 256

Memory Size

(bytes)

16K

Rev 2 Page: 17 of 107

Page 18

71M6521DE/DH/FE Data Sheet

0 0 1 1 2 2 3

1

CKCON register Stretch Value Read signals width Write signal width

CKCON.2 CKCON.1 CKCON.0

0 0 0 0 1 1 2 1

0 1 0 2 3 3 4 2

0 1 1 3 4 4 5 3

1 0 0 4 5 5 6 4

1 0 1 5 6 6 7 5

1 1 0 6 7 7 8 6

1 1 1 7 8 8 9 7

Table 5: Stretch Memory Cycle Widt h

There are two types of instructions, differing in whether they prov ide an eight -bit or sixteen-bit indirect address to th e

external data RAM.

In the first type (MOVX A,@Ri), t he cont ents of R0 or R1, in t he curr ent reg i st er bank , pr ov ide the e ig ht lowe r -ordered

bits of address. The eight hi gh-ord ered bit s of ad dress ar e specif ied with the USR2 SFR. This m ethod al lows the user

paged access (256 pages of 256 bytes each) to all ranges of the external data RAM. In the seco nd type of MOVX

instruction (MOVX A,@DPTR), t he data p ointer generates a sixteen-bit ad d ress . This form is faster and more efficient

when accessing very large data arrays (up to 64 Kbytes), since no additional instruct ions are needed to set up the

eight high ordered bits of address.

It is possible to mix the two M OVX types. This provides the user with four separate d ata pointers, two with direct

access and two with paged access to t he entire 64KB of external memory range.

Dual Data Pointer: The Dual Data Pointer accelerates the block moves of data. The standard DPTR is a 16-bit

register that is used to address externa l memor y or perip herals. In th e 80515 c ore, the s tandar d dat a pointer is cal le d

DPTR, the second data pointer is call ed DPTR1. The data pointer select bit chooses t he active pointer. The data

pointer select bit is located at the LSB of the DPS regis ter (DPS.0). DPTR is selected when DPS.0 = 0 and DPTR1 is

selected when DPS.0 = 1.

The user switches between poi nters by to ggling the LSB of t he DPS regis ter. All data poi nter-relat ed instructions use

the currently selected data pointer f or any activity.

The second data pointer may not be supported by certain compilers.

Internal Data Memory: The Internal dat a memory provides 256 bytes (0x00 to 0 xFF) of data memory. The internal

data memory address is always 1 b yte wide and can be ac cessed by either dir ect or in direct addr essing. T he Speci al

Function Registers occupy the upper 128 bytes. This SFR area is available only by direct ad dressing. Indirect

addressing accesses the upper 128 bytes of Internal RAM.

memaddr memrd memaddr memwr

Page: 18 of 107 Rev 2

Page 19

71M6521DE/DH/FE Data Sheet

Address

Direct addressing

Indirect addressing

Special Function Registers

F8

INTBITS

FF

F0

B

F7

E8

WDI

EF

E0

A

E7

D8

WDCON

DF

D0

PSW

D7

C0

IRCON

C7

IEN1

B0

FLSHCTL

PGADR

B7

A8

IEN0

IP0

S0RELL

AF

A0

P2

DIR2

DIR0

A7

IEN2

90

P1

DIR1

DPS

ERASE

97

88

TCON

TMOD

TL0

TL1

TH0

TH1

CKCON

8F

80

P0

SP

DPL

DPH

DPL1

DPH1

WDTREL

PCON

87

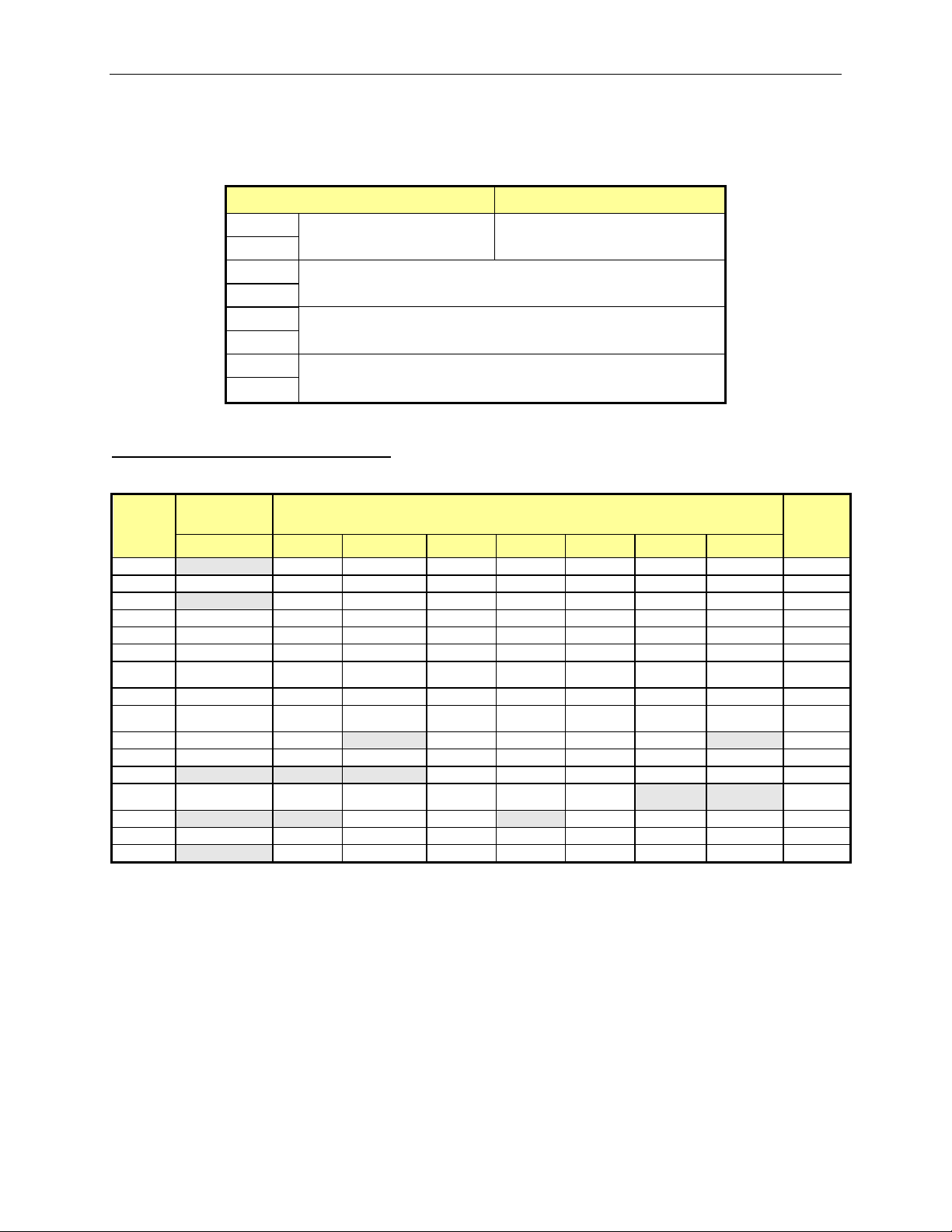

Internal Data Memory: The lower 128 bytes contain working re gisters and bit-addressable memory. The lower 3 2

bytes form four banks of eight registers ( R0-R7). Two bits on the program memory status word (PSW) select which

bank is in use. The next 16 bytes form a block of bit-addressable memor y space at bit addressees 0x 00-0x7F. All of

the bytes in the lower 128 b ytes are acces sible t hrough dir ect or indir ect addres sing. Table 6 s hows the int ernal d ata

memory map.

0xFF

0x80

0x7F

0x30

0x2F

0x20

0x1F

0x00

(SFRs)

Byte-addressabl e area

Bit-addressable area

Register banks R0…R7

Table 6: Internal Data Memory Map

Special Function Registers (SFRs)

A map of the Special Function Registers is shown in Table 7.

Hex\Bin

C8

Bit-address-

able

X000 X001 X010 X011 X100 X101 X110 X111

T2CON

Byte-addressable

RAM

Bin/Hex

CF

B8

98

Only a few addresses are oc cupied, the others are not im plemented. SFRs specific to t he 652X are shown in bold

print. Any read access to uni mplemented addresses will return und efined data, while any write acc ess will have no

effect. The registers at 0x80, 0x88, 0x90, etc., are bit-addressable, all others are byte-addressable.

S0CON S0BUF

IP1 S0RELH S1RELH USR2

S1CON S1BUF S1RELL

Table 7: Special Function Registers L ocations

EEDATA EECTRL

BF

9F

Rev 2 Page: 19 of 107

Page 20

71M6521DE/DH/FE Data Sheet

P0

0x80

0xFF

Port 0

SP

0x81

0x07

Stack Pointer

DPL

0x82

0x00

Data Pointer Low 0

DPH

0x83

0x00

Data Pointer High 0

DPL1

0x84

0x00

Data Pointer Low 1

DPH1

0x85

0x00

Data Pointer High 1

WDTREL

0x86

0x00

Watchdog Timer Reload register

PCON

0x87

0x00

UART Speed Control

TCON

0x88

0x00

Timer/Counter Control

TMOD

0x89

0x00

Timer Mode Control

TL0

0x8A

0x00

Timer 0, low byte

TL1

0x8B

0x00

Timer 1, high byte

TH0

0x8C

0x00

Timer 0, low byte

TH1

0x8D

0x00

Timer 1, high byte

CKCON

0x8E

0x01

Clock Control (Stretch=1)

P1

0x90

0xFF

Port 1

DPS

0x92

0x00

Data Pointer select Register

S0CON

0x98

0x00

Serial Port 0, Control Register

S0BUF

0x99

0x00

Serial Port 0, Data Buffer

IEN2

0x9A

0x00

Interrupt Enable Register 2

S1CON

S1BUF

0x9C

0x00

Serial Port 1, Data Buffer

S1RELL

0x9D

0x00

Serial Port 1, Reload Register, low byte

P2

0xA0

0x00

Port 2

IEN0

0xA8

0x00

Interrupt Enable Register 0

IP0

0xA9

0x00

Interrupt Priority Register 0

S0RELL

0xAA

0xD9

Serial Port 0, Reload Register, low byte

IEN1

0xB8

0x00

Interrupt Enable Register 1

IP1

0xB9

0x00

Interrupt Priority Register 1

S0RELH

0xBA

0x03

Serial Port 0, Reload Register, high b yte

S1RELH

0xBB

0x03

Serial Port 1, Reload Register, high b yte

USR2

0xBF

0x00

User 2 Port, high address byte for MOV X@Ri

IRCON

0xC0

0x00

Interrupt Request Control Regis ter

T2CON

0xC8

0x00

Polarity for INT2 and INT3

PSW

0xD0

0x00

Program Status Word

WDCON

0xD8

0x00

Baud Rate Control Register (only W DC ON.7 bit used)

A

0xE0

0x00

Accumulator

B

0xF0

0x00

B Register

Special Function Registers (Generic 80515 SFRs)

Table 8 shows the location of the SFRs and the value they assume at reset or power-up.

Name Location Reset value Description

0x9B 0x00 Serial Por t 1, Control Register

Table 8: Special Function Registers Reset Values

Page: 20 of 107 Rev 2

Page 21

71M6521DE/DH/FE Data Sheet

Bit

Symbol

Function

RS1/RS0

Bank selected

Location

Accumulator (ACC, A): ACC is the accumulator register. Most instructions use the accumulator to hold the

operand. The mnemonics for accumulator-specific instructions refer to accumulator as “A”, no t ACC.

B Register: The B register is used during multiply and divide instructions. It can also be used as a scratch-pad

register to hold temporary data.

Program Status Word (PSW):

MSB LSB

CV AC F0 RS1 RS OV - P

Table 9: PSW Register Flags

PSW.7 CV

PSW.6 AC

PSW.5 F0

Carry flag

Auxiliary Carry flag for BCD operations

General purpose Flag 0 available for user.

F0 is not to be confused with the F0 flag in the CE STATUS register.

PSW.4 RS1 Register bank select control bits. The c ontents of RS1 and RS0 select the working

register bank:

PSW.3 RS0

00 Bank 0 (0x00 – 0x07)

01 Bank 1 (0x08 – 0x0F)

10 Bank 2 (0x10 – 0x17)

11 Bank 3 (0x18 – 0x1F)

PSW.2 OV

PSW.1 PSW.0 P

Overflow flag

User defined flag

Parity flag, affected by hardware to indicate odd / even number of “one” bits in the

Accumulator, i.e. even parity.

Table 10: PSW Bit Functions

Stack Pointer (SP): The stack pointer is a 1-b yte register initialized to 0x07 af ter reset. This register is incremented

before PUSH and CALL instructions, causing the stack to begin at location 0x 08.