Page 1

EDA Simulator Link

User’s Guide

™3

Page 2

How to Contact The MathWorks

www.mathworks.

comp.soft-sys.matlab Newsgroup

www.mathworks.com/contact_TS.html T echnical Support

suggest@mathworks.com Product enhancement suggestions

bugs@mathwo

doc@mathworks.com Documentation error reports

service@mathworks.com Order status, license renewals, passcodes

info@mathwo

com

rks.com

rks.com

Web

Bug reports

Sales, prici

ng, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc.

3 Apple Hill Drive

Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

EDA S imulator Link™ User’s Guide

© COPYRIGHT 2003–2010 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used

or copied only under the terms of the license agreement. No part of this manual may be photocopied or

reproduced in any form without prior written consent from The MathW orks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation

by, for, or through the federal government of the United States. By accept ing delivery of the Program

or Documentation, the government hereby agrees that this software or documentation qualifies as

commercial computer software or commercial computer software documentation as such terms are used

or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and

conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern

theuse,modification,reproduction,release,performance,display,anddisclosureoftheProgramand

Documentation by the federal government (or other entity acquiring for or through the federal government)

and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the

government’s needs or is inconsistent in any respect with federal procurement law, the government agrees

to return the Program and Docu mentation, unused, to The MathWorks, Inc.

Trademarks

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See

www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand

names may be trademarks or registered trademarks of their respective holders.

Patents

The MathWorks products are protected by one or more U.S. patents. Please see

www.mathworks.com/patents for more information.

Page 3

Revision History

August 2003 Online only New for Version 1 (Release 13SP1)

February 2004 Online only Updated for Version 1.1 (Release 13SP1)

June 2004 Online only Updated for Version 1.1.1 (Release 14)

October 2004 Online only Updated for Version 1.2 (Release 14SP1)

December 2004 Online only Updated for Version 1.3 (Release 14SP1+)

March 2005 Online only Updated for Version 1.3.1 (Release 14SP2)

September 2005 Online only Updated for Version 1.4 (Release 14SP3)

March 2006 Online only Updated for Version 2.0 (Release 2006a)

September 2006 Online only Updated for Version 2.1 (Release 2006b)

March 2007 Online only Updated for Version 2.2 (Release 2007a)

September 2007 Online only Updated for Version 2.3 (Release 2007b)

March 2008 Online only Updated for Version 2.4 (Release 2008a)

October 2008 Online only Updated for Version 2.5 (Release 2008b)

March 2009 Online only Updated for Version 2.6 (Release 2009a)

September 2009 Online only Updated for Version 3.0 (Release 2009b)

March 2010 Online only Updated for Version 3.1 (Release 2010a)

Page 4

Page 5

Cosimulating HDL with MATLAB and

Simulink

Simulating an HDL C omponent in a MATLAB

Test Bench Environment

1

Contents

Using MATLA

Overview to

Workflow f

MATLAB Tes

Code HDL M

Overview

MATLAB

Choosin

Test Ben

Specify

with Tes

ying Port Data Types in HDL Modules for Use with

Specif

Test Be

Compil

Test B

Sampl

Code

Func

Proc

Syn

Sam

e VHDL Entity Definition

an EDA Simulator Link MATLAB Test Bench

tion

ess for Coding MATLAB EDA Simulator Link

Func

tax of a Test Bench Function

ple MATLAB Test Bench Function

BasaTestBench

MATLAB Test Bench Functions

or Simulating an HDL Component with a

t Bench Function

odules for Verification Using MATLAB

to Coding HDL Modules f or Verification with

...................................... 1-7

g an HDL Module Name for Use with a MATLAB

ch

.....................................

ing Port Direction Modes in HDL Module for Use

tBench

nch

ingandElaboratingtheHDLDesignforUsewith

ench

................................

.....................................

.....................................

........................................

tions

......................................

.....................

....................

.....................

.....................

...........

..

................

1-2

1-2

1-4

1-7

1-8

1-8

1-8

1-10

1-12

1-14

1-14

1-1

1-1

5

5

ace Test Bench Function on MATLAB Search Path

Pl

e MATLAB which Function to Find Test Bench

Us

d Test Bench Function to MATLAB Search Path

Ad

..

.......

......

111-

21

21

21

v

Page 6

Start Connection to HDL Simulator for Test Bench

Session

Start MATLAB Server for Test Bench Session

Example of Starting MATLAB Server for Test Bench

Session

Launch HDL Simulator for Use with MATLAB Test

Bench

Launching the HDL Simulator for Test Bench Session

Loading an HDL Design for Verification

Invoke matlabtb to Bind MATLAB Test Bench Function

Calls

Invoking the MATLAB Test Bench Command matlabtb

Binding the HDL Module Component to the MATLAB Test

Bench Function

......................................... 1-22

.......... 1-22

........................................ 1-23

.......................................... 1-24

... 1-24

............... 1-24

........................................... 1-26

.. 1-26

................................. 1-29

Schedule Options for a Test Bench Session

About Scheduling Options for Test Bench Sessions

Scheduling Test Bench Session Using matlabtb

Arguments

Scheduling Test Bench Functions Using the tnext

Parameter

Run MATLAB Test B ench Simulation

Process for Running MATLAB Test Bench Cosimulation

Checking the MATLAB Server’s Link Status for Test Bench

Cosimulation

Running a Test Bench Cosimulation

Applying Stimuli to Test B ench Session with the HDL

Simulator force Command

Restarting a Test Bench Simulation

Stop T est Bench Simulation

Tutorial – Running a Sample ModelSim and MATLAB

Test Bench Session

Tutorial Overv iew

Setting Up Tutorial Files

Starting the MATLAB Server

Setting Up the ModelSim Simulator

..................................... 1-31

..................................... 1-32

................................... 1-35

.................. 1-36

........................ 1-41

.................. 1-43

........................ 1-44

.............................. 1-45

................................. 1-45

........................... 1-46

....................... 1-46

.................. 1-47

........... 1-31

...... 1-31

................ 1-35

.. 1-35

vi Contents

Page 7

Developing the VHDL Code ......................... 1-49

Compiling the VHDL File

Developing the MATLAB Function

Loading the Simulation

Running the Simulation

Shutting Down the Simulation

........................... 1-51

................... 1-52

............................ 1-54

............................ 1-56

....................... 1-61

Replacing an HDL Component with a MATLAB

Component Function

2

Overview to Using a MATLAB Function as a

Component

How MATLAB and the HDL Simulator Communicate

During a Component Session

Workflow for Creating a MATLAB Component Function for

Use with the HDL Simulator

..................................... 2-2

...................... 2-2

...................... 2-4

Code HDL Modules for Visualization Using MATLAB

Overview to Coding HDL Modules for Visualization with

MATLAB

Choosing an HDL Module Name for Use with a MATLAB

Component Function

Specifying Port Direction Modes in HDL Module for Use

with Component Functions

Specifying Port Data Types in HDL Modules for Use with

Component Functions

Compiling and Elaborating t he HDL Desig n for Use with

Component Functions

Create an EDA Simulator Link MATLAB Component

Function

Overview to Coding an EDA Simulator Link Component

Function

Syntax of a Component Function

Place Component Function on MATLAB Search

Path

............................................ 2-15

...................................... 2-7

............................ 2-8

....................... 2-8

............................ 2-8

............................ 2-10

........................................ 2-13

....................................... 2-13

..................... 2-14

.. 2-7

vii

Page 8

Use MATLAB which Function to Find Component

Function

Add Component Function to MATLAB Search Path

Start Connection to HDL Simulator for Component

Function Session

Start MATLAB Server for Component Function Session

Example of Starting MATLAB Server for Component

Function Session

Launch HDL Simulator for Use with MATLAB

Component Session

Launching the HDL Simulator for Component Session

Loading an HDL Design for Visualization

Invoke matlabcp to Bind MATLAB Component Function

Calls

Invoking the MATLAB Component Function Command

matlabcp

Binding the HDL Module Component to the MATLAB

Component Function

....................................... 2-15

..... 2-15

................................ 2-16

.. 2-16

................................ 2-17

.............................. 2-18

... 2-18

.............. 2-18

........................................... 2-20

...................................... 2-20

............................ 2-23

viii Contents

Schedule Options for a Component Session

About Scheduling Options for Component Sessions

Scheduling Component Session Using matlabcp

Arguments

Scheduling Component Functions Using the tnext

Parameter

Run M ATLAB Component Function Simulation

Process for Running MATLAB Component Function

Cosimulation

Checking the MATLAB Server’s Link Status for Component

Cosimulation

Running a Component Function Cosimulation

Applying Stimuli to Component Function with the HDL

Simulator force Command

Restarting a Component Simulation

Stop Component Simulatio n

..................................... 2-25

..................................... 2-26

................................... 2-29

................................... 2-29

........................ 2-35

.................. 2-37

........................ 2-38

.......... 2-25

...... 2-25

...... 2-29

.......... 2-30

Page 9

Simulating an HDL Component in a Simulink

Test Bench Environment

3

Overview to Using Simulink as a Test Bench ......... 3-2

Understanding How the HDL Simulator and Simulink

Software Communicate Using EDA Simulator Link For

Test Bench Simulation

HDL Cosimulation B lo ck Features for Test Bench

Simulation

Workflow for Simulating an HDL Component in a Simulink

Test Bench Environment

Create a Simulink Model for Test Bench Cosimulation

with the HDL Simulator

Creating Your Simulink Model

Running Test Bench Hardware Model in Simulink

Adding a Value Change Dump (VCD) File (Optional)

Code an HDL Component for Use with Simulink Test

Bench Applications

Overview to Coding HDL Components for Simulink Test

Bench Sessions

Specifying Port Direction Modes in the HDL Component for

Test Bench Use

Specifying Port Data Types in the HDL Component for Test

Bench Use

Compiling and Elaborating the HDL Desi gn for Test Bench

Use

........................................... 3-13

..................................... 3-5

................................. 3-10

................................. 3-10

..................................... 3-11

........................... 3-2

......................... 3-6

.......................... 3-9

...................... 3-9

...... 3-9

.............................. 3-10

.... 3-9

Launch HDL Simulator for Test Bench Cosimulation

with Simulink

Starting the HDL Simulator from MATLAB

LoadinganInstanceofanHDLModuleforTestBench

Cosimulation

Add the HDL Cosimulation Block to the Simulink Test

Bench Model

Insert HDL Cosimulation Block

Connect Block Ports

................................... 3-14

............ 3-14

................................... 3-14

.................................... 3-16

...................... 3-16

............................... 3-17

ix

Page 10

Define the HDL Cosimulation Block Interface for Test

Bench Cosimulation

Accessing the HDL Cosimulation Block Interface

Mapping HDL Signals to Block Ports

Specifying the Signal Data Types

Configuring the Simulink and HDL Simulator Timing

Relationship

Configuring the Communication Link in the HDL

Cosimulation Block

Specifying Pre- and Post-Simulation Tcl Commands with

HDL Cosimulation Block Parameters Dialog Box

Programmatically Controlling the Block Parameters

................................... 3-35

............................. 3-18

....... 3-18

................. 3-19

.................... 3-35

.............................. 3-36

..... 3-39

..... 3-41

RunaTestBenchCosimulationSession

Setting Simulink Software Configuration Parameters

Determining an Available Socket Port Number

Checking the Connection Status

Running and Testing a Test Bench Cosimulation Model

Avoiding Race Conditions in HDL Simulation with Test

Bench Cosimulation and the EDA Simulator Link HDL

Cosimulation Block

Tutorial — Verifying an HDL Model Using Simulink,

the HDL Simulator, and the EDA Sim ulator Link

Software

Tutorial Overv iew

Developing the VHDL Code

Compiling the VHDL File

Creating the Simulink Model

Setting Up ModelSim for Use with Simulink

Loading Instances of the VHDL Entity for Cosimulation

with Simulink

Running the Simulation

Shutting Down the Simulation

........................................ 3-52

.............................. 3-50

................................. 3-52

........................... 3-54

.................................. 3-65

............................ 3-67

..................... 3-46

......................... 3-53

........................ 3-55

....................... 3-70

............. 3-44

.... 3-44

......... 3-46

........... 3-65

.. 3-46

x Contents

Page 11

Replacing an HDL Component with a Simulink

Algorithm

4

Overview to Component Simulation with Simulink ... 4-2

Understanding How the HDL Simulator and Simulink

Software Communicate Using EDA Simulator Link For

Component Simulation

HDL Cosimulation Block Features for Component

Simulation

Workflow for Using Simulink as HDL Component

Code an HDL Component for U se with Simulink

Applications

Overview to Coding H D L Modules for Simulink Component

Simulation

Specifying Port Direction Modes in the HDL Module for

Component Simulation

Specifying Port Data Types in the HDL Module for

Component Simulation

Compiling and Elaborating the HDL Des ign for Component

Simulation

..................................... 4-4

.................................... 4-8

..................................... 4-8

..................................... 4-10

........................... 4-2

....... 4-6

........................... 4-8

........................... 4-9

Create Simulink Model for Component Cosimulation

with the HDL Simulator

Creating the S imulink Model for Component

Cosimulation

Running and Testing a Component Hardware Model in

Simulink

Adding a Value Change Dump (VCD) File to Component

Model (Optional)

Launch HDL Simulator for Component Cosimulation

with Simulink

Starting the HDL Simulator from MATLAB

Loading an Instance of an HDL Module for Component

Cosimulation

Add the HDL Cosimulation Block to the Simulink

Component Model

Insert HDL Cosimulation Block

................................... 4-11

...................................... 4-11

................................ 4-11

................................... 4-13

................................... 4-13

.......................... 4-11

............ 4-13

............................... 4-15

...................... 4-15

xi

Page 12

Connect Block Ports ............................... 4-16

Define the HDL Cosimulation Block Interface for

Component Simulation

Accessing the HDL Cosimulation Block Interface

Mapping HDL Signals to Block Ports

Specifying the Signal Data Types

Configuring the Simulink and HDL Simulator Timing

Relationship

Configuring the Communication Link in the HDL

Cosimulation Block

Specifying Pre- and Post-Simulation Tcl Commands with

HDL Cosimulation Block Parameters Dialog Box

Programmatically Controlling the Block Parameters

................................... 4-33

.......................... 4-17

....... 4-17

................. 4-18

.................... 4-33

.............................. 4-34

..... 4-37

..... 4-39

Run a Component C osimulation Session

Setting Simulink Software Configuration Parameters

Determining an Available Socket Port Number

Checking the Connection Status

Running and Testing a Component Cosimulation Model

Avoiding Race Conditions in HDL Simulation with

Component Cosimulation and the EDA Simulator Link

HDL Cosimulation Block

..................... 4-44

......................... 4-48

............. 4-42

......... 4-44

Recording Simulink Signal State Transitions

for Post-Processing

5

Adding a Value Change Dump (VCD) File ............ 5-2

Introduction to the EDA Simulator Link To VCD File

Block

Using the To VCD File Block

To VCD File Block Tutorial

Tutorial: Overview

Tutorial: Instructions

......................................... 5-2

........................ 5-3

......................... 5-6

................................ 5-6

.............................. 5-6

.... 4-42

.. 4-44

xii Contents

Page 13

Additional Deployment Options

6

Adding Questa ADMS Support ...................... 6-2

Adding Libraries for Questa ADMS Support

Linking M ATLAB or Simulink Software to ModelSim in

Questa ADMS

Diagnosing and Customizing Your Setup for Use

with the HDL Sim ulator and EDA Simulator Link

Software

Overview to the EDA SimulatorLinkConfigurationand

Diagnostic Script

Using the Configuration and Diagnostic Script for

UNIX/Linux

Using the Configuration and Diagnostic Script with

Windows

........................................ 6-5

.................................. 6-2

................................ 6-5

.................................... 6-6

...................................... 6-13

............ 6-2

Performing Cross-Network Cosimulation

Why P erform Cross-Network Cosimulation?

Preparing for Cross-Network Cosimulation (MATLAB or

Simulink)

Performing Cross-Network Cosimulation with the HDL

Simulator and MATLAB

Performing Cross-Network Cosimulation with the HDL

Simulator and Simulink

Establishing EDA Simulator Link Machine

Configuration R equirements

Valid Configurations For Using the EDA Simulator Link

Software with MATLAB Applications

Valid Configurations For Using the EDA Simulator Link

Software with Simulink Software

Specifying TCP/IP Socket Comm unication

Communication Modes and Socket Ports

Choosing TCP/IP Socket Ports

Specifying TCP/IP Values

TCP/IP Services

Improving Simulation Speed

...................................... 6-15

......................... 6-18

.......................... 6-22

..................... 6-26

.................. 6-27

....................... 6-30

........................... 6-32

................................... 6-33

....................... 6-34

............ 6-15

............ 6-15

............... 6-26

........... 6-29

.............. 6-29

xiii

Page 14

Obtaining Baseline Performance Numbers ............. 6-34

Analyzing Simulation Performance

Cosimulating Frame-Based Signals with Simulink

................... 6-34

...... 6-36

Advanced Operational Topics

7

Avoiding Race Conditions in HDL Simulators ........ 7-2

Overview to Avoiding R ace Conditions

Potential Race Conditions in Simulin k Link Sessions

Potential Race Conditions in MATLAB Link Sessions

Further Reading

.................................. 7-4

................ 7-2

.... 7-2

.... 7-3

Performing Data Type Conversions

Converting HDL Data to Send to MATLAB

Array Indexing Differences Between MATLAB and

HDL

.......................................... 7-7

Converting Data for Manipulation

Converting Data for Return to the HDL Simulator

Understanding the Representation of Simulation

Time

Overview to the Representation of Simulation Time

Defining the Simulink and HDL Simulator Timing

Setting the Timing Mode with EDA Simulator Link

Relative Timing Mode

Absolute Timing Mode

Timing Mode Usage Considerations

Setting HDL Cosimulation Block Port Sample Times

Driving Clocks, Resets, and Enables

Options for Driving Clocks, Resets, and Enables

Adding Signals Using Simulink Blocks

Creating O ptional Clocks with the Clocks Pane of the HDL

Driving Signals by Adding Force commands

........................................... 7-14

Relationship

................................... 7-15

.............................. 7-17

............................. 7-23

Cosimulation Block

.............................. 7-30

................. 7-5

............ 7-5

.................... 7-9

...... 7-10

.................. 7-25

................. 7-29

........ 7-29

................ 7-29

............ 7-33

..... 7-14

..... 7-16

.... 7-27

xiv Contents

Eliminating Block Simulation Latency

.............. 7-37

Page 15

Applying Direct Feedthrough to Eliminate Block Simulation

Latency

Defining EDA Simulator Link MATL AB Functions and

Function Parameters

MATLAB Function Syntax and Function Argument

Definitions

Oscfilter Function Example

Gaining Access to and Applying Port Information

....................................... 7-37

............................ 7-42

..................................... 7-42

......................... 7-44

....... 7-45

Exporting Simulink Algorithms to

SystemC TLM 2.0 Components

Overview to TLM Component Generation

8

How T LM Component G eneration Works ............ 8-2

TLM Component Generation

How EDA Simulator Link Software G ene rates a TLM

Component

.................................... 8-3

........................ 8-2

Setting TLM Component Generation Configuration

Parameters

User Workflow for TLM Component Generation

Basic Workflow Steps

Select System Target File to Activate TLM Component

Generation Options

Select Features for Generated TLM Component

Select Option s for Associated Test Bench

Specify Attributes for Generated makefile

Generate TLM Component

Verify the Generated TLM Component

..................................... 8-7

...... 8-8

.............................. 8-8

.............................. 8-10

......... 8-11

.............. 8-13

............. 8-15

.......................... 8-16

................ 8-17

xv

Page 16

Selecting Features for the Generated TLM

Component

9

Overview of Component Features ................... 9-2

Memory Mapping

No Memory Map

Automatically Generated Memory Map w ith Single

Address

Automatically Generated Memory Map with Individual

Addresses

Command and Status Register

Interrupt

Test and Set Register

The Quantum

Buffering

TLM Component Timing Values

TLM Component Naming and Packaging

......................................... 9-14

......................................... 9-17

.................................. 9-4

.................................. 9-4

....................................... 9-5

...................................... 9-5

....................... 9-6

.............................. 9-15

..................................... 9-16

..................... 9-18

............ 9-19

xvi Contents

10

Creating and Applying a Test Bench for the

Generated TLM Component

Testing TLM Components .......................... 10-2

TLM Component Test Bench Overview

TLM Component Compilation

Automatic Verification of the Generated Component

Report Generation

Working with Configurations

................................. 10-3

....................... 10-2

........................ 10-3

................ 10-2

..... 10-3

Page 17

Considerations When Creating a TLM Component Test

Bench

......................................... 10-4

11

TLM Component Test Bench Generation Options

Verbose Me ssaging

Run-Time Timing Mode

Input and Output Buffer Triggering Modes

Verify TLM Component

................................ 10-6

............................ 10-6

............ 10-6

............................ 10-7

Using TLM Components in a SystemC

Environment

TLM Compon

About the T

SystemC In

SystemC Li

TLM Inclu

Compile w

Using th

How to Id

Create S

Create

and Tes

de Path

ith Debug Flags

e Generated TLM Component Files

entify Generated Files

tatic Library with the TLM Component

Standalone Executable with the TLM Component

tBench

ent Compiler Options

LM Component Compiler Options

clude Path

brary Path

.............................

.............................

.................................

..........................

.................................

..................

..........

..........

.....................

........

..... 10-6

11-2

11-2

11-2

11-2

11-3

11-3

11-4

11-4

11-5

11-6

12

Confi

TLM Generation Pane .............................. 12-2

TLM Component Generation Overview

Memory Map Type

Auto-Generated Memory Map Type

Include a command and status register in the memory

guration Parameters for TLM Generator

................ 12-4

................................ 12-5

................... 12-6

map

.......................................... 12-7

Targ

et

xvii

Page 18

Include a test and set register in the m emory map ...... 12-8

Create an interrupt request port on the generated TLM

component

Enable payload buffering

Payload input buffer depth

Payload output buffer depth

Enable quantum for loosely-timed simulation

Quantum for loosely-timed components (ns)

Algorithm step function (ns)

Single write transfer or the first write transfer in a burst

transaction (ns)

Subsequent write transfers in a burst transaction (ns)

Single read transaction or the first read transfer in a burst

transaction (ns)

Subsequent read transfers in a burst transaction (in ns)

User-tag for TLM component names

..................................... 12-9

........................... 12-10

.......................... 12-11

......................... 12-12

.......... 12-13

............ 12-14

......................... 12-15

................................. 12-16

... 12-17

................................. 12-18

.. 12-19

.................. 12-20

TLM Testbench Pane

TLM Component Testbench Pane Overview

Generate testbench

Generate ve rbo se messages during testbench execution

Run-time tim ing mode

Input buffer triggering mode

Output buffer triggering mode

TLM Compilation Pane

TLM Component Compilation Overview

SystemC include path

SystemC library path

TLM include path

Compile with debug flags

.............................. 12-21

............ 12-22

................................ 12-23

............................. 12-25

........................ 12-26

....................... 12-27

............................. 12-28

............... 12-29

.............................. 12-30

.............................. 12-31

................................. 12-32

........................... 12-34

.. 12-24

xviii Contents

Page 19

Creating and Managing Xilinx Projects for

FPGA Development

FPGA Project Generation Overview

13

EDA Simulator Link FPGA Project Generation

Overview

Introduction to EDA Simulator Link FPG A Project

Generation

Generated Project Files

Clock Modules

User Constraint Files (UCF) for Multicycle Paths

FPGA Hardw are-in-the-Loop (HIL)

For More Information

....................................... 13-2

..................................... 13-2

............................ 13-3

.................................... 13-4

....... 13-5

................... 13-7

.............................. 13-8

FPGA Project Development

14

Create New FPGA Project .......................... 14-2

Workflow for Creating a New FPGA Project

Create New or Open Existing Model

SetUpMATLABtoUseXilinxISE(NewProject)

Set Up FPGA Project Configuration Parameters for New

Project

Set Project Generation Settings with E DA Link

Configuration Parameters

Generate FPGA Project

Add Generated Files to Existing FPGA Project

Workflow for Adding Generated Files with Existing FPGA

Project

Create New or O pe n Existing Model for Adding to

Project

SetUpMATLABtoUseXilinxISE(AddtoProject)

Set Up FPGA W orkflow Configuration Parameters (Add to

Project)

Open E DA Link FPG A Workflow Pane (Add to Project)

........................................ 14-3

........................ 14-3

............................ 14-9

........................................ 14-11

........................................ 14-13

........................................ 14-13

.................. 14-3

............ 14-2

....... 14-3

....... 14-11

..... 14-13

.. 14-14

xix

Page 20

Specify FPGA Project Settings with EDA Link Configuration

Parameters

Add Generated Files to Project with Associate Project

Update Generated Files for Associated FPGA

Project

Workflow for Updating Generated Files

Open E DA Link FPGA Workflow Pane

Specify FPGA Project Settings with EDA Link Configuration

Parameters

Update FPGA Project

.................................... 14-15

......................................... 14-17

............... 14-17

................ 14-19

.................................... 14-20

.............................. 14-20

.... 14-15

15

Remove Project Association

Workflow for Removing Project Association

When to Remove Project Association

Generate Tcl Script for Project Generation

When to Use Gene rated Tcl Scripts

Workflow for Tcl Script Generation

........................ 14-22

............ 14-22

.................. 14-22

.......... 14-23

................... 14-23

................... 14-23

FPGA Hardware-in-the-Loop (HIL)

Introduction to FPGA Hardware-in-the-Loop (HIL) ... 15-2

Overview of FPGA Hardware-in-the-Loop (HIL)

Functionality

Simulink Emulation

Communication Channel

Downstream Workflow Automation

Design Considerations for FPGA HIL Project

Generation

................................... 15-2

............................... 15-3

........................... 15-4

................... 15-4

..................................... 15-4

xx Contents

Workflow for Generating FPGA HIL

Create Model for FPGA HIL

Set Up FPGA Project Configuration Parameters GUI

Specify Simulink

Parameters

Specify FPGA HIL Configuration Parameters

Generate FPGA Project

®

HDL Coder Configuration

.................................... 15-6

......................... 15-5

............................ 15-7

................. 15-5

.... 15-5

.......... 15-6

Page 21

Load Bitstream ................................... 15-8

Run Simulation

................................... 15-8

Index

xxi

Page 22

xxii Contents

Page 23

Cosimulating HDL with M ATLAB and Simulink

• Chapter 1, “Simulating an HDL Component in a MATLAB Test

Bench Environment”

• Chapter 2, “Replacing an HDL Component with a MATLAB

Component Function”

• Chapter 3, “Simulating an HDL Component in a Simulink Test

Bench Environment”

• Chapter 4, “Replacing an HDL Component with a Simulink

Algorithm”

• Chapter 5, “Recording Simulink Signal State Transitions for

Post-Processing”

• Chapter 6, “Additional Deployment Options”

• Chapter 7, “Advanced Operational Topics”

Page 24

Page 25

Simulating an HDL Component in a MATLAB Test Bench Environment

• “Using MATLAB as a Test Bench” on page 1-2

• “Code HDL Modules for Verifica tion Using MATLAB ” on page 1-7

• “Code an EDA Simulator Link MATLAB Test Bench Function” on page 1-14

1

• “Place Test Bench Function on MATLAB Search Path” on page 1-21

• “Start Connection to HDL Simulator for Test Bench Session” on page 1-22

• “LaunchHDLSimulatorforUsewithMATLABTestBench”onpage1-24

• “Invoke matlabtb to Bind MATLAB Test Bench Function Calls” on page

1-26

• “Schedule Options for a Test Bench Session” on page 1-31

• “Run MATLAB Test Bench Simulation” on page 1-35

• “Stop Test Bench Simulation” on page 1-44

• “Tutorial – Running a Sample ModelSim and MATLAB Test Bench

Session” on page 1-45

Page 26

1 Simulating an HDL Component in a MATLAB

®

Test Bench Environment

UsingMATLABasaTestBench

In this section...

“Overview to MATLAB Test Bench Functions” on page 1-2

“Workflow for Simulating an HDL Component with a MATLAB Test Bench

Function” on page 1-4

Overview to MATLAB Test Bench Functions

The EDA Simulator Link™ softw are provides a means for verifying HDL

modules within the MATLAB

model and a MATLAB function that can share data with the HDL model. This

chapter discusses the program ming, interfacing, and scheduling conventions

for MATLAB test bench functions that communicate with the HDL simulator.

MATLAB test bench functions let you verify the performance of the HDL

model, or of components within the model. A test bench function drives

values o nto signals connected to input ports of an HD L design unde r test and

receives signal values from the output ports of the module.

®

environment. YoudosobycodinganHDL

1-2

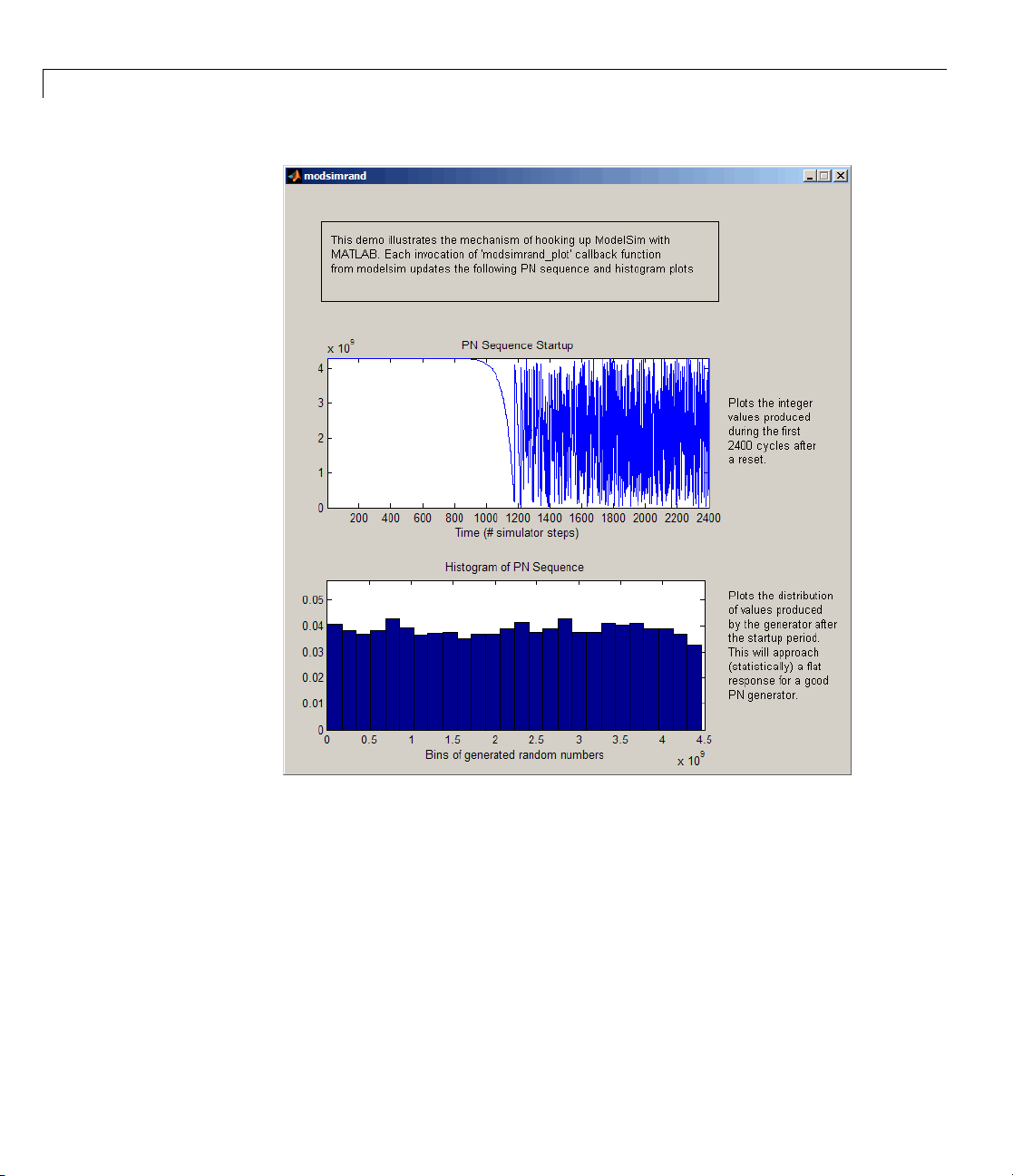

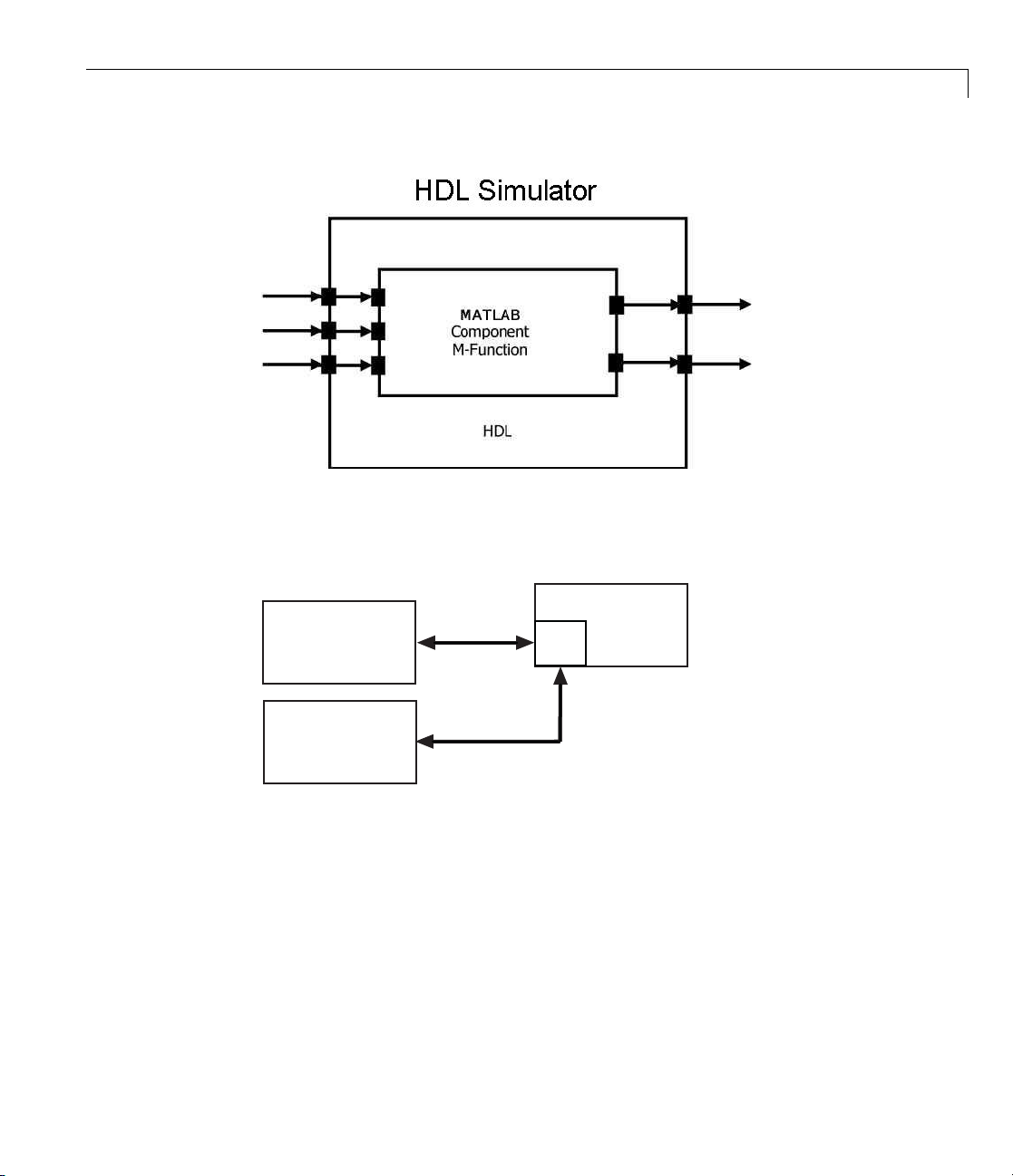

The following figure shows how a MATLAB function wraps around and

communicates with the HDL simulator during a test bench simulation session.

Page 27

MATLAB

MATLAB test bench M-Function

Using MATLAB as a Test Bench

Output

Arguments

Stimulus

HDL Simulator

HDL Entity

IN

OUT

Response

Input

Arguments

When linked with MATLAB, the HDL simulator functions as the client, with

MATLAB as the server. The following figure shows a multiple-client scenario

connecting to the server at TCP/IP socket port 4449.

HDL Simulator

Client

HDL Simulator

Client

Link

Port

4449

Link

MATLAB

Server

TheMATLABservercanservicemultiple simultaneous HDL simulator

sessions and HDL modules. How eve r, you should follow recommended

guidelines to ensure the server can track the I/O associated with each

module and session. The MATLAB server, which you start with the supplied

MATLAB function

hdldaemon, waits for connection requests from instances

of the HDL simulator running on the same or different computers. When

1-3

Page 28

1 Simulating an HDL Component in a MATLAB

the server receiv es a request, it ex ecutes the specified MATLAB function

you have coded to perform tasks on behalf of a module in your HDL design.

Parameters that you specify when you start the server indicate whether the

server establishes shared memory or TCP/IP socket communication links.

Refer to “Establishing EDA Simulator Link Machine Configuration

Requirements” on page 6 -26 for valid machine configurations.

Note The programming, interfacing, and scheduling conventions for test

bench functions and component functions are virtually identical (see Chapter

2, “Replacing an HDL Component with a MATLAB Compo ne nt Function”).

For the most part, the same procedures apply to both types of functions.

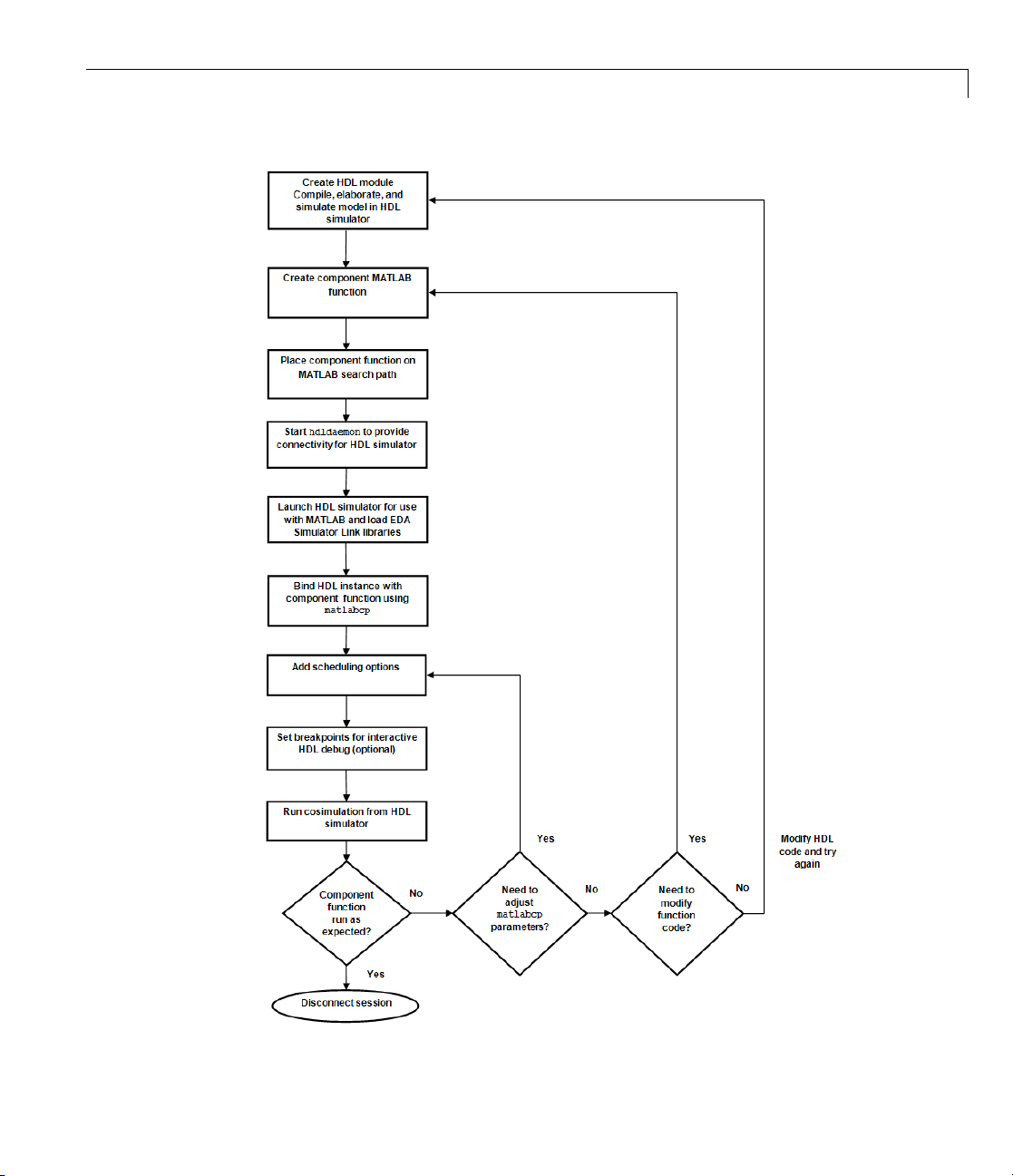

Workflow for Simulating an HDL Component with a

MATLAB Test Bench Function

The following workflow shows the steps nece ssary to create a MATLAB test

bench session for cosimulation with the HDL simulator using EDA Simulator

Link.

®

Test Bench Environment

1-4

Page 29

Using MATLAB as a Test Bench

1-5

Page 30

1 Simulating an HDL Component in a MATLAB

Theworkflowisasfollows:

1 “Code HDL Modules for Verification Using MA TLAB ” on page 1-7

2 “Code an ED A Simulator Link MATLAB Test Bench Function” on page 1-14

3 “Place Test Bench Function on MATLAB Search Path” on page 1-21

4 “Start Connection to HDL Simulator for Test Bench Session” on page 1-22

5 “LaunchHDLSimulatorforUsewithMATLABTestBench”onpage1-24

6 “Invoke matlabtb to Bind MATLAB Test Bench Function Calls” on page

1-26

7 “Schedule Options for a Test Bench Session” on page 1-31

8 Set breakpoints for interactive HDL debug (optional).

9 “Run MATLAB Test Bench Simulation” on page 1-35

®

Test Bench Environment

1-6

10 “Stop Test Bench Simulation” on page 1-44

Page 31

Code HDL Modules for Verification Using MATLAB

Code HDL Modules for Verification Using MATLAB

In this section...

“Overview to Coding HDL Modules for Verification with MATL AB” on

page 1-7

“Choosing an HDL Module Name for Use with a MATLAB Test Bench”

on page 1-8

“Specifying Port Direction Modes in HDL Module for Use with Test Bench”

on page 1-8

“Specifying Port Data Types in HDL Modules for Use with Test Bench”

on page 1-8

“Compiling and Elaborating the HDL Design for Use with Test Bench”

on page 1-10

“Sample VHDL Entity Definition” on page 1-12

Overview to Coding HDL Modules for Verification with MATLAB

The most basic element of communication in the EDA Simulator Link

interface is the HDL module. The interface passes all data between the HDL

simulator and MATL AB as port data. The EDA Simulator Link software

works with any existing HDL module. Howeve r, when you code an HDL

module that is targeted for MATLAB verification, you should consider its

name, the types of data to be shared between the two environments, and the

direction modes. The sections within this chapter cover these topics.

The process for coding HDL modules for MATLAB verification is as follows:

• Choose an HDL module name.

• Specify port d irection modes in HDL components.

• Specify port data types in HDL components.

• Compile and debug the HDL model.

1-7

Page 32

1 Simulating an HDL Component in a MATLAB

Choosing an HDL Module Name for Use with a MATLAB Test Bench

Although not required, when naming the HDL module, consider choosing a

name that also can be used as a MATLAB function name. (Generally, naming

rules for VHDL or V erilog and MATLAB are compatible.) By default, EDA

Simulator Link software assumes that an HDL module and its simulation

function share the same name. See “Invoke m atlabtb to Bind MATLAB Test

Bench Function Calls” on page 1-26.

For details on MATLAB function-naming guidelines, see “MATLAB

Programming Tips” on files and file names in the MATLAB documentation.

Specifying Port Direction Modes in HDL Module for

UsewithTestBench

In your module statement, you must specify each port with a direction mode

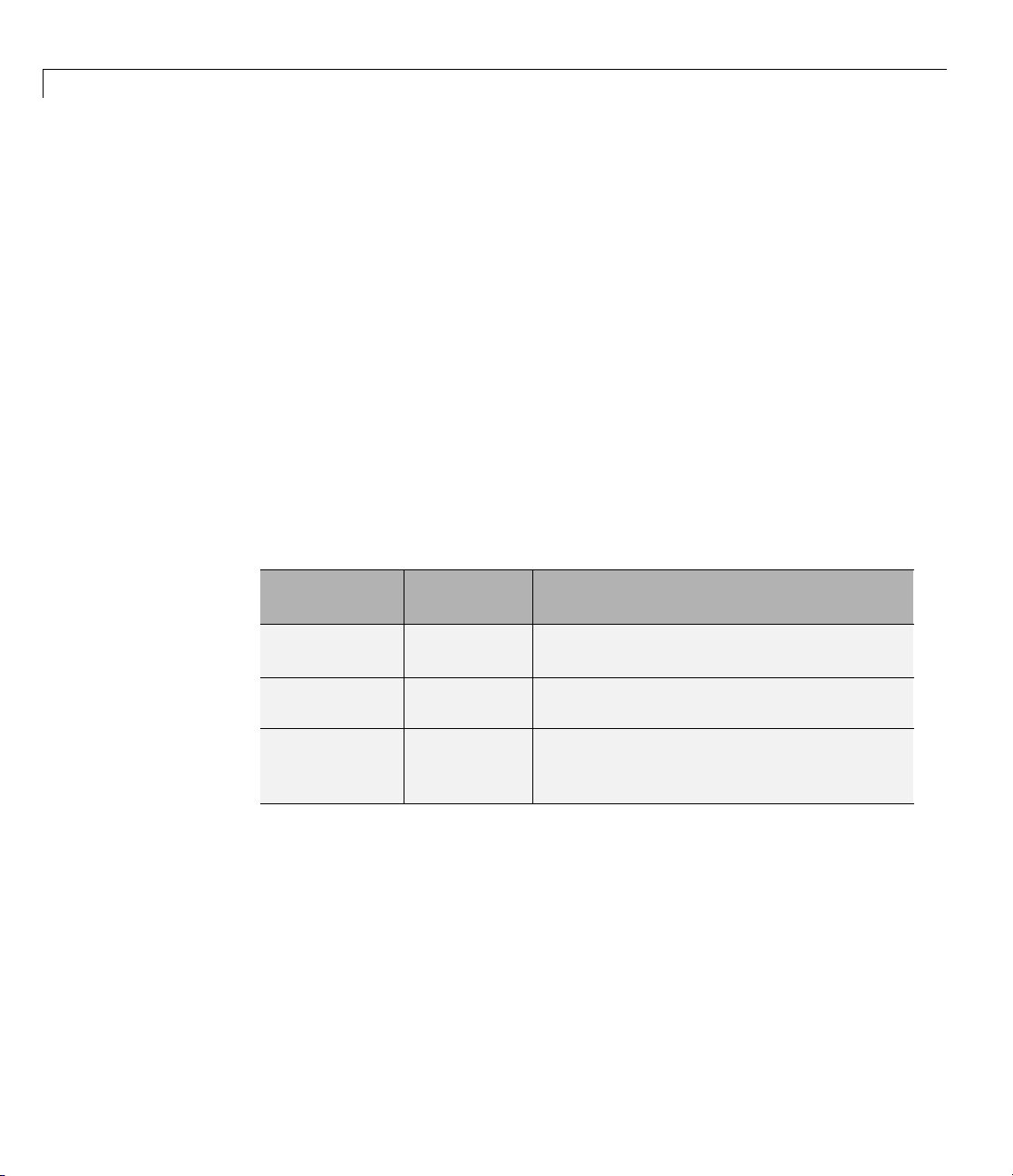

(input, output, or bidirectional). The following table defines these three modes.

®

Test Bench Environment

1-8

Use VHDL

Mode...

IN input

OUT output

INOUT inout

Use Verilog

Mode...

For Ports That...

Represent signals that can be driven by a

MATLAB function

Represent signal values that are passed to

a MATLAB function

Represent bidirectional signals that can

be driven by or pass values to a MATLAB

function

Specifying Port Data Types in HDL Modules for Use

with Test Bench

This section describes how to specify data types compatible with MATLAB

for ports in your HDL modules. For details on how the EDA Simulator Link

interface converts data types for the MATLAB environment, see “Performing

Data Type Conversions” on page 7-5.

Page 33

Code HDL Modules for Verification Using MATLAB

Note If you use unsupported types, the EDA Simulator Link software issues

a warning and ignores the port at run time. For example, if you define your

interface with f ive ports, one of which is a VHDL access port, at run time,

then the interface displays a warning and your code sees only four ports.

Port Data Types for VHDL Entities

In your entity statement, you must define each port that you plan to test with

MATLAB with a VHDL data type that is supported by the EDA Simulator

Link software. The interface can convert scalar and array data of the

following VHDL types to comparable MATLAB types:

•

STD_LOGIC, STD_ULOGIC, BIT, STD_LOGIC_VECTOR, STD_ULOGIC_VECTOR,

and

BIT_VECTOR

• INTEGER and NATURAL

• REAL

• TIME

• Enumerated types, including user-defined enumerated types and

CHARACTER

The interface also supports all subtypes and arrays of the preceding types.

Note The EDA Simulator Link software does not support VHDL extended

identifiers for the following components:

• Port and signal names used in cosimulation

• Enum literals when used as array indices of port and signal names used

in cosimulation

However, the software does support basic identifiers for VHDL.

1-9

Page 34

1 Simulating an HDL Component in a MATLAB

Port Data Types for Verilog Modules

In your modu le definition, you must defin e each port that you plan to t e s t

with MATLAB with a Verilog port data type that is supported by the EDA

Simulator Link software. The interface can convert data of the following

Verilog port types to comparable MATLAB types:

• reg

• integer

• wire

Note EDA Simulator Link software does not support Verilog escaped

identifiers for port and signal names used in cosimulation. However, it does

support simple identifiers for Verilog.

Compiling and Elaborating the HDL Design for Use with Test Bench

After you create or edit your HDL source files, use the HDL simulator

compiler to compile and debug the code.

®

Test Bench Environment

1-10

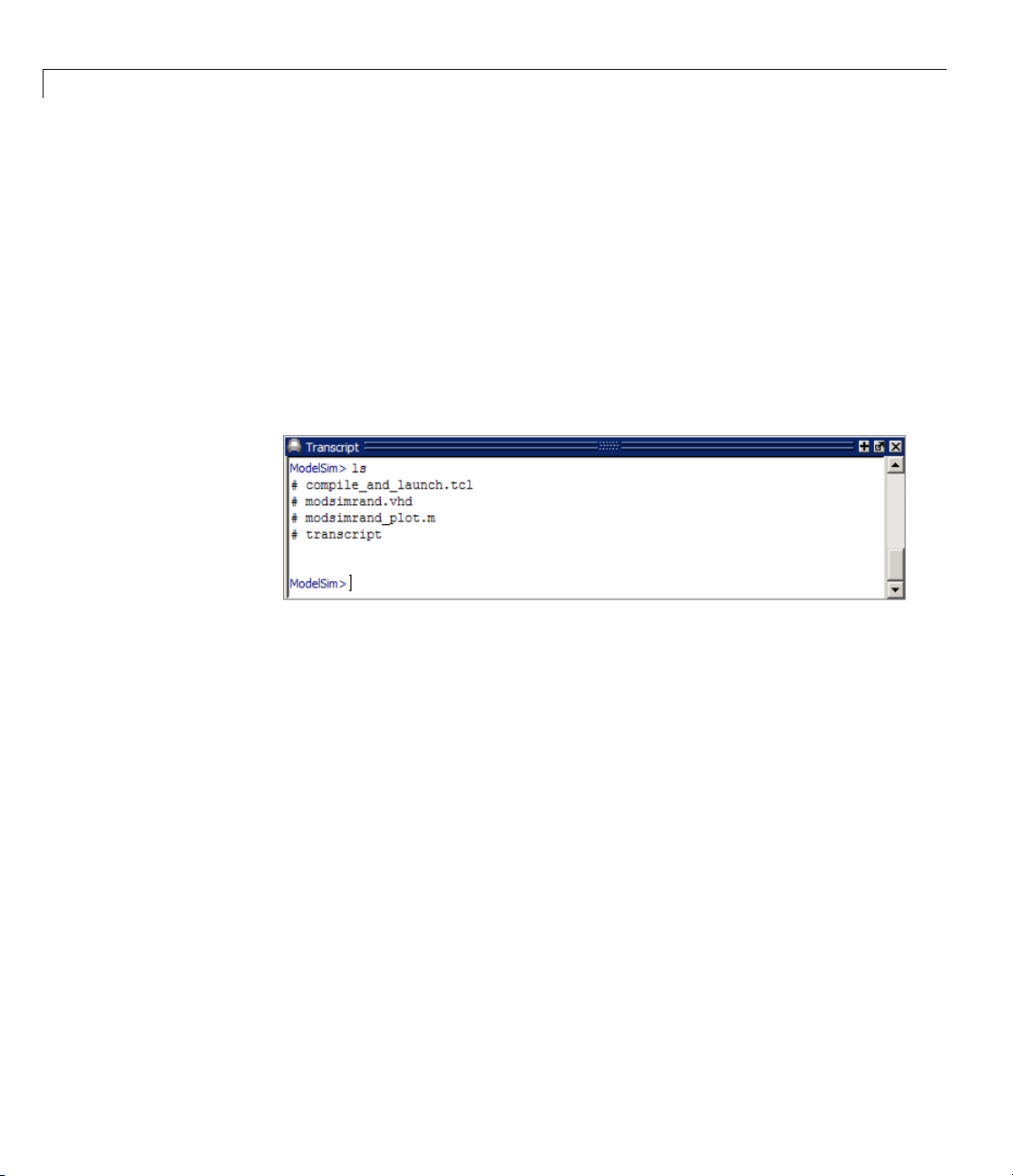

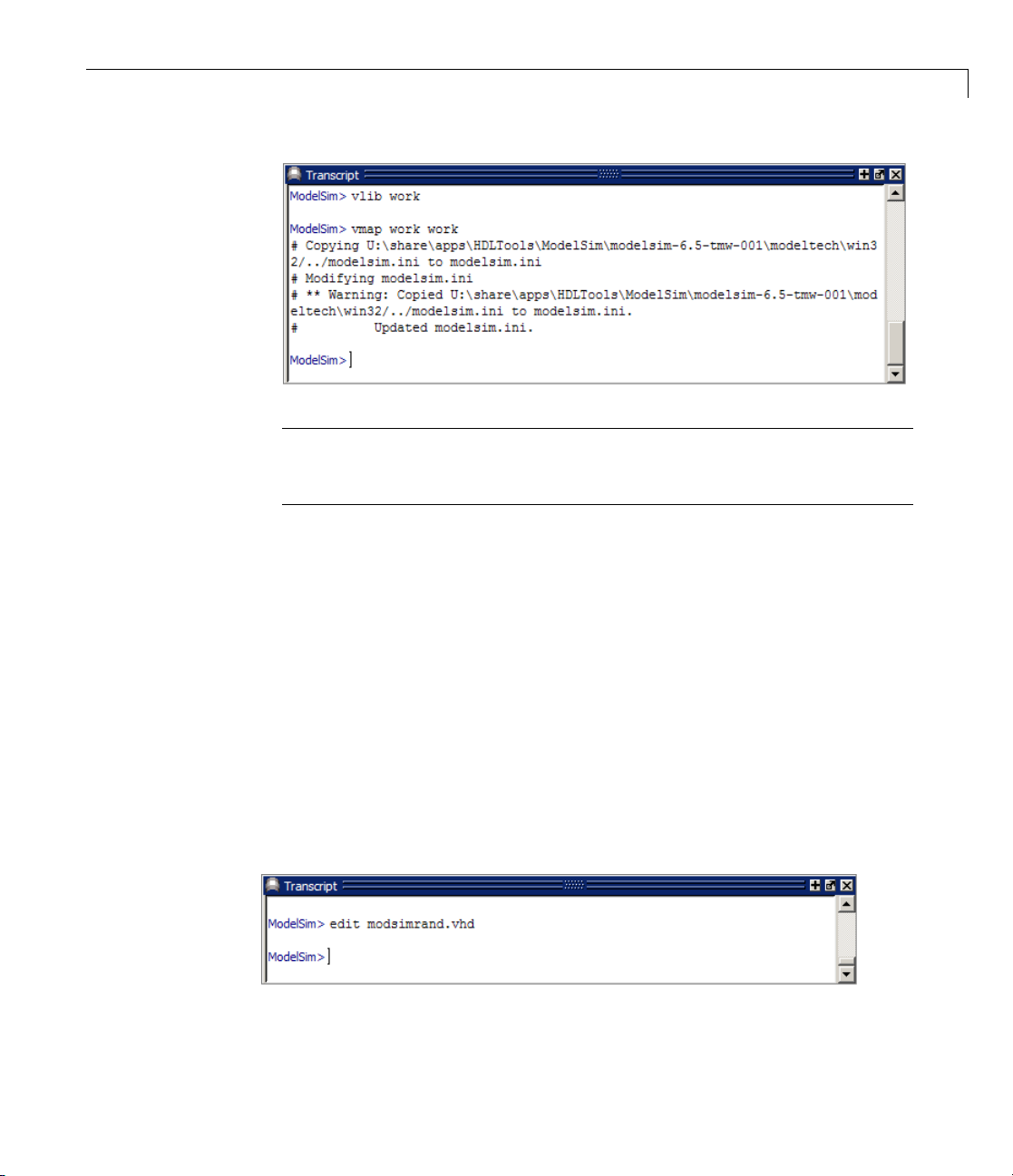

Compilation for ModelSim

You have the option of invoking the compiler from menus in the ModelSim

graphic interface or from the command line with the

following sequence of ModelSim commands creates and maps the design

library

The following sequence of ModelSim commands crea t es and maps the design

library

work and compiles the VHDL file modsimrand.vhd:

ModelSim> vlib work

ModelSim> vmap work work

ModelSim> vcom modsimrand.vhd

work and compiles the Verilog file test.v:

ModelSim> vlib work

ModelSim> vmap work work

ModelSim> vlog test.v

vcom command. The

Page 35

Code HDL Modules for Verification Using MATLAB

Note You should provide read/write access to the signals that are connecting

to the MATLAB session for cosimulation. For higher performance, you

want to provide access only to those signals used in cosimulation. You can

check read/write access through the HDL simulator—see HDL simulator

documentation for details.

Compilation for Incisive

The Cadence Incisive simulator allows for 1-step and 3-step processes for HDL

compilation, elaboration, and simulation. The following Cadence Incisive

simulator command compiles the Verilog file test.v:

sh> ncvlog test.v

The following Cadence Incisive simulator command compiles and elaborates

the Verilog design

test.v, and then loads it for si mulation, in a single step:

sh> ncverilog +gui +access+rwc +linedebug test.v

The following sequence of Cadence Incisive simulator commands performs all

thesameprocessesinmultiplesteps:

sh> ncvlog -linedebug test.v

sh> ncelab -access +rwc test

sh> ncsim test

Note You should provide read/write access to the signals that are connecting

to the MATLAB session for cosimulation. The previous example shows

how to provide read/write access to all signals in your design. For higher

performance, you want to provide access only to those signals used in

cosimulation. See the description of the

-access argument to ncelab for details.

+access flag to ncverilog and the

1-11

Page 36

1 Simulating an HDL Component in a MATLAB

Compilation for Discovery

Compilation of source files for use with MATLAB and Discovery is most

easily accomplished using the scripts automatically generated by the EDA

Simulator Link HDL simulator launch command

Examples section of the reference page for

Note You should provide read/write access to the signals that are connecting

to the MATLAB session for cosimulation. For higher performance, you want to

provide access only to those signals used in cosimulation. A tab file is included

in the simulation via the required

For more examples, see the EDA Simulator Link tutorialsanddemos. For

details on using the HDL compiler, see the simulator documentation.

Sample VHDL Entity Definition

This sample VHDL code fragment defines the entity decoder.Bydefault,the

entity is associated with MATLAB test bench function

®

Test Bench Environment

launchDiscovery.Seethe

launchDiscovery.

launchDiscovery property "AccFile".

decoder.

1-12

The keyword

two

IN ports—isum and qsum—and three OUT ports—adj, dvalid,andodata.

PORT marks the start of the entity’s port clause, which defines

The output ports drive signals to MATLAB function input ports for processing.

The input ports receive signals from the MATLAB function output ports.

Both input ports are defined as vectors consisting of five standard logic

values. The output port

consists of only two values. The output ports

adj is also defined as a standard logic vector, but

dvalid and odata are defined as

scalar standard logic ports. For information on how the EDA Simulator Link

interface converts data of standard logic scalar and array types for use in the

MATLAB environment, see “Performing Data Type Conversions” on page 7-5.

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

Page 37

odata : OUT std_logic);

END decoder ;

Code HDL Modules for Verification Using MATLAB

1-13

Page 38

1 Simulating an HDL Component in a MATLAB

®

Test Bench Environment

Code an EDA Simulator Link MATLAB Test Bench Function

In this section...

“Process for Coding MATLAB EDA Simulator Link Functions” on page 1-14

“Syntax of a Test Bench Function” on page 1-15

“Sample MATLAB Test Bench Function” on page 1-15

Process for Coding MATLAB EDA Simulator Link Functions

Coding a MATLAB function that is to verify an HDL module or component

requires that you follow specific coding conventions. You must also

understand the data type conversions that occur, and program data type

conversions for operating on data and returning data to the HDL simulator.

To code a MATLAB function that is to verify an HDL module or component,

perform the following steps:

1-14

1 Learn the syntax for a MATLAB EDA Simulator Link test bench function

(see “Syntax of a Test Bench Function” on page 1-15).

2 Understand how E DA Simulator Link software converts data from the

HDL simulator for use in the MATLAB environment (see “Performing

Data Type Conversions” on page 7-5).

3 Choos

4 Define expected parameters in the function definition line (see “MATLAB

5 Determine the types of port data being passed into the function (see

6 Ex

e a name for the MATLAB function (see “Binding the HDL Module

Compo

Function Syntax and Function Argument Definitions” on page 7-42).

“MATLAB Function Syntax and Function Argument Definitions” on page

7-42).

in

In

nent to the MATLAB Test B ench Function” on page 1-29).

tract and, if appropriate for the simulation, apply information received

the

portinfo structure (see “Gaining Access to and Applying Port

formation” on page 7-45).

Page 39

Code an EDA Simulator Link™ MATLAB®Test Ben c h F unct i on

7 Convert data for manipulation in the MATLAB environment, as necessary

(see “Converting HDL Data to Send to MATLAB” on page 7-5 ).

8 Convert data that needs to be returned to the HDL simulator (see

“Converting Data for Return to th e HDL Simulator” on page 7-10).

Syntax of a Test Bench Function

The syntax of a MATLAB test bench function is

function [iport, tnext] = MyFunctionName(oport, tnow, portinfo)

See the “MATLAB Function Syntax and Function Argument Definitions” on

page 7-42 for an explanation of each of the function arguments.

Sample MATLAB Test Bench Function

This section uses a sample MATLAB function to identify sections of a

MATLAB test bench function required by the EDA Simulator Link software.

Youcanseethefulltextofthecodeusedinthissampleinthesection

MATLAB Function Example: manchester_decoder.m on page 1-20.

For ModelSim Users This example uses a VHDL entity and MATLAB

function code drawn from the decoder portion of the Manchester Receiver

demo. For the complete VHDL and function code listings, see the following

files:

matlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\vhdl\manchester\decoder.vhd

matlabroot\toolbox\edalink\extensions\modelsim\modelsimdemos\manchester_decoder.m

As the first step to coding a MATLAB test bench function, you must

understand how the data modeled in the VH D L entity maps to data in the

MATLAB environment. The VHDL entity

ENTITY decoder IS

PORT (

isum : IN std_logic_vector(4 DOWNTO 0);

qsum : IN std_logic_vector(4 DOWNTO 0);

decoder is defined as follows:

1-15

Page 40

1 Simulating an HDL Component in a MATLAB

adj : OUT std_logic_vector(1 DOWNTO 0);

dvalid : OUT std_logic;

odata : OUT std_logic

);

END decoder ;

The following discussion highlights key lines of code in the definition of the

manchester_decoder MATLAB function:

1 Specify the MATLAB function name and required parameters.

®

Test Bench Environment

The following code is the function declaration of the

manchester_decoder

MATLAB function.

function [iport,tnext] = manchester_decoder(oport,tnow,portinfo)

See “MATLAB Function Syntax and Function Argum ent Definitions” on

page 7-42.

The function declaration performs the following actions:

• Names the function. This declaration names the function

manchester_decoder, which differs from the entity name decoder.

Because the names differ, the functionnamemustbespecifiedexplicitly

later when the entity is initialized for verification with the

matlabtbeval function. See “Binding the HDL Module Component to

matlabtb or

the MATLAB Test Bench Function” on page 1-29.

• Defines required argument and return param eters. A MATLAB test

bench function must return two parameters,

three arguments,

oport, tnow,andportinfo,andmust appear in the

iport and tnext,andpass

order shown. See “MATLAB Function Syntax and Function Argument

Definitions” on page 7-42.

The function outputs must be initialized to empty values, as in the

following code example:

tnext = [];

iport = struct();

1-16

You should initialize the function outputs at the beginning of the

function, to follow recommended best practice.

Page 41

Code an EDA Simulator Link™ MATLAB®Test Ben c h F unct i on

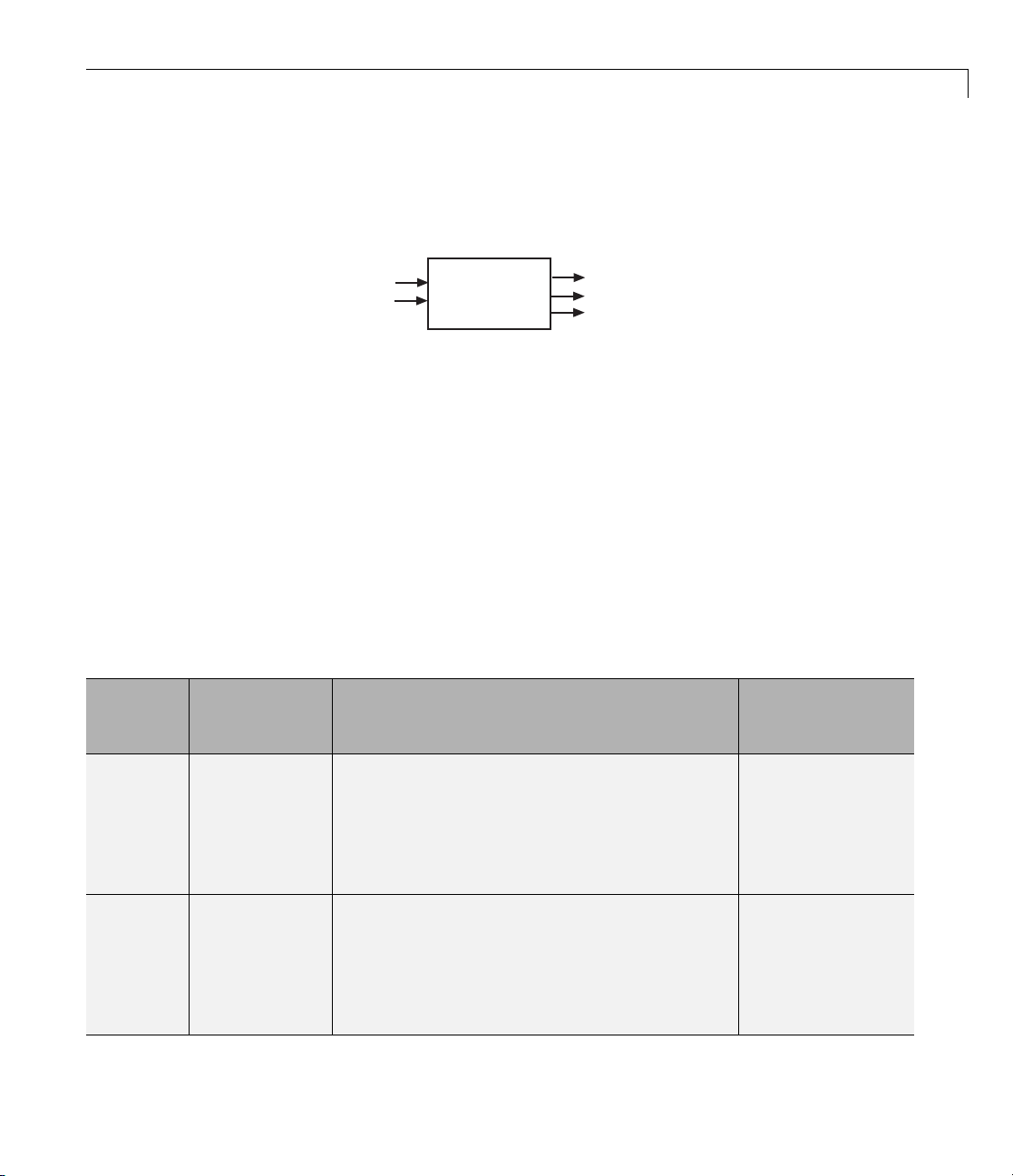

The following figure shows the relationship between the entity’s ports

and the MATLAB function’s

iport and oport parameters.

Input Signals

iport.isum (5)

iport.qsum (5)

decoder.vhd

Output Signals

oport.adj (2)

oport.dvalid(1)

oport.odata(1)

For more information on the required MATLAB test bench function

parameters, see “MATLAB Function Syntax and Function Argument

Definitions” on page 7-42.

2 Make note of the data types of ports defined for the entity being

simulated.

The ED A Simulator Link software converts HDL data types to comparable

MATLAB data types and vice versa. As you develop your MATLAB

function, you must know the types of the data that it receives from the

HDL simulator and needs to return to the HDL simulator.

The VHDL entity defined for this example consists of the following ports

VHDL Ex ample Port De fin itio ns

Port

isum IN STD_LOGIC_VECTOR(4 DOWNTO 0)

qsum IN STD_LOGIC_VECTOR(4 DOWNTO 0)

Direction

Type...

Converts

to/Requires

Conversion to...

A5-bitcolumn

or row vector of

characters where

each bit maps to

astandardlogic

character literal.

A5-bitcolumn

or row vector of

characters where

each bit maps to

astandardlogic

character literal.

1-17

Page 42

1 Simulating an HDL Component in a MATLAB

®

VHDL Example Port Definitions (Continued)

Test Bench Environment

Port

adj OUT STD_LOGIC_VECTOR(1 DOWNTO 0)

dvalid OUT STD_LOGIC

odata OUT STD_LOGIC

Direction

Type...

Converts

to/Requires

Conversion to...

A2-element

column vector of

characters. Each

character matches

a corresponding

character literal

that represents

alogicstateand

maps to a single

bit.

A character that

matches the

character literal

representing the

logic state.

A character that

matches the

character literal

representing the

logic state.

1-18

For more information on interface data type conversions, see “Performing

Data Type Co nvers ions” on page 7-5.

3 Set up any required timing parameters.

The

tnext assignment statem ent sets up timing parameter tnext such

that the simulator calls back the MATLAB function every nanosecond.

tnext = tnow+1e-9;

4 Convert output port data to appropriate MATLAB data types for

processing.

Page 43

Code an EDA Simulator Link™ MATLAB®Test Ben c h F unct i on

The following code excerpt illustrates data ty pe conversion of output port

data.

%% Compute one row and plot

isum = isum + 1;

adj(isum) = mvl2dec(oport.adj');

data(isum) = mvl2dec([oport.dvalid oport.odata]);

.

.

.

The two calls to mvl2dec convert the binary data that the MATLAB

function receives from the entity’s output ports,

adj, dvalid,andodata to

unsigned decimal values that MATLAB can compute. The function converts

the 2-bit transposed vector

4and

oport.dvalid and oport.odata to the decimal value 0 or 1.

oport.adj toadecimalvalueintherange0to

“Defining EDA Simulator Link MATLAB Functions and Function

Parameters” on page 7-42 provides a summary of the types of data

conversions to consider when coding simulation MATLAB functions.

5 Convert data to be returned to the HDL simulator.

The following code excerpt illustrates data type conversion of data to be

returned to the HDL simulator.

if isum == 17

iport.isum = dec2mvl(isum,5);

iport.qsum = dec2mvl(qsum,5);

else

iport.isum = dec2mvl(isum,5);

end

The three calls to dec2mvl convert the decimal values computed by

MATLAB to binary data that the MATLAB function can deposit to the

entity’s input ports,

isum and qsum. Ineachcase,thefunctionconvertsa

decimal value to 5-element bit vector with each bit representing a character

that m aps to a character literal representing a logic state.

1-19

Page 44

1 Simulating an HDL Component in a MATLAB

“Converting Data for Return to the HDL Simulator” on page 7-10 provides

a summary of the types of data conversions to consider when returning

data to the HDL simulator.

MATLAB Function Example: manchester_decoder.m

®

Test Bench Environment

1-20

Page 45

Place Test Bench Function on MATLAB Search Path

Place Test Bench Function on MATLAB Search Path

In this section...

“Use MATLAB which Function to Find Test Bench” on page 1-21

“Add Test Bench Function to MATLAB Search Path” on page 1-21

Use MATLAB which Function to Find Test Bench

The MATLAB function that you are associating with an HDL component must

be on the MATLAB search path or reside in the current working folder (see

the MATLAB

the MATL AB

function

which MyVhdlFunction

/work/incisive/MySym/MyVhdlFunction.m

If the specified function is on the search path, which displays the complete

path to the function. If the function is not on the search path,

you that the file was not found.

cd function). To verify whether the function is accessible, use

which function. The following call to which checks whether the

MyVhdlFunction is on the MATLAB search path, for example:

which informs

Add Test Bench Function to MATLAB Search Path

To add a M ATLA B function to the MATLAB search path, open the Set

Path window by clicking File > Set Path,orusethe

Alternatively, for temporary access, you can change the MATLAB working

folder to a desired location with the

cd command.

addpath command.

1-21

Page 46

1 Simulating an HDL Component in a MATLAB

®

Test Bench Environment

Start Connection to HDL Simulator for Test Bench Session

In this section...

“Start MATLA B Server for Test Bench Session” on page 1-22

“Example of Starting MATLAB Server for Test Bench Session” on page 1-23

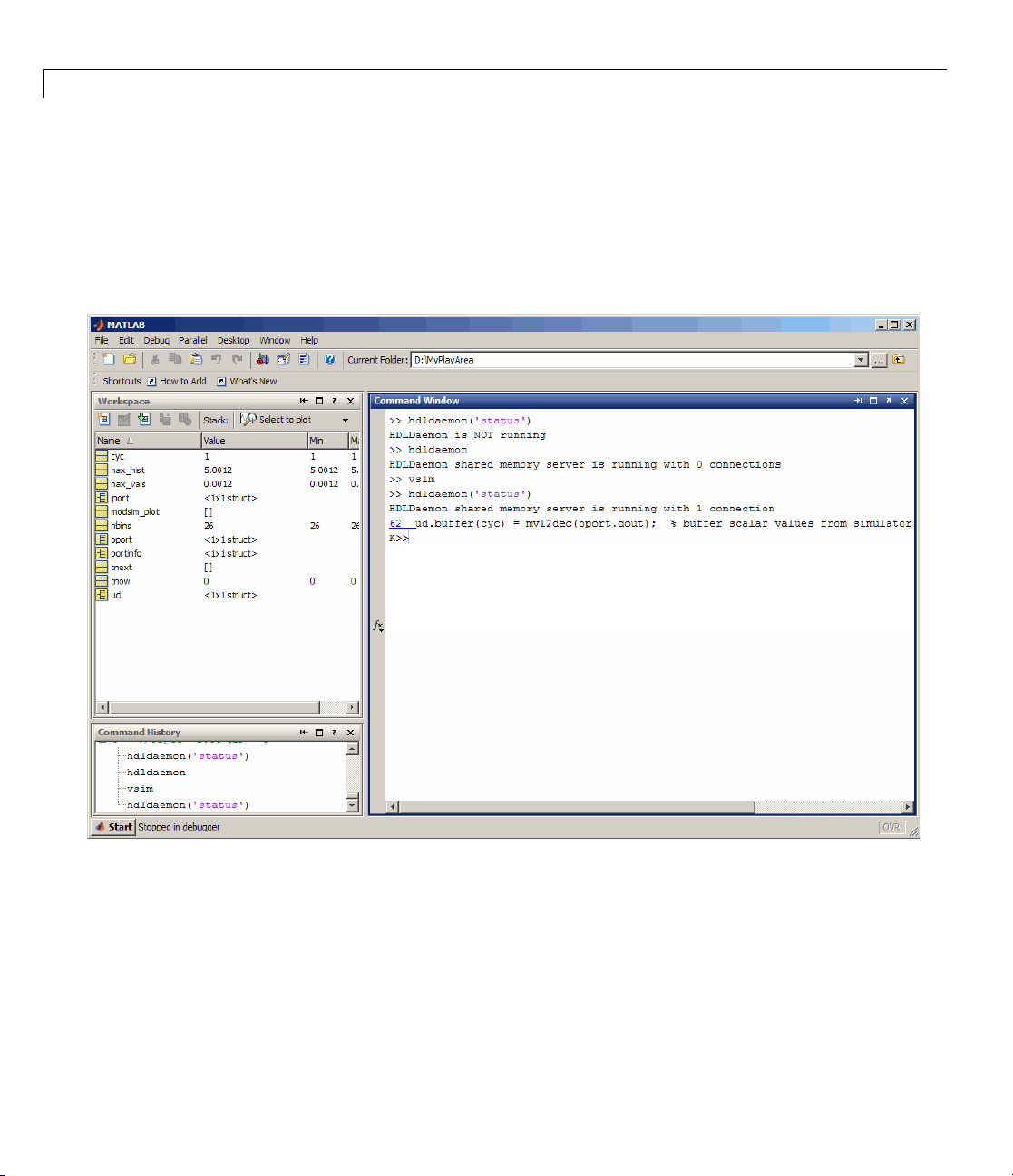

Start MATLAB Server for Test Bench Session

Start the MATLAB server as follows:

1 Start MATLAB.

2 In the MATLAB Command Window, call the hdldaemon function with

property name/property value pairs that specify whether the EDA

Simulator Link software is to perform the following tasks:

• Use shared m emo ry or TCP/IP socket communication

• Return time values in seconds or as 64-bit integers

1-22

See

hdldaemon reference documentation for when and how to specify property

name/property value pairs and for more examples of using

The communication mode that you specify (shared memory or TCP/IP sockets)

must match what you specify for the communication mode when you initialize

the HDL simulator for use with a MATLAB link session using the

or matlabcp function. In addition, if you specify TCP/IP socket mode, the

socket port that you specify with

match. For more information on modes of communication, see “Specifying

TCP/IP Socket Communication” on page 6-29.

TheMATLABservercanservicemultiple simultaneous HDL simulator

modules and clients. However, your code must track the I/O associated with

each entity or client.

hdldaemon and matlabtb or matlabcp must

hdldaemon.

matlabtb

Page 47

Start Connection to HDL Simulator for Test Bench Session

Note You cannot begin an EDA Simulator Link transaction between

MATLAB and the HDL simulator from MATLAB. The MATLAB server simply

responds to function call requests that it receives from the HDL simulator.

Example of Starting MATLAB Server for Test Bench Session

The following com mand specifies using socket communication on port 4449

and a 64-bit time resolution format for the MATLAB function’s output ports.

hdldaemon('socket', 4449, 'time', 'int64')

1-23

Page 48

1 Simulating an HDL Component in a MATLAB

®

Test Bench Environment

Launch HDL Simulator for Use with MATLAB Test Bench

In this section...

“Launching the HDL Simulator for Test Bench Session” on page 1-24

“Loading an HDL Design for Verification” on page 1-24

Launching the HDL Simulator for Test Bench Session

Start the HDL simulator directly from MATLAB by calling the M ATLAB

function

Link with HDL Simulators ” for instructions on starting the HDL simulator

for use with EDA Simulator Link.

Loading an HDL Design for Verification

After you start the HDL simulator from MATLAB with a call to vsim or

nclaunch, load an instance of an HDL module for verification or visualization

with the function

start the HDL simulator from MATLAB and load an instance of an HDL

module for verification with a call to

'PropertyValue'...)

your HDL model. Issue the function

instance of an entity or module in your model that you want to cosimulate.

For example (for use with Incisive):

vsim, nclaunch,orlaunchDiscovery. See “Using EDA Simulator

vsimmatlab or hdlsimmatlab. If you are using Discovery,

launchDiscovery('PropertyType',

. At this p oint, you should have coded and compiled

vsimmatlab or hdlsimmatlab for each

1-24

hdlsimmatlab work.osc_top

This command loads the EDA Simulator Link library, opens a simulation

workspace for

simulator command window as the simulator loads the entity (see demo for

remaining code).

Another example is (for use with Discovery):

launchDiscovery( ...

'VerilogFiles','osc_top.v', ...

'TopLevel', 'osc_top', ...

'RunMode','GUI', ...

'RunDir',projdir,...

osc_top, and displayd a series of me ssages in the HDL

Page 49

Launch HDL Simulator for Use with MATLAB Test Bench

'LinkType','MATLAB',...

'PreSimTcl', preSimTclCmds, ...

'AccFile',tabaccessfile,...

'VlogAnFlags', '"+v2k"' ...

);

This command loads osc_top in the HDL simulator and executes the

preSimTclCmds commands (see Oscillator demo for remaining code).

1-25

Page 50

1 Simulating an HDL Component in a MATLAB

®

Test Bench Environment

Invoke matlabtb to Bind MATLAB Test Bench Function Calls

In this section...

“Invoking the MATLAB T est Bench Comm and matlabtb” on page 1-26

“Binding the HDL Module Component to the MATLAB Test Bench

Function” on page 1-29

Invoking the MATLAB Test Bench Command matlabtb

You invoke matlabtb by issuing the command in the HDL simulator. See

the Examples section of the

of invoking

Be sure to follow the path specifications for MATLAB test bench sessions

when invoking

Module Paths for MA TLAB Test Bench Cosimulation” on page 1-26.

matlabtb.

matlabtb, as explained in “Specifying HDL Signal/Port and

matlabtb reference page for several examples

For instructions in issuing the

Bench Cosimulation” on page 1-36.

matlabtb command, see “Running a Test

Specifying HDL Signal/Port and Module Paths for MATLAB Test

Bench C

EDA Simulator Link software has specific requirements for specifying HDL

design hierarchy, the syntax of which is described in the following sections:

one for Verilog at the top level, and one for VHDL at the top level. Do not use

a file name hierarchy in place of the design hierarchy name.

The rules stated in this section apply to signal/port and module path

specifications for MATLAB l in k sessions. Other specifications m ay work but

the EDA Simulator Link software does not officially recognize nor support

them.

In the following example:

matlabtb u_osc_filter -mfunc oscfilter

u_osc_filter is the top-level component. If you specify a subcompone n t, you

must follow valid module path specifications for MATLAB link sessions.

osimulation

1-26

Page 51

Invoke matlabtb to Bind MATLAB Test Bench Function Calls

Path Specifications for MATLAB Link Sessions with Verilog Top Level.

• The path specification must start w ith a top-level module name.

• The path specification can include "." or "/" path delimiters, but it cannot

include mixed delimiters.

• The leaf m odule or signal must match the HDL language of the top-level

module.

The following examples show valid signal an d module path specifications:

top.port_or_sig

/top/sub/port_or_sig

top

top/sub

top.sub1.sub2

The following examples show invalid signal and module path specifications:

•

top.sub/port_or_sig

Why this specification is invalid: You cannot use mixed delimiters.

:sub:port_or_sig

•

:

:sub

Why this specification is invalid: When you use VHDL-specific delimiters

you limit the interoperability with paths when moving between HDL

simulators and between VHDL and Verilog.

Path Specifications for MATLAB Link Sessions with VHDL Top Level.

• The path specification can include the top-level module name, but you do

nothavetoincludeit.

• The path specification can include "." or "/" path delimiters, but it cannot

include mixed delimiters.

• The leaf m odule or signal must match the HDL language of the top-level

module.

1-27

Page 52

1 Simulating an HDL Component in a MATLAB

Examples for ModelSim and Incisive Users

The following examples show valid signal an d module path specifications:

top.port_or_sig

/sub/port_or_sig

top

top/sub

top.sub1.sub2

The following examples show invalid signal and module path specifications:

•

top.sub/port_or_sig

Why this specification is invalid: You cannot use mixed delimiters.

:sub:port_or_sig

•

:

:sub

®

Test Bench Environment

1-28

Why this specification is invalid: When you use VHDL-specific delimiters

you limit the interoperability with paths when moving between HDL

simulators and between VHDL and Verilog.

Examples for Discovery Users

The following examples show valid signal an d module path specifications:

top.port_or_sig

top

top/sub

top.sub1.sub2

The following examples show invalid signal and module path specifications:

•

top.sub/port_or_sig

Why this specification is invalid: You cannot use mixed delimiters.

/sub/port_or_sig

•

Why this specification is invalid: You have not specified the top level.

Page 53

Invoke matlabtb to Bind MATLAB Test Bench Function Calls

• :sub:port_or_sig

:

:sub

Why this specification is invalid: When you use VHDL-specific delimiters

you limit the interoperability with paths when moving between HDL

simulators and between VHDL and Verilog.

Binding the HDL Module Component to the MATLAB

Test Bench Function

Bydefault,theEDASimulatorLinksoftwareassumesthatthenamefora

MATLAB function matches the name of the HDL module that the function

verifies. When you create a test bench or component function that has a

different name than the design under test, you must associate the design

with the MATLAB function using the -mfunc argument to

argument associates the HDL module instance to a MATLAB function that

has a different name from the HDL instance.

matlabtb.This

For more information on the -mfunc argument and for a full list of

parameters, see the matlabtb function reference.

For details on MATLAB function naming guidelines, see "MATLAB

Programming Tips" on files and file names in the MATLAB documentation.

matlabtb

Example of Binding Test Bench and Component Function Calls

In this first example, you form an as sociation between the inverter_vl

component and the MATLAB test bench function inverter_tb by invoking the

function

The matlabtb command instructs the HDL simulator to call back the

inverter_tb function when inverter_vl executes in the simulation.

In this second example, you bind the model osc_top.u_osc_filter to the

component function oscfilter:

matlabtb with the -mfunc argument when y ou set up the simulation.

matlabtb inverter_vl -mfunc inverter_tb

matlabcp osc_top.u_osc_filter -mfunc oscfilter

1-29

Page 54

1 Simulating an HDL Component in a MATLAB

When the HDL simulator calls the oscfilter callback, the function knows to

operate on the model osc_top.u_osc_filter.

®

Test Bench Environment

1-30

Page 55

Schedule Options for a Test Bench Session

Schedule Options for a Test Bench Session

In this section...

“About Scheduling Options for Test Bench Sessions” on page 1-31

“Scheduling Test Bench Session Using matlabtb Arguments” on page 1-31

“Scheduling Test Bench Functions Using the tnext Parameter” on page 1-32

About Scheduling Options for Test Bench Sessions

TherearetwowaystoscheduletheinvocationofaMATLABfunction:

• Using the arguments to the EDA Simulator Link function

matlabcp

• Inside the MATLAB function using the tnext parameter

The two types of scheduling are not mutually exclusive. You can combine

the

matlabtb or matlabcp timing arguments and the tnext parameter of a

MATLAB function to schedule test ben ch or co mpo nent session callbacks.

matlabtb or

Scheduling Test Bench Session Using matlabtb Arguments

By default, the EDA Simulator Link software invokes a MATLAB test

bench or component function once (at the time that you make the call to

matlabtb/matlabcp). If you want to apply more control, and execute the

MATLAB function more than once, use the command scheduling options.

With these options, you can specify when and how often the EDA Simulator

Link software invokes the relevant MATLAB function. If necessary, modify

the function or specify timing arguments when you begin a MATLAB test

bench or component function session with the

You can schedule a MATLAB test bench or component function to execute

using the command arguments under any of the following conditions:

• Discrete time values—Ba sed on time specifications that can also include

repeat intervals and a stop time

matlabtb/matlabcp function.

• Rising edge—When a specified signal experiences a rising edge

1-31

Page 56

1 Simulating an HDL Component in a MATLAB

- VHDL: Rising edge is {0 or L} to {1 or H} .

- V erilog: Rising edge is the transition from 0 to x, z, or 1, and from x

or z to 1.

• Falling edge—When a specified signal experiences a falling edge

- V H DL: Falling edge is {1 or H } to {0 or L}.

- Verilog: Falling edge i s the transition from 1 to x, z, or 0, and from

xorzto0.

• Signal state change—When a specified signal changes state, based on a

list using the -sensitivity argument to

Scheduling Test Bench Functions Using the tnext Parameter

You can control the callback timing of a MATLAB function by using that

function’s

simulator, and the value gets added to the simulation schedule for that

function. If the function returns a null value ([]) , the software does not add

any new entries to the schedule.

tnext parameter. This parameter passes a time value to the HDL

®

Test Bench Environment

matlabtb.

1-32

You can set the value of

double to express the callback time in seconds. For example, to schedule

acallbackin1ns,specify::

tnext = 1e-9

Specify int64 to convert to a n integer multiple of the curre nt HDL simulator

time resolution limit. For example: if the HDL simulator time precision is 1

ns, to schedule a callback at 100 ns, specify:

tnext=int64(100)

tnext to a value of type double or int64.Specify

Page 57

Schedule Options for a Test Bench Session

Note The tnext parameter represents time from the start of the simulation.

Therefore,

tnext m ust always be greater than tnow. If it is less, the software

does not schedule a callback.

For more information on tnext and the function prototype, see “Defining EDA

Simulator Link MATLAB Functions and Function Parameters” on page 7-42.

Examples of Scheduling with tnext

In this first example, each time the HDL simulator calls the test bench

function (via EDA Simulator Link), tnext schedules the next callback to the

MATLAB function for 1 ns later, relative to the current simulation time:

tnext = [];