PXA300 and PXA310 Processor

Vol. I: System and Timer Configuration

Developers Manual, Rev 0.94

Product Number to be assigned at a later date.

Doc. No. MV-TBD-00, Rev. A

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

December 13, 2006

Document Classification: Proprietary Information

Not approved by Document Control. For review only.

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Product Number

Developers Manual

Document Conventions

Note

Provides related information or information of special importance.

Caution

Indicates potential damage to hardware or software, or loss of data.

Warning

Indicates a risk of personal injury.

Document Status

Doc Status: Preliminary Technical Publication: 0.xx

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

For more information, visit our website at: www.marvell.com

Disclaimer

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

No part of this document may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, for any

purpose, without the express written permission of Marvell. Marvell retains the right to make changes to this document at any time, without notice. Marvell makes no

warranty of any kind, expressed or implied, with regard to any information contained in this document, including, but not limited to, the implied warranties of

merchantability or fitness for any particular purpose. Further, Marvell does not warrant the accuracy or completeness of the information, text, graphics, or other items

contained within this document.

Marvell products are not designed for use in life-support equipment or applications that would cause a life-threatening situation if any such products failed. Do not use

Marvell products in these types of equipment or applications.

With respect to the products described herein, the user or recipient, in the absence of appropriate U.S. government authorization, agrees:

1) Not to re-export or rel ease any su ch info rma tion co nsi sting o f technology, software or source code controlled for national security reasons by the U.S. E xport Contr ol

Regulations ("EAR"), to a national of EAR Country Groups D:1 or E:2;

2) Not to export the direct product of such technology or such software, to EAR Country Groups D:1 or E:2, if such technology or software and direct products thereof

are controlled for national security reasons by the EAR; and,

3) In the case of technology controlled for national security reasons under the EAR where the direct product of the technology is a complete plant or component of a

plant, not to export to EAR Co untr y Gr oup s D:1 o r E :2 the dir ect p rodu ct o f th e p lant or maj or component thereof, if such d irect prod uct is controlled for nati onal security

reasons by the EAR, or is subject to controls under the U.S. Munitions List ("USML").

At all times hereunder, the recipient of any such infor matio n agr ees that they shall be deemed to have man ually sign ed th is docum ent in con necti on with their receipt of

any such information.

Copyright © 2006. Marvell International Ltd. All rights reserved. Marvell, the Marvell logo, Moving Forward Faster, Alaska, Fastwriter, Datacom Systems on Silicon,

Libertas, Link S treet, NetGX , PHYAdvantage, Prestera, Raising The Technology Bar, The T echnology Wi thin, V irtual C able Tester, and Yukon are re gistered tra demarks

of Marvell. Ants, AnyVoltage, Discovery, DSP Switcher, F eroce on, Ga lNet, Gal Tis, Horizon, Marvell Makes It A ll P ossible, RA DLA N, UniMAC , and VCT ar e tra dema rks

of Marvell. All other trademarks are the property of their respective owners.

Intel XScale® is a trademark or registered trademark of Intel Corporation and its subsidiaries in the United States and other countries.

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Doc. No. MV-TBD-00 Rev. A

Page 2 Document Classification: Proprietary Information December 13, 2006

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Copyright © 12/13/06 Marvell

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

Contents

1 Introduction..................................................................................................................................19

1.1 About This Manual......... ....... ...... ....... ...... ....... ...... ...... ....... ...... ...........................................19

1.1.1 Number Representation.........................................................................................20

1.1.2 Naming Conventions .............................................................................................20

1.1.3 Data Types ............................................................................................................20

1.1.4 Related Documents ...............................................................................................21

1.2 Product Overview ...............................................................................................................22

1.2.1 Intel XScale

1.2.2 Intel XScale

1.2.3 Multimedia Coprocessor ....... ...... ....... ...... ............................................. ....... ...... ....24

1.2.4 Power Management...............................................................................................24

1.2.5 Power I2C Controller .............................................................................................25

1.2.6 One-Wire Controller...............................................................................................25

1.2.7 Graphics Controller................................................................................................26

1.2.8 Performance Monitor .............................................................................................27

1.2.9 Internal Memory Architecture.................................................................................27

1.2.10 Internal SRAM Memory .........................................................................................27

1.2.11 External Memory Interfaces...................................................................................27

1.2.12 Dynamic Memory Controller ..................................................................................28

1.2.13 Static Memory Controller .......................................................................................28

1.2.14 Data Flash Controller.............................................................................................29

1.2.15 Interrupt Controller.................................................................................................30

1.2.16 Operating System Timers......................................................................................30

1.2.17 Pulse-Width Modulation Unit (PWM) .....................................................................31

1.2.18 Real-Time Clock (RTC)..........................................................................................31

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

1.2.19 General-Purpose I/O (GPIO) .................................................................................32

1.2.20 DMA Controller ......................................................................................................32

1.2.21 Mobile Scalable Link Controller .............................................................................33

1.2.22 Serial Ports ............................................................................................................33

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

1.2.23 LCD Panel Controller............................................ ...... ....... ...... ....... ...... ....... ..........37

1.2.24 Mini-LCD Panel Controller .....................................................................................38

1.2.25 Multimedia Card, SD Memory Card, and SDIO Card ............................................39

1.2.26 Keypad Interface....................................................................................................39

1.2.27 Universal Subscriber ID Controller.........................................................................40

1.2.28 Camera Image Capture Interface ..........................................................................40

1.2.29 Test........................................................................................................................42

1.3 Intel XScale

®

Microarchitecture Compatib ility ....................................................................42

®

Microarchitecture and Core.............................................................23

®

Microarchitecture Features............. ...... ....... ...... ..............................2 3

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

2 System Architecture Overview...................................................................................................43

2.0.1 Differences Between PXA300 Processor and PXA310 Processor........................43

2.1 Intel XScale

2.2 Endianness.........................................................................................................................44

2.3 Memory Switch vs. System Bus .........................................................................................44

2.4 I/O Ordering........................................................................................................................44

2.5 Accessing Peripherals on Internal Per i phe ral Bus................... ....... ....................................45

2.5.1 Programmed I/O Operations Using the Bridge ......................................................45

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 3

®

Microarchitecture Implementation Options...................................................43

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

CONFIDENTIAL

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

Product Number

Developers Manual

2.5.2 Data Transfer Using DMA......................................................................................45

2.6 Peripheral Access on Internal System Buses.....................................................................46

2.7 DMA/Peripheral Split Transactions.....................................................................................46

2.8 System Bus Arbiters ...........................................................................................................46

2.9 System Access Latencies...................................................................................................46

2.10 Semaphores .......................................................................................................................47

2.11 Interrupts.............................................................................................................................48

2.12 Reset ..................................................................................................................................48

2.13 Selecting Peripherals vs. General-Purpose I/O..................................................................49

2.14 Power-On Reset and Boot Operation.................................................................................49

2.15 Memory Map and Register Overview .................................................................................50

2.15.1 Intel XScale

2.15.2 Interrupt Controller Registers.................................................................................53

2.15.3 Performance Monitoring Registers........................................................................54

2.15.4 Clock Configuration and Power Management Registers.......................................55

2.15.5 Coprocessor Software Debug Registers ...............................................................55

2.15.6 Coprocessor 15 .....................................................................................................56

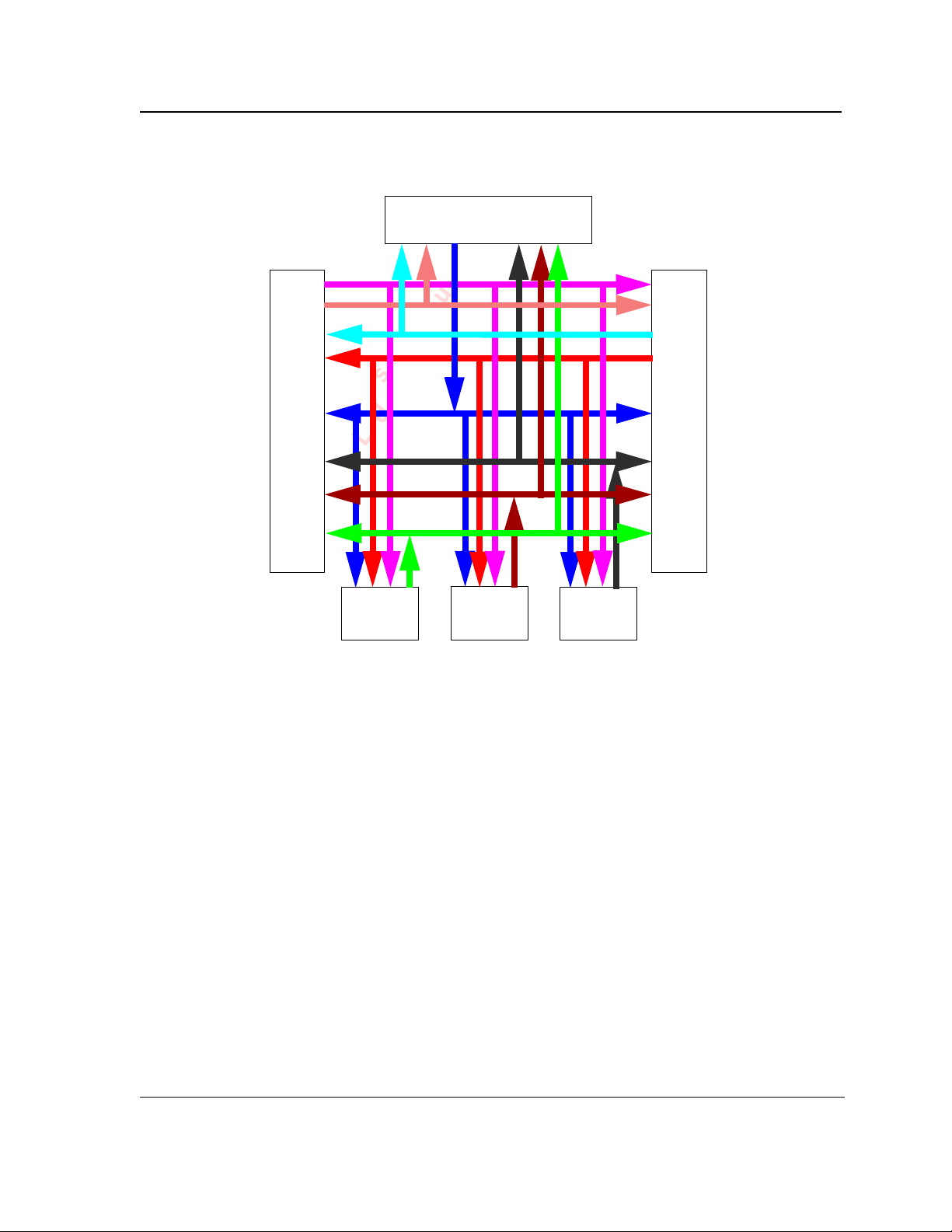

3 Memory Switch ............................................................................................................................61

3.1 Overview.............................................................................................................................61

3.1.1 Differences Between PXA300 Processor and PXA310 Processor........................61

3.2 Features..............................................................................................................................61

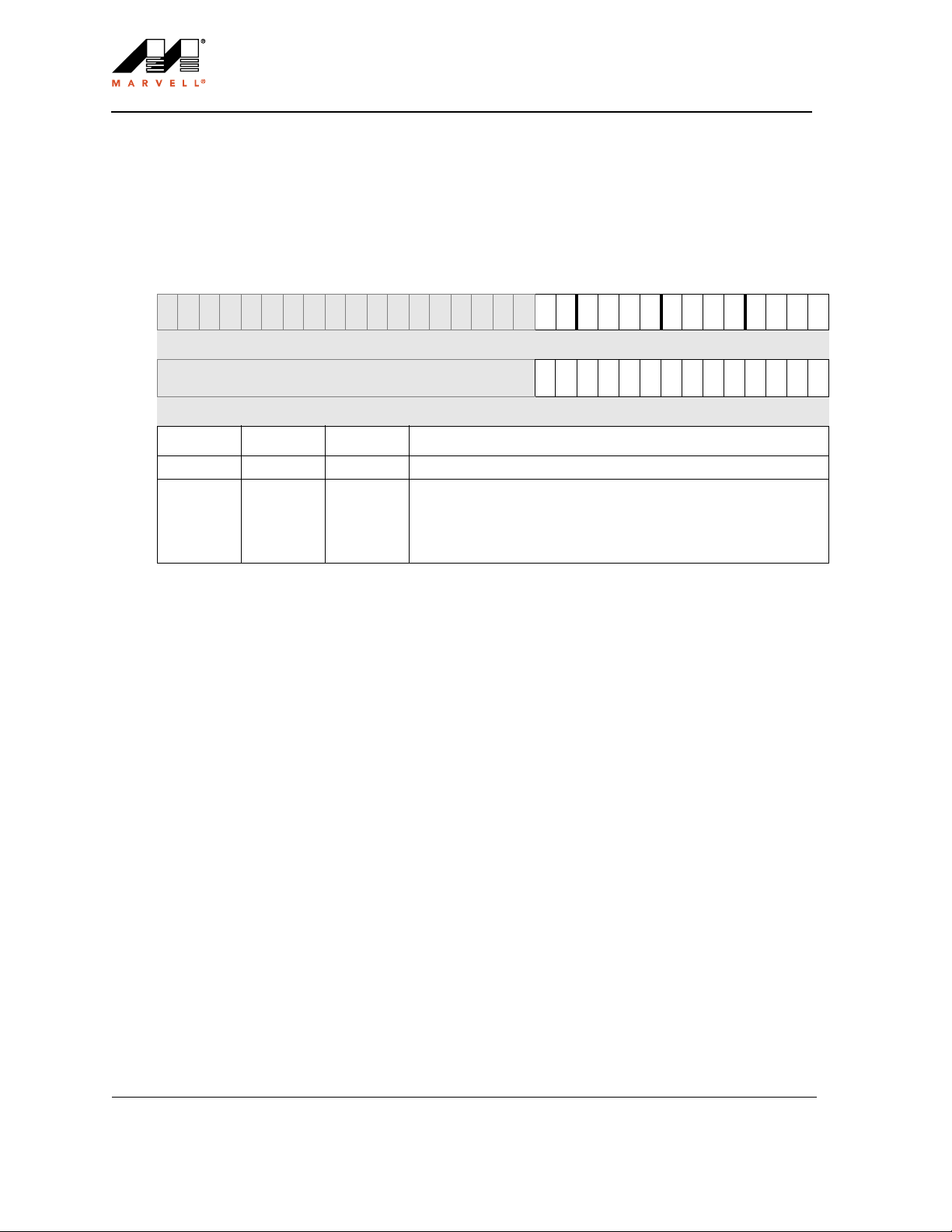

3.3 I/O Pins...............................................................................................................................62

3.4 Functional Description ............................................................................. ....... ...... ..............62

3.4.1 Priority Control.......................................................................................................62

3.4.2 The Memory Switch Concept.................................................................................64

®

Microarchitecture Coprocessor Register Summary.........................51

4 Pin Descriptions and Control.....................................................................................................65

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

4.1 Overview.............................................................................................................................65

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

4.1.1 Differences Between PXA300 and PXA310 Processors.......................................65

4.2 Features..............................................................................................................................65

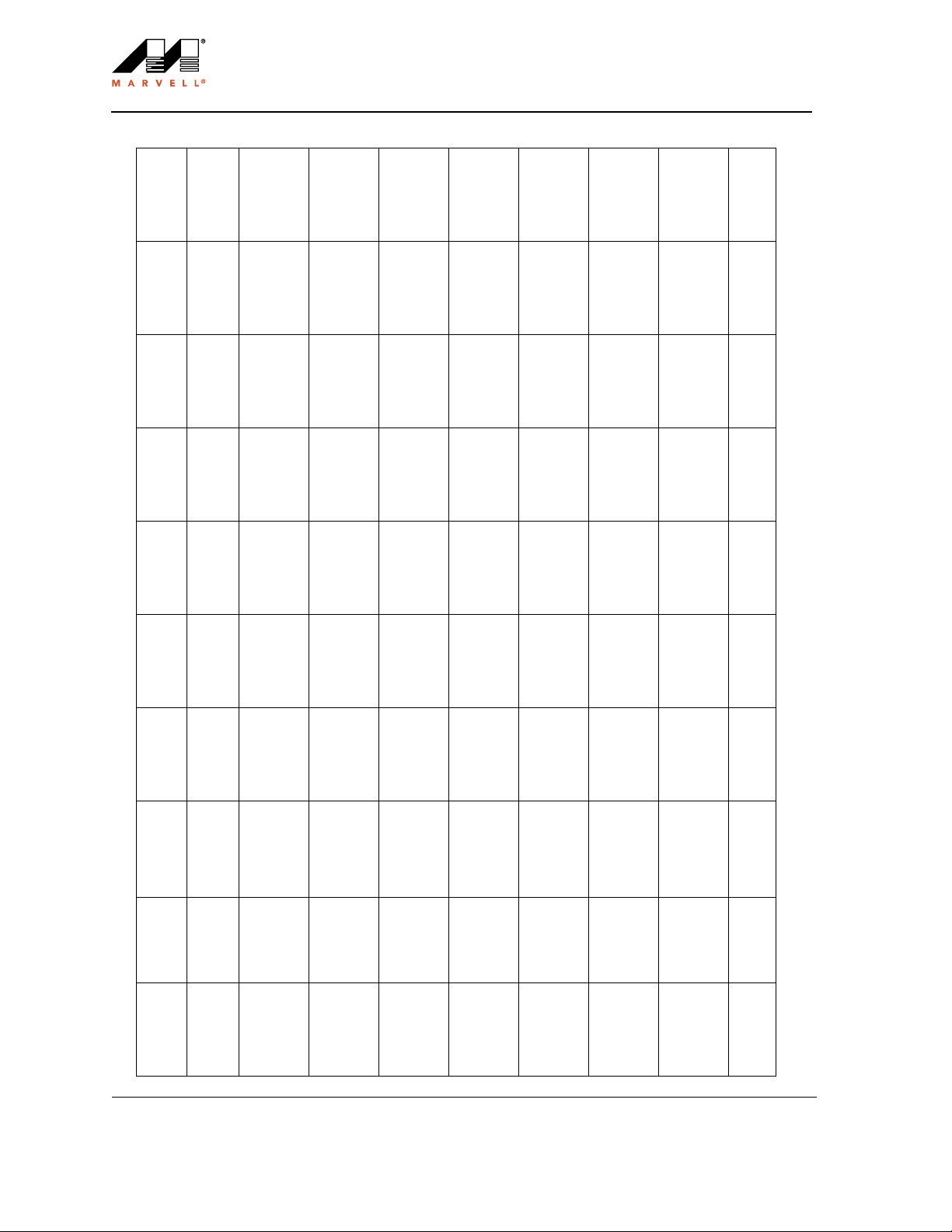

4.3 PXA300 Processors Pin List with Alternate Functions .......................................................66

4.4 PXA310 Processor Pin List with Alternate Functions .........................................................75

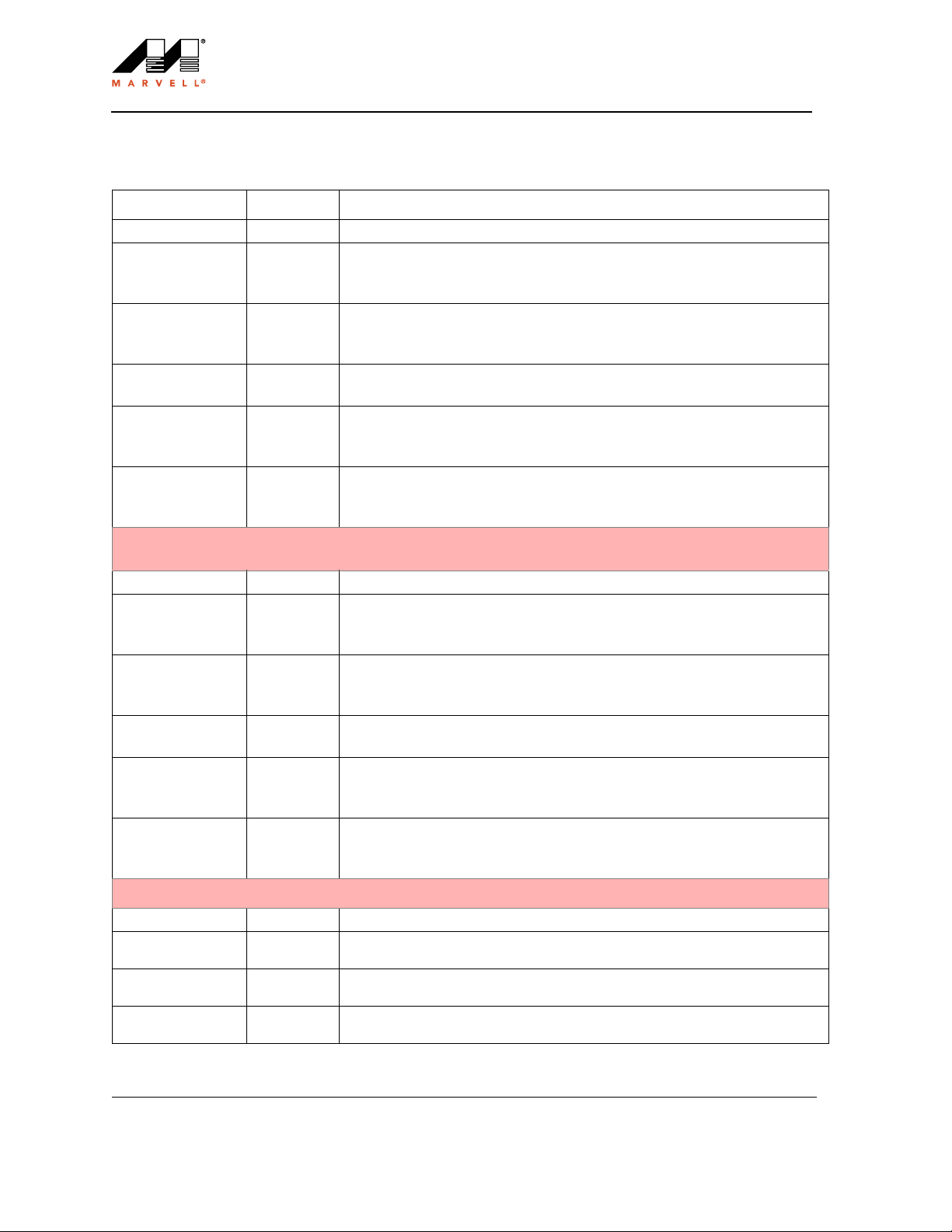

4.5 Signal Descriptions.............................................................................................................86

4.6 Pin Control Unit Overview...................................................................................................99

4.6.1 Checking for Completion of a Multi-Function Pin Operation................................100

4.6.2 Access to Nonexistent Registers or Pins.............................................................100

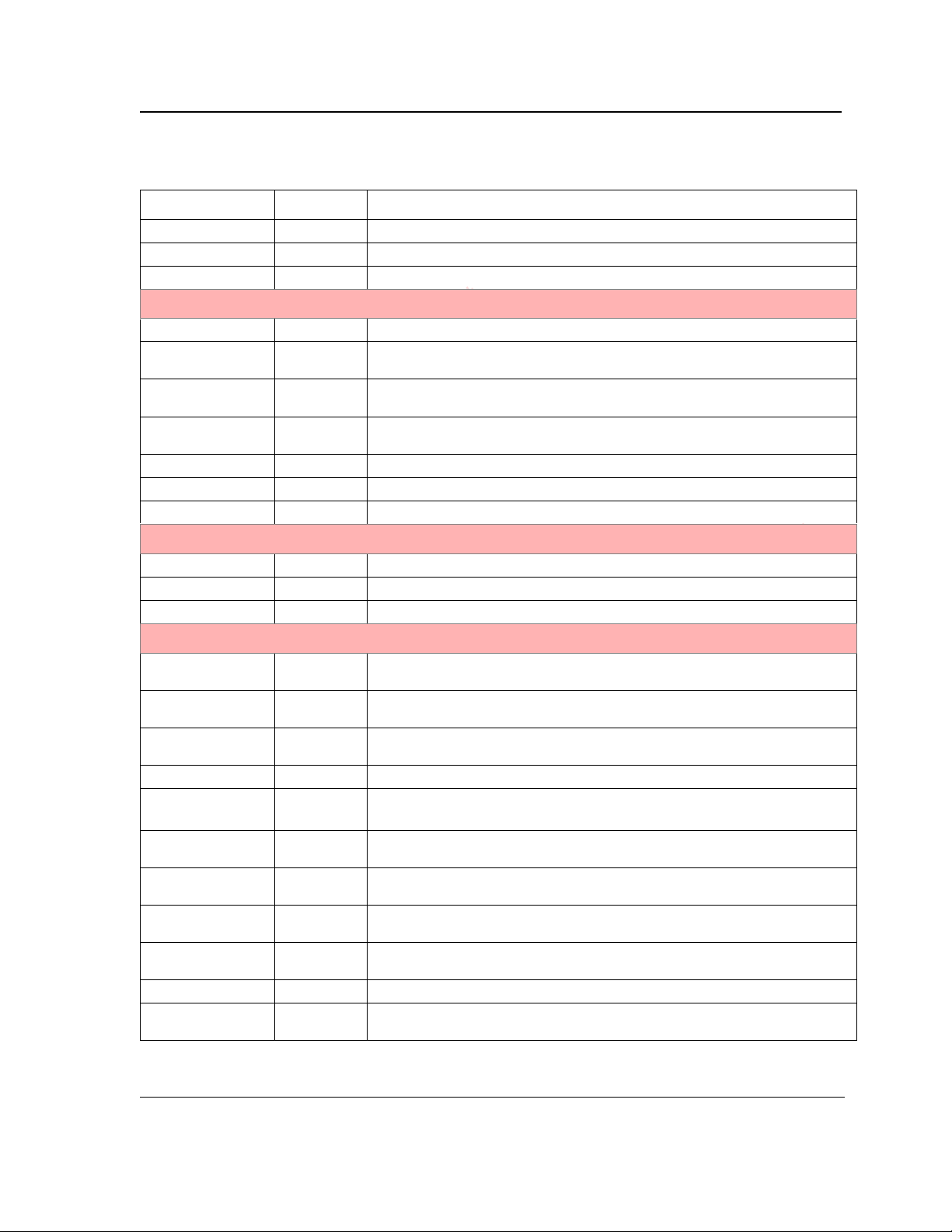

4.6.3 Pin Control Unit Address Map .............................................................................100

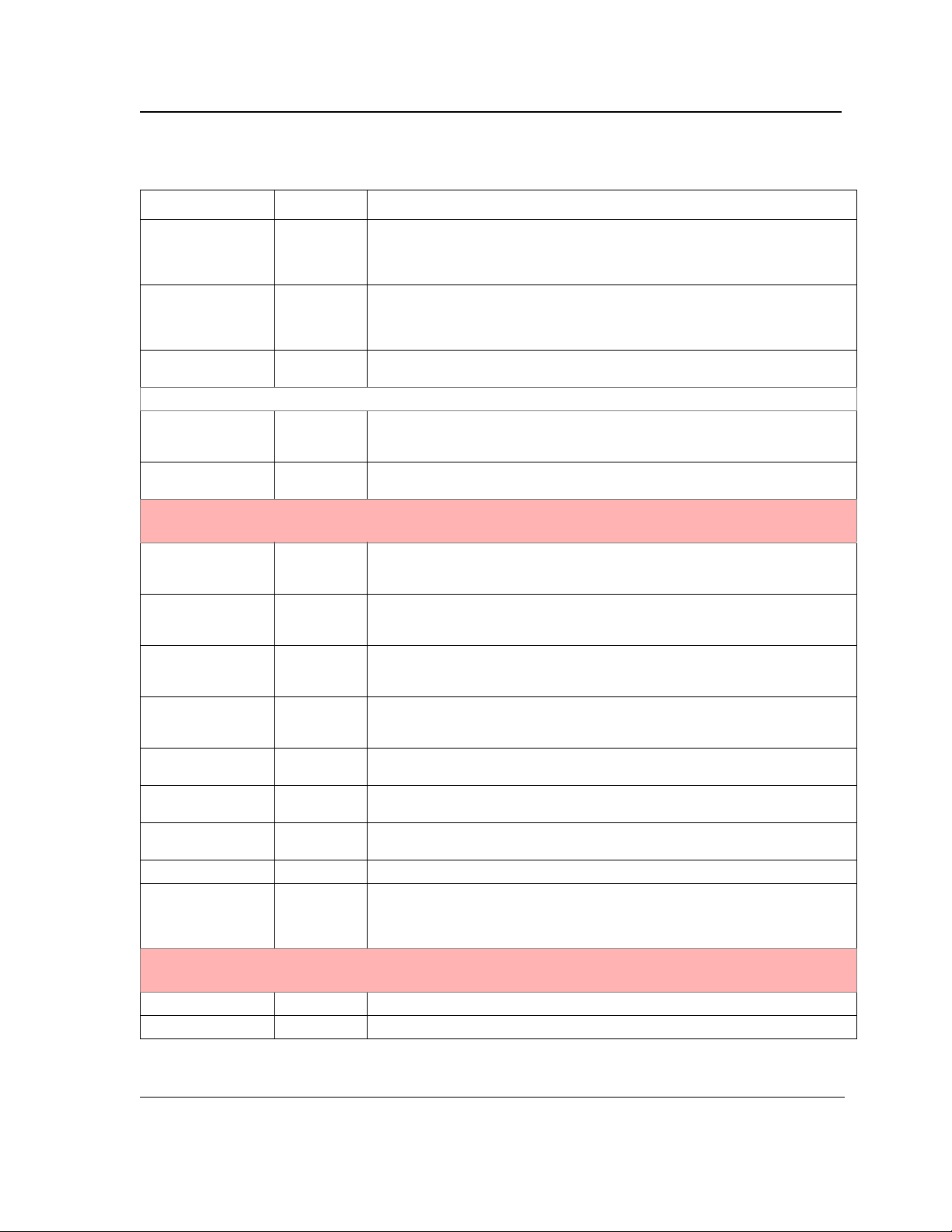

4.7 Register Descriptions........................................................................................................110

4.8 Multi-Function Pin Block Diagram.....................................................................................113

4.8.1 Example...............................................................................................................113

4.9 Edge-Detect Operation.....................................................................................................116

4.10 Low-Power Mode Operation.............................................................................................116

4.11 Wakeup Detection ............................................................................................................118

4.11.1 Services Wakeups................................ ............................................. ...... ....... .....118

4.11.2 Peripheral Controller Wakeups............................................................................118

4.11.3 Generic Wakeups ................................................................................................119

4.11.4 Wake-up Functionality on Multi-Function Pins.....................................................120

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 4

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

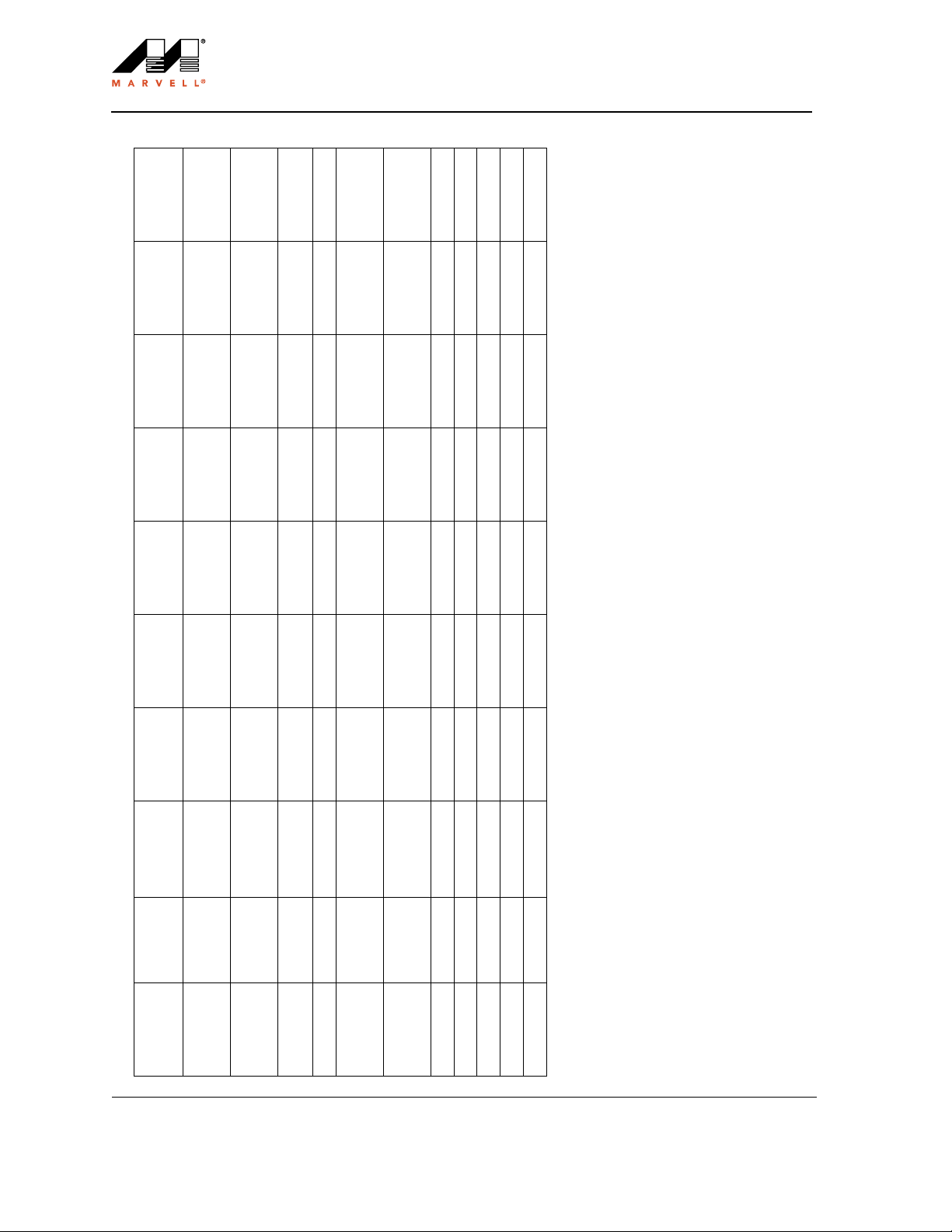

5 General-Purpose I/O Unit..........................................................................................................123

5.1 Overview...........................................................................................................................123

5.2 Features............................................................................................................................124

5.3 Register Descriptions........................................................................................................125

5.3.1 GPIO Pin-Level Registers (GPLRx).....................................................................126

5.3.2 GPIO Pin Direction Registers (GPDRx)...............................................................127

5.3.3 GPIO Pin Bit-Wise Set Direction Registers (GSDRx)..........................................128

5.3.4 GPIO Pin Bit-Wise Clear Direction Registers (GCDRx).......................................129

5.3.5 GPIO Pin Output Set Registers (GPSRx) and Pin Output Clear Registers

(GPCRx) ..............................................................................................................130

5.3.6 GPIO Rising-Edge Detect-Enable Registers (GRERx)........................................131

5.3.7 GPIO Bit-Wise Set Rising-Edge (GSRERx) and GPIO Bit-wise Clear Rising-

Edge (GCRERx) Detect-Enable Registers ..........................................................132

5.3.8 GPIO Falling-Edge Detect-Enable Registers (GFERx)........................................134

5.3.9 GPIO Bit-Wise Set Falling-Edge (GSFERx) and GPIO Bit-wise Clear Falling-

Edge (GCFERx) Detect-Enable Registers...........................................................134

5.3.10 GPIO Edge Detect Status Register (GEDRx)......................................................136

5.4 Register Summary............................................................................................................137

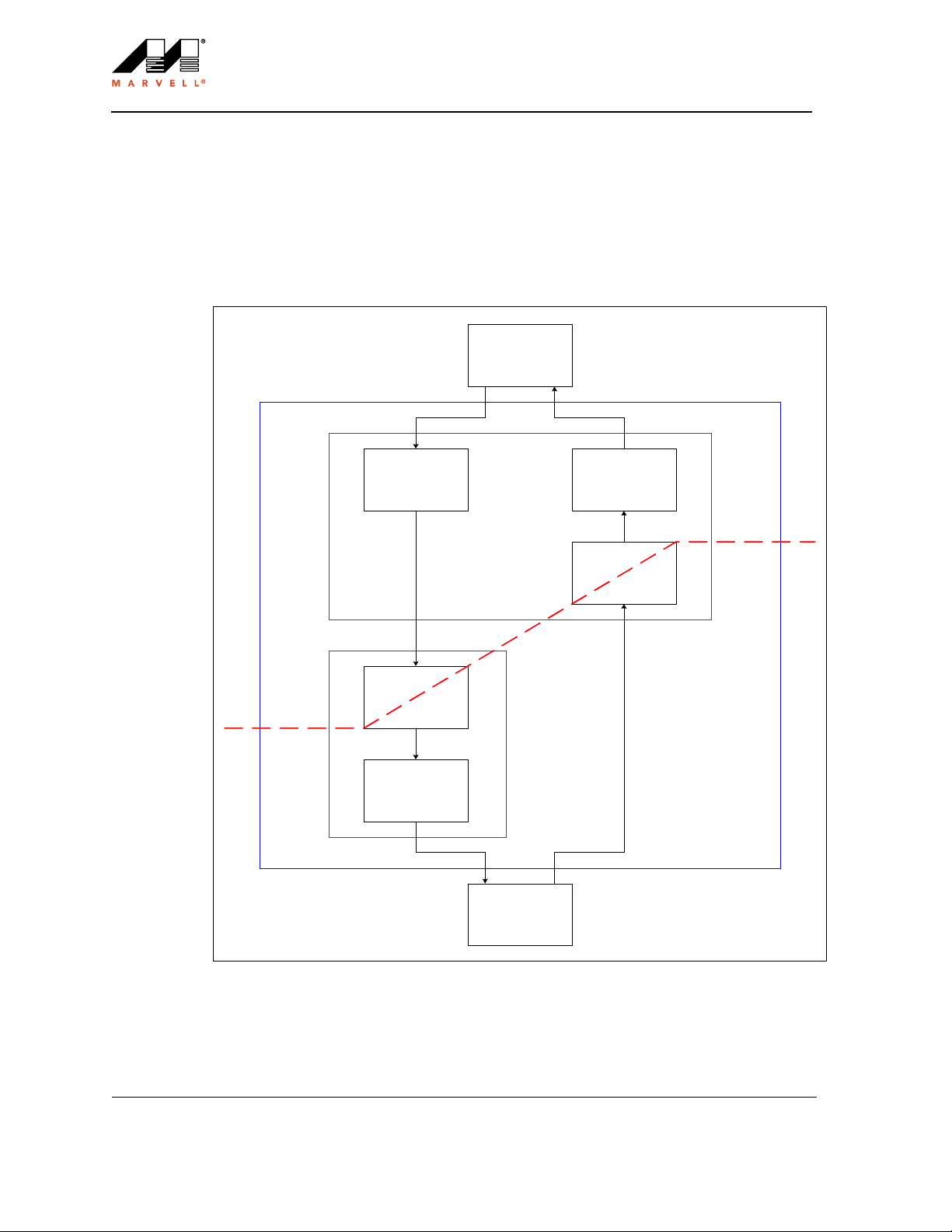

6 Services Clock Control Unit .....................................................................................................141

6.1 Overview...........................................................................................................................141

6.1.1 Differences between the PXA300 Processor and PXA310 Processor ................142

6.2 Features............................................................................................................................142

6.3 Signal Descriptions...........................................................................................................142

6.3.1 Processor Oscillator In (PXTAL_IN) and Processor Oscillator Out

(PXTAL_OUT) .....................................................................................................143

6.3.2 Timekeeping Oscillator Input (TXTAL_IN) and Timekeeping Oscillator Output ........

(TXTAL_OUT)......................................................................................................143

6.3.3 Processor Clock Output (CLK_POUT).................................................................143

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

6.3.4 Timekeeping Clock Output (CLK_TOUT) ............................................................144

6.3.5 VCTCXO Enable (VCTCXO_EN) ........................................................................144

6.4 Operation..........................................................................................................................144

6.4.1 System Clock Requirements................................................................................144

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

6.4.2 Functional Description .........................................................................................144

6.4.3 Processor Oscillator (13 MHz).............................................................................145

6.4.4 Timekeeping Oscillator (32.768 kHz)...................................................................146

6.4.5 Core Phase-Locked Loop (104–806 MHz) ..........................................................146

6.4.6 System Phase-Locked Loop (624 MHz)..............................................................146

6.4.7 Ring Oscillator (120 MHz ± 15%, 40 MHz ± 5%).................................................147

6.5 Register Descriptions........................................................................................................147

6.5.1 Oscillator Configuration Register (OSCC) ...........................................................147

6.6 Register Summary............................................................................................................149

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

7 Slave Clock Control Unit...........................................................................................................151

7.1 Overview...........................................................................................................................151

7.2 Features............................................................................................................................151

7.2.1 Functional Description .........................................................................................151

7.2.2 Core Phase-Locked Loop (104–624 MHz) ..........................................................152

7.2.3 System Phase-Locked Loop (624 MHz)..............................................................156

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 5

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

8 Services Power Management Unit...........................................................................................179

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Product Number

Developers Manual

7.2.4 Ring Oscillator (120 MHz ± 15%) .......................................................................156

7.2.5 Ring Oscillator (40 MHz ± 5%) During D1 Mode .................................................160

7.2.6 Functional Clock Gating .... ....... ...... ....... ...... ...... ....... ...... ......................................160

7.2.7 Performing Peripheral Frequency Changes ........................................................161

7.2.8 Changing PLL State.............................................................................................161

7.2.9 Core Idle Mode ....................................................................................................161

7.2.10 Core Idle Mode Coupled with Software-Controlled Voltage Changes.................162

7.3 Register Descriptions........................................................................................................162

7.3.1 Application Subsystem Clock Configuration Register (ACCR)............................163

7.3.2 Application Subsystem Clock Status Register (ACSR) .......................................169

7.3.3 Application Subsystem Interrupt Control/Status Register (AICSR) .....................172

7.3.4 D0 Mode Clock Enable Register A (D0CKEN_A)................................................173

7.3.5 D0 Mode Clock Enable Register B (D0CKEN_B)................................................174

7.3.6 AC ’97 Clock Divisor Value Register (AC97_DIV)...............................................176

7.3.7 Coprocessor 14: Clock ........................................................................................177

7.4 Register Summary............................................................................................................178

8.1 Overview...........................................................................................................................179

8.2 Differences Between the PXA300 Processor and PXA310 Processor.............................180

8.3 Features............................................................................................................................180

8.4 Signal Descriptions...........................................................................................................181

8.4.1 Hardware Reset (nRESET) .................................................................................182

8.4.2 Reset Out (nRESET_OUT)..................................................................................182

8.4.3 GPIO Reset (nGPIO_RESET)........................................................... ...... ....... .....182

8.4.4 EXT_WAKEUP<1:0>...........................................................................................183

8.4.5 Battery Fault (nBATT_FAULT) ............................................................................183

8.4.6 System Power Enable (SYS_EN)........................................................................184

8.4.7 Power Enable (PWR_EN)....................................................................................184

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

8.4.8 Power Management Unit I2C Clock (PWR_SCL)................................................184

8.4.9 Power Management Unit I2C Data (PWR_SDA)............................................ .....184

8.4.10 Power Management Unit Capacitor Pins (PWR_CAP<1:0>) ..............................184

8.4.11 Power Management Supply Output (PWR_OUT) ...............................................185

8.5 Operation..........................................................................................................................185

8.6 Reset Management Operation..........................................................................................185

8.6.1 Power-On Reset (POR).......................................................................................186

8.6.2 Hardware Reset...................................................................................................187

8.6.3 GPIO Reset ...................... ............................................. ....... ...... ....... ..................188

8.6.4 S3 Low-Power State Exit Reset...........................................................................190

8.6.5 Watchdog Reset ..................................................................................................191

8.6.6 Summary of Module Reset Sensitivity.................................................................191

8.6.7 Summary of Reset Sequences............................................................................192

8.7 Power Management Operation.........................................................................................193

8.7.1 Power Domains ...................................................................................................194

8.7.2 Processor Power Modes......................................................................................199

8.8 Voltage Management........................................................................................................213

8.8.1 Programming Restrictions for the PWR_I2C .......................................................214

8.8.2 External Voltage Regulator Requirements ..........................................................214

8.8.3 Hardware-Controlled Vol tag e-Cha nge Sequencer..............................................214

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 6

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

8.8.4 Accessing PI2C registers directly through S/W ...................................................221

8.9 Register Descriptions........................................................................................................222

8.9.1 Power Management Unit Control Register (PMCR) ............................................222

8.9.2 Power Management Unit Status Register (PSR).................................................224

8.9.3 Power Management Unit Scratch-Pad Register (PSPR).....................................225

8.9.4 Power Management Unit General Configuration Register (PCFR)......................226

8.9.5 Power Manager Wake-Up Enable Register (PWER)...........................................229

8.9.6 Power Manager Wake-Up Status Register (PWSR)............................................230

8.9.7 Power Manager EXT_WAKEUP<1:0> Control Register (PECR) ........................230

8.9.8 Power Manager Mask Event Register (PMER)....................................................232

8.9.9 Power Management Unit Voltage Change Control Register (PVCR)..................234

8.10 Register Summary............................................................................................................236

9 Slave Power Management Unit ................................................................................................237

9.1 Overview...........................................................................................................................237

9.1.1 Differences Between PXA300 Processor and PXA310 Processor......................239

9.2 Operation..........................................................................................................................239

9.2.1 Reset Management ....................................... ....... ...... ....... ...... ............................239

9.2.2 Power Management.............................................................................................241

9.2.3 nBATT_FAULT Occurrence.................................................................................256

9.2.4 Wake-Up Detection..............................................................................................256

9.2.5 Other Power Modes.............................................................................................256

9.2.6 Voltage Management...........................................................................................256

9.3 Register Descriptions........................................................................................................256

9.3.1 Application Subsystem Power Status/Configuration Register (ASCR)................257

9.3.2 Application Subsystem Reset Status Register (ARSR) .......................................258

9.3.3 Application Subsystem Wake-Up from D3 Enable Register (AD3ER).................259

9.3.4 Application Subsystem Wake-Up from D3 Status Register (AD3SR)..................261

9.3.5 Application Subsystem Wake-Up from D2 to D0 State Enable Register

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

(AD2D0ER)..........................................................................................................264

9.3.6 Application Subsystem Wake-Up from D2 to D0 Status Register (AD2D0SR)....266

9.3.7 Application Subsystem Wake-Up from D2 to D1 State Enable Register

(AD2D1ER)..........................................................................................................269

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

9.3.8 Application Subsystem Wake-Up from D2 to D1 Status Register (AD2D1SR)....269

9.3.9 Application Subsystem Wake-Up from D1 to D0 State Enable Register

(AD1D0ER)..........................................................................................................270

9.3.10 Application Subsystem Wake-Up from D1 to D0 Status Register (AD1D0SR)....273

9.3.11 Application Subsystem D3 Configuration Register (AD3R).................................276

9.3.12 Application Subsystem D2 Configuration Register (AD2R).................................277

9.3.13 Application Subsystem D1 Configuration Register (AD1R).................................278

9.3.14 Application Subsystem General Purpose Register (AGENP)..............................279

9.3.15 Core PWRMODE Register (CP14 Register 7).....................................................280

9.4 Register Summary............................................................................................................281

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

10 1-Wire Bus Master Interface .....................................................................................................283

10.1 Overview...........................................................................................................................283

10.2 Signal Descriptions...........................................................................................................284

10.3 Operation..........................................................................................................................284

10.3.1 Writing a Byte .....................................................................................................284

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 7

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

11 DMA Controller..........................................................................................................................293

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

12 Interrupt Controller....................................................................................................................347

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Product Number

Developers Manual

10.3.2 Reading a Byte ....................................................................................................284

10.3.3 I/O Signaling ........................................................................................................285

10.4 Register Descriptions........................................................................................................287

10.4.1 1-Wire Command Register (W1CMDR)...............................................................287

10.4.2 1-Wire Transmit/Receive Buf fer (W1 TRR) ........................................ ...... ....... .....289

10.4.3 1-Wire Interrupt Register (W1INTR)....................................................................289

10.4.4 1-Wire Interrupt Enable Register (W1IER) ..........................................................290

10.4.5 1-Wire Clock Divisor Register (W1CDR) .............................................................291

10.5 Register Summary............................................................................................................292

11.1 Overview...........................................................................................................................293

11.2 Features............................................................................................................................293

11.3 Operation..........................................................................................................................294

11.3.1 DMA Channels.....................................................................................................295

11.3.2 DMA Descriptors..................................................................................................297

11.3.3 Transferring Data.................................................................................................302

11.3.4 Programming Tips ...............................................................................................304

11.3.5 How DMA Handles Trailing Bytes........................................................................305

11.3.6 Quick Reference to DMA Programming ..............................................................308

11.3.7 Examples.............................................................................................................314

11.4 Register Descriptions........................................................................................................319

11.4.1 DMA Request to Channel Map Register (DRCMRx)...........................................319

11.4.2 DMA Descriptor Address Registers (DDADRx)...................................................320

11.4.3 DMA Source Address Register (DSADRx)..........................................................321

11.4.4 DMA Target Address Registers (DTADRx) .........................................................322

11.4.5 DMA Command Registers (DCMDx)...................................................................323

11.4.6 DREQ Status Register (DRQSR0) ......................................................................327

11.4.7 DMA Channel Control/Status Registers (DCSRx)...............................................328

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

11.4.8 DMA Interrupt Register (DINT)............................................................................336

11.4.9 DMA Alignment Register (DALGN)......................................................................336

11.4.10 DMA Programmed I/O Control Status Register (DPCSR)...................................337

11.5 DMA Register Summary...................................................................................................338

12.1 Overview...........................................................................................................................347

12.2 Features............................................................................................................................347

12.3 Signal Descriptions...........................................................................................................348

12.4 Operation..........................................................................................................................348

12.4.1 Accessing Interrupt Controller Registers .............................................................349

12.4.2 Enabling Coprocessor Access.............................................................................350

12.4.3 Accessing the Coprocessor.................................................................................350

12.4.4 Bit Positions and Peripheral IDs .............................. ............................................351

12.5 Register Descriptions........................................................................................................353

12.5.1 Interrupt Controller Pending Registers (ICPR and ICPR2)..................................353

12.5.2 Interrupt Controller IRQ Pending Registers (ICIP and ICIP2)..............................358

12.5.3 Interrupt Controller FIQ Pending Registers (ICFP and ICFP2)............................365

12.5.4 Interrupt Controller Mask Registers (ICMR and ICMR2) .....................................370

12.5.5 Interrupt Controller Level Registers (ICLR and ICLR2) .......................................375

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 8

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

12.5.6 Interrupt Controller Control Register (ICCR)........................................................380

12.5.7 Interrupt Priority Registers 0 to 52 ......................................................................381

12.5.8 Interrupt Control Highest Priority Register (ICHP) ...............................................382

12.6 Register Summary............................................................................................................383

13 Real-Time Cloc k (RTC)..............................................................................................................385

13.1 Overview...........................................................................................................................385

13.2 Differences Between the PXA300 Processor and PXA310 Processor.............................385

13.3 Features............................................................................................................................385

13.4 Signal Description.............................................................................................................386

13.5 Operation..........................................................................................................................386

13.5.1 Timer Module.......................................................................................................389

13.5.2 Wristwatch Module ..............................................................................................389

13.5.3 Stopwatch Module ...............................................................................................394

13.5.4 Periodic Interrupt Module.....................................................................................395

13.5.5 Trimmer Module...................................................................................................396

13.6 Register Descriptions........................................................................................................398

13.6.1 RTC Trim Register (RTTR)..................................................................................399

13.6.2 RTC Status Register (RTSR)...............................................................................400

13.6.3 RTC Alarm Register (RTAR)................................................................................402

13.6.4 Wristwatch Day Alarm Registers (RDARx)..........................................................403

13.6.5 Wristwatch Year Alarm Registers (RYARx).........................................................404

13.6.6 Stopwatch Alarm Registers (SWARx)..................................................................405

13.6.7 Periodic Interrupt Alarm Register (PIAR).............................................................405

13.6.8 RTC Counter Register (RCNR)............................................................................406

13.6.9 RTC Day Counter Register (RDCR) ....................................................................406

13.6.10 RTC Year Counter Register (RYCR) ...................................................................407

13.6.11 Stopwatch Counter Register (SWCR)..................................................................408

13.6.12 Periodic Interrupt Counter Register (RTCPICR)..................................................408

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

13.7 Register Summary............................................................................................................409

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

14 Operating System Timers.........................................................................................................411

14.1 Overview...........................................................................................................................411

14.1.1 Differences Between PXA300 Processor and PXA310 Processor .....................411

14.2 Features............................................................................................................................411

14.3 Signal Descriptions...........................................................................................................412

14.4 Operation..........................................................................................................................412

14.4.1 Block Diagram ......................................... ...... ....... ...... .........................................412

14.4.2 Compares and Matches.......................................................................................413

14.4.3 Marvell PXA25x Processor Compatibility.............................................................414

14.4.4 Timer Channels ...................................................................................................414

14.4.5 Counter Resolutions ............................................................................................414

14.4.6 External Synchronization (EXT_SYNC<1:0>)......................................................415

14.4.7 Snapshot Mode....................................................................................................416

14.4.8 Operation in Low-Power Modes ..........................................................................416

14.5 Register Descriptions........................................................................................................416

14.5.1 OS Match Control Registers (OMCRx)................................................................417

14.5.2 OS Timer Match Registers (OSMRx)...................................................................422

14.5.3 OS Timer Watchdog Match Enable Register (OWER) ........................................423

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 9

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

Product Number

Developers Manual

14.5.4 OS Timer Interrupt Enable Register (OIER) ......................... ...... ....... ...... ....... .....424

14.5.5 OS Timer Count Register 0 (OSCR0)..................................................................424

14.5.6 OS Timer Count Registers (OSCR4–OSCR11) ..................................................425

14.5.7 OS Timer Status Register (OSSR) ................................ ....... ...... ....... ...... ....... .....425

14.5.8 OS Timer Snapshot Register (OSNR)..................... ...... ....... ...... ....... ...... ....... .....426

14.6 Register Summary............................................................................................................427

15 Performance Monitoring and Debug .......................................................................................429

15.1 Overview...........................................................................................................................429

15.1.1 Differences Between the PXA300 Processor and PXA310 Processor................429

15.2 Features............................................................................................................................429

15.3 Signal Descriptions...........................................................................................................429

15.4 Operation..........................................................................................................................430

15.4.1 Performance Monitoring ......................................................................................430

15.4.2 PXA300 Processor and PXA310 Processor - Level Performance Events...........430

15.4.3 Debug Functionality.............................................................................................433

15.5 Register Definitions...........................................................................................................434

15.5.1 Event Select Registers (PML_ESL_(7-0)) ...........................................................434

15.5.2 PXA300 Processor and PXA310 Processor Debug Unit (MDU) Configuration

Registers .......................... ....... ............. ............ ............. ............. ............. ............435

15.6 Register Summary............................................................................................................438

16 System Bus Arbiters .................................................................................................................441

16.1 Overview...........................................................................................................................441

16.1.1 Differences Between PXA300 Processor or PXA310 Processor.........................441

16.2 Features............................................................................................................................441

16.3 Signal Descriptions...........................................................................................................441

16.4 Operation..........................................................................................................................441

16.4.1 Programmable Weights .......................................................................................442

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

16.4.2 Bus Parking .........................................................................................................443

16.4.3 Bus Locking .........................................................................................................443

16.4.4 System Considerations: System Bus Access Latency ........................................444

16.5 Register Descriptions........................................................................................................445

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

17 JTAG...........................................................................................................................................451

16.5.1 System Bus Arbiter Control Registers (ARB_CNTRL_1 and ARB_CNTRL_2)...445

16.6 Register Summary............................................................................................................449

17.1 Overview...........................................................................................................................451

17.1.1 Differences Between PXA300 Processor and PXA310 Processor......................451

17.2 Features............................................................................................................................452

17.3 Signal Descriptions...........................................................................................................452

17.4 Operation..........................................................................................................................452

17.4.1 TAP Controller Reset...........................................................................................452

17.4.2 Instruction Register.................. ............................................. ...... ....... ...... ............4 53

17.4.3 Test Data Registers.............................................................................................454

17.4.4 TAP Controller .....................................................................................................456

17.5 Register Descriptions........................................................................................................460

17.6 Register Summary............................................................................................................460

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 10

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

18 Memory Map...............................................................................................................................461

18.1 Overview...........................................................................................................................461

18.2 Differences Between the PXA300 Processor and PXA310 Processor.............................461

18.3 Memory-Mapped Registers Summary..............................................................................464

18.4 Boot ROM Space..............................................................................................................466

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 11

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

Product Number

Developers Manual

Figures

1-1 Block Diagram ....................................... ....... ............................................. ...... ....... ...... ..............23

2-1 Physical Address Map Decode Regions ....................................................................................51

3-1 PXA300 and PXA310 Processor Memory Switch Block Diagram ..............................................63

3-2 Memory Switch Concept.............................................................................................................64

4-1 Pad Module Output Path..........................................................................................................114

4-2 Pad Module Input Path .............................................................................................................115

5-1 General-Purpose I/O Block Diagram........................................................................................124

6-1 Power and Clock Management Top-Level Block Diagram .......................................................141

6-2 PXTAL_IN and PXTAL_OUT Connections to External Clock SourcesPXTAL_IN and PXTAL_Out

Connections to External Clock Sources ...................................................................................143

6-3 TXTAL_IN and TXTAL_OUT Connections to External Clock Sources.....................................143

8-1 MPMU and BPMU Power States..............................................................................................180

8-2 Subsystem Reset Distribution .................................................................................................186

8-3 Power Domains Connection....................................................................................................197

8-4 Services Unit Power Domains..................................................................................................198

8-5 MPMU and BPMU Power Modes.............................................................................................199

8-6 SOD Power-On Master PMU State Sequence.........................................................................201

8-7 Steps Taken by Master and Subsystem for Initial Power Up and Exit of Reset .......................202

8-8 S0 13-MHz Clock Enable Sequence ........................................................................................203

8-9 S0 Low Voltage Supply Enable Sequence...............................................................................204

9-1 Application Subsystem Power States.......................................................................................238

9-2 Application Subsystem Reset Distribution................................................................................240

9-3 BPMU Power States........... ...... ....... ...... ....... ............................................. ...... ....... ...... ............243

10-11-Wire Bus Master Block Diagram ...........................................................................................283

10-21-Wire Initialization Sequence (Reset and Presence Pulses) ..................................................285

10-31-Wire Write Slots.....................................................................................................................286

10-41-Wire Read Time Slots ...........................................................................................................287

11-1DMAC Block Diagram...............................................................................................................294

11-2DREQ Timing Requirem ents ..................................... ...... ...... ....... ...... ....... ...... ....... ...... ....... .... .295

11-3Descriptor-Fetch Transfer Channel State Diagram..................................................................299

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

11-4Flow Chart for Descriptor Branching ........................................................................................300

11-5No-Descriptor-Fetch Transfer Channel State Diagram ............................................................301

11-6Descriptor Chain for Software Implementation of Full and Empty Bits.....................................319

11-7Descriptor Behavior on End-of-Receive (EOR)........................................................................334

12-1Interrupt Controller Block Diagram ...........................................................................................349

13-1RTC Block Diagram..................................................................................................................387

13-2Operational Flow of the RTC Modules .....................................................................................388

13-3Block Diagram of Wristwatch Module.......................................................................................390

14-1Operating System Timers Block Diagram ................................................................................413

14-2Example: Reset of OSCR6 Based on Rising Edge of EXT_SYNC1 .......................................415

16-1PXA300 Proces so r or PXA310 Pr oc esso r Bl oc k Diagra m ................. ....... ...... ....... ...... ............4 45

17-1JTAG Block Diagram................................................................................................................451

17-2TAP Controller State Diagram..................................................................................................457

18-1Physical Address Map Decode Regions ..................................................................................461

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 12

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

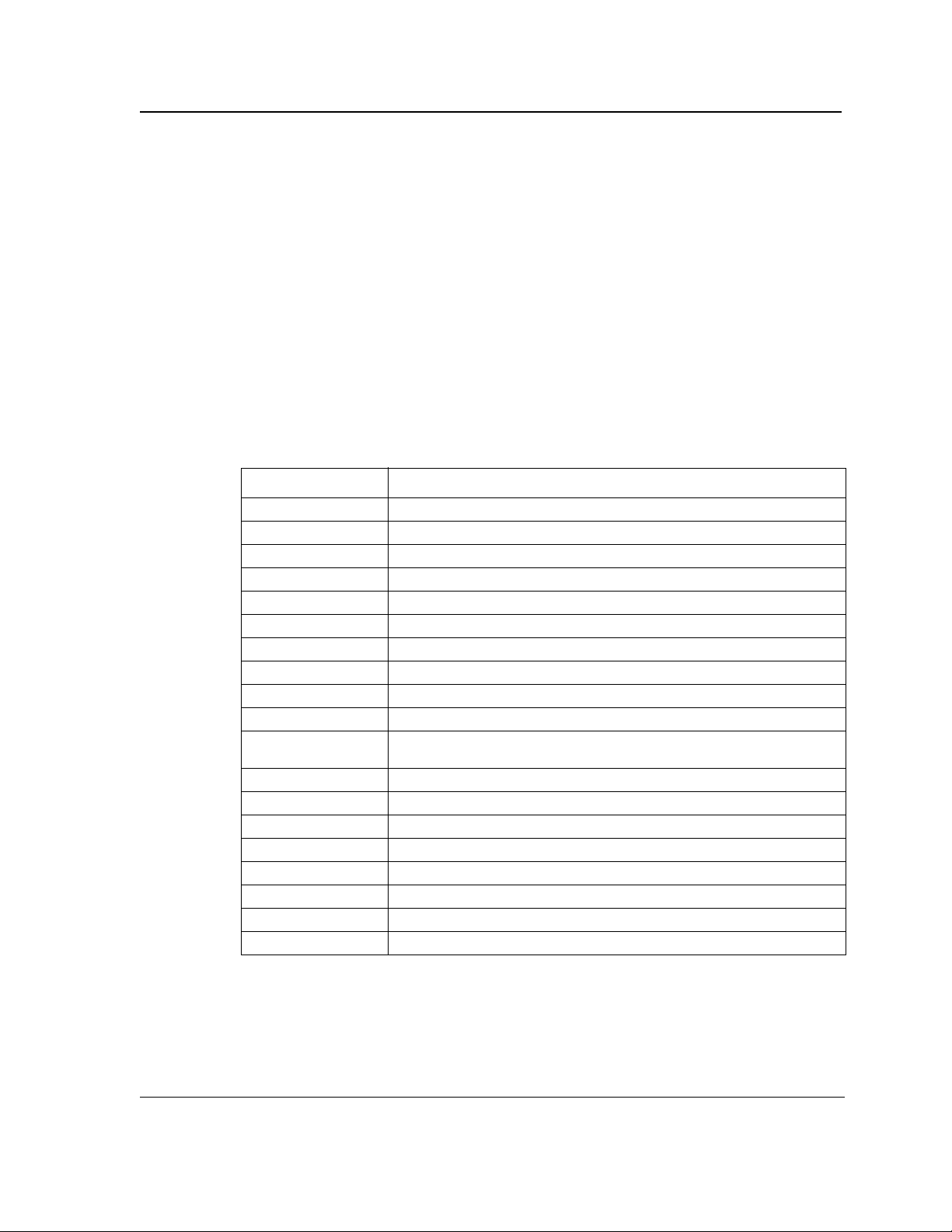

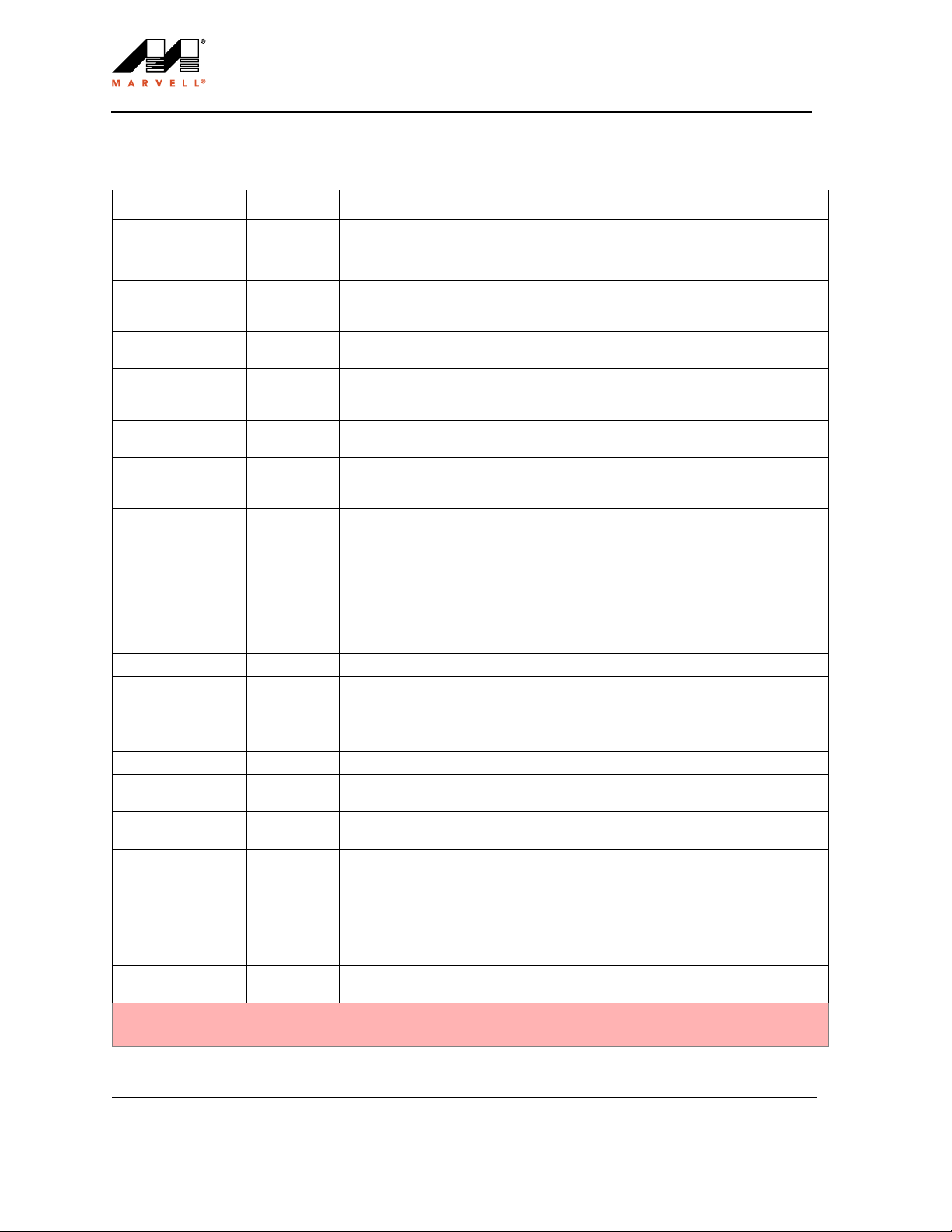

Tables

1-1 Supplemental Documentation.....................................................................................................21

2-1 Little-Endian Value Encodin g . ....... ...... ....... ............................................. ...... ....... .......................44

2-2 Effect of Each Type of Reset on Internal Register State............................................................49

2-3 Coprocessor Register Summary.................................................................................................51

2-4 Performance Monitoring Registers.............................................................................................54

2-5 Devices Operating in Ring Oscillator Mode................................................................................55

2-6 Processor ID Register............ ....... ...... ....... ...... ....... ...... ...... ....... ...... ....... ...... ..............................56

2-7 Coprocessor: New CPU ID and JTAG ID Values .......................................................................57

2-8 Processor CPAR Register ..... ....... ...... ............................................. ....... ...... ....... ...... ....... ..........58

4-1 PXA300 Processors Alternate Function Table ...........................................................................66

4-2 PXA310 Processor Alternate Function Table.............................................................................75

4-3 PXA300 Processors Signal Descriptions....................................................................................86

4-4 PXA300 Processor Pad Control Addresses .............................................................................101

4-5 PXA310 Processor Pad Control Addresses .............................................................................105

4-6 MFPR Bit Definitions........ ...... ............................................. ....... ...... .........................................111

4-7 Low-Power Mode States...........................................................................................................116

4-8 SLEEP_SEL and RDH Multi-function Pin State Summary.......................................................117

4-9 Peripheral Controller Wake Ups...............................................................................................118

4-10Generic Wakeups.....................................................................................................................120

5-1 GPIO Controller Interface Signals Summary............................................................................125

5-2 GPLR Bit Definitions.................................................................................................................127

5-3 GPDR Bit Definitions ................................................................................................................128

5-4 GSDR Bit Definitions ................................................................................................................129

5-5 GCDR Bit Definitions ................................................................................................................130

5-6 GPSR Bit Definitions.................................................................................................................131

5-7 GPCR Bit Definitions ................................................................................................................131

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

5-8 GRERx Bit Definitions...............................................................................................................132

5-9 GSRERx Bit Definitions ............................................................................................................133

5-10GCRERx Bit Definitions............................................................................................................133

5-11GFERx Bit Definiti ons......................... ....... ............................................. ...... ....... ...... ...............134

5-12GSFER Bit Definitio ns ..... ...... ............................................. ....... ...... ................................. ........135

5-13GCFER Bit Definitions..............................................................................................................136

5-14GEDR Bit Definitions ................................................................................................................137

5-15GPIO Register Summary..........................................................................................................137

6-1 Clock Manager Pin Definitions..................................................................................................142

6-2 Primary System Clocks and Frequencies.................................................................................145

6-3 OSCC Bit Definitions ................................................................................................................148

6-4 Services Unit Clock Control Unit Register Summary................................................................149

7-1 Primary Processor System Clocks and Frequencies................................................................152

7-2 Core PLL, Turbo and Run Mode Output Frequencies..............................................................153

7-3 Intel XScale® Core PLL, Turbo and Run Mode Output Frequencies.......................................153

7-4 Devices Operating in D0CS Mode............................................................................................157

7-5 D1 Frequencies from Ring Oscillator........................................................................................160

7-6 ACCR Bit Definitions........ ...... ....... ...... ....... ...... ....... ...... ...... ....... ...... .........................................165

7-7 ACSR Bit Update Events..........................................................................................................169

7-8 ACSR Bit Definitions.................................................................................................................170

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 13

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

Product Number

Developers Manual

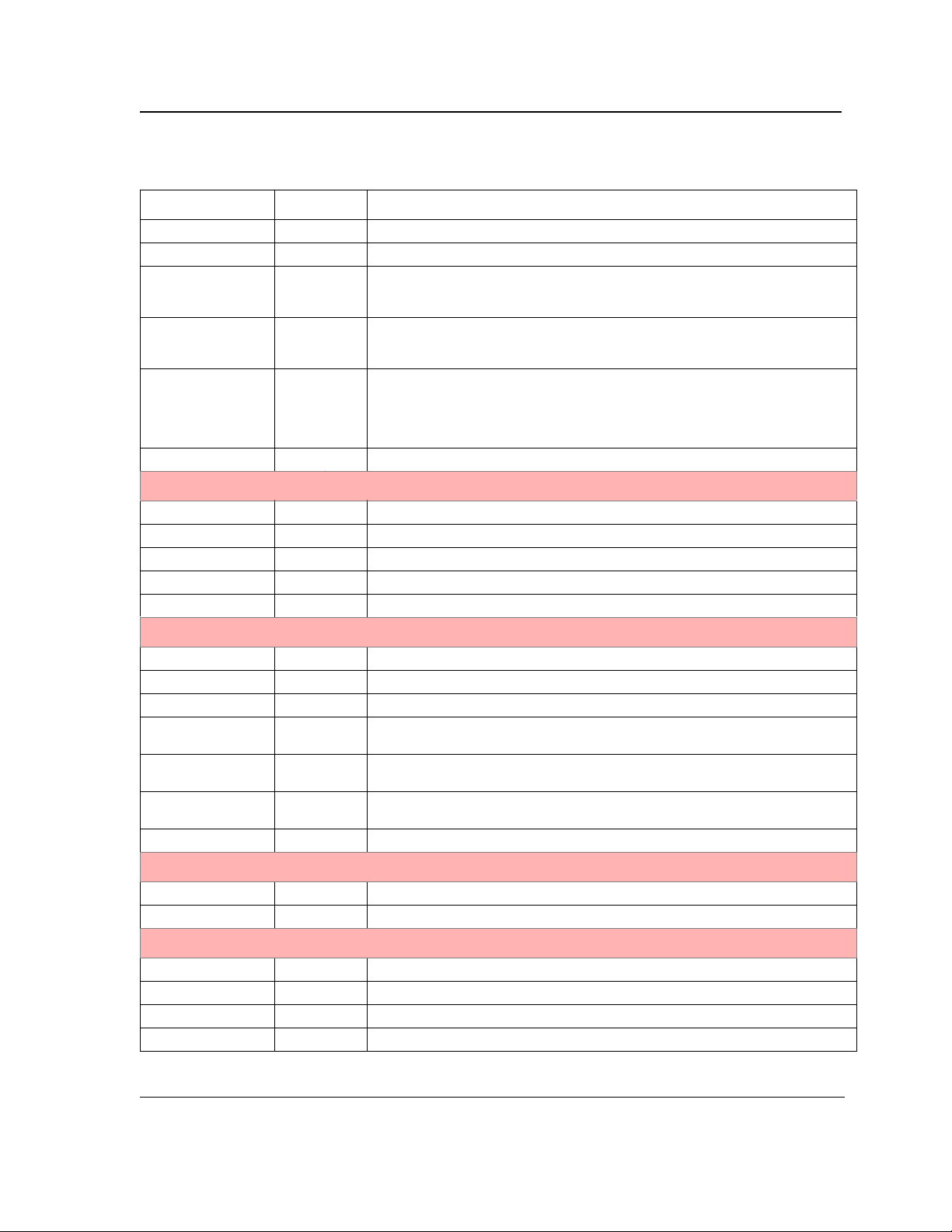

7-9 AICSR Bit Definitions................................................................................................................172

7-10D0CKEN_A Bit Definitions: Clock Enable Mappings for Units .................................................173

7-11D0CKEN_A: Clock Enable Mappings for CKEN Bits................................................................173

7-12D0CKEN_B Bit Definitions: Clock Enable Mappings for Units .................................................174

7-13D0CKEN_B: Clock Enable Mappings for CKEN Bits................................................................175

7-14Low-Speed I/O Clock Clustering .............................................................................................176

7-15AC97_DIV Bit Definitions..........................................................................................................177

7-16XCLKCFG Bit Definitions..........................................................................................................178

7-17Clocks Register Summary........................................................................................................178

7-18Clocks Register Summary........................................................................................................178

7-18IAS Revision Changes..............................................................................................................178

7-18DM Revision Changes..............................................................................................................178

8-1 Power Management Unit Pin Definitions..................................................................................181

8-2 Summary of Module Reset Functions ......................................................................................191

8-3 Summary of Subsystem Dx States...........................................................................................194

8-4 Internal Power Domains ..........................................................................................................195

8-5 External Power Supplies ..........................................................................................................195

8-6 PMCR Bit Definitions................................................................................................................222

8-7 PSR Bit Definitions ...................................................................................................................224

8-8 PSPR Bit Definitions.................................................................................................................226

8-9 PCFR Bit Definitions.................................................................................................................227

8-10PWER Bit Definitions................................................................................................................229

8-11PWSR Bit Definitions................................................................................................................230

8-12PECR Bit Definitions.................................................................................................................231

8-13PMER Bit Definitio ns ................ ....... ............................................. ...... ....... ...............................234

8-14PVCR Bit Definitions.................................................................................................................235

8-15Power Management Unit Register Summary ...........................................................................236

9-1 Summary of Application Subsystem Dx States ........................................................................238

9-2 ..................................................................................................................................................242

9-3 ASCR Bit Definitions.................................................................................................................257

9-4 ARSR Bit Definitions.................................................................................................................259

9-5 AD3ER Bit Definitions .. ....... ...... ....... ...... ....... ...... ............................................. ....... ...... .... ........260

9-6 AD3SR Bit Definitions .. ....... ...... ....... ...... ....... ...... ............................................. ....... ...... .... ........262

9-7 AD2D0ER Bit Definitions ..........................................................................................................264

9-8 AD2D0SR Bit Definitions ..........................................................................................................267

9-9 AD2D1ER Bit Definitions ..........................................................................................................269

9-10AD2D1SR Bit Definitions..........................................................................................................270

9-11AD1D0ER Bit Definitions..........................................................................................................271

9-12AD1D0SR Bit Definitions..........................................................................................................274

9-13AD3R Bit Definitions.................................................................................................................277

9-14AD2R Bit Definitions.................................................................................................................277

9-15AD1R Bit Definitions.................................................................................................................278

9-16AGENP Bit Definitio ns .................................. ...... ....... ...... ...... ....... ...... ....... ...............................279

9-17PWRMODE Bit Definitions .......................................................................................................281

9-18Processor Power Management Unit Register Summary - Physical Addresses .......................281

9-19Processor Power Management Unit Register Summary - Coprocessor Address ....................282

10-11-Wire Signal Descriptions .......................................................................................................284

10-2W1CMDR Bit Definitions ..........................................................................................................288

10-3W1TRR Bit Definitions..............................................................................................................289

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

MARVELL CONFIDENTIAL, UNDER NDA# 12101050

Copyright © 12/13/06 Marvell

December 13, 2006 Document Classification: Proprietary Information Page 14

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

Not approved by Document Control. For review only.

CONFIDENTIAL

Doc. No. MV-TBD-00 Rev. A

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact * UNDER NDA# 12101050

69rlq62d-f714peg4 * Memec (Headquarters) - Unique Tech, Insight, Impact

MARVELL CONFIDENTIAL - UNAUTHORIZED DISTRIBUTION OR USE STRICTLY PROHIBITED

10-4W1INTR Bit Definitions.............................................................................................................289

10-5W1IER Bit Definitions ...............................................................................................................291

10-6W1CDR Bit Definitions..............................................................................................................292

10-71-Wire Bus Register Summary .................................................................................................292