Service

H

6960

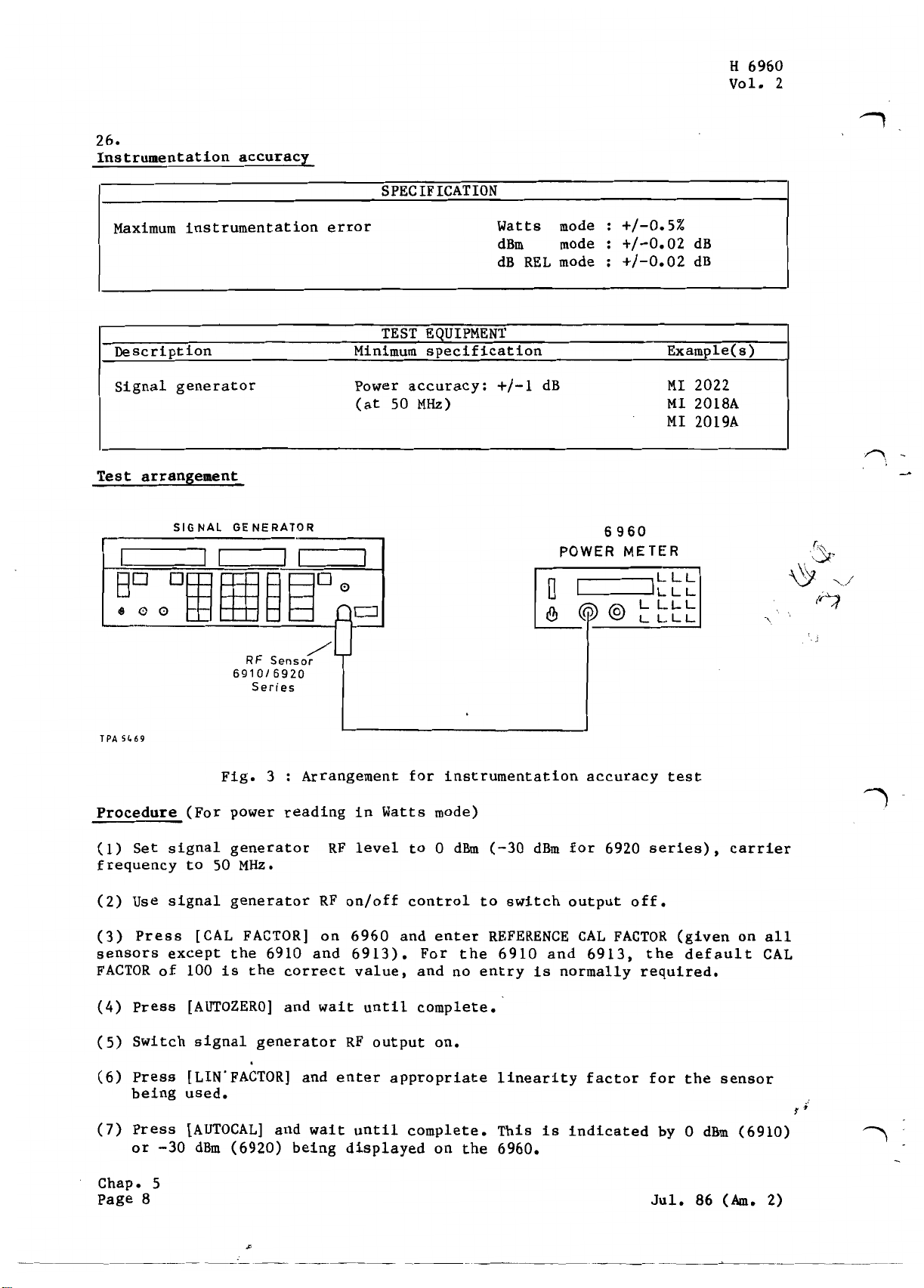

Vol.

2

Manual

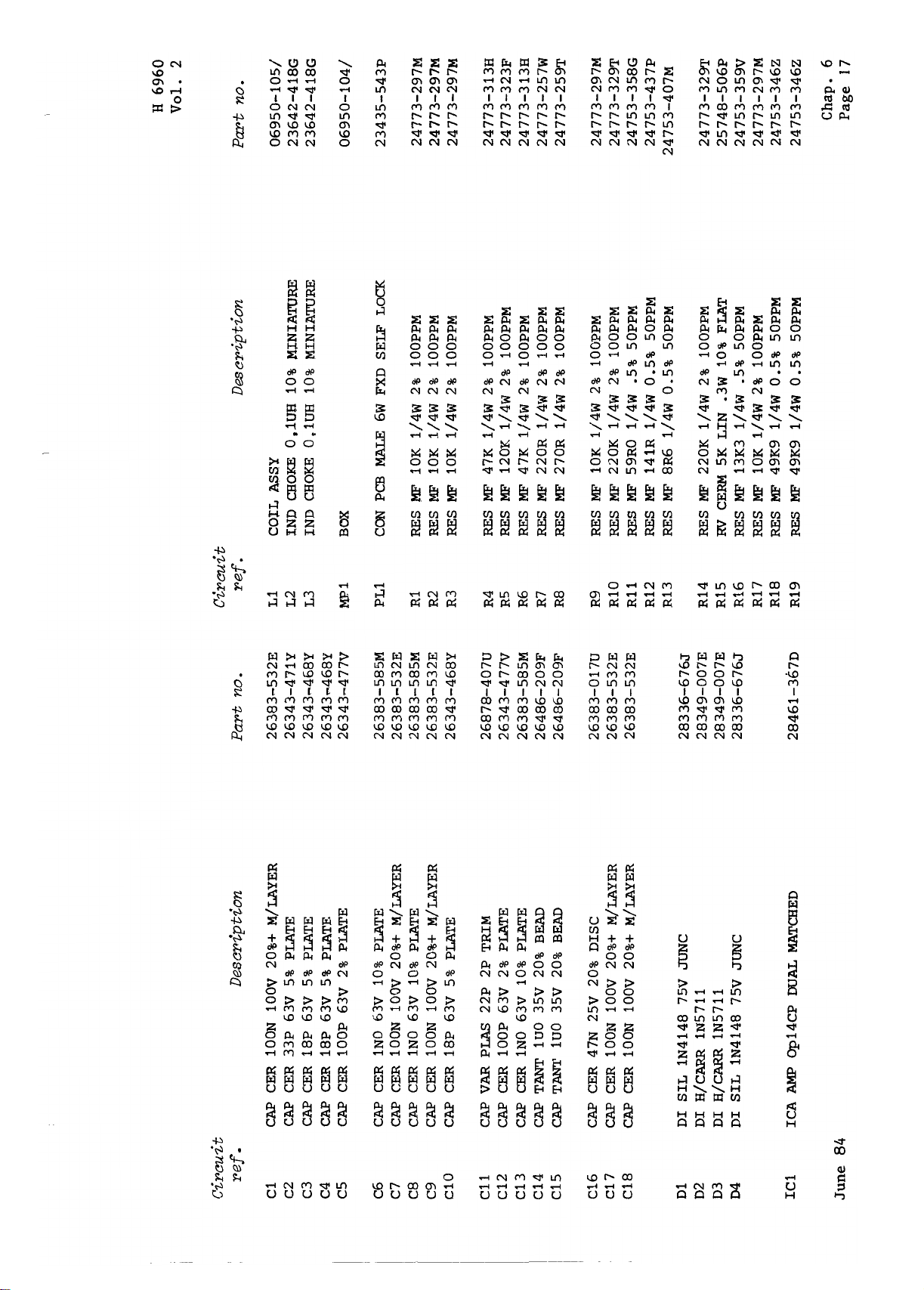

AMENDMENT

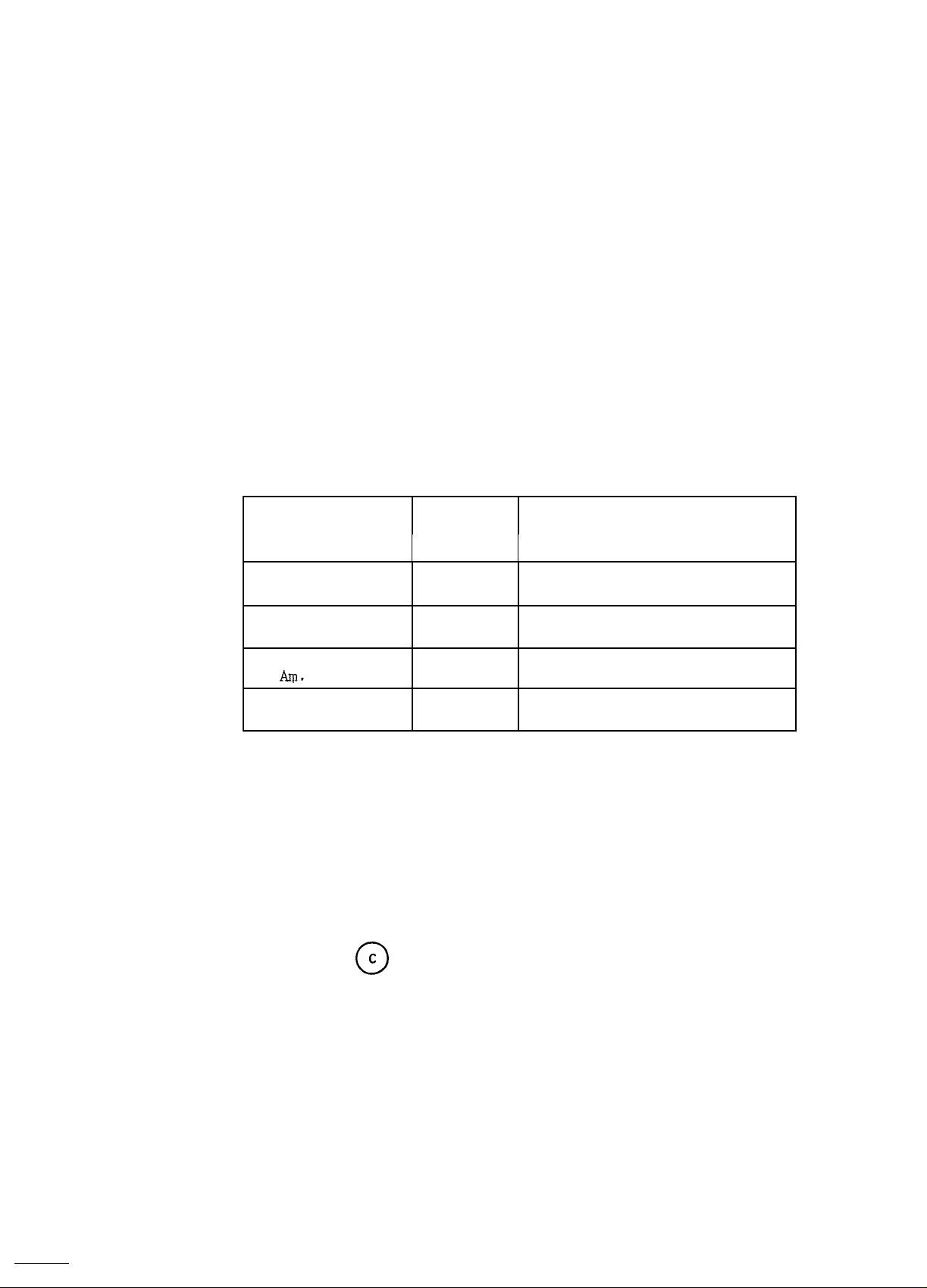

The

RECORD

following

Amendment

No.

Am.

Am.

Am.

Including

amendments

1

2

3

4

RF

Option

Power Meter

6960

3964-650

are

incorporated

Date

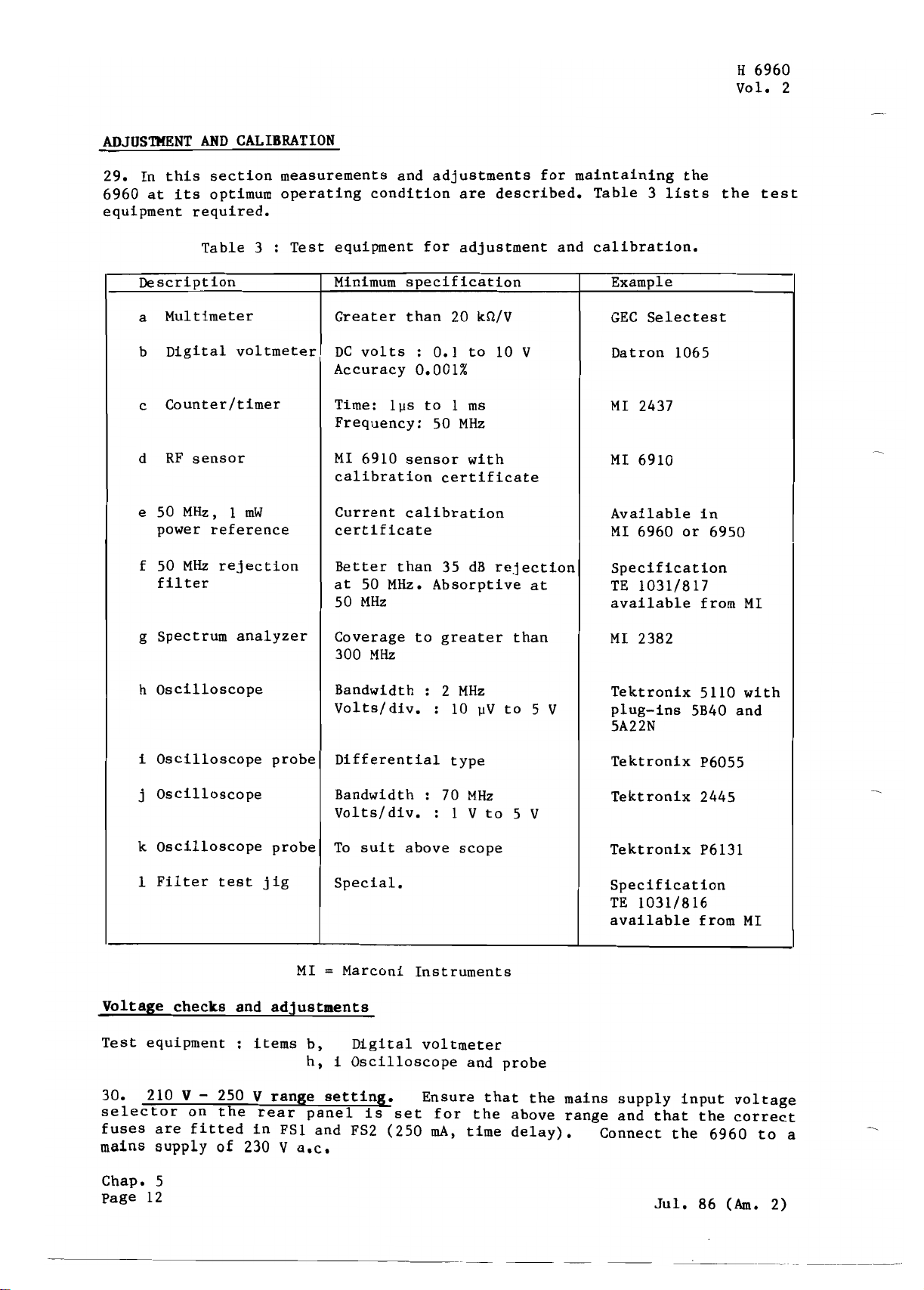

Mar. 85

July

86

87

Apr.

Nov.

87

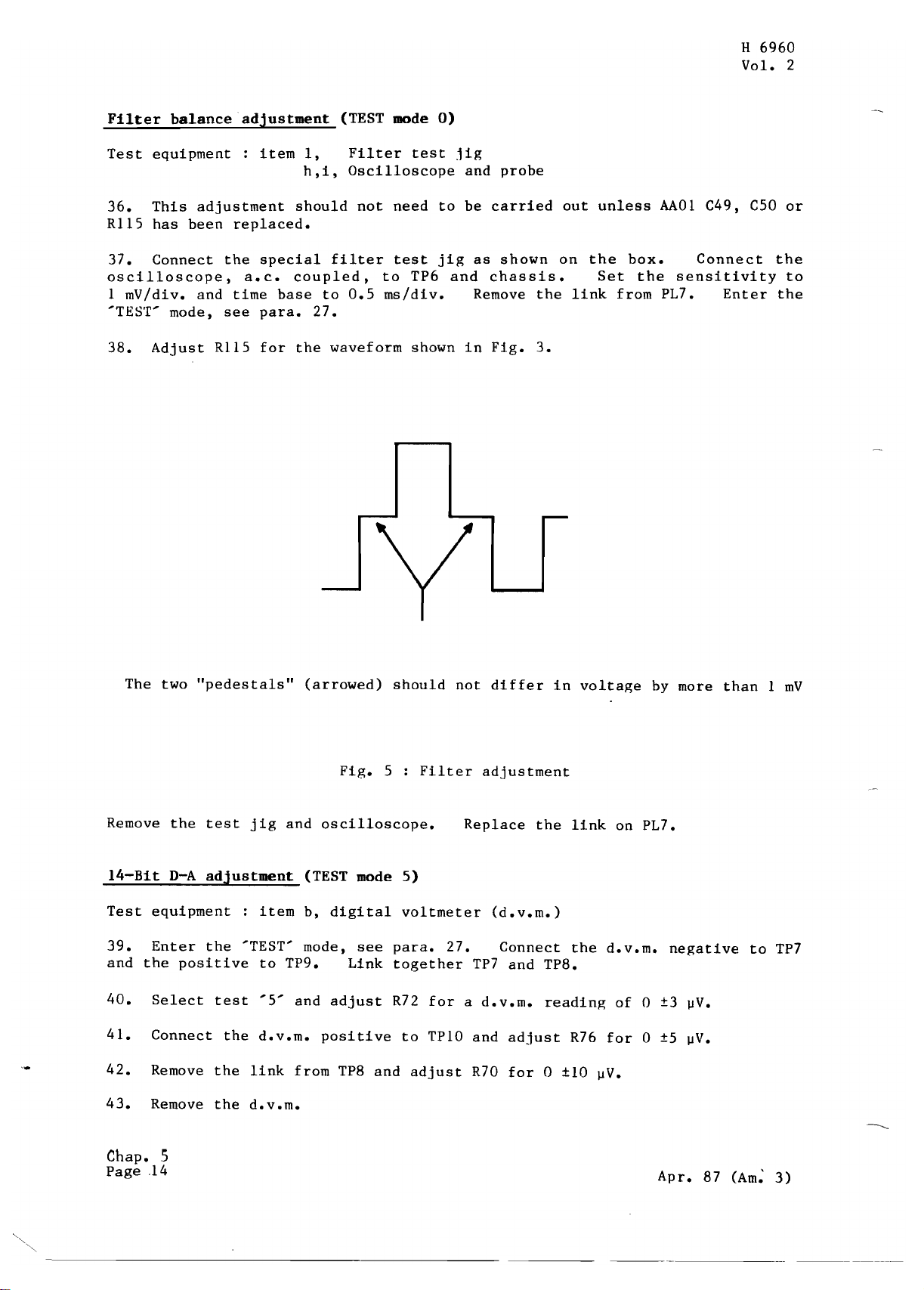

(GPIB

in

Issued

Interface)

this

manual.

serial

at

518

1069

1570

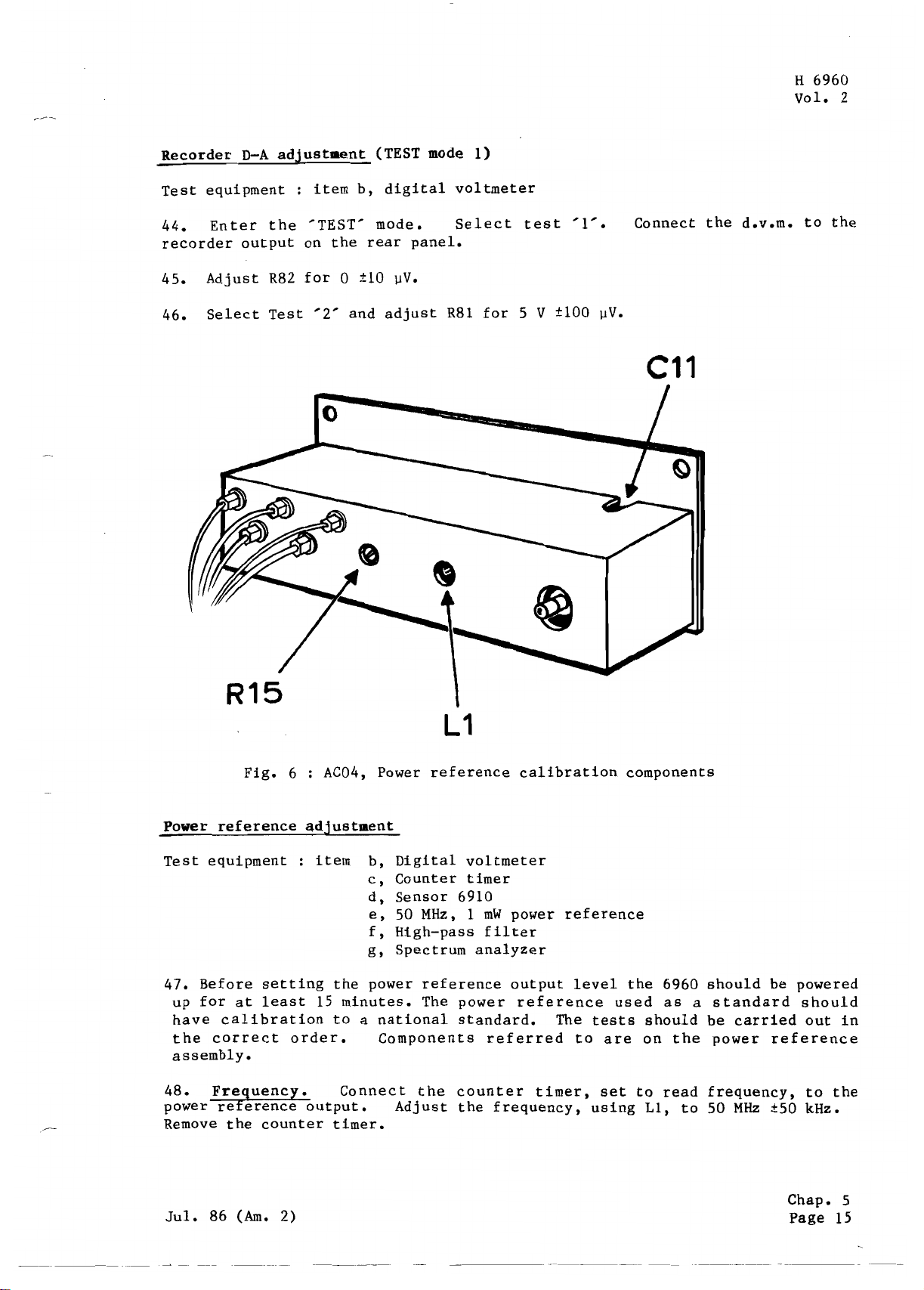

1820

no.:

Nov. 87

(Am.

4)

MARCONI

Print

Part

INSTRUMENTS

Printed in the

code:

D-11

no,

46881-553L

/87,

LTD.

UK

MI

1984

3c

Page

(i)

CONTENTS

H 6960

Vol.

2

PRELIMINARI

CHAPTERS

HAZARD

WARNING

The

Title

Contents

Notes

I

2

3-1

3-2

4

5

6

7

following

page

and

General

Ins talla

Operation

Applications

Technical

Maintenance

Replaceable

Servicing

ES

Cautions

inforniation

tion

description

parts

diagrams

SYMBOLS

symbols

Static

appear

Type

on

of

hazard

sensitive

These

separate

}

the

device

chapters

Operat1ng

equipment

contained

Manual

Reference

Vol.

2,

Page

in

Vol.

(iv)

in

a

I.

Note

...

Each

page

and

date

amended

amendment

show

amendment

coded

the

triangles

Cl,

bears

of

the

material

is

indicated

extent

do

not

state

C2

etc.

Supply

the

date

latest

of

technical

of

the

appear.

of

the

voltage

of

the

amendment

importance

by

triangles

change.

Any

manual

are

original

(Am.

positioned

When a chapter

changes

included

issue

I,

Am.

introduced

subsequent

Vol.

2

on

2,

or

the

etc.).

thus

is

reissued

to

inserted

Page

code

by

the

New

the

•

f

latest

sheets

(iii)

number

or

latest

to

the

Page

(ii)

June

84

H 6960

Vol.

2

ELECTRICAL

This

has

been

Requirements

safe

condition.

ensure

Defects

result

equipment

operation.

precautions

parts.

out

equipment

voltage

aware

safe

Whenever

of

Removal

any

of

SAFETY

equipment

designed

operation

and

abnormal

damage

shall

of

covers

have

The

adjustment,

shall

is

inevitable

the

hazard

is

and

for

Electronic

The

it

is

likely

caused

be

made

of

the

covers

been

equipment

replacement

be

opened.

involved.

NOTES

AND

PRECAUTIONS

protected

tested

following

and

to

stresses

that

by

severe

inoperative

is

taken

shall

it

shall

Measuring

in

according

precautions

retain

protection

conditions

likely

in

the

be

disconnected

or

If

any

only

accordance

and

design

maintenance

adjustment,

be

CAUTIONS

with

to

IEC

Publication

Apparatus',

the

to

carried

must

equipment

has

be

secured

expose

of

be

been

of

transport

live

the

equipment

from

and

maintenance

out

IEC

Safety

and

has

observed

in a safe

impaired,

against

parts

the

supply

repair

by a

skilled

Class

348,

been

or

although

during

'Safety

supplied

by

condition.

for

storage,

any

unintended

to

shield

before

or

repair

person

1.

the

user

example

reasonable

such

carrying

which

in

to

the

the

under

who

It

as

a

a

is

Note

equipment

work

be

gether

Mains

protective

use

equipment

Primary

nectors,

connecting

continuous

inside

discharged;

The

of

the

protective

Note

the

supply

the

equipment

To

the L (live)

plug

an

provide

that

has

been

the

mains

earth

extension

dangerous.

fuses

that

lead.

could

and

filter

plug)

rating

capacitors

disconnected

equipment,

to

discharge

and N

plug

shall

contact.

lead

conductor

there

protection

is a supply

If

only

remain

where

should

not

exceeding 6 A.

inside

capacitors

(neutral)

only

The

without

inside

one

at

against

fitted,

be

used

from

mains

be

protective

protective

or

fuse

of

supply

in

the

equipment

the

connected

filter

pins

inserted

outside

in

these

potential.

breakdown

an

external

the

live

supply.

capacitors,

of

the

in a socket

action

conductor.

the

both

fuses

the

should

of

supply

lead.

may

still

Before

to

high

if

mains

equipment

the

plug.

shall

live

rupture,

supply

fuse

The

be

carrying

voltage

fitted,

outlet

not

Any

is

and

neutral

lead,

(e.g.

fuse

charged

out

points

short

provided

be

negated

interruption

likely

certain

should

to

wires

its

fitted

when

any

with

by

make

parts

con-

in

have

the

should

to-

a

the

of

the

of

of

the

a

June

84

Page

(Hi)

sure

specified

short-circuiting

type

that

only fuses with the required

are

used

for

replacement.

of

fuse

holders

shall

be

avoided.

The

rated

use

of

current

mended

and

fuses

H 6960

Vol.

of the

and

the

2

CAUTION:

Components

parts

is

bearing

to

or

(I)

(2)

STATIC SENSITIVE

identified

lists

also

prevent

fast

If a printed

cated

stored

If a static

following

A work

Metallic

A

An

operator,

are

indicated

the

same

these

surges.

by a

warning

in a conductive

anti-static

bench

tools

low-voltage

earthed

wrist

whose

static

in

symbol.

components

board

sensitive

with

with

sensitive

the

containing

disc

an

earthed

earthed

strap

outer

COMPONENTS

the

symbol on

devices.

equipment

Certain

being

or

plastic

component

equipment

earthed

either

soldering

and a

clothing

by

handling

permanently

static

flag)

bag.

conductive

permanently

conductive

must

orange

is

is

to

must

iron.

the

The

discs,

precautions

damaged by

sensitive

removed,

be

removed

be

used.

surface.

or

earthed

not

be

circuit

presence

flags

components

it

must

or

by

repeated

seat

of

man-made

diagrams

of

such

or

labels

must

be

static

be

temporarily

replaced

cover

fibre.

and/or

devices

observed

charges

(as

indi-

the

discharges.

for

the

(3)

As a general

sitive

ducting

(4)

If

programmable

WARNING: HANDLING

This

endeavour

be

WARNING

equipment

taken,

Lithium:

stances

in

normal

exposed

circuit

show

the

an

authorized

:

TOX

Many

of

and

other

Appropriate

these

items.

component.

using a freezer

has

particularly

A

lithium

must

waste.

electrical

occurring

nature

I C

HAZARD

the

chemicals

precaution,

mount

until

ICs

HAZARDS

is

formed

been

made

battery

any

lithium

They must

connections

during

of

the

toxic

electronic

precautions

waste

which

When

it

is

aerosol

as

this

may

from

metal

to

remove

when

servicing

is

battery

be

transit.

hazard

contractor.

components

give

should

avoid

handling

used

and

touching

required

in

fault

affect

pressings

sharp

in

be

crushed,

separately

adequately

They must

then

used

off

toxic

therefore

a new

for

finding,

their

points

the

equipment,

this

insulated

disposed

in

this

fumes

be

the

leads

one,

leave

use.

take

contents.

and

although

and

edges,

equipment.

incinerated

and

securely

be

clearly

of

in a safe

equipment

on

incineration.

taken

in

of a static

it

in

care

not

every

care

to

avoid

Under no

or

disposed

packed

to

avoid a short

identified

employ

the

disposal

sen-

its

con-

to

spray

should

minor

manner by

circum-

and

resins

cuts.

of

any

to

of

Page

(iv)

Mar. 85

(Am.

1)

H 6960

Vol.

2

Para.

I

Overall

6

Detailed

6

Analogue

47

51

70 Keyboard

72

80

Table

1

Attenuator

2

Sensor

3

PPI

Power

Processor

GPIB

Software

port

circuit

technical

p.c.b.

reference

p.c.b.

and

interface

description

control

Zener

voltages

allocations

TECHNICAL

description

description

display

module

...

CONTENTS

p.c.b.

Chapter

4

DESCRIPTION

Page

4

6

16

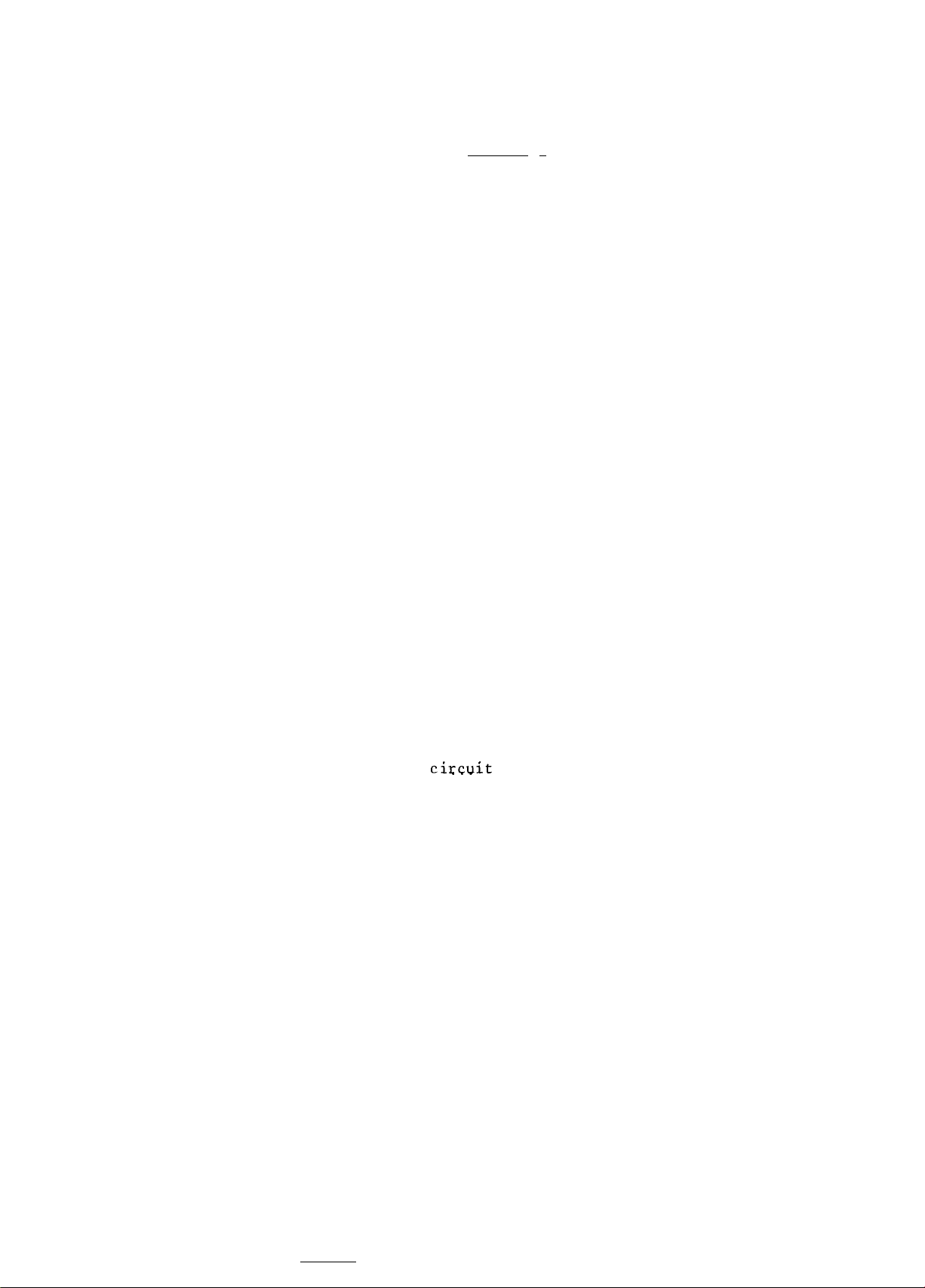

Fig.

1

RF

Power

2

First

Spike

3

Overall

4

7543

5

6

Step-up

Step-down

7

8

Machine

9

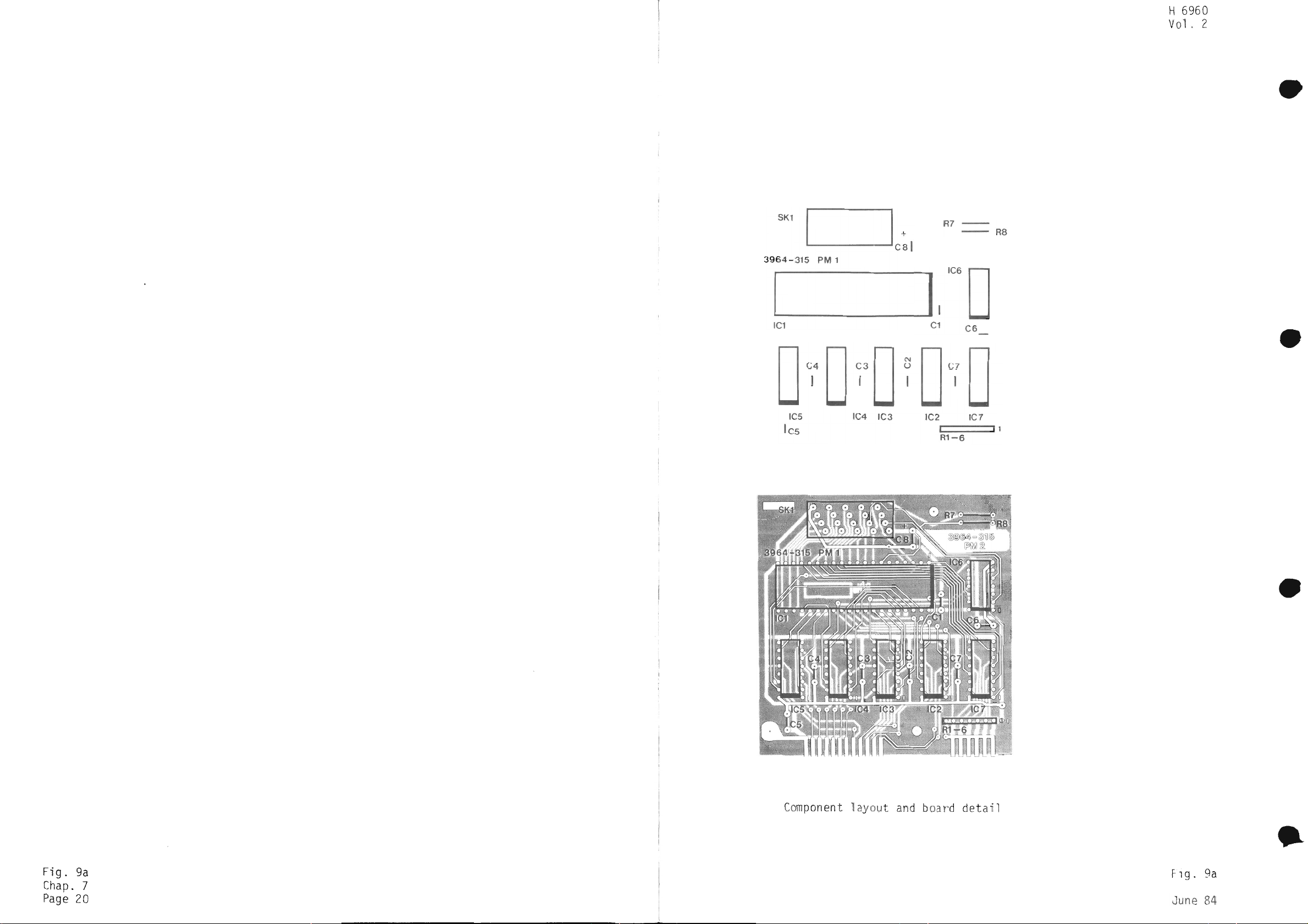

Memory

10

Simplified

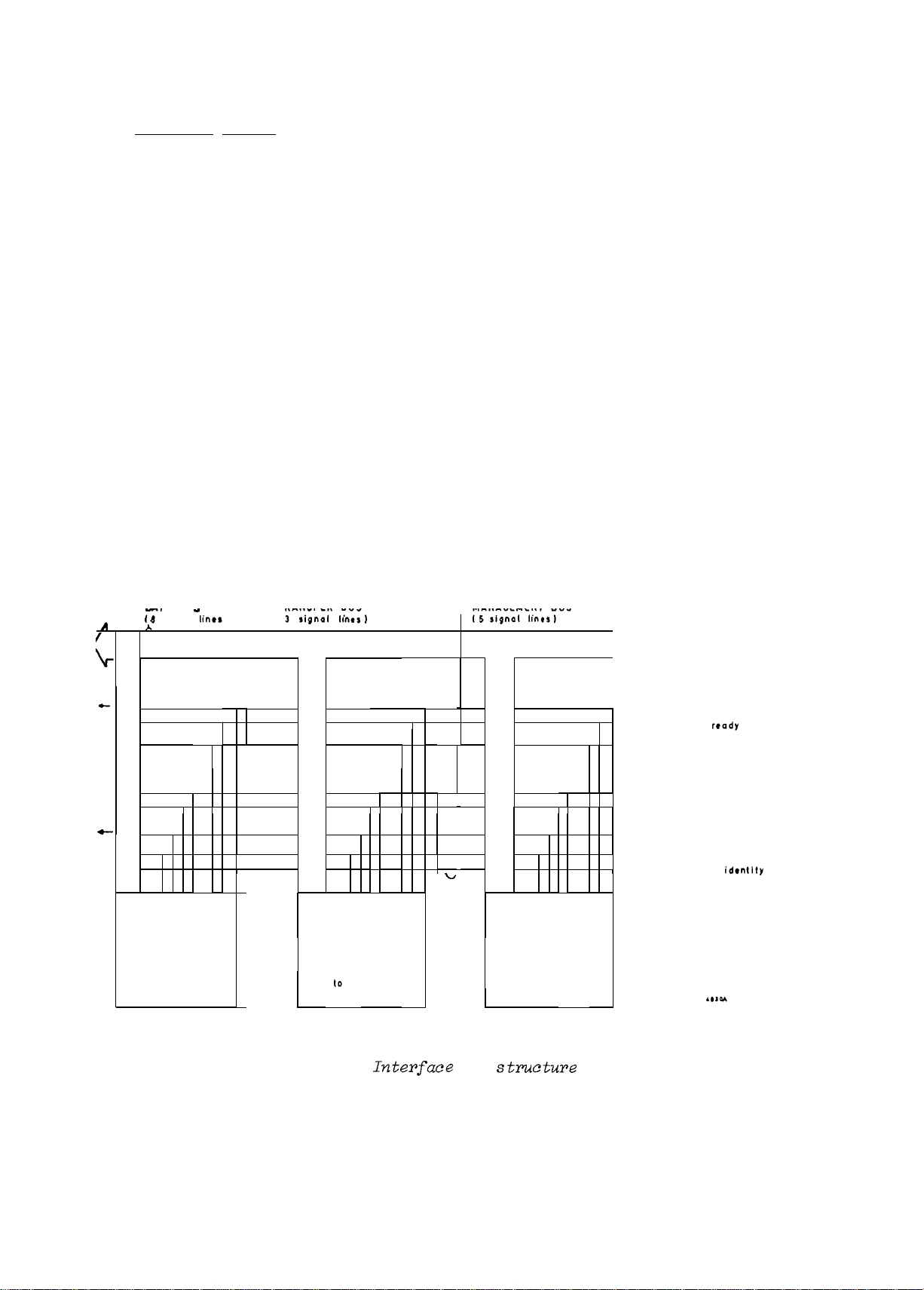

Interface

11

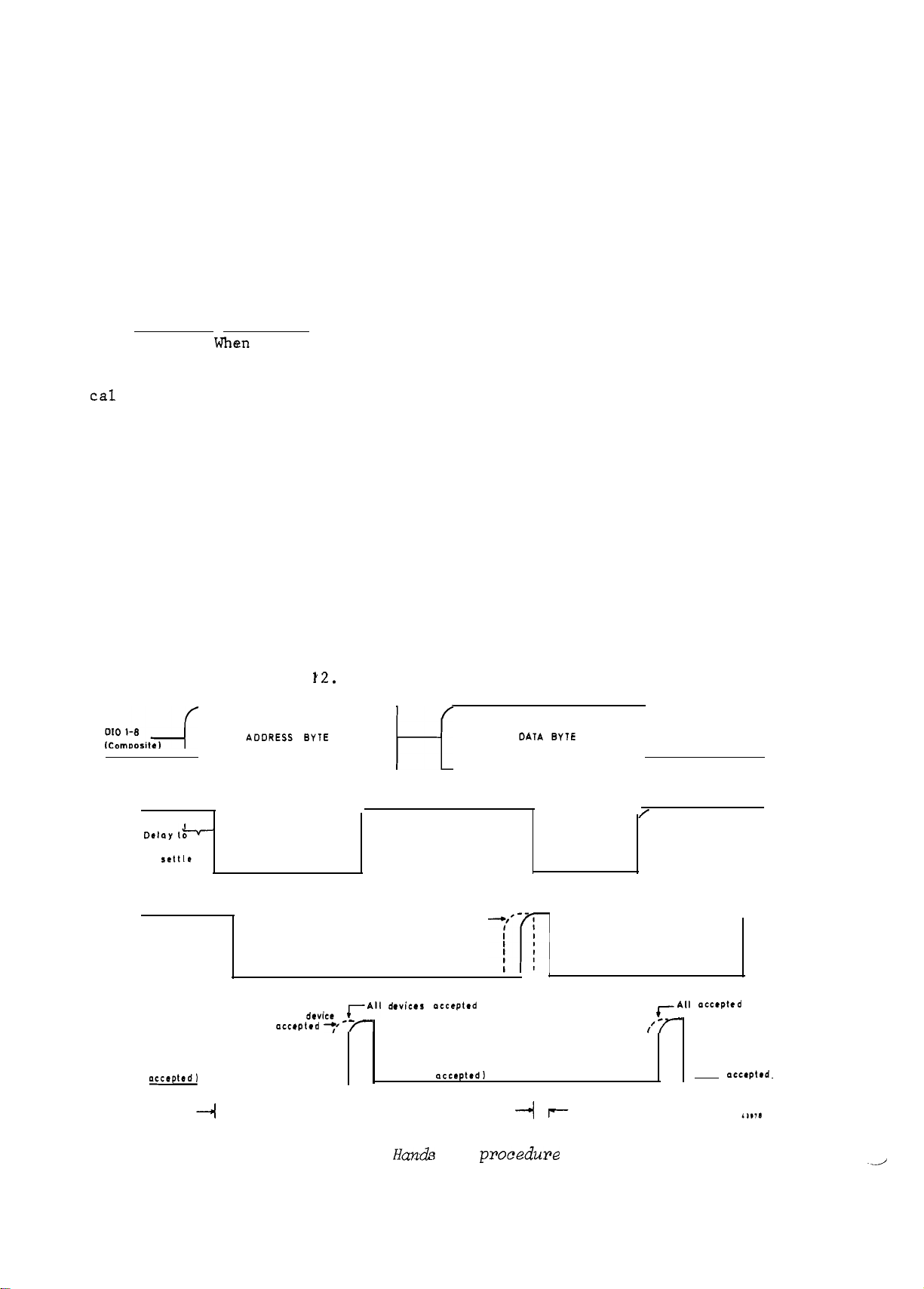

Handshake

12

OVERALL

1. a Refer

low

d.c.

an

a.c.

signal

to

be

used.

2.

The

parts,

power

removes

chopper.

The

attenuator

and

together

the

meter.

signal

3rd

amplifiers

spikes

Meter

amplifier

blanking

timing

Serial

voltage

voltage

cycle : Wait

decoding

reset

bus

procedure

CIRCUIT

to

the

voltage

by

chopped

first

The

on

The

following

is

then

controls

with

the

6960

block

D-A

regulator

regulator

state

control

structure

..

DESCRIPTION

6960

block

when power

the

signal

signal

part

being

signal

the

edges

fed

to

the

provide

gain

D-A,

is

fed

is

buffer

the

gain

the

diagram

chopper

in

then

of

of

provides

diagram

..

and

is

applied.

to

the

the

passed

the

also

1st

attenuator

the

rest

Fetch

shown

enabling

first

r.f.

sensor

square

corrects

amplifier

of

the

fine

instruction

in

Fig.

This

high

amplifier

package

to

the

spike

wave

signal

for

which,

strip

required

adjustment

1.

d.c.

gain,

sensor

together

in

gain.

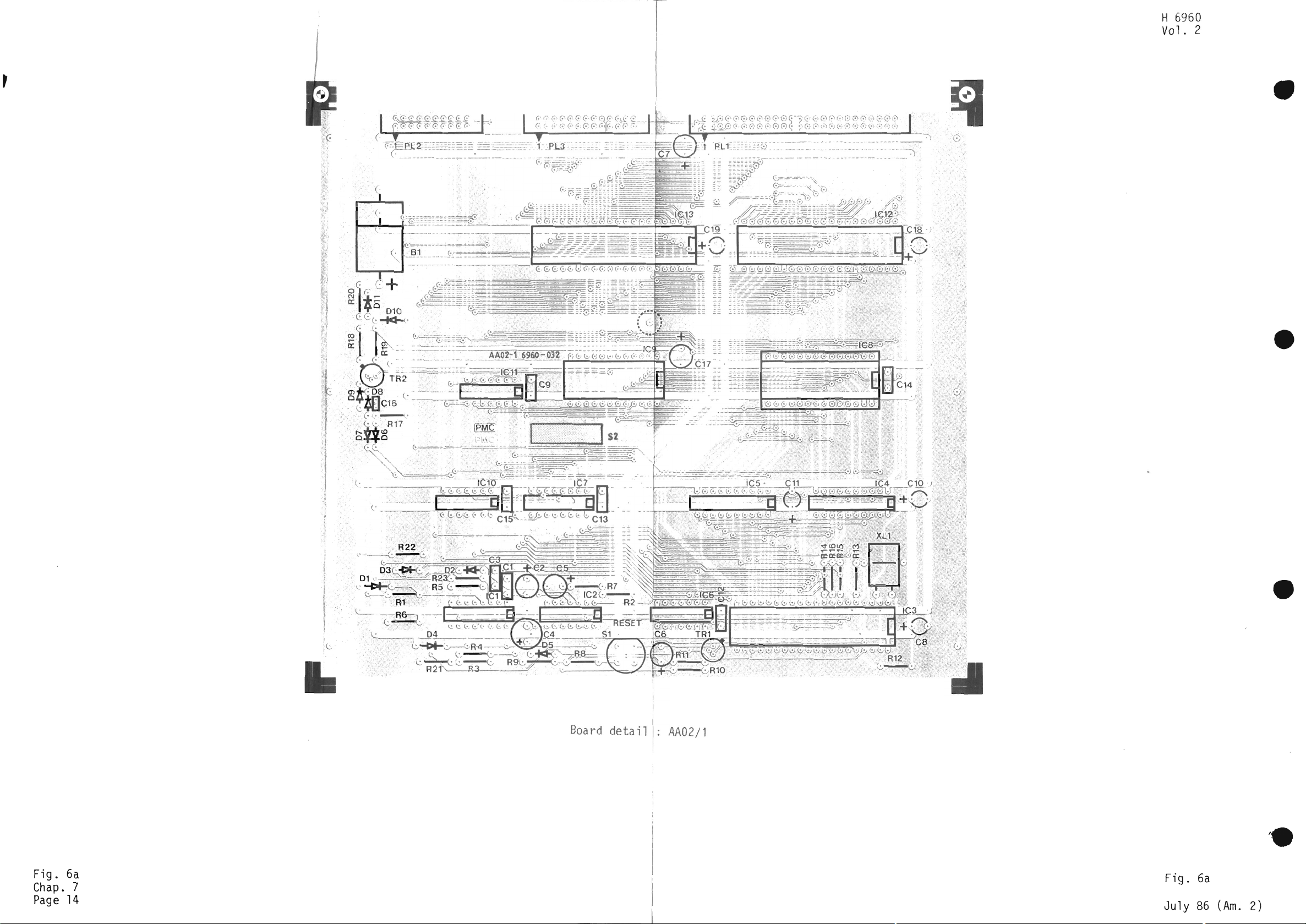

(AAOZ)

The

r.f.

signal

low

which

blanking

produced

of

is

and

the

non-linearities.

10

dB

The

the

a.c.

sensor

is

converted

noise

split

other

circuit

by

witb

steps.

4th

gain.

gi

amplifiers

into

in

the

which

the

signal

the

2nd

The 2nd

amplifier,

2

3

4

7

8

9

10

12

14

15

18

20

ves

to

two

June

84

Chap.

Page

4

1

H 6960

Vol.

2

3.

The

phase

signal.

detector

to

the

4.

Data

Outputs

D-A,

GPIB

taken

5.

are

peaking

The

microprocessor

storage

from

the

recorder

interface

from

Power

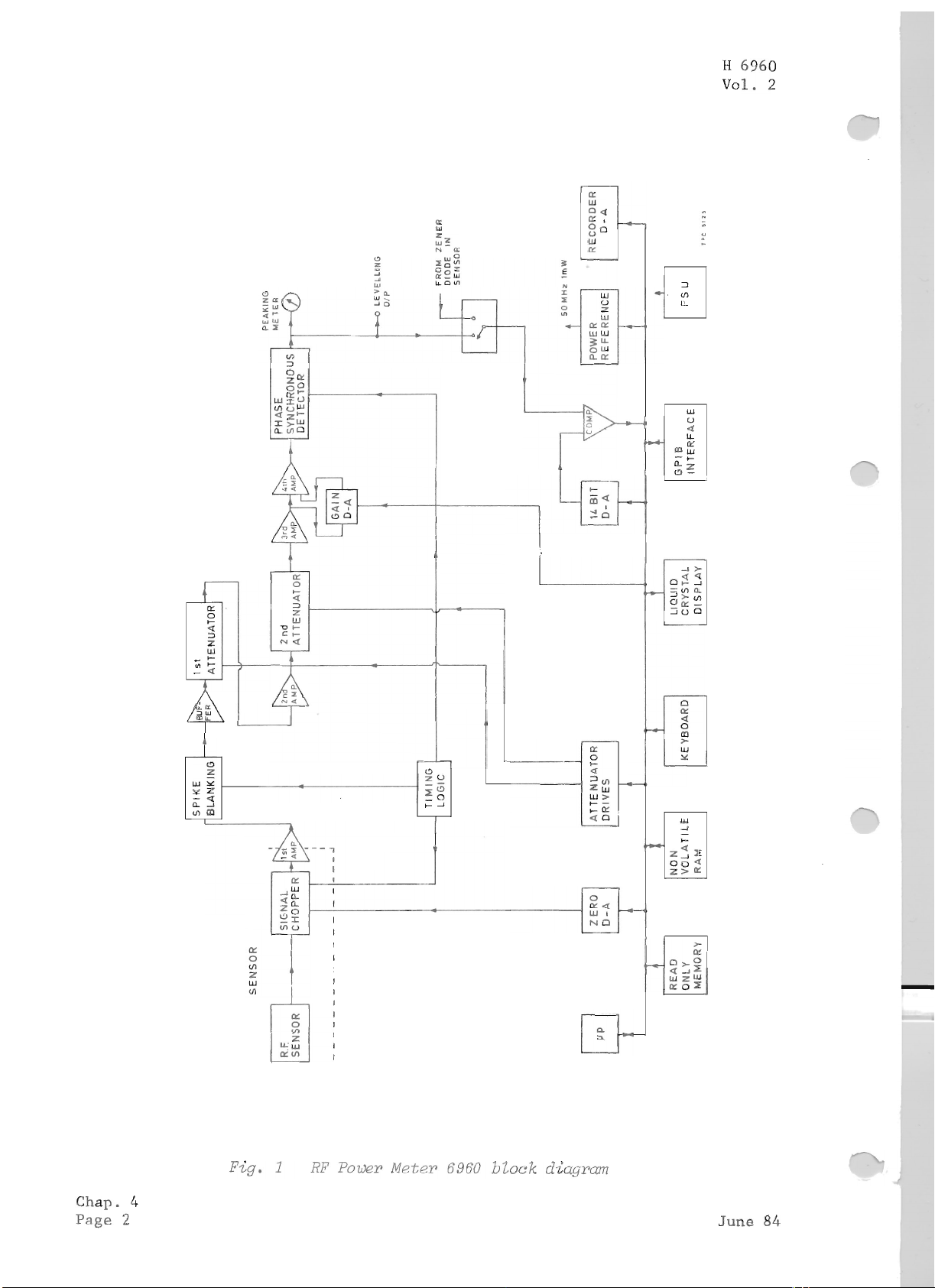

DETAILED

Analogue

6.

7.

second

assembly.

approximately

p.c.b.

Refer

First

part

synchronous

Timing

signals

provided

meter

is

the

and,

achieved

microprocessor

D-A,

and

the

the

comparator,

for

all

of

TECHNICAL

to

Chap.

amplifier

of

the

When

1000.

7,

(sheet

1st

using

detector

for

the

signal

by

the

timing

via a switch

by

runs

using

the

non

drive

the

attenuator

power

the

reference.

the

stages

keyboard

is

DESCRIPTION

AAOI

circuit

I).

amplifier,

the

6910

Fig.

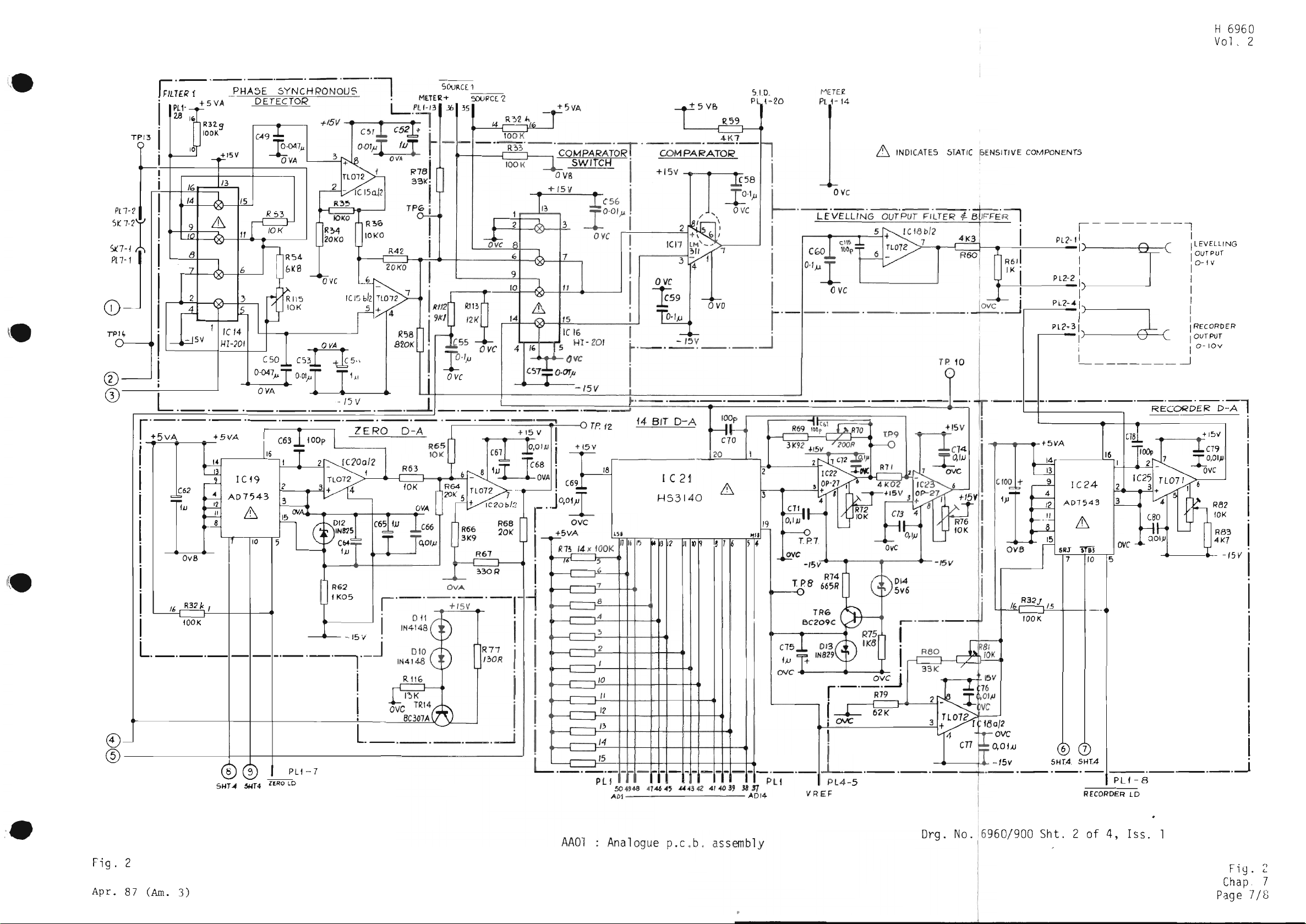

2 shows a

ICI and

the

series

then

synchronously

chopper,

logic.

to

the

program

volatile

the

zero

drives,

Inputs

and

provided

diagram.

associated

first

sensors

simplified

spike

The

recovered

comparator.

stored

RAM

D-A,

the

liquid

to

the

GPIB

by

the

part

being

this

complete

de-modulates

blanking

in

read

(Random

the

14

crystal

the

microprocessor

interface.

PSU.

components

in

the

amplifier

amplifier.

and

d.c.

signal

only

Access

bit

D-A,

form

power

has a gain

the

the

passes

memory.

Memory) •

the

display,

are

the

sensor

a.c.

gain

the

of

8.

AC

gain

power

C2,

sensor

sensor

C6

and

controls

characteristic

is

controlled

transistor.

C9

control

the

centred

low

Chopped

signal

by

DC

the

high

frequency

at

the

Fig.

the

components

bias

for

frequency

response.

chop

rate

2

the

transistor

response

of

925 Hz.

in

The

the

emitter

and

amplifier

is

the

-

circuit

set

by

RI

to

capacitor

has a band-pass

output

of

in

the

RS.

the

June

84

Chap.

Page

4

3

H 6960

Vol.

2

9. 0

follower

sensor.

a.c.

gain

small

a

ID.

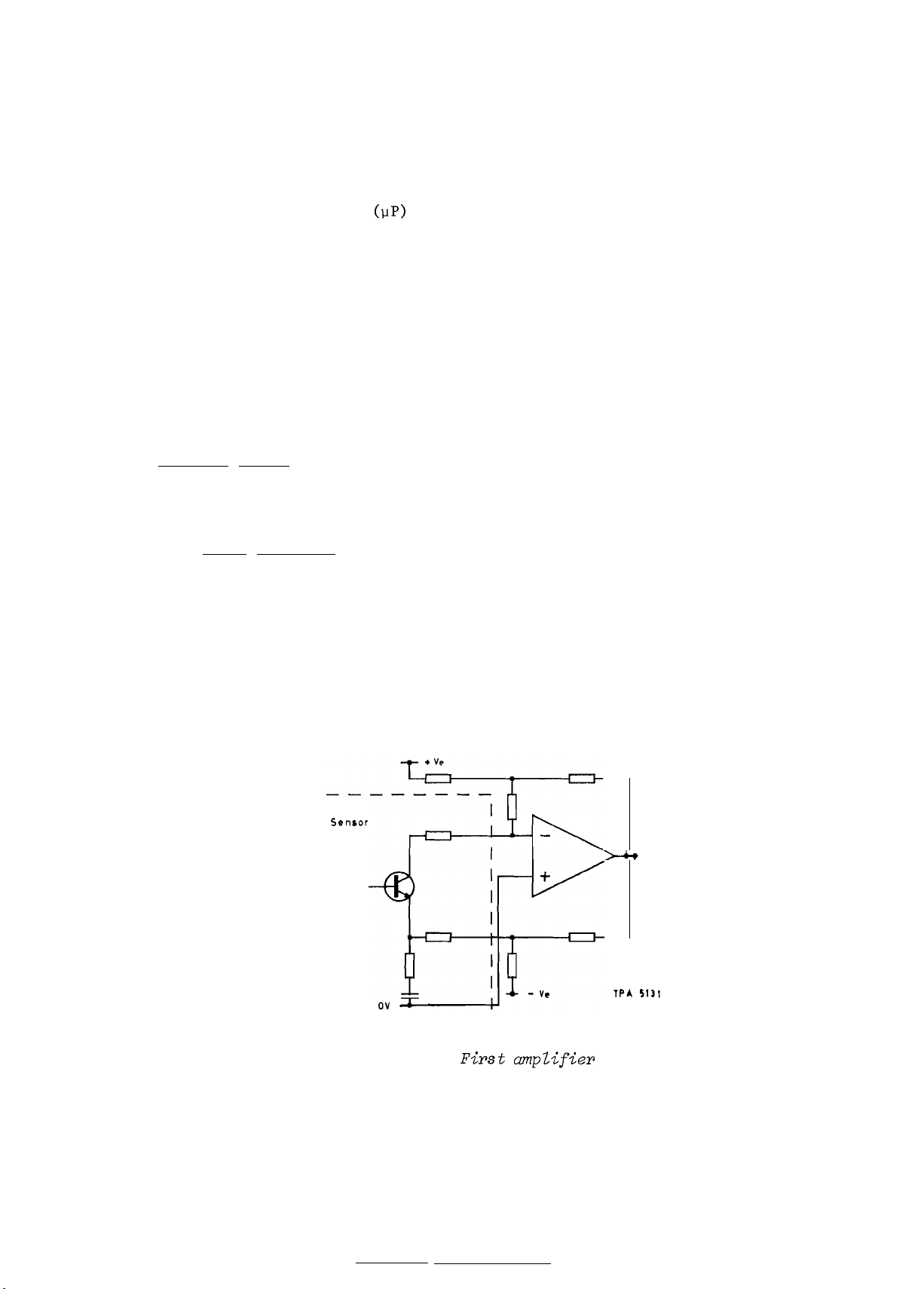

Spike

remove

chopped

a

sample

changes

by

the

levels.

and

hold.

VA

control.

which

amount

spikes

d.c.

and

state

hold

This

stages.

blanking.

that

signal

hold

and

time

IC4b

provides

earth

(about

acts

SAMPLE/HOLD

TIMI

Ie2,

an

reference,

DI,

D2

0.5

The

are

generated

from

circuit.

lasts

interfering

for a period

as a high

J \

NG

RIO,

RII

earth

and

R9

V)

when no

spike

the

r.f.

The

with

impedance

I I

and

TRI

reference

indicated

ensure

sensor

blanking

on

the

sensor

hold

period

of

large

.'--

provide a very

from

the

signal

by 0

VA,

is

that

the

earth

is

connected

circuitry,

leading

(see

180 RI14

signal

buffer

Fig.

is

for

and

3).

from

levels

the

---J

trailing

low

offset

ground

used

by

the

reference

to

the

power

R114, Cl6 and

edges

IC3c and CI6

the

signal

reduces

at

high

signal

errors

r.f.

from

in

rest

only

IC3c,

of

power

the

source

the

power

of

the

moves

meter.

the

act

as

chopper

caused

sample

CHOPPED

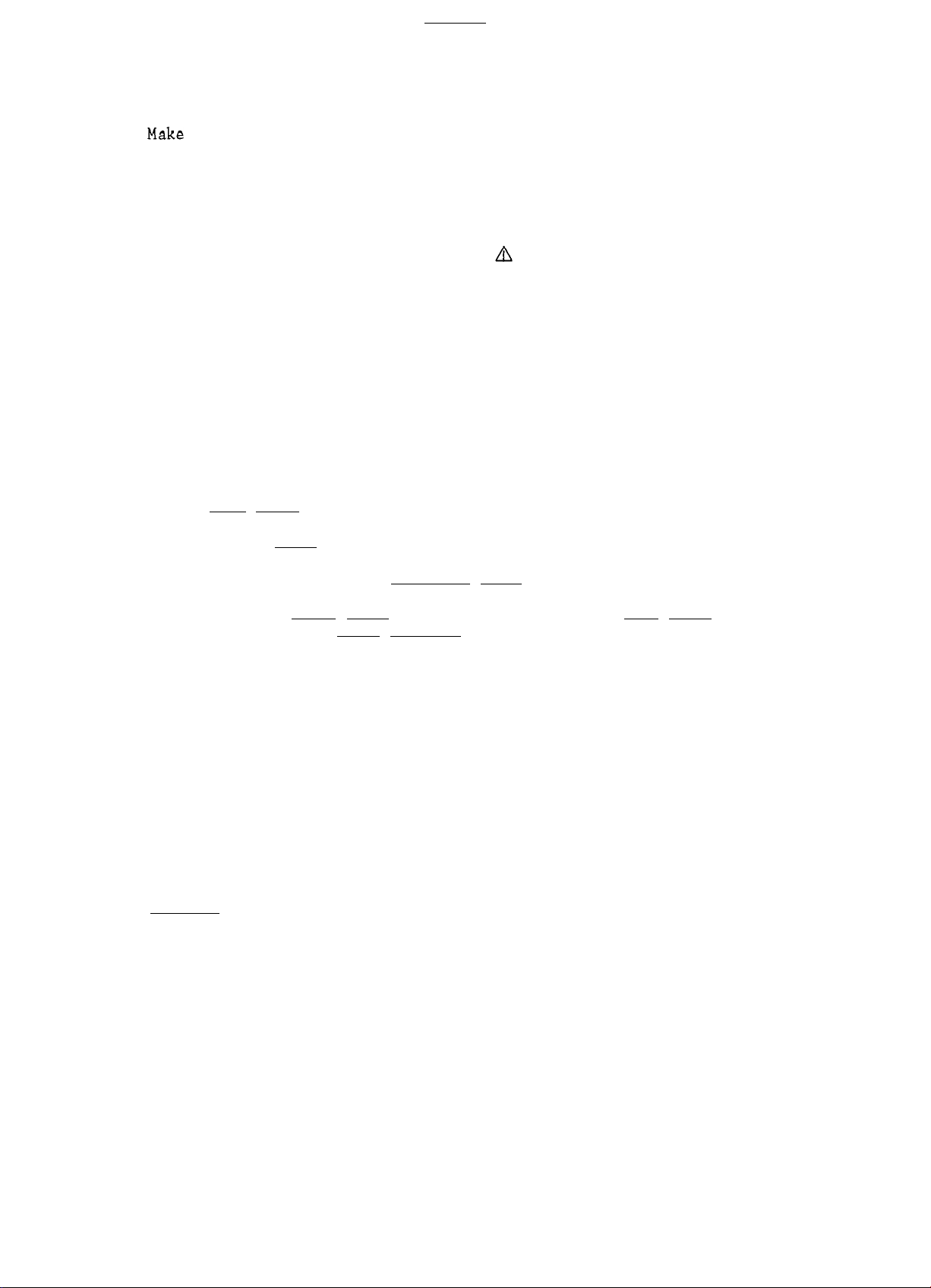

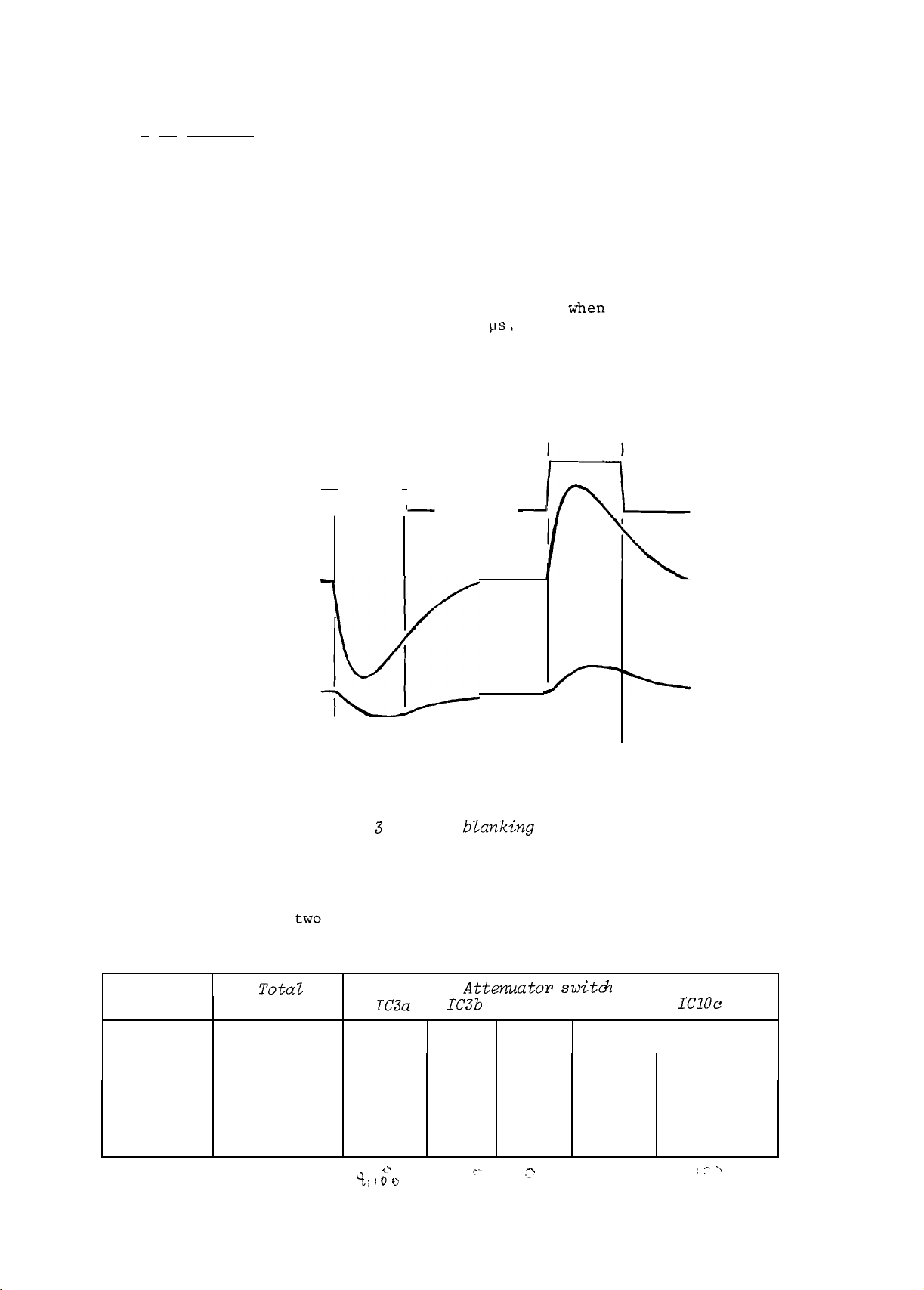

11.

First

form a switchable,

C23

together

control.

Range

attenuator.

with

attenuation

D.

C.

OUTPUT

divide

the

TABLE

Fig.

Precision

by 100

resistors

1

Spike

resistors

attenuator

forms a

ATTENUATOR

RI4

and

for

range

high-pass

CONTROL

IC10a

Rl5

with

changing

filter

es

IC10b

CCS084

IC3a,

(see

for

IC3b

Table

bandwidth

1).

Chap.

Page 4

4

2

3

4

5

I

None

1/

10

1/100

1/1000

1/10000

ON

ON

OFF

OFF

OFF

'

OFF

OFF

ON

ON

ON

ON

OFF

ON

OFF

OFF

OFF

ON

OFF

ON

OFF

OFF

OFF

OFF

OFF

ON

June

84

12.

Second

second

amplifier.

frequency

13.

Second

The

principle

above.

14.

Third

Resistors

frequency

15.

Fourth

amplifier

basically

and

non-inverting

input

and

which

the

reference,

finally

amplifier.

roll

off.

attenuator.

of

This

attenuator

amplifier.

R30

and

roll

off.

amplifier.

stages,

a

standard

has a gain

inverting

the

gain

controlled

The

operation

R31

control

in

that

gain

inputs.

of

input,

of

the

over

IC4a

with

gain

The

is

R24

to

is

the

also

has a divide

third

approximately

R26

the

The

fourth

its

gain

stage

The

(ICllb,

main

approximately

from

the

amplifier

the

range I to

feedback

and

same

as

amplifier

gain

of

amplifier

can

be

R3?,

signal

3.

gain

D-A

is

reduced.

3.

components

25.

ICI0

form

the

first

by

10

stage

IClla.

is

controlled

R38),

is

applied

When a signal

which

R22

C35

controls

the

second

attenuator

setting.

has a gain

C38

controls

different

very

but

having

to

uses

the

This

and

R23

the

attenuator.

described

of

about

the

from

the

precisely.

both

the

non-inverting

is

applied

signal

the

H 6960

Vol.

form

the

high

35.

high

other

It

inverting

to

R37

as

gain

to

2

is

its

be

16.

Phase

to

d.c.

by

closing

ing

up

sample

synchronous

by

this

the

to

the

and

hold

ensure a fast

determined

amplifier

complete

17.

When

R53

and

crease

pass

C49

18.

filter.

ICI5

and

rence

resistors

otherwise

19.

The

ICllb

sample

the

the

acts

CSO

to

the 0 VC

R34,

linearity

output

by

charge

comparator,

ling

output

buffer

ICI8b.

circuit.

switches

sample

capacitors

response

the

effective

and

to

power

time

as

an

so

maintaining

reference

35,

from

ICI?,

after

via

being

detector

Samples

ICI4a

voltage

must

to

changes

impedance

the

value

be

obtained

meter

placed

of

is

in

the

instrumentation

their

used

36 and

errors

ICISb

42

would

is

switch

passed

(sheet

of

and IC14d

during

be

the

able

in

of

C49

within

on

the

most

series

capacitors

charge

throughout

ensure

that

result

then

fed

ICI6b.

through

2).

the

signal

alternately,

time

to

charge

signal

of

the

and

C50.

the

sample

sensitive

with

the

so

amplifier

and

the

if

these

to

the

This

output

the

low-pass

The

input

are

a.c.

taken

with

the

switch

and

level.

switch

Together

is

discharge

The

time

and

the

theSe

period.

range

coupling

(range

switches.

forming a very

offering

a

allowing a shift

the

d.c.

gain

on

stages.

each

differed.

peaking

is

meter

also

filters,

signal

on

each

c49

and

closed.

constant

qutput

i

high

of

input

via

used

R58

is

restored

half

C50

charg-

These

rapidly

of

4th

allow

1),

an

resistors

These

frequency

impedance

earth

refe-

Precision

is

the

R78

and

for

the

and

C60,

cycle

to

is

almost

inlow-

to

same

the

level-

and

June

84

Chap. 4

Page 5

H 6960

Vol.

2

20. Comparator

Serial

from

phase-synchronous

ment

conversions.

14-bit

the

to

whether

21.

decide

mA

5

The

applied

22.

corrections

indicates

that

Zener

Input

the

allows

D-A.

output

reset.

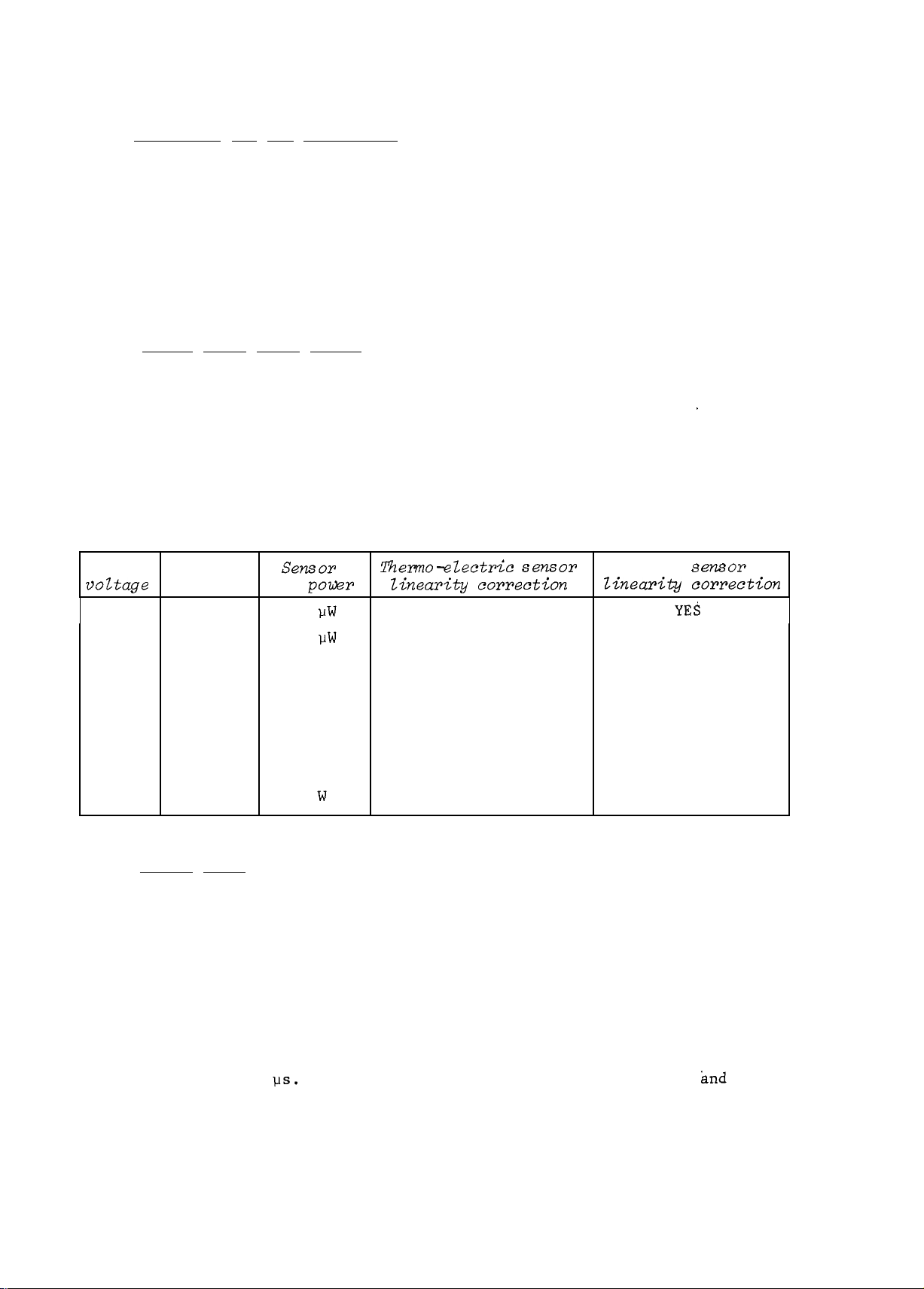

Sensor

which

constant

voltage

The

are

14-bit

the

of

The

to

keep

Zener

from

to

the

type

that

the

applied.

Sensor

Type No.

Data

It

the

type

current

Zener

and

A-n

(SID)

D-A. The

detector

processor

To

do

this

then

reads

comparator

processor

or

discard

diode

of

sensor

circuit

the

Zener

comparator.

of

sensor

must

be

voltages

TABLE

top

conversion.

pin

of

the

non-inverting

or

the

to

make

the

processor

SID

to

is

high

continues

each

bit

drive.

is

in

consisting

diode

in

use

applied

defines

used

2

is

to

with

SENSOR

The

processor.

input

Zener

successive

The

use.

diode

sets

check

by

until

scaled

give a true

the

the

data

setting

Zener

The

of

the

the

ZENER VOLTAGES

comparator

is

in

approximation

the

output

is

each

all

14

diode

Zener

R77,

by RI12 and RI13

required

power

appropriate

The

driven

the

most

kept;

bits

in

RII6,

output

inverting

sensor.

significant

of

the

bit

have

the

diode

DID, DII and TRI4.

scaling

reading.

scaling

is

taken to the

input

from

either

This

arrange-

analogue-to-digital

bit

comparator.

if

not

the

bit

in

turn,

been

sensor

is

driven

before

checked.

is

and

and

deciding

used

ftom

being

linearity

Table

corrections

Diode

is

the

.

driven

of

the

If

is

to

a

2

set

2.7

3.3

3.9

4.7

5.6

6.9

9.2

10.0

23.

provide

section

blanking

tion

24.

manently

is

925

is

at

Hz

Timing

The

twice

all

of

circuitry

and

925 Hz.

master

on by

square

0920

-

Spare

-

6910

6912

-

-

logic

the

the

its

the

waves.

(sheet

timing

drive

phase

oscillator

control

925

Hz

ID

ID

-

30

mW

mW

100

lOO

mW

IOW

lOO

I).

signals

the

synchronous

is

lines.

chop

rate

ICs 5

for

the

signal

detector.

IC5

which

and

to

power

chopper

Three

pins

NO

NO

-

NO

YES

YES

YES

YES

9 and

is a gated

their

meter.

in

The

outputs

10

and

the

II

associated

Outputs

power

basic

astable

are

provided

provide

components

from

sensor,

frequency

(4047)

by

complementary

NO

-

NO

NO

NO

NO

NO

this

the

of

set

rC5;

spike

opera-

per-

pin

13

25.

The

output

with a period

output

The

switch,

Chap. 4

Page 6

from IC6

rC3c.

from

of

rC5

180 The

provides

pin

13

drives

timing

the

sample/hold

IC6

which

components

timing

is

of

wired

IC6

for

as a monostable

are

RI8,

R55

the

spike

blanking

June

C24.

84

26.

The

precision

the

sample

drives

the

chopped

pulses

27.

Both

signals

a

dual

pins

duration

1 and

in

phase

sequence

28.

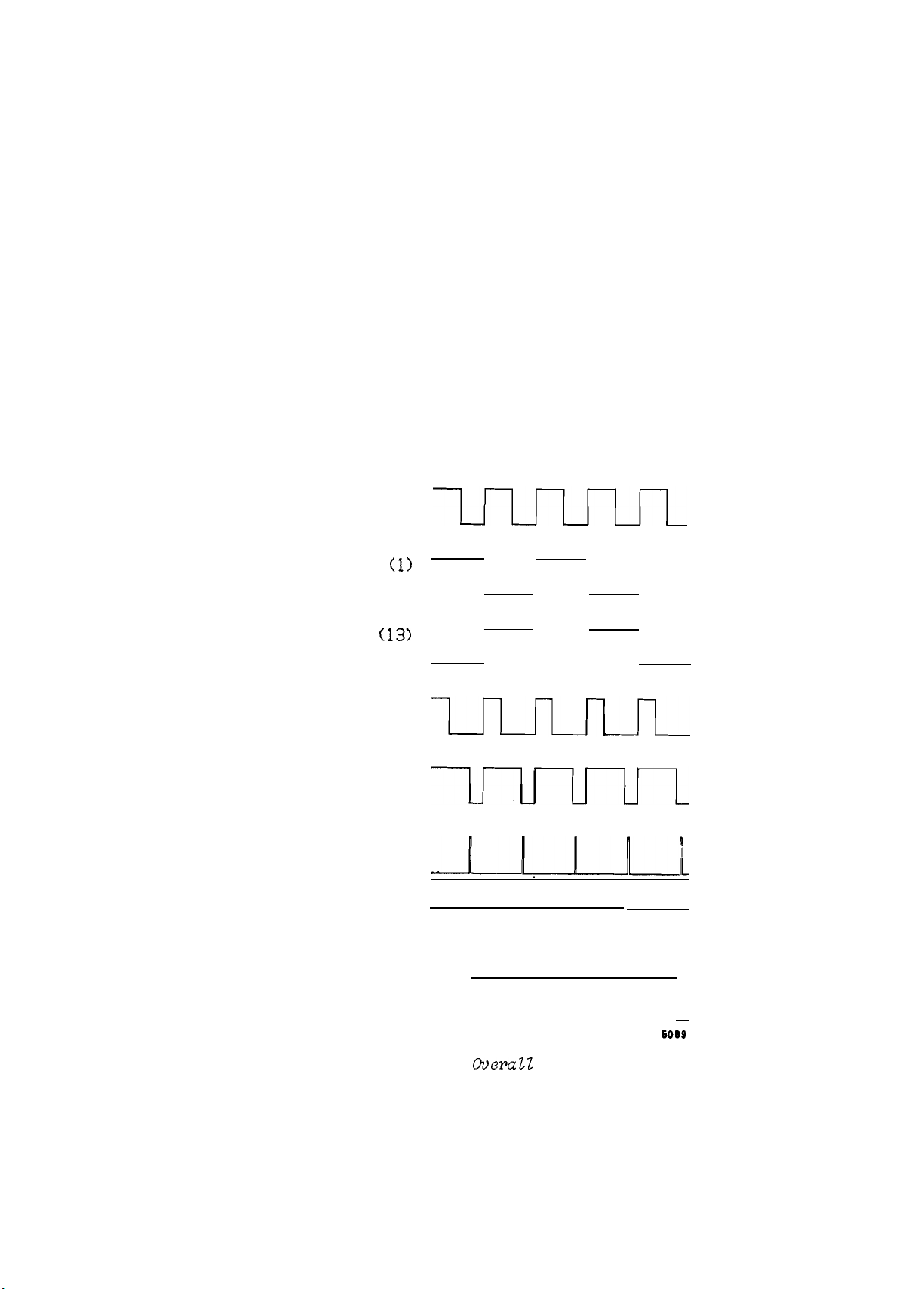

Fig.

output

dual

pulse

the

second

waveform.

to

the

of

the

for

the

D-type

13

and

leading

relationship

of

operation.

4 shows

from

monostable.

correct

power

bistable,

are

IC5

required

monostable

sample

925

Hz

sensor.

out

of

that

ensures

the

relationships

MASTER

pin

13

The

by

the

providing

Two

NAND

switch

signals

by

the

phase,

from

a

TP2

CLOCK

also

drives

first

phase

gates,

from

Both

action

with

pin

predetermined

monostable

synchronous

sample

part

in

the

IC5

signals

of

the

1 by a

of

the

the

pulses

of

detector.

are

used

are

R27,

C32

signal

fractional

signal

timing

input

provides

detector.

ICB,

to

delayed

and

from

signals.

of

one

the

on

each

are

used

derive

at

R28, C33.

pin

13

amount.

chopper

half

delay

This

half

to

the

chopper

the

input

having

The

f.e.t.

of

lC7,

before

then

cycle

direct

of

Outputs

the

difference

on/off

H 6960

Vol.

a

of

the

drive

IC9,

at

greater

2

IC

CHOPPER

DRIVE

IC9

CHOPPER

SPIKE

TIME

DRIVE

BLANKING

TO

SAMPLE

IC

SAMPLE

rc

SAMPLE

9

1

2

TP3

TPll

SAMPLE

TP4

TIMING

8

(3)

1

8

(4)

2

I

I

I

I

r

CC

June

84

Fig.

4

timing

Chap. 4

Page

7

29.

D-A

verter.

D-A

Ie21,

bipolar

offsets

point

30.

ultra-stable

stant

output

generated

of

The

current

converters.

Its

digital

with

the

-6.2 V reference

operational

of

D-A

output.

Zener

source

inputs

approximately

by

the

diode,

consisting

The

14-bit

are

amplifiers

operational

required

D13. The

D-A

(sheet

generated

IG22 and IG23,

±6.2

V.

amplifiers

by

the

Zener

of

R74, R75, DI4

2)

is a CMOS

on

processor

Resistors

and

D-A

circuit

diode

is

and

p.c.b.

is

arranged

R72

and

R70

adjusts

is

driven

TR6.

multiplying

AA02. The

to

R76

adjust

the

generated

from a

7.5

D-A

give

centre

from

mA

H 6960

Vol.

2

con-

a

any

an

con-

31.

AD

parallel-out

Once

register

cessor

sheet

7543.

(see

the

Serial

2)

Fig.

SRI

the

p.c.b.

pin

D-A's.

are

This

5).

is

shift

by

all

based

device

The DAC's

shift

clocked

register

sending

AA02.

The

on

is

register

into

is

LDI

low.

Gain

D-A

the

same

special

logic

circuitry

and a 12-bit

the

shift

full

its

These

(sheet

type

in

that

register

contents

control

J)

Zero

of

multiplying

data

consists

DAG

input

are

signals

D-A

is

loaded

of a 12-bit

register.

on

the

loaded

and

Recorder

D-A

into

trailing

into

are

derived

RFB

D-A

converter,

it

serially

serial-in

Serial

edge

the

DAC

on

(both

the

data

of

input

the

at

STB3.

pro-

32.

The

Gain

amplifier'

33.

The

Zero

sensor

ICI9

operational

provides

by

amplifier

34.

etc.

stable

components.

the

part

Chap. 4

Page 8

to

and

IC20a

a

R67

and

The

Recorder

The

-6.2 V reference

recorder

of

the

D-A

is

arranged

above

null

-3.1 V to

R68

lC20b

-10 V reference

D-A

for

D-A

circuitry

out

provides

amplifier

before

is

D-A

R81

is

output.

circuit.

more

any

+3.1 V

generated

used

Fig. 5

for

details

provides

offsets

a

IC20b which

going

provides

DJ3.

R82

generated

unipolar

output

to

the

by a low

a 0

voltage

It

to

adjust

provides

V-A

unipolar

of

how

a

0

to

also

from IC20b

sensor.

to

to

is

amplified

the

the

output

this

D-A

small

has a -6.2 V reference

drift

+10 V

do

voltage

by

the

signal

+6.2 V output.

pin 7 which

The

Zener

output

this

is

to

-10 V to

ability

to

using

is

-6.2 V reference

diode,

for

generated

-10

give

null

lC13.

used.

which

chopper.

This

D12.

use

V by

the

out

is

sent

is

input.

is

then

with

from

ICI8a

correct

any

See

'Fourth

to

The D-A,

fed

scaled

for

chart

the

ultra-

and

scaling

offset

the

to

This

down

ICI9

and

recorders

associated

to

on IC25,

June

84

35.

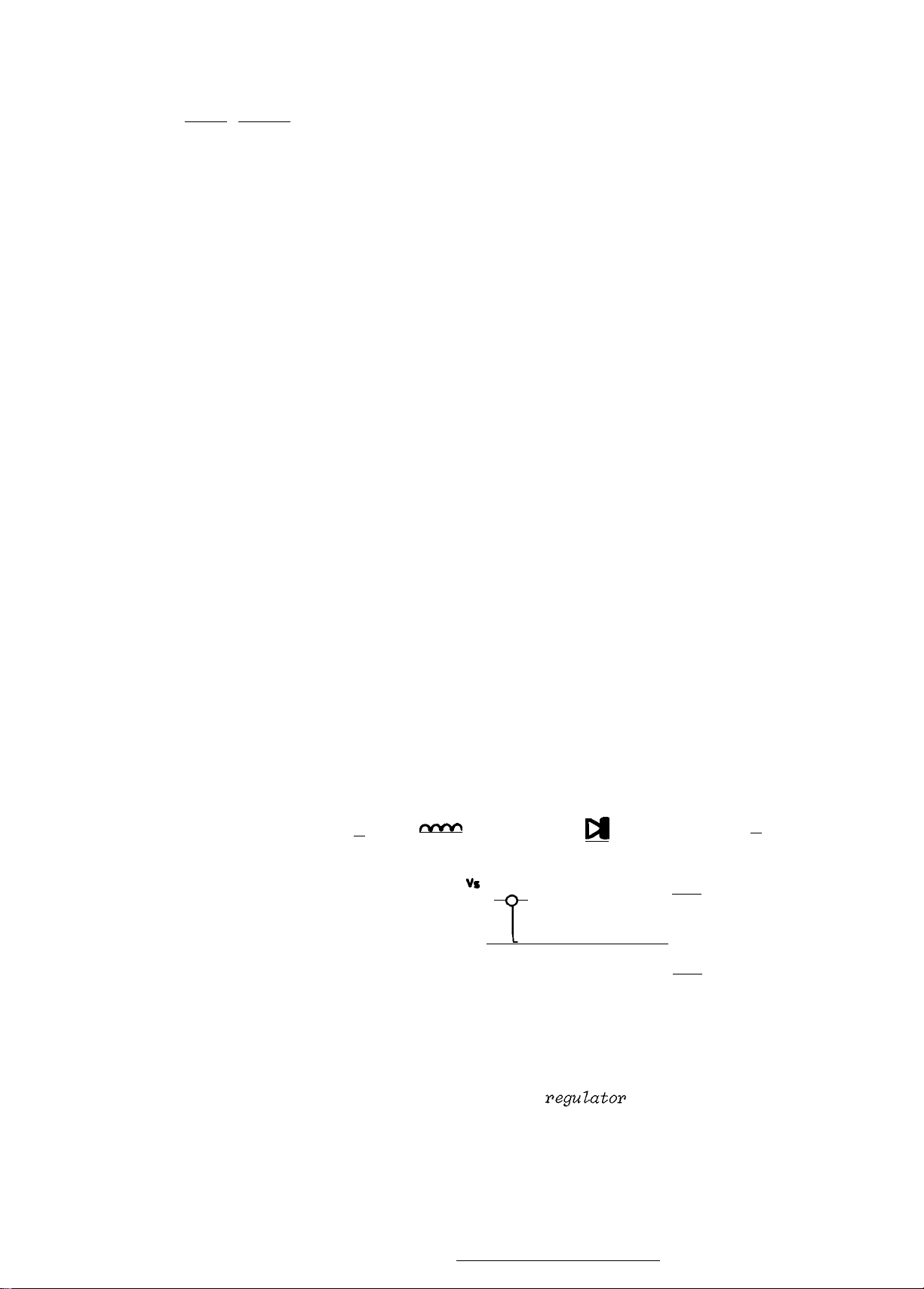

Power

6960 Power

amplifiers,

current

parts

cases,

36.

fier

to

cater

varies

37.

regulator

give

38.

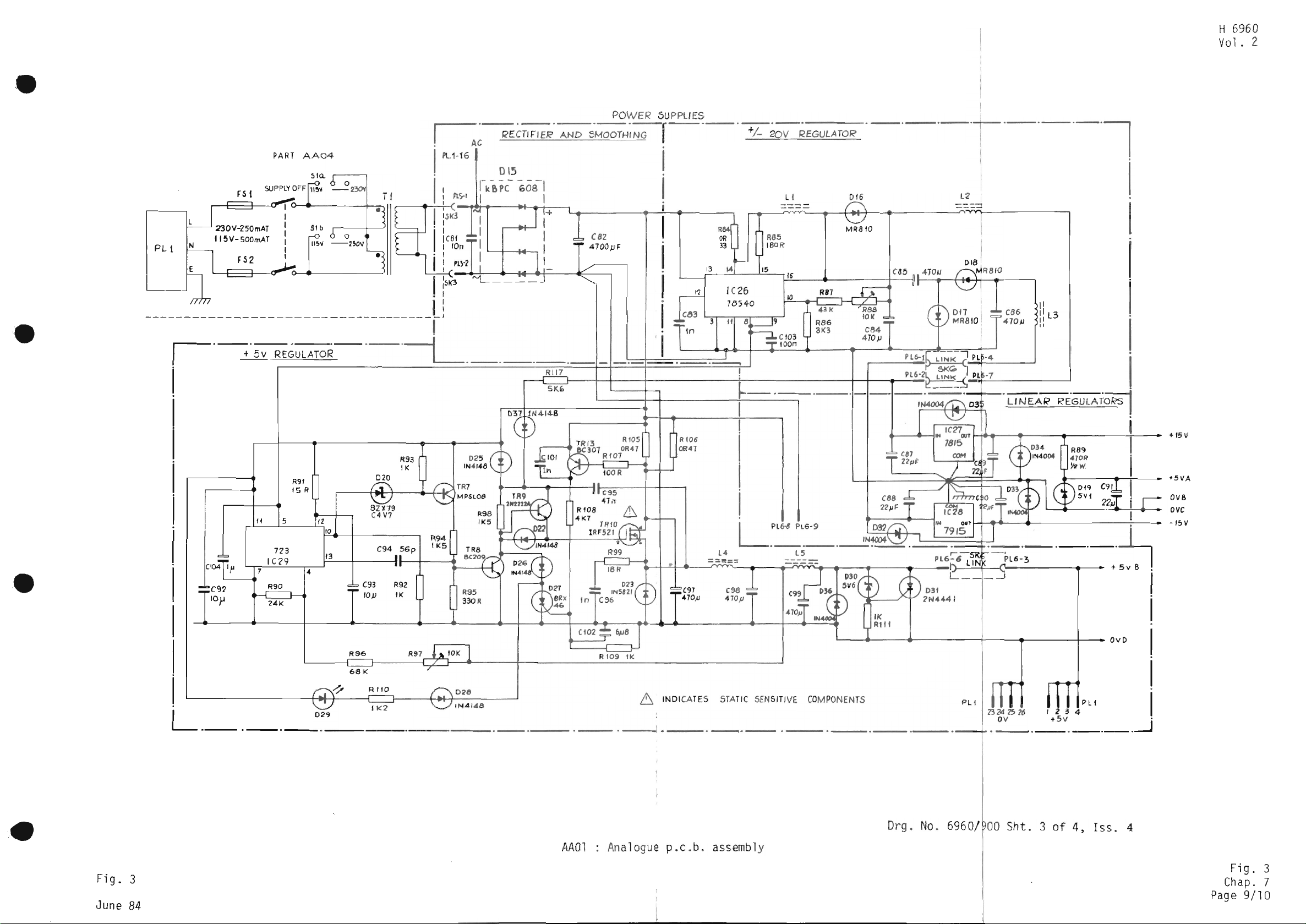

Fig.

zero

the

less

flow

not

put

the

linear

average

current

dead

on

and

output

5 V

to

except

The

DI5

from

The +15 V

IS V.

The

6):

(Va-Vs),

inductor

than

to

the

change

voltage

diode

rate,

diode

is

time

off

current.

supply

Meter.

a 5 V low

for

these

raw

d.c.

and

reservoir

for

mains

about

set

for

This

theory

when

and

current

the

output

output.

instantly,

plus

to

the

determined

current

less

with

times,

(sheet

positive

the

processor

supplies;

for

the

supply

supply

10 V to

and

-IS V supply

approximately

ensures

of

the

the

switch

the

to

voltage,

the

diode

load

than

the

no

current

so

the

3).

and

current

a

raw

high

voltage

Again,

capacitor,

current

is

provided

capacitor

inputs

20 V

clean

switching

closes,

increase

and

the

voltage.

by

Vout-Vd-Vin.

(Id)

so

maximum

to

average

when

the

Four

basic

negative

rail

Vin-Vs

applied

it

is

and GPIB

d.c.

5 V

C82. The

of

115 V and 230 V.

depending

rails

20 V

supply

step-up

the

linearly.

the

diode

the

and

is

equal

output

output.

input

d.c.

used

boards.

supply,

supply,

by

mains

on

are

derived

out,

followed

rails

regulator

applied

is

applied

is

switch

voltage

At

this

the

inductor

Timing

to

current,

current

IS V

rails

for

switching

linear

transformer

primary

the

for

voltage

Because

reverse

opens,

changes

time

the

Input

is

supplies

are

the

timing

Basically

regulators.

circuit

actual

from a

by

linear

the

amplifier

is

as

(Va)

across

the

biased

the

to

current

current

adjustments

load

current.

off

time

current

always

are

required

used

regulators

This

supply

step-up

the

applied

inductor

can

greater

for

circuitry

there

TI,

bridge

of

raw

voltage.

regulators

follows

drops

inductor,

and

current

the

total

can

decreases

control

is

increased

flow

all

are

and

TI

is

d.c.

switching

stages.

(refer

to

voltage

current

of

flow

If

during

than

H 6960

Vol.

by

the

the

and a

three

in

all

recti-

switched

supply

to

to

almost

causing

is

cannot

can-

the

through

at

a

the

the

load

by a

both

the

2

high

out-

39.

The

couples

fies

IC26

switched

it.

Vout

Vin

Vs

Vd

contains

d.c.

the

switching

with

C86

::

Regulated

::

Unregulated

::

Switch

::

Diode

most

is

also

power

providing

Vin

Output

Voltage

Voltage

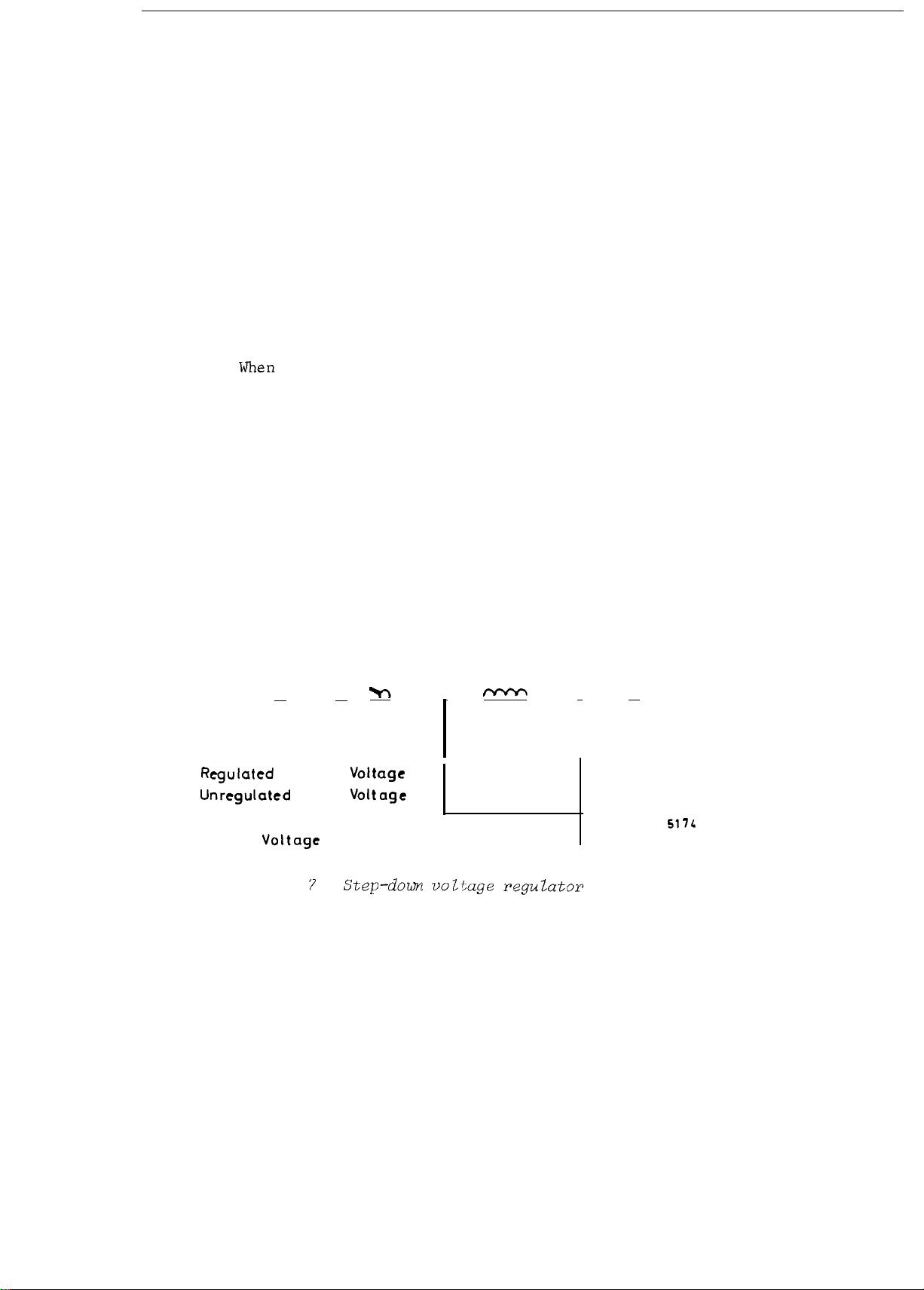

Fig. 6

of

the

used

0

Input

Drop

components

to

provide a simple

to

d.c.

the

output

L

Voltage

Voltage

Step-up

required

restoration

capacitance.

Va

J.

voltage

by

negative

diode

0

this

type

supply.

D17. DI8

I

C

I

of

regulator.

then

CC

C8S

recti-

o

5087

a.c.

Vout

June

84

----------

Chap.

Page

---

4

9

40.

The

tered

by

regulators.

regulator.

and

possible

fails.

41.

The low

the

+15 V

42.

The

board

ABO

type.

43.

The

is

as

follows:

(Vin-Vs),

current

inductor

inductor

the

extra

current

iL

will

the

inductor

turn

on and

is

now

-(Vout-Vd)

inductor

cycle

time

the

is

of S so

average

positive

L2, L3,

C89

oscillations.

current

rail

high

1 and

basic

and

to

rise

and

into

current,

current

the

remaining

increase

current

provide

current

repeated.

that

capacitor

and

C87

IC27

and e90

by

series

current

the

GPIB

theory

the

voltage

from

the

iL,

and Vout

until

so

continues

the

negative

and

C88

before

is

the

+15 V

decouple

D32

+5 V is

+5 V is

board.

of

switch S closes,

zero.

load

is

current

the

cannot

the

inductor

the

The

average

current

used

resistor

used

the

step-down

Va-Vout

This

and

less

than

decreases

flows

switch

change

change

to

fall

electronics

inductor

will

outputs

being

three

the

to

D35

by

R89

by

The

regulator

is

current

output

the

into

is

instantly,

current.

in

inductor

toward

be

from

applied

terminal

outputs

protect

the

timing

and

Zener

the

processor

switchmode

the

voltage

applied

flows

capacitor.

load

slightly.

the

turned

in

zero,

off.

The

current

zero

the

system

current

and Vout

the

switching

to

regulator

of

IC27 and IC28

the

logic.

diode

is

of

regulator

across

from

current,

When

capacitor,

Va

falls

voltage

until

equals

the

regulators

D19.

board,

the

step-down

Va

rises

the

induct

the

When

the

iL

the

capacitor

exceeds

increasing

At

this

to

across

will

be

S

turns

controls

the

will

regulator

inputs

and

This

AA02;

switch

instance,

-Vd

output

remain

of

Ie28

to

if

is

(refer

close

or

through

instantaneous

so

the

negative.

on

again

the

on

H 6960

Vol.

are

fil-

the

linear

the

-15

V

reduce

one

derived

the

noise

or

other

from

display

switchmode

to

Fig.

to

Vin

causing

the

the

provides

the

output

Vout;

since

diode D can

inductor

The

and

the

and

off

current;

constant.

2

7)

44.

The

TR7

and

f.e.t.

sufficient

L4

is

the

diode.

be

set

45.

Additions

tection.

When

the

turned

the

m.o.s.

flowing

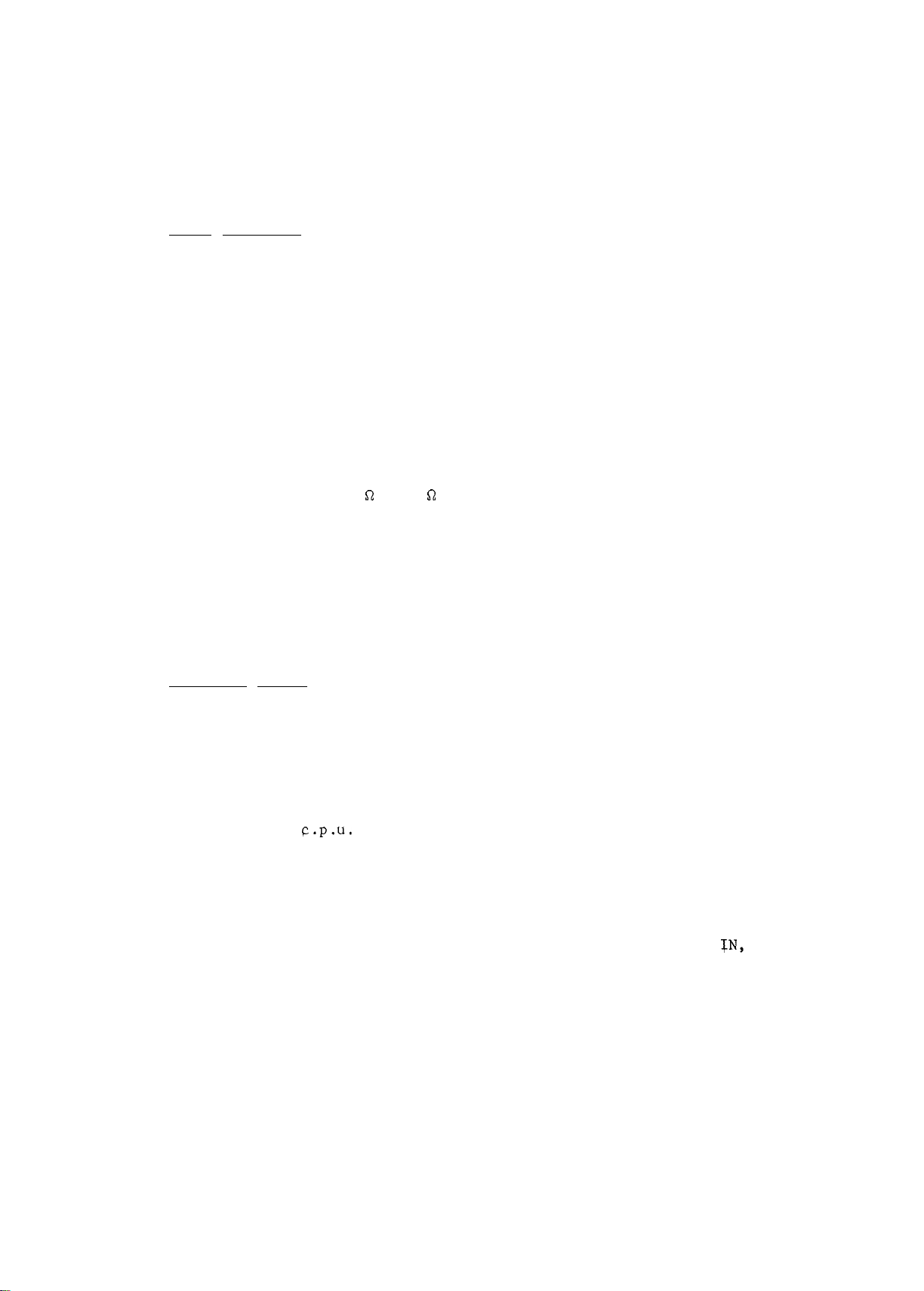

Vout =

Vin =

Vs =Switch

Vd =Diode

controlling

TR8

level

TRIO

which

drive

switched

Voltage

correctly.

to

Resistors

voltage

on;

which

f.e.t.

through

Vin

0 0

Output

Voltage

Fig.

of

shift

acts

voltage

inductor;

feedback

the

basis

RI05 and RI06

across

turns

switch,

l.e.d.

D29, and

Input

Drop

the

+5 V regulator

and

amplify

as

the

switch.

available

C98

is

via

supply

the

resistor

on

thyristor

TRIO. The

5

R96

series

the

on

the

the

output

and

provide

sense

reaches

D27.

thyristor

Va

•

o

is

output

TR9,

gate

R97,

over-current

the

This

resistor

j L

_

L

c

performed

from

IC29

D22

and

C95

of

TRIO

capacitor

allowing

current

approximately

RIIO.

flowing

removes

is

held

• 0

by

IC29.

to

drive

ensure

to

turn

and

D23

the

output

and

over-voltage

0.6

the

on

by

When

Vout

CC

it

the

into

V,

gate

the

the

Transistors

the

that

there

on

properly.

recovery

voltage

the

TR13

drive

current

output

m.o.s.

is

to

pro-

inductor.

is

from

voltage

Chap.

Page

10

4

June

84

H 6960

Vol.

2

exceeds

when enough

on, a very

comes

46.

Power

47.

48.

1.00

applied

thus

of

greater

power

49.

can

coupled

circuit

detector

levelled

bined

attenuator

5.6

into

The

+5 V supply

reference

Refer

The power

mW.

to

turning

reference

TR3

and

be

level

from

consisting

D2

circuit

with

V,

Zener

current

high

The

a 2

which

current

operation.

to

Chap.

reference

reference

the

transistor

TR2

on,

than

1.5 V is

off.

associated

controlled

the

source

and

d.c.

is

dB

attenuator

then

diode

is

flowing

is

is

7,

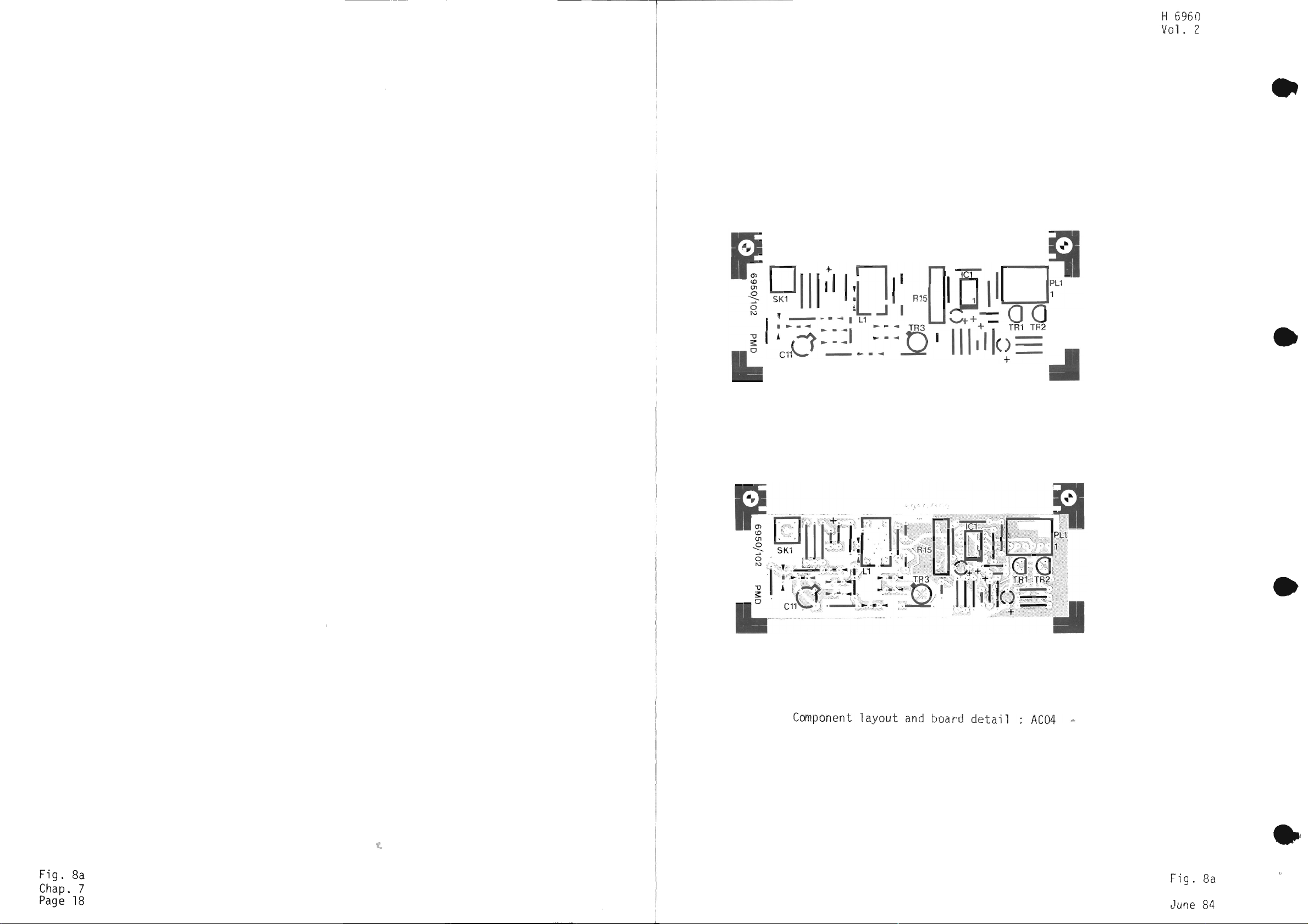

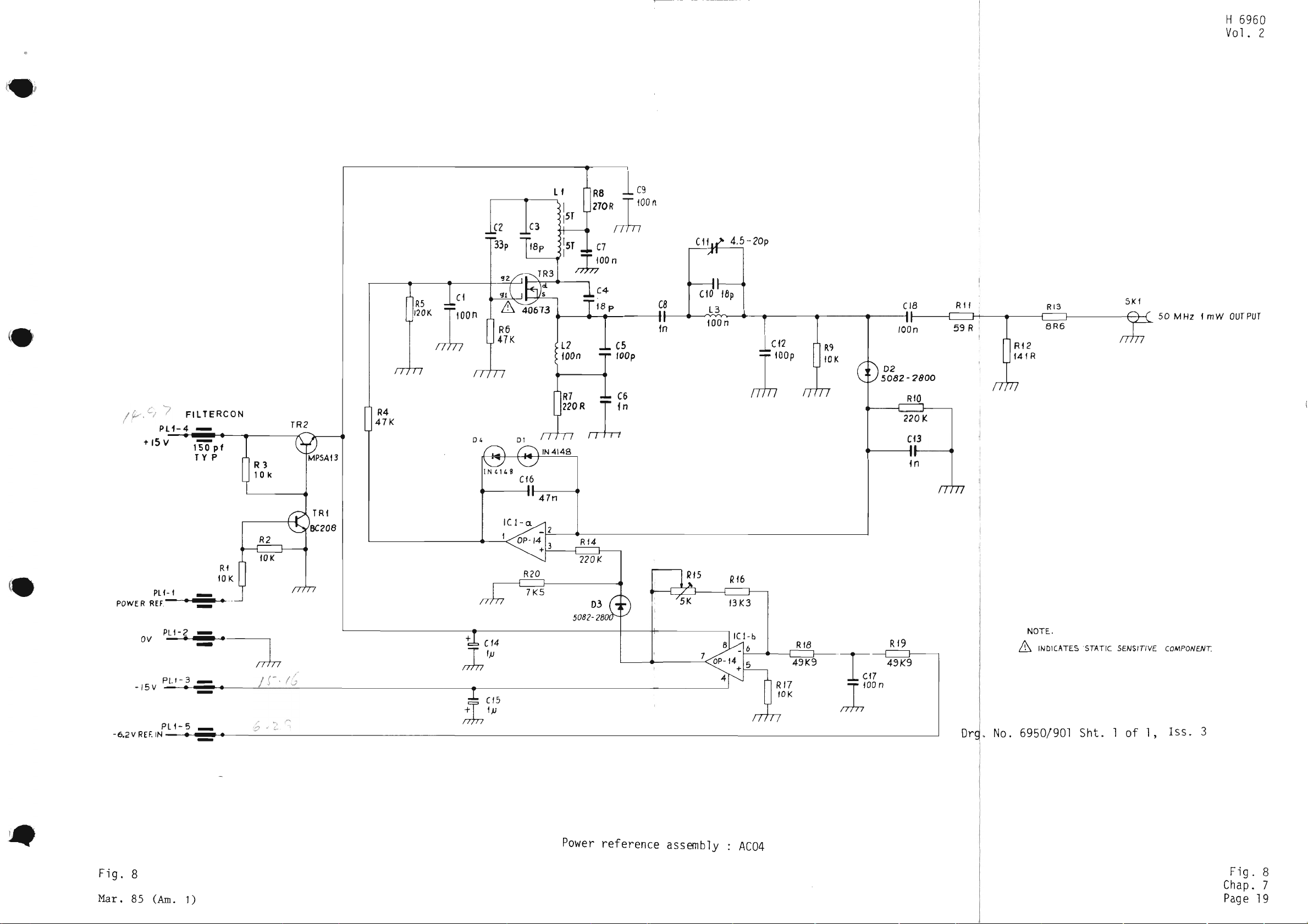

AC04

enabling

components

by

of

of

CIO

blocking

0 a 50

passes

D30

starts

through

drawn

filtered

circuit

supplies

oscillator

switches

the

applied

the

second

TR3

by

to

CI2

capacitor

source

in

r.f.

from

by

power

to

CB

and

RII.

power

to

the

the

the

diagram.

a low

is

enabled

TRI

and

reference.

RI,

TRI

form a

gate

to

the

L3.

C18.

resistor

R12

to

conduct

Zener

supply

action

spurii

TR2.

turns

modified

on

the

matching

The

and

the

and

will

diode.

and

the

of

L5

and C99.

50

MHz

carrier

by a digital

Applying

When a positive

on,

turning

Hartley

m.o.s.

and

matching

As

the

is

required.

RI3

output.

source

form

circuit

the

fire

thyristor

When

D31

current

levelled

control

0 V

turns

TR2

oscillator

f.e.t.

harmonic

impedance

This

rest

is

limit

signal

and

Output

rejection

then

is

of

the

D31

turned

circuit

at

TRI

off

voltage

the

that

is

feeds

of

a

com-

50.

The

output

comparator

the

gain

being

is

fed

via

non-inverting

gate

of

the

Processor

51.

52.

data

interfaces

are

briefly

can

be

purpose

data

buses.

non-volatile

rupts,

53.

internally

reset

at

least

resets

Refer

The

lines,

found

of

and

The

is

the

p.c.b.

processor

c.p.u.,

applied

three

from

ICla.

set

D3

which

input

oscillator

to

Chap.

address

(PPIs)

described

the

features

divided

following:-

in

"MCS85

The

RAM.

full

and

program

IC3,

down

to

the

detector

The

-6.2 V voltage

by R15, R16, RI8

is

used

of

7,

AA02

board

decoding,

reset

below,

Users

is

The

a

multiplexed

uses a 10

IC3

clock

to

ICla.

transistor

circuit

contains

circuitry.

full

Manual"

to

control

is

contained

c.p.u.

to

give

pin

36.

cycles

provide

The

TR3.

EPROM,

is

MHz

a 5

The

synchronizes

diode,

output

an

descriptions

an

address/data

MHz

D2

reference

and

R19. The

temperature

of

diagram.

8085AH-2

non-volatile

Components

publishec

the

instrument

in

the

8-bit

crystal

n.m.o.s.

operating

reset

feeds

for

instruction

input

ICla

CPU,

of

by

EPROM

bus.

its

with

one

resultant

compensation

drives

buffers

RAM,

the

Intel

by means

frequency.

the

side

of

the

is

buffered

reference

the

level

for

the

programmable

and

their

8085

Corporation.

and

data

microprocessor

clock

RESET

internal

interconnections

CPU

and

of

the

is

generator.

At

levelling

by

for

D2,

control

address

peripheral

8255

address

stored

with

power-on

lasting

clock

IClb,

voltage

to

PPIs

The

in

inter-

This

and

the

and

and

the

is

a

for

June

(I)

(2)

(3)

(4)

84

Program

Instruction

Interrupts

All

tri-state

counter

register

are

is

cleared.

disabled.

bus

lines

is

cleared.

are

floated

(ALE

is

not

tri-state).

Chap.

Page

4

I 1

H 6960

Vol.

2

54.

are

AD7

addresses

lines,

4 k

55.

write

cycles

Address

output-only

are

bi-directional

and

A12-A15

in

the

Wait

states.

sequences

(or T states)

four T states

occur

the

within

instruction

decoding.

lines

also

are

bottom

called

and

three

register.

carrying

double

decoded

half

of

The

machine

with

the

remainder

clock

Address

lines

and

the

which

high-order

output

as a bi-directional

by lC7 3

the

memory map.

operation

of

cycles.

the

instruction

three

periods

T1

for

HEl

data

lines

byte

the

low-order

data

to 8 decoder

the

c.p.u.

These

fetch

(see

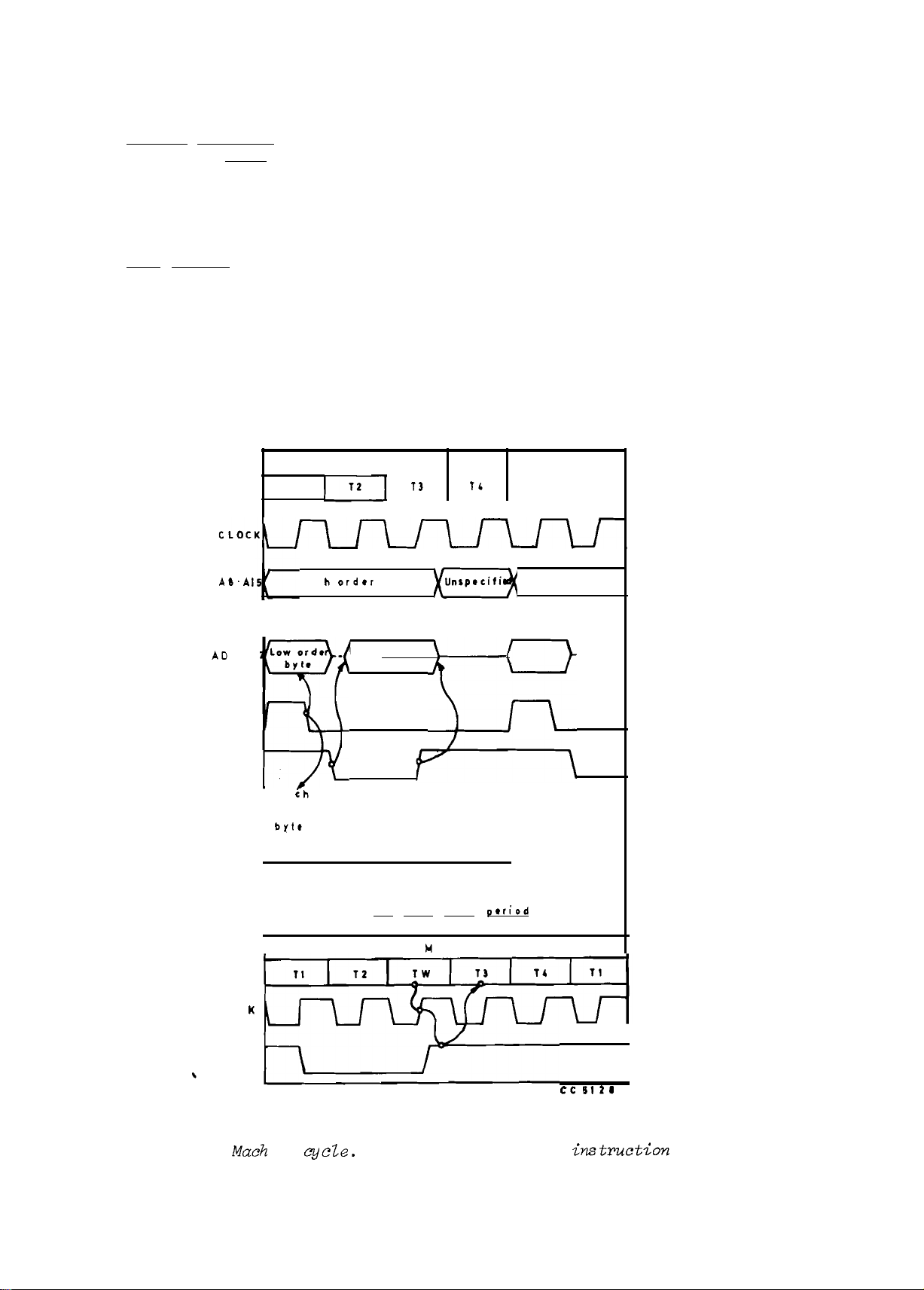

Fig.

in

this

time

are

to

is

may

MC1

8).

of

bus.

directed

contain

lC3

TI

multiplexed,

memory

byte

addresses.

of

The

give

addressing

into

from 3 to 6 clock

containing

A memory

places

HE2

the

T 2

pins

memory

top

four

blocks

read

a minimum

read

must

input

A8-A15

ADO-

address

of

and

of

into

ALE

RO

CL

O-AD

DC

Hig

L

ut

loword.r

uddr.ss

Fetch

...nput

tlon

inllructlon

byte

inllruc-)

byte

Th.

wuit

D.cod.

clock

Cl

inltrurtion

Chap. 4

Page

12

Fig.

8

R EAOY

ine

Wait

state

and Fetoh

(AAOZ)

June

84

56.

Slower

necessary

is

made

READY

at

would

clock

signal

logical

be

period

generated

circuit

next

period

57.

in

the

58.

latch

ALE

(Address

spikes

sition

clock

As

is

range

Address

and

on

from

input/output

to

delay

by

the

ability

line

low a Wait

generated

only

in

the

first

holds

the

period

only

Wait

generated

4000H

and

data

de-multiplexes

Latch

the

output

Data

to

the

input

of

is

sampled by

until

is

required

machine

READY

T3

then

states

only

to

7FFFH.

buffering.

Enable)

latched

Address

devices

the

clock

the

line

follows.

are

when

the

signal.

and

require

to

the

instruction

c.p.u.

the

c.p.u.

period

READY

by

signal

the

cycle

low

for

required

address

IC4

low-order

address

are

to

more

to

generate

will

follow,

line

6960,

are

shown

one

by

PPls

line

Address

address

Timing

lines;

be

expected.

time

to

register.

a

'Wait

at

the

clock

further

is

asserted

the

clock

in

Fig.

count

only

ICI2 and

AI4

goes

buffer

and

data

requirements

these

are

respond

period

periods

9.

then

ICI3,

high,

is

lines

caused

Provision

clock

Wait

high

and

IC6 and

asserts

the

i.e.

an

octal

cause

therefore

periods'.

T2,

if

clock

signals

ICIOc,d

high,

Wait

for

addresses

transparent

by

means

some

noise

during

H 6960

Vol.

it

for

this

this

periods

One

Wait

the

clock

of

the

the

tran-

2

is

The

is

59.

IC5

Data

buffer

the

data

bus

(DO-D7). The

read

line

60.

an

61.

outputs

this

address

for

62.

The

with

(RD)

signal

is

logical

EPROM.

ultraviolet

The

EPROM

remain

time

the

lines

the

EPROM

RAM.

small

select

the

c.p.u.

The

erasable

is

tri-state

data

AO

and

I

The random

battery

line

from

Reset

RI8 and TR2. The

is

powered

locations

63.

The

OE,

and

low,

data

low

data

down

of

the

direction

write

is

output

is

written

TR2

enable,

is

from

the

low.

instrument

accessed

from

to

AI2

other

devices.

access

to

decoder

line.

output

is

turned

RAM

can

of

data

WE,

from

into

an

octal

direction

c.p.u.

operating

EPROM.

when

until

the

location

is

placed

provide

IC7

from

be

written

to

control

the

RAM

the

RAM.

bus

Data

The

its

the

output

on

memory

standby

is

The

NAND

TR2

off

by

and

from IC9

lines.

to

transceiver

of

the

is

program

EPROM

CE

enable

in

the

the

data

is

a 2 k x

inverted

gate

collector

the

reset

to

as

the

data

and

buffers

transceiver

sent

to

the

is

contained

is

an

8 k x

line

is

enable,

EPROM

bus.

OE,

specified

Fig.

8-bit

power making

by ICIOb

is

made up from

drives

IC9 CS.

circuitry

the

+5 V supply

is

controlled

When

bus.

WE

is

If

is

c.p.u.

8-bit

logical

line

9 shows

c.m.o.s.

the

RAM

before

ensuring

fails.

by

logical

DE

is

data

to

controlled

when

in

the

IC8,

device.

low.

low.

by

the

state

the

device.

non-volatile.

being

D6

to

When

NANDed

D9,

the

that

the

output

high

and

high

and

and from

by

read

which

The

At

of

decoding

This

RI7,

6960

no

enable,

OE

WE

is

the

is

is

64.

When

Lithium

special

no power

forward

the

battery

diodes

passes

voltage

approximately

5

years

June

and

84

6960

BI

. The

DIO

from

so

2 V. The

possibly

is

powered down,

battery

and

DII.

the

battery

that

the

expected

10

years.

DIO

battery

the

is

isolated

has

extremely

to

the

can

lifetime

standby

supply

be

used

of

power

from

low

rail.

until

the

for

the

reverse

DII

the

battery

IC9 comes

+5

V power

has a very

voltage

is

supply

leakage

out

a minimum

from

so

that

low

is

of

Chap. 4

Page

by

13

H 6960

Vol.

2

ADDRESS

HEXADECIMAL

BOOOH

7000H

6000H

5000H

4000H

3000H

27FFH

-

PPI 2

(3

LOCATIONS)

PPI I

(3

LOCATIONS)

GPIB

SWITCH

(I

LOCATION)

GPIB

CONTROLLER

(B

LOCATIONS)

---------------

t

DATA

AREA

ADDRESS

AI5

0

AI4 AI3

0 I I

0 I I

0

0

0

I

I

0

0

LINES

0

0 0

I

I

SELECTED

AI2

I

0

I ICI3

I

0 IC9

SPACE

ICI2

AAII

IC7

AAII

lel

IC

65.

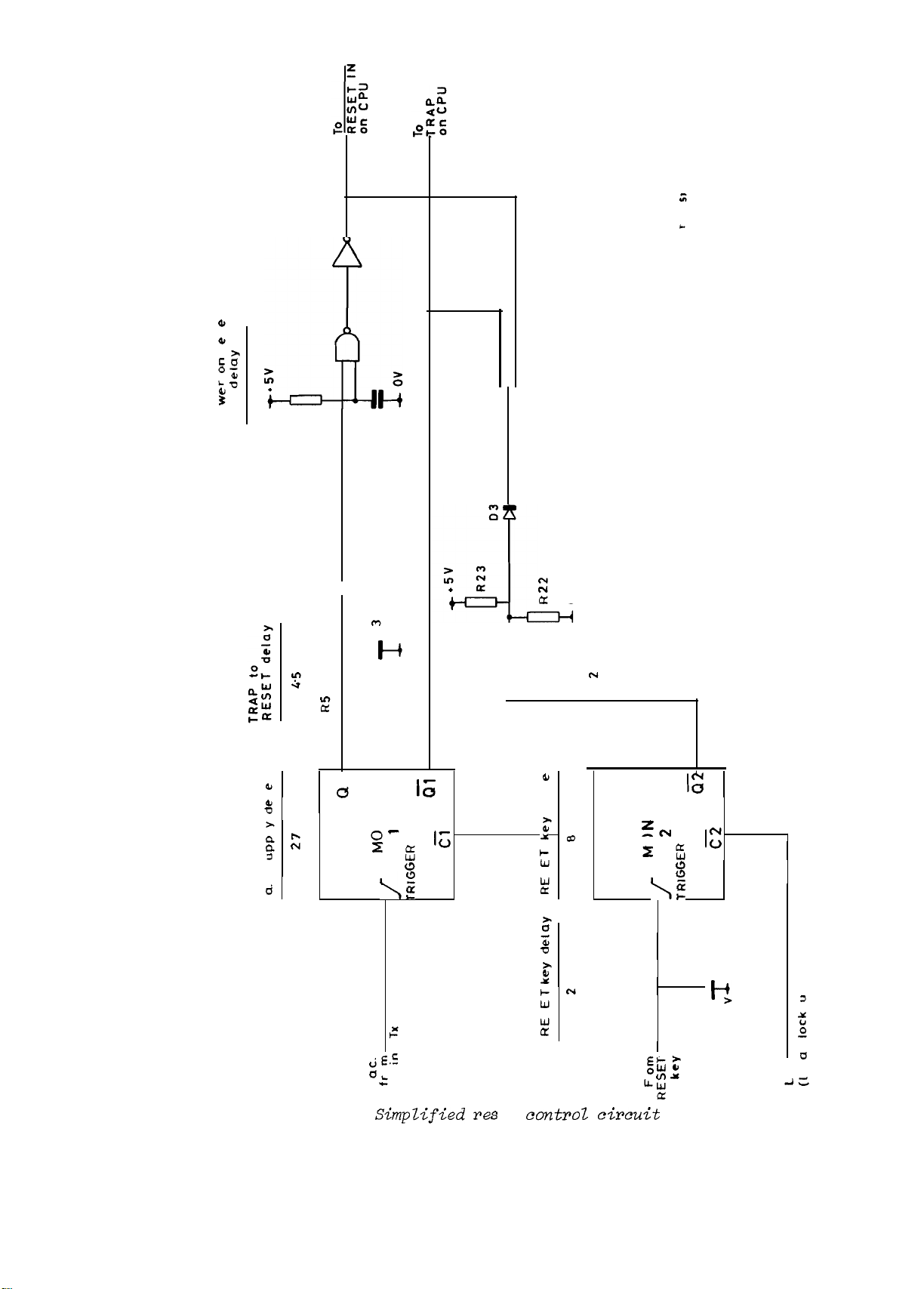

Reset

of

a power-down

clearly.

The

loss

of

front

When

processing

panel

the

2000H

IOOOH

OOOOH

control.

situation

Fig.

non-maskable,

supply.

settings

RESET

and

When

IN

sends

OPERATING

PROGRAM

The

shows a

this

in

line

on

all

t

I

I

Fig.

reset

and

to

simplified

interrupt

interrupt

STORE

0 so

the

c.p.u.

outputs

0 0 0

0

9

control

ensure

is

to a tri-state

diagram

used

that

becomes

circuitry

that

they

0 0

decoding

the

of

the

to

inform

the

may

logical

mode.

is

c.p.u.

reset

the

c.p.u.

be

recalled

used

itself

c.p.u.

low

I

0

to

inform

control

stores

on

the

c.p.u.

ICB

lCB

the

powers

of

the

power-up.

down

circuit.

an impending

halts

.

c.p.u.

any

Chap. 4

Page

14

June

84

....

III

...

o

Q.

..

N

u

..

H 6960

Vol.

2

>

0

>

u 0

III

E

o

u

III

E

III

u

0

Z

E

III

E

0

III

III

E

0

0

III

0

0

0

0

June

84

Fig.

10

·0Cl

III

10

u

E

...

...Jo

et

Chap.

Page

4

15

---

--------

---------

---

--

---------------

H 6960

Vol.

2

66. The

derived

mains

part I is

When

ing

RESET

are

QI

from

This

supply

stable

67.

delay

Q2

Therefore

allows

of

68.

power

RESET

the

triggered

the

the

IN

stored

low

is

the

ensures

recovers.

stays

The

fixed

low

output

the

the

6960

The

via

IN

processor

first

from

set

half

the

to

monostable

TRAP

line

in

interrupt.

of

RAM.

NANDed

NAND

gate

that

un-triggered

front

by

panel

R7

is

the

RESET

c.p.u.

amplifiers

dual

monostable

D4

and

lines

remain

board.

of

secondary

until

27

the

ms

is

the

c.p.u.

The

together

is

fed

the

monas

Potential

key

and C5.

taken

key

to

be

storage

steady

dual

rectriggerable

of

mains

so

that

no

longer

At

low

4.5

ms

with

via

table

divider

until

RESET

This

to

the

has

the

reset

etc.

and

capacitor

the

mains

supply

supply

triggered

the

same

4.5

delay

the

D3

to

remains

the

fires

monostable

clear

same

without

the

NAND

until

monostable

transformer.

is

removed. The

frequencies

the

time

QI

ms

later.

is

generated

c.p.u.

the

RESET

clear,

in

R22

and

+5 V rail

the

second

input

(Cl low)

function

removing any

gates,

C4.

all

This

power

ICI,

Thus

as

low

QI

low

output

high

the

R23

has

goes

low

During

IN

Cl,

same

also

by

delay

line

input

state

ensure

this

by

reached a satisfactory

monostable

has a duration

of

the

as

turning

supplies,

ICI and IC2,

ensures

has

been

that

removed from

is

the

pulse

as

45

which

time

network

IC2a.

of

the

even

after

of

first

the

are

the

triggered

monostable

duration

Hz

may

be

goes

high,

sends

the

settings

R5

and C3.

The

output

monostable.

if

the

mains

that

the

mono-

a 200

ms

180 ms. The

monostable.

supply

ensuring

supplied

CPU,

off,

stability

TRAP

the

with

rest

by

a.c.

re-

of

ICI

used.

rais-

the

value.

but

and

of

69.

face

PPls.

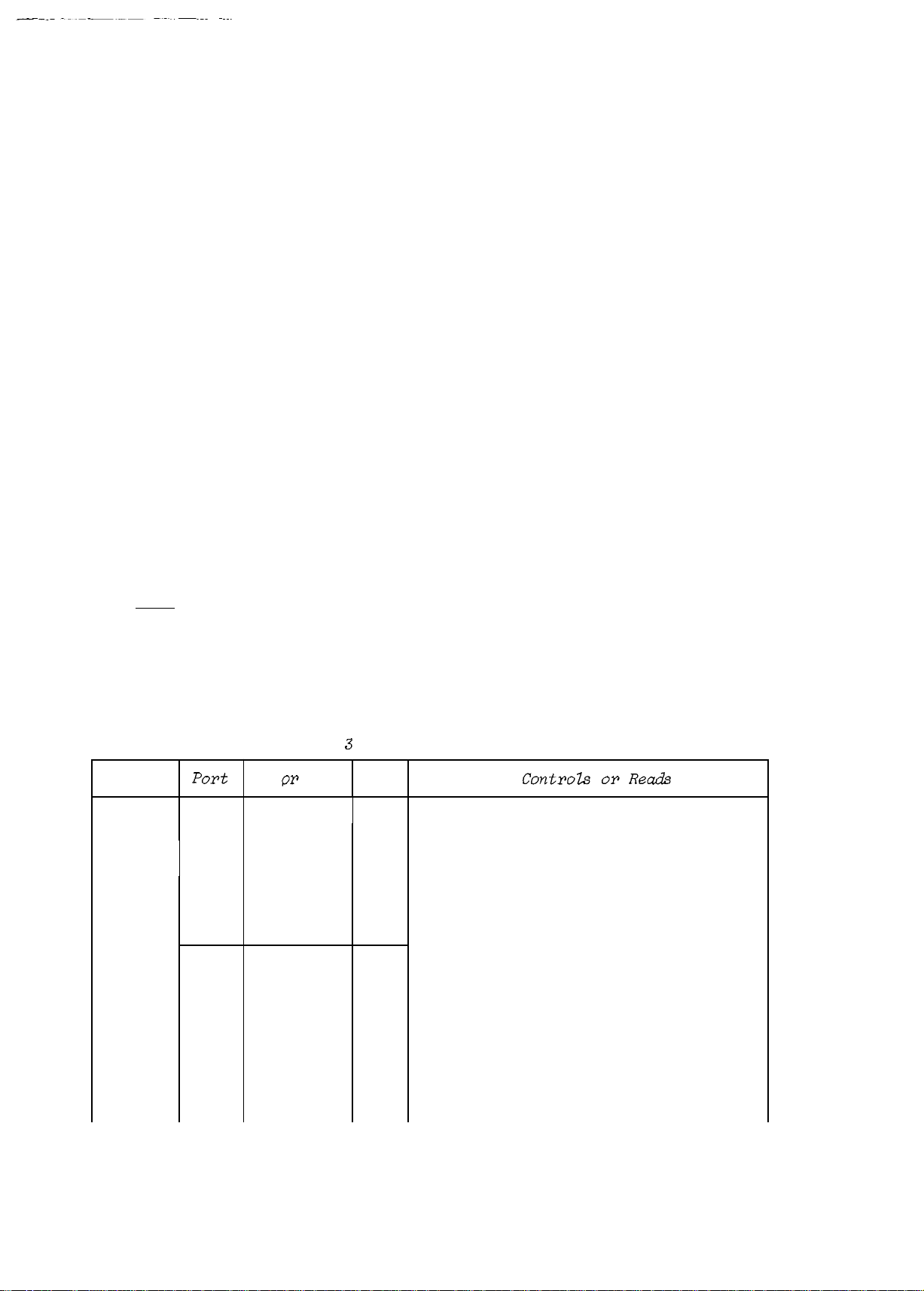

(PPI)

programmed

but

only

refer

to

selected

input

or

output

circuitry

PPI

I

ICI3

ICI2 and ICI3

devices

in

two

one

of

these

the

Intel

the

I/O

pins.

to

which

A

B

type

or

three

is

publication

pins

are

each

TABLE

In

Input

Input

are

8255.

groups.

used.

split

Table

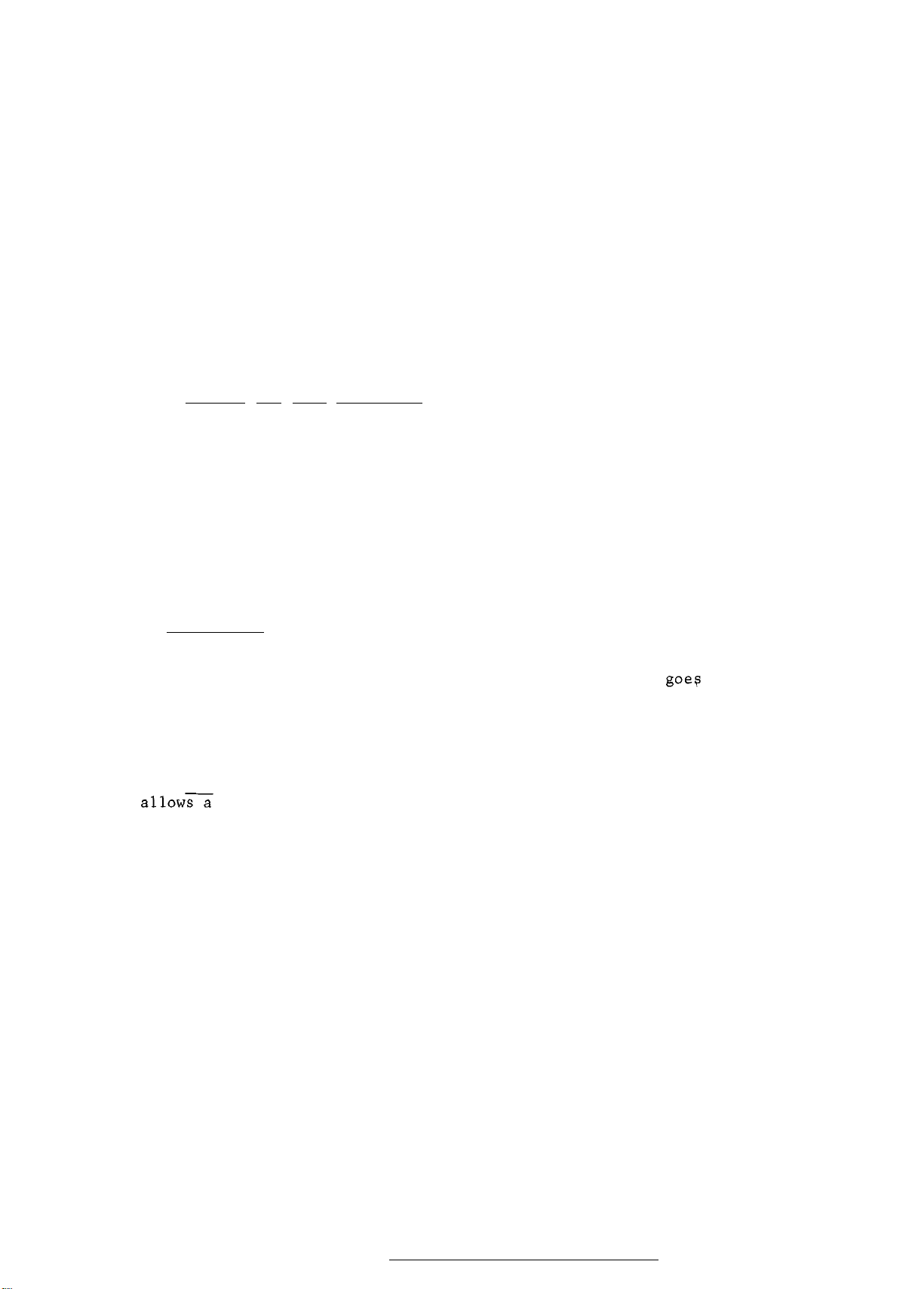

goes.

Out

general

Each

For

'MCS-85

into

3 shows

PPI

Bit

0

I

2

3

4

5

6

7

0

I

2

3

4

5

6

7

purpose

has

24

These

more

details

User's

groups

how

the

PORT

ALLOCATIONS

Key

4

Key

5

Key

6

Key

7

Key

8

Key

9

Key

DP

Key

ENT

Spare

Spare

Spare

Key

- (Minus)

Key

0

Key

Key

2

Key

3

Programmable

I/O

pins

are

three

Manual'.

of

8 which

groups

I

which

major

of

the

may

are

Keyboard

Peripheral

may

be

modes

8255

In

be

it

the

used

allocated

ABO

I

Inter-

individually

of

operation

is

best

operating

as

either

and

the

to

mode

Chap. 4

Page

16

June

84

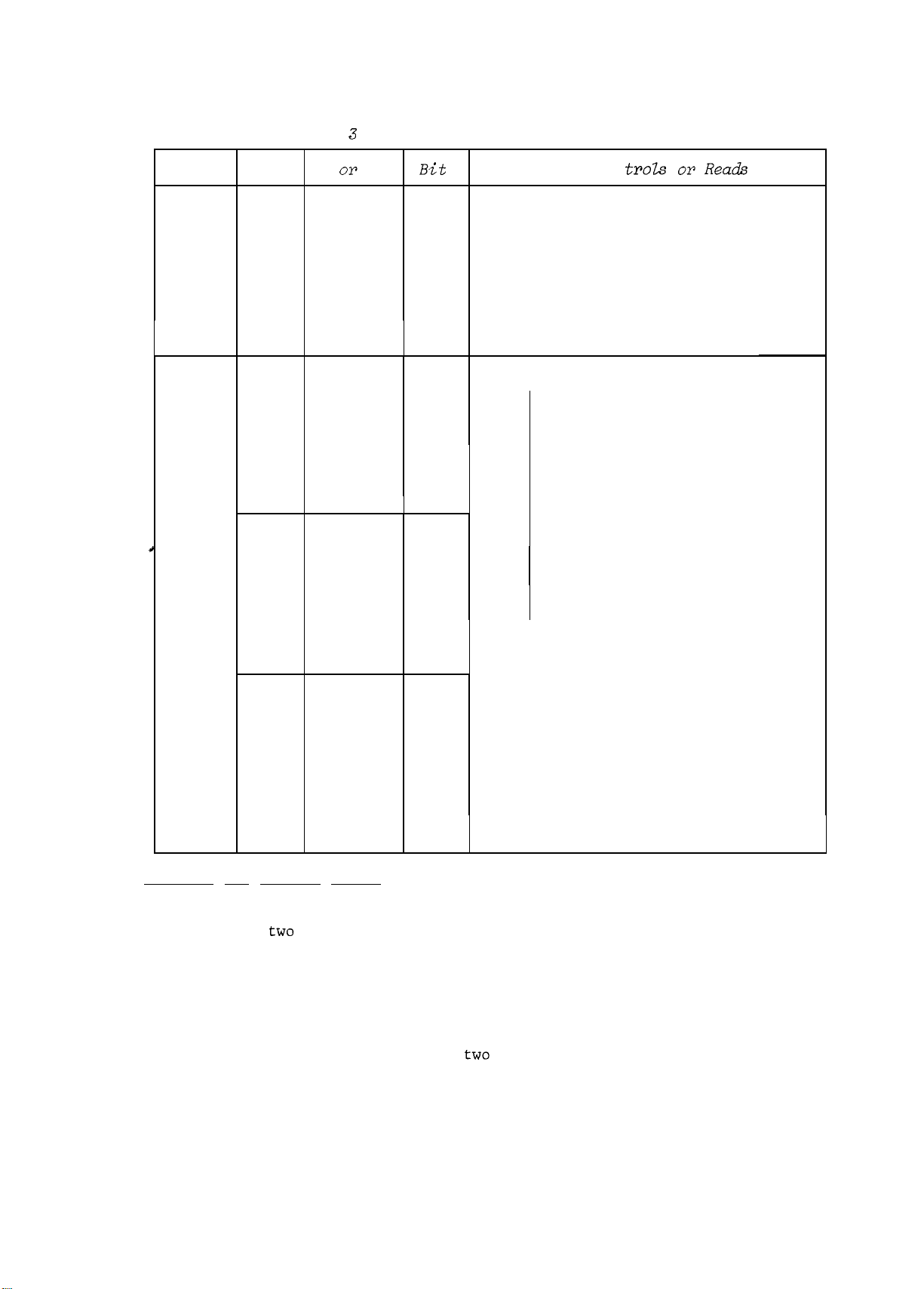

TABLE

PPI

PART

ALLOCATIONS

(continued)

H 6960

Vol.

2

PPI

2

ICI2

Port

C

A

B

In

Output

Output

Output

Out

0

0

I

2

3

4

5

6

7

I

2

3

4

5

6

7

0

I

2

3

4

5

6

7

Serial

CAL

ZERO

D-A

D-A

D-A

LOAD

RECORDER

DISPLAY

POWER

REAR

LOCAL

14-BIT

14-BIT

SOURCE

SOURCE

DRIVER

REFERENCE

PANEL

LOCKOUT

D-A

D-A

I )

2 )

Con

and

DISPLAY

LOAD

D-A

LOAD

LOAD

BLANKING

TO

LEAST

MOST

CONTROL

HEAD

STROBE

ON/OFF

OUTPUT

RESET

CONTROL

SIGNIFICANT

SIGNIFICANT

WHICH

ZENER

Tp

OF

BE

LINES

BIT

BIT

SIGNAL

OR

MEASURED

Keyboard and

70.

Refer

be

split

play

71.

devices

drives

CLX

high

into

drivers.

The

liquid

thus

from

input

on

the

line.

that 3 lines

C

display

to

Chap.

they

each

LOAD

control

7,

distinct

crystal

only

i.c.

This

signal

Output

p.c.b.

ABO I circuit

parts.

display

have 3

The

serial

data

is

line.

both

ICI and

0

I

2

3

4

5

6

7

(l.c.d.)

control

data

then

The

IC2.

GAIN

GAIN

GAIN

GAIN

GAIN

SPACE

FILTER

FILTER

diagram.

These

being

drivers

lines

is

loaded

integrated

CONTROL

CONTROL

CONTROL

CONTROL

CONTROL

CONTROL

CONTROL

Components on

the

ICI and IC2,

but

provide

clocked

to

the

in

display

circuits

A

B

C

D

E

I

2

key

by a

this

switches

are

up

to

32

falling

drive

are

p.c.b.

and

the

serial

segment

edge

by a

logical

cascaded

can

dis-

input

on

so

the

June

84

----

--------

Chap. 4

17

Page

H 6960

Vol.

2

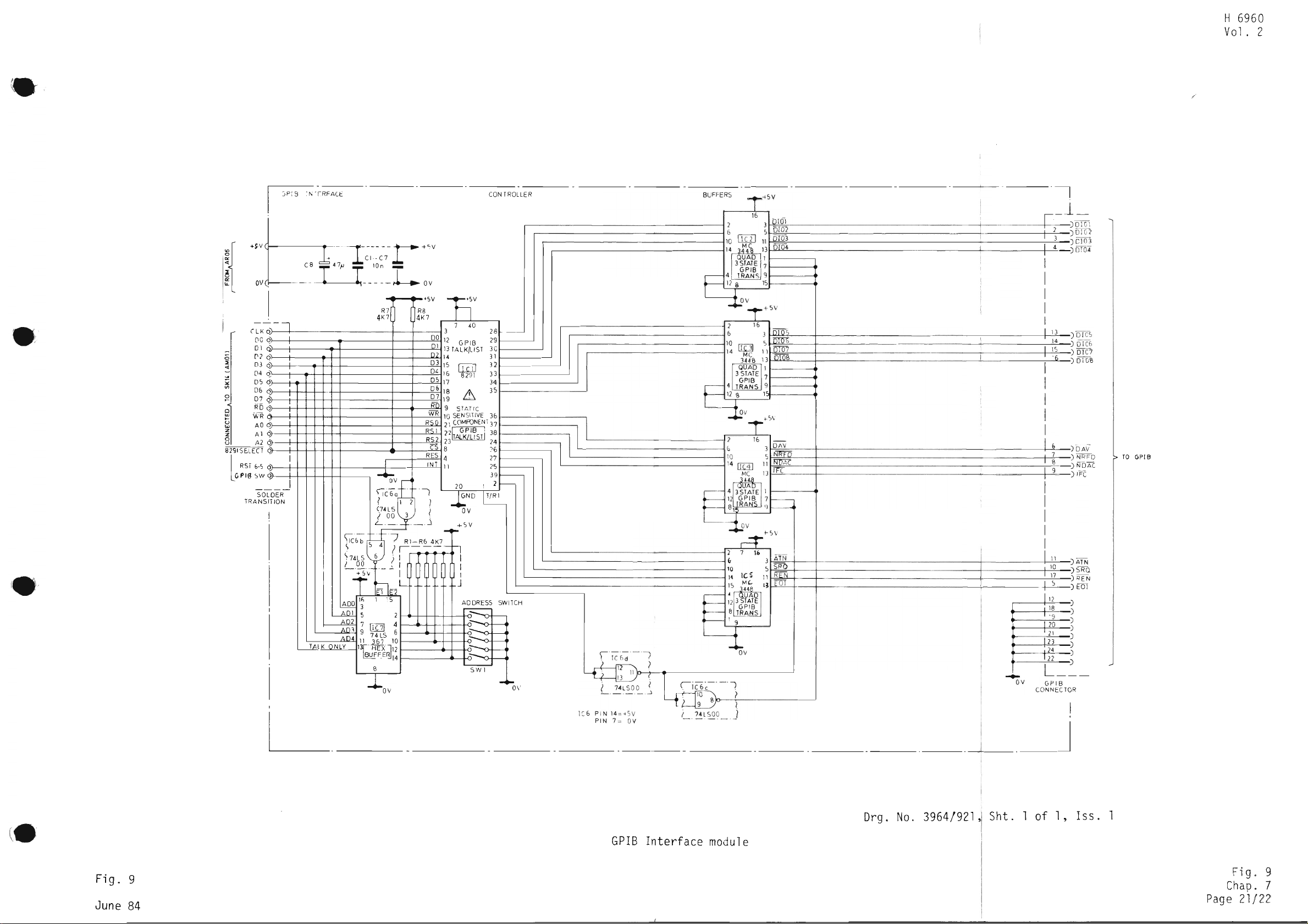

GPIB

direct

interface

Circuit

72.

This

facilities

IEEE 488

73.

ICI (8291

diagram:

module

are

connection

specifications

microprocessor

ICS