MACOM AM55-0024TR, AM55-0024RTR, AM55-0024 Datasheet

Hi Dyn Range 2 Channel IF Amp with

V 2.00

Power Control, 100 - 400 MHz

AM55-0024

Features

n Attenuation: 0.5 dB steps to 31.5 dB

n 6 Bit Digital Gain Control

n CMOS Logic

n Serial Logic Interface

n Single Positive Voltage Supply

n 8 mm PBGA Package

n JEDEC MO-151 Footprint

n Single Package Solution for GSM,CDMA,PCS

Description

The M/A-COM AM55-0024 is a dual channel IF amplifier

and digital attenuator packaged in a multi-layer multi-chip

module (MCM). Gain control is via two separate serial

logic interfaces. The part utilizes Plastic Ball Grid Array

(PBGA) interconnect technology to achieve high circuit

density and superior performance. This device is ideal for

GSM/DCS/PCS digital base station applications where high

dynamic range gain control functionality is required.

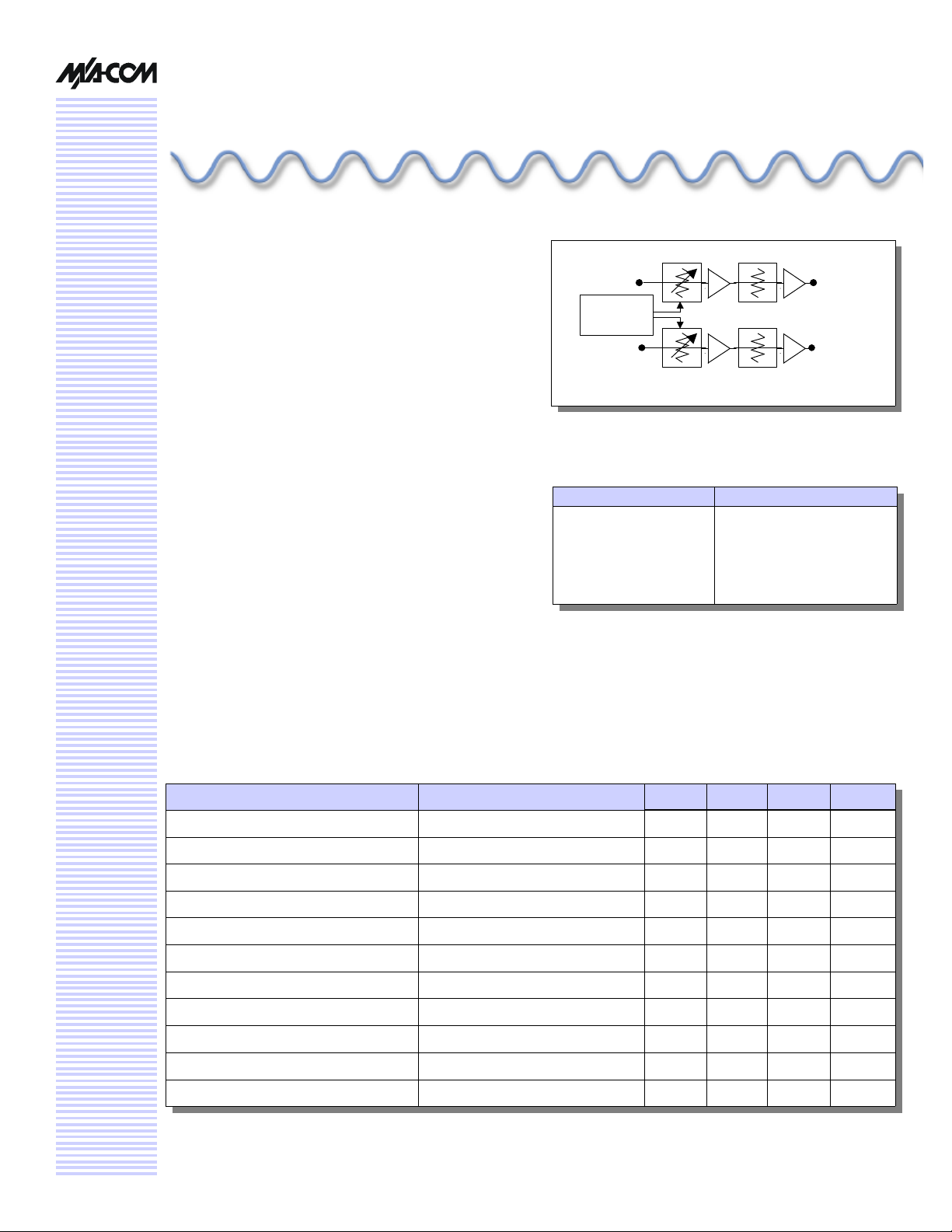

Functional Block Diagram

IF in A

Logic

Interface

IF in B

IF out A

IF out B

Absolute Maximum Ratings 1

Parameter Absolute Maximum

Input Power2 +20 dBm

Operating Voltage2 VDD = +6 V

Operating Temperature -40°C to +85°C

Storage Temperature -65°C to +150°C

1. Exceeding any one or combination of these limits may

cause permanent damage.

2. Ambient Temperature (TA) = +25°C.

Electrical Specifications: TA = 25°C, Z0 = 50Ω 1

Parameter Test Conditions Units Min. Typ. Max.

Gain 100 - 400 MHz

Gain Control Range 100 - 400 MHz dB 31.5

Minimum Gain Control Step Size 100 - 400 MHz dB 0.5

Return Loss 100 - 400 MHz dB 10 12

Output IP3 100 - 400 MHz @ 5V dBm 30

Supply Voltage V 3/5

Supply Current @ 3V / @ 5V mA 300/400

Switching Speed (50% TTL to 90% RF) nS 50

Isolation dBc 50 60

P1 dB dBm 15 17.5

Noise Figure 100 - 400 MHz dB 4

1. All measurements in a 50 Ohm system.

dB 19.5 21 22.5

Hi Dyn Range 2 Channel IF Amp w/Pwr Cntrl, 100 - 400 MHz

3VA13VA23VB13V

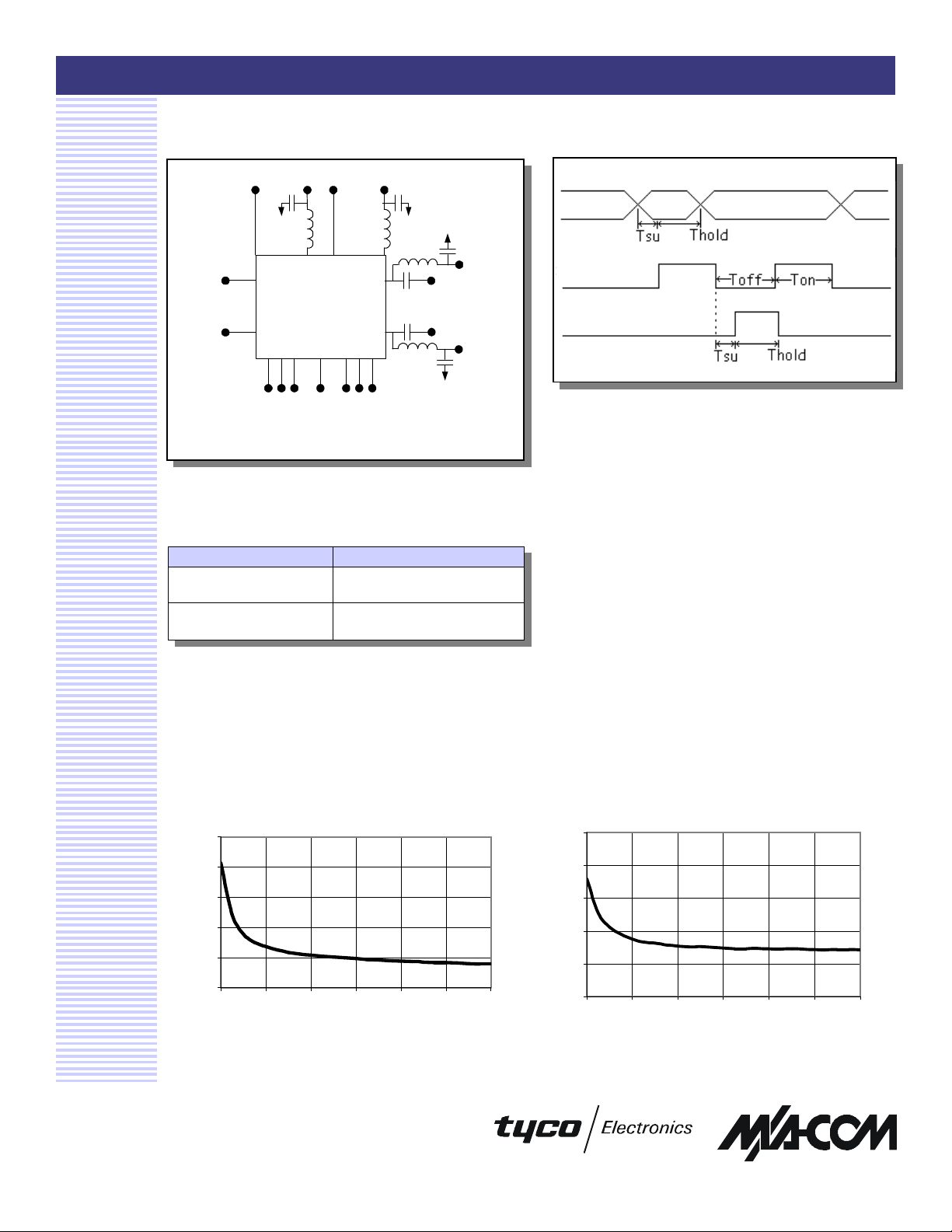

External Components

1, 2, 3

Clock Diagram

1, 2, 3, 4, 5

AM55-0024

V 2.00

B2

IF In A

AM55-0024

IF In B

Data B

Latch A

Digital VDD

Data A

Clk A

1. All inductors are 470 nH

2. All Capacitors are 10000 pF

3. IF outputs must be supplied +3 Volts.

Clk B

Latch B

Component Value

L 470 nH

C 10000 pF

3V A3

IF Out A

IF Out B

3V B3

Data

Clock

Latch

1. Max Clock Speed = 40 MHz

2. Ton = Toff

3. Tsu = >3ns

4. Thold = >7ns

5. Data clocked in on rising clock edge

Serial Interface

Each channel in the AM55-0024 is independently

controllable with a 3 wire serial interface: Clock, Data,

and Latch Enable. These lines can be shared based on

application requirements. The attenuator within the

device is controlled with a 6 bit word, enabling the

selection of 64 possible states. The highest gain state is

'000000', and the lowest is '111111'. The sequence for

shifting the data is as follows: Present data (MSB first),

strobe clock, repeat until 6 bits have been presented and

clocked, then strobe the latch enable line, which

implements the state change.

Typical Performance Curves

Input V

3.5

3.0

2.5

2.0

VSWR (dB)

1.5

1.0

0.045 0.105 0.165 0.225 0.285 0.345 0.405

Specifications subject to change without notice.

n North America: Tel. (800) 366-2266

n Asia/Pacific: Tel.+81-44-844-8296, Fax +81-44-844-8298

n Europe: Tel. +44 (1344) 869 595, Fax+44 (1344) 300 020

Visit www.macom.com for additional data sheets and product information.

SWR

Frequency (GHz)

Output V

3.5

3.0

2.5

2.0

VSWR (dB)

1.5

1.0

0.045 0.105 0.165 0.225 0.285 0.345 0.405

SWR

Frequency (GHz)

2

Loading...

Loading...