Advisory

August 5, 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

Device Advisory for Version 5 of the Device

Register Architecture (RA) Map

RA-1. Reset Bit

The software reset bit (bit 0) of register 0x00 is not functional.

RA-2. Transmit Path AIS Insert Bit

The TXPAISINS bit (bit 5) of register 0x01 produces both AIS-P and AIS-L.

RA-3. STS-1 Loss of Pointer Mask Bit

The STS1LOPMSK bit (bit 2) of register 0x04 masks both STS1LOP and STS1LOF.

RA-4. STS-1 Loss of Frame Mask Bit

The STS1LOFMSK bit (bit 1) of register 0x04 is not functional.

RA-5. VTLABCOM and VTRFIRDICOM Interrupt Bits

Occasionally, it might require multiple reads to clear the composite interrupt bits VTLABCOM (bit 2 of

register 0x05) and VTRFIRDICOM (bit 4 of register 0x05).

Error Insertion (EI)

EI-1. DS1/E1 Alarm Indication Signal

The device does not insert DS1/E1 AIS towards the STS-1 if there is an LOC condition in the incoming DS1/E1

signal.

EI-2. LOC Condition in E1 Loopback Mode

In the absence of an input clock, the device detects an LOC condition and generates TU-AIS upstream, even if the

loopback path is selected (the loopback signal is overwritten by TU-AIS).

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisor

y

(

)

)

(

q

(

g

(

)

g

)

(

)

Device Advisory for Version 5 of the Device August 5, 1999

Error Insertion (EI)

continued

EI-3. False S-BIP, L-BIP, and P-BIP Error Insertion

The device transmits S-BIP, L-BIP, and P-BIP errors when configured for automatic insertion of REI, and certain

STS-1 error conditions such as LOS, LOF, LOP-P, S-BIP, L-BIP, and P-BIP are inserted.

VT Alarms (VT

VT-1. VT Path Payload Label Mismatch

The device reports PLM-V when it detects three consecutive consistent new values for the VT label. This is in compliance with G.783 Section 2.2.2.7 and T1.231 Section 8.1.3.5.2.4.2 specifications, but is not compliant with

GR-253 Section 6.2.1.1.8.C.

VT-2. Failure in the Detection of VT Loss of Pointer Defects

The device also apparently fails to detect an LOP-V defect when it continuously receives a VT pointer word of

6C68

i.e., a value indicating a VT1.5 with an offset of 104 bytes, versus a maximum valid offset of 103 bytes). In

this case, the device inserts the re

nonconformance to GR 253, R6-71).

ure

uired DS1 AIS downstream, but does not subsequently declare an LOP-V fail-

VT-3. Inappropriate Termination of VT Loss of Pointer Defect Condition

After the device has detected an LOP-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

terminated unless a valid pointer is received in three consecutive VT superframes

R6-75

.

the same value as the previous valid pointer. According to GR 253, an LOP-V defect must not be

nonconformance to GR 253,

VT-4. Inappropriate Termination of VT Alarm Indication Signal Defect Condition

After the device has detected an AIS-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

0110

. According to GR 253, an AIS-V defect must not be terminated unless a normal valid pointer is received in

three consecutive VT superframes, or a valid pointer with a set NDF is received in one VT superframe

mance to GR 253, R6-183

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

E-MAIL:

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

CHINA: Microelectr on ic s G r ou p, Lucent Techno lo gies (China) Co. , Ltd., A-F2, 23/F, Zao Fon g U niverse Building, 1800 Zhong Shan Xi Road, Shanghai

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE:

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No

rights under any patent accompany the sale of any such product(s) or information.

the same value as the previous valid pointer and without a set NDF (e.g., with the N bits set to

.

http://www.lucent.com/micro

docmaster@micro.lucent.com

1-800-372-2447

Tel. (65) 778 8833

200233 P. R. China

Tel. (81) 3 5421 1600

Technical Inquiries: GERMANY:

, FAX 610-712-4106 (In CANADA:

, FAX (65) 777 7495

Tel . ( 86) 21 6440 0468, ext. 316

, FAX (81) 3 5421 1700

FRANCE:

(39) 02 6608131

ITALY:

(49) 89 95086 0

(33) 1 40 83 68 00

1-800-553-2448

, F A X ( 86) 21 6440 0652

(Munich), UNITED KINGDOM:

(Paris), SWEDEN:

(Milan), SPAIN:

, FAX 610-712-4106)

Tel. (44) 7000 582 368

(34) 1 807 1441

, FAX (44) 1189 328 148

(44) 1344 865 900

(46) 8 594 607 00

(Madrid)

(Stockholm), FINLAND:

(Ascot),

(358) 9 4354 2800

nonconfor-

(Helsinki),

Copyright © 1999 Lucent Technologies Inc.

All Rights Reserved

August 5, 1999

AY99-025SONT (Must accompany DS99-068SONT)

Advisory, Rev. 2

p

)

August 5, 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

Device Advisory for Version 2 of the Device

Register Architecture (RA) Ma

RA-1. Reset Bit

The software reset bit (bit 0) of register 0x00 is not functional.

RA-2. Transmit Path AIS Insert Bit

The TXPAISINS bit (bit 5) of register 0x01 produces both AIS-P and AIS-L.

RA-3. STS-1 Loss of Pointer Mask Bit

The STS1LOPMSK bit (bit 2) of register 0x04 masks both STS1LOP and STS1LOF.

RA-4. STS-1 Loss of Frame Mask Bit

The STS1LOFMSK bit (bit 1) of register 0x04 is not functional.

RA-5. VTLABCOM and VTRFIRDICOM Interrupt Bits

Occasionally, it might require multiple reads to clear the composite interrupt bits VTLABCOM (bit 2 of

register 0x05) and VTRFIRDICOM (bit 4 of register 0x05).

Error Insertion (EI

EI-1. DS1/E1 Alarm Indication Signal

The device does not insert DS1/E1 AIS towards the STS-1 if there is an LOC condition in the incoming DS1/E1

signal.

EI-2. LOC Condition in E1 Loopback Mode

In the absence of an input clock, the device detects an LOC condition and generates TU-AIS upstream, even if the

loopback is selected (the loopback signal is overwritten by TU-AIS).

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

(

)

g

)

y

(

q

(

g

(

)

g

)

(

)

Device Advisory for Version 2 of the Device August 5, 1999

Error Insertion (EI)

continued

EI-3. False S-BIP, L-BIP, and P-BIP Error Insertion

The device transmits S-BIP, L-BIP, and P-BIP errors when configured for automatic insertion of REI, and certain

STS-1 error conditions such as LOS, LOF, LOP-P, S-BIP, L-BIP, and P-BIP are inserted.

EI-4. Forcing AIS Condition

In order to force AIS using the VTDROP bits, a value of 0x1D must be programmed for DS1 AIS, and a value of

0x1E must be pro

rammed for E1 AIS.

VT Mapping (VT

VT-1. VT Path Payload Label Mismatch

The device reports PLM-V when it detects three consecutive consistent new values for the VT label. This is in compliance with G.783 Section 2.2.2.7 and T1.231 Section 8.1.3.5.2.4.2 specifications, but is not compliant with

GR-253 Section 6.2.1.1.8.C.

VT-2. Failure in the Detection of VT Loss of Pointer Defects

■

The device fails to detect an LOP-V defect or insert the required DS1/E1 AIS do wnstream whe n it receives V T

pointer words with the N bits continuousl

■

The device also apparently fails to detect an LOP-V defect when it continuously receives a VT pointer word of

6C68

i.e., a value indicating a VT1.5 with an offset of 104 bytes, versus a maximum valid offset of 103 bytes). In

this case, the device inserts the re

failure

nonconformance to GR 253, R6-71).

set to 1001 (i.e., with a continuously set NDF).

uired DS1 AIS downstream, but does not subsequently declare an LOP-V

VT-3. Inappropriate Termination of VT Loss of Pointer Defect Condition

After the device has detected an LOP-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

terminated unless a valid pointer is received in three consecutive VT superframes

R6-75

.

the same value as the previous valid pointer. According to GR 253, an LOP-V defect must not be

nonconformance to GR 253,

VT-4. Inappropriate Termination of VT Alarm Indication Signal Defect Condition

After the device has detected an AIS-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

0110

. According to GR 253, an AIS-V defect must not be terminated unless a normal valid pointer is received in

three consecutive VT superframes, or a valid pointer with a set NDF is received in one VT superframe

mance to GR 253, R6-183

the same value as the previous valid pointer and without a set NDF (e.g., with the N bits set to

nonconfor-

.

2 Lucent Technologies Inc.

Advisory, Rev. 2 TMPR28051 STS-1/AU-3 (STM-0) Mapper

(

)

g

g

g

y

g

q

y

(

y

g

p

)

g

August 5, 1999 Device Advisory for Version 2 of the Device

VT Mapping (VT)

continued

VT-5. C-Bit Decodin

In the presence of a receive SONET/SDH bit error rate, the device may destuff the DS1 from the VT1.5 incorrectly.

This is the result of an error in the VT1.5 C-bit decodin

correctin

incorrectl

of this error is that both positions will call for a stuff, resultin

will force downstream e

The minimum time to false decode severit

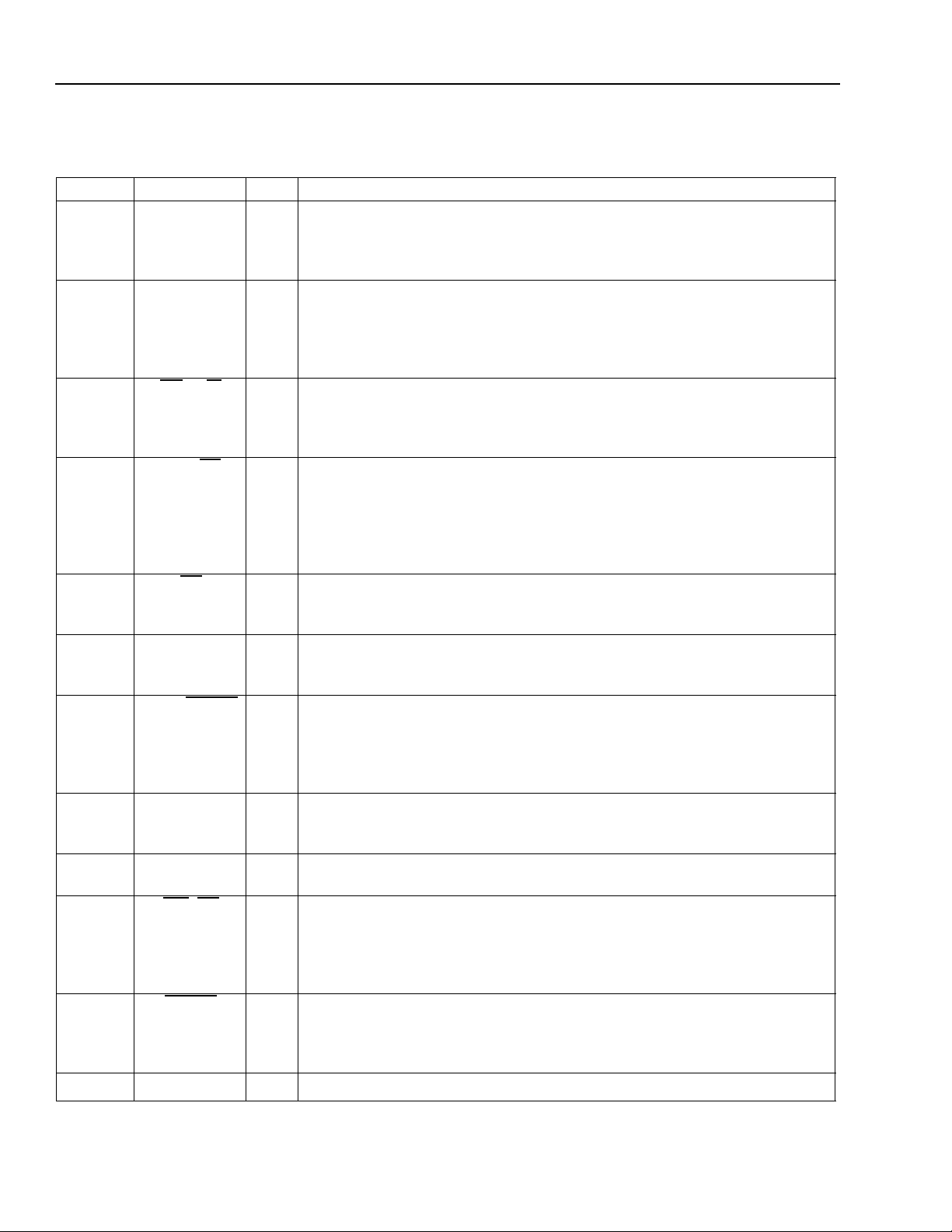

Table VT-5. Minimum Time

single errors to the C bits. Because of this error, an error in the first or second C bit for position 2 will be

decoded if the first C-bit position is calling for a stuff and the second C-bit position is not. The end result

uipment to experience a reframe.

is as shown in Table VT-5 (in terms of seconds to false decode).

in Seconds) to

False Decode Severit

BER Theoretical Actual

10

10

10

10

10

10

10

10

–3

–4

–5

–6

–7

–8

–9

–10

125 0.25

12500 2.5

1250000 25

1.25e+8 250

1.25e+10 2500

1.25e+12 2.5e+4

1.25e+14 2.5e+5

1.25e+16 2.5e+6

of the C Bit

process. The C-bit decoding process should be capable of

in a bit being removed from the DS1 data stream. This

In the absence of an external bit error rate, the al

orithm decodes these C bits correctly.

Test Pattern (TP) Generator/Monitor

TP-1. Test Pattern Insert

The transmitted test pattern comes out on the opposite edge with respect to the jitter-attenuated data.

TP-2. Test Pattern Dro

The test pattern detector always inverts the clock coming into the block before retiming the data.

Jitter Attenuation (JA

JA-1. Jitter Attenuator

The digital jitter attenuator buffers are not functional. The DJACTL bit in register 0x01 should be set to 0 in this

device. Puttin

the device in the jitter attenuator mode (DJACTL = 1) causes loss of transmission.

3Lucent Technologies Inc.

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

)

)

Device Advisory for Version 2 of the Device August 5, 1999

STS Path Overhead (POH

POH-1. False H4LOMF Indication

Forcing a SONET/SDH line level decrement (H1, H2) from a value of either 348 or 347 results in false H4LOMF

indications.

Loss of Data (LOD

LOD-1. Loss of DS1/E1 Data

Simultaneously forcing VT pointer adjustments while forcing SONET/SDH decrements from values of 348 and 347

results in loss of DS1/E1 data.

AY99-026SONT-2 Replaces AY99-026SONT to Incorporate the Following Updates

Added issues RA-5 and EI-3 to the document.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

E-MAIL:

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

CHINA: Microelectr on ic s G r ou p, Lucent Technologies (China) Co., Ltd., A- F 2, 23/F, Zao Fong Univer s e B ui lding, 1800 Zhong Shan Xi Road, Shanghai

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE:

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No

rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1999 Lucent Technologies Inc.

All Rights Reserved

August 5, 1999

AY99-026SONT-2 (Replaces AY99-026SONT and must accompany DS99-068SONT)

http://www.lucent.com/micro

docmaster@micro.lucent.com

1-800-372-2447

Tel. (65) 778 8833

200233 P. R. China

Tel. (81) 3 5421 1600

Technical Inquiries: GERMANY:

, FAX 610-712-4106 (In CANADA:

, FAX (65) 777 7495

Tel . ( 86) 21 6440 0468, ext. 316

, FAX (81) 3 5421 1700

FRANCE:

(39) 02 6608131

ITALY:

(49) 89 95086 0

(33) 1 40 83 68 00

(Milan), SPAIN:

1-800-553-2448

, F A X ( 86) 21 6440 0652

(Munich), UNITED KINGDOM:

(Paris), SWEDEN:

, FAX 610-712-4106)

Tel. (44) 7000 582 368

(46) 8 594 607 00

(34) 1 807 1441

(Madrid)

, FAX (44) 1189 328 148

(44) 1344 865 900

(Stockholm), FINLAND:

(Ascot),

(358) 9 4354 2800

(Helsinki),

Advisory, Rev. 2

p

)

August 5, 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

Device Advisory for Version 3 of the Device

Register Architecture (RA) Ma

RA-1. Reset Bit

The software reset bit (bit 0) of register 0x00 is not functional.

RA-2. Transmit Path AIS Insert Bit

The TXPAISINS bit (bit 5) of register 0x01 produces both AIS-P and AIS-L.

RA-3. STS-1 Loss of Pointer Mask Bit

The STS1LOPMSK bit (bit 2) of register 0x04 masks both STS1LOP and STS1LOF.

RA-4. STS-1 Loss of Frame Mask Bit

The STS1LOFMSK bit (bit 1) of register 0x04 is not functional.

RA-5. VTLABCOM and VTRFIRDICOM Interrupt Bits

Occasionally, it might require multiple reads to clear the composite interrupt bits VTLABCOM (bit 2 of

register 0x05) and VTRFIRDICOM (bit 4 of register 0x05).

Error Insertion (EI

EI-1. DS1/E1 Alarm Indication Signal

The device does not insert DS1/E1 AIS towards the STS-1 if there is an LOC condition in the incoming DS1/E1

signal.

EI-2. LOC Condition in E1 Loopback Mode

In the absence of an input clock, the device detects an LOC condition and generates TU-AIS upstream, even if the

loopback is selected (the loopback signal is overwritten by TU-AIS).

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

(

)

g

)

y

(

q

(

g

(

)

g

)

(

)

Device Advisory for Version 3 of the Device August 5, 1999

Error Insertion (EI)

continued

EI-3. False S-BIP, L-BIP, and P-BIP Error Insertion

The device transmits S-BIP, L-BIP, and P-BIP errors when configured for automatic insertion of REI, and certain

STS-1 error conditions such as LOS, LOF, LOP-P, S-BIP, L-BIP, and P-BIP are inserted.

EI-4. Forcing AIS Condition

In order to force AIS using the VTDROP bits, a value of 0x1D must be programmed for DS1 AIS, and a value of

0x1E must be pro

rammed for E1 AIS.

VT Mapping (VT

VT-1. VT Path Payload Label Mismatch

The device reports PLM-V when it detects three consecutive consistent new values for the VT label. This is in compliance with G.783 Section 2.2.2.7 and T1.231 Section 8.1.3.5.2.4.2 specifications, but is not compliant with

GR-253 Section 6.2.1.1.8.C.

VT-2. Failure in the Detection of VT Loss of Pointer Defects

■

The device fails to detect an LOP-V defect or insert the required DS1/E1 AIS do wnstream whe n it receives V T

pointer words with the N bits continuousl

■

The device also apparently fails to detect an LOP-V defect when it continuously receives a VT pointer word of

6C68

i.e., a value indicating a VT1.5 with an offset of 104 bytes, versus a maximum valid offset of 103 bytes). In

this case, the device inserts the re

failure

nonconformance to GR 253, R6-71).

set to 1001 (i.e., with a continuously set NDF).

uired DS1 AIS downstream, but does not subsequently declare an LOP-V

VT-3. Inappropriate Termination of VT Loss of Pointer Defect Condition

After the device has detected an LOP-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

terminated unless a valid pointer is received in three consecutive VT superframes

R6-75

.

the same value as the previous valid pointer. According to GR 253, an LOP-V defect must not be

nonconformance to GR 253,

VT-4. Inappropriate Termination of VT Alarm Indication Signal Defect Condition

After the device has detected an AIS-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

0110

. According to GR 253, an AIS-V defect must not be terminated unless a normal valid pointer is received in

three consecutive VT superframes, or a valid pointer with a set NDF is received in one VT superframe

mance to GR 253, R6-183

the same value as the previous valid pointer and without a set NDF (e.g., with the N bits set to

nonconfor-

.

2 Lucent Technologies Inc.

Advisory, Rev. 2 TMPR28051 STS-1/AU-3 (STM-0) Mapper

(

)

g

g

g

y

g

q

y

(

y

g

p

)

August 5, 1999 Device Advisory for Version 3 of the Device

VT Mapping (VT)

continued

VT-5. C-Bit Decodin

In the presence of a receive SONET/SDH bit error rate, the device may destuff the DS1 from the VT1.5 incorrectly.

This is the result of an error in the VT1.5 C-bit decodin

correctin

incorrectl

of this error is that both positions will call for a stuff, resultin

will force downstream e

The minimum time to false decode severit

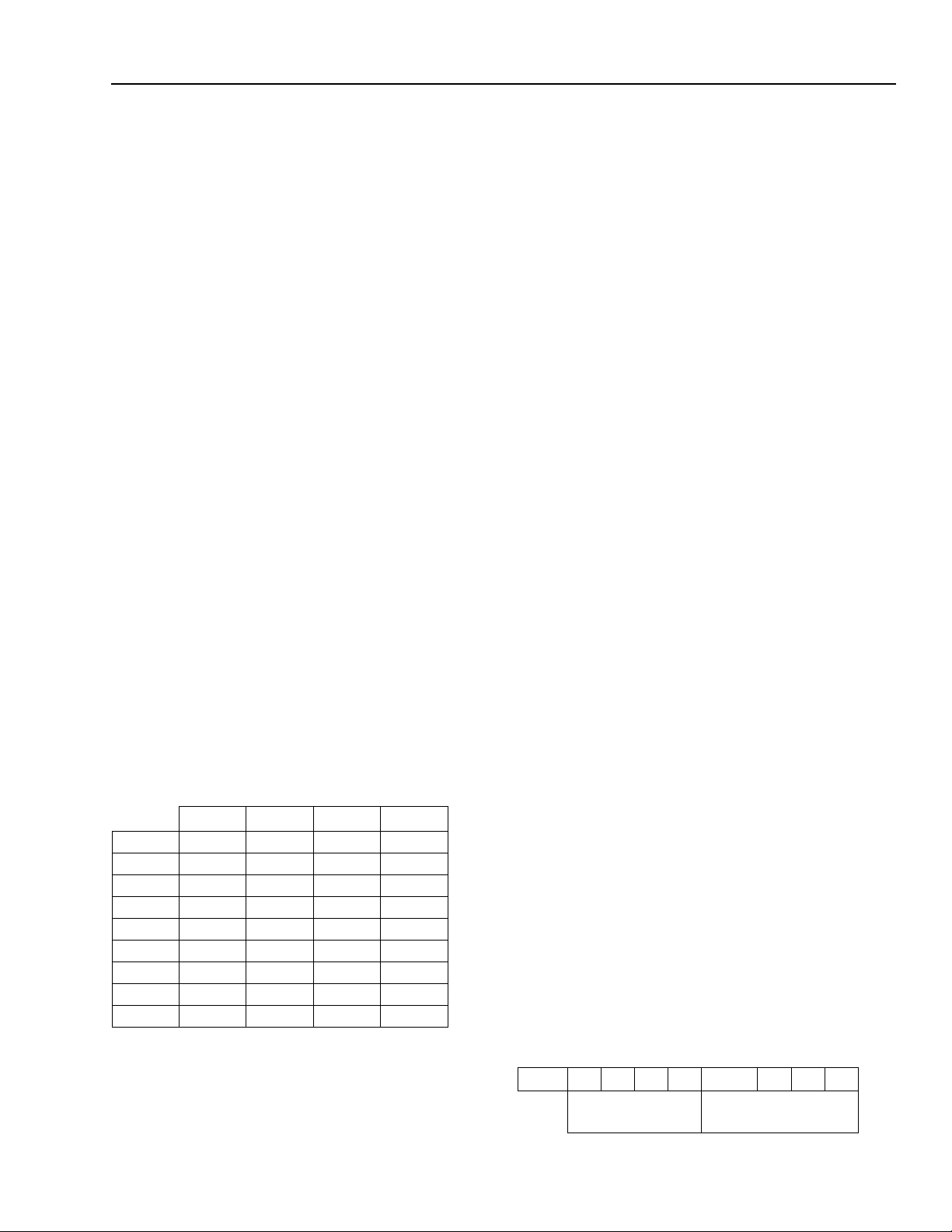

Table VT-5. Minimum Time

single errors to the C bits. Because of this error, an error in the first or second C bit for position 2 will be

decoded if the first C-bit position is calling for a stuff and the second C-bit position is not. The end result

uipment to experience a reframe.

is as shown in Table VT-5 (in terms of seconds to false decode).

in Seconds) to

False Decode Severit

BER Theoretical Actual

10

10

10

10

10

10

10

10

–3

–4

–5

–6

–7

–8

–9

–10

125 0.25

12500 2.5

1250000 25

1.25e+8 250

1.25e+10 2500

1.25e+12 2.5e+4

1.25e+14 2.5e+5

1.25e+16 2.5e+6

of the C Bit

process. The C-bit decoding process should be capable of

in a bit being removed from the DS1 data stream. This

In the absence of an external bit error rate, the al

orithm decodes these C bits correctly.

Test Pattern (TP) Generator/Monitor

TP-1. Test Pattern Insert

The transmitted test pattern comes out on the opposite edge with respect to the jitter-attenuated data.

TP-2. Test Pattern Dro

The test pattern detector always inverts the clock coming into the block before retiming the data.

Device Version (DV

DV-1. Device Version Report

The device version register, 0x16, reports the device version as 0x02.

3Lucent Technologies Inc.

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

Device Advisory for Version 3 of the Device August 5, 1999

AY99-027SONT-2 Replaces AY99-027SONT to Incorporate the Following Updates

Added issues RA-5 and EI-3 to the document.

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

E-MAIL:

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

CHINA: Microelectr on ic s G r ou p, Lucent Technologies (China) Co., Ltd., A- F 2, 23/F, Zao Fong Univer s e B ui lding, 1800 Zhong Shan Xi Road, Shanghai

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE:

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No

rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1999 Lucent Technologies Inc.

All Rights Reserved

http://www.lucent.com/micro

docmaster@micro.lucent.com

1-800-372-2447

Tel. (65) 778 8833

200233 P. R. China

Tel. (81) 3 5421 1600

Technical Inquiries: GERMANY:

, FAX 610-712-4106 (In CANADA:

, FAX (65) 777 7495

Tel . ( 86) 21 6440 0468, ext. 316

, FAX (81) 3 5421 1700

FRANCE:

(39) 02 6608131

ITALY:

(49) 89 95086 0

(33) 1 40 83 68 00

(Milan), SPAIN:

1-800-553-2448

, F A X ( 86) 21 6440 0652

(Munich), UNITED KINGDOM:

(Paris), SWEDEN:

, FAX 610-712-4106)

Tel. (44) 7000 582 368

(46) 8 594 607 00

(34) 1 807 1441

(Madrid)

, FAX (44) 1189 328 148

(44) 1344 865 900

(Stockholm), FINLAND:

(Ascot),

(358) 9 4354 2800

(Helsinki),

August 5, 1999

AY99-027SONT-2 (Replaces AY99-027SONT and must accompany DS99-068SONT)

Advisory, Rev. 2

p

)

August 5, 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

Device Advisory for Version 4 of the Device

Register Architecture (RA) Ma

RA-1. Reset Bit

The software reset bit (bit 0) of register 0x00 is not functional.

RA-2. Transmit Path AIS Insert Bit

The TXPAISINS bit (bit 5) of register 0x01 produces both AIS-P and AIS-L.

RA-3. STS-1 Loss of Pointer Mask Bit

The STS1LOPMSK bit (bit 2) of register 0x04 masks both STS1LOP and STS1LOF.

RA-4. STS-1 Loss of Frame Mask Bit

The STS1LOFMSK bit (bit 1) of register 0x04 is not functional.

RA-5. VTLABCOM and VTRFIRDICOM Interrupt Bits

Occasionally, it might require multiple reads to clear the composite interrupt bits VTLABCOM (bit 2 of

register 0x05) and VTRFIRDICOM (bit 4 of register 0x05).

Error Insertion (EI

EI-1. DS1/E1 Alarm Indication Signal

The device does not insert DS1/E1 AIS towards the STS-1 if there is an LOC condition in the incoming DS1/E1

signal.

EI-2. LOC Condition in E1 Loopback Mode

In the absence of an input clock, the device detects an LOC condition and generates TU-AIS upstream, even if the

loopback is selected (the loopback signal is overwritten by TU-AIS).

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

(

)

)

y

(

q

(

g

(

)

g

)

(

)

Device Advisory for Version 4 of the Device August 5, 1999

Error Insertion (EI)

continued

EI-3. False S-BIP, L-BIP, and P-BIP Error Insertion

The device transmits S-BIP, L-BIP, and P-BIP errors when configured for automatic insertion of REI, and certain

STS-1 error conditions such as LOS, LOF, LOP-P, S-BIP, L-BIP, and P-BIP are inserted.

VT Mapping (VT

VT-1. VT Path Payload Label Mismatch

The device reports PLM-V when it detects three consecutive consistent new values for the VT label. This is in compliance with G.783 Section 2.2.2.7 and T1.231 Section 8.1.3.5.2.4.2 specifications, but is not compliant with

GR-253 Section 6.2.1.1.8.C.

VT-2. Failure in the Detection of VT Loss of Pointer Defects

■

The device fails to detect an LOP-V defect or insert the required DS1/E1 AIS do wnstream whe n it receives V T

pointer words with the N bits continuousl

■

The device also apparently fails to detect an LOP-V defect when it continuously receives a VT pointer word of

6C68

i.e., a value indicating a VT1.5 with an offset of 104 bytes, versus a maximum valid offset of 103 bytes). In

this case, the device inserts the re

failure

nonconformance to GR 253, R6-71).

set to 1001 (i.e., with a continuously set NDF).

uired DS1 AIS downstream, but does not subsequently declare an LOP-V

VT-3. Inappropriate Termination of VT Loss of Pointer Defect Condition

After the device has detected an LOP-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

terminated unless a valid pointer is received in three consecutive VT superframes

R6-75

.

the same value as the previous valid pointer. According to GR 253, an LOP-V defect must not be

nonconformance to GR 253,

VT-4. Inappropriate Termination of VT Alarm Indication Signal Defect Condition

After the device has detected an AIS-V defect, it inappropriately terminates that defect upon receiving two pointer

words containin

0110

. According to GR 253, an AIS-V defect must not be terminated unless a normal valid pointer is received in

three consecutive VT superframes, or a valid pointer with a set NDF is received in one VT superframe

mance to GR 253, R6-183

the same value as the previous valid pointer and without a set NDF (e.g., with the N bits set to

nonconfor-

.

2 Lucent Technologies Inc.

Advisory, Rev. 2 TMPR28051 STS-1/AU-3 (STM-0) Mapper

(

)

g

g

g

y

g

q

y

(

y

g

)

August 5, 1999 Device Advisory for Version 4 of the Device

VT Mapping (VT)

continued

VT-5. C-Bit Decodin

In the presence of a receive SONET/SDH bit error rate, the device may destuff the DS1 from the VT1.5 incorrectly.

This is the result of an error in the VT1.5 C-bit decodin

correctin

incorrectl

of this error is that both positions will call for a stuff, resultin

will force downstream e

The minimum time to false decode severit

Table VT-5. Minimum Time

single errors to the C bits. Because of this error, an error in the first or second C bit for position 2 will be

decoded if the first C-bit position is calling for a stuff and the second C-bit position is not. The end result

uipment to experience a reframe.

is as shown in Table VT-5 (in terms of seconds to false decode).

in Seconds) to

False Decode Severit

BER Theoretical Actual

–3

10

10

10

10

10

10

10

10

–4

–5

–6

–7

–8

–9

–10

125 0.25

12500 2.5

1250000 25

1.25e+8 250

1.25e+10 2500

1.25e+12 2.5e+4

1.25e+14 2.5e+5

1.25e+16 2.5e+6

of the C Bit

process. The C-bit decoding process should be capable of

in a bit being removed from the DS1 data stream. This

In the absence of an external bit error rate, the al

orithm decodes these C bits correctly.

Device Version (DV

DV-1. Device Version Report

The device version register, 0x16, reports the device version as 0x03.

AY99-028SONT-2 Replaces AY99-028SONT to Incorporate the Following Updates

Added issues RA-5 and E1-3 to the document.

3Lucent Technologies Inc.

TMPR28051 STS-1/AU-3 (STM-0) Mapper Advisory, Rev. 2

Device Advisory for Version 4 of the Device August 5, 1999

For additional information, contact your Microelectronics Group Account Manager or the following:

INTERNET:

E-MAIL:

N. AMERICA: Microelectronics Group, Lucent Technologies Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18103

ASIA PACIFIC: Microelectronics Group, Lucent Technologies Singapore Pte. Ltd., 77 Science Park Drive, #03-18 Cintech III, Singapore 118256

CHINA: Microelectr on ic s G r ou p, Lucent Technologies (China) Co., Ltd., A- F 2, 23/F, Zao Fong Univer s e B ui lding, 1800 Zhong Shan Xi Road, Shanghai

JAPAN: Microelectronics Group, Lucent Technologies Japan Ltd., 7-18, Higashi-Gotanda 2-chome, Shinagawa-ku, Tokyo 141, Japan

EUROPE: Data Requests: MICROELECTRONICS GROUP DATALINE:

Lucent Technologies Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application. No

rights under any patent accompany the sale of any such product(s) or information.

Copyright © 1999 Lucent Technologies Inc.

All Rights Reserved

http://www.lucent.com/micro

docmaster@micro.lucent.com

1-800-372-2447

Tel. (65) 778 8833

200233 P. R. China

Tel. (81) 3 5421 1600

Technical Inquiries: GERMANY:

, FAX 610-712-4106 (In CANADA:

, FAX (65) 777 7495

Tel . ( 86) 21 6440 0468, ext. 316

, FAX (81) 3 5421 1700

FRANCE:

(39) 02 6608131

ITALY:

(49) 89 95086 0

(33) 1 40 83 68 00

(Milan), SPAIN:

1-800-553-2448

, F A X ( 86) 21 6440 0652

(Munich), UNITED KINGDOM:

(Paris), SWEDEN:

, FAX 610-712-4106)

Tel. (44) 7000 582 368

(46) 8 594 607 00

(34) 1 807 1441

(Madrid)

, FAX (44) 1189 328 148

(44) 1344 865 900

(Stockholm), FINLAND:

(Ascot),

(358) 9 4354 2800

(Helsinki),

August 5, 1999

AY99-028SONT-2 (Replaces AY99-028SONT and must accompany DS99-068SONT)

Data Sheet

August 1999

TMPR28051 STS-1/AU-3 (STM-0) Mapper

Features

■

Maps signals in one of the following ways:

— Maps up to 28 asynchronous DS1 signals to

SONET STS-1 via VT Groups, or SDH AU-3 via

TUG-2.

— Maps up to 21 asynchronous E1 signals to SDH

AU-3 via TUG-2, or SONET STS-1 via VT

Groups.

— Maps any valid combination of DS1/E1 signals

at the VT Group/TUG-2 level.

■

PLL-free receive operation using built-in digital jitter attenuators.

■

High-speed microprocessor interface configurable

to operate with most commercial microprocessors.

■

Inserts valid B1, B2, and B3 bit interleaved parity

(BIP) in the transmit direction.

■

Detects and counts B1, B2, and B3 BIP-8 errors on

either a bit or block basis for performance monitoring in the receive directio n.

■

Detects and counts V5 BIP-2 errors on either a bit

or block basis for performance monitoring.

■

Configurable continuous B1, B2, B3, and V5 BIP-2

error insertion.

■

Configurable remote error indication (REI) insertion for B2, B3, and V5 BIP-2 errors.

■

Detects and counts remote errors.

■

Built-in test pattern insertion and drop for setup

and maintenance.

■

Configurable VT1.5/TU-1 1 slot selection for DS1

insertion and drop.

■

Configurable VT2/TU-12 slot selection for E1

insertion and drop.

■

Automatic receive monitoring functions can be

configured to provide an interrupt to the control

system, or the device can be operated in a polled

mode.

■

User configurable for VT/TU label, AIS-V, RDI-V,

REI-V, force BIP-2 errors, or unequipped tributary

insertion.

■

Typical 3.3 V operation with 5 V TTL tolerant I/O

and boundary scan.

■

–40 °C to +85 °C temperature range.

■

208-pin shrink quad flat pack (SQFP) package.

■

Provides alarm and control features to easily

implement the latest release of the following standards:

GR253-CORE (12/97 with the exception of

GR-253 section 6.2.1.1.8.C) ,

G.707 (3/96),

G.783 (1/94), G.823.393, T1.105-1995,

T1.105.02-1995, T1.105.03-1994,

T1.105.03A-1995, T1.105.07-1996,

T1.105.09-1996, ETS300.147 (1/95),

ETS300.417-1-1 (1/96).

Applications

■

SONET/SDH path termination multiplexers

■

SONET/SDH add/drop multiplexers

■

SONET/SDH cross connects

■

Digital access cross connects

■

DS1/E1 broadcast

■

SONET/SDH test equipment

Description

■

Detects STS-1 path loss of pointer (LOP-P), loss of

H4 multiframe (H4LOMF), path alarm indication

signal (AIS-P), and path remote defect indication

(RDI-P).

■

Automatic receive monitor functions include VT/TU

remote defect indication (RDI-V), VT/TU remote

error indication (REI-V), BIP-2 errors, VT/TU AIS

(AIS-V), and VT/TU loss of pointer (LOP-V).

The Lucent Technologies Microelectronics Group

TMPR28051 device is designed to map any valid

combination of DS1 and E1 signals into a stream at a

rate of 51.84 Mbits/s. This device provides all of the

functions necessary to insert and drop any valid combination up to 28 asynchronous DS1 signals or 21

asynchronous E1 signals into an SPE.

Data Sheet

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

y

y

y

g

y

g

g

g

TMPR28051 STS-1/AU-3 (STM-0) Mapper August 1999

Table of Contents

Contents Page

Features ...................................................................................................................................................................1

Applications .............................................................................................................................................................. 1

Description ............................... ............. ............. ............. ............. ............. ............. ...... ....... ............. ............. ............1

Block Dia

Pin Information .........................................................................................................................................................6

Nomenclature Assumptions ....................................................................................................................................10

DS1/E1 to STS-1 Block Descriptions .....................................................................................................................10

LOC and AIS Monitor .........................................................................................................................................10

DS1/E1 Loopback Select Lo

Input Select Lo

Elastic Store .......................................................................................................................................................11

VT Generate .......................................................................................................................................................11

STS-1/AU-3 Generate ... ...... ....... ....................................... ...... ....... ...... ...... ....... ...... ....... ................................ ....13

SPE Insertion Lo

STS-1 to DS1/E1 Block Descriptions .....................................................................................................................16

Loopback Select Lo

SPE Locate .........................................................................................................................................................16

STS-1/AU-3 Terminate ............................ ...... ....... ...... ....... ...... ....................................... ...... . ...... ...... ....... ..........16

SPE Drop Lo

VT Terminate ......................................................................................................................................................17

Jitter Attenuate ...................................................................................................................................................18

Drop Select Lo

Test Pattern Block Descriptions .............................................................................................................................19

Test Pattern Insert ..............................................................................................................................................19

Test Pattern Drop ...............................................................................................................................................19

Microprocessor Interface Description .....................................................................................................................20

Overview .............................. ....... ...... ....... ...... ....... ...... ....... ...... ....... ...... ...... ....... ...... ................................. ...... ....20

Microprocessor Confi

Microprocessor Interface Pins ............................................................................................................................21

Re

Re

I/O Timin

Absolute Maximum Ratin

Handlin

Operatin

Electrical Characteristics ........................................................................................................................................66

Timin

Operational Timin

Transmit S

Receive S

T

pical Uses ...........................................................................................................................................................72

Path Termination Multiplex .................................................................................................................................72

Di

Test Pattern Use—Complete S

Test Pattern Use—End to End ...........................................................................................................................73

Outline Dia

208-Pin SQFP ....................................................................................................................................................74

Orderin

DS99-068SONT Replaces DS98-100TIC to Incorporate the Followin

ram .......................................................................................................................................................... 5

ic ............................ ....................................................................... ....................... 10

ic ............................. ................................................................. ................................................. 10

ic .......................... ....................................................................... ........................................... 14

ic .......................................................................................................................................16

ic ................................ ....................................................................... ........................................... 17

ic ...............................................................................................................................................18

uration Modes .................................................................................................................20

ister Architecture Map ..................................................................................................................................23

ister Architecture Description .......................................................................................................................37

................................... ................................................................ ........................................................ 60

s ...................................... ............................................. ............................................. .... 65

Precautions .............. ....... ...... ....... ...... ....................................... ...... ....... ...... ....... ...... ... .... ...... ....... ...... ....65

Conditions ...................... ...... ....... ...... ....... ...... ....... ...... ....... ...... ...... ....................................... ....... ...... ....66

Characteristics ............................................................................................................................................67

.............................................................................................................................................67

nc Timing .................................... ....................................... ....................................... .......................70

nc Timing ..................................... ....................................... ....................................... .......................71

ital Cross Connect .........................................................................................................................................72

stem ................................ ............. ............ ............. ............. ............. ............. ....73

ram .................................... ............. ............. ............. ............. ............. ............. ......... .......... ............. ....74

Information ...............................................................................................................................................75

Updates ...................................................75

2 Lucent Technologies Inc.

Data Sheet

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

August 1999 TMPR28051 STS-1/A U-3 (STM-0) Mapper

List of Figures

Figures Page

Figure 1. Block Diagram .................................... .......................... .......................... .......................... ................... ...... 5

Fi

ure 2. Pin Diagram of 208-Pin SQFP ..................................................................................................................6

Fi

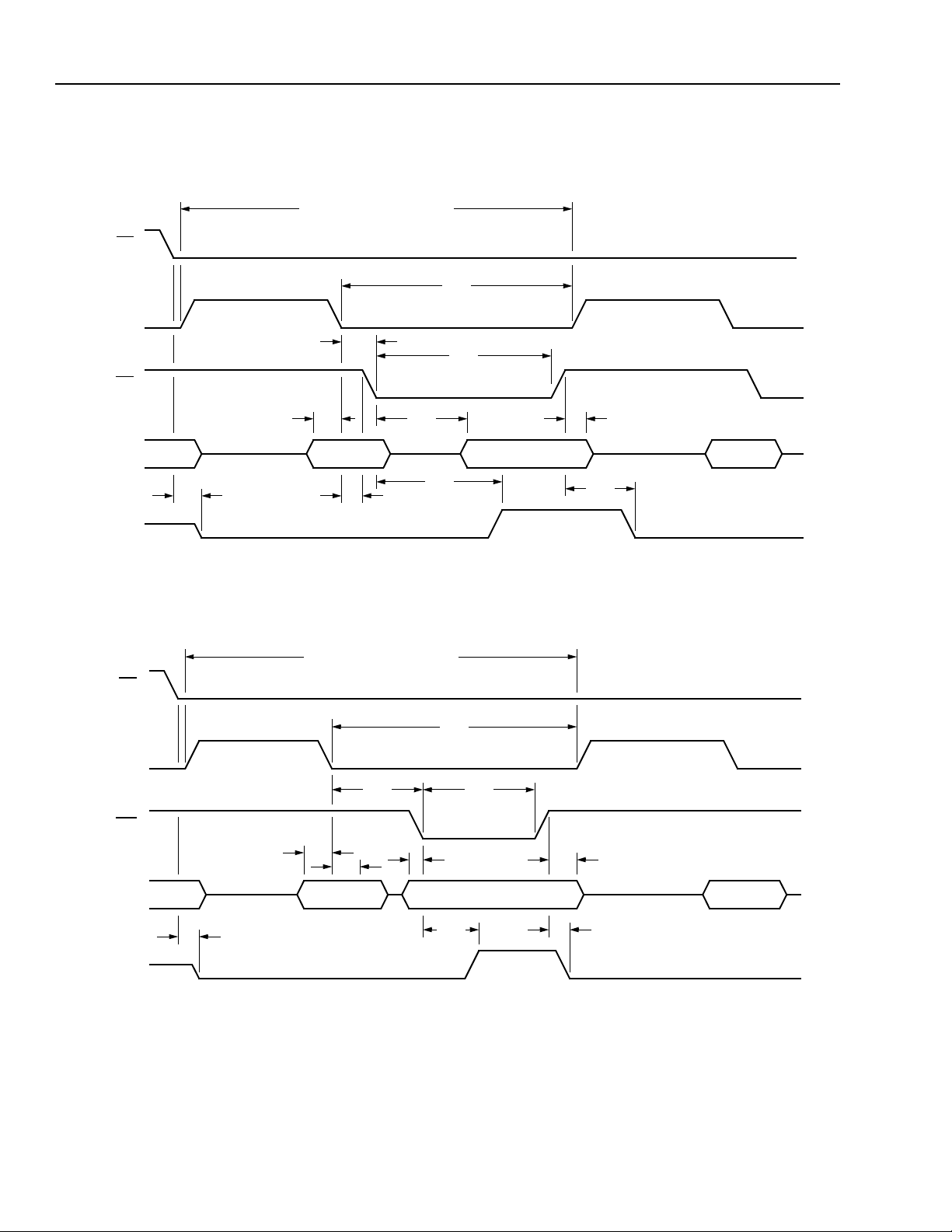

ure 3. Mode 1—Read Cycle Timing (MPMODE = 0, MPMUX = 0) ..................................... ..............................61

Fi

ure 4. Mode 1—Write Cycle Timing (MPMODE = 0, MPMUX = 0) ...................................................................61

Fi

ure 5. Mode 2—Read Cycle Timing (MPMODE = 0, MPMUX = 1) ..................................... ..............................62

Fi

ure 6. Mode 2—Write Cycle Timing (MPMODE = 0, MPMUX = 1) ...................................................................62

Fi

ure 7. Mode 3—Read Cycle Timing (MPMODE = 1, MPMUX = 0) ..................................... ..............................63

Fi

ure 8. Mode 3—Write Cycle Timing (MPMODE = 1, MPMUX = 0) ...................................................................63

Fi

ure 9. Mode 4—Read Cycle Timing (MPMODE = 1, MPMUX = 1) ..................................... ..............................64

Fi

ure 10. Mode 4—Write Cycle Timing (MPMODE = 1, MPMUX = 1) .................................................................64

Fi

ure 11. Interface Data Timing .................................... .......................... .......................... .......................... .......... 68

Fi

ure 12. Serial Mode Transmit Sync Timing ....................................................................................................... 70

Fi

ure 13. Bus Mode Transmit Sync Timing .......................................................................................................... 70

Fi

ure 14. Nonbus Parallel Mode Transmit Sync Timing ...................................... ................................................. 71

Fi

ure 15. Bus Parallel Mode Receive Sync Timing ..............................................................................................71

Fi

ure 16. SDH/SONET Path Termination Multiplex Application ...........................................................................72

Fi

ure 17. Digital Cross Connect Application .........................................................................................................72

Fi

ure 18. Test Pattern Usage for Complete System ............................................................................................73

Fi

ure 19. Test Pattern Usage for End-to-End Operation ......................................................................................73

3Lucent Technologies Inc.

Data Sheet

y

y

y

g

g

g

[

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

g

TMPR28051 STS-1/AU-3 (STM-0) Mapper August 1999

List of Tables

Tables Page

Table 1. Pin Descriptions ......................................................................................................................................... 7

Table 2. VT1.5 Overhead B

Table 3. RFI-V, RDI-V Description ........................................................................................................................ 11

Table 4. VT1.5 Superframe ................................................................................................................................... 12

Table 5. VT2 Superframe ...................................................................................................................................... 12

Table 6. STS-1 Overhead B

Table 7. G1 Path Condition/Performance B

Table 8. VT1.5 SPE Insertion Format .................................................................................................................... 15

Table 9. Mappin

Table 10. VT2 SPE Insertion Format ..................................................................................................................... 15

Table 11. Mappin

Table 12. Microprocessor Conf i

Table 13. Mode

Table 14. Device Re

Table 15. Re

Table 16. Re

Table 17. DS1/E1 Insertion Selection Format ....................................................................................................... 49

Table 18. Re

Table 19. VT Drop Selection Format ..................................................................................................................... 50

Table 20. VT to Address Mappin

Table 21. Re

Table 22. Re

Table 23. Re

Table 24. Re

Table 25. Re

Table 26. Re

Table 27. Re

Table 28. Re

Table 29. Re

Table 30. Re

Table 31. Re

Table 32. Re

Table 33. Microprocessor In terface I/O Timin

Table 34. Absolute Maximum Ratin

Table 35. ESD Threshold Volta

Table 36. Recommended Operatin

Table 37. Lo

Table 38. Input Clock Specifications ..................................................................................................................... 67

Table 39. Input Timin

Table 40. Output Clock Specifications ................................................................................................................... 69

Table 41. Output Timin

of VT1.5 # to (VT Group #, VT #) ................................. ............. ............. ............. ............. ......... 1 5

of VT2 # to (VT Group #, VT #) .................................. ...... ....... ...... ....... ...... ............. ....... ...... ... 15

1—4] Microprocessor Pin Definitions ......................................................................................... 21

ister Map ............................................................................................................................. 23

isters 0x00—0x16: Device-Level Control, Alarm, and Mask Bits .................................................... 37

isters 0x17—0x32: DS1/E1 Insertion Selection ............................................................................. 47

isters 0x33—0x4E: VT Drop Selection ............................................................................................49

isters 0x4F—0x6A: Tx VT Overhead Insertion Control ................................................................... 51

isters 0x6B—0x86: Rx VT Drop Monitoring .................................................................................... 52

isters 0x88—0x89: Signal Override Control .................................................................................... 53

isters 0x8A—0x8F: Digital Jitter Attenuator Controls ...................................................................... 54

ister 0x91: STS-1 LOS Detect/Test Pattern Edge Control .............................................................. 55

ister 0xBF: Block Control ................................................................................................................ 56

isters 0xC0—0xFD: Detected BIP Errors ........................................................................................ 57

isters 0xFE, 0xFF: Received SONET/SDH Pointer Value .............................................................. 57

isters 0xC0—0xFD: Detected REI Errors ........................................................................................ 58

isters 0xFE—0xFF: Reserved ......................................................................................................... 58

isters 0xC0—0xFF: Receive J1 Path Trace Bytes ................................ .......................................... 5 9

isters 0xC0—0xFF: Transmit J1 Path Trace Bytes ............................... .......................................... 5 9

ic Interface Characteristics .............................................................................................................. 66

te Format (V5) ....................................... ............................................. ...................... 11

te Allocation ............................................................................................................. 13

te Format ......................................................................................... 13

uration Modes .................................................................................................... 20

.................................. ....................................................................... ................ 5 0

Specifications .............................................................................. 60

s ............................ ............................................. ....................................... ... 65

e .................................. ....................................................................... ................ 6 5

Conditions ................................................................................................... 66

Specifications .......... ...... ....... ...... ....... ...................................... ....... ...... ....... ...... ....... ...... ... 68

Specifications ................................................................................................................. 69

4 Lucent Technologies Inc.

Data Sheet

(

)

g

g

q

g

q

y

g

g

August 1999 TMPR28051 STS-1/A U-3 (STM-0) Mapper

Description

continued

On the STS-1 side, the device can be configured for either a serial bit stream or an 8-bit parallel bus. This allows

the device to drive an OC-1 optical si

nal directly and also allows for modular growth in terminal or add/drop appli-

cations.

On the DS1/E1 side, the device is desi

or e

uivalent, using the internal digital jitter attenuator buffer for PLL-free operation.

The TMPR28051 device contains built-in test pattern insertion and drop that allows end-to-end testin

setup or maintenance without the need for external test e

E1 sides provide maximum flexibilit

multiplexers, add/drop multiplexers, and di

user pro

rammability for VT slot insertion and drop provide maximum flexibility for DS1/E1 I/O configuration.

ned to interface with the Lucent T7698FL3/T7693 Quad Line Transceiver,

for initial

uipment. Built-in loopbacks at both the STS-1 and DS1/

for use in a number of SONET/SDH or DS1/E1 products including terminal

ital cross connects. A high-speed microprocessor interface and full

Block Diagram

The block diagram is shown in Figure 1. For illustration purposes, only two of the DS1/E1 bidirectional blocks are

shown.

STS-1/AU-3

GENERATE

DS1/E1 #1 IN

LOC AND

AIS

MONITOR

LOOP-

BACK

SELECT

LOGIC

INPUT

SELECT

LOGIC

ELASTIC

STORE

VT

GENERATE

LOC AND

DS1/E1 #n IN

DS1/E1 #1 OUT

DS1/E1 #n OUT

Note: “n” represents 28 or 21 for DS1 or E1, respectively.

MONITOR

TEST

PATTERN

INSERT

AIS

LOOP-

BACK

SELECT

LOGIC

SELECT

SELECT

DROP

LOGIC

DROP

LOGIC

INPUT

SELECT

LOGIC

ELASTIC

STORE

TEST

PATTERN

DROP

JITTER

ATTENUATE

JITTER

ATTENUATE

VT

GENERATE

VT

TERMINATE

VT

TERMINATE

SPE

INSERTION

LOGIC

SPE

DROP

LOGIC

MICROPROCESSOR

INTERFACE

SPE

LOCATE

STS-1/AU-3

TERMINATE

LOOP-

BACK

SELECT

LOGIC

STS-1/AU-3 OUT

STS-1/AU-3 IN

5-4875(F).ar.10

Figure 1. Block Diagram

5Lucent Technologies Inc.

Data Sheet

TMPR28051 STS-1/AU-3 (STM-0) Mapper August 1999

Pin Information

E1BLUECLK

VSS

TCLK11

TDAT A11

RCLK11

RDATA11

RDATA12

RCLK12

TDAT A12

TCLK12

TCLK13

TDAT A13

VDD

RCLK13

RDATA13

RDATA14

RCLK14

TDAT A14

TCLK14

TDO

TRST

VSS

TMS

TDI

TCK

RDY_DTACK

VSS

RD_R/W

MPMODE

MPMUX

ALE_AS

VSS

WR_DS

TCLK15

TDAT A15

RCLK15

RDATA15

RDATA16

RCLK16

TDAT A16

VDD

TCLK16

TCLK17

TDAT A17

RCLK17

RDATA17

RDATA18

RCLK18

TDAT A18

TCLK18

VSS

VSS

208

207

206

205

204

203

202

201

200

199

198

197

196

195

194

193

192

191

190

189

188

187

186

185

184

183

182

181

180

179

178

177

176

175

174

173

172

171

170

169

168

167

166

165

164

163

162

161

160

159

158

VSS

VSS

TCLK10

TDAT A10

RCLK10

RDATA10

RDATA9

RCLK9

TDAT A9

TCLK9

TCLK8

VDD

TDAT A8

RCLK8

RDATA8

RDATA7

RCLK7

TDAT A7

TCLK7

TCLK6

VSS

TDAT A6

RCLK6

RDATA6

RDATA5

VDD

RCLK5

TDAT A5

TCLK5

TCLK4

VSS

TDAT A4

RCLK4

RDATA4

RDATA3

RCLK3

TDAT A3

TCLK3

TCLK2

VDD

TDAT A2

RCLK2

RDATA2

RDATA1

RCLK1

TDAT A1

TCLK1

AD7

AD6

AD5

VSS

VDD

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

36

37

38

39

40

41

42

43

44

45

46

47

48

49

50

51

52

5354555657585960616263646566676869707172737475767778798081828384858687888990919293949596979899

157

156

155

154

153

152

151

150

149

148

147

146

145

144

143

142

141

140

139

138

137

136

135

134

133

132

131

130

129

128

127

126

125

124

123

122

121

120

119

118

117

116

115

114

113

112

111

110

109

108

107

106

105

100

101

102

103

104

ICT

VSS

TCLK19

TDAT A19

RCLK19

RDATA19

VDD

RDATA20

RCLK20

TDAT A20

TCLK20

TCLK21

VDD

TDAT A21

RCLK21

RDATA21

RDATA22

RCLK22

TDAT A22

TCLK22

TCLK23

VSS

TDAT A23

RCLK23

RDATA23

RDATA24

VDD

RCLK24

TDAT A24

TCLK24

TCLK25

VSS

TDAT A25

RCLK25

RDATA25

VDD

RDATA26

RCLK26

TDAT A26

TCLK26

VDD

TCLK27

TDAT A27

RCLK27

RDATA27

VDD

RDATA28

RCLK28

TDAT A28

TCLK28

RESET

VSS

AD3

AD2

AD1

AD0

A7A6A5A4A3

AD4

VSS

VSS

VDD

A2A1A0

VDD

RSTS1PAR

CS

VSS

RSTS1DATA0

RSTS1DATA1

RSTS1DATA2

VSS

VSS

RSTS1DATA3

RSTS1DATA4

RSTS1DATA5

RSTS1DATA6

RSTS1DATA7

INT

VSS

VDD

RSTS1CLK

RSTS1SERIAL

TSTS1CLKOUT

VDD

TSTS1SYNC

TSTS1CLKIN

TSTS1DATA6

TSTS1DATA5

TSTS1DATA4

TSTS1DATA3

TSTS1DATA2

TSTS1DATA1

TSTS1SERIAL/TSTS1DATA7

VSS

VDD

DS1_E1N

TSTS1PAR

TSTS1DATA0

DS1BLUECLK

5-4873(F).cr.5

Figure 2. Pin Diagram of 208-Pin SQFP

6 Lucent Technologies Inc.

Data Sheet

(

)

[

]

y

[

]

y

[

]

g

[

]

g

p

g

y

y

y

g

(

g

(

g

g

g

g

g

g

g

g

August 1999 TMPR28051 STS-1/A U-3 (STM-0) Mapper

Pin Information

continued

Table 1. Pin Descriptions

Pin Symbol Type* Name/Description

47, 39, 38, 30,

TCLK

29, 20, 19, 11,

10, 3, 206, 199,

198, 190, 175,

167, 166, 159,

154, 146, 145,

137, 136, 127,

126, 117, 115,

107

46, 41, 37, 32,

TDATA

28, 22, 18, 13, 9,

4, 205, 200, 197,

191, 174, 169,

165, 160, 153,

147, 143, 138,

134, 128, 124,

118, 114, 108

45, 42, 36, 33,

RCLK

27, 23, 17, 14, 8,

5, 204, 201, 195,

192, 173, 170,

164, 161, 152,

148, 142, 139,

133, 129, 123,

119, 113, 109

44, 43, 35, 34,

RDATA

25, 24, 16, 15, 7,

6, 203, 202, 194,

193, 172, 171,

163, 162, 151,

149, 141, 140,

132, 131, 122,

120, 112, 110

102 DS1_E1N I

101 DS1BLUECLK I

208 E1BLUECLK I

1:28

1:28

1:28

1:28

Transmit DS1/E1 Clock.

O

occup

Transmit DS1/E1 Data.

O

occup

u

Receive DS1/E1 Clock.

I

TCLK[1:21].

TDATA[1:21].

internal 20 kΩ pull-up resist o r. E1 si

u

Receive DS1/E1 Data.

I

nal 20 kΩ pull-up resistor. E1 si

DS1/E1 In

ut Identifier.

DS1/E1 clock output. E1 signals can only

Transmit data output. E1 signals can only

Receive clock input. These pins have an

nals can only occupy RCLK[1:21].

Receive data input. These pins have an inter-

nals can only occupy RDATA[1:21].

If this pin i s pull ed hi

h, the devi ce wi ll d ef aul t

to DS1 to STS-1 mode and transmit 0s in the unused overhead b

and 00 in the SS bits of H1. If pulled low, the device will default to E1 to

AU-3 mode and transmit 1s in the unused overhead b

tes and 10 in

the SS bits of H1. This default selection can be overridden b

TOVERRIDE and ROVERRIDE bits in re

isters 0x88 (bit 0) and 0x89

bit 0), respectively. The seven VT Groups can then be individually pro-

rammed to carry either DS1 (TVTG-1. . . 7 = 1, RVTG-1. . . 7 = 1) or

E1

TVTG-1. . . 7 = 0, RVTG-1. . . 7 = 0) signals.

DS1 Blue Si

unprovisioned DS1 output, this clock si

DS1 blue si

times this rate when usin

E1 Blue Si

unprovisioned E1 output, this clock si

blue si

times this rate when usin

nal Clock.

In the event of a loss of input DS1 clock or an

nal is used to generate the

nal (all 1s). This clock must be 1.544 MHz ± 32 ppm or 16

the digital jitter attenuator.

nal Clock.

In the event of a loss of input E1 clock or an

nal is used to generate the E1

nal (all 1s). This clock must be 2.048 MHz ± 50 ppm or 16

the digital jitter attenuator.

tes

setting

* Iu indicates an internal pull-up; Id indicates an internal pull-down. All I/O not explicitly stated with a buffer type are 5 V TTL compatible; they will

tolerate 5 V at their inputs.

7Lucent Technologies Inc.

Data Sheet

(

)

(

)

p

g

g

(

p

y

g

y

(

y

y

g

y

g

g

(

g

g

y

(

g

p

g

g

g

y

g

g

g

ge (

[

]

p

[

]

p

g

(

y

y

(

(

g

g

(

g

TMPR28051 STS-1/AU-3 (STM-0) Mapper August 1999

Pin Information

Table 1. Pin Descriptions

continued

continued

Pin Symbol Type* Name/Description

179 MPMUX I

Micro

rocessor Multiplex Mode.

Settin

cessor interface to accept the multiplexed address and data si

MPMUX = 0 allows the microprocessor interface to accept demultiplexed

separate) address and data signals.

180 MPMODE I

Micro

latch enable t

write controls. Settin

strobe t

rocessor Mode.

When MPMODE = 1, the device uses the address

pe microprocessor read/write protocol with separate read and

MPMODE = 0 allows the device to use the address

pe microprocessor read/write protocol with a separate data strobe

and a combined read/write control.

181 RD

_R/W I

178 ALE_AS

Read

cessor to initiate a read c

Read/Write.

to indicate a read c

Address Latch Enable.

I

Active-Low).

If MPMODE = 1, this pin is asserted low b

cle.

If MPMODE = 0, th i s pi n is asserted hi

cle or asserted low to indicate a write cycle.

If MPMODE = 1, this pin becomes the address latch

enable for the microprocessor. When this pin transitions from hi

address bus inputs are latched into the internal re

Address Strobe

Active-Low).

If MPMODE = 0, this pin becomes the

address strobe for the microprocessor. When this pin transitions from hi

low, the address bus inputs are latched into the internal re

u

87 CS

86 INT O

183 RDY_DTACK

Chip Select (Active-Low).

I

enable the microprocessor interface

Modes section on pa

Interru

t.

alarm condition in re

microprocessor re

.

Read

O

If MPMODE = 1, this pin is asserted hi

This pin is asserted hi

e20). This pin has an internal 100 kΩ pull-up resistor.

ister 3 or 5. The activation of this pin can be masked by

isters 4 and 6.

This pin is asserted low b

see Microprocessor Configuration

h to indicate an interrupt produced by an

completed a read or write operation. This pin is in a hi

when CS is hi

Data Transfer Acknowled

h.

Active-Low).

asserted low to indicate the device has completed a read or write operation.

48—50,

55—59

AD

7:0

Micro

I/O

become the bidirectional, 3-statable data bus. If MPMUX = 1, these pins

rocessor Interface Address/Data Bus.

become the multiplexed address/data bus.

60—64,

66—68

176 WR

A

7:0

_DS I

Micro

I

address bus for the microprocessor interface re

Write

processor to initiate a write c

Data Strobe

rocessor Interface Address.

Active-Low).

If MPMODE = 1, this pin is asserted low b

cle.

Active-Low).

If MPMODE = 0, this pin becomes the data

If MPMUX = 0, these pins become the

strobe for the mi croprocessor . W hen R/ W = 0

106 RESET

latches the si

u

Hardware Reset (Active-Low).

I

nal on the data bus into internal registers.

If RESET is forced low, all internal states in

the transceiver paths are reset and data flow throu

184 TCK

interrupted

section on pa

u

Boundary-Scan Clock.

I

see Device-Level Control, Alarm, and Mask Bits (0x00—0x16)

e37). This pin has an internal 20 kΩ pull-up resistor.

This pin has an internal 20 kΩ pull-up resistor.

MPMUX = 1 allows the micropro-

nals. Setting

the micropro-

h by the microprocessor

h to low, the

isters.

h to

isters.

the microprocessor to

h to indicate the device has

h-impedance state

If MPMODE = 0, this pin is

If MPMUX = 0, these pins

isters.

the micro-

write), a low applied to this pin

h each channel will be

* Iu indicates an internal pull-up; Id indicates an internal pull-down. All I/O not explicitly stated with a buffer type are 5 V TTL compatible; they will

tolerate 5 V at their inputs.

8 Lucent Technologies Inc.

Data Sheet

(

)

(

)

y

y

y

y

y

[

g

y

y

y

y

(

p

y

[

]

y

g

y

y

g

y

g

g

g

pply

August 1999 TMPR28051 STS-1/A U-3 (STM-0) Mapper

Pin Information

Table 1. Pin Descriptions

continued

continued

Pin Symbol Type* Name/Description

185 TDI

Boundary-Scan Input Data.

I

This pin has an internal 20 kΩ pull-up

u

resistor.

u

186 TMS

Boundary-Scan Mode Select.

I

This pin has an internal 20 kΩ pull-up

resistor.

d

188 TRST

Boundary-Scan Reset (Active-Low).

I

This pin has an internal 20 kΩ

pull-down resistor.

189 TDO O

89 TSTS1CLKIN I

90 TSTS1SYNC I

92,

TSTS1DATA

6:0] O

94—99

100 TSTS1PAR O

Boundar

Transmit STS-1 Clock.

input data, or 19.44 MHz or 6.48 MHz for b

Transmit STS-1 S

8 kHz onl

Transmit STS-1 Data.

of the data bus. TSTS1DATA7 is the most si

b

te.

Transmit STS-1 Parit

-Scan Output Data.

The STS-1 clock can be 51.84 MHz for serial

te-wide data.

nc.

The STS-1 s

nc pulse can be either J0 for

or a composite of J0J1V1 for 2 kHz.

In the byte-wide output mode, this is bit 6—bit 0

.

The parit

output is only defined for byte-wide

nificant bit of the output

data. The device can be provisioned to source either an odd or even

parit

.

91 TSTS1SERIAL/

TSTS1DATA7

Transmit STS-1 Serial Data/Transmit STS-1 Data Bit 7

O

serial mode, this pin provides 51.84 Mbits/s serial data. In parallel

MSB).

In

mode, this pin provides TSTS1DATA7.

88 TSTS1CLKOUT O

82 RSTS1CLK I

80, 78—75,

RSTS1DATA

73—71

7:0

Transmit STS-1 Out

Receive STS-1 Clock.

input data, or 19.44 MHz or 6.48 MHz for b

u

Receive STS-1 Data.

I

with RSTS1DATA7 as the mo st si

ut Clock.

The STS-1 clock can be 51.84 MHz for serial

te-wide data.

In the b

te-wide input mode, this is the data bus

nificant bit of the input byte. This pin

has an internal 100 kΩ pull-up resistor.

u

70 RSTS1PAR

Receive STS-1 Parity.

I

The parit

input is only defined for byte-wide

data. The device can be provisioned to accept either an odd or even

parit

. This pin has an internal 100 kΩ pull-up resistor.

85 RSTS1SERIAL I

Receive STS-1 Serial Data.

If the device is operatin

in the serial

mode, then RSTS1SERIAL is used as the input data pin. In the bus

156 ICT

mode, this pin is used to s

pa

e 71).

u

In-Circuit Test Control (Active-Low).

I

pins are placed in the hi

nchronize byte 1 of 3 (see Figure 15,

If ICT is forced low, all output

h-impedance state. This pin has an internal

20 kΩ pull-up resistor.

1, 2, 21, 31,

SS

V

Ground Reference for Di

I

ital Circuitry.

51, 53, 54, 74,

79, 81, 84,

103, 105, 125,

135, 155, 157,

158, 177, 182,

187, 207

12, 26, 40, 52,

DD

V

I

Power Su

for Digital Circuitry.

65, 69, 83, 93,

104, 111, 116,

121, 130, 144,

150, 168, 196

* Iu indicates an internal pull-up; Id indicates an internal pull-down. All I/O not explicitly stated with a buffer type are 5 V TTL compatible; they will

tolerate 5 V at their inputs.

9Lucent Technologies Inc.

Data Sheet

)

g

g

g

y

(

y

(SS)

g

g

g

y

g

(

y

(

(

(

[

(

g

(

g

g

y by

(

g

(

(

g

g

g

g

[

(

g

(

(

y

y

g

y

)

y

y cy

y

(

(

g

(

y

q

y

[

g

[

g

g

g

g

q

g

q

y

TMPR28051 STS-1/AU-3 (STM-0) Mapper August 1999

Nomenclature Assumptions

The mapping methods (VT1.5, VT2, and VT Group in

ANSI nomenclature; TU-11, TU-12, and TUG-2 in ITU

nomenclature

document will be referred to as VT1.5, VT2, or VT

Group. STS-1 and AU-3 are also analo

minor differences.

For the remainder of this document, the 51.84 Mbits/s

si

nals are referred to as STS-1.

are analogous, and for the rest of this

ous with a few

DS1/E1 to STS-1 Block Descriptions

In the descriptions of the block diagram of Figure 1,

some of the control bits exist for each of the DS1/E1 or

VT si

nals.

Upon start-up, the device will set all of the input data

t

pes (DS1 or E1) based on the level of the DS1_E1N

pin

pin 102). DS1_E1N controls the value transmitted

in the unused overhead b

transmitted spare bits

hi

h, then all of the VT Groups are populated with DS1

si

nals. If this pin is low, then all of the VT Groups are

populated with E1 si

This default selection can be overridden b

TOVERRIDE and ROVERRIDE bits in re

bit 0) and 0x89 (bit 0), respectively. The seven VT

Groups can then be individuall

either DS1

TVTG-1 . . . 7 = 0, RVTG-1 . . . 7 = 0) signals.

TVTG-1 . . . 7 = 1, RVTG-1 . . . 7 = 1) or E1

LOC and AIS Monitor

The incoming DS1/E1 signal is first checked for loss of

clock

LOC). LOC is reported to the microprocessor via

the DS1/E1LOC

LOC = 1, 0 otherwise) in registers 0x17—0x32 (bit 6)

and also via the AISLOCCOM composite bit in re

0x05

bit 1). If LOC is present, the device inserts DS1/

E1 AIS towards the STS-1 usin

The incomin

retimed immediatel

RCLK[28:1]). The edge of the clock that is used to

retime th e dat a is us er-pr ovisio nabl e at th e devi ce lev el

to either the risin

0x02

bit 1) or falling edge (RXDS1EDGE = 0) in regis-

ter 0x02

After bein

checked for AIS. The device will declare AIS if the input

data is at lo

to ei

bit 1).

ht errors in t he 3 ms pe ri od. AI S i s rep or ted to th e

1:21] and DS1LOC[22:28] bit

DS1/E1 data (RDATA[28:1]) is

edge (RXDS1EDGE = 1) in register

retimed, the incoming data stream is

ic 1 for 3 ms. The device will withstand up

tes and the value of the

in the H1 byte. If this pin is

nals.

setting

isters 0x88

programmed to carry

ister

the blue signal clock.

the associated DS1/E1 clock

microprocessor via the AISLOCCOM composite bit in

ister 0x05 (bit 1) and the individual

re

DS1/E1AIS

0x17—0x32

The blue si

at the exact DS1/E1 rate

times the DS1/E1 rate

erance of 32 ppm or 50 ppm for DS1 or E1, respectivel

. This allows users of the Lucent Technologies

T7698FL3/T7693 devices to reuse the XCLK on the

board. The TMPR28051 is provisioned to accept the

exact DS1 rate b

re

ister 0x00), but can be changed to perform the

divide-b

ister 0x00

55% because the data is retimed internall

device. The dut

ance when used for XCLK as described earlier.

1:21] and DS1AIS[22:28] bits in registers

bit 7).

nal clock input signal to the device can be

1.544/2.048 MHz) or at 16

24.704/32.768 MHz), with a tol-

default (BLUECLKSEL = 0 in bit 2 of

-16 function (BLUECLKSEL = 1 in bit 2 of reg. The duty cycle of the clock can be 45%/

in the

cle requires a much tighter toler-

DS1/E1 Loopback Select Logic

The first stage after retiming the signal into the device

is selection of the externall

DS1/E1LB[1:21] or DS1LB[22:28] = 0) or the looped

back DS1/E1

This selection is provisionable per DS1/E1 input in re

isters 0x17—0x32

DS1/E1LB[1:21] or DS1LB[22:28] = 1).

bit 5).

received DS1/E1

Input Select Logic

Once the DS1/E1 data sources have been selected,

the DS1/E1 for each VT tributar

selection re

which DS1/E1 input to use b

DS1/E1INS

re

isters 0x17—0x32 (bits 4 through 0). The range

1:28] following the _ refers to the target VT #. Refer to

Table 8 on pa

on the VT locations within the SPE.

The numberin

ran

es from 00001 to 11100 where the binary value of

the 5 bits corresponds to the DS1/E1 input. For

instance, the value 00001 corresponds to selectin

DS1/E1 #1.

The unused value of 00000 results in VT une

bein

transmitted. This is the default value for all the

VT slots at powerup. VT une

pointer and all-zero pa