Advisory

September 2001

Ambassador

®

T8110

Version History

Introduction

The purpose of this advisory is to provide information on the different versions of the

Ambassador

T8110.

T8110 Version 1

Models of the T8110 V1 had two device issues. The two device issues only affect the microprocessor interface

and packet switching capabilities. The T8110 V1 can function as a 4096 connection standard telephony switch

when using the PCI interface.

Issue 1: Microprocessor interface: The RDY(DTACKn) signal can oscillate if the microprocessor device

driving the microprocessor interface does not relinquish its RDn (or WRn) signal within one

65 MHz clock cycle after the reassertion of RDY (

Intel

®

mode) or deassertion of DTACKn

(

Motorola

®

mode).

Workaround: The processor or board-level component driving the microprocessor port must deassert RDn

or WRn immediately (within 15 ns) upon reassertion of RDY.

Issue 2: Packet switch malfunction: The T8110 does not disable its upper byte lanes on the descriptor

table update, resulting in an over-write of descriptor table data. The descriptor table update

occurs as the last phase of a PCI Master PUSH & PULL cycle. This results in virtual channel

connection malfunctions. TDM switching is unaffected.

Workaround: A systemic workaround for the user is to keep a shadow table for the UOR portion of the

descriptor table.

T81 10 version 1 models can be identified by the markings on the device or by reading the version ID register. If

the last line of the device markings is a 7 digit number followed by no version number, then the device is a version 1. Reading the version ID register 0x00128 will read back a value of 01h, indicating the device is version

1.

Samples of version 1 are no longer available (version 2 samples are now available).

T8110 Version 2

Models of the T8110 V2 have one device issue. The device issue only affects the packet switching capabilities.

The T8110 V2 can function as a 4096 connection standard telephony switch when using either PCI or microprocessor interface.

Issue 1 (from version 1): Fixed. The microprocessor interface issue has been resolved.

Issue 2 (from version 1): Will be fixed in version 3.

T81 10 version 2 models can be identified by the markings on the device or by reading the version ID register. If

the last line of the device markings is a 7 digit number followed by V2, then the device is a version 2. Reading

the version ID register 0x00128 will read back a value of 02h, indicating the device is a version 2.

Samples of version 2 are currently available.

For additional information, contact your local FAE (field application engineer), or call 1-800-372-2447.

Agere Systems Inc. reserves the right to make changes to the product(s) or information contained herein without notice. No liability is assumed as a result of their use or application.

Copyright © 2001 Agere Systems Inc.

All Rights Reserved

September 2001

AY01-038CTI (Replaces AY01-021CTI and must accompany DS00-434CTI)

For additional information, contact your Agere Systems Account Ma nager or the following:

INTERNET: http://www.agere.com

E-MAIL: docmaster@agere.com

N. AMERICA: Agere Systems Inc., 555 Union Boulevard, Room 30L-15P-BA, Allentown, PA 18109-3286

1-800-372-2447, FAX 610-712-4106 (In CANADA: 1-800-553-2448, FAX 610-712-4106)

ASIA: Agere Systems Hong Kong Ltd., Suites 3201 & 3210-12, 32/F, Tower 2, The Gateway, Harbour City, Kowloon

Tel. (852) 3129-2000, FAX (852) 3129-2020

CHINA: (86) 21-5047-1212 (Shangha i) , (86) 10-6522-5566 (Beijing), (86) 755-695-7224 (Shenzhen)

JAPAN: (81) 3-5421-1600 (Tokyo), KOREA: (82) 2-767-1850 (Seoul), SINGAPORE: (65) 778-8833, TAIWAN: (886) 2-2725-585 8 (Taipei)

EUROPE: Tel. (44) 7000 624624, FAX (44) 1344 488 045

Intel

is a registered trademark of Intel Corporation.

Motorola

is a registered trademark of Motorola, Inc.

Data Sheet

May 2001

Ambassador

®

T8110 PCI-Based H.100/H.110 Switch

and Packet Payload Engine

1 Introduction

The T8110 is Agere Systems Inc.’s newest addition

to the

Ambassador

series of computer telephony

integrated circuits. This device not only has the capabilities of previous members of the

Ambassador

series but al so extends them by providing a flexible

interface for switching packet payloads between a

local PCI bus and the H.100/H.110 buses. Packets

may also be switched between the local PCI bus and

local TDM streams. This part is intended to work with

a coprocessor for providing header, framing, and

checksum generation. Since the T8110 operates

purely on payloads, multiple protocols such as IP,

ATM, and A-Bis can therefore be supported simultaneously. To re duce sy st em in t egration costs, sup port

for non-PCI devices is provided through a minibridge.

1.1 Features

n

4,096-connection unified switch

n

Packet payload engine suppor ts up to 512 virt ual

channels

n

Full H.100/H.110 support (32 data lines, all clock

modes)

n

32 local I/O lines (2, 4, 8, or 16 Mbits/s)

n

PCI interface: combined master/slave with burst

n

Microprocessor interface:

Motorola*/Intel

†

modes

n

Minibridge with programmable chip selects

n

Interrupt controller with external inputs

n

Eight independent general-purpose I/O lines

n

Eight independently programmed framing signals

n

Four local clocks

n

T1/E1 rate adaptation

n

Two clock-fallback modes

n

Stratum 4/4E and AT&T 62411 MTIE compliant

n

Incorporates 38 H.100 and 34 H.110 termination

resistors

n

Subrate switching of 4 bits, 2 bits, or 1 bit

n

Backward compatible to all T810x devices

n

JTAG/boundary-scan testing support

n

BSDL files available

n

Assists H.110 hot swap

n

Single 3.3 V supply with 5 V tolerant inputs and

TTL compatible outputs

n

272 PBGA package

n

Evaluation boards available, PCI and

CompactPCI

‡

Hot Swap

5-8921F

Figure 1. Basic Application of the T8110 as a CT

Switch and CT-IP Payload Processor

FRAMERS

AGERE

T8110

COPROCESSOR

ETHERNET

MAC/PHY

MEMORY

PCI-PCI

BRIDGE

TRUNKS

STREAMS

BRIDGE

I/F

STREAMS

& CLOCKS

PCI

10/100

H.100 BUS

LOCAL PCI BUS

HOST PCI BUS

PCI

PCI

PCI

* Motorola

is a registered trademark of Motorola, Inc.

†

Intel

is a registered trademark of Intel Corporation.

‡

CompactPCI

is a registered trademark of the PCI Industrial Computer Manufacturers Group.

Table of Contents

Contents Page

2 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

1 Introduction ............................................................................................................................................................1

1.1 Features .......................................................................................................................................................... 1

2 Pin Description ...................................................................................................................................................... 8

2.1 Interface Signal s .............................................................................................................................................8

2.2 T8110 P inout Inform ation ............................................................................................................................. 11

2.3 Special Buffer Req uir e me n ts ......... ................. ................ ................. ................ ................. ........................ ....18

2.3.1 H1x0 Bus Signal Internal Pull-Up/Pull-Down ................................................................................... 18

2.3.2 Lo cal Bus Signal Internal Pull-Up .................................................................................................... 18

3 Main Architect u r a l Fea tures .................... ................ ................. ................ ................. ................ ................. .........19

3.1 T8110 A rchite cture .......................................................................................................................................19

4 PCI Interface .......................... ................. ................ ................. ................ ................. ....................... ................. ..22

4.1 Target ...........................................................................................................................................................22

4.1.1 PCI Interface Registers .................................................................................................................... 23

4.1.2 Register Space Target Access ........................................................................................................29

4.1.3 Connection Memory Space Target Access .....................................................................................29

4.1.4 Data Memory Space Target Access ................................................................................................29

4.1.4.1 Posted Write Transaction ....................................................................................................29

4.1.4.2 Delayed Read Transact ion ....................... ................ ................. ................ ................. ....... ..30

4.1.5 Virtual Chann el Memory Space Target Access ...............................................................................30

4.1.5.1 Posted Write Transaction ....................................................................................................30

4.1.5.2 Delayed Read Transact ion ....................... ................ ................. ................ ................. ....... ..30

4.1.6 Mini bridge Spac e Target Access . .................................................................................................... 30

4.1.6.1 Posted Write Transaction ....................................................................................................31

4.1.6.2 Delayed Read Transact ion ....................... ................ ................. ................ ................. ....... ..31

4.2 Initiator ..........................................................................................................................................................31

4.2.1 PUSH Operation (Upstream Transaction) .......................................................................................31

4.2.2 PULL Operation (Downstream Transaction) ....................................................................................32

4.3 Configuration Space/EEPROM Interface ......................................................................................................34

4.3.1 Loadable PCI Configuration Space Via EEPROM ...........................................................................36

5 Microproce sso r In te r face .................... ................ ................. ................. ......... ................. ....... ......... ................. ....38

5.1

Intel/Motorola

Protocol Sele ctor ............ .......... ................ ................. ................ ................. ................. ...........38

5.2 Word/Byte Addressing Selector ............... ......... ................. ................ ................. ................ ....... .......... .........38

5.3 Access Via the Microprocessor Bus .............................................................................................................39

5.3.1 Microprocessor Interface Register Map ...........................................................................................40

5.3.2 Register Space Access ....................................................................................................................44

5.3.3 Connection Memor y Sp ace Access ............ ................. ................ ................. ................ ...................44

5.3.4 Data Memory Space Access ...........................................................................................................45

5.3.5 Virtual Chann el Memory Space Access .......................................................................................... 45

6 Operating Control and Status ..............................................................................................................................46

6.1 Control Registers ..........................................................................................................................................46

6.1.1 Reset Registers ...............................................................................................................................46

6.1.2 Master Output Enable Register .......................................................................................................47

6.1.3 Con nection Control—V irtual Chann el Enable and Data Memory Selector Register ........................48

6.1.4 General Clock Control (Phase Alignment, Fallback, Watchdogs) Register .................. .......... ....... ..49

6.1.5 Phase Alignment Select Register ....................................................................................................50

6.1.6 Fallback Control Register ................................................................................................................ 50

6.1.7 Fallback Type Select Register .........................................................................................................51

6.1.8 Fallback Trigger Registers ............................................................................................................... 51

6.1.9 W atchdo g Select, C8, and NETREF Registers ................................................................................52

Table of Contents (continued)

Contents Page

Agere Systems Inc. 3

May 2001 and Packet Payload Engine

Data Sheet

Ambassador

T8110 PCI-Based H.100/H.110 Switch

6.1.10 Watchdog EN Register ....................................................................................................................53

6.1.11 F ailsafe Control Registers ................................................................................................................ 54

6.1.12 External Buffers—Descriptor Table Base Address ..........................................................................55

6.2 Error and Status Registers ...........................................................................................................................55

6.2.1 Clock Errors .....................................................................................................................................56

6.2.1.1 Transient Clock Errors Registers ......................................................................................... 56

6.2.1.2 Latched Clock Error Register ..............................................................................................57

6.2.2 System Status ..................................................................................................................................58

6.2.3 Clock Fallback Status Register ........................................................................................................58

6.2.4 PLL and S witch ing Status Registe r . .................................................................................................58

6.2.5 System Errors Register ....................................................................................................................59

6.2.6 Device Identification Registers .........................................................................................................60

6.2.7 Misc ellaneous Status .......................................................................................................................61

7 Clock Architecture ...............................................................................................................................................62

7.1 Clock Input Control Registers ....................................................................................................................... 63

7.1.1 Main Input Selector Register ........................................... ....... .......... ....... .. ....... .......... .. ..... ...............63

7.1.2 Main Divider Register .......................................................................................................................64

7.1.3 Analog PLL1 (APLL1) Input Selector Register ................................... ..... ....... ....... ....... ..... ....... ..... ...64

7.1.4 APLL1 Rat e Register . ......................................................................................................................65

7.1.5 Main Inversion Select Register ........................................................................................................65

7.1.6 Resource Divider Register ...............................................................................................................66

7.1.7 Analog PLL2 (APLL2) Rate Register ................................... .. .......... ....... ....... .. .......... ....... .. .............66

7.1.8 LREF Input Select Registers ................................................ .. .......... ....... .. ....... .......... ....... ...............67

7.1.9 DPLL1 Input Selector .......................................................................................................................68

7.1.9.1 DPLL1 Rate Register ...........................................................................................................68

7.1.10 DPLL2 Input Selector ................................... .......... .. ....... ....... ..... ....... ....... ....... ..... ....... ....................69

7.1.10.1 DPLL2 Rate Register ...........................................................................................................69

7.1.11 NET REF1 Registers ........................................................................................................................70

7.1.12 NET REF2 Registers ........................................................................................................................71

7.2 Clock Output Control Registers ....................................................................................................................72

7.2.1 Master Output Enables Register ......................................................................................................72

7.2.2 Clock Output Format Registers ........................................................................................................74

7.2.3 TCLK and L_SCx Select Registers ..................................................................................................74

7.3 Clock Register Access ..................................................................................................................................76

7.4 Clock Circuit Operation—A P LL1 ..................................................................................................................76

7.4.1 Main Clock Selection, Bit Clock, and Frame .................................................... .......... .. ....... ........ .....76

7.4.1.1 Watchdog Timers ................................................................................................................77

7.4.1.2 Frame Center Sampling ......................................................................................................78

7.4.2 Main and Resource Dividers ............................................................................................................78

7.4.3 DPLL1 .............................................................................................................................................. 79

7.4.4 Reference Selector ..........................................................................................................................79

7.4.5 Internal Clock Generation ................................................................................................................ 79

7.4.5.1 Phase Alignment .......... ................. ................. ................ ................. ................ ................. ...80

7.5 Clock Circuit Operation, APLL2 ....................................................................................................................81

7.5.1 DPLL2 .............................................................................................................................................. 81

7.6 Clock Circuit Operation, CT_NETR EF Generation .......................................................................................81

7.6.1 NETREF Source Select ...................................................................................................................81

7.6.2 NETREF Divider ..............................................................................................................................81

7.7 Clock Circuit Operation—Fa llback and Fai lsafe ........................................................................................... 82

Table of Contents (continued)

Contents Page

4 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

7.7.1 Clock Fallback .................................................................................................................................82

7.7.1.1 Fallback Events ...................................................................................................................82

7.7.1.2 Fallback Scenarios—Fixed vs. Rotating Secondary ............................................................83

7.7.1.3 H-Bu s Clock Enable/Disabl e on Fallback ............................................................................86

7.7.2 Clock Failsafe ..................................................................................................................................88

7.7.2.1 Failsafe Events .......... ................ .......... ................. ................ ................. ................ . .............88

8 Frame Group and FG I/O .................................................................................................................................... 90

8.1 Frame Group Control Re gisters ............ ................. ................ ................. ................. ....................... ..............90

8.1.1 FGx Lower and Upper Start Registers ............................................................................................. 90

8.1.2 FGx Width Registers ........................................................................................................................ 91

8.1.3 FGx Rate Registers .........................................................................................................................91

8.2 FG7 Timer Option .........................................................................................................................................92

8.2.1 FG7 Count er (Low and High Byte) Registers ..................................................................................92

8.3 FGIO Control Registers ................................................................................................................................ 93

8.3.1 FGIO Data Register .........................................................................................................................93

8.3.2 FGI O Read Ma sk Register .............................................................................................................. 93

8.3.3 FGIO R/W Register .......................................................................................................................... 94

8.4 FG Circuit Operation .....................................................................................................................................95

8.4.1 Frame Group 8 kHz Reference Generation .....................................................................................96

8.4.2 FGIO General-Purpose Bits .............................................................................................................97

8.4.3 Programmable Timer (FG7 Only) .................................................................................................... 97

8.4.4 FG External Interrupts .....................................................................................................................97

8.4.5 FG Diagnostic Test Point Observation .... ........................................................................................97

9 General-Purpose I/O . .......................................................................................................................................... 98

9.1 GPIO Control Registers ................................................................................................................................ 98

9.1.1 GPIO Data Register .........................................................................................................................98

9.1.2 GPIO Read Mask Register ..............................................................................................................99

9.1.3 GPIO R/W Register .........................................................................................................................99

9.1.4 GPIO Override Register .................................................................................................................100

9.2 GP Circuit Operation ...................................................................................................................................100

9.2.1 GPIO General-Purpose Bits ..........................................................................................................101

9.2.2 GP Dual-Purpose Bits GPIO (Override) .........................................................................................1 01

9.2.2.1 GP H.110 Clock Master Indicators (GP0, GP1 Only) ........................................................101

9.2.2.2 PCI_RST# Indicator (GP2 Only) ........................................................................................101

9.2.3 GP External Interrupts ...................................................................................................................101

9.2.4 GP Diagnostic Test Point Observation ..........................................................................................101

10 Stream Rate Control .......................................................................................................................................1 02

10.1 H-Bus Stream Rate Control Registers ...................................................................................................103

10.1.1 H-Bus Rate Registers ....................................................................................................................103

10.2 L-Bus Stream Rate Control Registers ...................................................................................................103

10.2.1 L-Bus Rate Registers ..................................................................................................................... 1 03

10.2.2 L-Bus 16.384 Mbits/s Operation ....................................................................................................104

10.2.3 16 .384 Mbits/s Local I/O Superrate ...............................................................................................105

11 Minibridge ........................................................................................................................................................107

11.1 W ait-State Control Registers .................................................................................................................107

11.1.1 Minibridge Wait-State Control Registers .. ......................................................................................107

11.2 Strobe Control Registers .......................................................................................................................110

11.3 Minibridge Circuit Operation .................................................................................................................. 1 10

11.4 Minibridge Operational Addressing .......................................................................................................1 12

Table of Contents (continued)

Contents Page

Agere Systems Inc. 5

May 2001 and Packet Payload Engine

Data Sheet

Ambassador

T8110 PCI-Based H.100/H.110 Switch

12 Error Reporting and Interrupt Control ..............................................................................................................113

12.1 Interrupt Control Registers ....................................................................................................................113

12.1.1 Interrupts Via External FG[7:0] Registers ......................................................................................113

12.1.1.1 FGIO Interrupt Pending Register ........................................... ....... ..... ....... ....... ..... ....... ..... .113

12.1.2 Interrupts Via External GP[7:0] ......................................................................................................115

12.1.2.1 GPIO Interrupt Pending Register .......................................................................................115

12.1.2.2 GPIO Edge/Level and GPIO Polarity Registers ................................................................1 16

12.1.3 Interrupts Via Internal System Errors .............................................................................................116

12.1.4 System Interrupt Pending High/Low Registers ..............................................................................117

12.1.5 System Interrupt Enable High/Low Registers ................................................................................118

12.1.6 Interrupts Via Internal Clock Errors ................................................................................................ 1 19

12.1.7 Cl ock Interrupt Pending High/Low Registers ................................................................................. 1 20

12.1.8 Cl ock Interrupt Enable High/Low Registers ...................................................................................121

12.1.9 Interrupt Servicing Registers ..........................................................................................................1 22

12.1.9.1 Arbitration Control Register ...............................................................................................122

12.1.10 PCI_INTA Output Select Register ..................................................................................................122

12.1.10.1 SYSERR and CLKERR Output Select Register ................................................................122

12.1.10.2 Interrupt In-Service Registers ...........................................................................................123

12.2 Error Reporting and Interrupt Controller Circuit Operation ....................................................................125

12.2.1 Externally Sourced Interrupts Via FG[7:0], GP[7:0] .......................................................................126

12.2.2 Internally Sourced System Error Interrupts ....................................................................................126

12.2.3 Internally Sourced Clock Error Interrupts .......................................................................................126

12.2.4 Arbitration of Pending Interrupts ....................................................................................................126

12.2.4.1 Arbitration Off .................... ................. ................ ................. ................ ........................ ......126

12.2.4.2 Flat Arbitration ...................................................................................................................126

12.2.4.3 Tier Arbitration ...................................................................................................................1 26

12.2.4.3.1 Pre-Empting Disabled ..................................................................................127

12.2.4.3.2 Pre-Empting Enabled ..................................................................................127

12.2.5 CLKERR Output .............................................................................................................................127

12.2.6 SYSERR Output ....... ......... ................. ................. ................ ................. ................ ................. ........127

12.2.7 PCI_INTA# Output ............................ ................ ................. ................ ................. ........................ ...127

12.2.8 System Handling of Interrupts ........................................................................................................ 127

13 Test and Diagnostics ..................................................... ..... ....... ....... ..... ....... ....... ....... ..... ................. ...............128

13.1 Diagnostics Control Registers ...............................................................................................................128

13.1.1 F G Testpoint Enable Register ........................................................................................................128

13.1.2 GP Testpoint Enable Register .......................................................................................................129

13.1.3 State Counter Modes Registers .....................................................................................................132

13.1.4 Miscellaneous Diagnostics Low Register .................................... ..... .. ..... .. ..... .. ..... ..... .. ..... .. ..... . .....133

13.1.5 External Buffer Retry Timer Register ............................................................................................. 1 34

13.2 Diagnostic Circuit Operation .................................................................................... ..............................135

14 Connection C ontrol—St andard and Virtual Channel ......................................................................................136

14.1 Programming Interface .......................................................................................................................... 1 36

14.1.1 PCI Interface .................... ................. ................ ................. ................ ................. ........................ ...136

14.1.1.1 PCI Connection Memory Programming .............................................................................136

14.1.1.2 PCI Virtual Channel Memory Programming . .....................................................................138

14.1.2 Microproce sso r In te rface .................... ................. ................ ................. ................ ........................ .139

14.1.2.1 Microprocessor Connection Memory Programming .................................................... ......139

14.1.2.2 Microprocessor Virtual Channel Memory Programming ............................................... 144

14.2 Switching Operation ..............................................................................................................................1 46

Table of Contents (continued)

Contents Page

6 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

14.2.1 Memory Architecture and Configuration ........................................................................................ 146

14.2.1.1 Connection Memory ..........................................................................................................146

14.2.1.1.1 Virtual Channel Switching, Nonbonded Connections ..................................147

14.2.1.1.2 Virtual Channel Switching, Bonded Connections ........................................147

14.2.1.2 Data Memory ........ .......... ................ ................. ................ ................. ................ .................148

14.2.1.3 Virtual Channel Memory ....................................................................................................149

14.2.2 Standard Switching . ....................................................................................................................... 149

14.2.2.1 Constant Delay and Minimum Delay Connections ............................................................ 149

14.2.2.2 Pattern Mode ..................................................................................................................... 1 49

14.2.2.3 Subrate ..............................................................................................................................149

14.2.2.3.1 Subrate Switching Overview ........................................................................150

14.2.2.3.2 Subrate Switching Using T8 110 ..................................................................1 51

14.2.2.3.3 Subrate Packing of Outgoing Bytes .............................................................152

14.2.2.3.4 Subrate Unpacking of Incoming Bytes ........................................................153

14.2.3 Virtual Channel (Packet Payload) Switching .................................................................................155

14.2.3.1 Nonbonded Channels ........................................................................................................155

14.2.3.2 Subrate ..............................................................................................................................157

14.2.3.3 Bonded Channels ..............................................................................................................158

14.2.3.4 External Buffer Access ......................................................................................................1 60

14.2.3.4.1 Overview ......................................................................................................160

14.2.3.4 .2 Descript or Table ..................... ................. ................. ................ ................. ..161

14.2.3.4 .3 External Buffer ..... ................. ................. ................ ................. ................ .....162

14.2.3.4 .4 Transfer Pr o to co l ...... .......... ................ ................. ................ ................. .......162

14.2.3.4.5 External Buffer Data Transfer ......................................................................1 64

14.2.3.4.6 Descriptor Table Update ..............................................................................1 64

14.2.3.5 T8110 Packet Switching, Circuit Operation .......................................................................164

14.2.3.5 .1 System Errors Du e to Pa cke t Swi tch ing ....... ................ ................. ..............165

15 Electrical Char ac te r istics ....................... ................ ................. ................ ................. ............................... .........166

15.1 Absolute Maximum Ratings ................................................................................................................... 1 66

15.1.1 Handling Preca u tions ........... ......... ................. ................ ................. ................ ........................ .......166

15.2 Crystal Specificati o n s .......... .......... ................ ................. ................. ................ ........................ ..............166

15.2.1 XTAL1 Crystal ................. ................ ................. ......... ................. ................. .............................. .....166

15.2.2 XTAL2 Crystal ................. ................ ................. ......... ................. ................. .............................. .....167

15.2.3 Reset Pulse ...................................................................................................................................168

15.3 Thermal Considerations for the 272 PBGA ...........................................................................................168

15.4 dc Electrical Characteristics ..................................................................................................................168

15.4.1 PCI Signals ........... .......... ................ ................. ................. ................ ................. ....... ......... ............168

15.4.2 Electrical Drive Specifications, CT_C8 and /CT_FRAME ..............................................................168

15.4.3 All Other Pins .................................................................................................................................169

15.5 H-Bus Timing .........................................................................................................................................169

15.5.1 T iming Diagrams ............................................................................................................................169

15.6 ac Electrical Characteristics ..................................................................................................................170

15.6.1 Skew Timing, H-Bus ......................................................................................................................170

15.7 Hot-Swap ............................................................................................................................................... 171

15.7.1 LPUE (Local Pull-Up Enable) ........................................................................................................1 71

15.8 Decoupling ............................................................................................................................................171

15.9 APLL V

DD Fil te r .................... .......... ................ ................. ................. ................ ................. .....................171

15.10PC Board PBGA Considerations ...........................................................................................................172

15.11Unused Pins ........................... ................ ................. ................. ................ ........................ ................ .....172

Table of Contents (continued)

Contents Page

Agere Systems Inc. 7

May 2001 and Packet Payload Engine

Data Sheet

Ambassador

T8110 PCI-Based H.100/H.110 Switch

15.12 T8110 Evaluation Boards ......................................................................................................................172

15.13 T8110 Ordering Information ..................................................................................................................172

16 Package Out line ... ...........................................................................................................................................1 73

16.1 Pin and Pad Assignments ..................................................................................................................... 173

17 JTAG/Boundary Scan ............................ ................ ................. ................ ................. ........................ ...............177

17.1 The Principle of Boundary-Scan Architecture ........................................................................................1 77

17.1.1 Instruction Register ........................................................................................................................178

17.2 Boundary-Scan Register .......................................................................................................................178

Appendix A. Constant and Minimum Connections ................................................................................................190

A.1 Connection Definitions............................................................................................................................... 1 90

A.2 Delay Type Definitions ...............................................................................................................................190

Appendix B. Register Bit Field Mnemonic Summary.............................................................................................193

8 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description

2.1 Interface Signals

* Intel

is a registered trademark of Intel Corporat ion.

†

Motorola

is a registered tr ademark of Motorola, Inc.

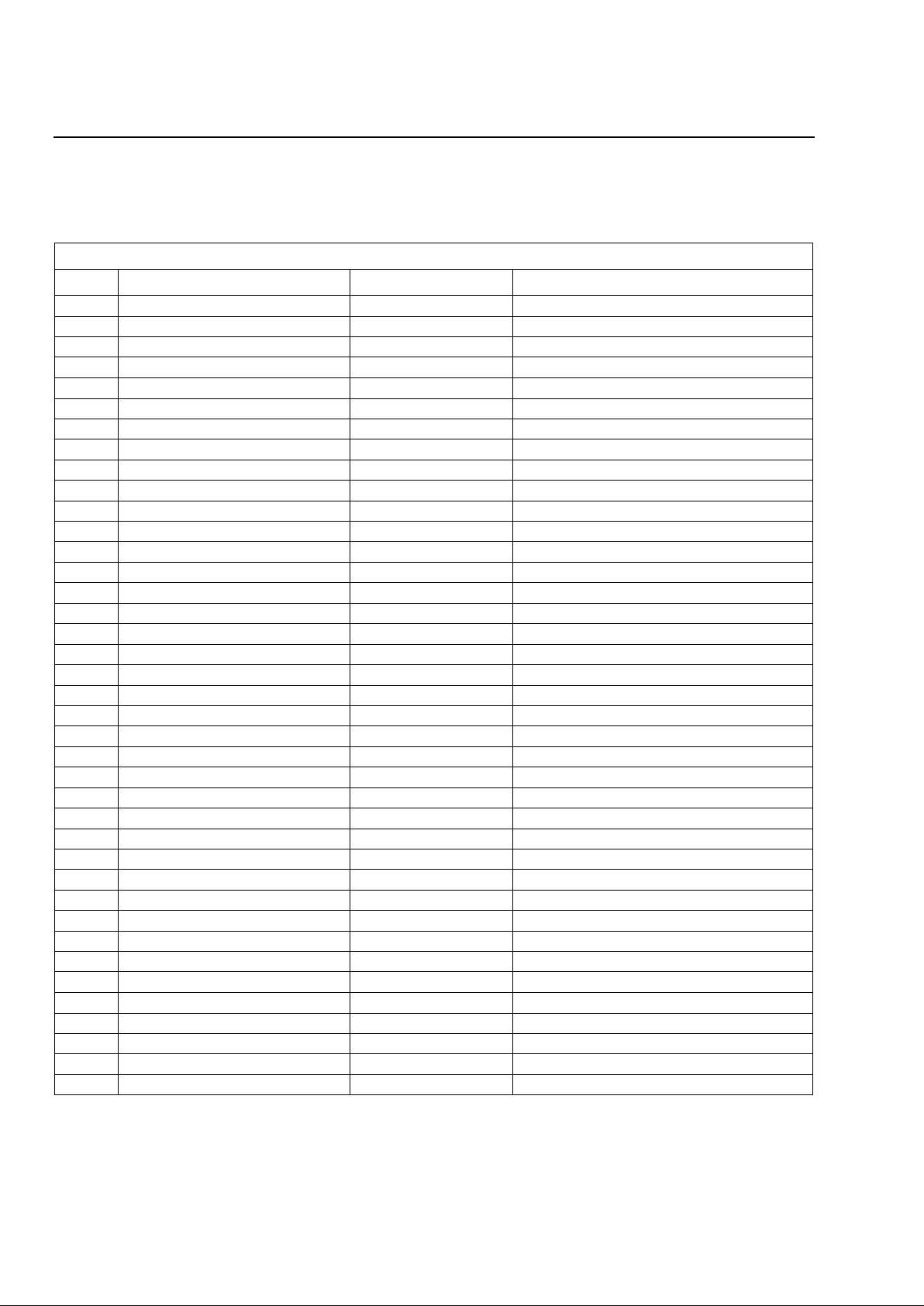

Table 1. Interface Signals

Signal I/O Width Function

PCI_AD I/O 32 PCI bus address/data.

PCI_CBE# I/O 4 PCI bus command/byte enable.

PCI_CLK In 1 PCI bus clock (33 MHz).

PCI_DEVSEL# I/O 1 PCI bus device sel e ct.

PCI_FRAME# I/O 1 PCI bus cycle frame.

PCI_GNT# In 1 PCI bus grant.

PCI_I DSE L In 1 P C I b us in iti aliz ation device selec t .

PCI_INTA# Out 1 PCI bus interrupt.

PCI_IRDY# I/O 1 PCI bus initiator ready.

PCI_LOCK# In 1 PCI bus lock.

PCI_PAR I/O 1 PCI bus parity.

PCI_PERR# I/O 1 PCI bus parity error.

PCI_REQ# Ou t 1 PCI bus request.

PCI_RST# In 1 PCI bus reset.

PCI_SERR# Out 1 PCI bus system error.

PCI_STOP# I/O 1 PCI bus stop.

PCI_TRDY# I/O 1 PCI bus target ready.

T able 2. Minibridge Interface Signals

Signal I/O Width Minibridge Function Microprocessor Interface Function

MB_A I/O 16 Address[15:0] out.

Note: Special power-on function

for PCI core EEPROM.

MB_A[3] = EE_SK_OUT

MB_A[2] = EE_DI_OUT

MB_A[1] = EE_DO_IN

Address[15:0] in.

MB_D I/O 16 Data bus I/O. Data bus in/out.

MB_RD I/O 1 Read strobe output. RDn(DSn) in.

MB_WR I/O 1 Write strobe output. WRn(R/Wn) in.

MB_CS0 I/O 1 Chip select 0 output. Address[16] in.

MB_CS1 I/O 1 Chip select 1 output. Address[17] in.

MB_CS2 I/O 1 Chip select 2 output. Address[18] in.

MB_CS3 I/O 1 Chip select 3 output. Address[19] in.

MB_CS4 I/O 1 Chip select 4 output. CSn in.

MB_CS5 I/O 1 Chip select 5 output. Word/byte select in.

MB_CS6 Out 1 Chip select 6 output. RDY(DTACKn) out.

MB_CS7 I/O 1 Chip select 7 output.

Intel*/Motorola

†

select in.

Agere Systems Inc. 9

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

*

MVIP

is a trademark of Natural MicroSys tems Corporation.

Table 3. H-Bus (H.100/H.110 Interface) Signals

Signal I/O Width Function

VPRECHARGE In 1 Precharge voltage for pull-downs, H.110 bus signals:

CT_D, CT_NETREF1, CT_NETREF2.

H1 10_ENABLE In 1 Pull-down enable for H.110 bus signals: CT_D, CT_NETREF1,

CT_NETREF2.

H100_ENABLE In 1 Pull-up enable for H.100 bus signals: CT_D, CT_NETREF1,

CT_NETREF2, CT_C8_A, CT_C8_B, /CT_FRAME_A, /CT_FRAME_B.

CT_D I/O 32 H.100/H.110 bus data.

CT_C8_A I/O 1 H.100/H.110 bit clock A.

/CT_FRAME_A I/O 1 H.100/H.1 10 frame reference A.

CT_C8_B I/O 1 H.100/H.110 bit clock B.

/CT_FRAME_B I/O 1 H.100/H.1 10 frame reference B.

CT_NETREF1 I/O 1 H.100/H.110 network reference 1.

CT_NETREF2 I/O 1 H.100/H.110 network reference 2.

/C16+ I/O 1 H-

MVIP

* compatibility clock ( 16.384 MH z, differential ).

/C16– I/O 1 H-

MVIP

compatibility clock (16.384 MHz, differential).

/C4 I/O 1

MVIP

compatibility clock (4.096 MHz).

C2 I/O 1

MVIP

compatibility clock (2.048 MHz).

SCLK I/O 1 SC-bus compatib ilit y cloc k .

/SCLK x2 I/O 1 SC- bu s co mp atibility cloc k .

/FR_COMP I/O 1 Compatibi lity frame reference.

Table 4. L-Bus (Local) Interface Signals

Signal I/O Width Function

L_D I/O 32 Local bus data.

L_SC Out 4 Local bus clock output s.

FG I/O 8 Local frame groups.

Table 5. Clock Circuit Interface Signals

Signal I/O Width Function

XTAL1_IN In 1 C rysta l osc illat or #1 input (16.384 MHz ).

XTAL1_OUT Out 1 C r yst al o s cilla t or #1 feedback.

XTAL2_IN In 1 Cryst al osc illato r #2 input (6.176 MHz or 12.352 MHz).

XTAL2_OUT Out 1 C r yst al o s cilla t or #2 fee dback.

10 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Signal I/O Width Function

LREF In 8 Local clock reference inputs.

TCLK_OUT Out 1 Int ernal chip clock output.

PRI_REF_OUT Out 1 Main divider reference out for CLAD/DJAT.

PRI_REF_IN In 1 CLAD/DJAT reference in for APLL1.

NR1_SEL_OUT Out 1 CT_NETREF1 selection out for CLAD/DJAT.

NR1_DIV_IN In 1 CLAD/DJAT reference in for CT_NETREF1 divider.

NR2_SEL_OUT Out 1 CT_NETREF2 selection out for CLAD/DJAT.

NR2_DIV_IN In 1 CLAD/DJAT reference in for CT_NETREF2 divider.

T able 6. GPIO Interface Signals

Signal I/O Wid t h GPIO Function Alter nate Func tion

GP0 I/O 1 GPIO bit 0 I/O A-master indicator out.

GP1 I/O 1 GPIO bit 1 I/O B-master indicator out.

GP2 I/O 1 GPIO bit 2 I/O Forwarded PCI_RST# o ut.

GP3 I/O 1 GPI O bit 3 I/O —

GP4 I/O 1 GPI O bit 4 I/O —

GP5 I/O 1 GPI O bit 5 I/O —

GP6 I/O 1 GPI O bit 6 I/O —

GP7 I/O 1 GPI O bit 7 I/O —

Table 7. Miscellaneous Interface Signals

Signal I/O Width Function

RESET# In 1 Chip reset.

SYSERR Out 1 System error ind icator.

CLKERR Out 1 Clocking error indicator.

LPUE In 1 Pull-up enable for signals: FG, GP, L_D, LREF, MB_D, NR1_DIV_IN,

NR2_DIV_IN, PRI_REF_IN.

EE_CS Out 1 EEPROM chip select.

VIO/µP_SELECT In 1 PCI bus environment, apply GND for microprocessor interface, apply 3.3 V or

5 V for PCI interface.

Table 8. JTAG Signals

Signal I/O Width Function

TRST# In 1 JTAG reset.

TCK In 1 JTAG clock.

TMS In 1 JTAG mode select.

TDI In 1 JTAG data in.

TDO Out 1 JTAG data out.

Table 5. Clock Circuit Interface Signals (continued)

Agere Systems Inc. 11

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

2.2 T8110 Pinout Information

The T8110 package is a 272-pin PBGA ball grid array. Refer to the table below for ball assignment, buffer type, and

pull-up/pull-down information.

Note: The pull-up/down column in the following table is defined as follows:

n

20 kΩ down—20 kΩ pull-down resistor is always in-circuit.

n

50 kΩ up—50 kΩ pull-up resistor is always in-circuit.

n

LPUE: 50 kΩ up—when LPUE = 1, a 50 kΩ pull-up resistor is in-circuit.

n

Enabled: 50 kΩ up/20 kΩ Vpre—when H100_ENABLE = 1, a 50 kΩ pull-up resistor is in-circuit (see Figure 2 on

page 18). When H110_ENABLE = 1, a 20 kΩ pull-down resistor from the VPRECHARGE input to this signal is

in-circuit.

Table 9. T8110 Pinouts

PCI Interface

Ball Pin Name Buffer Type Pull-Up /Down

Y18 PCI_A D0 PCI I/O —

W17 PCI_AD1 PCI I/O —

V16 PCI_A D2 PCI I/O —

U16 PCI_AD3 PCI I/O —

Y17 PCI_A D4 PCI I/O —

Y16 PCI_A D5 PCI I/O —

W16 PCI_AD6 PCI I/O —

V15 PCI_A D7 PCI I/O —

Y15 PCI_A D8 PCI I/O —

W15 PCI_AD9 PCI I/O —

W14 PCI_AD10 PCI I/O —

V14 PCI_AD11 PCI I/O —

Y14 PCI_AD12 PCI I/O —

Y13 PCI_AD13 PCI I/O —

W13 PCI_AD14 PCI I/O —

V13 PCI_AD15 PCI I/O —

Y9 PCI_AD16 PCI I/O —

W9 PCI_AD17 PCI I/O —

V9 PCI_AD18 PCI I/O —

V8 PCI_AD19 PCI I/O —

Y8 PCI_AD20 PCI I/O —

W8 PCI_AD21 PCI I/O —

W7 PCI_AD22 PCI I/O —

V7 PCI_AD23 PCI I/O —

Y7 PCI_AD24 PCI I/O —

Y6 PCI_AD25 PCI I/O —

12 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

PCI Interface (continued)

Ball Pin Name Buffer Type Pull-Up/Down (see note on page 11)

W6 PCI_AD26 PCI I/O —

V6 PCI_AD27 PCI I/O —

Y5 PCI_AD28 PCI I/O —

W5 PCI_AD29 PCI I/O —

V5 PCI_AD30 PCI I/O —

V4 PCI_AD31 PCI I/O —

U14 PCI_CBE0# PCI I/O —

U12 PCI_CBE1# PCI I/O —

U9 PCI_CBE2# PCI I/O —

U7 PCI_CBE3# PCI I/O —

Y3 PCI_CLK PCI input —

W11 PCI_DEVSEL# PCI I/O —

Y10 PCI_FRAME# PCI I/O —

W4 PCI_GNT# PCI input —

W10 PCI_IDSEL PCI input —

Y4 PCI_INTA# PCI output/open drain —

Y11 PCI_IRDY# PCI I/O —

V10 PCI_LOCK# PCI input —

U11 PCI_PAR PCI I/O —

W12 PCI_PERR# PCI I/O —

W3 PCI_REQ# PCI output —

Y2 PCI_RST# PCI input —

V12 PCI_SERR# PCI output/open drain —

V11 PCI_STOP# PCI I/O —

Y12 PCI_TRDY# PCI I/O —

Minibridge Interface

F1 M B_A0 /UP_AO 8 mA I/O-Schmitt 20 kΩ down

G1 MB_A1/UP_A 1/ EE_ DO 8 mA I/O-Schmitt 20 kΩ down

K3 MB_A10/UP_A10 8 mA I/O-Schmitt 20 kΩ down

J3 MB_A 11/UP_A11 8 mA I/O-S chmi tt 20 kΩ down

K1 MB_A12/UP_A12 8 mA I/O-Schmitt 20 kΩ down

K2 MB_A13/UP_A13 8 mA I/O-Schmitt 20 kΩ down

L3 MB_A 14/UP _A 14 8 mA I/O-S chmitt 20 kΩ down

L4 MB_A 15/UP _A 15 8 mA I/O-S chmitt 20 kΩ down

G2 MB_A2/UP_A 2/EE_DI 8 mA I/O-Schmitt 20 kΩ down

G3 MB_A3/UP _A3/EE _SK 8 mA I/O-Schmitt 20 kΩ down

H1 MB_A4/UP_A4 8 mA I/O-Schmitt 20 kΩ down

Agere Systems Inc. 13

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

Minibridge Interface (continued)

Ball Pin Name Buffer Type Pull-Up/Down (see note on page 11)

H2 MB_A5/UP_A5 8 mA I/O-Schmitt 20 kΩ down

H3 MB_A6/UP_A6 8 mA I/O-Schmitt 20 kΩ down

J4 M B_A7/UP _A 7 8 mA I/O-Schmitt 20 kΩ down

J1 M B_A8/UP _A 8 8 mA I/O-Schmitt 20 kΩ down

J2 M B_A9/UP _A 9 8 mA I/O-Schmitt 20 kΩ down

W1 MB_D0 8 mA I/O-Schmitt LPUE: 50 kΩ up

V1 MB_D1 8 mA I/O - Sch mitt LPUE: 50 kΩ up

V2 MB_D2 8 mA I/O - Sch mitt LPUE: 50 kΩ up

U3 MB_D3 8 mA I/O-Schmitt LPUE: 50 kΩ up

U1 MB_D4 8 mA I/O-Schmitt LPUE: 50 kΩ up

U2 MB_D5 8 mA I/O-Schmitt LPUE: 50 kΩ up

T3 MB_D6 8 mA I/O-Schmitt LPUE: 50 kΩ up

T4 MB_D7 8 mA I/O-Schmitt LPUE: 50 kΩ up

T1 MB_D8 8 mA I/O-Schmitt LPUE: 50 kΩ up

T2 MB_D9 8 mA I/O-Schmitt LPUE: 50 kΩ up

R3 MB_D10 8 mA I/O-Schmitt LPUE: 50 kΩ up

P4 MB_D11 8 mA I/O-Schmitt LPUE: 50 kΩ up

R1 MB_D12 8 mA I/O-Schmitt LPUE: 50 kΩ up

R2 MB_D13 8 mA I/O-Schmitt LPUE: 50 kΩ up

P2 MB_D14 8 mA I/O-Schmitt LPUE: 50 kΩ up

P3 MB_D15 8 mA I/O-Schmitt LPUE: 50 kΩ up

N1 MB_RD/UP_RD#(DS#) 8 mA I/O-Schmitt LPUE: 50 kΩ up

P1 MB_WR/UP_WR#(R/W#) 8 mA I/O-Schmitt LPUE: 50 kΩ up

L1 MB_CS 0/UP_A16 8 mA I/O-Schmitt 20 kΩ down

L2 MB_CS 1/UP_A17 8 mA I/O-Schmitt 20 kΩ down

M1 MB_CS2/UP_A18 8 mA I/O-Schmitt 20 kΩ down

M2 MB_CS3/UP_A19 8 mA I/O-Schmitt 20 kΩ down

M3 MB_CS4/UP _ CS N 8 mA I/O-Schmitt LPUE: 50 kΩ up

M4 MB_CS5/UP_WB_SEL 8 mA I/O-Schmi tt LPUE: 50 kΩ up

N2 MB_CS6/UP_RDY(DTACK#) 8 mA 3-state External pull-up required

N3 MB_CS7/IM_SEL 8 mA I/O-Schmi tt LPUE: 50 kΩ up

H-Bus Interface

C1 VPRECHARGE Op amp noninvert —

D5 H110_ENABLE Input 20 kΩ down

D7 H100_E NABL E Input 20 kΩ down

A11 CT_D0 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B11 CT_D1 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C10 CT_D2 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C1 1 CT_D3 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A10 CT_D4 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B10 CT_D5 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

14 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

H-Bus Interface (continued)

Ball Pin Name Buffer Type Pull-Up/Down (see note on page 11)

B9 CT_D6 P CI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C9 CT_D7 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A9 CT_D8 P CI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B8 CT_D9 P CI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C8 CT_D10 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A8 CT_D11 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C7 CT_D12 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A7 CT_D13 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B7 CT_D14 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C6 CT_D15 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A6 CT_D16 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B6 CT_D17 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C5 CT_D18 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A5 CT_D19 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B5 CT_D20 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A4 CT_D21 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B4 CT_D22 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C4 CT_D23 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A3 CT_D24 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B3 CT_D25 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C3 CT_D26 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A2 CT_D27 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B2 CT_D28 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B1 CT_D29 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

C2 CT_D30 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

D2 CT_D31 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

A13 CT_C8_A 24 mA I/O-Schmitt Enabled: 50 kΩ up

A12 /CT_FRAME_A 24 mA I/O-Schmitt Enabled: 50 kΩ up

B13 CT_C8_B 24 mA I/O-Schmitt Enabled: 50 kΩ up

B12 /CT_FRAME_B 24 mA I/O-Schmitt Enabled: 50 kΩ up

A14 CT_NETREF1 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

B14 CT_NETREF2 PCI I/O Enabled: 50 kΩ up/20 kΩ Vpre

D9 /C16+ 24 mA I/O-Schmitt 50 kΩ up

D10 /C16– 24 mA I/O-Schmitt 50 kΩ up

D12 /C4 8 mA I/O-Schmitt 50 kΩ up

D14 C2 8 mA I/O-Schmitt 50 kΩ up

C14 SCLK 24 mA I/O-Schmitt 50 kΩ up

C13 /SCLKX2 24 mA I/O-Schmitt 50 kΩ up

C12 /FR_COMP 24 mA I/O-Sc hmitt 50 kΩ up

Agere Systems Inc. 15

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

L-Bus Interface

Ball Pin Name Buffer Type P ull Up/Down

(see note on page 11)

J20 LD0 8 mA I/O-Schmi tt LPUE: 50 kΩ up

J19 LD1 8 mA I/O-Schmi tt LPUE: 50 kΩ up

J18 LD2 8 mA I/O-Schmi tt LPUE: 50 kΩ up

K17 LD3 8 mA I/O-Schmitt LPUE: 50 kΩ up

K20 LD4 8 mA I/O-Schmitt LPUE: 50 kΩ up

K19 LD5 8 mA I/O-Schmitt LPUE: 50 kΩ up

K18 LD6 8 mA I/O-Schmitt LPUE: 50 kΩ up

L18 LD7 8 mA I/O-Schmitt LPUE: 50 kΩ up

L20 LD8 8 mA I/O-Schmitt LPUE: 50 kΩ up

L19 LD9 8 mA I/O-Schmitt LPUE: 50 kΩ up

M18 LD10 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

M17 LD11 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

M20 LD12 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

M19 LD13 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

N19 LD14 8 mA I/O-Schmitt LPUE: 50 kΩ up

N18 LD15 8 mA I/O-Schmitt LPUE: 50 kΩ up

N20 LD16 8 mA I/O-Schmitt LPUE: 50 kΩ up

P20 LD17 8 mA I/O-Schmitt LPUE: 50 kΩ up

P19 LD18 8 mA I/O-Schmitt LPUE: 50 kΩ up

P18 LD19 8 mA I/O-Schmitt LPUE: 50 kΩ up

R20 LD20 8 mA I/O-Schmitt LPUE: 50 kΩ up

R19 LD21 8 mA I/O-Schmitt LPUE: 50 kΩ up

R18 LD22 8 mA I/O-Schmitt LPUE: 50 kΩ up

P17 LD23 8 mA I/O-Schmitt LPUE: 50 kΩ up

T20 LD24 8 mA I/O-Schmitt LPUE: 50 kΩ up

T19 LD25 8 mA I/O-Schmitt LPUE: 50 kΩ up

T18 LD26 8 mA I/O-Schmitt LPUE: 50 kΩ up

U20 LD27 8 mA I/O-Schmitt LPUE: 50 kΩ up

V20 LD28 8 mA I/O-Schmitt LPUE: 50 kΩ up

U19 LD29 8 mA I/O-Schmitt LPUE: 50 kΩ up

U18 LD30 8 mA I/O-Schmitt LPUE: 50 kΩ up

T17 LD31 8 mA I/O-Schmitt LPUE: 50 kΩ up

H20 L_SC0 8 mA 3-st ate —

H19 L_SC1 8 mA 3-st ate —

H18 L_SC2 8 mA 3-st ate —

G19 L_SC3 8 mA 3-state —

Y20 FG0 8 mA I/O-Schmitt LPUE: 50 kΩ up

Y19 FG1 8 mA I/O-Schmitt LPUE: 50 kΩ up

W20 FG2 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

W19 FG3 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

W18 FG4 8 mA I/O-Sc hmitt LPUE: 50 kΩ up

V19 FG5 8 mA I/O-Schmitt LPUE: 50 kΩ up

V18 FG6 8 mA I/O-Schmitt LPUE: 50 kΩ up

V17 FG7 8 mA I/O-Schmitt LPUE: 50 kΩ up

16 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

Clock Circuit Interface

Ball Pin Name Buffer Type Pull Up/Down (see note on page 11)

B20 XTAL1_IN Input —

C19 XTAL1_OUT Crystal feedback —

E20 XTAL2_IN Input —

F19 XT AL2_OUT Crystal feedback —

A15 LREF0 Input-Schmit t LPUE: 50 kΩ up

B15 LREF1 Input-Schmit t LPUE: 50 kΩ up

C15 LREF2 Input-Sch mi tt LPUE: 50 kΩ up

C16 LREF3 Input-Sch mi tt LPUE: 50 kΩ up

A16 LREF4 Input-Schmit t LPUE: 50 kΩ up

B16 LREF5 Input-Schmit t LPUE: 50 kΩ up

B17 LREF6 Input-Schmit t LPUE: 50 kΩ up

C17 LREF7 Input-Sch mi tt LPUE: 50 kΩ up

G20 TCLK_OUT 8 mA 3-state —

A17 PRI_REF_OUT 8 mA 3-state —

A18 PRI_REF_IN Input-Schmitt LPUE: 50 kΩ up

B18 NR1_SEL_OUT 8 mA 3-state —

A19 NR1_DIV_IN Input-Schmitt LPUE: 50 kΩ up

D19 NR2_SEL_OUT 8 mA 3-state —

C20 NR2_DIV_IN Input-Schmitt LPUE: 50 kΩ up

GPIO Interface

D1 GP0/AMAS TER 8 mA I/O-Schmitt LPUE: 50 kΩ up

E1 GP1/BMASTER 8 mA I/O-Schmitt LPUE: 50 kΩ up

E2 GP2/FWD_PCIRST# 8 mA I/O-Schmitt LPUE: 50 kΩ up

F2 GP3 8 mA I/O-Schmit t LPUE: 50 kΩ up

D3 GP4 8 mA I/O-Schmitt LPUE: 50 kΩ up

F3 GP5 8 mA I/O-Schmitt LPUE: 50 kΩ up

E3 GP6 8 mA I/O-Schmitt LPUE: 50 kΩ up

E4 GP7 8 mA I/O-Schmitt LPUE: 50 kΩ up

Miscellaneous Interfaces

Y1 RESET# Input-Schmitt 50 kΩ up

V3 SYSERR 8 mA 3-state —

W2 CLKERR 8 mA 3-state —

J17 LPUE Input 50 kΩ up

G4 EE_CS 8 mA 3-state —

U5 VIO/µP_SELECT — 20 kΩ down

JTAG Interface

C18 TRST# Input-Schmitt 50 kΩ up

E18 TCK Input-Schmitt 50 kΩ up

D18 TMS Input-Schmitt 50 kΩ up

F18 TDI Input-Schmitt 50 kΩ up

G18 TDO 4 mA 3-state —

Agere Systems Inc. 17

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

Table 9. T8110 Pinouts (continued)

Power

Ball Pin Name Buffer Type Pull Up/Down

B19 APLL1VDD Analog VDD —

E19 AP LL2V

DD Analog VDD —

D6 V

DD ——

D11 V

DD ——

D15 V

DD ——

F4 V

DD ——

F17 V

DD ——

K4 V

DD ——

L17 V

DD ——

R4 V

DD ——

R17 V

DD ——

U6 V

DD ——

U10 V

DD ——

U15 V

DD ——

Ground

A1 V

SS ——

D4 V

SS ——

D8 V

SS ——

D13 V

SS ——

D17 V

SS ——

H4 V

SS ——

H17 V

SS ——

N4 V

SS ——

N17 V

SS ——

U4 V

SS ——

U8 V

SS ——

U13 V

SS ——

U17 V

SS ——

Therma l Gr oun d

J9—12 — — —

K9—12 — — —

L9—12 — — —

M9—12 — — —

No Connects

A20 No connects must be left unconnected.

D16

D20

E17

F20

G17

18 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

2 Pin Description (continued)

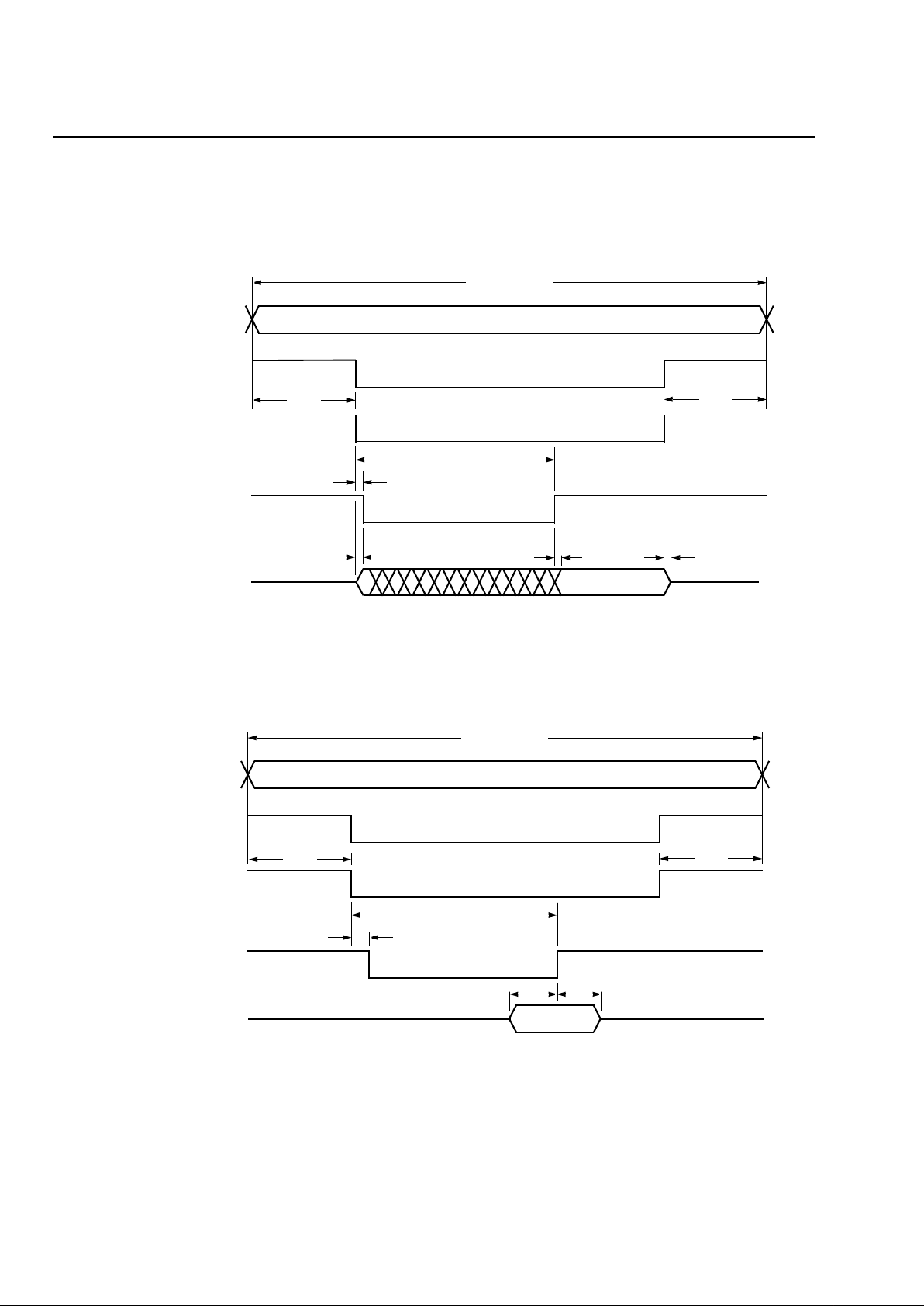

2.3 Special Buffer Requirements

2.3.1 H1x0 Bus Signal Internal Pull-Up/Pull-Down

The H1x0 bus pins require special consideration for H.100 and H.110 usage. There are two control pins to select

between various internal bus pull-ups/pull-downs, as shown below:

n

H100_ENABLE. Enables internal 50 kΩ pull-ups on CT_Dn, CT_NETREF1, CT_NETREF2, CT_C8_A,

CT_C8_B, /CT_FRAME_A, and /CT_FRAME_B signals.

n

H1 10_ENABLE. Enables internal 20 kΩ pull-downs on all 32 CT_Dn signals, CT_NETREF1, and CT_NETREF2

to the VPRECHARGE signal.

Note: The two H1x0 enables are active-high. Only one or the other should ever be asserted.

Warning: Do not assert both at the same time.

Please refer to Figure 2 for more detail.

5-9611 (F)

Figure 2. T8110 Pull-Up/Pull-Down Arrangement for H1x0 Pins

2.3.2 Local Bus Signal Internal Pull-Up

The LPUE input is active-high; and is used to activate pull-ups on the following local signals: GP[7:0], FG[7:0],

MB_D[15:0], LD[31:0], LREF[7:0], PRI_REF_IN, NR1_DIV_IN, and NR2_DIV_IN.

PAD

PAD

PAD

PAD

50 kΩ, MIN

PAD

20 kΩ, MIN

V

DD

V

DD

50 kΩ, MIN

CT_C8_A, CT_C8_B,

/CT_FRAME_A, /CT_FRAME_B

TO OTHER

CT_Dn

VPRECHARGE

H100_ENABLE

H110_ENABLE

CT_Dn, CT_NETREF1, CT_NETREF2

APPLY 0.7 V, NOMINAL

Agere Systems Inc. 19

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

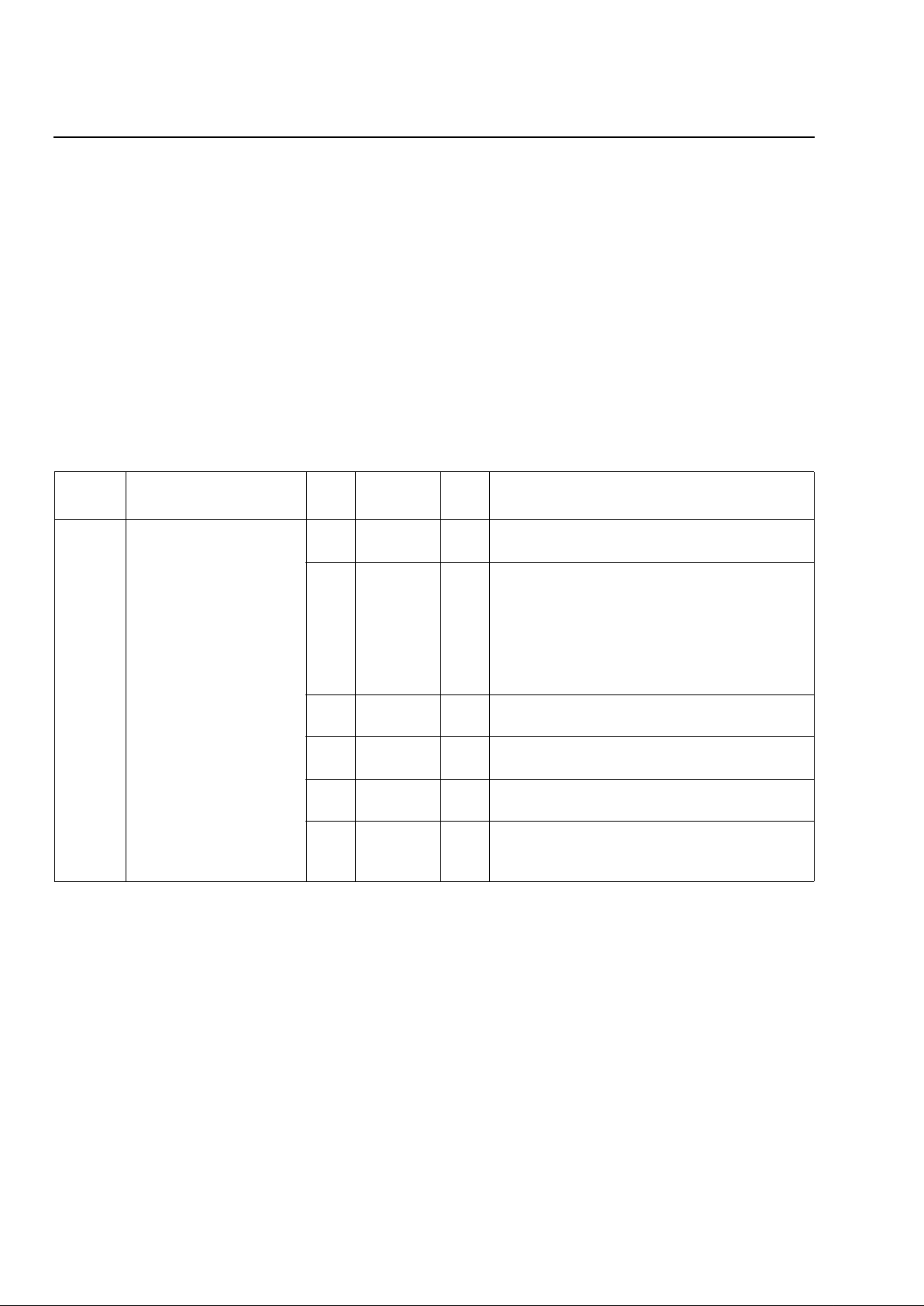

3 Main Architectural Features

3.1 T8110 Architecture

The T8110 includes all of the clocking and standard switching functions found on previous

Ambassador

devices,

plus additional functionalities which are described in the following sections. There are two architectures: PCI (see

Section 4 on page 22) and microprocessor (see Section 5 on page 38).

The local PCI bus interface allows the T81 10 to act as a target (access control registers, memories, etc.) and as an

initiator. The T8110 performs standard H-bus/L-bus switching, and the capability of the initiator allows an interface

for switching packet payloads to/from the H-bus/L-bus; see Section 14, starting on page 136, for more details. With

this architecture selection, the minibridge port converts PCI target accesses into a simple handshake, and passes

these accesses to external devices connected to this port; see Section 11, starting on page 107.

The microprocessor bus interface allows the T81 10 to perform standard H-bus/L-bus switching (i.e., there is no

packet payload switching between the H-bus/L-bus and the microprocessor port). With this architecture, the

minibridge port is used as the microprocessor bus port, and the PCI interface is ignored.

5-8920 (F)

Figure 3. T8110 Block Dia g ra m

ERROR

SIGNALS

GENERAL-

PURPOSE

I/O

BRIDGE

SIGNALS

FRAME

GROUPS

ADDITIONAL

I/O

INTERRUPT

AND

ERROR

CONTROL

GENERALPURPOSE

I/O

MINIBRIDGE

CLOCKING

AND TIMING

CONTROL

H1x0 EVEN

CONNECTION

MEMORY

H1x0 ODD

CONNECTION

MEMORY

LOCAL HIGH

CONNECTION

MEMORY

LOCAL LOW

CONNECTION

MEMORY

CONNECTION

MEMORY

CONTROLLER

REGISTER

ACCESS

CONTROL

PCI MASTER/SLAVE CORE WITH BURST

(LOCAL) PCI BUS

SYSTEM

ERRORS

INTERNAL

CLOCKS

LOCAL

CLOCKS

H1x0

CLOCKS

ERRORS

CLOCK

FG

TIMING

VIRTUAL

CHANNEL

CONTROLLER

DATA

MEMORY

CONTROLLER

DATA

MEMORY

2K x 8

DATA

MEMORY

2K x 8

PARALLEL-TO-SERIAL CONVERSION (OUTPUT)

SERIAL-TO-PARALLEL CONVERSION (INPUT)

H1x0

STREAMS

(BIDIRECTIONAL)

LOCAL

STREAMS

(BIDIRECTIONAL)

FRAME

GROUPS

AND GP I/O

20 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

3 Main Architectural Features (continued)

5-9423a (F)

Figure 4. T8110 Architecture 1—PCI Bus Interface

INTERRUPT

CONTROLLER

GENERAL-PURPOSE

REGISTER

LOCAL BUS

BRIDGE

CONTROLLER

FRAME GRP

TIMING

DERIVATION

APLL1

APLL2

DATA

PAGE 1 LO

VALID FLAG

STORE

H.100 EVEN

CONNECTION

MEMORY

VALID FLAG

STORE

H.100 ODD

CONNECTION

MEMORY

VALID FLAG

STORE

LOCAL HI

CONNECTION

MEMORY

VALID FLAG

STORE

LOCAL LOW

CONNECTION

MEMORY

DATA

PAGE 1 HI

DATA

PAGE 2

MEMORY BIST

CONTROLLER

SCAN

INTERFACE

DATA MEMORY

ACCESS SCHEDULER

SETUP/CONTROL

REGISTERS

REGISTER

ACCESS

CONTROLLER

CONNECTION

MEMORY

ACCESS

CONTROLLER

DATA

MEMORY

ACCESS

CONTROLLER

(DIAGNOSTICS)

PCI CORE

DATA MEMORY

ACCESS

CONTROLLER

(PACKET SWITCH)

PULL

FIFO

NOTIFY

FIFO

NOTIFY

PENDING

PUSH

FIFO

VIRTUAL

CHANNEL

MEMORY

ACCESS

CONTROLLER

SCRATCH

VCMEM

STATIC

PARALLEL-TO-SERIAL (OUTPUT)

SERIAL-TO-PARALLEL (INPUT)

CONVERSION

RESETN

65.536 MHz

32.768 MHz

16.384 MHz

FRAME SYNC

TARGET BUS INITIATOR BUS

EEPROM I/F

PCI BUS

LOCAL STREAMS

(BIDIRECTIONAL)

H.100 STREAMS

(BIDIRECTIONAL)

JTAG/SCAN

PORT

16.384

MHz

6.176 MHz

OR

12.352 MHz

H.100 CLOCKS,

LOCAL

CLOCKS

MINIBRIDGE PORT GENERAL-PURPOSE I/O LOCAL INTERRUPTS, ERROR FLAGS FRAME GROUPS

Agere Systems Inc. 21

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

3 Main Architectural Features (continued)

5-9424 (F)

Figure 5. T8110 Architecture 2—Microprocessor Bus Interface

INTERRUPT

CONTROLLER

GENERAL-PURPOSE

REGISTER

FRAME GRP

TIMING

DERIVATION

APLL1

APLL2

DATA

PAGE 1 LO

VALID FLAG

STORE

H.100 EVEN

CONNECTION

MEMORY

VALID FLAG

STORE

H.100 ODD

CONNECTION

MEMORY

VALID FLAG

STORE

LOCAL HI

CONNECTION

MEMORY

VALID FLAG

STORE

LOCAL LOW

CONNECTION

MEMORY

DATA

PAGE 1 HI

DATA

PAGE 2

MEMORY BIST

CONTROLLER

SCAN

INTERFACE

DATA MEMORY

ACCESS SCHEDULER

SETUP/CONTROL

REGISTERS

REGISTER

ACCESS

CONTROLLER

CONNECTION

MEMORY

ACCESS

CONTROLLER

DATA

MEMORY

ACCESS

CONTROLLER

(DIAGNOSTICS)

PARALLEL-TO-SERIAL (OUTPUT)

SERIAL-TO-PARALLEL (INPUT)

CONVERSION

RESETN

65.536 MHz

32.768 MHz

16.384 MHz

FRAME SYNC

TARGET BUS

LOCAL STREAMS

(BIDIRECTIONAL)

H.100 STREAMS

(BIDIRECTIONAL)

JTAG/SCAN

PORT

6.176 MHz

OR

12.352 MHz

H.100 CLOCKS ,

LOCAL

CLOCKS

MINIBRIDGE PORT GENERAL-PURPOSE I/O LOCAL INTERRUPTS, ERROR FLAGS FRAME GROUPS

NO CONNECTION

PCI BUSEEPROM I/F

PCI CORE

16.348 MHz

MICROPROCESSOR

INTERFACE

22 Agere Systems Inc.

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

4 PCI Interface

The T8110 provides a selection of two interface mechanisms via the VIO/µP_SELECT input. This must be a static

signal (either pulled high or pulled low).

n

VIO/µP_SELECT tied to GND = T8110 interface to a microprocessor bus, connected via the minibridge port.

n

VIO/µP_SELECT tied to 3.3 V = T8110 interface to a local PCI bus, 3.3 V signaling.

n

VIO/µP_SELECT tied to 5 V = T8110 interface to a local PCI bus, 5 V signaling.

The T8110 is a single-function PCI device; it can act as a target or an initiator. All addressing is DWORD aligned for

32-bit data transfers. Refer to Section 2.1 on page 8 for pin descriptions. When the PCI interface is selected, the

minibridge port functions as a bridge to convert the PCI access protocol into a simple handshake protocol for external, non-PCI devices connected to this port. For more details, see Section 11, starting on page 107.

The PCI interface is arranged to provide a mixture of accesses. Initialization and register programming is typically

under coprocessor control. As a result, the T8110 operates as a slave when being programmed by the coprocessor

or by the host via a PCI-PCI bridge. Diagnostics and error handling are also defined as slave operations. However,

when packets are processed by either taking data from the H1x0 bus and passing it to memory, or when data is

retrieved from memory and sent to the H1x0 bus, the T8110 operates as a master, arbitrating for the bus and taking

control of its own burst transactions. This ensures that the bandwidth required by the T8110 as a local PCI bus

owner is kept to a minimum. Packet transactions are not limited to the H1x0 bus and local time slots can be routed

to and from the PCI bus as well.

4.1 Target

The T8110 PCI bus interface allows target access to five internal regions: registers, connection memory, data

memory, virtual channel memory, and the minibridge. Target burst transactions are only allowed to the register and

connection memory space. No target bursts are allowed to/from the data memory, virtual channel memory, or the

minibridge space. All target accesses get synchronized between the PCI’s 33 MHz clock domain and the T8110's

internal 65.536 MHz clock domain. Of the 32 bits of address provided, the upper 12 decode the base address,

while the lower 20 provide addressing for the internal regions of the T8110, as shown in Table 10.

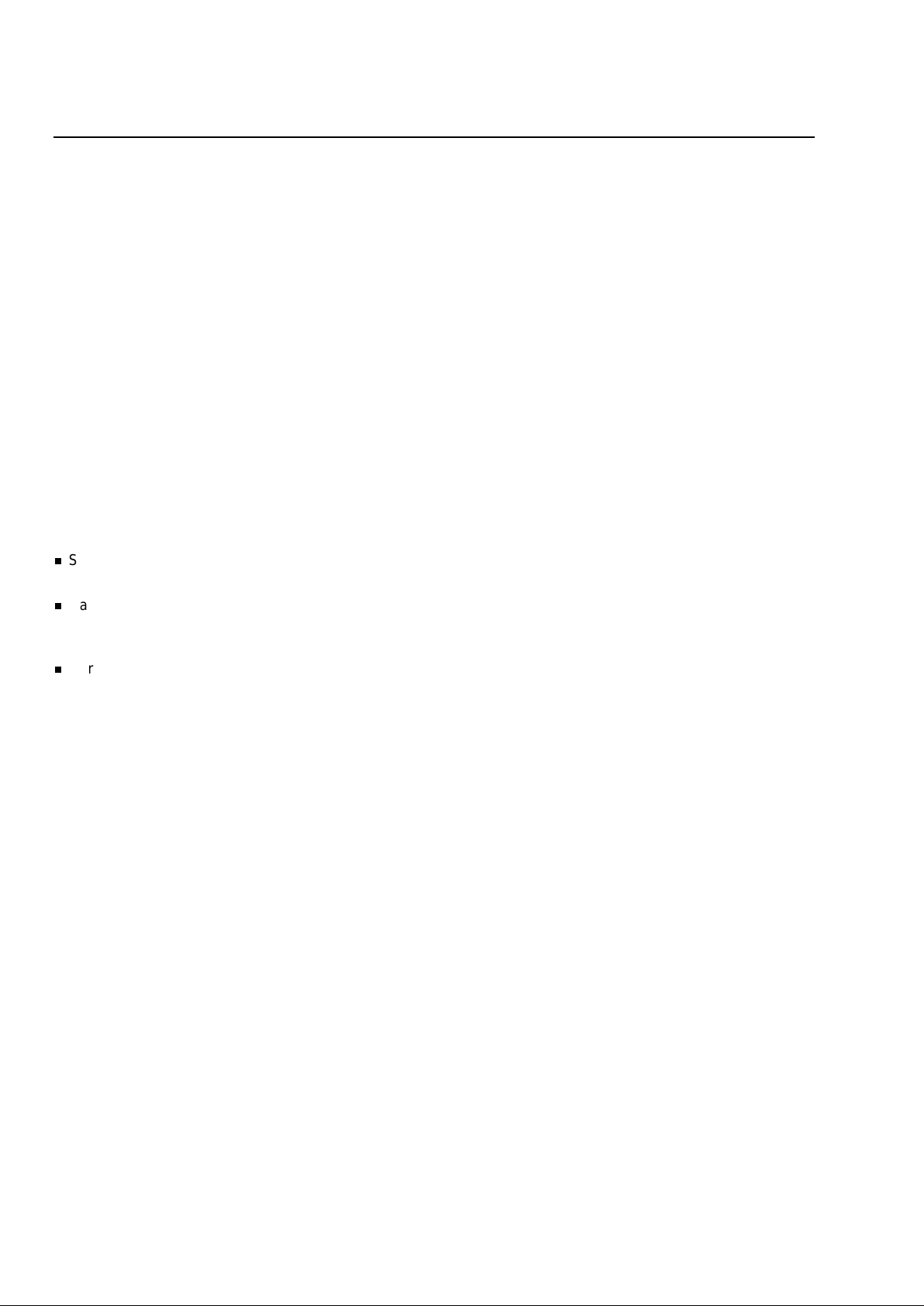

Table 10. T8110 Memory Mapping to PCI Space

Region Subregion Range (hex)

Registers Reserved 0x00000—0x000FF

Operating control and status 0x00 100— 0x 001F F

Clocks 0x00200—0x002FF

Rate control 0x00300—0x003FF

Frame group 0x00400—0x004FF

General-purpose I/O 0x00500—0x005FF

Interrupt control 0x00600—0x006FF

Minibridge control 0x00700—0x007FF

Reserved 0x00800—0x0FFFF

Virtual channel memory — 0x10000—0x1FFFF

Data memory — 0x20000—0x2FFFF

Reserved — 0x30000—0x3FFFF

Connection memory — 0x40000—0x4FFFF

Reserved — 0x50000—0x6FFFF

Minibridge — 0x70000—0x7FFFF

Reserved — 0x80000—0xFFFFF

Agere Systems Inc. 23

Data Sheet

May 2001

and Packet Payload Engine

Ambassador

T8110 PCI-Based H.100/H.110 Switch

4 PCI Interface (continued)

4.1.1 PCI Interface Registers

Table 11. PCI Interface Registers Map

DWORD

Address

(20 bits)

Section

Cross

Reference

Registers

Byte 3 Byte 2 Byte 1 Byte 0

0x00100 6.1.1, 6.1.2 Master enable Reserved Reset select Soft reset

0x00104 6.1.3, 6.1.4 Phase alignment select Clock register

access select

Data memo ry m ode

select

VCST AR T

0x00108 6.1.4 Fallback trigger, upper Fallback trigger,

lower

Fallback type select Fallback control

0x0010C 6.1.4 Watchdog EN, upper W atchdog EN,

lower

Watchdog select,

NETREF

Watchdog select, C8

0x00110 14.2.3.4.2 E xt ernal buffers descriptor table—base address register[31:0]

0x00114 4.1.5 Reserved Failsafe threshold

low

Failsafe enable and

status

Failsafe control

0x00120 6.2.1 Status 3, latched clock

errors, upper

Status 2, latched

clock errors, lower

Status 1, transient