Page 1

TECHNICAL

MANUAL

LSI53C1510

I2O-Ready

PCI RAID Ultra2

SCSI Controller

Version 2.2

April 2001

®

S14024.B

Page 2

This document contains proprietary information of LSI Logic Corporation. The

information contained herein is not to be used by or disclosed to third parties

without the express written permission of an officer of LSI Logic Corporation.

LSI Logic products are not intended for use in life-support appliances, devices,

or systems. Use of any LSI Logic product in such applications without written

consent of the appropriate LSI Logic officer is prohibited.

Document DB14-000101-02, Fourth Edition (April 2001)

This document describes the LSI Logic LSI53C1510 I

O-Ready PCI RAID Ultra2

2

SCSI Controller and will remain the official reference source for all

revisions/releases of this product until rescinded by an update.

To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to makechanges to any products herein

at any time without notice. LSI Logic does not assume any responsibility or

liability arising out of the application or use of any product described herein,

except as expressly agreed to in writing by LSI Logic; nor does the purchase or

use of a product from LSI Logic convey a license under any patent rights,

copyrights, trademark rights, or any other of the intellectual property rights of

LSI Logic or third parties.

Ultra SCSI is the term used by the SCSI Trade Association (STA) to describe

Fast-20 SCSI, as documented in the SCSI-3 Fast-20 Parallel Interface standard,

X3.277-199X.

Ultra2 SCSI is the term used by the SCSI Trade Association (STA) to describe

Fast-40 SCSI, as documented in the SCSI Parallel Interface–2 standard, (SPI–2)

X3T10/1142D.

Copyright © 1998–2001 by LSI Logic Corporation. All rights reserved.

TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design, TolerANT, SDMS, SCRIPTS, SYMplicity, and LVDlink

are registered trademarks or trademarks of LSI Logic Corporation. ARM is a

registered trademark of Advanced RISC Machines Limited, used under license.

All other brand and product names may be trademarks of their respective

companies.

SR

ii

Page 3

Audience

Preface

This book is the primary reference and technical manual for the LSI Logic

Corporation LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller. It

contains a complete functional description for the product and includes

complete physical and electrical specifications.

This technical manual assumes the user is familiar with the current and

proposed standards for SCSI and PCI. For additional background

information on these topics, please refer to the list of reference materials

provided in the Related Publications list.

This document was prepared for system designers and programmers

who are using this device to design an Ultra2 SCSI port for PCI-based

personal computers, workstations, servers or embedded applications.

Organization

This document has the following chapters and appendix:

• Chapter 1, Introduction, provides a general overview about the

LSI53C1510.

• Chapter 2, Functional Description, describes the main functional

areas of the chip in more detail, including the interfaces to the SCSI

bus and external memory.

• Chapter 3, Software Description, describes the software features,

firmware features, and hardware requirements.

• Chapter 4, Signal Descriptions, contains the pin configuration

signal definitions.

Preface iii

Page 4

• Chapter 5, Registers (Nonintelligent Mode), describes the PCI and

• Chapter 6, Registers (Intelligent Mode), describes the PCI and

• Chapter 7, Specifications, contains the electrical characteristics and

• Appendix A, Register Summary, is a register summary.

Related Publications

For background please contact:

ANSI

11 West 42nd Street

New York, NY 10036

(212) 642-4900

Ask for document number X3.131-199X (SCSI-2)

Global Engineering Documents

15 Inverness Way East

Englewood, CO 80112

(800) 854-7179 or (303) 397-7956 (outside U.S.) FAX (303) 397-2740

Ask for document number X3.131-1994 (SCSI-2) or X3.253

(SCSI-3 Parallel Interface)

host interface registers that are visible to the host in nonintelligent

mode.

host interface registers that are visible to the host in intelligent mode.

AC timing diagrams.

ENDL Publications

14426 Black Walnut Court

Saratoga, CA 95070

(408) 867-6642

Document names:

SCSI Tutor

Prentice Hall

113 Sylvan Avenue

Englewood Cliffs, NJ 07632

(800) 947-7700

Ask for document number ISBN 0-13-796855-8,

the Small Computer System Interface

iv Preface

SCSI Bench Reference, SCSI Encyclopedia,

SCSI: Understanding

Page 5

LSI Logic World Wide Web Home Page

www.lsil.com

PCI Special Interest Group

2575 N. E. Katherine

Hillsboro, OR 97214

(800) 433-5177; (503) 693-6232 (International); FAX (503) 693-8344

I2O (Intelligent Input/Output) SIG Web Site

http:\\www.i2osig.org

LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller Programming

Guide

SCSI SCRIPTS Processors Programming Guide,

S14044.A

LSI53C896 PCI to Dual Channel Ultra2 SCSI Multifunction Controller

Technical Manual

Conventions Used in This Manual

The word

deassert

Hexadecimal numbers are indicated by the prefix “0x” —for example,

0x32CF. Binary numbers are indicated by the prefix “0b” —for example,

0b0011.0010.1100.1111.

assert

means to drive a signal false or inactive.

Order Number

, Order Number S14015.B

means to drive a signal true or active. The word

Preface v

Page 6

Revision Record

Revision Date Remarks

0.1 3/98 First Draft.

0.2 4/98 Second Draft.

1.0 5/98 Preliminary.

1.1 5/98 Preliminary. Change bars mark all changes. In Chapter 7, all

2.0 1/00 Final Version.

2.1 11/00 Updated Table 7.2 Operating Conditions. All product names changed from

2.2 4/01 Updated DC electrical specifications and test conditions.

GPIO0_FETCH/ and GPIO1_MASTER/ items were deleted.

SYM to LSI.

vi Preface

Page 7

Contents

Chapter 1 Introduction

1.1 General Description 1-1

1.1.1 Block Diagram 1-2

1.2 Module Overviews 1-3

1.2.1 PCI Interface 1-3

1.2.2 Memory Controller 1-3

1.2.3 I2O Message Unit 1-3

1.2.4 ARM7TDMI RISC Processor 1-4

1.2.5 RAID Parity Assist Engine (PAE) 1-4

1.2.6 SCSI Cores 1-4

1.3 LSI53C1510 Features 1-4

1.3.1 Features List 1-5

1.4 LSI53C1510 Benefits 1-5

1.4.1 Ultra2 SCSI Benefits 1-5

1.4.2 LVDlink™ Benefits 1-6

1.4.3 TolerANT®Technology Benefits 1-6

1.4.4 I2O Benefits 1-7

1.4.5 PAE Benefits 1-7

1.4.6 ARM7TDMI RISC Processor Benefits 1-8

1.5 LSI53C1510 Benefits Summary 1-8

1.5.1 PCI Performance 1-8

1.5.2 SCSI Performance 1-8

1.5.3 RAID Performance 1-9

1.5.4 Testability 1-9

1.5.5 Integration 1-10

1.5.6 Reliability 1-10

1.6 Applications 1-11

1.6.1 Embedded Motherboard Application 1-11

1.6.2 Host Adapter Board Application 1-12

Contents vii

Page 8

Chapter 2 Functional Description

2.1 Modes of Operation 2-2

2.1.1 LSI53C1510 Overview 2-3

2.1.2 Configuration and Initialization 2-4

2.1.3 I2O Overview 2-6

2.1.4 I2O Conceptual Overview 2-6

2.1.5 I2O Benefits 2-7

2.1.6 The I2O Communications Model 2-8

2.1.7 Operational Overview 2-8

2.1.8 System Interface 2-8

2.2 The Host Interface 2-11

2.2.1 Messages 2-11

2.2.2 Message Transport 2-11

2.2.3 Request Message 2-12

2.2.4 Reply Message 2-14

2.3 LSI53C1510 Protocol Engine 2-16

2.3.1 Random Block Storage Class 2-16

2.4 Support Components 2-18

2.4.1 DRAM Memory 2-19

2.4.2 Flash ROM 2-19

2.4.3 Serial EEPROM 2-19

Chapter 3 Software Description

3.1 PCI RAID Software Solutions 3-1

3.1.1 PCI RAID 3-1

3.1.2 SYMplicity Storage Manager 3-2

3.1.3 Wind River Systems’ IxWorks RTOS 3-3

3.2 Management Software Features 3-3

3.3 RAID Firmware Features 3-3

3.3.1 RAID Levels 0, 1, 3, 5, and 10 3-4

3.3.2 Caching 3-5

3.3.3 Runs in Optimal and Degraded Mode 3-5

3.3.4 Hardware Assisted Parity Calculation 3-6

3.3.5 Tagged Command Queuing 3-6

3.3.6 Global Hot Spare Drives 3-6

3.3.7 Hot Swap Drive with Automatic, Transparent

Reconstruction 3-7

viii Contents

Page 9

3.3.8 Variable Stripe Size 3-7

3.3.9 Online Dynamic Capacity Expansion 3-7

3.3.10 Online RAID Level Migration/Reconfiguration 3-7

3.3.11 Battery Backup Support and Cache Recovery 3-8

3.3.12 Supports SAF-TE 3-8

3.4 SDMS Software 3-8

3.5 Memory Requirements 3-8

Chapter 4 Signal Descriptions

4.1 Signal Groupings 4-2

4.2 PCI Interface Signals 4-4

4.2.1 System Signals 4-4

4.2.2 Address and Data Signals 4-5

4.2.3 Interface Control Signals 4-6

4.2.4 Arbitration Signals 4-7

4.2.5 Interrupt Signals 4-7

4.2.6 ARM Signal 4-8

4.2.7 Error Recording Signals 4-8

4.2.8 Power Management Signal 4-8

4.2.9 GPIO Interface Signals 4-9

4.3 SCSI Interface Signals 4-10

4.3.1 SCSI Clock Signal 4-10

4.3.2 SCSI A-Channel Interface Signals 4-10

4.3.3 SCSI B-Channel Interface Signals 4-13

4.4 Memory Interface Signals 4-15

4.4.1 ROM/SRAM Interface Signals 4-15

4.4.2 SCAN Signals 4-16

4.4.3 DRAM Interface Signals 4-17

4.5 Miscellaneous Interface Signals 4-18

4.5.1 UART Interface Signals 4-18

4.5.2 JTAG Interface Signals 4-18

4.5.3 ARM Debug Interface Signals 4-19

4.5.4 RAID Interface Signal 4-19

4.5.5 Power and Ground Signals 4-20

Contents ix

Page 10

Chapter 5 Registers (Nonintelligent Mode)

5.1 PCI Functional Description (Nonintelligent Mode) 5-3

5.1.1 PCI Addressing 5-3

5.1.2 PCI Bus Commands and Functions Supported 5-5

5.1.3 Internal Arbiter 5-9

5.1.4 PCI Cache Mode 5-9

5.2 PCI Configuration Registers (Nonintelligent Mode) 5-10

5.3 Differences from the LSI53C895 and the LSI53C896 5-26

Chapter 6 Registers (Intelligent Mode)

6.1 Programming Models 6-3

6.1.1 System Programming Model 6-3

6.1.2 Local Programming Model 6-3

6.2 PCI Configuration Registers (Intelligent Mode) 6-4

6.3 Host Interface Registers (Intelligent Mode) 6-19

6.4 Shared Memory 6-27

Chapter 7 Specifications

7.1 DC Characteristics 7-1

7.2 TolerANT Technology Electrical Characteristics 7-7

7.3 AC Characteristics 7-11

7.4 PCI and External Memory Interface Timing Diagrams 7-14

7.4.1 Target Timing 7-14

7.4.2 Initiator Timing 7-20

7.4.3 External Memory Timing 7-31

7.5 SCSI Timing Diagrams 7-36

7.6 Pinouts and Packaging 7-43

Appendix A Register Summary

Index

Customer Feedback

x Contents

Page 11

Figures

1.1 LSI53C1510 Block Diagram 1-2

1.2 Typical LSI53C1510 Mainboard Applications 1-11

1.3 Typical LSI53C1510 Host Adapter Board Application 1-12

2.1 LSI53C1510 Block Diagram 2-3

2.2 Example of LSI53C1510 Physical Configurations 2-7

2.3 Hardware Messaging Unit 2-10

2.4 LSI53C1510 Request Message Transport 2-14

2.5 LSI53C1510 Reply Message Transport 2-15

2.6 Typical Implementations 2-18

4.1 LSI53C1510 Functional Signal Groupings 4-3

5.1 LSI53C1510 Block Diagram in Nonintelligent Mode 5-2

6.1 LSI53C1510 Block Diagram in Intelligent Mode 6-2

6.2 Shared Memory Address Translation 6-27

7.1 LVD Driver 7-3

7.2 LVD Receiver 7-4

7.3 Rise and Fall Time Test Condition 7-8

7.4 SCSI Input Filtering 7-8

7.5 Hysteresis of SCSI Receivers 7-9

7.6 Input Current as a Function of Input Voltage 7-9

7.7 Output Current as a Function of Output Voltage 7-10

7.8 External Clock 7-11

7.9 Reset Input 7-12

7.10 Interrupt Output 7-13

7.11 PCI Configuration Register Read 7-15

7.12 PCI Configuration Register Write 7-16

7.13 Operating Registers/SCRIPTS RAM Read, 32-Bit 7-17

7.14 Operating Registers/SCRIPTS RAM Write, 32-Bit 7-18

7.15 Nonburst Opcode Fetch, 32-Bit Address and Data 7-21

7.16 Burst Opcode Fetch, 32-Bit Address and Data 7-23

7.17 Back-to-Back Read, 32-Bit Address and Data 7-25

7.18 Back-to-Back Write, 32-Bit Address and Data 7-27

7.19 Burst Read, 32-Bit Address and Data 7-29

7.20 Burst Write, 32-Bit Address and Data 7-31

7.21 EDO DRAM Burst Read 7-33

7.22 FLASH ROM Normal Read Only Mode 7-34

7.23 FLASH ROM Program/Verify Mode 7-35

Contents xi

Page 12

Tables

7.24 Initiator Asynchronous Send 7-36

7.25 Initiator Asynchronous Receive 7-37

7.26 Target Asynchronous Send 7-38

7.27 Target Asynchronous Receive 7-38

7.28 Initiator and Target Synchronous Transfer 7-42

7.29 Left Half of the LSI53C1510 388 BGA Chip - Top View 7-44

7.30 LSI53C1510 388 Ball Grid Array 7-48

7.31 388 PBGA (II) Mechanical Drawing 7-49

2.1 LSI53C1510 Modes 2-2

2.2 ROM Size Configurations 2-5

2.3 Configuration Options 2-5

2.4 Supported Random Block Storage Messages 2-17

4.1 Pin Type Description 4-1

4.2 System Signals 4-4

4.3 Address and Data Signals 4-5

4.4 Interface Control Signals 4-6

4.5 Arbitration Signals 4-7

4.6 Interrupt Signals 4-7

4.7 ARM Signal 4-8

4.8 Error Recording Signals 4-8

4.9 Power Management Signal 4-8

4.10 GPIO Interface Signals 4-9

4.11 SCSI Clock Signal 4-10

4.12 SCSI A-Channel Interface Signals 4-10

4.13 SCSI B-Channel Interface Signals 4-13

4.14 ROM/SRAM Interface Signals 4-15

4.15 SCAN Signals 4-16

4.16 DRAM Interface Signals 4-17

4.17 UART Interface Signals 4-18

4.18 JTAG Interface Signals 4-18

4.19 ARM Debug Interface Signals 4-19

4.20 RAID Interface Signal 4-19

4.21 Power and Ground Signals 4-20

5.1 PCI Bus Commands Encoding 5-5

5.2 PCI Configuration Register Map 5-10

xii Contents

Page 13

6.1 PCI Configuration Register Map 6-4

6.2 LSI53C1510 Host Interface Register Map 6-19

7.1 Absolute Maximum Stress Ratings 7-2

7.2 Operating Conditions 7-2

7.3 LVD Driver SCSI Signals—SD[15:0]+, SDP[1:0]/, SREQ/,

SACK/, SMSG/, SIO/, SCD/, SATN/, SBSY/, SSEL/,

SRST/ 7-3

7.4 LVD Receiver SCSI Signals—SD[15:0]/, SDP[1:0]/,

SREQ/, SACK/, SMSG/, SIO/, SCD/, SATN/, SBSY/,

SSEL/, SRST/ 7-3

7.5 DIFFSENS SCSI Signal 7-4

7.6 RBIAS SCSI Signal 7-4

7.7 Input Capacitance 7-4

7.8 Bidirectional Signals—GPIO0, GPIO1, GPIO2, GPIO3,

GPIO4 7-5

7.9 Output Signals—MCE/, MOE/_TESTOUT, MWE/, TDO 7-5

7.10 Bidirectional Signals—AD[31:0], C_BE[7:0]/, FRAME/,

IRDY/, TRDY/, DEVSEL/, STOP/, PERR/, PAR 7-5

7.11 Input Signals—CLK, GNT/, IDSEL, RST/, SCLK, TCK,

TDI, TEST_HSC, TEST_RSTN, TMS 7-6

7.12 Output Signals—INTA, INTB 7-6

7.13 Output Signal—SERR/ 7-6

7.14 TolerANT Technology Electrical Characteristics for SE

SCSI Signals 7-7

7.15 External Clock 7-11

7.16 Reset Input 7-12

7.17 Interrupt Output 7-13

7.18 PCI Configuration Register Read 7-15

7.19 PCI Configuration Register Write 7-16

7.20 Operating Registers/SCRIPTS RAM Read, 32-Bit 7-17

7.21 Operating Registers/SCRIPTS RAM Write, 32-Bit 7-18

7.22 Nonburst Opcode Fetch, 32-Bit Address and Data 7-20

7.23 Burst Opcode Fetch, 32-Bit Address and Data 7-22

7.24 Back-to-Back Read, 32-Bit Address and Data 7-24

7.25 Back-to-Back Write, 32-Bit Address and Data 7-26

7.26 Burst Read, 32-Bit Address and Data 7-28

7.27 Burst Write, 32-Bit Address and Data 7-30

Contents xiii

Page 14

7.28 DRAM Timing Parameters (Using 50 ns Extended

Data Out Mode) 7-32

7.29 Initiator Asynchronous Send 7-36

7.30 Initiator Asynchronous Receive 7-37

7.31 Target Asynchronous Send 7-38

7.32 Target Asynchronous Receive 7-38

7.33 SCSI-1 Transfers (SE 5.0 Mbytes) 7-39

7.34 SCSI-1 Transfers (Differential 4.17 Mbytes) 7-39

7.35 SCSI-2 Fast Transfers 10.0 Mbytes (8-Bit transfers) or

20.0 Mbytes (16-Bit transfers) 40 MHz Clock 7-40

7.36 SCSI-2 Fast Transfers 10.0 Mbytes (8-Bit Transfers) or

20.0 Mbytes (16-Bit Transfers) 50 MHz Clock 7-40

7.37 Ultra SCSI SE Transfers 20.0 Mbytes (8-Bit Transfers) or

40.0 Mbytes (16-Bit Transfers) Quadrupled 40 MHz Clock 7-41

7.38 Ultra SCSI HVD Transfers 20.0 Mbytes (8-Bit Transfers)

or 40.0 Mbytes (16-Bit Transfers) 80 MHz Clock 7-41

7.39 Ultra2 SCSI Transfers 40.0 Mbytes (8-Bit Transfers) or

80.0 Mbytes (16-Bit Transfers) Quadrupled 40 MHz

Clock 7-42

7.40 Signal Names and BGA Position 7-46

7.41 Signal Names By BGA Position 7-47

A.1 LSI53C1510 PCI Registers (Nonintelligent Mode)

Register Map A-1

A.2 LSI53C1510 PCI Registers (Intelligent Mode) Register

Map A-2

A.3 LSI53C1510 Host Interface Registers (Intelligent Mode) A-4

xiv Contents

Page 15

Chapter 1

Introduction

This chapter provides a general overview of the LSI53C1510 I2O-Ready

PCI RAID Ultra2 SCSI Controller. The chapter contains the following

sections:

• Section 1.1, “General Description,” page 1-1

• Section 1.2, “Module Overviews,” page 1-3

• Section 1.3, “LSI53C1510 Features,” page 1-4

• Section 1.4, “LSI53C1510 Benefits,” page 1-5

• Section 1.5, “LSI53C1510 Benefits Summary,” page 1-8

• Section 1.6, “Applications,” page 1-11

1.1 General Description

The LSI53C1510 is a single chip I2O-Ready PCI RAID Ultra2 SCSI

Controller. The LSI53C1510 contains a 32-bit RISC ARM7TDMI

Processor and a RAID Parity Assist Engine (PAE). The RISC processor

frees the host CPU from the burden of processing I/O requests and

reduces the number of I/O interrupts, thus improving system

performance. The RISC processor and associated firmware contain the

ability to manage an I/O from start to finish without host intervention. The

RISC processor manages the Intelligent Input/Output (I2O) message

passing interface.

LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller 1-1

Page 16

The LSI53C1510 has two modes of operation: intelligent or nonintelligent

mode. In intelligent mode, the LSI53C1510 functions as an embedded

RAID controller on a motherboard or as an add-in RAID host adapter

board. In nonintelligent mode the LSI53C1510 functions as a PCI to

SCSI dual channel wide Ultra2 controller.

The LSI53C1510 is sold as a package with LSI Logic I2O RAID software

to provide a RAID solution. Therefore, this manual describes the

hardware and software only in enough detail for system intergrators to

design the LSI53C1510 onto a motherboard or a host adapter board. The

I2O RAID software consists of the LSI Logic I2O RAID Device Driver

Module (DDM), SYMplicity™ Storage Manager, and Wind River Systems’

IxWorks RTOS.

The LSI53C1510 is a combination of many tried and proven modules.

These modules have been proven in single and multimodule

configurations. The following block diagram illustrates the major modules

of the LSI53C1510.

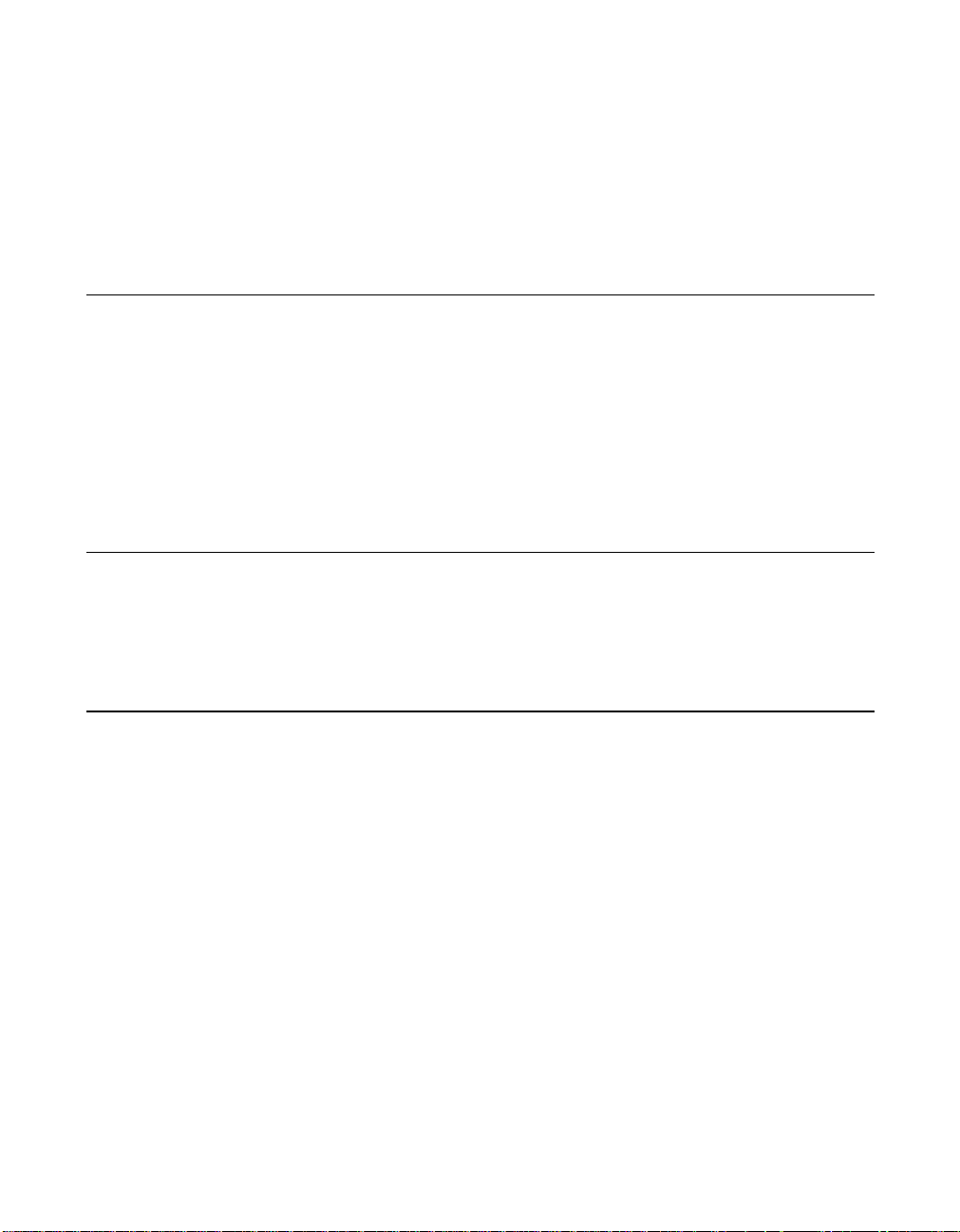

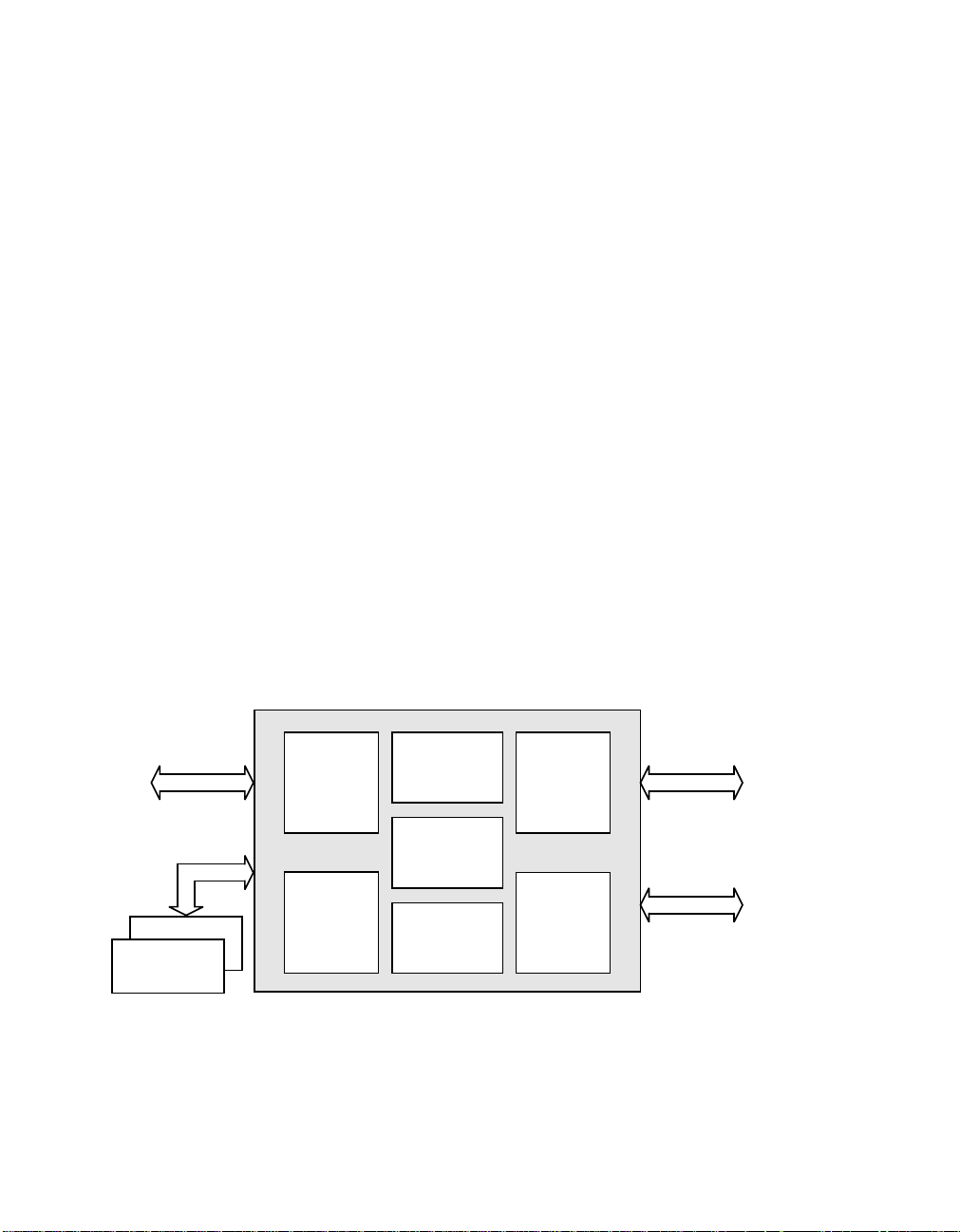

1.1.1 Block Diagram

The LSI53C1510 is a multifunction device composed of many modules.

Figure 1.1 is a block diagram of the LSI53C1510.

Figure 1.1 LSI53C1510 Block Diagram

32-Bit,

33 MHz

PCI Bus

132 Mbytes

160 Mbytes,

Memory

Interface

DRAM

DRAM

PCI

Interface

32-Bit

Memory

Controller

1-2 Introduction

Message

32-Bit RISC

ARM7TDMI

Processor

RAID

Parity Assist

Engine

I

2

Unit

O

SCSI

Core

SCSI

Core

80 Mbytes

Wide

Ultra2

SCSI Bus

80 Mbytes

Page 17

1.2 Module Overviews

This section provides an overview of the six major LSI53C1510 modules,

which consist of the PCI Interface, Memory Controller, I2O Messaging

Unit, ARM7TDMI RISC Processor, RAID PAE and SCSI Cores.

Chapter 2, “Functional Description,”provides a detailed description of the

functions of each module.

1.2.1 PCI Interface

The PCI interface is a 32-bit, 33 MHz host PCI bus. The PCI interface

supports Dual Address Cycle (DAC), PCI Power Management, and

Subsystem Vendor ID. The PCI interface also contains a PCI Master and

Slave control block, PCI configuration registers, and DMA channel

arbitration. This chip supports 64-bit addressing as a PCI master and

supports 32-bit addressing as a PCI slave.

1.2.2 Memory Controller

The memory controller provides access to Flash ROM, SRAM, and

32-bit EDO DRAM with parity (50 ns access time). It supports two

64 Mbytes (maximum configuration of 128 Mbytes) banks of DRAM. To

support the ROM and SRAM, there is a general purpose 8-bit expansion

memory bus that supports up to 4 Mbytes Flash ROM. It also supports

up to 2 Mbytes of SRAM and is designed to interface efficiently to an

external 8 K x 8 battery backed up SRAM.

1.2.3 I2O Message Unit

The messaging interface efficiently passes messages between the

LSI53C1510 and other I/O agents in an I2O enabled system. The

I2O Message Unit consists of the following four hardware FIFOs for the

message queuing lists: Request Free, Request Post, Reply Free, and

Reply Post. The LSI53C1510 provides control logic for the I2O Message

Unit and external local memory provides storage for the messages.

Module Overviews 1-3

Page 18

1.2.4 ARM7TDMI RISC Processor

The LSI53C1510 uses an optimized 32-bit ARM7 RISC Processor core

to control all RAID functionality. This frees the host CPU for other

processing activity and improves I/O performance. The RISC processor

and associated firmware contain the ability to manage an I/O from start

to finish without host intervention. The RISC processor also manages the

I2O message passing I/O interface.

1.2.5 RAID Parity Assist Engine (PAE)

The Hardware PAE offloads the parity generation and checking from the

host. It allows multiple parity operations to be queued for maximum

efficiency.

1.2.6 SCSI Cores

The integrated SCSI cores are high-performance dual wide Ultra2 SCSI

channels supporting either Single-Ended (SE) or Low Voltage Differential

(LVD) SCSI. The cores are based on the popular LSI53C8XX controllers

and are capable of up to Ultra2 transfer rates for each channel.

1.3 LSI53C1510 Features

The LSI53C1510 integrates a PCI bus master DMA core, two

high-performance SCSI cores, and two LSI Logic SCSI SCRIPTS™

processors to meet the broad requirements of Wide Ultra2 SCSI

standards. It is designed to implement multithreaded I/O algorithms with

a minimum of processor intervention, solving the protocol overhead

problems of previous intelligent and nonintelligent controller designs.

In nonintelligent mode, the LSI53C1510 is fully supported by the Storage

Device Management System (SDMS™), a software package that

supports the Advanced SCSI Protocol Interface (ASPI). SDMS software

provides BIOS and driver support for hard disk, tape, removable media

products, and CD-ROM under the major PC operating systems.

1-4 Introduction

Page 19

In intelligent mode, the LSI53C1510 is a complete, single chip RAID

solution for the motherboard—just add memory. The RAID product

solution consists of a RAID SYMplicity Storage Manager, SYMplicity

I2O RAID firmware with Wind River System IxWorks, and hardware.

1.3.1 Features List

• Highly integrated single chip RAID Controller

• I

• RAID PAE

• 32-bit/33 MHz host PCI Bus

• Two wide Ultra2 SCSI Channels

• 32-bit RISC ARM7TDMI Processor

• 32-bit Memory Controller

O Messaging Unit

2

–DAC

– PCI Power Management

– PCI cache commands (MRL, MRM, MWI)

– SE or LVD SCSI

– Based upon the popular LSI53C8XX controller

– Up to two banks of 64 Mbytes EDO (50 ns access time) DRAM

• General purpose 8-bit expansion bus

– Supports up to 4 Mbytes ROM

– Chip enable to support an external 8 K x 8 battery backed SRAM

1.4 LSI53C1510 Benefits

This section provides a description of the major LSI53C1510 benefits.

1.4.1 Ultra2 SCSI Benefits

Ultra2 SCSI is an extension of the SPI-2 draft standard that allows faster

synchronous SCSI transfer rates and defines a new physical layer, LVD

SCSI, that provides an incremental evolution from SCSI-2 and Ultra

SCSI. When enabled, Ultra2 SCSI (8-bit) performs transfers of

LSI53C1510 Benefits 1-5

Page 20

40 Mbytes/s, which results in approximately double the synchronous

transfer rate of Ultra SCSI. The LSI53C1510 can perform 16-bit (wide),

Ultra2 SCSI synchronous transfers as fast as 80 Mbytes/s. This

advantage is most noticeable in heavily loaded systems, or large block

size applications such as video on-demand and image processing.

An advantage of Ultra2 SCSI is that it significantly improves SCSI

bandwidth while preserving existing hardware and software investments.

1.4.2 LVDlink™ Benefits

The LSI53C1510 supports LVD SCSI, a signaling technology that

increases the reliability of SCSI data transfers over longer distances than

supported by SE SCSI. The low current output of LVD allows the I/O

transceivers to be integrated directly onto the chip. LVD provides the

reliability of High Voltage Differential (HVD) SCSI without the added cost

of external differential transceivers. Ultra2 SCSI with LVD allows a longer

SCSI cable and more devices on the bus, with the same cables defined

in the SCSI-3 parallel interface standard for Fast-20 (Ultra SCSI). LVD

provides a long-term migration path to even faster SCSI transfer rates

without compromising signal integrity, cable length, or connectivity.

For backward compatibility to existing SE devices, the LSI53C1510

features universal LVDlink transceivers that can switch between LVD

SCSI and SE modes. The LVDlink technology also supports high power

differential signaling in legacy systems, when external transceivers are

connected to the LSI53C1510. This allows the LSI53C1510 to be used

in both legacy and Ultra2 SCSI applications.

1.4.3 TolerANT®Technology Benefits

The LSI53C1510 features TolerANT technology, which includes active

negation on the SCSI drivers and input signal filtering on the SCSI

receivers. Through active negation, the SCSI Request, Acknowledge,

Data, and Parity signals are actively driven high rather than passively

pulled up by terminators. Active negation is enabled by setting bit 7 in

the STEST3 register.

TolerANT receiver technology improves data integrity in unreliable

cabling environments, where other devices are subject to data corruption.

TolerANT receivers filter the SCSI bus signals to eliminate unwanted

transitions, without the long signal delay associated with RC-type input

1-6 Introduction

Page 21

filters. This improved driver and receiver technology helps eliminate

double clocking of data, the single biggest reliability issue with SCSI

operations. TolerANT input signal filtering is a built-in feature of the

LSI53C1510 and all LSI Logic fast SCSI, Ultra SCSI, and Ultra2 SCSI

devices.

The benefits of TolerANT technology include increased immunity to noise

on the deasserting signal edge, better performance due to balanced duty

cycles, and improved Ultra2 SCSI transfer rates. In addition, TolerANT

SCSI devices do not cause glitches on the SCSI bus at power-up or

power-down, so other devices on the bus are also protected from data

corruption. TolerANT technology is compatible with both the Alternative

One and Alternative Two termination schemes proposed by the American

National Standards Institute.

1.4.4 I2O Benefits

The I2O-ready design of the LSI53C1510 improves system performance

by reducing interrupts to the host CPU and minimizing PCI bandwidth

through the packetized mailbox interface. These features are particularly

important in high-performance symmetric multiprocessing servers and

clustered computing systems. The benefits of the I2O architecture fully

compliment those of SCSI and include reduced host CPU I/O overhead

for better system performance, improved scalability, reduced time to

market for new I/O technology, reduced cost of integration and support

for I/O.

1.4.5 PAE Benefits

When the LSI53C1510 is in intelligent mode, the embedded PAE works

with RAID applications to perform parity generation or checking as

requested. The PAE writes any generated parity data block back into

local memory. The hardware PAE offloads the parity generation and

checking from the host and it generates parity faster than software

applications. The PAE allows multiple parity operations to be queued for

maximum efficiency. This frees the host CPU for other processing activity

and improves I/O performance.

LSI53C1510 Benefits 1-7

Page 22

1.4.6 ARM7TDMI RISC Processor Benefits

The ARM processor manages the I2O message passing I/O interface.

The embedded RISC processor (ARM7TDMI) improves system

performance by reducing interrupts to the host CPU and minimizing PCI

bandwidth. The ARM processor and associated software contain the

ability to manage an I/O from start to finish without host intervention. This

frees the host CPU for other processing activity and improves I/O

performance.

1.5 LSI53C1510 Benefits Summary

This section provides a summary of the PCI, SCSI, and RAID

performance benefits. It also provides a summary of the Testability,

Integration, and Reliability benefits.

1.5.1 PCI Performance

• Fully PCI 2.1 Specification compliant

• True multifunction device as defined in PCI 2.1 Specification in

nonintelligent mode and it presents only one load to the PCI bus

• Supports 32-bit word data bursts with variable burst lengths of 2, 4,

8, 16, 32, 64 or 128 Dwords across the PCI bus

• Prefetches up to 8 Dwords of SCSI SCRIPTS

• Performs zero wait-state bus master data bursts at 132 Mbytes/s

(@ 33 MHz)

• Supports PCI Cache Line Size register

• Supports PCI Memory Write and Invalidate, Memory Read Line, and

Memory Read Multiple commands

1.5.2 SCSI Performance

• Includes 4 Kbytes internal RAM on each SCSI channel for SCRIPTS

instruction storage, thus reducing PCI bus utilization

• Wide Ultra SCSI SE Interface

• Performs Wide Ultra2 SCSI synchronous transfers as fast as

80 Mbytes/s with LVD

1-8 Introduction

Page 23

• 816-byte DMA FIFO for more effective PCI and SCSI bus utilization

• SCSI synchronous offset of 31 levels for maximum performance in

long cable situations

• Supports variable block size and scatter/gather data transfers

• Minimizes SCSI I/O start latency

• Performs complex bus sequences without interrupts, including

restore data pointers

• Reduces ISR overhead through a unique interrupt status reporting

method

• Load/Store SCRIPTS instruction increases performance of data

transfers to and from chip registers

• Supports target disconnect and later reconnect with no interrupt to

the system processor

• Supports multithreaded I/O algorithms in SCSI SCRIPTS with fast

I/O context switching

• Expanded register Move instruction support

• Software (drivers and SCRIPTS) compatible with LSI53C8XX

• Integrated clock quadrupler enables Ultra2 SCSI with 40 MHz SCSI

clock input

1.5.3 RAID Performance

• Maximum transfer rate: 80 Mbytes/s with Wide Ultra2 SCSI

• Number of drives: 30 maximum (10 to 15 drives in typical application)

• Supports RAID levels 0, 1, 3, 5, 10 and JBOD

1.5.4 Testability

• Access to all SCSI signals through programmed I/O

• SCSI loopback diagnostics

• SCSI bus signal continuity checking

• Single-step mode operation

LSI53C1510 Benefits Summary 1-9

Page 24

1.5.5 Integration

1.5.6 Reliability

• Dual Channel SCSI Multifunction Controller

• 3.3 V/5 V PCI interface

• Full 32-bit PCI DMA bus master

• High-performance SCSI cores

• Integrated SCSI SCRIPTS processors

• ARM7TDMI 32-bit RISC processor

• RAID PAE

• I

O Message Unit

2

• 2 kV ESD protection on SCSI signals

• Typical 300 mV SCSI bus hysteresis

• Protection against bus reflections due to impedance mismatches

• Controlled bus assertion times (reduces RFI, improves reliability, and

eases FCC certification)

• Latch-up protection greater than 150 mA

• Voltage feed-through protection (minimum leakage current through

SCSI pads)

• Power and ground isolation of I/O pads and internal chip logic

• TolerANT technology provides:

– Active negation of SCSI Data, Parity, Request, and Acknowledge

signals for improved fast SCSI transfer rates

– Input signal filtering on SCSI receivers improves data integrity,

even in noisy cabling environments

1-10 Introduction

Page 25

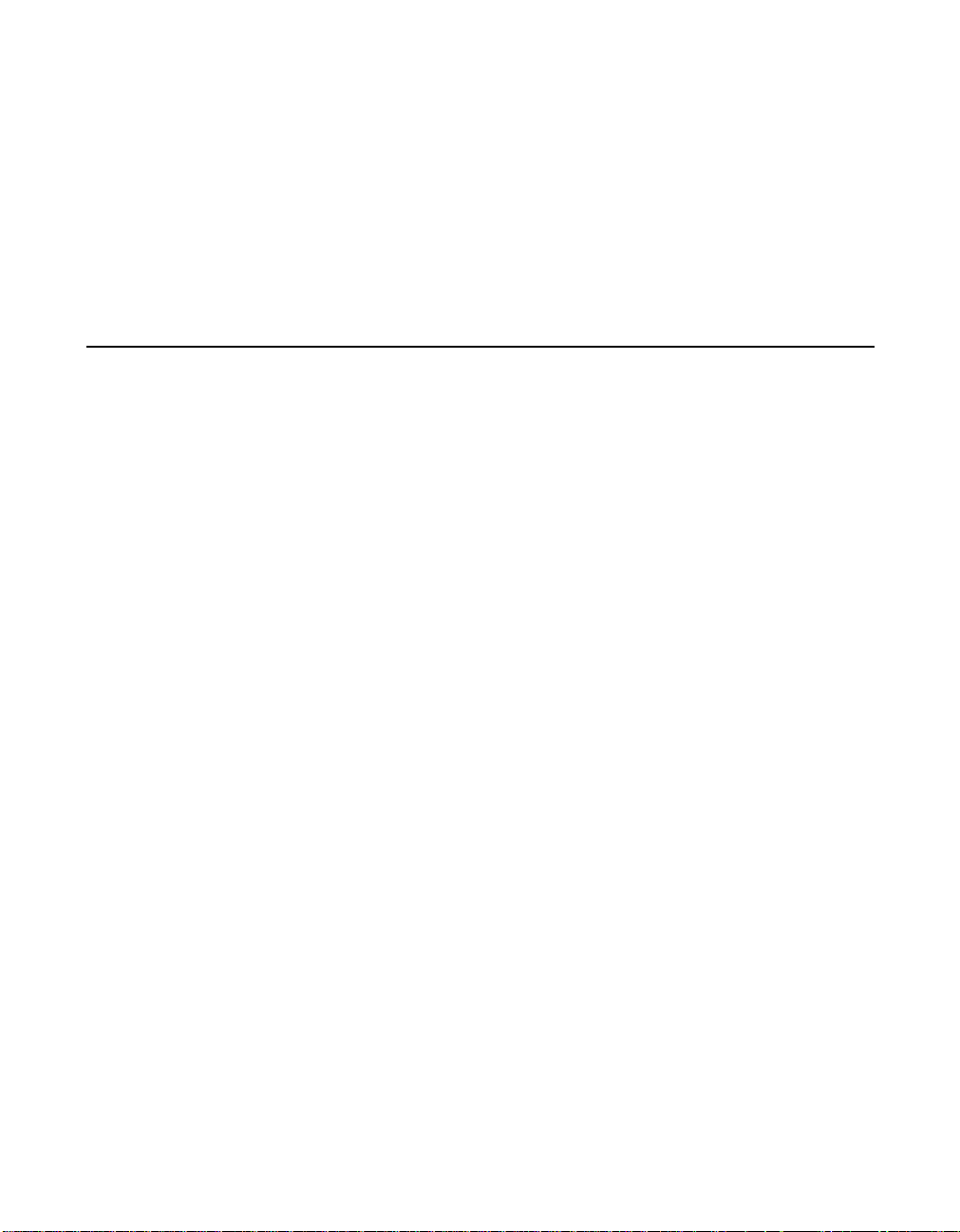

1.6 Applications

There are many different applications and configurations for the

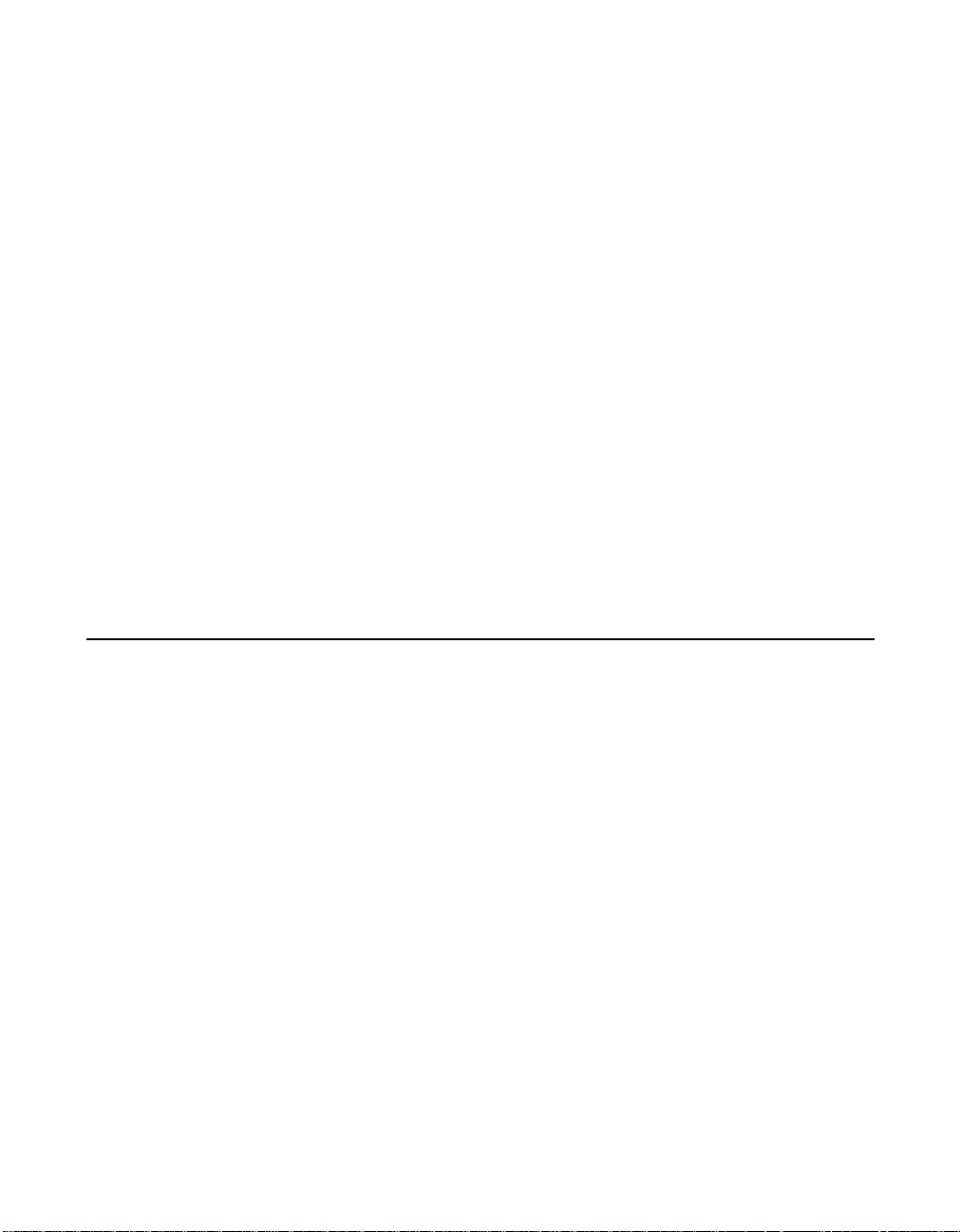

LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller. Figure 1.2

illustrates a typical LSI53C1510 embedded motherboard application.

Figure 1.3 illustrates a typical LSI53C1510 host adapter board

application.

Figure 1.2 Typical LSI53C1510 Mainboard Applications

Host PCI

Bridge

32-bit, 33 MHz Primary PCI Bus

LSI53C1510

PCI to SCSI

I

O-Ready

2

RAID Controller

SCSI BSCSI A

Ultra2 SCSI Bus

1.6.1 Embedded Motherboard Application

The LSI53C1510 is ideally suited for embedded motherboard RAID

applications. The amount of motherboard space required to implement

such an application is critical. The limited space available on the

motherboard dictates a highly integrated solution like the LSI53C1510.

All of the major functional blocks of RAID controller including processor,

memory controller, XOR engine, and SCSI controllers are integrated into

the LSI53C1510. This greatly reduces the amount of board space

EDO DRAM

w/parity

(8–128 Mbyte)

8 Kbyte Battery Backed

SRAM w/RTC

Flash

(Up to

4 Mbyte)

Applications 1-11

Page 26

required to implement a RAID controller. Not only does this make RAID

on the motherboard a viable solution, it also greatly reduces the cost of

implementing it.

Because the LSI53C1510 supports both RAID and non-RAID operational

modes, it gives the motherboard designer the option of building a base

motherboard that uses the LSI53C1510 as a dual channel Ultra2 SCSI

controller. The additional memory and real time clock required for RAID

operation can then be provided on an optional RAID upgrade card that

plugs into a connector mounted on the motherboard.

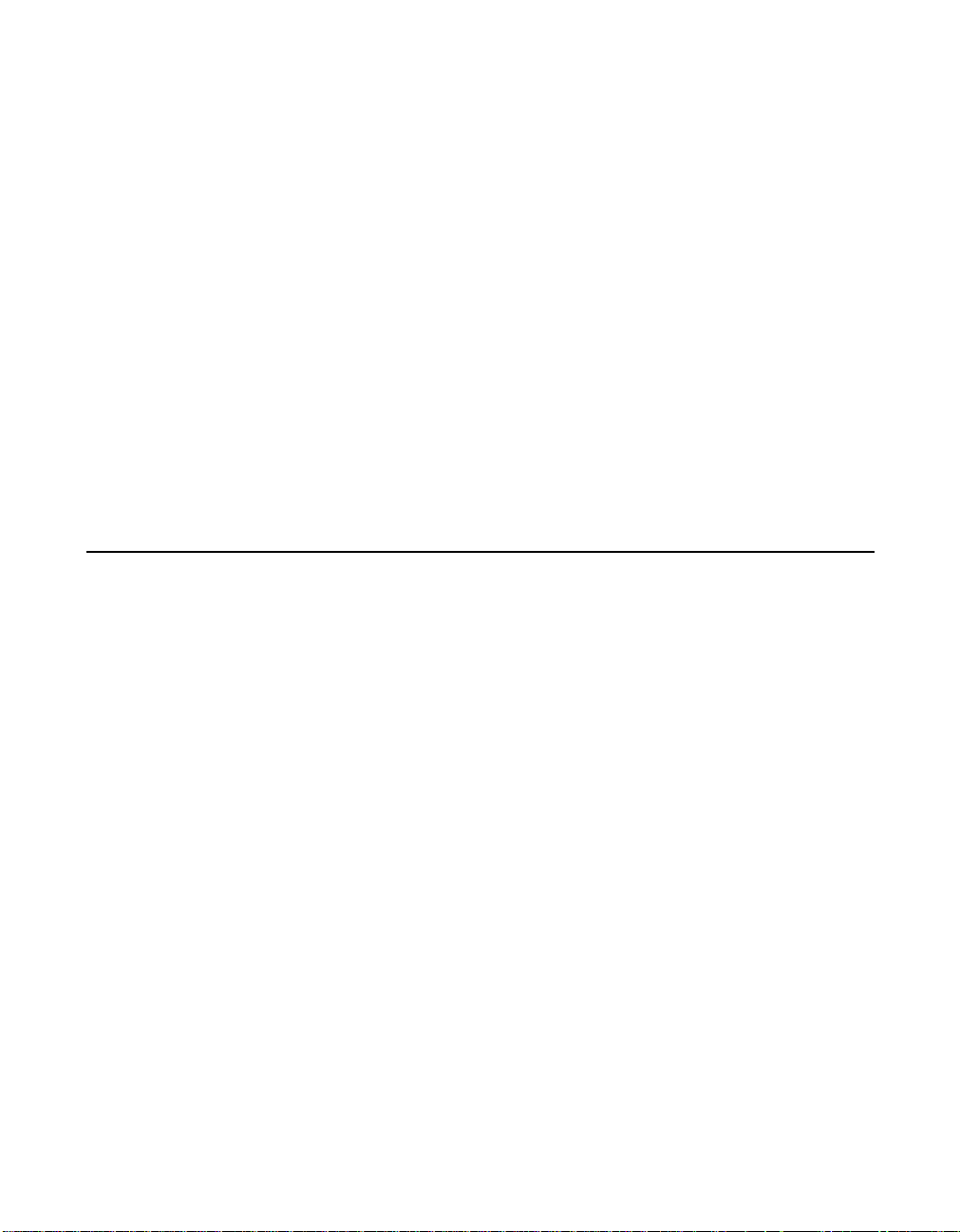

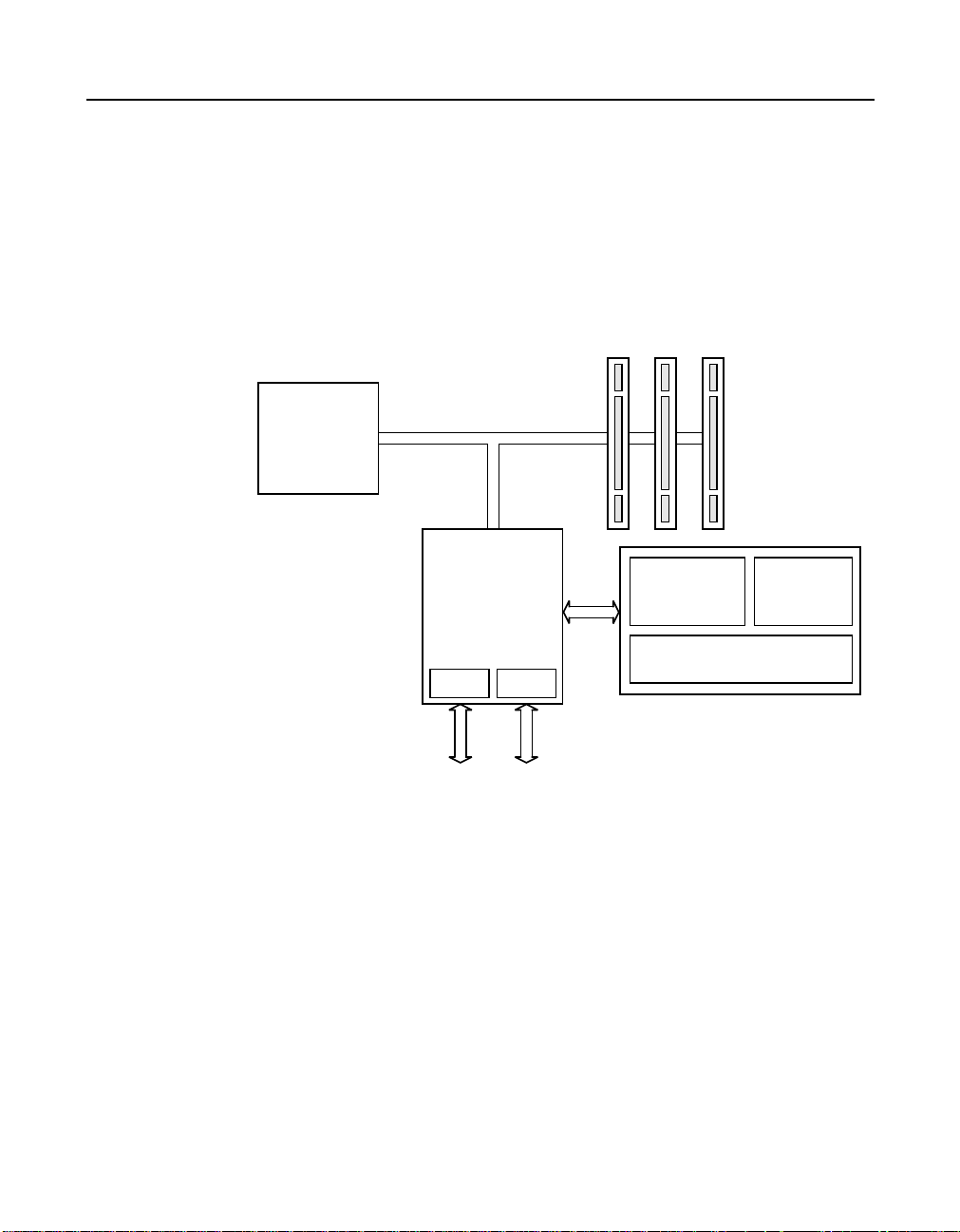

Figure 1.3 Typical LSI53C1510 Host Adapter Board Application

VHDCI

Ultra2 SCSI Bus

VHDCI

Auto

Term

Auto

Term

Clock

NVRAM

68-pin

High Density

Ultra2 SCSI Bus

LSI53C1510

PCI to SCSI

I2O-Ready RAID

Controller

32-bit, 33 MHz PCI Bus

High Density

1.6.2 Host Adapter Board Application

The LSI53C1510 single chip RAID solution can be designed on an

add-in host adapter card. This provides a highly scalable solution where

additional storage and/or performance can be obtained by adding

additional host adapter cards.

68-pin

Battery Backed

SRAM

(8 K x 8) w/RTC

Flash

(2 to 4 Mbyte)

EDO DRAM

w/parity

(8 to 128 Mbyte)

Memory

Back-up

1-12 Introduction

Page 27

Chapter 2

Functional Description

The chapter contains the following sections:

• Section 2.1, “Modes of Operation,” page 2-2

• Section 2.2, “The Host Interface,” page 2-11

• Section 2.3, “LSI53C1510 Protocol Engine,” page 2-16

• Section 2.4, “Support Components,” page 2-18

The LSI53C1510 contains an ARM7 32-bit RISC Processor, a RAID

PAE, and a DMA engine. The RISC processor frees the host CPU for

other processing activity and improves performance. The RISC

processor and associated software contain the ability to manage an I/O

from start to finish without host intervention. The RISC processor also

manages the I2O message passing I/O interface. The DMA engine

moves blocks of data between system memory and the LSI53C1510

local memory.

The LSI53C1510 uses a 32-bit PCI interface for communication with the

host CPUs and system memory. The host interface to the LSI53C1510

is designed to minimize the amount of PCI bandwidth required to support

I/O requests. A packetized message passing I/O interface is used to

reduce the number of single cycle PCI bus cycles. All data traffic across

the PCI bus occurs with zero wait-state bursts.

The intelligent LSI53C1510 architecture allows the host to specify I/Os at

a very high level. Complete SCSI functionality is provided in the

LSI53C1510, relieving the host CPU(s) from managing I/Os.

LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller 2-1

Page 28

2.1 Modes of Operation

The LSI53C1510 has two modes of operation: intelligent or nonintelligent

mode. In intelligent mode, the LSI53C1510 functions as an embedded

RAID controller on a motherboard or as an add-in RAID host adapter

board. In nonintelligent mode the LSI53C1510 functions as a PCI to

SCSI dual channel wide Ultra2 controller. These modes are entered

during the initialization of the LSI53C1510 on power-up. The presence or

absence of external memory determines which mode is entered. In

intelligent mode, the LSI53C1510 uses its built-in ARM processor. In

nonintelligent mode, the ARM processor is disabled. Table 2.1 shows the

LSI53C1510 modes of operation.

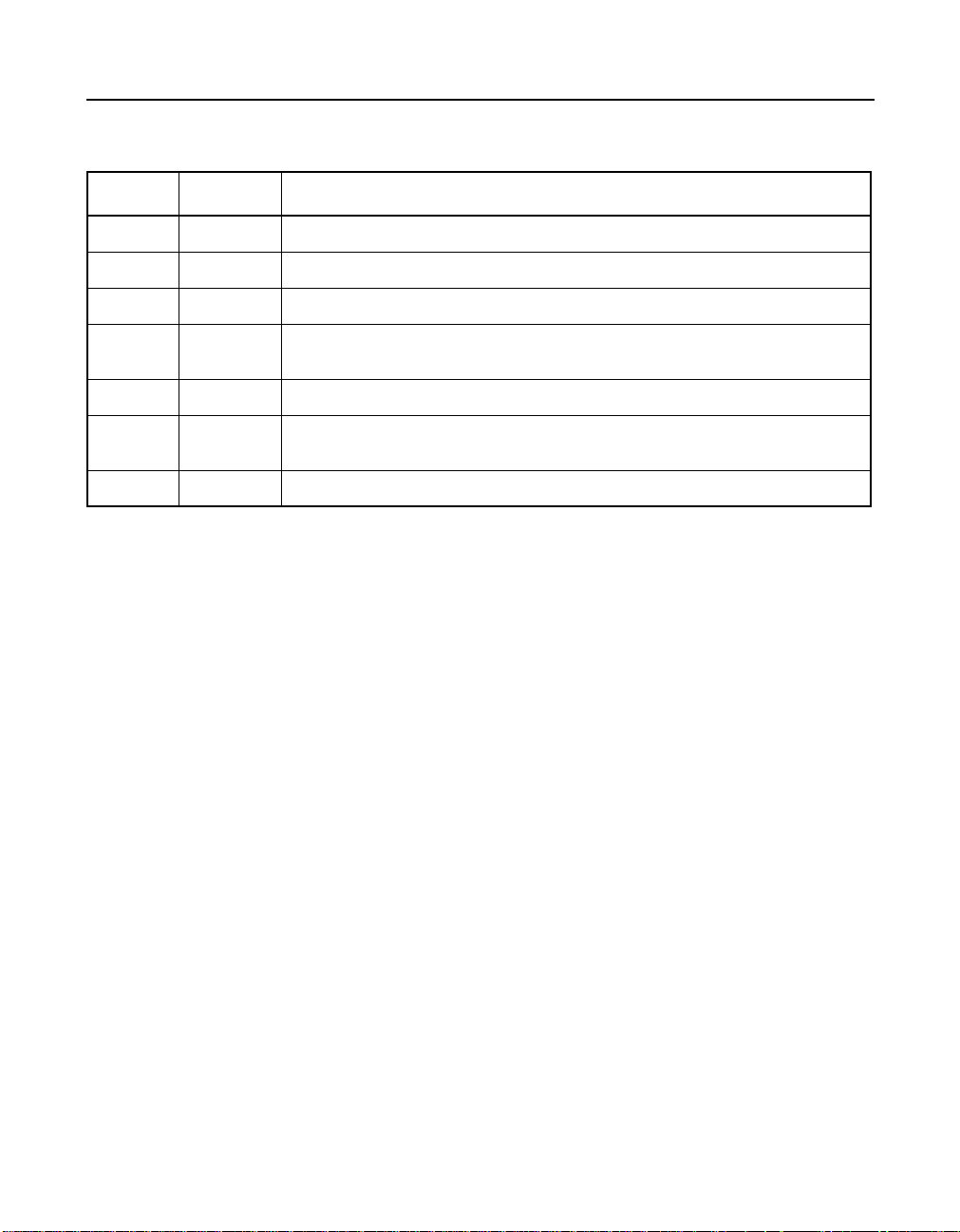

Table 2.1 LSI53C1510 Modes

Modes External Memory Configurations

Intelligent I

Controller

Nonintelligent Dual

Channel Controller

O RAID

2

Yes RAID

No Dual Channel Wide

Ultra2 SCSI Controller

2-2 Functional Description

Page 29

2.1.1 LSI53C1510 Overview

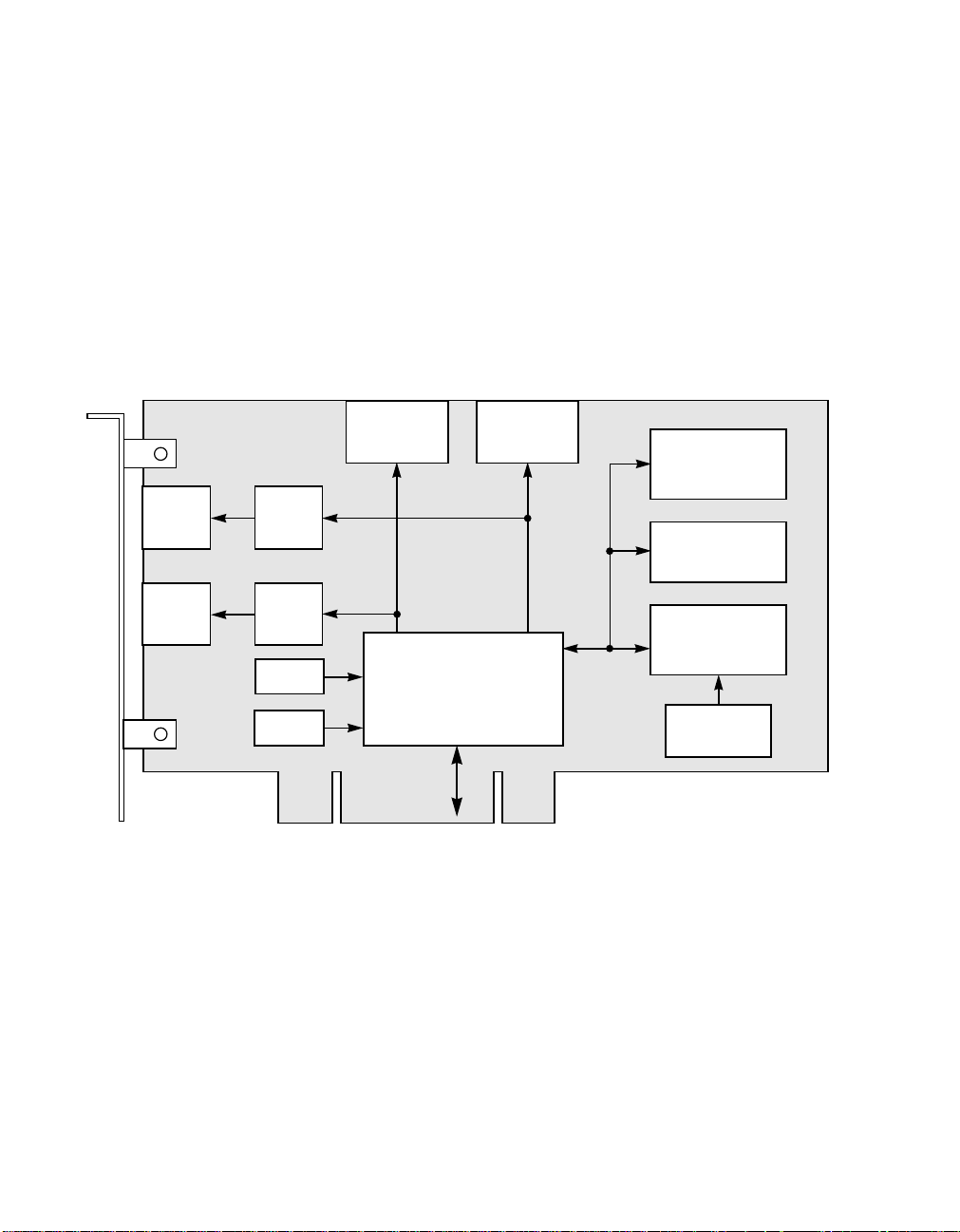

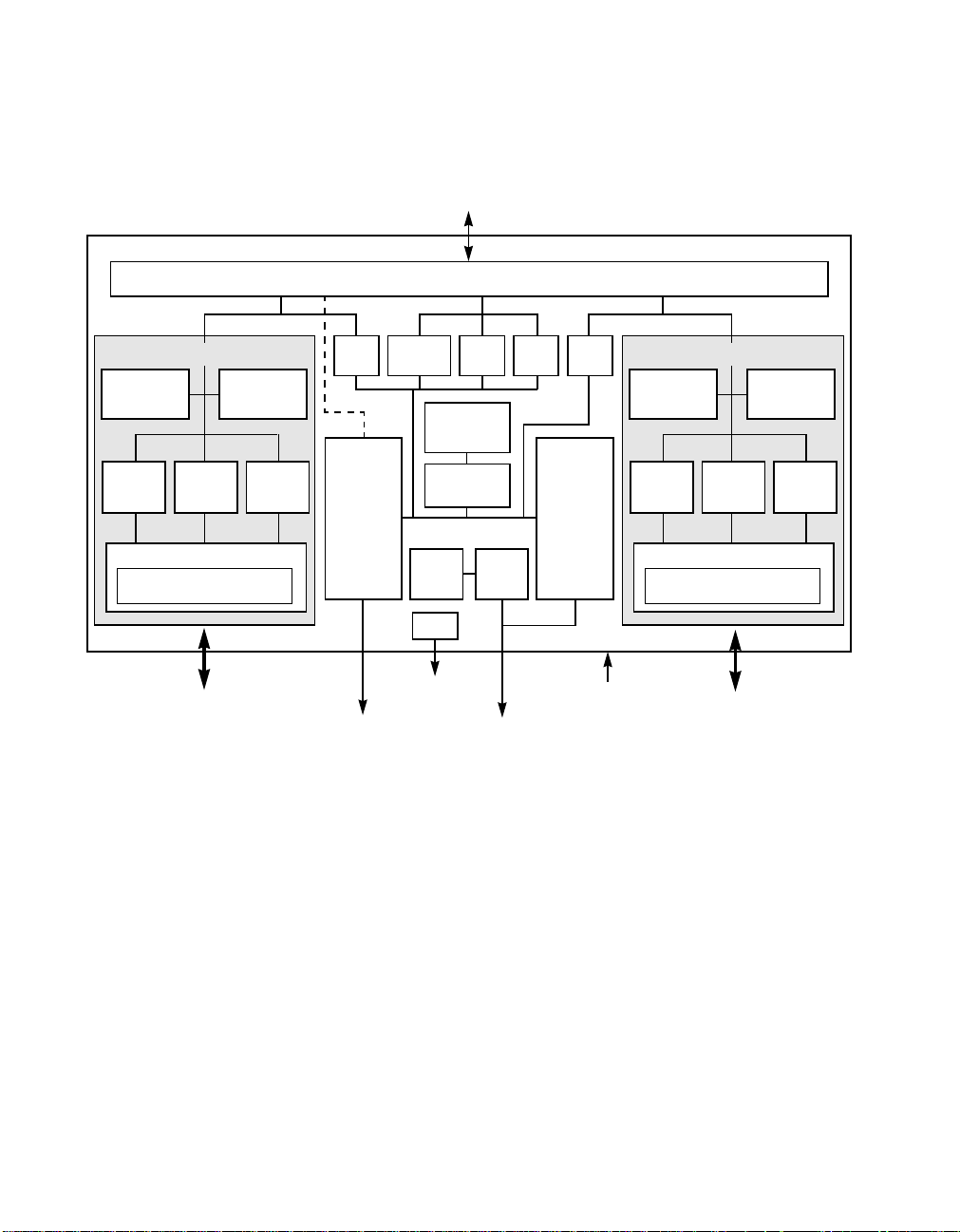

Figure 2.1 LSI53C1510 Block Diagram

Host PCI Bus (32-bit, 33 MHz)

PCI Master and Slave Control Block, PCI Configuration Registers (1/2 sets), and DMA Channel Arbitration

Ultra2 SCSI Controller

8 Dword

SCRIPTS

Prefetch Buffer

816 Byte

DMA FIFO

SCSI FIFO and SCSI Control Block

SCRIPTS

Processor

LVDlink Drivers and Receivers

SCSI

4 Kbyte

SCRIPTS RAM

Operating

Registers

Wide Ultra2 SCSI Bus

(A Channel)

Figure 2.1 illustrates the major components of the LSI53C1510 controller.

A dual channel PCI interface function block provides slave access

steering between the two SCSI cores when operating in nonintelligent

mode.

Buffer Buffer

Serial

EEPROM

and Auto-

Configuration

I2O

Msg Unit

8 Kbyte ARM

Instruction/

Data Buffer

ARM RISC

Processor

Internal Module Bus

Parity

Assist

Engine

JTAG

DMA

DRAM

Engine

Slave

Flash ROM

JTAG

ARM Debug

2-Wire Serial

EEPROM Bus

Flash ROM/DRAM

Memory Bus

Memory

Control

External

Interrupt Pin

Ultra2 SCSI Controller

SCSI

8 Dword

SCRIPTS

Prefetch Buffer

Operating

Registers

4 Kbyte

SCRIPTS RAM

816 Byte

DMA FIFO

SCSI FIFO and SCSI Control Block

SCRIPTS

Processor

LVDlink Drivers and Receivers

Wide Ultra2 SCSI Bus

(B Channel)

The Slave Access and Messaging Unit utilizes a FIFO for fast host

system service and for speed matching between the 33 MHz domain of

the PCI bus and the 40 MHz clock domain of the memory controller. The

DMA unit contains a single data FIFO for both read and write operations.

The SCSI cores each contain control registers and 4 Kbytes SCRIPTS

RAM. When operating in nonintelligent mode, these are mapped

Modes of Operation 2-3

Page 30

according to the Memory 0 and Memory 1 Base Address registers. When

in intelligent mode, the control registers are mapped into Memory 0 Base

Address registers.

The PAE accesses data and parity in the LSI53C1510 local memory and

performs XOR operations to generate parity and data blocks. Multiple

sources can be specified for each operation and multiple operations can

be queued within the unit.

The memory controller includes a 32-bit with parity EDO DRAM interface,

plus an 8-bit utility interface supporting SRAM, Flash ROM, plus

user-defined external components.

2.1.2 Configuration and Initialization

The LSI53C1510 initializes as a nonintelligent dual channel SCSI

controller, or as an intelligent I/O Processor (IOP). External pins are

sensed at power-on and either nonintelligent mode or intelligent mode is

selected. The power-on mode also determines which set of PCI

configuration register values will be used. When in nonintelligent mode,

the LSI53C1510 is a dual function PCI device with two sets of

configuration registers. When in intelligent mode, the LSI53C1510 is a

single function device with a single set of PCI configuration registers.

The MEM_ADDR bus is used to determine power-on configuration.

During power-on, internal 25 µA pull-downs are activated. If desired,

these pull-downs can be overridden using 10 kΩ external pull-up

resistors. This will change the default power-up conditions of the part.

Table 2.2 shows the ROM size configurations the eight MEM_ADDR lines

generate. The eight MEM_ADDR lines control the following configuration

options. Options shown in Table 2.3 are enabled using pull-up resistors.

2-4 Functional Description

Page 31

Table 2.2 ROM Size Configurations

MEM_ADDR [3:0] Options

0000 16 Kbytes ROM Size (No external pull-ups)

0001 32 Kbytes ROM Size

0010 64 Kbytes ROM Size

0011 128 Kbytes ROM Size

0100 256 Kbytes ROM Size

0101 512 Kbytes ROM Size

0110 1024 Kbytes ROM Size

0111 2048 Kbytes ROM Size

1000 4096 Kbytes ROM Size

1001–1110 Reserved

1111 No ROM present

Table 2.3 Configuration Options

MEM_ADDR [4:9] Options

Bit 4 Disable boot

Bit 5 RAID_MODE, based on SIMM/memory population

Bit 6 Disables SCSI SCRIPTS RAM

Bit 7 Disables EEPROM downloads

Bit 8 Reserved

Bit 9 Channel B uses INTA instead of INTB

Modes of Operation 2-5

Page 32

2.1.3 I2O Overview

When the LSI53C1510 is in intelligent mode, the RISC processor

manages the I2O message passing I/O interface. I2O defines a standard

architecture for intelligent I/O, where low level interrupts are offloaded

from the host CPU to the ARM IOP designed specifically to handle I/O.

With support for message passing between multiple independent

processors, the I2O architecture relieves the host of interrupt intensive

I/O tasks, greatly improving I/O performance in high bandwidth

applications such as RAID. I2O imposes no restrictions on where layered

modules execute, providing support for single processor, multiprocessor

and clustered systems.

The I2O specification also defines a “split driver” model for creating

drivers that are portable across multiple OSs and host platforms.

Through the split driver model, I2O significantly decreases the number of

drivers required. OS vendors write a single I2O-ready driver for each

class of device, such as SCSI Peripheral Class or Random Block Storage

Class. Device manufacturers, like LSI Logic, write a single I2O software

program for each device, such as the LSI53C1510, which works for any

OS that supports I2O.

2.1.4 I2O Conceptual Overview

The split I2O drivers are composed of two parts: the Operating System

Services Module (OSM), that resides on and interfaces to the host OS;

and the Hardware Device Module (HDM), that resides on and interfaces

with the LSI53C1510 adapter to be managed by the driver. The HDM and

the Intermediate Service Module (ISM) are often referred to collectively

as DDMs. The ISM is a driver an independent software vendor can

supply to add value or a specialized function to the LSI53C1510. These

modules interface with each other through a communication system

comprised of two layers: a Message Layer that sets up a communication

session, and a Transport Layer that defines how information will be

shared. Much like a standard communications protocol, the Message

Layer resides on top of the Transport Layer.

2-6 Functional Description

Page 33

2.1.5 I2O Benefits

The I2O operating environment of the LSI53C1510 provides two main

advantages. First, it enables the system vendor, LSI Logic, to create an

I/O platform that can support a number of intelligent configurations. The

second advantage is the capability of stacked drivers, that enable a third

party software vendor to provide value added expansion capability,

independent of both the OS and the hardware. Figure 2.2 illustrates

various ways the LSI53C1510 can be configured.

Figure 2.2 Example of LSI53C1510 Physical Configurations

Host System

Disk

Drive

Disk

Drive

Disk

Drive

SCSI

Channel

A

SCSI Bus A

Processor

Disk

Drive

Disk

Drive

Disk

Drive

LSI53C1510

RISC

System Bus

IOP

Memory

(Shared

Memory)

Other

Modules

System Memory

Disk

Drive

Disk

Drive

SCSI

Channel

B

Disk

Drive

SCSI Bus B

Modes of Operation 2-7

Page 34

2.1.6 The I2O Communications Model

The communications model for the I2O architecture is a message

passing system. The communication model defines how two entities

exchange messages by using the Message Layer to set up a connection

and exchange data and control.

When the OSM is presented with a request from the host OS, it

translates the request into an I2O message and dispatches it to the

LSI53C1510 for processing. Upon completion of the request, the

LSI53C1510 dispatches the result back to the OSM by sending a

message through the I2O Message Layer. To the host OS, the OSM

appears just like any other device driver. See Section 2.2.1, “Messages,”

later in this chapter for more detail.

2.1.7 Operational Overview

After power-on, the LSI53C1510 is configured as either a nonintelligent

or intelligent controller. In intelligent mode, the LSI53C1510 initializes

from local ROM and then issues and responds to I2O messages

exchanged with the host system. Messages are decoded into local

actions, usually involving the transfer of data. Data may be moved

between the host system and the LSI53C1510 local memory through the

LSI53C1510’s DMA controller, or by the host system. The two SCSI

cores transfer data between disk and local memory or between disk and

host system memory.

2.1.8 System Interface

The LSI53C1510 architecture features a generic, message passing I/O

interface. The LSI53C1510 Protocol Engine provides a set of four

hardware FIFOs for Message Queuing between the LSI53C1510 and the

primary host (or other hosts and peers). The four FIFOs are:

• Request Free List

• Request Post List

• Reply Free List

• Reply Post List

These FIFOs are used to manage how/where messages are sent and

received.

2-8 Functional Description

Page 35

Control logic for the four hardware FIFOs is provided within the Protocol

Engine. Storage for the FIFO entries is provided in external local

memory. Each element within each of these FIFOs contains a Message

Frame Address (MFA). The MFA is the offset from the first memory base

address register (Memory 0 Base Address) where a Message Frame is

located (Push model). The number of FIFO elements is configurable.

Supported FIFO depths are powers of two between 256 and 4096.

In addition to the hardware FIFOs, a region of shared memory is

provided (the LSI53C1510 local memory mapped to System Addresses)

for the host to write Request Message Frames into. This is the default

method (Push model) for Request Message Frame transport, where the

host itself copies the Request Message Frame into the LSI53C1510 local

memory.

To support shared memory access (read/write), the LSI53C1510

Protocol Engine includes a slave burst FIFO (depth of 128 bytes), slave

burst logic including address capture and increment, and address

translation between System and Local memory addresses.

Reply Message Frames are always pushed from the LSI53C1510

Protocol Engine to System memory; the Protocol Engine includes a DMA

channel for transferring Reply Message Frames. This DMA channel may

also be used for other purposes such as downloading software or

uploading trace information. Also present within the Protocol Engine is a

System Read/Write interface which provides the ARM processor the

ability to read/write a single arbitrary Dword from system memory. See

Figure 2.3 for an illustration of the FIFOs and memory in the Protocol

Engine and External Memory.

2.1.8.1 LSI53C1510 Protocol Engine Overview

The LSI53C1510 Protocol Engine contains an ARM processor core, a

local bus and controller, an 8 Kbytes Instruction Cache, an 8 Kbyte

Instruction/Data Buffer, an External Memory Controller, an Instruction

Prefetch Unit, a write Buffer, an interface to the host system, and a

Timer/Control block. The LSI53C1510 Protocol Engine functions as an

intelligent IOP. It receives Request Messages from the host CPU,

processes them, and sends Reply Messages back to the host.

Processing of Request Messages typically involves an I/O transaction;

the Protocol Engine and associated software together contain the ability

to manage an I/O from start to finish without host intervention.

Modes of Operation 2-9

Page 36

Figure 2.3 Hardware Messaging Unit

Protocol Engine

PCI Interface

External Memory

Request Free List FIFO Control

Request Post List FIFO Control

Reply Free List FIFO Control

Reply Post List FIFO Control

Slave Burst FIFO

Master Burst FIFO

Request Free List FIFO Data

Request Post List FIFO Data

Reply Free List FIFO Data

Reply Post List FIFO Data

Shared Memory

(Request Message Frames)

Private Memory

(Code + Data)

2-10 Functional Description

Page 37

2.2 The Host Interface

The LSI53C1510 host interface is compliant with the I2O Specification,

Revision 1.5. This host interface is a high-performance, packetized,

mailbox architecture which leverages intelligence in the LSI53C1510 to

minimize traffic on PCI. See http:\\www.i2osig.org on the I2O Special

Interest Group (SIG) web site for more information.

SYMplicity is the LSI Logic implementation of I2O architecture. There are

two basic constructs in I2O. The first construct, the Message, is used to

communicate between the host and the LSI53C1510. Messages are

moved between the host(s) and the LSI53C1510 using the second

construct, a Transport mechanism.

2.2.1 Messages

The LSI53C1510 uses Request and Reply Messages to communicate

with the host. Request messages are created by the host to “request” an

action by the LSI53C1510. Reply messages are used by the

LSI53C1510 to send status information back to the host.

Request message data structures are 128 bytes in length. The message

includes a message header and a payload. The header includes

information to uniquely identify the message. The message header

information is sophisticated enough to support multiple hosts and targets.

The payload may be any one of three different mechanisms to

communicate scatter/gather information to the LSI53C1510.

2.2.2 Message Transport

Request and Reply Messages reside in preallocated message frames.

Message frames may reside in PCI shared memory local to the

LSI53C1510 or in host memory.

The host selects where the Request and Reply messages are located

during the LSI53C1510 initialization. The default, power-up configuration,

places Request messages in PCI shared memory local to the

LSI53C1510. As an option, the Request messages can reside in host

memory. The Reply messages, however, always reside in host memory.

The Host Interface 2-11

Page 38

Pointers that point to the Request and Reply Messages are called MFAs.

The LSI53C1510 is responsible for the initialization and management of

the MFAs in the default model. The LSI53C1510 includes a set of four

FIFOs which are used to track the Request and Reply MFAs. The four

FIFOs are:

• Request Free List

• Request Post List

• Reply Free List

• Reply Post List

Each element within the FIFOs contains the 32-bit MFAs. The Free List

FIFO contains MFAs to memory locations which are “free” to be used for

new messages. The LSI53C1510 first enters these MFAs into the

Request Free List FIFO at initialization. The Host initializes the Reply

Free List by writing the MFAs for the Reply messages into the Reply

Register. The act of writing to this register pushes the MFA into the FIFO.

The Post List FIFOs contain pointers to memory locations which contain

new messages. The presence of a MFA in the Post FIFO indicates to the

host or to the LSI53C1510 that a message is pending. The depth of the

FIFOs determines the number of outstanding Request Messages which

may be pending. The total number of outstanding or open I/Os is limited

by the number of Request Messages. Therefore, the maximum number

of open I/Os is determined by the size or depth of the FIFOs. The depth

of the FIFOs in the LSI53C1510 is software configurable, from 256 to

4096, in powers of two. The storage elements for the FIFO are in the

local DRAM external to the chip. Therefore, the size of the FIFOs will

have an impact on the total amount of DRAM required. See

Section 2.4.1, “DRAM Memory,” later in the chapter for more information

regarding local DRAM requirements.

2.2.3 Request Message

The LSI53C1510 maintains a list of pointers to memory structures. The

pool of pointers (MFAs) are stored in the LSI53C1510 Free FIFO. The

top FIFO entry is provided to the host driver by reading the LSI53C1510

Request Register. In the default operation, the LSI53C1510 provides

MFAs to the LSI53C1510 local memory, mapped as shared memory. The

2-12 Functional Description

Page 39

process of the host writing to shared memory local to the LSI53C1510 is

analogous to “pushing” messages down the PCI hierarchy to the

LSI53C1510. This process may be referred to as the Push model.

Alternatively, the LSI53C1510 may be configured to provide MFAs to

memory located on the host. Once configured as such, the LSI53C1510

will “pull” the messages to memory local to the LSI53C1510 using PCI

bus master cycles. This process may be referred to as the Pull model.

The LSI Logic I2O RAID software uses the Push model.

2.2.3.1 To Send a Request Message

Figure 2.4 illustrates the LSI53C1510 Request Message Transport.

1. The host driver reads the LSI53C1510 Request Register to retrieve

a pointer to the next available message structure. If the Message

structure resides in PCI shared memory local to the LSI53C1510 (the

default), the host reads the offset of the Message structure with

shared memory. Device drivers may be written to request several

pointers through a series of fast back-to-back PCI slave read cycles.

If there are no available message structures, Request Register reads

return the value of FFFF–0xFFFF.

2. The host driver then builds the Request Message(s) and writes the

contents to the available message structure(s).

3. When the Request Message is built, the host driver writes the

MFA(s) back to the LSI53C1510 Request Register. This action

creates a queued entry in the LSI53C1510 Post FIFO. Host drivers

may post several MFAs during fast back-to-back PCI write cycles.

4. The LSI53C1510 Protocol Engine is interrupted on the first post

creating a “Request Post FIFO Not Empty” condition.

5. The LSI53C1510 removes all of the MFAs from the Post FIFO.

6. If the LSI53C1510 is operating under the Pull model, then the

LSI53C1510 arbitrates for the PCI bus with the intent to copy the

Request Message(s) in host memory using burst read cycles to

memory local to the LSI53C1510. The LSI53C1510 will immediately

start operating on request message(s) already written to local PCI

shared memory, if it is operating in the Push model.

The Host Interface 2-13

Page 40

7. Finally, the LSI53C1510 frees the memory associated with the

message request by placing the MFA back in the Request Free FIFO.

If the operation requested by the Request Message requires a Reply

Message from the LSI53C1510 to the host, then a similar message

transfer process is initiated (see Section 2.2.4, “Reply Message”).

The host driver may choose to poll the Reply Messages or have the

LSI53C1510 interrupt on exception conditions.

Figure 2.4 LSI53C1510 Request Message Transport

MF_1

MF_2

MF_3

MF_N

REQUEST

Message Frames

2

MFA_1

MFA_2

MFA_N

Free FIFO

6

2.2.4 Reply Message

The Reply Queue provided by the LSI53C1510 is managed similarly,

except the LSI53C1510 generates the Reply Messages. The host has

the responsibility to allocate the Reply Message Pool, and post the MFA

of each message frame to the Reply Register.

2.2.4.1 To Send a Reply Message

Host Driver

1

1 3

Request Register

7

LSI53C1510

3

4

5

MFA_1

MFA_2

MFA_N

Post FIFO

Figure 2.5 illustrates the LSI53C1510 Reply Message Transport.

1. The LSI53C1510 retrieves a MFA to the next free message frame

from the Reply Message Free FIFO.

2. The LSI53C1510 then writes the message to the Reply Message

frame queue.

2-14 Functional Description

Page 41

3. When the Reply Message is written into the queue, the LSI53C1510

writes the pointer into the LSI53C1510 Post FIFO.

4. The LSI53C1510 Protocol Engine causes an interrupt to the host

when the Reply Message is posted.

5. The host driver reads the Reply Register to retrieve the Reply

Message pointer from the Post FIFO. If there are no posted

messages when the host reads the Reply Register, the host receives

the value FFFF–0xFFFF.

6. The host driver then retrieves the Reply Message.

7. Finally, the host driver writes the MFA (now a free message frame)

to the Reply Register.

Figure 2.5 LSI53C1510 Reply Message Transport

MFA_1

MFA_2

MFA_N

Free FIFO

7

4

1

2.2.4.2 The “Push” Model

The “Push” model for the data transfer defines the host’s “push” of

request messages down to the PCI shared memory local to the

LSI53C1510. The location to which the host writes is provided by the

Request Free List.

Host Driver

7

Reply Register

LSI53C1510

5

3

5

6

MFA_1

MFA_2

MFA_N

Post FIFO

MF_1

MF_2

MF_3

2

MF_N

REPLY

Message Frames

The Host Interface 2-15

Page 42

2.3 LSI53C1510 Protocol Engine

The LSI53C1510 provides a Protocol Engine to manage the execution of

various I2O protocols. The Protocol Engine offloads the host processor

from management of the I2O protocol by providing a higher level of

abstraction for the SCSI protocols. This abstraction allows multiple SCSI

protocols to operate simultaneously, with no coordination required

between the host-based drivers.

Each of the abstracted classes of service has well defined Request and

Reply Message protocols. The SYMplicity I2O RAID software supports

the Random Block Storage Class. This class provides a high level

abstraction for random access block-oriented storage devices.

2.3.1 Random Block Storage Class

The Random Block Storage Class provides a high level abstraction for

random access block-oriented storage media. The class definition

abstracts normal I/O operation using a message that consists of the

starting logical block address, the number of bytes, the data buffer, the

operation code, and the device handle on which to operate. The

LSI53C1510 optimizes the request processing by attempting to sort and

concatenate different requests, thereby reducing seek and latency time

on the drives, and overall command overhead per request. Each request

is managed as a single exchange and appropriate error recovery and

reporting is provided. Table 2.4 lists the base messages that comprise

the Random Block Storage Class message protocol.

2-16 Functional Description

Page 43

Table 2.4 Supported Random Block Storage Messages

Function Description

BsaBlockRead Read from device to memory

BsaBlockReassign Reassign block addresses

BsaBlockWrite Write to device from memory

BsaBlockWriteVerify Write to device from memory then verify

BsaCacheFlush Write dirty cache to media

BsaDeviceReset Reset the device

BsaMediaFormat Not defined at this time

BsaMediaVerify Verify accessibility of data

BsaPowerMgt Power Management

BsaStatusCheck Check device status

In addition to the base messages for each class, the class definitions

also provide utility messages to allow for management and configuration

of devices. A generic user interface scripting language is used to allow

for building generic configuration and management applications.

LSI53C1510 Protocol Engine 2-17

Page 44

2.4 Support Components

The memory controller block within the LSI53C1510 provides access to

external local memory resources. External memory devices supported

include Flash ROM, DRAM, and SRAM.

The sections below provide guidance in choosing the support

components necessary for a fully functional implementation using the

LSI53C1510. A LSI53C1510 typical implementation diagram is shown

below in Figure 2.6 for reference.

Figure 2.6 Typical Implementations

VHDCI

Ultra2 SCSI Bus

VHDCI

Auto

Term

Auto

Term

Clock

NVRAM

68-pin

High Density

Ultra2 SCSI Bus

LSI53C1510

PCI to SCSI

I2O-Ready RAID

Controller

32-bit, 33 MHz PCI Bus

68-pin

High Density

Battery Backed

SRAM

(8 K x 8) w/RTC

Flash

(2 to 4 Mbyte)

EDO DRAM

w/parity

(8 to 128 Mbyte)

Memory

Backup

2-18 Functional Description

Page 45

2.4.1 DRAM Memory

The DRAM memory stores a run time image of the LSI53C1510

software. This memory also provides a data cache for RAID operations.

The LSI53C1510 uses a 32-bit demultiplexed memory bus to access the

DRAM. This memory bus has the capability to address up to 128 Mbytes

of EDO DRAM. The memory controller managing this bus has the

flexibility to support variable DRAM access speeds. The speed of the

DRAMs will have a dramatic impact on the performance of the

LSI53C1510 and 50 ns EDO DRAM is required. The LSI53C1510

memory controller also supports optional byte-wide parity error detection.

2.4.2 Flash ROM

The memory controller in the LSI53C1510 manages an optional Flash

ROM. If present, the Flash ROM is used to store the software for the

LSI53C1510 Protocol Engine and INT 0x13 boot software.

If the Flash ROM is not used, then the host platform is responsible for

downloading the Protocol Engine software to the LSI53C1510 through

the PCI interface. The LSI53C1510 supports a diagnostic interface that

is enabled through a sequence of commands issued to the WRSEQ

register in the host interface register set. Software may be directly written

to the LSI53C1510 internal memory and external DRAM through the

diagnostic interface. Details of this implementation are not currently

defined; therefore, LSI Logic recommends using Flash ROM for software

storage.

The Flash ROM is accessed using the lower 8 bits of the DRAM Memory

Interface.

2.4.3 Serial EEPROM

The serial EEPROM is primarily used during nonintelligent mode

operations. It can be programmed using the host interface of the

LSI53C1510.

Support Components 2-19

Page 46

2-20 Functional Description

Page 47

Chapter 3

Software Description

This chapter describes the software features, firmware features, and

memory requirements for the LSI53C1510 in the following sections:

• Section 3.1, “PCI RAID Software Solutions,” page 3-1

• Section 3.2, “Management Software Features,” page 3-3

• Section 3.3, “RAID Firmware Features,” page 3-3

• Section 3.4, “SDMS Software,” page 3-8

• Section 3.5, “Memory Requirements,” page 3-8

3.1 PCI RAID Software Solutions

The LSI53C1510 is the first in high-integration RAID processor. LSI Logic

offers a full PCI RAID software solution consisting of the LSI Logic RAID

DDM, SYMplicity Storage Manager utility, and Wind River Systems’

IxWorks RTOS. These applications run in the LSI53C1510 intelligent

mode.

3.1.1 PCI RAID

Operating in intelligent mode, the LSI53C1510 can use the LSI Logic PCI

RAID software package.

Leveraging third generation software from the LSI Logic established and

successful bridge controllers and subsystems, the LSI Logic RAID

software for the LSI53C1510 provides an extremely stable, feature rich,

high availability platform.

LSI53C1510 I2O-Ready PCI RAID Ultra2 SCSI Controller 3-1

Page 48

3.1.2 SYMplicity Storage Manager

SYMplicity Storage Manager provides host-based, transparent

management of disk array controllers and the following features.

• Common Features

– Obtaining a RAID Module Profile

– Naming a RAID Module (user-defined)

– Locating a RAID Module

• Configuration

– LUN creation, deletion using GUI or command line

– Easy default configurations or detailed parameter options

available

– Manages multiple RAID modules

– Hot Spare Creation/Deletion

– Dynamic Reconfiguration features

• Status

– Event logging in system log or Storage Manager (specific log)

– Scriptable error notification_SNMP, email, etc.

– LUN Reconstruction progress and in-progress tuning

– Performance Monitor

◊ GUI displays key statistics for a card and its logical units

◊ Command line interface captures full set of detailed data

• Recovery

– Health Check for immediate report of component failures

– Lead-through Recovery Steps from Single or Multiple Failures

• Maintenance/Tuning

– Cache Management

– Parity Check and Repair

– Set LUN Reconstruction Rates

3-2 Software Description

Page 49

3.1.3 Wind River Systems’ IxWorks RTOS

Wind River Systems has ported IxWorks to the LSI53C1510. This

version of IxWorks has been tuned for optimal performance.

3.2 Management Software Features

Management software has the following features:

• Supported by SYMplicity Storage Manager

• Client/Server Model (Windows NT/Win95 Client with Windows NT,

Netware, or UNIXWare Server)

• Compatible with Microsoft Cluster Server (Wolfpack)

• Online maintenance and event notification

• BBU Support with Utility level software

• Remote Diagnostic Capability

• Configurable Drive Rebuild rate

• Recovery Guru

3.3 RAID Firmware Features

RAID firmware has the following features:

• RAID Levels 0, 1, 3, 5, and 10

• Caching

– Caching (Read-ahead, write through, or write back)

– Cache memory options of 8 Mbyte to 128 Mbyte

• Runs in optimal and degraded mode

• Hardware Assisted Parity Calculation

• Variable Stripe Size

• Tagged Command Queuing

• Global hot spare drives

• Drive hot swap with automatic, transparent reconstruction

Management Software Features 3-3

Page 50

• Online Dynamic Capacity Expansion

• Online RAID Level Migration/Reconfiguration

• Battery Backup Support and Cache Recovery

• Supports SCSI Accessed Fault-Tolerant Enclosure (SAF-TE)

3.3.1 RAID Levels 0, 1, 3, 5, and 10

This section describes RAID and the different RAID levels.

3.3.1.1 RAID (Redundant Array of Independent Disks)

A disk array in which part of the storage capacity is used to store

redundant information about user data stored on the remainder of the

storage capacity. The redundant information enables regeneration of

user data if one of the disk drives in the drive group fails.

3.3.1.2 RAID Level

Indicates the way the controller reads and writes data and array parity

on the drives. The LSI53C1510 controller can create RAID Level 0, 1, 3,

and 5 logical units. These levels DO NOT indicate any certain hierarchy

or preference.

3.3.1.3 RAID Level 0

RAID Level 0 is a nonredundant RAID Level where data, without parity,

is striped across a drive group/LUN. All drives are available for storing

user data. Any single drive failure causes data loss and a logical unit

status of Dead.

3.3.1.4 RAID Level 1

RAID Level 1 or disk mirroring, protects data against disk failure by

replicating all data stored on the virtual disk at least once. For some I/O

intensive applications, a RAID Level 1 can improve performance

significantly over a single disk. As implemented by LSI Logic, RAID 1

combines both striping and mirroring. The striping and mirroring

combination is also referred to as RAID 0+1 or RAID 10.

3-4 Software Description

Page 51

3.3.1.5 RAID Level 3

RAID Level 3 adds parity to a striped array, permitting user data to be

regenerated in the event of a failure. RAID Level 3 arrays use normal disk

mechanisms for failure detection and the parity for data regeneration in

the event of a failure. RAID Level 3 relies on close coordination of

member disk activities.

3.3.1.6 RAID Level 5

RAID Level5 is another independent access RAID Level. It is functionally

equivalent to RAID Level 4, using a single parity strip to protect data

stored on severaldata strips in the same stripe. It differs from RAID Level

4 in that its parity strips are distributed across multiple array members

rather than being concentrated on a dedicated parity disk. This provides

some relief from the write bottleneck that characterizes RAID Level 4,

and is the reason that RAID 5 is most often implemented in independent

access RAID array products rather than RAID Level 4.

3.3.2 Caching

Cache memory is an area on the controller used for intermediate storage

of read and write data. By using cache, you can increase system

performance because the data for a read or write operation from the host

may already be in the cache from a previous operation (thus the need to

access the drive itself is eliminated), or the write operation is considered

complete once it is written to the cache. The following caching options

are supported.

• Caching (Read-ahead, write through, or write back)

• Cache memory options of 8 Mbyte to 128 Mbyte

3.3.3 Runs in Optimal and Degraded Mode

The software permits your RAID system to produce optimal performance.

If a failure occurs, the system can run in a degraded mode until

replacement of the failed unit occurs.

RAID Firmware Features 3-5

Page 52

3.3.4 Hardware Assisted Parity Calculation

RAID firmware uses the Hardware PAE in the LSI53C1510 to offload

parity generation and checking from the host. The PAE calculates the

parity for write operations much faster than what can be done in

software/firmware. It also allows multiple parity operations to be queued

for maximum efficiency.

3.3.5 Tagged Command Queuing

Tagged command queuing provides the capability for the host to issue

multiple commands to a logical unit. This capability is essential for an

array logical unit that is made up of multiple devices. Without tagged

queuing, the controller can only execute one operation on the logical unit

at a time, even though there are multiple drives available for overlapped

operations. The maximum number of commands which can be queued

in the controller (the sum of all logical units) is 256. This is the number

of available structures the controller has for operations received from the

host. If the host attempts to issue more commands to the controller than

it has structures available for, a Queue Full status will be returned.

The controller maintains a queue for each logical unit and a queue for

each drive in the logical unit. How a command moves from queue to

queue is dependent on the type of queue tag received with the

command.

3.3.6 Global Hot Spare Drives

This drive contains no valid data but if a failure occurs, the controller can

automatically reconstruct and use the global hot spare drive to replace a

failed drive. Hot spare drive allows full performance and data redundancy

to be restored without user intervention. The user simply replaces the

failed drive at a later time. This is an important feature because it can

significantly reduce mean time to data loss. A global hot spare drive can

replace a failed drive of the same or smaller capacity anywhere on the

disk array.

3-6 Software Description

Page 53

3.3.7 Hot Swap Drive with Automatic, Transparent Reconstruction

This disk drive replaces a failed drive. Hot Swap technology makes it

possible to remove and replace an array component while power is

applied and data activity to and from the system continues. The controller

automatically reconstructs data on the new drive, or initiates copying

back the data from the global hot spare drive that is standing in for the

failed drive. This data reconstruction is transparent to the user and allows

full performance and data redundancy to be restored.

3.3.8 Variable Stripe Size

The Dynamic Segment Sizing (DSS) feature provides the ability to

change the segment size for a LUN. Changing the segment size causes

the LUN to be reconfigured such that the data is mapped according to

the new segment size. This feature is provided while allowing full user

data availability and accessibility. The RAID firmware allows variable

stripe size. A striped array is also known as a RAID Level 0 array.

3.3.9 Online Dynamic Capacity Expansion

The Dynamic Capacity Expansion feature provides the ability to add