AUTO SHUT-OFF AC POWER SWITCH

WITH PROGRAMMABLE TIMER

FEATURES:

• Phase-Lock Loop Synchronization allows use in

Wall Switch Applications.

• PLL accuracy delivers Pure AC Power.

• Timer programmable with external R-C.

• ON input switches AC Power On and starts Timer.

• OFF input switches AC Power Off.

• 50/60Hz Line Frequency.

• +12V to +18V Operation (VSS - VDD).

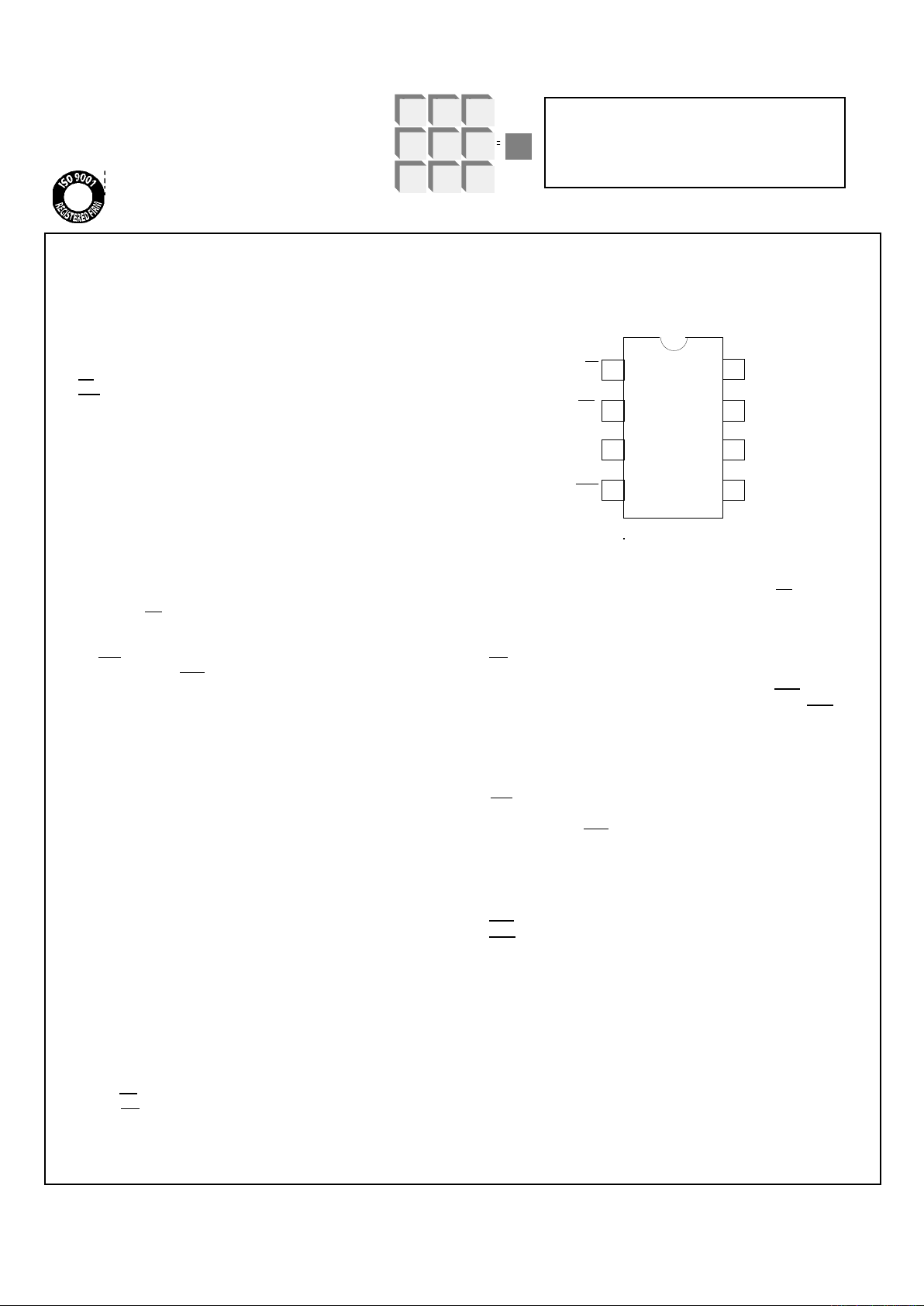

• LS7339, LS7340 ( DIP) - See Figure 1

LS7339-S, LS7340-S (SOIC)

APPLICATIONS:

• AUTO SHUT-OFF TIMER for appliances such as coffee pots,

curling irons, hair curlers, electric blankets, hand dryers.

• TIMED-ON WALL SWITCH for incandescent lighting and

heat lamps.

DESCRIPTION:

The LS7339 and LS7340 are monolithic MOS integrated circuits designed to turn a triac On and Off in a Power Switch for AC loads. Activation of the ON input will always turn the triac On and start a Timer.

The triac remains On for the duration of the Timer which is controlled

by an external R-C connected to the OSCILLATOR input. Activation

of the OFF input will always turn the triac Off. The two ICs differ only

in the width of the TRIG pulse used to trigger the triac. (See I/O Description, Pin 4.)

In a typical application (Figure 5), the output of the LS7339 drives the

gate of a triac in series with the load. Because the LS7339 is accurately synchronized to the line frequency with a phase-lock loop, the

power delivered by the triac to the load is pure AC, allowing use with

inductive loads such as motors and transformers.

There are two states through which the LS7339 can be stepped. The

states and their corresponding operating modes, phase angles, and

delivered power levels are shown in Table 1.

TABLE 1

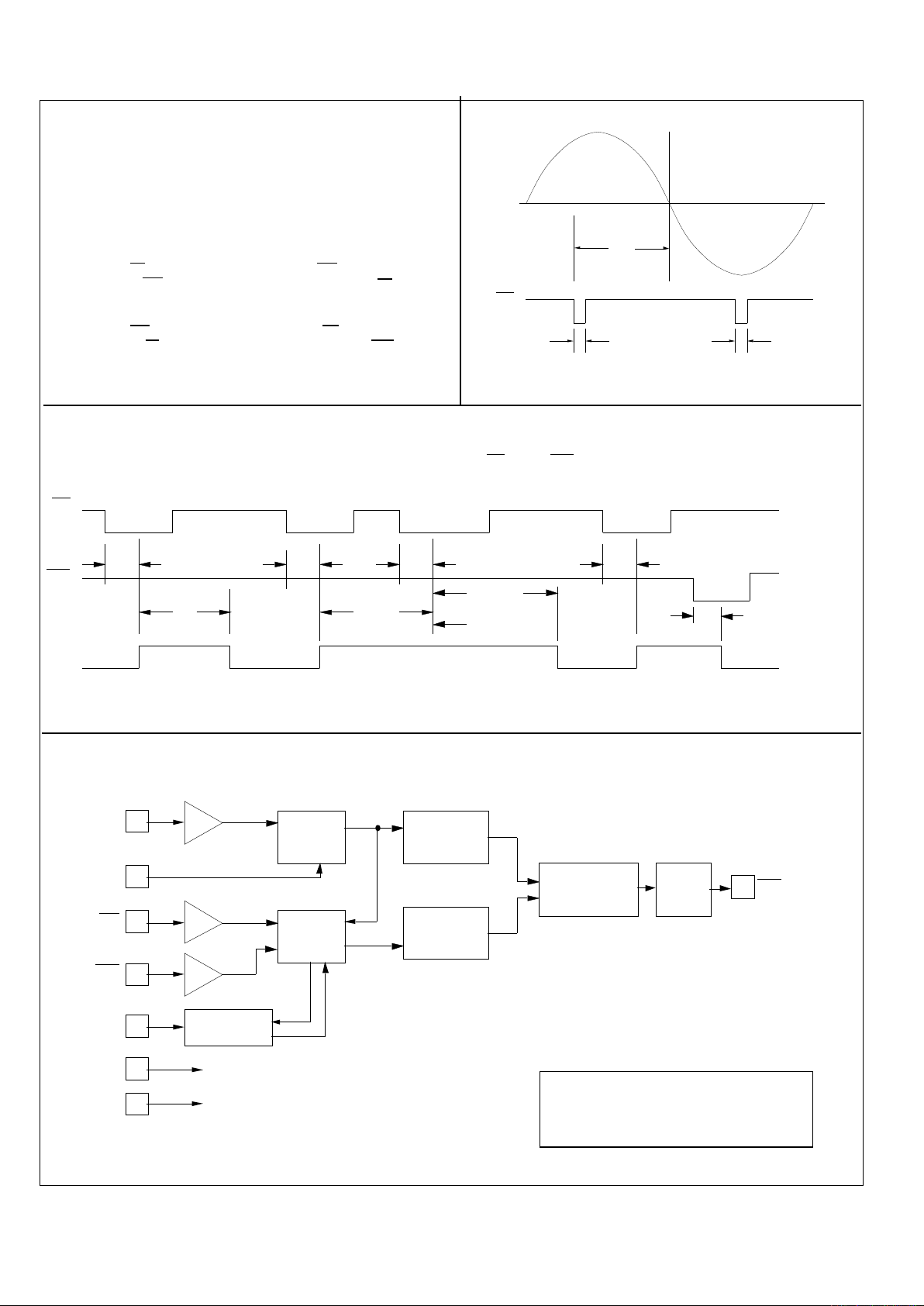

(See Figures 2 and 3) STATE 0 STATE 1

OPERATING MODE OFF Timed-On

PHASE ANGLE, ø No Output 159˚

% LOAD POWER (1) 0 99

(1) The percentage of full power delivered to a resistive load by the

triac switch.

If left in STATE 1, after a time-out period determined by the

frequency set at the OSC input (See I/O Description, Pin 6),

the circuit automatically steps to STATE 0. If the ON input transitions to logic 0 before completion of the time-out period in

STATE 1, the Timer is restarted, beginning a new time-out

June 2001

7339/40-032499-1

1

2

3

4

5

6

7

LSI

8

PIN ASSIGNMENT - TOP VIEW

FIGURE 1

ON

OFF

VDD (-V)

TRIG

VSS (+V)

SYNC

CAP

OSC

LS7339/7340

LSI/CSI

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

LS7339-7340

U

L

®

A3800

OPERATING DESCRIPTION:

Upon power up, internal power-on-reset starts the LS7339 in STATE 0.

When the ON input transitions to logic 0, the circuit steps to STATE 1.

When the OFF input transitions to logic 0, the circuit steps to STATE 0.

When implemented as shown in the application example (Figure 5),

this is accomplished by the momentary switching of the appropriate input to VDD through S1. STATE 1 is a quasi-stable state.

INPUT/OUTPUT DESCRIPTION:

ON (Pin 1) - See NOTE 1

A logic 0 applied to this input for a minimum of three SYNC cycles, TS1 (50ms for 60Hz, 60ms for 50Hz), turns TRIG On and

starts a Timer. Upon completion of the Time-out, TD1, TRIG

turns Off. While the Time-out is in progress a new transition to

logic 0 at this input for a minimum of three SYNC Cycles, TS1,

restarts the Timer. This input is designed for Touch or Switch

control. (See Figure 5.)

OFF (Pin 2) - See NOTE 2

A logic 0 applied to this input for a minimum of three SYNC cycles, TS1, turns TRIG Off. This input is designed for Switch control only. (See Figure 5.)

VDD (Pin 3)

Supply voltage negative terminal.

TRIG (Pin 4)

TRIG is a negative going pulse occurring once every half cycle

of the SYNC input. Pulse width is 1ms (LS7339) or 33µs

(LS7340). The LS7339 wide pulse width may be required for inductive loads. The LS7340 narrow pulse width allows use of a

smaller value of C2 power supply capacitor. (See Figure 5.)

VSS (Pin 5)

Supply voltage positive terminal.

OSC (Pin 6)

An R-C network connected to this input controls the frequency

of oscillation which determines the Time-out, TD1, in State 1. TD1

is approximately 255RC. The Oscillator is active only in State 1.

Chip to chip Oscillation Tolerance is ±10% for fixed value of RC.

Tie Pin 6 to VSS if a Time-out is not desired. (See Figure 5.)

CAP (Pin 7)

The CAP input is for external component connection for the PLL filter capacitor. (See Figure 5.)

SYNC (Pin 8).

The AC Line Frequency (50/60Hz) is applied to this input. The

Phase-Lock Loop synchronizes all internal timings to the AC signal

at the SYNC input. (See Figure 5.)

NOTE 1: ON will function as described if OFF is at logic 1.

If OFF is held at logic 0, the transitions at ON will

not cause the output to turn On.

NOTE 2: OFF will function as described if ON is at logic 1.

If ON is held at logic 0, the transitions at OFF

will not cause the the output to turn Off.

Tw Tw

ø

FIGURE 2. OUTPUT CONDUCTION ANGLE, Ø

SYNC

TRIG

7339/40-032499-2

ON

OFF

Ø

OFF

T

S1

T

D1

T

S1

T

S1

T

S1

T

S1

T

D1

<T

D1

OFF

OFF

159˚/STATE 1 159˚/STATE 1

159˚/STATE 1

T

D1 RESTART

OFF/STATE 0

FIGURE 3. PHASE ANGLE, Ø, vs ON AND OFF

DIGITAL

COMPARATOR

ø

DECODE

SYNC

PHASE-ANGLE

POINTER

PHASELOCK

LOOP

CONTROL

LOGIC

BUF

BUF

BUF

SYNC

CAP

ON

OFF

V

SS

VDD

FIGURE 4. LS7339/7340 BLOCK DIAGRAM

TRIG

OSC/TIMER

OSC

(+V)

(-V)

DRIVER

4

8

7

1

2

6

5

3

The information included herein is believed to be

accurate and reliable. However, LSI Computer Systems,

Inc. assumes no responsibilities for inaccuracies, nor for

any infringements of patent rights of others which may

result from its use.

Loading...

Loading...