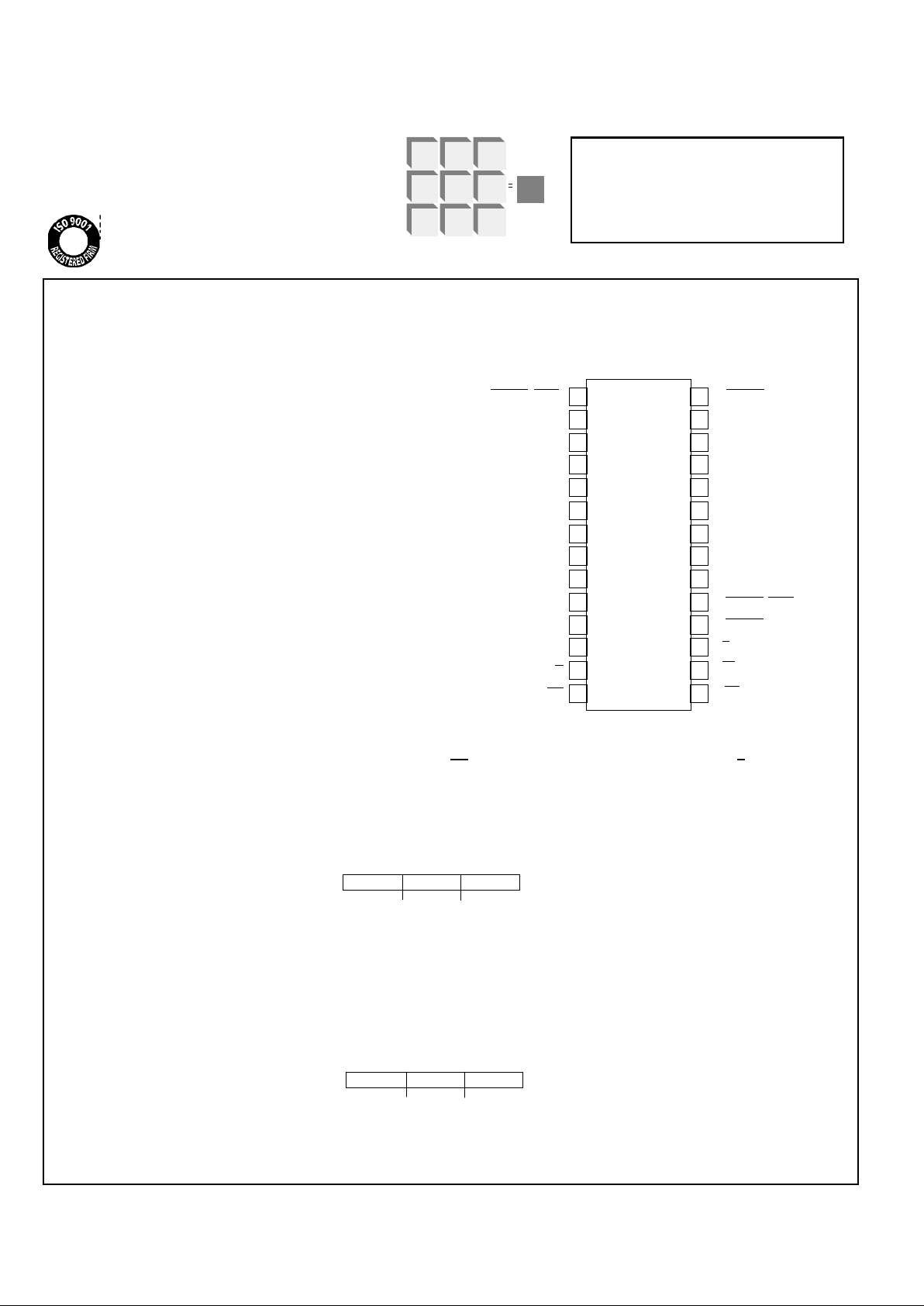

24-BIT DUAL-AXIS QUADRATURE COUNTER

LS7266R1 Registers:

LS7266R1 has a set of registers associated with each X and Y axis. All X-axis registers have the name prefix X,

whereas all Y-axis registers have the prefix Y. Selection of a specific register for Read/Write is made from the decode

of the three most significant bits (D7-D5) of the data-bus. CS input enables the IC for Read/Write. C/D input selects

between control and data information for Read/Write. Following is a complete list of LS7266R1 registers.

December 2002

7266R1-121002-1

28

27

26

25

24

23

22

21

20

19

18

17

16

15

14

13

12

11

10

9

8

7

6

5

4

3

2

1

YLCNTR/YLOL

FCK

VDD (+5V)

D0

D1

D2

D3

D4

D5

D6

D7

VSS (GND)

C/D

WR

LS7266R1

CS

RD

XRCNTR/XABG

XLCNTR/XLOL

XA

XB

XFLG1

YA

YB

YFLG2

YFLG1

YRCNTR/YABG

XFLG2

X/Y

PIN ASSIGNMENT - TOP VIEW

28-Pin Package

Preset Registers: XPR and YPR

Each of these PRs are 24-bit wide. 24-bit data can be written into a PR, one byte at a time, in a sequence of three data

write cycles.

7 70 0 7 0

HI BYTE MID BYTE LO BYTE

PR

(PR2) (PR1) (PR0)

Output Latches: XOL and YOL

Each OL is 24-bits wide. In effect, the OLs are the output ports for the CNTRs. Data from each CNTR can be loaded

into its associated OL and then read back on the data-bus, one byte at a time, in a sequence of three data Read

cycles.

7 70 0

7

0

HI BYTE MID BYTE LO BYTE

OL

(OL2) (OL1) (OL0)

Counters: XCNTR and YCNTR

Each of these CNTRs are 24-bit synchronous Up/Down counters. The count clocks for each CNTR is derived from its

associated A/B inputs. Each CNTR can be loaded with the content of its associated PR.

Byte Pointers: XBP and YBP

The Read and Write operations on an OL or a PR always accesses one byte at a time. The byte that is accessed is

addressed by one of the BPs. At the end of every data Read or Write cycle on an OL or a PR, the associated BP is

automatically incremented to address the next byte.

FEATURES:

• 30 MHz count frequency in non-quadrature mode,

17MHz in x4 quadrature mode.

• Dual 24-bit counters to support X and Y axes in

motion control applications.

• Dual 24-bit comparators.

• Digital filtering of the input quadrature clocks

• Programmable 8-bit separate filter clock prescalers

for each axis.

• Error flags for noise exceeding filter band width.

• Programmable Index Input and other programmable I/Os.

• Independent mode programmability for each axis.

• Programmable count modes:

Quadrature (x1, x2, x4) / Non-quadrature,

Normal / Modulo-N / Range Limit / Non-Recycle,

Binary / BCD.

• 8-bit 3-State data I/O bus.

• 5V operation (VDD-VSS).

• TTL/CMOS compatible I/Os.

• LS7266R1 (DIP); LS7266R1-SD (Skinny DIP);

LS7266R1-S (SOIC); LS7266R1-TS (TSSOP)

LSI/CSI

LS7266R1

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

U

L

®

A3800

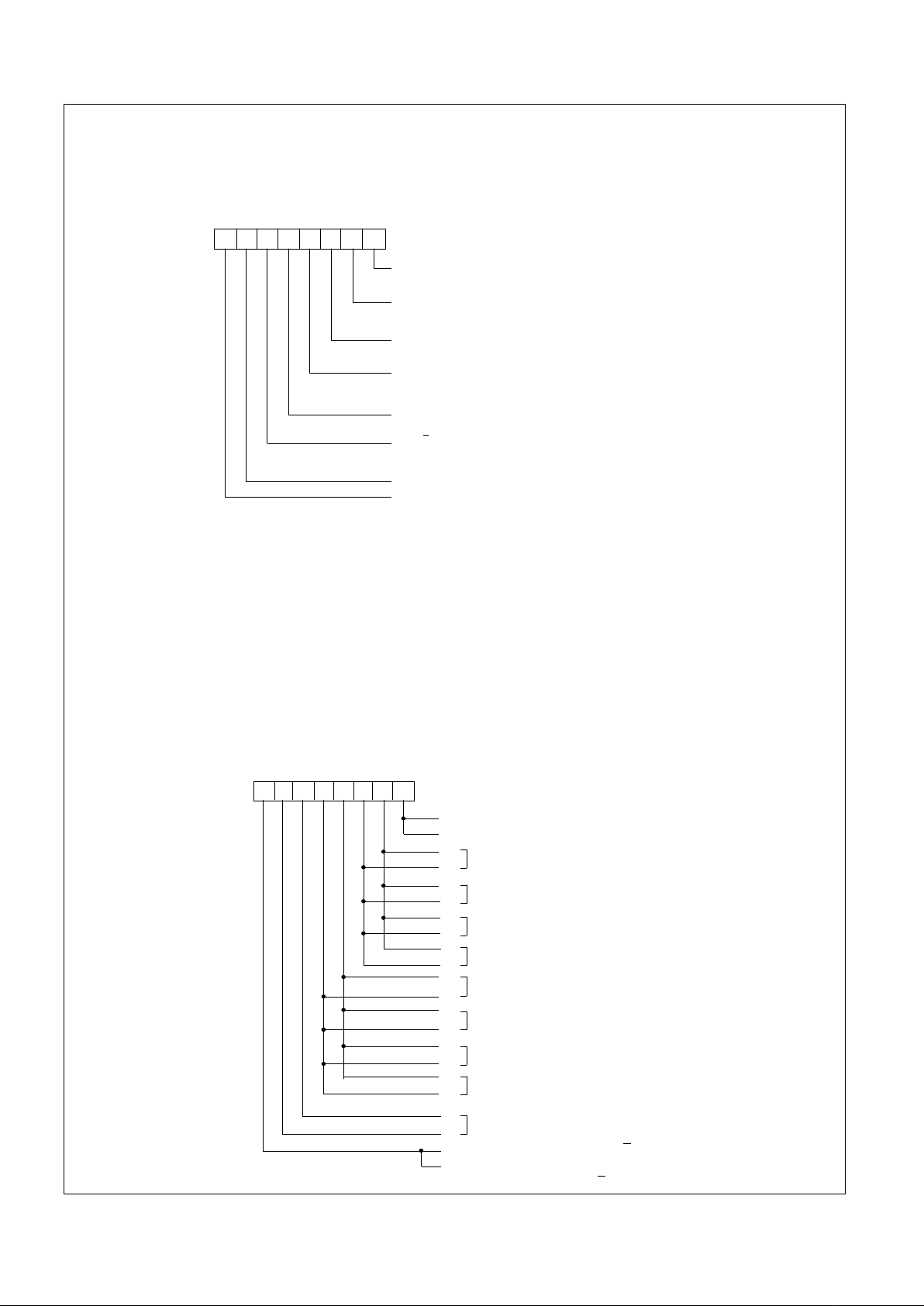

7 6 5 4 3 2 1 0

BT: Borrow Toggle flip-flop.

Toggles every time CNTR underflows.

CT: Carry toggle flip-flop.

Toggles every time CNTR overflows.

CPT: Compare toggle flip-flop.

Toggles every time PR equals CNTR.

S: Sign flag. Set to1 when CNTR underflows.

Reset to 0 when CNTR overflows.

FLAG

E: Error flag. Set to 1 when excessive noise is present at the count

inputs in quadrature mode. Irrelevant in non-quadrature mode.

U/D: Up/Down flag. Set to 1 when counting up

and reset to 0 when counting down.

Not used. Always reset to 0.

IDX: Index. Set to 1 when selected index input is at active level.

0

Filter Clock Prescalers: XPSC and YPSC

Each PSC is an 8-bit programmable modulo-N down counter, driven by the FCK clock. The factor N is down loaded

into a PSC from the associated PR low byte register PR0. The PSCs provide the ability to generate independent filter

clock frequencies for each channel. The PSCs generate the internal filter clock, FCKn used to

validate inputs XA, XB, YA, YB in the quadrature mode.

Final filter clock frequency fFCKn = ( fFCK/(n+1) ) , where n = PSC = 0 to FFH. For proper counting in the quadrature

mode, fFCKn ≥ 8fQA (or 8fQB), where fQA and fQB are the clock frequencies at inputs A and B. In non-quadrature mode

filter clock is not needed and the FCK input (Pin 2), should be tied to VDD.

7266R1-111196-2

Flag Register: XFLAG and YFLAG

The FLAG registers hold the status information of the CNTRs and can be read out on the data bus. The E bit of a

FLAG register is set to 1 when the noise pulses at the quadrature inputs are wide enough to be validated by the

input filter circuits. E = 1 indicates excessive noise at the inputs but not a definite count error. Once set, E can

only be reset via the RLD.

7 6 5 4 3 2 1 0

0: NOP

0

1

0

RLD

1: Reset BP

0

0

1

0

1

1

0

0 : Select the RLD addressed by X/Y input

1 : Select both XRLD and YRLD together

(Note: D7 = 1 overrides X/Y input)

: Select RLD

: NOP

: Reset CNTR

: Reset BT, CT, CPT,S

: Reset E

0

0

1

0

0

1

1

1

: NOP

: Transfer PR to CNTR

(Note: All 24-bits are transferred in parallel)

: Transfer CNTR to OL

(Note: All 24-bits are transferred in parallel)

: Transfer PR0 to PSC

Reset and Load Signal Decoders: XRLD and YRLD

Following functions can be performed by writing a control byte into an RLD: Transfer PR to CNTR, Transfer

CNTR to OL, reset CNTR, reset FLAG and reset BP.

:

7266R1-111196-3

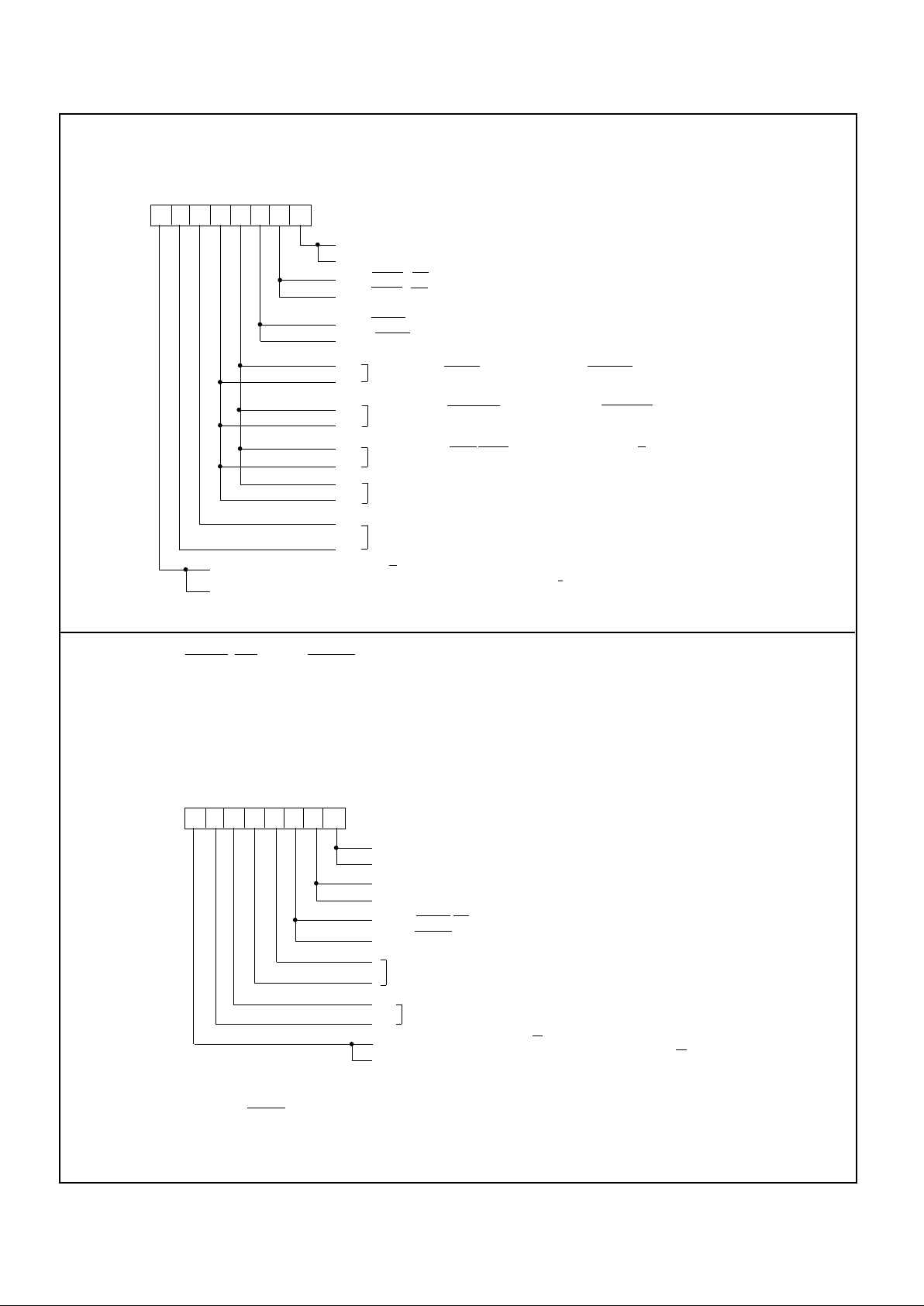

Counter Mode Registers: XCMR and YCMR

The CNTR operational mode is programmed by writing into the CMRs.

7 6 5 4 3 2 1 0

0 : Binary count

: Normal count

: Range Limit

: Non-recycle count

: Modulo-N

CMR

1 : BCD count

0

0

1

1

: Quadrature X1

0

: Non-quadrature

: Quadrature X2

1

: Quadrature X4

1

0: Select CMR addressed by X/Y input

1: Select both XCMR and YCMR together (Note: D7=1 overrides X/Y input)

: Select CMR

0

0

1

0

1

1

0

1

1

0

0

DEFINITIONS OF COUNT MODES:

Range Limit. In range limit count mode, an upper and a lower limit is set, mimicking limit switches in the me-

chanical counterpart. The upper limit is set by the content of the PR and the lower limit is set to be 0. The

CNTR freezes at CNTR = PR when counting up and at CNTR=0 when counting down. At either of these limits,

the counting is resumed only when the count direction is reversed.

Non-Recycle. In non-recycle count mode, the CNTR is disabled, whenever a count overflow or underflow takes

place. The end of cycle is marked by the generation of a Carry (in Up Count) or a Borrow (in Down Count). The

CNTR is re-enabled when a reset or load operation is performed on the CNTR.

Modulo-N. In modulo-N count mode, a count boundary is set between 0 and the content of PR. When counting

up, at CNTR=PR, the CNTR is reset to 0 and the up count is continued from that point. When counting down, at

CNTR=0, the CNTR is loaded with the content of PR and down count is continued from that point.

The modulo-N is true bidirectional in that the divide-by-N output frequency is generated in both up and down direction of counting for same N and does not require the complement of N in the UP instance. In frequency divider application, the modulo-N output frequency can be obtained at either the Compare (FLG1) or the Borrow

(FLG2) output. Modulo-N output frequency, fN = (fi / (N+ 1) ) where fi = Input count frequency and N = PR.

The information included herein is believed to be

accurate and reliable. However, LSI Computer Systems,

Inc. assumes no responsibilities for inaccuracies, nor for

any infringements of patent rights of others which may

result from its use.

Input/Output Control Register: XIOR and YIOR

The functional modes of the programmable input and output pins are written into the IORs.

7 6 5 4 3 2 1 0

0 : Disable inputs A and B

0 : LCNTR/LOL pin is Load CNTR input

0 : RCNTR/ABG pin is Reset CNTR input

0

IOR

1 : Enable inputs A and B

1 : LCNTR/LOL pin is Load OL input

1 : RCNTR/ABG pin is A and B Enable gate

0

0

: FLG1 pin is COMPARE output; FLG2 pin is BORROW output

1

: FLG1 pin is CARRY output; FLG2 pin is BORROW output

: FLG1 pin is Carry/Borrow output and FLG2 pin is U/D (FLAG register bit 5)

: FLG1 is IDX (FLAG register bit 6); FLG2 is E (FLAG register bit 4)

0: Select IOR addressed by X/Y input

1: Select both XIOR and YIOR together (Note: D7=1 overrides X/Y input)

: Select IOR

1

1

1

0

1

0

7266R1-120899-4

INDEX CONTROL REGISTERS: XIDR and YIDR

Either the LCNTR/LOL or the RCNTR/ABG inputs can be initialized to operate as an index input. When

initialized as such, the index signal from the encoder, applied to one of these inputs performs either the

Reset CNTR or the Load CNTR or the Load OL operation synchronously with the quadrature clocks. Note

that only one of these inputs can be selected as the Index input at a time and hence only one type of indexing function can be performed in any given set-up.

The index function must be disabled in non-quadrature count mode.

7 6 5 4 3 2 1 0

0: Disable Index

0: Negative Index Polarity

0: LCNTR/LOL pin is indexed (See Note 1)

IDR

1: Enable Index

1: Positive Index Polarity

1: RCNTR/ABG pin is indexed (See Note 2)

1

1

0: Select IDR addressed by X/Y input

Not used

: Select IDR

1: Select both XIDR and YIDR (Note: D7=1 overrides X/Y input)

Note 1: Function selected for this pin via IOR, becomes the operating INDEX function.

Note 2: RCNTR/ABG input must also be initialized as the reset CNTR input via IOR

:

(See Note 3)

Note 3: “Enable Index” causes the synchronous mode for the selected index input (as described in Pin 18

and Pin 19 sections of the I/O Description) to be enabled. “Disable Index” causes the

non-synchronous mode to be enabled. The input, however, is not disabled in either selection.

(See Note 3)

Absolute Maximum Ratings:

Parameter Symbol Values Unit

Voltage at any input VIN VSS - 0.3 to VDD + 0.3 V

Supply Voltage VDD +7.0 V

Operating Temperature TA -25 to +80

o

C

Storage Temperature TSTG -65 to +150

o

C

DC Electrical Characteristics. (TA = -25˚C to +80°C, VDD = 4.5V to 5.5V)

Parameter Symbol Min. Value Max.Value Unit Remarks

Supply Voltage VDD 4.5 5.5 V Supply Current IDD - 800 µA All clocks off

Input Logic Low VIL - 0.8 V Input Logic High VIH 2.0 - V Output Low Voltage VOL - 0.5 V IOSNK = 5mA

Output High Voltage VOH VDD - 0.5 - V IOSRC = 1mA

Input Leakage Current IILK - 30 nA Data Bus Leakage Current IDLK - 60 nA Data bus off

Output Source Current IOSRC 1.0 - mA VO = VDD - 0.5V

Output Sink Current IOSNK 5.0 - mA VO = 0.5V

7266R1-111196-5

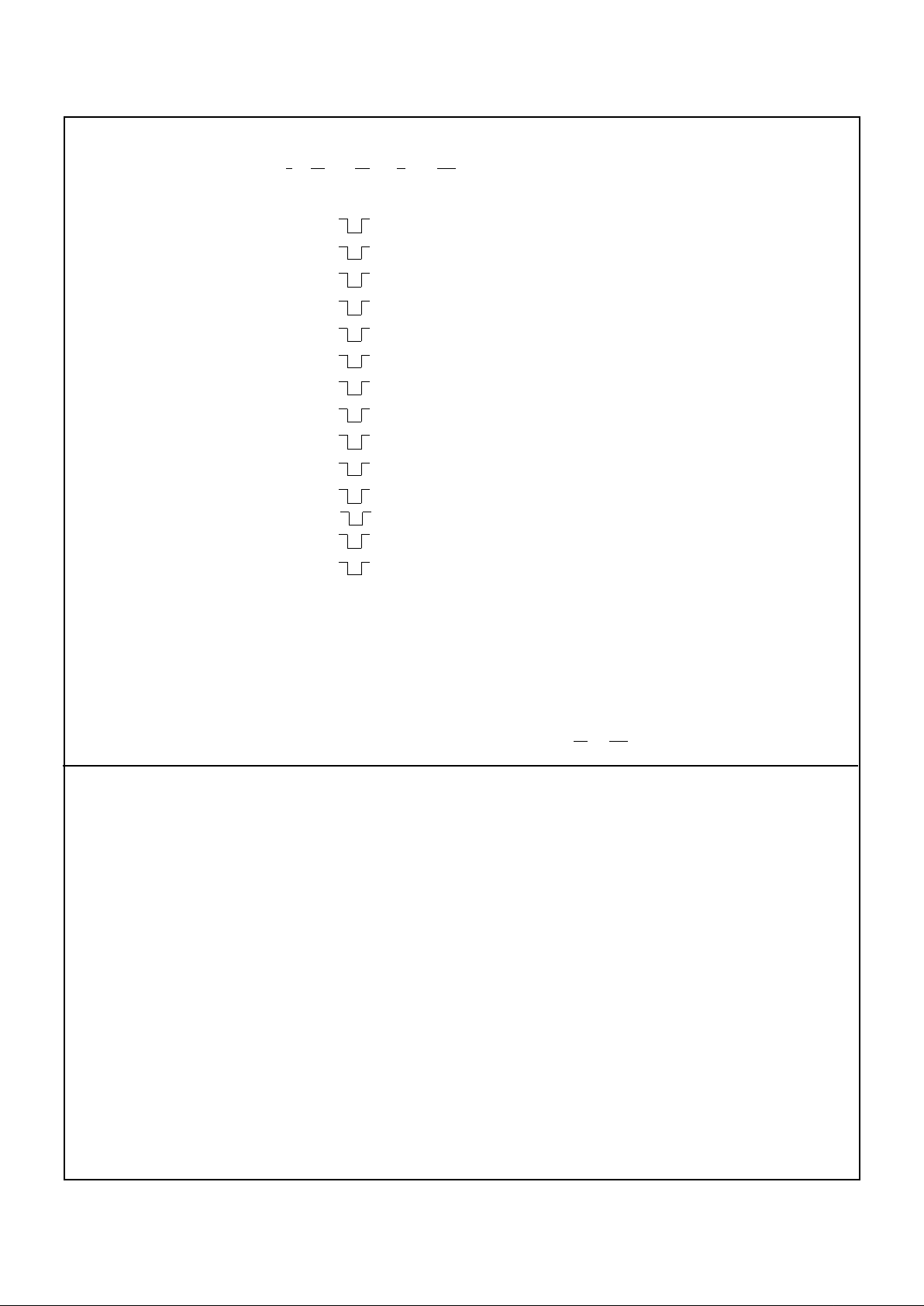

REGISTER ADDRESSING MODES

D7 D6 D5 C/D RD WR CS

FUNCTION

X X X X X 1 Disable both axes for Read/Write

X X 0 1 0

X X 0 1 0

0 0 1 1 0

0 0 1 1 0

0 0 1 1 0

0 1 1 1 0

Write to XPR byte segment addressed by XBP (Note 3)

Write to YPR byte segment addressed by YBP (Note 3)

Write to XRLD

Write to both XRLD and YRLD

Write to XCMR

X

X

X

0

0

1

0

X/Y

X

0

1

0

1

X

0

0 0 1

1 1 0

1

0 1 1 11 0X

1 0 1 10 0 0

1 0 1 10

0

1

1 0 1 11 X 0

Write to YRLD

Write to YCMR

Write to both XCMR and YCMR

Write to XIOR

Write to YIOR

Write to both XIOR and YIOR

X = Don't Care

Note 3: Relevant BP is automatically incremented at the trailing edge of RD or WR pulse

1

1

1

1

X X X 0 0 0 0

X X X 0 0 1 0

X X X 1 0 0 0

X X X 1 0 1 0

Read XOL byte segment addressed by XBP (Note 3)

Read YOL byte segment addressed by YBP (Note 3)

Read XFLAG

Read YFLAG

1 1

1 1

0 Write to XIDR0 0

0 1 1

1 1 0

1

1 1 1 11 0X

Write to YIDR

Write to both XIDR and YIDR

Loading...

Loading...