LSI/CSI

b

d

e

f

g

U

L

®

A3800

LSI Computer Systems, Inc. 1235 Walt Whitman Road, Melville, NY 11747 (631) 271-0400 FAX (631) 271-0405

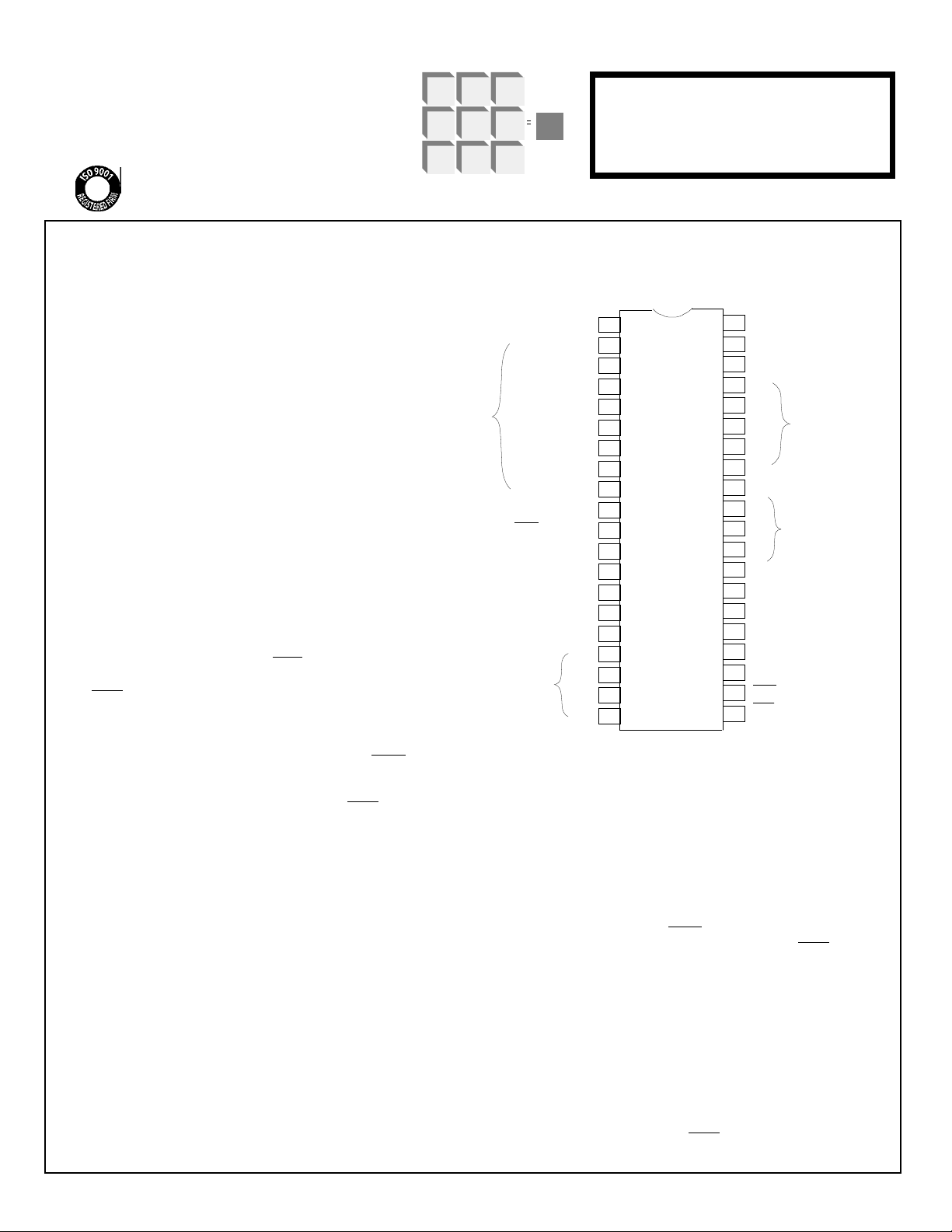

LS7030

8 DECADE MULTIPLEXED COUNTER

FEATURES:

• DC to 7.5 MHz Count Frequency

• Multiplexed BCD and 7 Segment Outputs

• DC to 500 kHz Scan Frequency

• +4.75V to +15V Operation (VDD-VSS)

• Compatible with CMOS Logic

• High Input Noise Immunity

• Counter Output Latches

• Leading Zero Blanking

• Low Power Dissipation

• All inputs protected

• 40 Pin DIP- See Figure 1

DESCRIPTION:

The LS7030 is a monolithic, ion implanted MOS Silicon Gate, 8

decade up counter. The circuit includes latches, multiplexer,

leading zero blanking and 7 segment data outputs.

8 DECADE UP COUNTER

The eight decade ripple through counter increments on the negative edge of the input count pulse. Maximum ripple time is 12µs

(99999999 to 00000000). Maximum count frequency is 7.5MHz.

RESET

All decades are reset to zero when Reset input is brought low for

a minimum of 4µs. The Overflow flip-flop is reset at the same

time. Reset must be high for a minimum of 1µs before next valid

count can be recorded.

SCAN RESET INPUT

MSD STROBE 8

DIGIT

STROBE

OUTPUTS

LSD STROBE 1

DECIMAL POINT INPUT

BLANK OUTPUT

OVERFLOW OUTPUT

OVERFLOW INPUT

DECADE 6 OUTPUT, D8

DECADE 7 OUTPUT, D7

DECADE 6 OUTPUT, D6

BCD

DATA

OUTPUTS

STROBE 7

STROBE 6

STROBE 5

STROBE 4

STROBE 3

STROBE 2

B8

B4

B2

B1

CONNECTION DIAGRAM - TOP VIEW

LSI

1

2

3

4

5

6

7

8

LS7030

9

10

11

12

13

14

15

16

17

18

19

20

40

OSC. INPUT

SCAN INPUT

39

38

LAMP TEST INPUT

37

a

36

N.C.

35

c

34

33

COUNT INPUT

32

31

30

29

28

TEST COUNT INPUT, DIGITS 3 - 8

27

VSS

26

VGG

25

N.C.

24

N.C.

23

VDD

RESET COUNTER INPUT

22

LOAD LATCH INPUT

21

December 2002

SEGMENT

OUTPUTS

SEGMENT

OUTPUTS

LATCHES

Contents of counter are transferred to latches when LOAD signal

is brought low for a minimum of 4µs and kept low until a minimum

of 12µs has elapsed from previous negative edge of count pulse

(ripple time). Storage of valid data occurs when LOAD signal is

high for a minimum of 1µs before next negative edge of count

pulse or reset. Data is transferred for Overflow flip-flop to Overflow latch at the same time.

SCAN OSCILLATOR AND COUNTER

The scan counter is driven by an internal oscillator whose frequency is determined by a capacitor connected between Oscillator input and Scan input. An external scan clock applied to

Scan input can also drive the scan counter. Scan counter advances on negative edge of scan clock.

The counter scans from MSD to LSD. When Scan Reset input is

brought high the scan counter is forced to MSD state. Internal

synchonization guarantees proper scanning no matter when Scan

Reset is brought low relative to scan clock. Maximum scan

frequency is 500kHz.

DECIMAL POINT

A high at the Decimal Point input resets the Blanking flip-flop

causing the display to unblank. Decimal Point should be brought

high at start of digit time which has active Decimal Point.

7030-121102-1

FIGURE 1

DIGIT STROBES

Timing of Digit Strobes is arranged such that both edges of strobe

are guardbanded by a minimum 400ns within valid BCD data when

scan frequency is 100kHz or less. The guardband is a minimum of

200ns at 250kHz scan frequency. At 500kHz only negative edge of

Strobe is guaranteed to be within valid BCD data by a minimum

200ns.

OVERFLOW

The Overflow flip-flop sets on the first negative transition of the Overflow Input and remains set until Reset is brought low. Data is transferred from Overflow flip-flop to Overflow Latch when Load is brought

low. A high at the Overflow Latch causes display to unblank. Overflow Output is output of Overflow Latch. MSB outputs of Decades

6, 7, 8 are available for use as Overflow Input.

BLANKING

Leading zero blanking is employed. At start of each MSD to LSD

scan, display is blanked until a nonzero digit or active decimal point is

encountered. Displaly unblanks during LSD time and for a whole

scan when Overflow output is high. When Scan Reset is applied, display blanks to prevent display damage.

Blanking information is available at Blank output and is incorporated

into 7 segment information.

BCD and 7 SEGMENT DATA

Data is available in BCD and 7 segment format. BCD data can be

demultiplexed using Digit Strobes as latch enable signals.

POWER SUPPLIES

+4.75 Volts to +15 Volts single power supply operation is obtained

when VGG and VDD are tied together. Inputs and outputs are

CMOS compatible and Minimum Input Noise Immunity of 25% of

power supply is guaranteed except for Test Count Input. (Inputs

are TTL compatible at +4.75V to +5.25V operation.)

MAXIMUM RATINGS

PARAMETER SYMBOL VALUE UNITS

Storage Temperature Tstg -65 to +150 °C

Operating Temperature TA -25 to +70 °C

Voltage (any pin to Vss) Vmax -30 to +0.5 V

DC ELECTRICAL CHARACTERISTICS

(VDD = VGG= OV, Vss = +4.75 to +15V, -25°C ≤ TA ≥ +70°C unless otherwise specified.)

PARAMETER SYMBOL MIN MAX UNITS

Operating Supply Current Idds - 15 mA

(fC = 7.5MHz)

Input Noise Immunity

Low and High Vni 25% - V

Test Count Input Vil Vss - 20 Vss - 3.95 V

Vih Vss - 1.0 Vss V

D6, D7, D8

OF, BCD

Blank

(See Note 1)

Segment

and

Strobe

Outputs

(See Note 2)

Output Voltage “0" Vol - +0.2 V

{

Output Voltage “1" Voh Vss - 1.0 - V

Output Voltage “0"

(sinking 10µA) Vol - +0.5 V

Output Voltage “1"

Vss = 4.75 (Voh = Vss - 0.5V) - 0.05 - mA

(Voh = Vss - 1V) - 0.25 - mA

(Voh = Vss - 4V) - 0.90 - mA

Vss = 10V (Voh = Vss - 2V) - 2.0 - mA

(Voh = Vss - 3V) - 3.0 - mA

Vss = 15V (Voh = Vss - 2V) - 3.0 - mA

(Voh = Vss - 3V) - 4.5 - mA

With VGG at -12V, VDD at OV and Vss at +5V, all inputs are TTL

and CMOS compatible. All outputs are CMOS compatible and

BCD and BLANK outputs also provide standard TTL compatibility. In addition, Overflow Output is low power TTL compatible.

In either mode outputs swing between VDD and Vss.

(Vss-VDD)

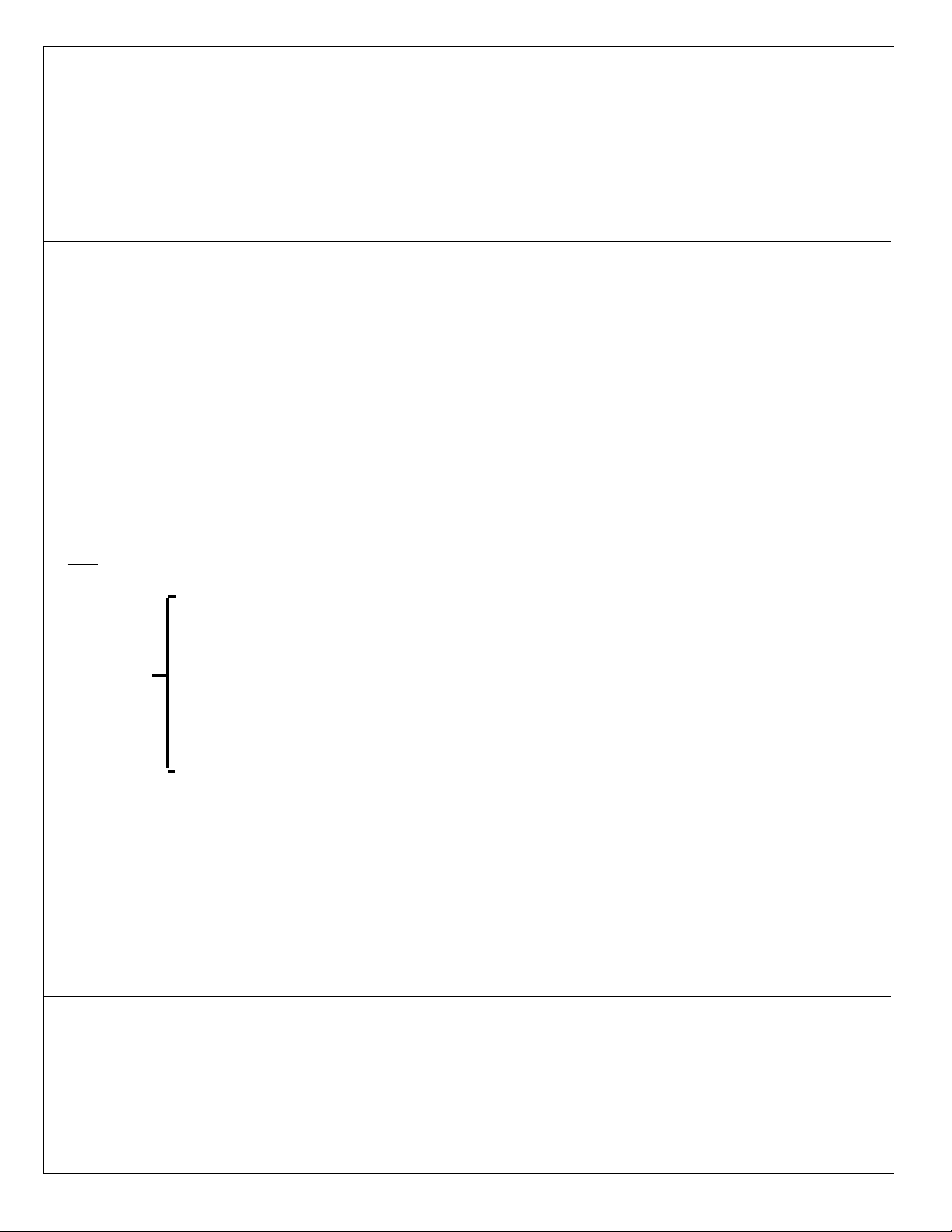

SCAN OSCILLATOR

7030-110201-2

NOTE 1: Current Sink = Same as segment and strobe outputs.

Current Source = N/A at Voh = Vss -.5V for Vss = +4.75V

35µA at Voh = Vss -1V for Vss = +4.75V

40% of segment and strobe outputs at all other specified operating points.

NOTE 2: Limit segment current to 4.5mA maximum.

Limit strobe current to 6mA maximum.

The following inputs have internal pull down resistors to VDD with maximum sink current of 5µA at Vss input.

Scan Reset Test Count Count

Decimal Point Overflow Lamp Test

CAPACITANCE TYPICAL OSCILLATOR FREQUENCY

4.75V 10V 15V

50pF 40.0 kHz 24.2kHz 22.2 kHz

100pF 22.2 kHz 14.8kHz 13.8 kHz

470pF 5.0 kHz 3.6kHz 3.5 kHz

750pF 3.3 kHz 2.4kHz 2.2 kHz

2000pF 1.3 kHz 0.91kHz 0.85 kHz

Loading...

Loading...