LRC MC74VHC1G03DFT1, MC74VHC1G03DTT1, MC74VHC1G03DTT3, MC74VHC1G03DFT2, MC74VHC1G03DFT4 Datasheet

2–Input NAND Gate with

LESHAN RADIO COMPANY, LTD.

Open Drain Output

The MC74VHC1G03 is an advanced high speed CMOS 2–input NOR gate with an open drain output fabricated with silicon gate

CMOS technology. It achieves high speed operation similar to equivalent Bipolar Schottky TTL while maintaining CMOS low power

dissipation.

The internal circuit is composed of three stages, including an open drain output which provides the capability to set output switching

level. This allows the MC74VHC1G03 to be used to interface 5 V circuits to circuits of any voltage between V

resistor and power supply.

The MC74VHC1G03 input structure provides protection when voltages up to 7 V are applied, regardless of the supply voltage.

• High Speed: t

• Low Internal Power Dissipation: I

• Power Down Protection Provided on Inputs

• Pin and Function Compatible with Other Standard Logic Families

• Chip Complexity: FETs = 62; Equivalent Gates = 16

= 3.6 ns (Typ) at V

PD

= 5 V

CC

= 2 mA (Max) at T A = 25°C

CC

MC74VHC1G03

and 7 V using an external

CC

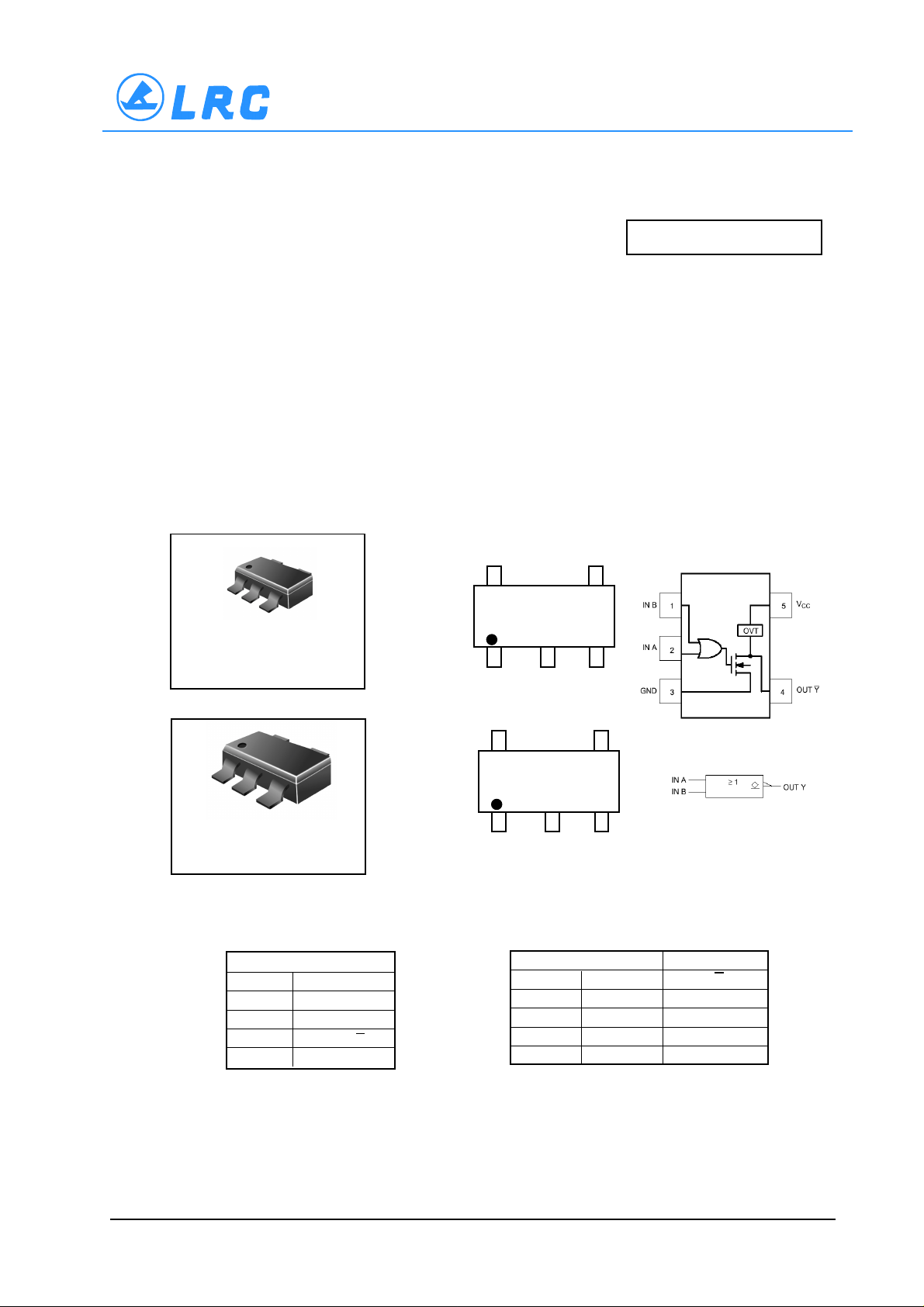

MARKING DIAGRAMS

5

4

1

2

3

SC–88A / SOT–353/SC–70

DF SUFFIX

CASE 419A

5

4

Pin 1

d = Date Code

VP

d

Figure 1. Pinout (Top View)

1

2

3

TSOP–5/SOT–23/SC–59

DT SUFFIX

CASE 483

PIN ASSIGNMENT

1 IN B

2 IN A

3 GND

4 OUT Y

5V

d

VP

Figure 2. Logic Symbol

Pin 1

d = Date Code

FUNCTION T ABLE

Inputs Output

AB Y

LL Z

LH L

HL L

CC

HH L

ORDERING INFORMATION

See detailed ordering and shipping information in the

package dimensions section on page 4 of this data sheet.

VH3–1/4

LESHAN RADIO COMPANY, LTD.

MC74VHC1G03

MAXIMUM RATINGS

Symbol Parameter Value Unit

V

CC

V

IN

V

OUT

I

IK

I

OK

I

OUT

I

CC

P

D

θ

JA

T

L

T

J

T stg Storage temperature –65 to +150 °C

V

ESD

I

LATCH–UP

1. Maximum Ratings are those values beyond which damage to the device may occur. Exposure to these conditions or conditions

beyond those indicated may adversely affect device reliability . Functional operation under absolute–maximum–rated conditions is

not implied. Functional operation should be restricted to the Recommended Operating Conditions.

2. Tested to EIA/JESD22–A114–A

3. Tested to EIA/JESD22–A115–A

4. Tested to JESD22–C101–A

5. Tested to EIA/JESD78

RECOMMENDED OPERATING CONDITIONS

Symbol Parameter Min Max Unit

V

CC

V

IN

V

OUT

T

A

t r ,t

f

DC Supply Voltage – 0.5 to + 7.0 V

DC Input Voltage – 0.5 to 7.0 V

DC Output Voltage V CC=0 – 0.5 to 7.0 V

High or Low State –0.5 to V cc + 0.5

Input Diode Current –20 mA

Output Diode Current V

< GND; V

OUT

OUT

> V

CC

+20 mA

DC Output Current, per Pin + 25 mA

DC Supply Current, V

and GND +50 mA

CC

Power dissipation in still air SC–88A, TSOP–5 200 mW

Thermal resistance SC–88A, TSOP–5 333 °C/W

Lead Temperature, 1 mm from Case for 10 s 260 °C

Junction T emperature Under Bias + 150 °C

ESD Withstand Voltage Human Body Model (Note 2) >2000 V

Machine Model (Note 3) > 200

Charged Device Model (Note 4) N/A

Latch–Up Performance Above V

and Below GND at 125°C (Note 5) ± 500 mA

CC

DC Supply Voltage 2.0 5.5 V

DC Input Voltage 0.0 5.5 V

DC Output Voltage 0.0 7.0 V

Operating T emperature Range – 55 + 125 °C

Input Rise and Fall Time V

= 3.3 ± 0.3 V 0 100 ns/V

CC

V

= 5.0 ± 0.5 V 0 20

CC

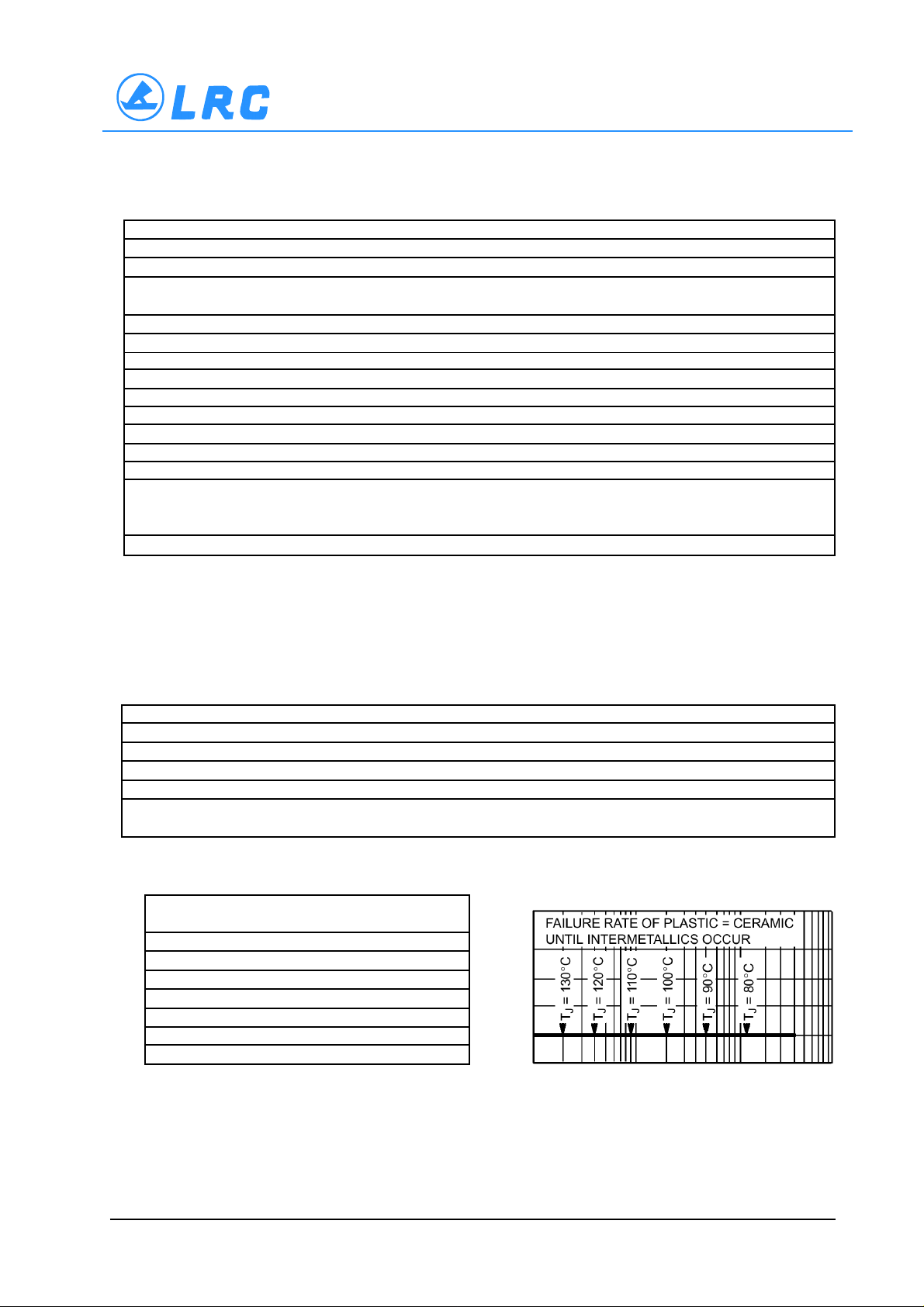

DEVICE JUNCTION TEMPERATURE VERSUS

TIME TO 0.1% BOND FAILURES

Junction Time, Time,

Temperature °C Ho urs Years

80 1,032,200 117.8

90 419,300 47.9

100 178,700 20.4

1 10 79,600 9.4

120 37,000 4.2

130 17,800 2.0

140 8,900 1.0

1

NORMALIZED FAILURE RATE

1 10 100 1000

TIME, YEARS

Figure 3. Failure Rate vs. Time

Junction Temperature

VH3–2/4

Loading...

Loading...