DEVICES INCORPORATED

LF3330

Vertical Digital Image Filter

LF3330

DEVICES INCORPORATED

FEATURES DESCRIPTION

❑❑

❑ 83 MHz Data Rate

❑❑

❑❑

❑ 12-bit Data and Coefficients

❑❑

❑❑

❑ On-board Memory for 256

❑❑

Coefficient Sets

❑❑

❑ LF InterfaceTM Allows All 256

❑❑

Coefficient Sets to be Updated

Within Vertical Blanking

❑❑

❑ Selectable 16-bit Data Output with

❑❑

User-Defined Rounding and

Limiting

❑❑

❑ Seven 3K x 12-bit, Programmable

❑❑

Two-Mode Line Buffers

❑❑

❑ Separate Input Port for Odd and

❑❑

Even Field Filtering

❑❑

❑ 8 Filter Taps

❑❑

❑❑

❑ Cascadable for More Filter Taps

❑❑

❑❑

❑ Supports Interleaved Data Streams

❑❑

❑❑

❑ 3.3 Volt Power Supply

❑❑

❑❑

❑ 5 Volt Tolerant I/O

❑❑

❑❑

❑ 100 Lead PQFP

❑❑

The LF3330 filters digital images in

the vertical dimension at real-time

video rates. The input and coefficient

data are both 12 bits and in two’s

complement format. The output is

also in two’s complement format and

may be rounded to 16 bits.

The filter is an 8-tap FIR filter with all

required line buffers contained onchip. The line buffers can store video

lines with lengths from 4 to 3076

pixels.

Multiple LF3330s can be cascaded

together to create larger vertical

filters.

Due to the length of the line buffers,

interleaved data can be fed directly

into the device and filtered without

Vertical Digital Image Filter

separating the data into individual

data streams. The number of interleaved data sets that the device can

handle is limited only by the length of

the on-chip line buffers. If the interleaved video line has 3076 data values

or less, the filter can handle it.

The LF3330 contains enough on-board

memory to store 256 coefficient sets.

The LF InterfaceTM allows all 256

coefficient sets to be updated within

vertical blanking.

Selectable 16-bit data output with

user-defined rounding and limiting

minimizes the constraints put on

coefficient sets for various filter

implementations.

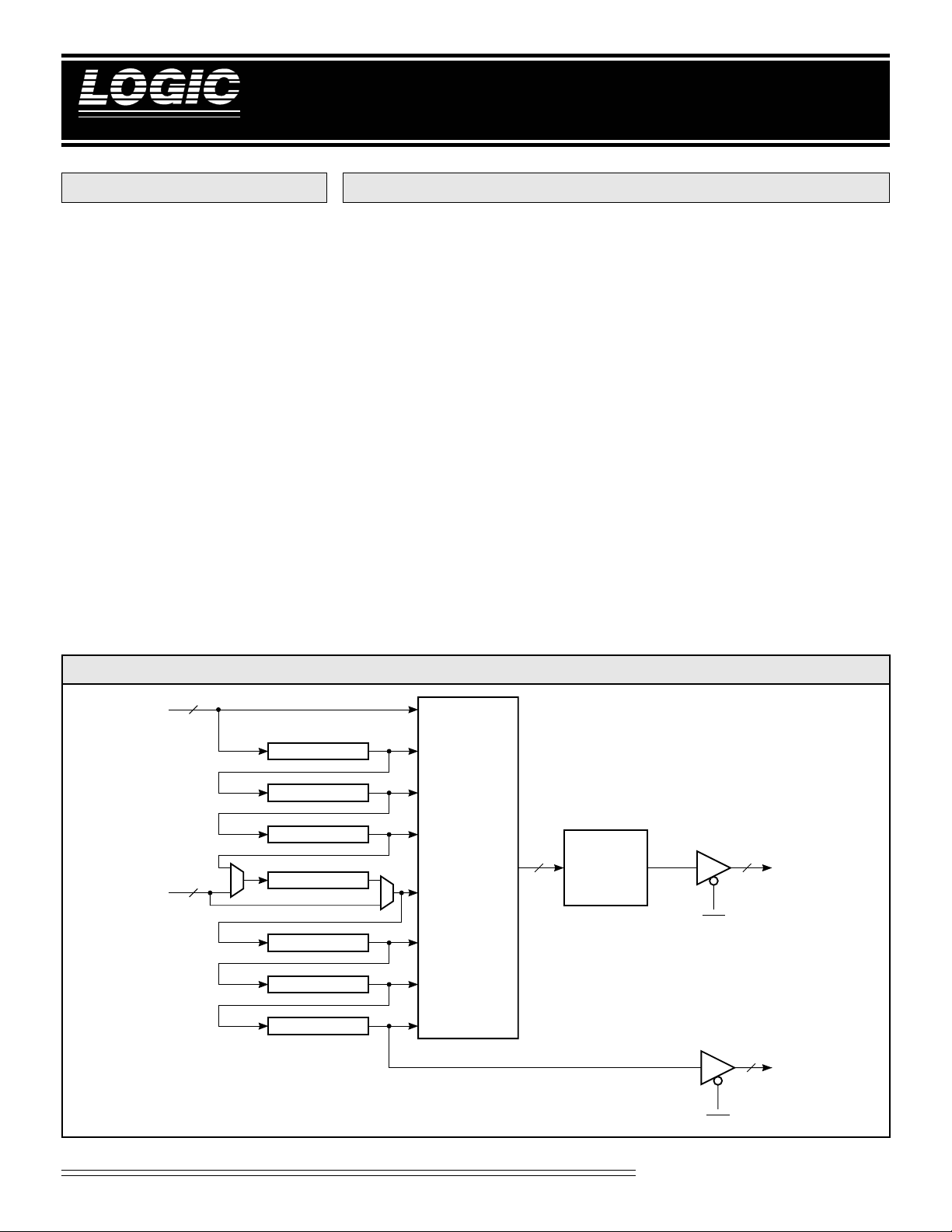

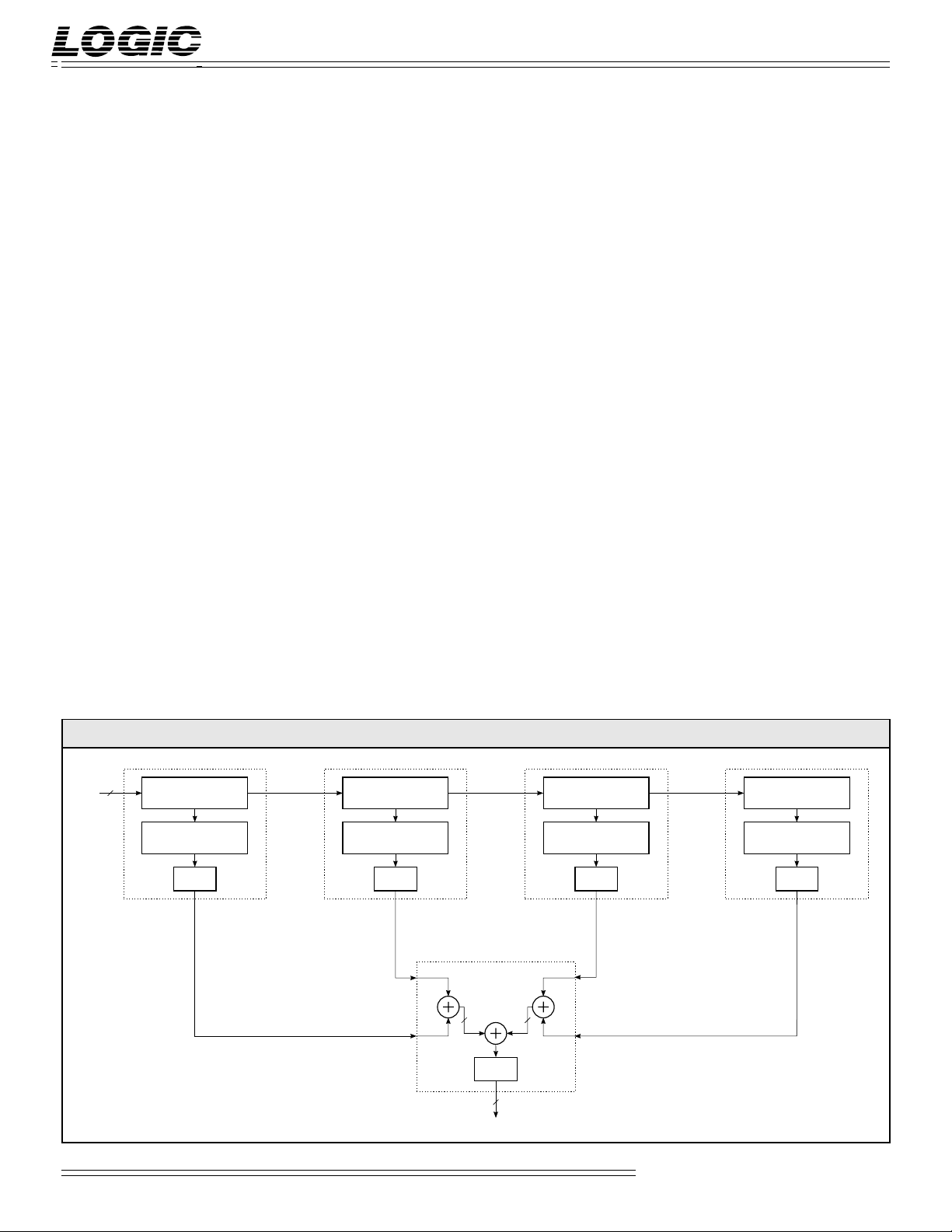

LF3330 BLOCK DIAGRAM

DIN

VB

12

11-0

12

11-0

3K LINE BUFFER

3K LINE BUFFER

3K LINE BUFFER

3K LINE BUFFER

3K LINE BUFFER

3K LINE BUFFER

3K LINE BUFFER

32

8-TAP VERTICAL FILTER

256 COEFFICIENT SET STORAGE

ROUND

SELECT

LIMIT

CIRCUITRY

OED

OEC

16

12

DOUT

COUT

15-0

11-0

Video Imaging Products

1

11/08/2001–LDS.3330-M

DEVICES INCORPORATED

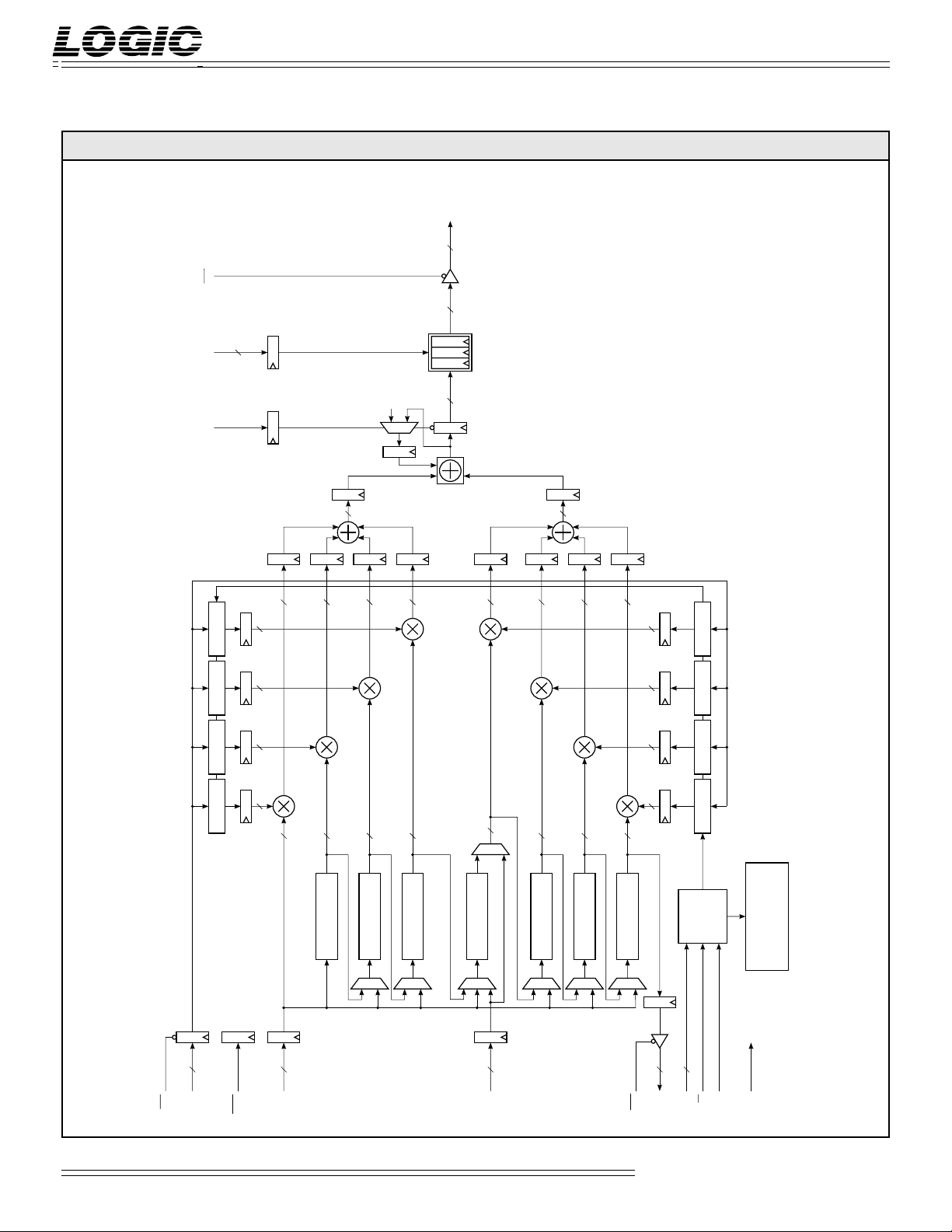

FIGURE 1. LF3330 FUNCTIONAL BLOCK DIAGRAM

OED

3-0

4

RSL

16

16

15-0

DOUT

LIMIT

SELECT

ROUND

LF3330

Vertical Digital Image Filter

ACC

Coef Bank 7 Coef Bank 6 Coef Bank 5 Coef Bank 4

"0"

26

24

24

24

12 12 12 12

12

12

12

32

26

24

12

24

12

24

24

24

12 12 12 12

12

12

12

Coef Bank 0 Coef Bank 1 Coef Bank 2 Coef Bank 3

CEN

LF

12

11-0

CF

INTERFACE

LD

PAUSE

CONFIGURATION AND

CONTROL REGISTERS

CLK

3K Line Buffer

3K Line Buffer

3K Line Buffer

8

7-0

CA

SHEN

12

11-0

DIN

3K Line Buffer

12

11-0

VB

3K Line Buffer

3K Line Buffer

3K Line Buffer

12

11-0

OEC

COUT

Video Imaging Products

2

11/08/2001–LDS.3330-M

DEVICES INCORPORATED

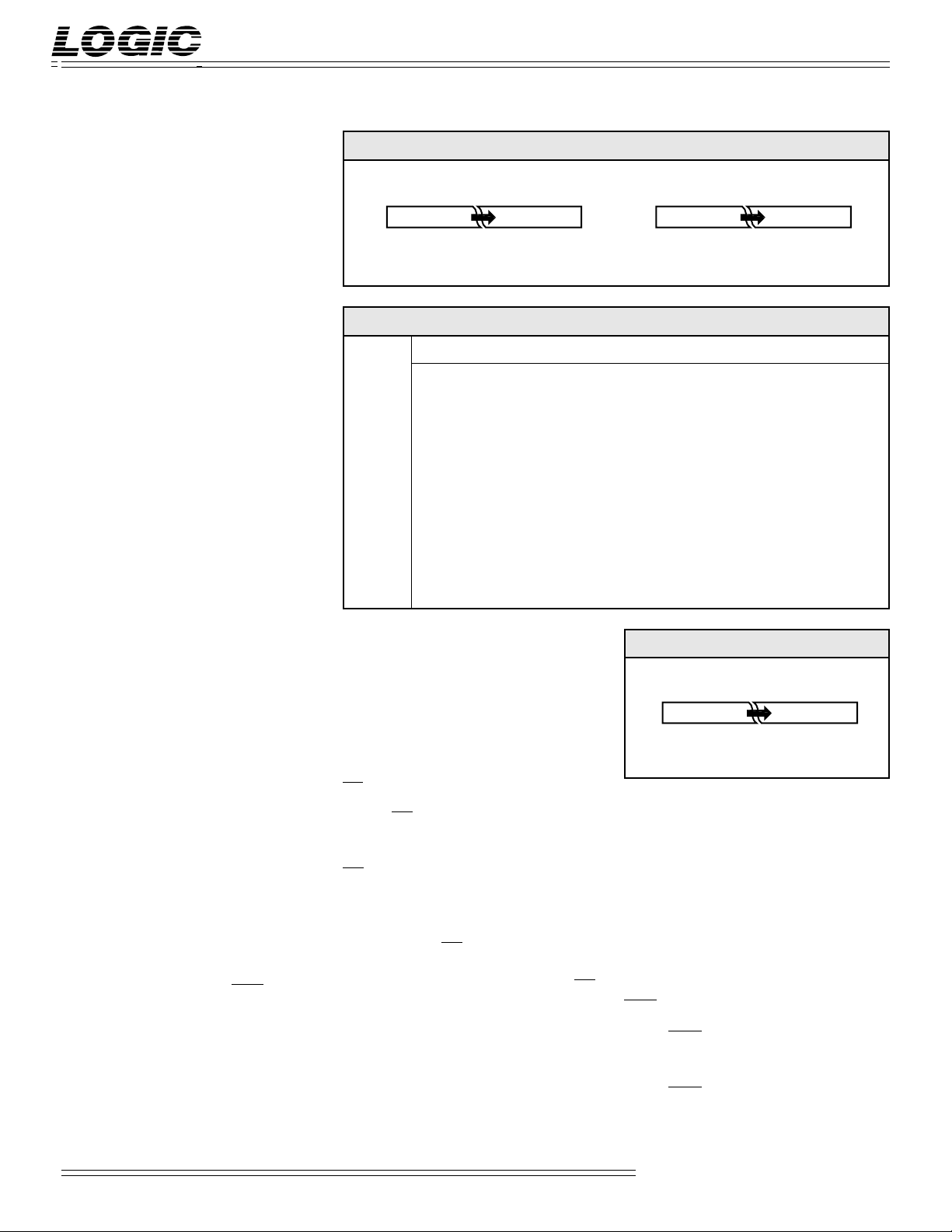

31 30 29 2 1 0

–2

20

(Sign)

2192

18

2–92

–102–11

Accumulator Output

LF3330

Vertical Digital Image Filter

SIGNAL DEFINITIONS

Power

VCC and GND

+3.3 V power supply. All pins must be

connected.

Clock

CLK — Master Clock

The rising edge of CLK strobes all

enabled registers.

Inputs

DIN11-0 — Data Input

DIN11-0 is the 12-bit registered data

input port. Data is latched on the rising

edge of CLK.

VB11-0 — Field Filtering Data Input

VB11-0 is the 12-bit registered data

input port used only when implementing Odd and Even Field Filtering (see

Functional Description section for a full

discussion). Data is latched on the

rising edge of CLK.

CF11-0 — Coefficient Input

CF11-0 is used to load data into the

coefficient banks and configuration/

control registers. Data present on

CF11-0 is latched into the LF Interface

on the rising edge of CLK when LD is

LOW (see the LF InterfaceTM section for

a full discussion).

CA7-0 — Coefficient Address

CA7-0 determines which row of data in

the coefficient banks is fed to the

multipliers. CA7-0 is latched into the

Coefficient Address Register on the

rising edge of CLK when CEN is LOW.

Outputs

DOUT15-0 — Data Output

DOUT15-0 is the 16-bit registered data

output port.

FIGURE 2. INPUT FORMATS

Input Data Coefficient Data

11 10 9 2 1 0

11

–2

(Sign)

2102

9

22212

0

11 10 9 2 1 0

–2

(Sign)

0

2–12

–2

2–92

TABLE 1. OUTPUT FORMATS

SLCT4-0 S15 S14 S13 · · · S8 S7 · · · S2 S1 S0

00000 F15 F14 F13 · · · F8 F7 · · · F2 F1 F0

00001 F16 F15 F14 · · · F9 F8 · · · F3 F2 F1

00010 F17 F16 F15 · · · F10 F9 · · · F4 F3 F2

· ··· ·· ···

· ··· ·· ···

· ··· ·· ···

01110 F29 F28 F27 · · · F22 F21 · · · F16 F15 F14

01111 F30 F29 F28 · · · F23 F22 · · · F17 F16 F15

10000 F31 F30 F29 · · · F24 F23 · · · F18 F17 F16

COUT11-0 — Cascade Data Output

FIGURE 3. ACCUMULATOR FORMAT

COUT11-0 is a 12-bit cascade

output port. COUT11-0 on one

device should be connected to

DIN11-0 of another LF3330.

Controls

TM

LD — Coefficient Load

PAUSE — LF InterfaceTM Pause

When LD is LOW, data on CF11-0

is latched into the LF Interface

TM

on the rising edge of CLK. When

LD is HIGH, data can not be

latched into the LF InterfaceTM.

When enabling the LF Interface

for data input, a HIGH to LOW

transition of LD is required in

order for the input circuitry to

When PAUSE is HIGH, the LF

InterfaceTM loading sequence is halted

until PAUSE is returned to a LOW

state. This effectively allows the user

TM

to load coefficients and control

registers at a slower rate than the

master clock (see the LF Interface

section for a full discussion).

function properly. Therefore, LD

must be set HIGH immediately

CEN — Coefficient Address Enable

after power up to ensure proper

operation of the input circuitry

(see the LF InterfaceTM section for

a full discussion).

When CEN is LOW, data on CA7-0 is

latched into the Coefficient Address

Register on the rising edge of CLK.

When CEN is HIGH, data on CA7-0 is

not latched and the register’s contents

will not be changed.

Video Imaging Products

3

–102–11

TM

11/08/2001–LDS.3330-M

DEVICES INCORPORATED

LF3330

Vertical Digital Image Filter

TABLE 2. CONFIGURATION REGISTER 0 – ADDRESS 200H

BITS FUNCTION DESCRIPTION

11-0 Line Buffer Length See Line Buffer Description Section

TABLE 3. CONFIGURATION REGISTER 1 – ADDRESS 201H

BITS FUNCTION DESCRIPTION

0 Line Buffer Mode 0: Delay Mode

1: Recirculate Mode

1 Line Buffer Load 0: Normal Load

1: Parallel Load

2 Odd and Even Field 0: VB Port Disabled

Filtering Port Enable 1: VB Port Enabled

3 Odd and Even Field 0: VB Line Buffer Disabled

Filtering Line Buffer Enable 1: VB Line Buffer Enabled

11-4 Reserved Must be set to “0”

TABLE 4. CONFIGURATION REGISTER 2 – ADDRESS 202H

BITS FUNCTION DESCRIPTION

0 Limit Enable 0: Limiting Disabled

1: Limiting Enabled

11-1 Reserved Must be set to “0”

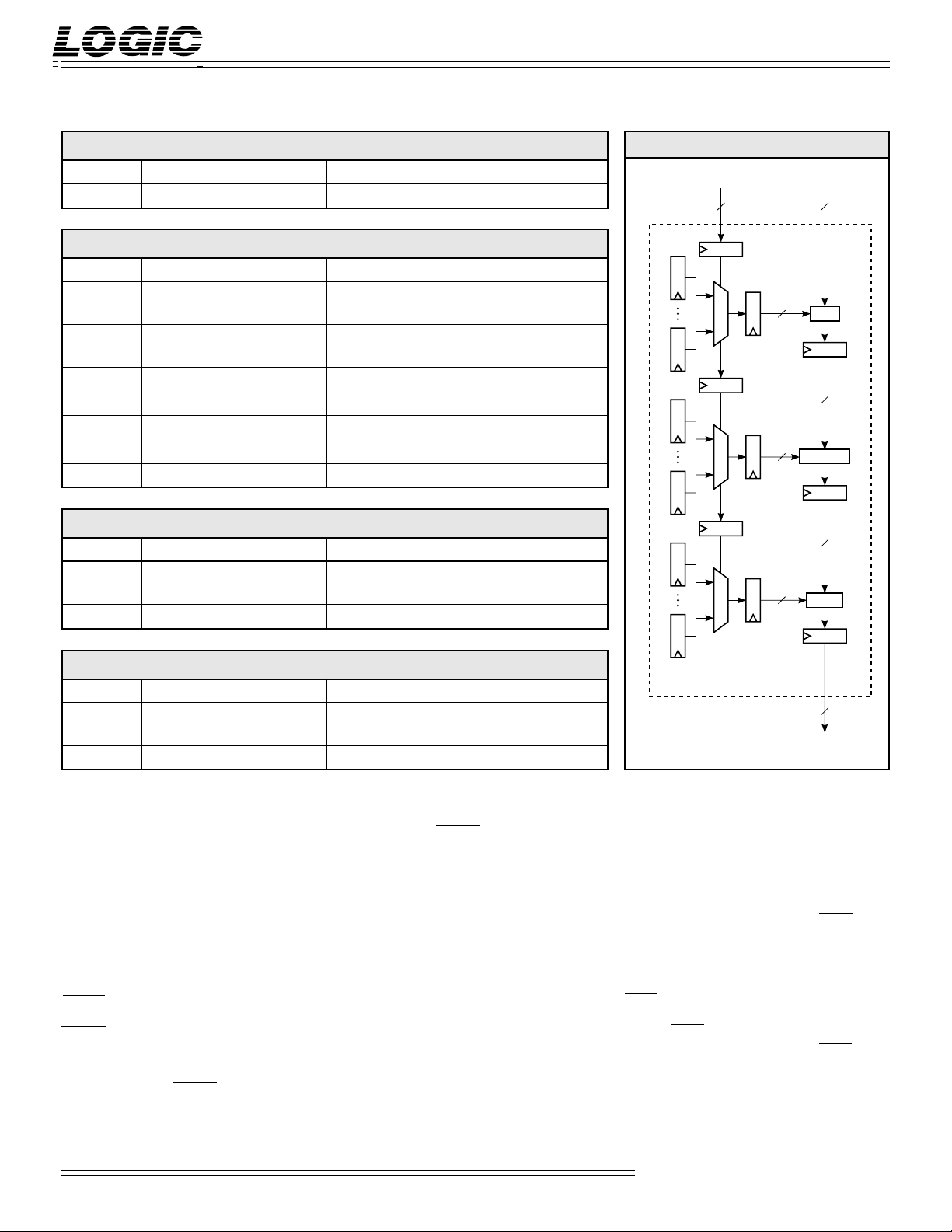

FIGURE 4. RSL CIRCUITRY

RSL

3-0

4

R0R15

S0S15

L0L15

DATA IN

32

32

RND

32

5

SELECT

16

32

LIMIT

TABLE 5. CONFIGURATION REGISTER 3 – ADDRESS 203H

BITS FUNCTION DESCRIPTION

0 Cascade Mode 0: First Device

1: Cascaded Device

11-1 Reserved Must be set to “0”

ACC — Accumulator Control

When ACC is HIGH, the accumulator

is enabled for accumulation and the

accumulator output register is

disabled for loading. When ACC is

LOW, no accumulation is performed

and the accumulator output register

is enabled for loading. ACC is

latched on the rising edge of CLK.

SHEN — Shift Enable

SHEN enables or disables the

loading of data into the input/

cascade registers and the line

buffers. When SHEN is LOW, data

is loaded into the input/cascade

registers and shifted through the

line buffers on the rising edge of

CLK. When SHEN is HIGH, data

can not be loaded into the input/

cascade registers or shifted through

the line buffers and their contents

will not be changed.

RSL3-0 — Round/Select/Limit Control

RSL3-0 determines which of the

sixteen user-programmable round/

select/limit registers are used in the

round/select/limit circuitry. A

value of 0 on RSL3-0 selects round/

select/limit register 0. A value of 1

selects round/select/limit register 1

and so on. RSL3-0 is latched on the

RSL CIRCUITRY

16

DATA OUT

rising edge of CLK (see the round,

select, and limit sections for a

complete discussion).

OED — DOUT Output Enable

When OED is LOW, DOUT15-0 is

enabled for output. When OED is

HIGH, DOUT15-0 is placed in a

high-impedance state.

OEC — COUT Output Enable

When OEC is LOW, COUT15-0 is

enabled for output. When OEC is

HIGH, COUT15-0 is placed in a highimpedance state.

Video Imaging Products

4

11/08/2001–LDS.3330-M

DEVICES INCORPORATED

LF3330

Vertical Digital Image Filter

FUNCTIONAL DESCRIPTION

Line Buffers

The maximum delay length of each line

buffer is 3076 cycles and the minimum

is 4 cycles. Configuration Register 0

(CR0) determines the delay length of

the line buffers. The line buffer length

is equal to the value of CR0 plus 4. A

value of 0 for CR0 sets the line buffer

length to 4. A value of 3072 for CR0

sets the line buffer length to 3076. Any

values for CR0 greater than 3072 are not

valid.

The line buffers have two modes of

operation: delay mode and recirculate

mode. Bit 0 of Configuration Register 1

determines which mode the line buffers

are in. In delay mode, the data input to

the line buffer is delayed by an amount

determined by CR0. In recirculate

mode, the output of the line buffer is

routed back to the input of the line

buffer allowing the line buffer contents

to be read multiple times.

Bit 1 of Configuration Register 1 allows

the line buffers to be loaded in parallel.

When Bit 1 is “1”, the input register

(DIN11-0) loads all seven line buffers in

parallel. This allows all the line buffers

to be preloaded with data in the

amount of time it normally takes to

load a single line buffer.

Odd and Even Field Filtering

The LF3330 is capable of odd and even

field filtering. Bit 2 of Configuration

Register 1 enables the VB Data Input

port required for odd and even field

filtering. Bit 3 of the same configuration register enables the line buffer in

the VB Data path. Line buffer length is

set to the length written to Configuration Register 0. If line buffer parallel

load is enabled and odd and even field

filtering is enabled, the data for the VB

line buffer comes from the VB Data

Input port.

Interleaved Data

The LF3330 is capable of handling

interleaved data. The number of data

sets it can handle is determined by the

number of data values contained in a

video line. If the interleaved video line

has 3076 data values or less, the LF3330

can handle it no matter how many data

sets are interleaved together.

Cascading

A cascade port is provided to allow

cascading of multiple devices for

more filter taps (see Figure 5).

COUT11-0 of one device should be

connected to DIN11-0 of another

device. As many LF3330s as desired

may be cascaded together. However, the outputs of the LF3330s

must be added together with external adders.

The first line buffer on a cascaded

device must have its length shortened by two delays. This is to

account for the added delays of the

input register on the device and the

cascade output register from the

previous LF3330. If Bit 0 of Configuration Register 3 is set to “1”,

the length of the first line buffer will

be reduced by two. This will make

its effective length the same as the

other line buffers on the device. If

Bit 0 of Configuration Register 3 is

set to “0”, the length of the first line

buffer will be the same as the other

line buffers. When cascading

devices, the first LF3330 should

have Bit 0 of Configuration Register

FIGURE 5. MULTIPLE LF3330S CASCADED TOGETHER

12

DIN LINE BUFFERS

VERTICAL FILTER

RSL

CIRCUIT

COUT DIN

LINE BUFFERS LINE BUFFERS LINE BUFFERS

VERTICAL FILTER VERTICAL FILTER VERTICAL FILTER

RSL

CIRCUIT

COUT

29 TAP RESULT

5

LF3330LF3330LF3330

DIN DIN

RSL

CIRCUIT

LF3347

2525

RSL

CIRCUIT

16

DATA OUT

LF3330

COUT

RSL

CIRCUIT

Video Imaging Products

11/08/2001–LDS.3330-M

Loading...

Loading...