DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

LF3320

DEVICES INCORPORATED

FEATURES DESCRIPTION

❑❑

❑ 83 MHz Data Rate

❑❑

❑❑

❑ 12-bit Data or Coefficients (Expand-

❑❑

able to 24-bit)

❑❑

❑ 32-Tap FIR Filter, Cascadable for

❑❑

More Filter Taps

❑❑

❑ Over 49 K-bits of on-board Memory

❑❑

❑❑

❑ LF InterfaceTM Allows All 256

❑❑

Coefficient Sets to be Updated

Within Vertical Blanking

❑❑

❑ Various Operating Modes: Dual

❑❑

Filter, Single Filter, Double Wide

Data or Coefficient, Matrix Multiplication, and Accumulator Access.

❑❑

❑ Selectable 16-bit Data Output with

❑❑

User-Defined Rounding and Limiting

❑❑

❑ Supports Interleaved Data Streams

❑❑

❑❑

❑ Supports Decimation up to 16:1 for

❑❑

Increasing Number of Filter Taps

❑❑

❑ 3.3 Volt Supply

❑❑

❑❑

❑ 144 Lead PQFP

❑❑

The LF3320 filters digital images in the

horizontal dimension at real-time

video rates. The input and coefficient

data are both 12 bits and in two’s

complement format. The output is also

in two’s complement format and may

be rounded to 16 bits.

The LF3320 is designed to take

advantage of symmetric coefficient

sets. When symmetric coefficient sets

are used, the device can be configured

as a single 32-tap FIR filter or as two

separate 16-tap FIR filters.

When asymmetric coefficient sets are

used, the device can be configured as a

single 16-tap FIR filter or as two

separate 8-tap FIR filters. Multiple

LF3320s can be cascaded to create

larger filters.

Horizontal Digital Image Filter

Interleave/Decimation Registers (I/D

Registers) allow interleaved data to be

fed directly into the device and filtered

without separating the data into

individual data streams.

The LF3320 can handle a maximum of

sixteen data sets interleaved together.

The I/D Registers and on-chip accumulators facilitate using decimation to

increase the number of filter taps.

Decimation of up to 16:1 is supported.

The LF3320 contains enough on-board

memory to store 256 coefficient sets.

Two separate LF InterfacesTM allow all

256 coefficient sets to be updated within

vertical blanking.

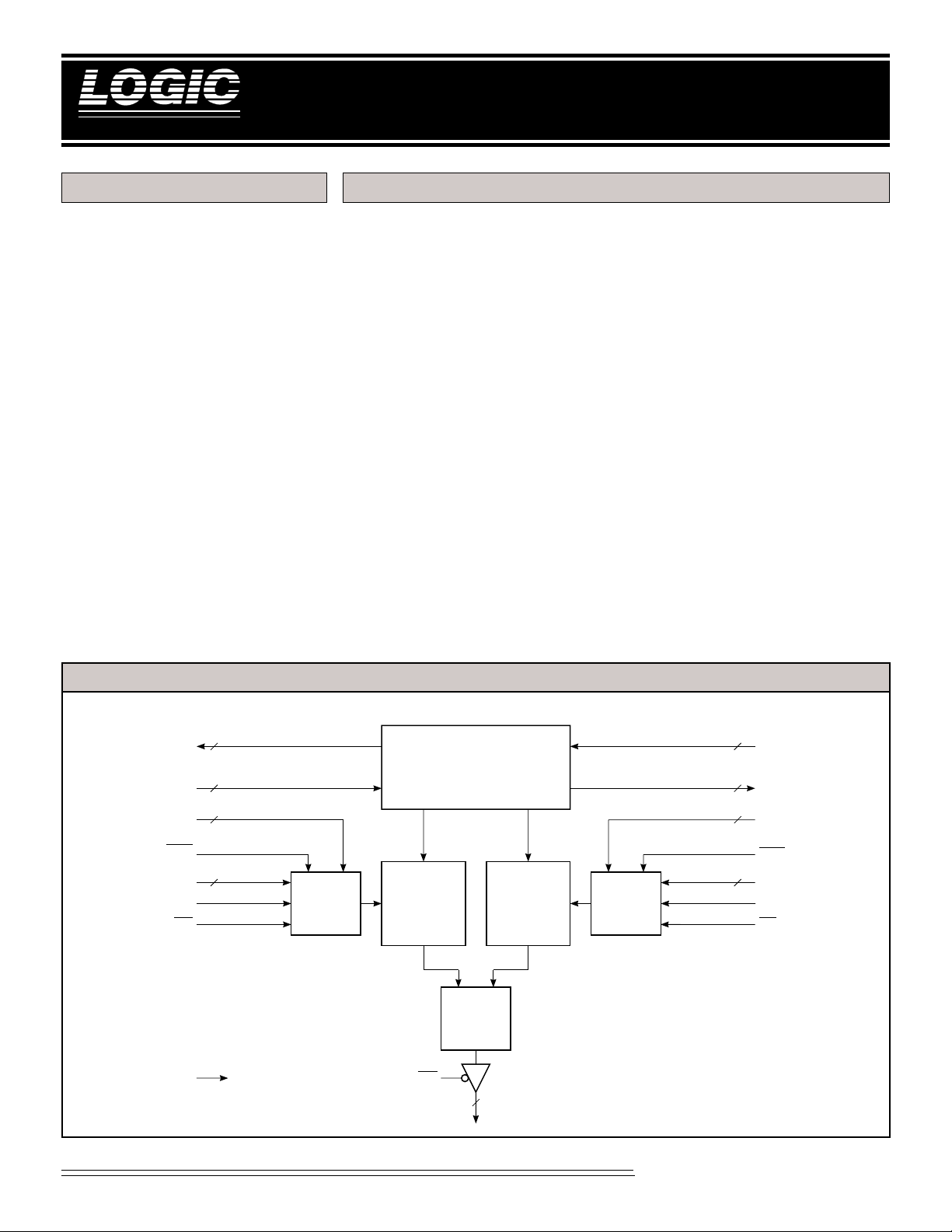

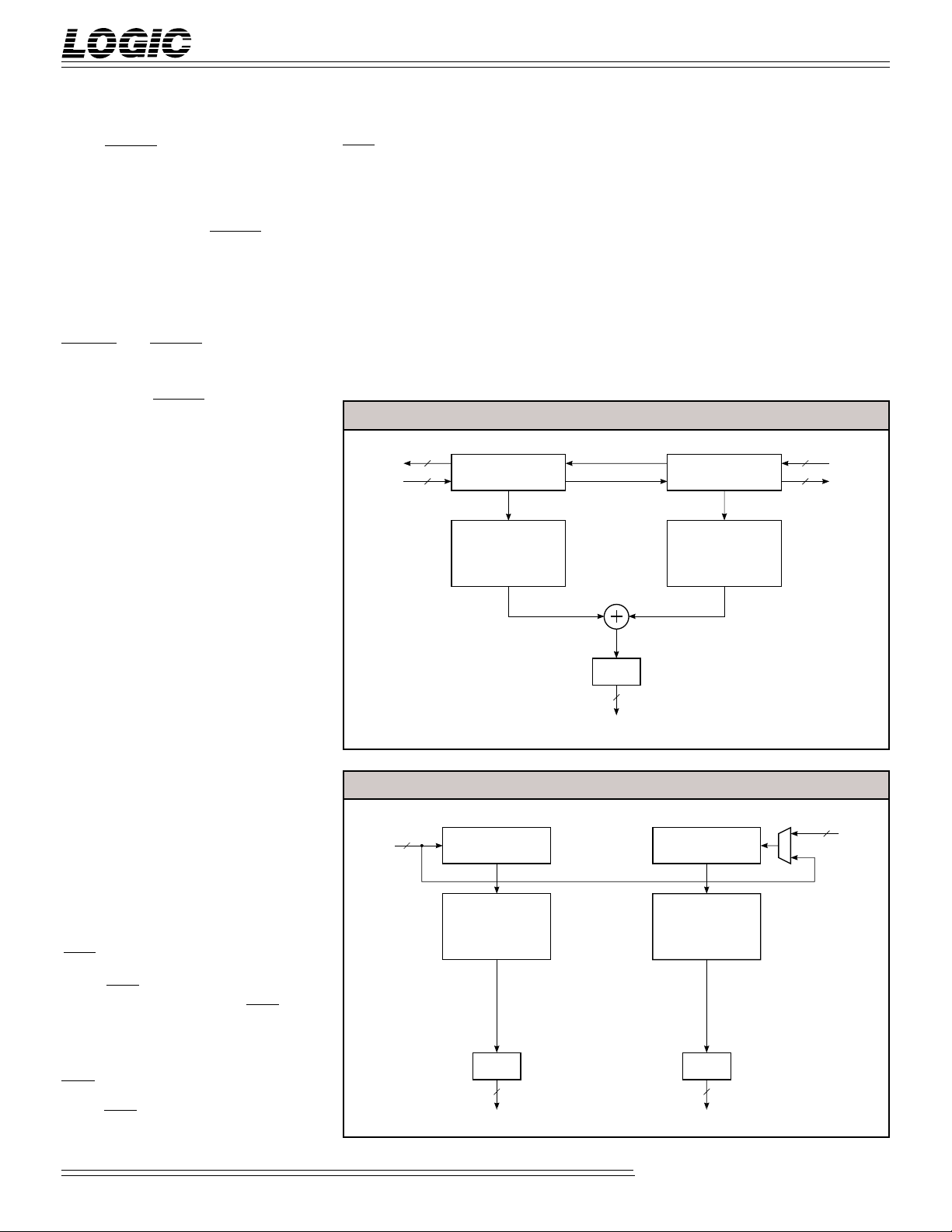

LF3320 BLOCK DIAGRAM

ROUT

CFA

PAUSEA

12 12

11-0

12

11-0

DIN

CENA

11-0

LDA

CLK

8

7-0

12

CAA

256

COEFFICIENT

SET

STORAGE

INTERLEAVE / DECIMATION

REGISTERS

16-TAP

FILTER A

ROUND

SELECT

CIRCUITRY

OED

DOUT

FILTER B

LIMIT

16

15-0

16-TAP

256

COEFFICIENT

SET

STORAGE

RIN

11-0

12

COUT

11-0

8

CAB

7-0

CENB

12

CFB

11-0

PAUSEB

LDB

2-1

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

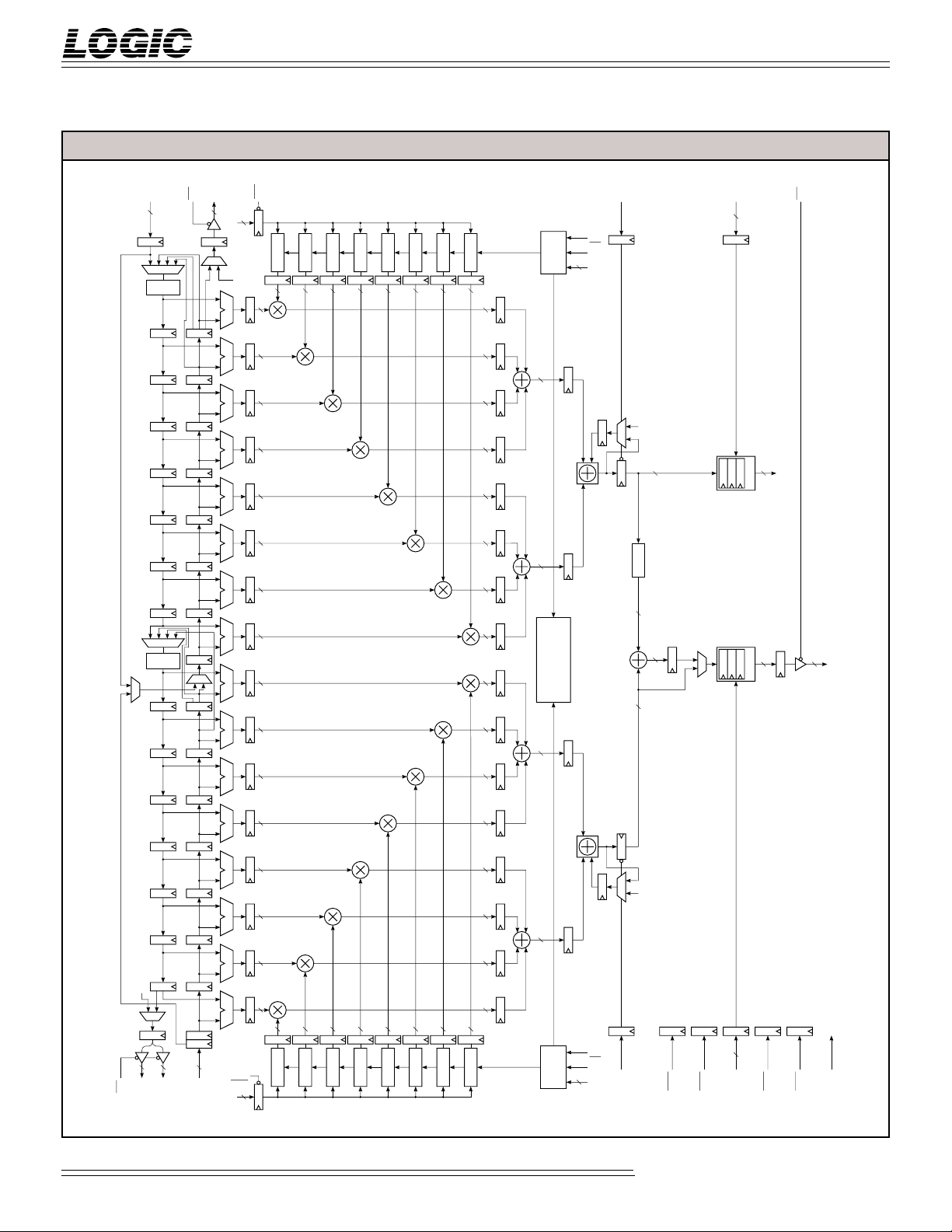

FIGURE 1. LF3320 FUNCTIONAL BLOCK DIAGRAM

LF3320

Horizontal Digital Image Filter

11-0

RIN

12

R

DATA

REVERSAL

1-16

1-16

1-16

1-16

1-16

1-16

1-16

DATA

REVERSAL

1-16

1-16

1-16

11-0

CENB

COUT

OEC

12

7-0

8

CAB

LF

Coef Bank 9

Coef Bank 11

Coef Bank 15

Coef Bank 14

Coef Bank 13

IEO

1-16

1-16

1-16

1-16

1-16

1-16

1-16

IEOS

1-16

1-16

1-16

1-16

11-0

RSLB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

ALU

AB

OUT

12

12

13

13

13

13

13

13 13

13

13

13

13

Coef Bank 12

12

12

Coef Bank 10

12

12

Coef Bank 8

12

12

25

25

25

25

25

25

25

25

25

25

25

FILTER B

INTERFACE

27

27

CONFIGURATION AND

CONTROL REGISTERS

27

ACCB

LDB

PAUSEB

CFB

11-0

12

"0"

32

ACCM B

SCALE

32

32

32

4

ROUND

ROUND

3-0

RSLB

SELECT

SELECT

LIMIT

LIMIT

FILTER B

FILTER A

16

16

15-0

RSLB OUT

OED

15-0

16

DOUT

1-16

FILTER A I/D REGISTERS FILTER B I/D REGISTERS

1-16

1-16

15-12

1-16

RSLB OUT

4

8

3-0

OEC

ROUT

11-4

ROUT

ALU

13

AB

1-16

ALU

13

AB

1-16

ALU

13

AB

1-16

ALU

13

AB

1-16

ALU

13

AB

1-16

12

11-0

DIN

12

CENA

Coef Bank 0

7-0

8

CAA

12

Coef Bank 1

12

Coef Bank 2

12

Coef Bank 3

12

Coef Bank 4

12

Coef Bank 5

12

Coef Bank 6

12

Coef Bank 7

25

25

25

27

25

25

FILTER A

LF

INTERFACE

ACCM A

"0"

LDA

PAUSEA

CFA

11-0

ACCA

12

TXFRA

TXFRB

4

3-0

RSLA

SHENA

SHENB

CLK

Video Imaging Products

2-2

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

SIGNAL DEFINITIONS

Power

VCC and GND

+3.3 V power supply. All pins must be

connected.

Clock

CLK — Master Clock

The rising edge of CLK strobes all

enabled registers.

Inputs

DIN

11-0 — Data Input

11-0 is the 12-bit data input port to

DIN

Filter A. In Dual Filter Mode, DIN11-0

can also be the 12-bit input port to

Filter B. Data is latched on the rising

edge of CLK.

RIN11-0 — Reverse Cascade Input

In Single Filter Mode, RIN11-0 is the 12bit reverse cascade input port. This

port is connected to ROUT11-0 of

another LF3320. In Dual Filter Mode,

RIN11-0 can be the 12-bit input port to

Filter B. Data is latched on the rising

edge of CLK.

CFA11-0 — Coefficient A Input

CFA11-0 is used to load data into the

Filter A coefficient banks (banks 0

through 7) and the configuration/

control registers. Data present on

CFA11-0 is latched into the Filter A LF

InterfaceTM on the rising edge of CLK

when LDA is LOW (see the LF

InterfaceTM section for a full discussion).

CAA7-0 — Coefficient Address A

CAA7-0 determines which row of data

in coefficient banks 0 through 7 is fed

to the multipliers. CAA7-0 is latched

into Coefficient Address Register A on

the rising edge of CLK when CENA is

LOW.

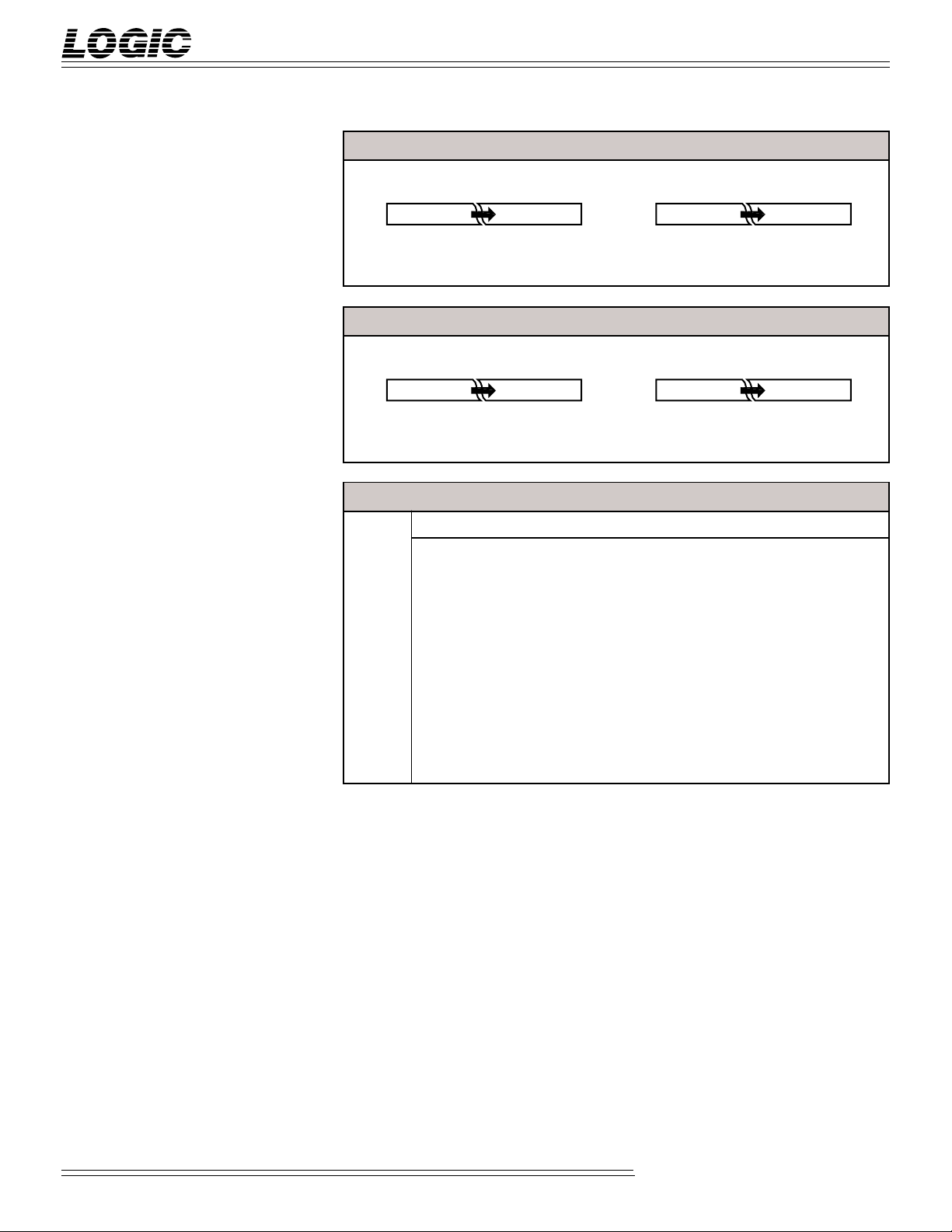

FIGURE 2. INPUT FORMATS

Input Data Coefficient Data

11 10 9 2 1 0

11

–2

(Sign)

2102

9

22212

0

11 10 9 2 1 0

–2

(Sign)

0

2–12

–2

2–92

–102–11

FIGURE 3. ACCUMULATOR OUTPUT FORMATS

Accumulator A Output Accumulator B Output

31 30 29 2 1 0

20

–2

(Sign)

2192

18

2–92

–102–11

31 30 29 2 1 0

–2

(Sign)

20

2192

18

2–92

–102–11

TABLE 1. OUTPUT FORMATS

SLCT4-0 S15 S14 S13 · · · S8 S7 · · · S2 S1 S0

00000 F15 F14 F13 · · · F8 F7 · · · F2 F1 F0

00001 F16 F15 F14 · · · F9 F8 · · · F3 F2 F1

00010 F17 F16 F15 · · · F10 F9 · · · F4 F3 F2

· ··· ·· ···

· ··· ·· ···

· ··· ·· ···

01110 F29 F28 F27 · · · F22 F21 · · · F16 F15 F14

01111 F30 F29 F28 · · · F23 F22 · · · F17 F16 F15

10000 F31 F30 F29 · · · F24 F23 · · · F18 F17 F16

CFB11-0 — Coefficient B Input

CFB11-0 is used to load data into the

Filter B coefficient banks (banks 8

through 15) and the configuration/

control registers. Data present on

CFB11-0 is latched into the Filter B LF

InterfaceTM on the rising edge of CLK

when LDB is LOW (see the LF

InterfaceTM section for a full discussion).

CAB7-0 — Coefficient Address B

CAB7-0 determines which row of data in

coefficient banks 8 through 15 is fed to the

multipliers. CAB7-0 is latched into

Coefficient Address Register B on the

rising edge of CLK when CENB is LOW.

Outputs

DOUT15-0 — Data Output

DOUT15-0 is the 16-bit registered data

output port for the overall filter (Single

Filter Mode) or Filter A (Dual Filter

Mode).

COUT11-0 — Cascade Output

In Single Filter Mode, COUT11-0 is a

12-bit registered cascade output port.

COUT11-0 should be connected to

DIN11-0 of another LF3320. In Dual

Filter Mode, COUT11-0 is a 12-bit

registered output port for the lower

twelve bits of the 16-bit Filter B output.

2-3

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

ROUT11-0 — Reverse Cascade Output

In Single Filter Mode, ROUT

11-0 is a

12-bit registered cascade output port.

ROUT11-0 on one device should be

connected to RIN11-0 of another LF3320.

In Dual Filter Mode, ROUT3-0 is a 4-bit

registered output port for the upper four

bits of the 16-bit Filter B output. In this

mode, ROUT11-4 is disabled.

Controls

LDA — Coefficient A Load

When LDA is LOW, data on CFA11-0 is

latched into the Filter A LF Interface

TM

on the rising edge of CLK. When LDA is

HIGH, data is not loaded into the Filter

A LF InterfaceTM. When enabling the LF

InterfaceTM for data input, a HIGH to

LOW transition of LDA is required in

order for the input circuitry to function

properly. Therefore, LDA must be set

HIGH immediately after power up to

ensure proper operation of the input

circuitry (see the LF Interface

TM

section

for a full discussion).

CENA — Coefficient Address Enable A

When CENA is LOW, data on CAA7-0

is latched into Coefficient Address

Register A on the rising edge of CLK.

When CENA is HIGH, data on CAA 7-0

is not latched and the register’s

contents will not be changed.

LDB — Coefficient B Load

When LDB is LOW, data on CFB11-0 is

latched into the Filter B LF Interface

TM

on the rising edge of CLK. When LDB is

HIGH, data is not loaded into the Filter

B LF InterfaceTM. When enabling the LF

InterfaceTM for data input, a HIGH to

LOW transition of LDB is required in

order for the input circuitry to function

properly. Therefore, LDB must be set

HIGH immediately after power up to

ensure proper operation of the input

circuitry (see the LF InterfaceTM section

for a full discussion).

CENB — Coefficient Address Enable B

When CENB is LOW, data on CAB7-0

is latched into Coefficient Address

Register B on the rising edge of CLK.

When CENB is HIGH, data on CAB7-0

is not latched and the register’s

contents will not be changed.

TXFRA — Filter A LIFO Transfer

Control

TXFRA is used to change which LIFO

in the data reversal circuitry sends

data to the reverse data path and

which LIFO receives data from the

forward data path in Filter A. When

TXFRA goes LOW, the LIFO sending

data to the reverse data path becomes

the LIFO receiving data from the

forward data path, and the LIFO

receiving data from the forward data

path becomes the LIFO sending data to

the reverse data path. The device must

see a HIGH to LOW transition of

TXFRA in order to switch LIFOs.

TXFRA is latched on the rising edge of

CLK.

TXFRB — Filter B LIFO Transfer

Control

TXFRB is used to change which LIFO

in the data reversal circuitry sends

data to the reverse data path and

which LIFO receives data from the

forward data path in Filter B. When

TXFRB goes LOW, the LIFO sending

data to the reverse data path becomes

the LIFO receiving data from the

forward data path, and the LIFO

receiving data from the forward data

path becomes the LIFO sending data to

the reverse data path. The device must

see a HIGH to LOW transition of

TXFRB in order to switch LIFOs.

TXFRB is latched on the rising edge of

CLK.

ACCA — Accumulator A Control

When ACCA is HIGH, Accumulator A

is enabled for accumulation and the

Accumulator A Output Register is

disabled for loading. When ACCA is

LOW, no accumulation is performed

and the Accumulator A Output Register

is enabled for loading. ACCA is latched

on the rising edge of CLK.

ACCB — Accumulator B Control

When ACCB is HIGH, Accumulator B

is enabled for accumulation and the

Accumulator B Output Register is

disabled for loading. When ACCB is

LOW, no accumulation is performed

and the Accumulator B Output Register is enabled for loading. ACCB is

latched on the rising edge of CLK.

SHENA — Filter A Shift Enable

In Dual Filter Mode, SHENA enables

or disables the loading of data into the

Input (DIN11-0) and Filter A I/D

Registers. When SHENA is LOW, data

is latched into the Input/Cascade

Registers and shifted through the I/D

Registers on the rising edge of CLK.

When SHENA is HIGH, data can not

be loaded into the Input/Cascade

Registers or shifted through the I/D

Registers and their contents will not be

changed.

In Single Filter Mode, SHENA also

enables or disables the loading of data

into the Reverse Cascade Input (RIN11-

0), Cascade Output (COUT11-0), Reverse

Cascade Output (ROUT11-0) and Filter B

I/D Registers. It is important to note

that in Single Filter Mode, both SHENA

and SHENB should be connected

together. Both must be active to enable

data loading in Single Filter Mode.

SHENA is latched on the rising edge of

CLK.

SHENB — Filter B Shift Enable

In Dual Filter Mode, SHENB enables or

disables the loading of data into the

Reverse Cascade Input (RIN11-0),

Cascade Output (COUT11-0), Reverse

Cascade Output (ROUT3-0) and Filter B

I/D Registers. When SHENB is LOW,

data is latched into the Cascade Registers and shifted through the I/D

2-4

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

Registers on the rising edge of CLK.

When SHENB is HIGH, data can not be

loaded into the Cascade Registers or

shifted through the I/D Registers and

their contents will not be changed.

In Single Filter Mode, SHENB also

enables or disables the loading of data

into the Input (DIN

11-0), Reverse

Cascade Output (ROUT11-0) and Filter

A I/D Registers. It is important to note

that in Single Filter Mode, both

SHENA and SHENB should be

connected together. Both must be

active to enable data loading in Single

Filter Mode. SHENB is latched on the

rising edge of CLK.

RSLA

3-0 — Filter A Round/Select/Limit

Control

RSLA3-0 determines which of the

sixteen user-programmable Round/

Select/Limit registers (RSL registers)

are used in the Filter A RSL circuitry.

A value of 0 on RSLA3-0 selects RSL

register 0. A value of 1 selects RSL

register 1 and so on. RSLA3-0 is

latched on the rising edge of CLK (see

the round, select, and limit sections for

a complete discussion).

RSLB3-0 — Filter B Round/Select/Limit

Control

ROUT3-0 are enabled for output. When

OEC is HIGH, COUT11-0 and ROUT3-0

are placed in a high-impedance state.

TM

PAUSEA — LF Interface

Pause

When PAUSEA is HIGH, the Filter A

LF InterfaceTM loading sequence is

halted until PAUSEA is returned to a

LOW state. This effectively allows the

user to load coefficients and control

registers at a slower rate than the

master clock (see the LF Interface

TM

section for a full discussion).

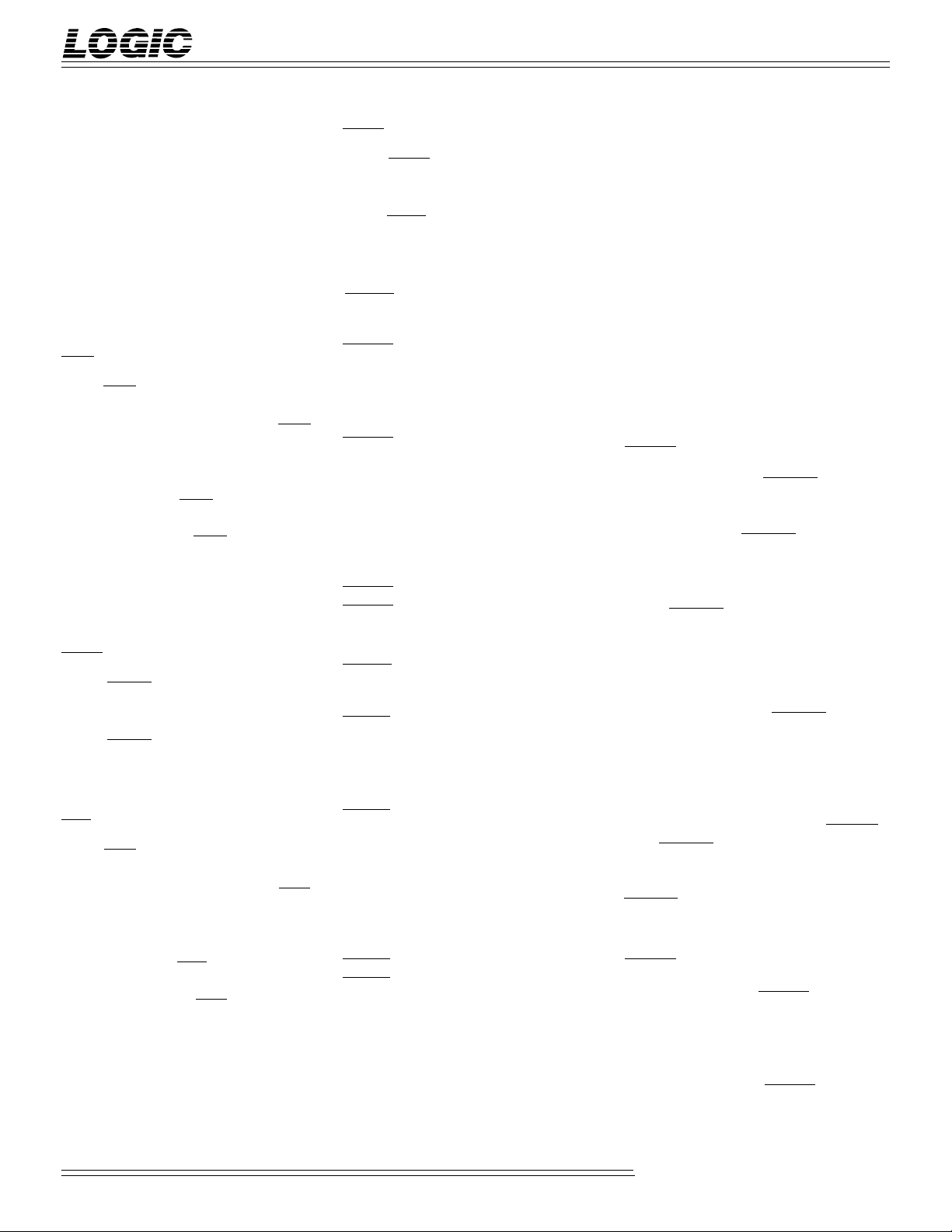

FIGURE 4. SINGLE FILTER MODE

ROUT

DIN

12

11-0

12 12

11-0

I/D

REGISTERS

FILTER

A

PAUSEB — LF Interface

TM

Pause

When PAUSEB is HIGH, the Filter B LF

TM

Interface

loading sequence is halted

until PAUSEB is returned to a LOW

state. This effectively allows the user

to load coefficients and control registers at a slower rate than the master

clock (see the LF InterfaceTM section for

a full discussion).

12

RSL

CIRCUIT

16

DOUT

15-0

I/D

REGISTERS

FILTER

B

RIN

COUT

11-0

11-0

RSLB3-0 determines which of the sixteen

user-programmable RSL registers are

used in the Filter B RSL circuitry. A

value of 0 on RSLB3-0 selects RSL

register 0. A value of 1 selects RSL

register 1 and so on. RSLB3-0 is latched

on the rising edge of CLK (see the round,

select, and limit sections for a complete

discussion).

OED — DOUT Output Enable

When OED is LOW, DOUT15-0 is

enabled for output. When OED is

HIGH, DOUT15-0 is placed in a highimpedance state.

OEC — COUT/ROUT Output Enable

When OEC is LOW, COUT11-0 and

FIGURE 5. DUAL FILTER MODE

DIN

11-0

12

I/D

REGISTERS

FILTER

A

R.S.L.

CIRCUIT

16

DOUT

2-5

15-0

12

RIN

11-0

REGISTERS

ROUT

I/D

FILTER

B

R.S.L.

CIRCUIT

16

3-0

/ COUT

11-0

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

OPERATIONAL MODES

Single Filter Mode

In this mode, the device operates as a

single FIR filter (see Figure 4). It can be

configured to have as many as 32 taps if

symmetric coefficient sets are used. If

asymmetric coefficient sets are used, the

device can be configured to have as

many as 16 taps. Cascade ports are

RIN11-0 or DIN11-0 can be the data

input for Filter B. The Filter B input is

determined by Bit 2 in Configuration

Register 5. DOUT15-0 is the data

output for Filter A. COUT11-0 and

ROUT3-0 together form the data output

for Filter B. COUT11-0 is the twelve

least significant bits and ROUT3-0 is

the four most significant bits of the

16-bit Filter B output.

provided to facilitate cascading multiple

devices to increase the number of filter

taps. Bit 1 in Configuration Register 5

determines the filter mode. In Single

Filter Mode, DIN11-0 is the data input

for the filter and DOUT15-0 is the data

output for the filter.

Dual Filter Mode

In this mode, the device operates as

two separate FIR filters (see Figure 5).

Each filter can be configured to have as

many as 16 taps if symmetric coefficient sets are used. If asymmetric

coefficient sets are used, each filter can

be configured to have as many as 8

taps. In Dual Filter Mode, DIN11-0 is

the data input for Filter A. Either

Matrix-vector Multiply Mode

In this mode, the LF3320 can be

configured to multiply a square matrix

of maximum size N (N = 8 or 16),

multiplied by a matrix-vector of

maximum size [8,1] or [16,1]. The

mathematical representation for this

operation is in Figure 7. When configured in the dual filter mode, the LF3320

can process two matrix-vector multipliers simultaneously (i.e. [8x8][8x1]). In

the single filter mode, the LF3320 can

process a single matrix-vector multiply

(i.e. [16x16][16x1]). This mode of

operation allows the user to organize

data values (e.g. pixels) into an array

(e.g. blocks). This function is useful for

any application requiring the opera-

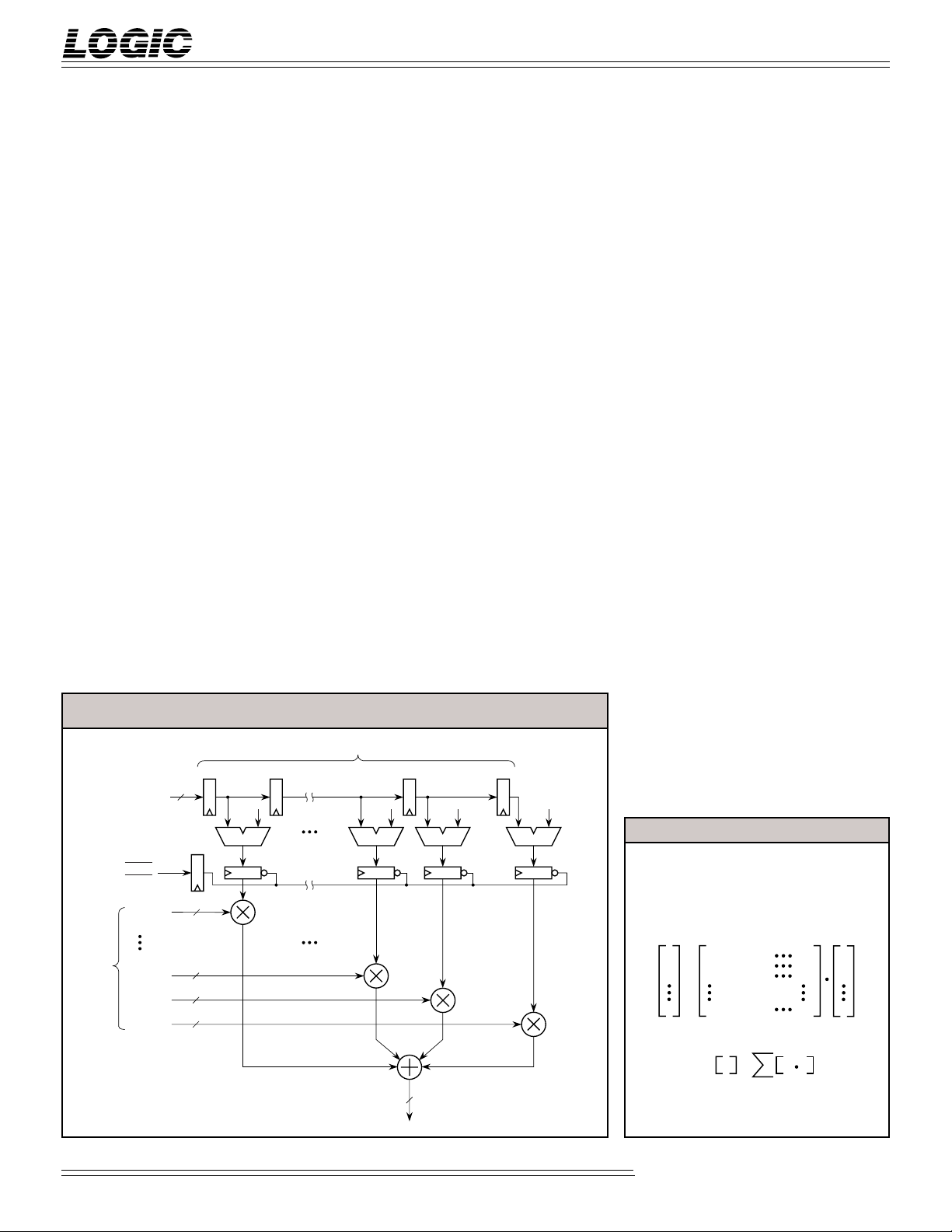

FIGURE 6. MATRIX-VECTOR MULTIPLY MODE

N

12

DIN11-0

RIN11-0

0

tion of matrix multiplication; a function that is used when generating

Discrete Cosine Transform coefficients

(DCT) for the purpose of further

processing.

When configuring the LF3320 for an

[8x8][8x1] matrix-vector operation, the

coefficient banks will require 8 coefficient sets to be loaded into the coefficient

memory banks; each coefficient set will

have 8, 12-bit coefficients. The input

data, [8x1] column-vector, will be loaded

through DIN11-0 for Filter A; either

RIN11-0 or DIN11-0 can be the data

input for Filter B. Conversely, when

configured for a [16x16][16x1]

matrix-vector operation, the coefficient

banks will require 16 coefficient sets to

be loaded into the coefficient memory

banks; each coefficient set will have 16,

12-bit coefficients. The input data,

[16x1] column-vector, will be loaded

through DIN11-0.

To configure the LF3320 for

matrix-vector multiplication, bit 4 of

Configuration Register 5 must be set to

1 (Table 7). The configuration for

single filter mode or dual filter mode

will still apply. Writing 012H or 016H

to Configuration Register 5 will

configure the device for dual filter

mode, [8x8][8x1] matrix-vector multiplication. Subsequently, writing 014H

to Configuration Register 5 will

00

0

configure the device for single filter

N

TXFRA

TXFRB

COEF (N-1)

COEF 2

COEF 1

COEF 0

AB

ALU

12

12

12

12

Dual Filter Mode, N=8

Single FIlter Mode, N=16

AB

ALU

32

AB

ALU

2-6

AB

ALU

FIGURE 7. MATRIX EQUATION

C = COEFFICIENTS

D = DATA INPUT

R = DATA OUTPUT

C

00

0

R

R

1

R

2

R

i

C

01

C

10

C

11

C

20

C

=

21

C

i0

C

i1

R

i

For j=0,1,2,...,(N-1)

=

N=8 or 16

C

C

C

C

(N-1)

i=0

C

0j

02

12

22

i2

C

ij

D

C

C

C

0

1j

D

1

2j

D

2

ij

D

i

D

i

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

LF3320

Horizontal Digital Image Filter

mode, [16x16][16x1] matrix-vector

multiplication.

Some functions of the LF3320 must be

disabled when configured for

matrix-vector multiplication. This will

apply to both the single filter mode and

the dual filter mode; these functions

are data reversal and

interleave/decimation. The LF3320

can be cascaded to realize larger

matrices.

Data reversal can be disabled by

setting bit 6, of Configuration Register 1 (Filter A) and Configuration

Register 3 (Filter B), both to 1. The

Odd-Tap, interleave mode will need to

be disabled. Writing a 0 to bit 0 of

Configuration Register 1 and Configuration Register 3 will disable the

odd-tap interleave mode for Filter A

and Filter B. When data is not being

interleaved or decimated, the I/D

Register length should be set to a

length of one (Table 3 and Table 5).

Therefore, writing 040H to Configuration Register 1 and 3 will disable the

data reversal and set the corresponding inherent characteristics for the

desired matrix function.

The Filter A ALU and Filter B ALU are

to be configured for A+B (Table 2 and

Table 4); so that condition A+0 is

satisfied. To accomplish this, bit 0 is to

be reset to 0, bit 1 is to be set to 1, and

bit 2 is to be reset to 0. Writing 002H to

Configuration Register 0 (Filter A) and

Configuration Register 2 (Filter B) will

set the corresponding registers to

satisfy the A+0 condition.

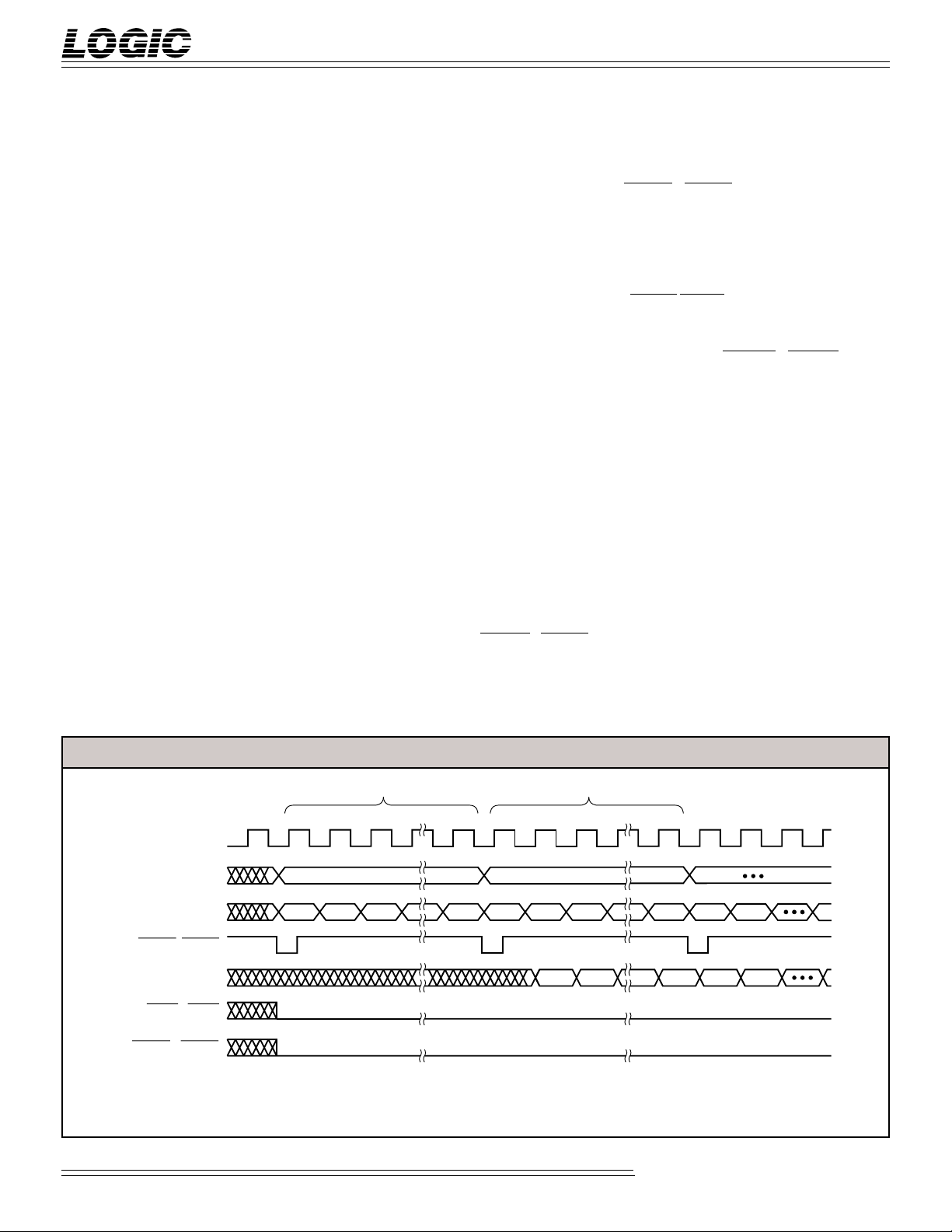

The timing diagrams in Figure 8 and 9

will assume that the Configuration

Registers, the coefficient sets, and the

first set of data values (data set) have

been loaded. Loading input data for an

[8x8][8x1] matrix operation requires 9

clock cycles and loading input data for a

[16x16][16x1] matrix operation requires

17 clock cycles. When configured for an

[8x8][8x1] matrix-vector operation, 8

data values are required for loading.

When configured for a [16x16][16x1]

matrix-vector operation, 16 data values

are required for loading. Each data

value is fed through the I/D Registers,

using the corresponding input.

Once the final data value, of the data

set, has been loaded TXFRA/TXFRB

should be brought LOW for one clock

cycle to complete the loading. Once

this occurs, the data set is then bank

loaded into the respective registers

ready to begin the matrix-vector

multiplication operation. The current

data set will not change until

TXFRA/TXFRB is brought LOW

again. To satisfy the matrix equation (see Figure 7), the current data set

is held for the duration of the required

matrix dimension while cycling

through each coefficient set

(CENA/CENB must be held LOW).

During this time new data values can be

loaded serially, ready for the next

activation of TXFRA/TXFRB. To

insure the correct evaluation of the

matrix-vector multiplication

equation, it is imperative that the

coefficient values are paired with

their corresponding data values.

For the [8x8][8x1] matrix-vector

configuration (dual filter mode), the

first result will appear 19 clock cycles

from the first data input, DIN15-0

(Filter A) and RIN15-0 (Filter B); device

latency for the first result is 10 clock

cycles (10+9 = 19).

The result will appear at the corresponding filter output, DOUT15-0

(Filter A) and ROUT3-0/COUT11-0

(Filter B). For the [16x16][16x1]

matrix-vector configuration (single

filter mode), the first result will appear

FIGURE 8. DUAL FILTER, MATRIX MULTIPLY TIMING SEQUENCE

CLK

DIN

11-0

RIN11-0

CAA7-0

CAB7-0

TXFRA/ TXFRB

ROUT3-0/COUT15-0

DOUT15-0

CENA / CENB

SHENA / SHENB

Data Set 1 with 8 Coefficient Sets

2

1

DATA SET 0

CF00

CF01 CF02

* 8 Clocks - End of First Data/Coefficient Set

** 10 Clocks - First Output of First Data/Coefficient Set

*** 17 Clocks - Final Output of First Data/Coefficient Set

3

CF07

Data Set 2 with 8 Coefficient Sets

9

8*

CF

10 CF11 CF12

2-7

10**

DATA SET 1

OUT

0

11

18

17***

CF20

OUT

CF17

1

OUT

7

OUT

CF21

0

OUT

1

Video Imaging Products

08/16/2000–LDS.3320-N

DEVICES INCORPORATED

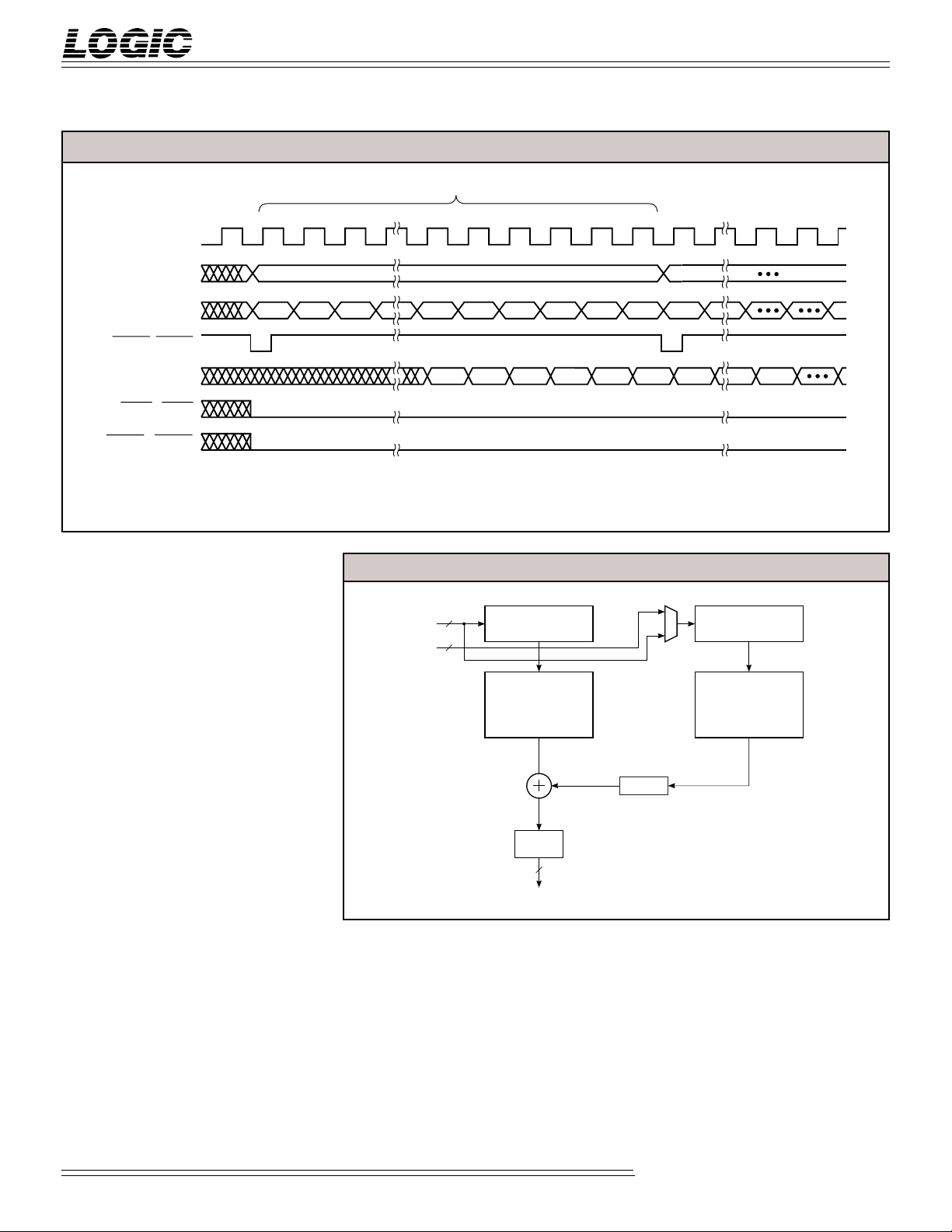

FIGURE 9. SINGLE FILTER, MATRIX MULTIPLY TIMING SEQUENCE

1 Data Set with 16 Coefficient Sets

LF3320

Horizontal Digital Image Filter

2

1

CLK

DIN

11-0

RIN

11-0

CAA

7-0

CAB

7-0

TXFRA/ TXFRB

DOUT

15-0

CENA / CENB

SHENA / SHENB

* 11 Clocks - First Output of First Data/Coefficient Set

** 16 Clocks - End of First Data/Coefficient Set

*** 26 Clocks - Final Output of First Data/Coefficient Set

CF

DATA SET 0

00

CF01CF

28 clock cycles from the first data

input, DIN15-0; device latency for the

first result is 11 clock cycles

(11+17 = 28). The result will appear at

the corresponding filter output,

DOUT15-0. Subsequently, for both dual

and single filter mode configurations,

the sum of products will continue to

appear every clock cycle thereafter

until the matrix dimension has been

realized. The total pipeline latency for

a complete [8x8][8x1] matrix-vector

operation is 26 clock cycles and the

total pipeline latency for a complete

[16x16][16x1] matrix-vector operation

is 43 clock cycles. Therefore, to process

two square matrices simultaneoulsy, of

size N=8, a total of 73 clock cycles are

all that is required. Similarly, to

process a single square matrix, of size

N=16, a total of 283 clock cycles are

required.

Once again, the timing diagrams (see

Figure 8 and 9) will assume that the

Configuration Registers, the coefficient

sets, and the data values have been

loaded. The corresponding timing

diagram loading sequence for the

coefficient banks and

Configuration/Control registers are

included in the LF3320 data sheets

12

3

02

11*

CF0BCF0CCF

CF

0A

OUT

0

OUT

1

13

DATA SET 0

OUT

2

15 17

14

0D

CF

OUT

3

0E

OUT

16**

CF

0F

OUT

10

5

OUT

6

CF

4

FIGURE 10. DOUBLE WIDE DATA/COEFFICIENT MODE

12

DIN

11-0

12

RIN

11-0

(Figure 11 and Figure 12 respectively).

Further reference to timing diagram

loading sequence for the RSL registers

are also included in the device data

sheet (Figure 15, Figure 14, and Figure

13). The Filter A and Filter B

LF InterfaceTM are used to load data

into the Filter A and Filter B Configuration Registers and coefficient banks.

The Matrix Multiplication Mode is

valid in the Double Wide

I/D

REGISTERS

FILTER

A

R.S.L.

CIRCUIT

16

DOUT

15-0

SCALE

Data/Coefficient Mode. However,

there are some special considerations

when this mode is desired. The

LF3320 must be configured for single

filter mode only, for a maximum (8x8)

matrix. The user must disable the

cascaded filter mode, the accumulator

access mode, and the data reversal

(see Table 7).

Double Wide Data/Coefficient Mode

26***

I/D

REGISTERS

FILTER

B

OUT

15

2-8

Video Imaging Products

08/16/2000–LDS.3320-N

Loading...

Loading...