LOGIC LF2272QC25, LF2272QC20 Datasheet

DEVICES INCORPORATED

DEVICES INCORPORATED

LF2272

Colorspace Converter/

LF2272

Corrector (3 x 12-bits)

Colorspace Converter/

Corrector (3 x 12-bits)

FEATURES

❑❑

❑ 50 MHz Data and Computation

❑❑

Rate

❑❑

❑ Full Precision Internal Calculations

❑❑

with Output Rounding

❑❑

❑ On-board 10-bit Coefficient Storage

❑❑

❑❑

❑ Overflow Capability in Low

❑❑

Resolution Applications

❑❑

❑ Two’s Complement Input and

❑❑

Output Data Format

❑❑

❑ 3 Simultaneous 12-bit Channels

❑❑

(64 Giga Colors)

❑❑

❑ Applications:

❑❑

• Component Color Standards

Translations (RGB, YIQ, YUV)

• Color-Temperature Conversion

• Image Capturing and Manipulation

• Composite Color Encoding/

Decoding

• Three-Dimensional Perspective

Translation

❑❑

❑ Replaces TRW/Raytheon/Fairchild

❑❑

TMC2272

❑❑

❑ 120-pin PQFP

❑❑

DESCRIPTION

The LF2272 is a high-speed digital

colorspace converter/corrector

consisting of three simultaneous 12-bit

input and output channels for functionality up to 64 Giga (236) colors.

Some of the applications the LF2272

can be used for include phosphor

colorimetry correction, image capturing and manipulation, composite color

encoding/decoding, color matching,

and composite color standards

conversion/transcoding.

The 3 x 3 matrix multiplier (triple dot

product) allows users to easily perform three-dimensional perspective

translations or video format conversions at real-time video rates. By

using the LF2272, conversions can be

made from the RGB (color component) format to the YIQ (quadrature

encoded chrominance) or YUV (color

difference) formats and vice versa

(YIQ or YUV to RGB). Differing signal

formats in each stage of a system can

be disregarded. For example, using

an LF2272 at each format interface

allows each stage of a system to

operate on the data while in the

appropriate format.

All inputs and outputs, as well as all

control lines, are registered on the

rising edge of clock. The LF2272

operates at clock rates up to 50 MHz

over the full commercial temperature

and supply voltage ranges. A narrower data path can be used to allow

the LF2272 to work with many

different imaging applications.

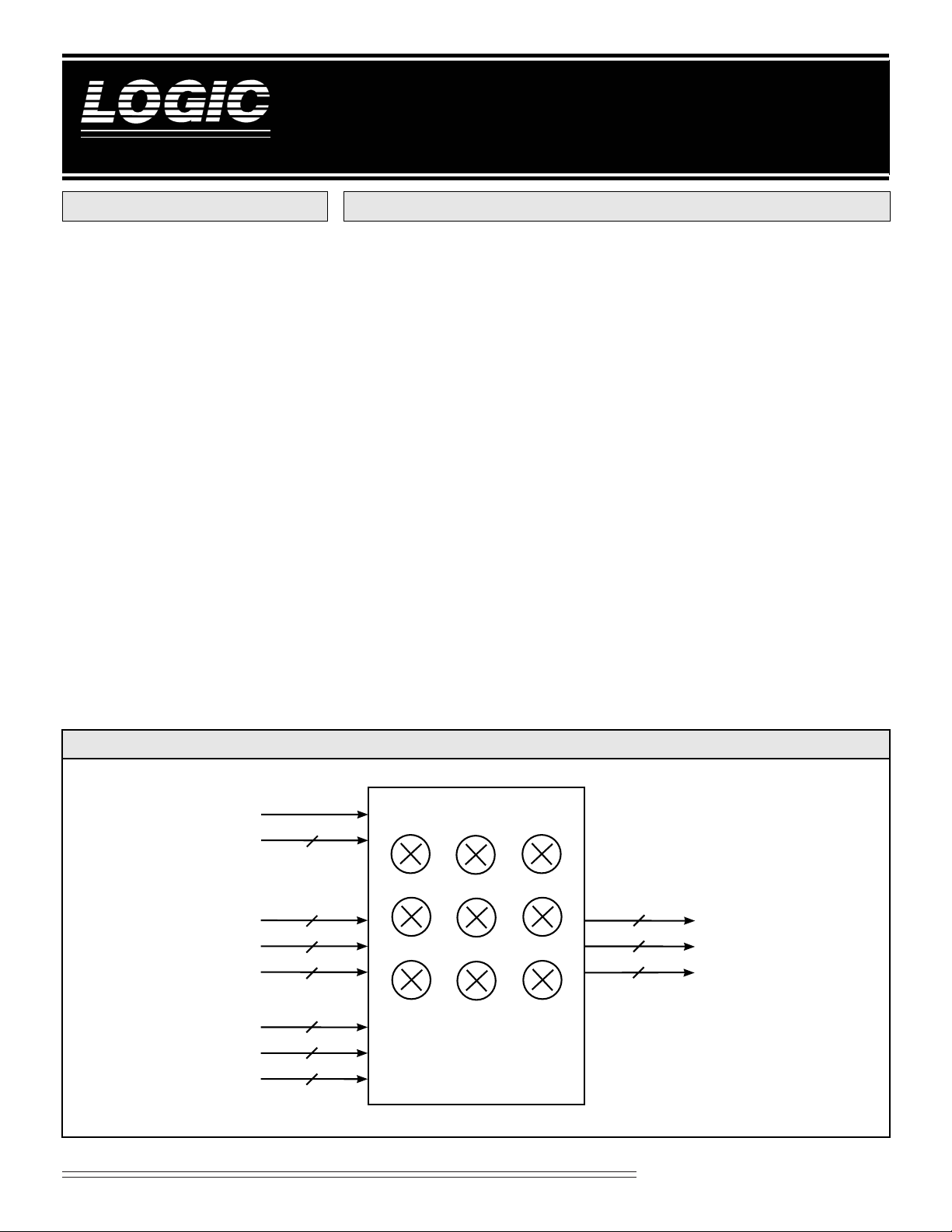

DETAILS OF OPERATION

All three input ports (A, B, C) and all

three output ports (X, Y, Z) are

utilized to implement a 3 x 3 matrix

multiplication (triple dot product).

Each truncated 12-bit output is the

sum of all three input words multiplied by the appropriate coefficients

(Table 1). The pipeline latency is five

clock cycles. Therefore, the sum of

LF2272 BLOCK DIAGRAM

CLK

1-0

CWEL

A

11-0

DATA

INPUTS

COEFFICIENT

INPUTS

{

{

B

C

KA

KB

KC

11-0

11-0

9-0

9-0

9-0

10

10

10

12

12

12

2

12

12

12

X

Y

Z

11-0

11-0

11-0

{

DATA

OUTPUTS

9-MULTIPLIER

ARRAY

Video Imaging Products

1

08/16/2000–LDS.2272-I

DEVICES INCORPORATED

LF2272

Colorspace Converter/

Corrector (3 x 12-bits)

products will be output five clock

cycles after the input data has been

registered. New output data is

subsequently available every clock

cycle thereafter.

DATA FORMATTING

The data input ports (A, B, C) and

data output ports (X, Y, Z) are 12-bit

integer two’s complement format.

The coefficient input ports (KA, KB,

KC) are 10-bit fractional two’s

complement format. Refer to

Figures 1a and 1b.

BIT WEIGHTING

The internal sum of products of the

LF2272 can grow to 23 bits. However,

in order to keep the output format

identical to the input format, the X, Y,

and Z outputs are rounded to 12-bit

integer words. The rounding is done

only at the final output stage to allow

accuracy, with correct rounding and

overflow, for applications requiring

less than 12-bit integer words. The

user may adjust the bit weighting by

applying an identical scaling correction factor to both the input and

output data streams.

TABLE 1. LATENCY EQUATIONS

X(n+4) = A(n)KA1(n) + B(n)KB1(n) + C(n)KC1(n)

Y(n+4) = A(n)KA2(n) + B(n)KB2(n) + C(n)KC2(n)

Z(n+4) = A(n)KA3(n) + B(n)KB3(n) + C(n)KC3(n)

DATA OVERFLOW

Because the LF2272’s matched input

and output data formats accommodate unity gain (0 dB), input conditions that could lead to numeric

overflow may exist. To ensure that no

overflow conditions occur, the user

must be aware of the maximum input

data and coefficient word sizes

allowable for each specific algorithm

being performed.

FIGURE 1A.INPUT FORMATS

Data Input

11 10 9 6 5 487 3210

1121029

–2

(Sign)

7

282

Coefficient Input

SYSTEMS SMALLER THAN 12-BITS

Using a data path less than 12-bits

requires the input data to be right

justified and sign extended to 12-bits

because the LF2272 carries out all

calculations to full precision. Since all

least-significant bits are used, the

desired X, Y, and Z outputs are

rounded correctly and upper-order

output bits are used for overflow.

26252

4

2322212

0

987 43265 10

02–12–2

–2

(Sign)

20 19 18 3 2 117 0

1121029

–2

(Sign)

FIGURE 1B.OUTPUT FORMAT

11 10 9 6 5 487 3210

1121029

–2

(Sign)

2

282

–4

2–32

2–52–62

Internal Sum

8

2

2–62–72

Result

7

26252

Video Imaging Products

–7

2–82

–8

2

4

2322212

–9

–9

0

08/16/2000–LDS.2272-I

DEVICES INCORPORATED

LF2272

Colorspace Converter/

Corrector (3 x 12-bits)

SIGNAL DEFINITIONS

Power

VCC and GND

+5 V power supply. All pins must be

connected.

Clock

CLK — Master Clock

The rising edge of CLK strobes all

enabled registers. All timing specifications are referenced to the rising

edge of CLK.

Inputs

A11-0, B11-0, C11-0 — Data Inputs

A, B, and C are the 12-bit registered

data input ports. Data presented to

these ports is latched into the multiplier input registers.

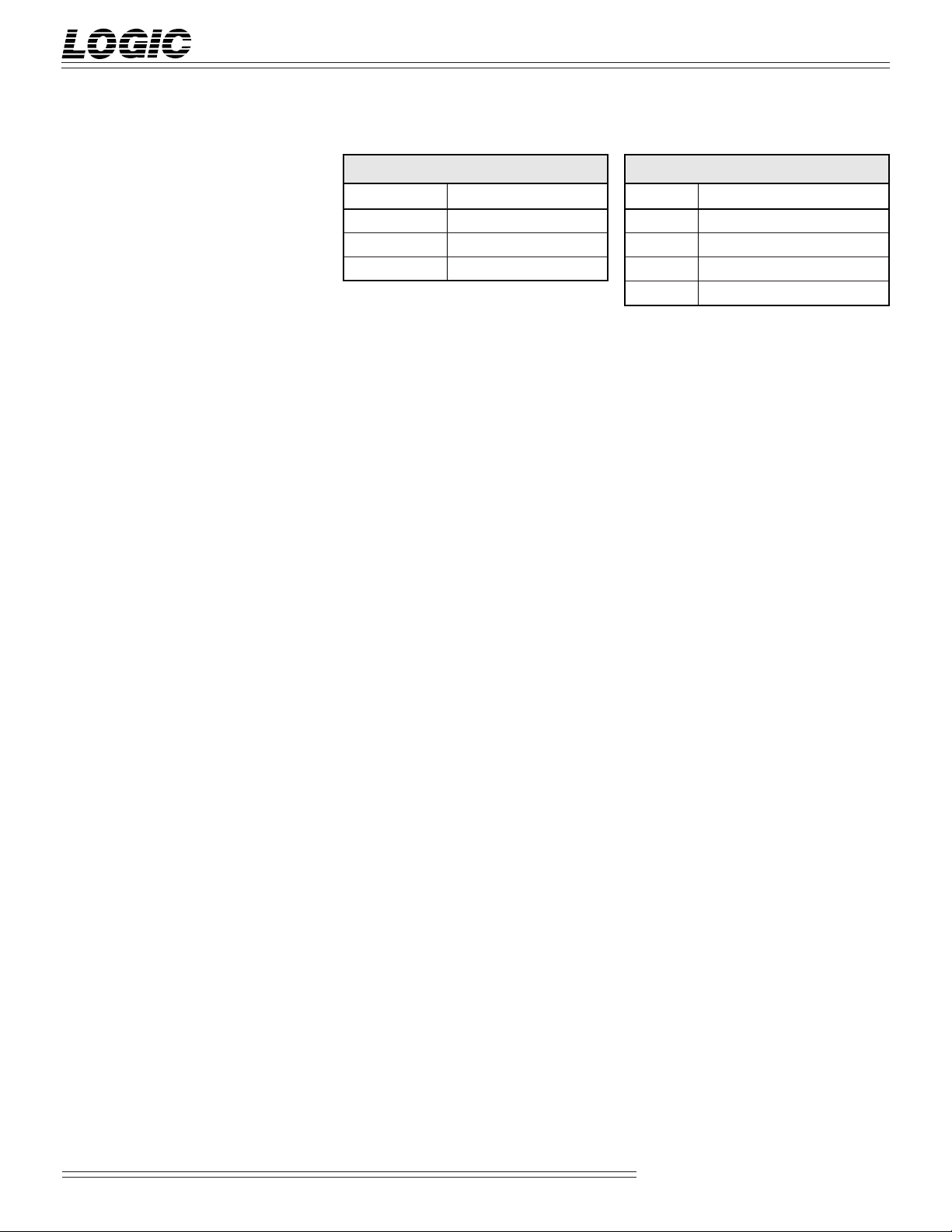

TABLE 2. COEFFICIENT INPUTS

INPUT PORT REG. AVAILABLE

KA KA1, KA2, KA3

KB KB1, KB2, KB3

KC KC1, KC2, KC3

Outputs

X11-0, Y11-0, Z11-0 — Data Outputs

X, Y, and Z are the 12-bit registered

data output ports.

Controls

CWEL1-0 — Coefficient Write Enable

The registered coefficient write enable

inputs determine which internal

coefficient register set to update

(Table 3) on the next clock cycle.

TABLE 3. COEFF. REG. UPDATE

CWEL1-0 COEFFICIENT SET

00 Hold All Registers

01 KA1, KB1, KC1

10 KA2, KB2, KC2

11 KA3, KB3, KC3

KA9-0, KB9-0, KC9-0 — Coefficient Inputs

KA, KB, and KC are the 10-bit registered coefficient input ports. Data

presented to these ports is latched into

the corresponding internal coefficient

register set defined by CWEL1-0

(Table 3) on the next rising edge of

CLK. Table 2 shows which coefficient

registers are available for each coefficient input port.

Video Imaging Products

3

08/16/2000–LDS.2272-I

Loading...

Loading...