DEVICES INCORPORATED

L4C381

16-bit Cascadable ALU

L4C381

DEVICES INCORPORATED

FEATURES DESCRIPTION

❑❑

❑ High-Speed (15ns), Low Power

❑❑

16-bit Cascadable ALU

❑❑

❑ Implements Add, Subtract, Accumu-

❑❑

late, Two’s Complement, Pass, and

Logic Operations

❑❑

❑ All Registers Have a Bypass Path

❑❑

for Complete Flexibility

❑❑

❑ 68-pin PLCC, J-Lead

❑❑

The L4C381 is a flexible, high speed,

cascadable 16-bit Arithmetic and

Logic Unit. It combines four 381-type

4-bit ALUs, a look-ahead carry

generator, and miscellaneous interface

logic — all in a single 68-pin package.

While containing new features to

support high speed pipelined architectures and single 16-bit bus configurations, the L4C381 retains full performance and functional compatibility with

the bipolar ’381 designs.

The L4C381 can be cascaded to

perform 32-bit or greater operations.

See “Cascading the L4C381” toward

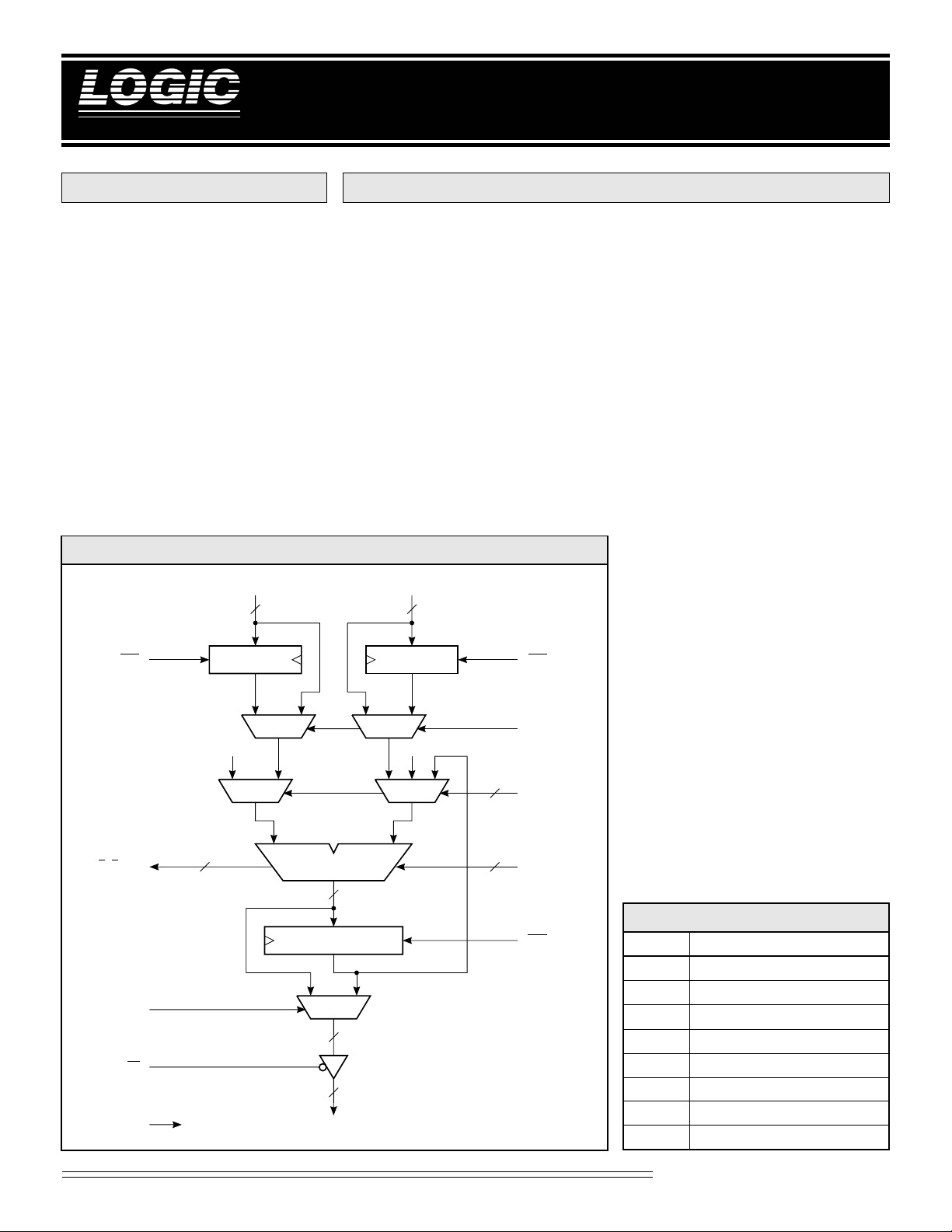

L4C381 BLOCK DIAGRAM

B15-B

0

B REGISTER

ENA

A15-A

0

16 16

A REGISTER

16-bit Cascadable ALU

the end of this data sheet for more

information.

ARCHITECTURE

The L4C381 operates on two 16-bit

operands (A and B) and produces a

16-bit result (F). Three select lines

control the ALU and provide 3

arithmetic, 3 logical, and 2 initialization functions. Full ALU status is

provided to support cascading to

longer word lengths. Registers are

provided on both the ALU inputs and

the output, but these may be bypassed

under user control. An internal

feedback path allows the registered

ALU output to be routed to one of the

ALU inputs, accommodating chain

operations and accumulation. Furthermore, the A or B input can be

forced to Zero allowing unary func-

ENB

tions on either operand.

P, G, C

OVF, Z

FTF

OE

CLK

ALU OPERATIONS

FTAB

00

2

OSA

OSB

The S2–S0 lines specify the operation

to be performed. The ALU functions

and their select codes are shown in

Table 1.

The two functions, B minus A and

A minus B, can be achieved by setting

16

ALU

16

45

S

2-S0

, C

0

the carry input of the least significant

slice and selecting codes 001 and 010

respectively.

TABLE 1. ALU FUNCTIONS

ENF

S2-S0 FUNCTION

000 CLEAR (F = 00 • • • 00)

001 NOT(A) + B

010 A + NOT(B)

011 A + B

100 A XOR B

101 A OR B

110 A AND B

111 PRESET (F = 11 • • • 11)

TO ALL REGISTERS

RESULT REGISTER

16

16

F15-F

0

Arithmetic Logic Units

1

08/16/2000–LDS.381-P

DEVICES INCORPORATED

L4C381

16-bit Cascadable ALU

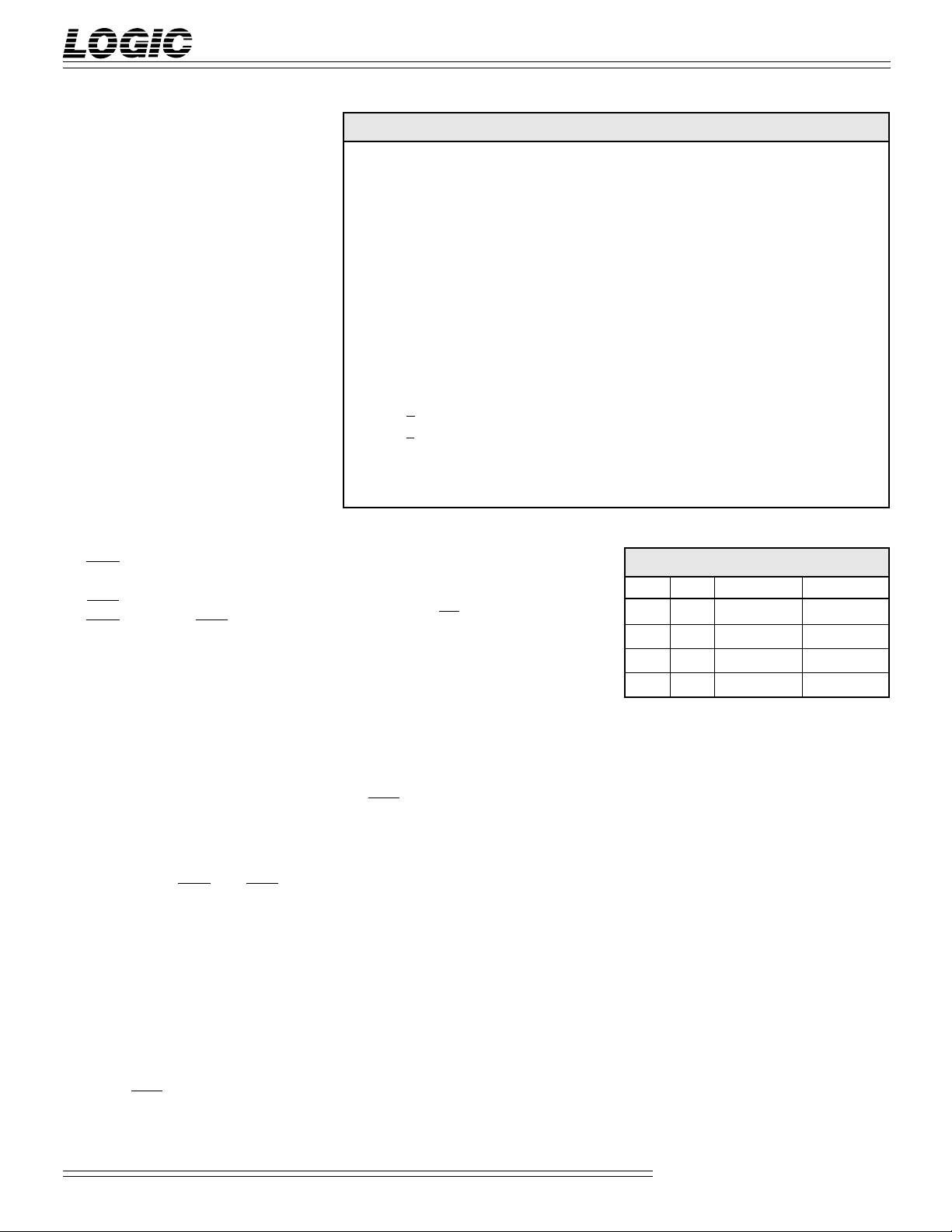

ALU STATUS

The ALU provides Overflow and Zero

status bits. Carry, Propagate, and

Generate outputs are also provided

for cascading. These outputs are

defined for the three arithmetic

functions only. The ALU sets the Zero

output when all 16 output bits are

zero. The Generate, Propagate, C16,

and OVF flags for the A + B operation

are defined in Table 2. The status

flags produced for NOT(A) + B and

A + NOT(B) can be found by complementing Ai and Bi respectively in

Table 2.

OPERAND REGISTERS

The L4C381 has two 16-bit wide input registers for operands A and B.

These registers are rising edge triggered by a common clock. The A

register is enabled for input by setting

the ENA control LOW, and the B

register is enabled for input by setting

the ENB control LOW. When either

the ENA control or ENB control is

HIGH, the data in the corresponding

input register will not change.

This architecture allows the L4C381 to

accept arguments from a single 16-bit

data bus. For those applications that

do not require registered inputs, both

the A and B operand registers can be

bypassed with the FTAB control line.

When the FTAB control is asserted

(FTAB = HIGH), data is routed

around the A and B input registers;

however, they continue to function

normally via the ENA and ENB

controls. The contents of the input

registers will again be available to the

ALU if the FTAB control is released.

OUTPUT REGISTER

The output of the ALU drives the

input of a 16-bit register. This risingedge-triggered register is clocked by

the same clock as the input registers.

When the ENF control is LOW, data

from the ALU will be clocked into the

TABLE 2. ALU STATUS FLAGS

Bit Carry Generate = gi =AiBi for i = 0 ... 15

Bit Carry Propagate = pi =Ai + B i for i = 0 ... 15

P 0 =p0

Pi =pi (P i–1 ) for i = 1 ... 15

and

G 0 =g0

Gi=gi + p i (Gi–1 ) for i = 1 ... 15

C i =Gi–1 + Pi–1 (C 0 ) for i = 1 ... 15

then

G = NOT(G15)

P = NOT(P15)

C 16 =G15 + P 15C 0

OVF = C15 XOR C16

output register. By disabling the

output register, intermediate results

can be held while loading new input

operands. Three-state drivers controlled by the OE input allow the

L4C381 to be configured in a single

bidirectional bus system.

The output register can be bypassed

by asserting the FTF control signal

(FTF = HIGH). When the FTF control

is asserted, output data is routed

around the output register, however,

it continues to function normally via

the ENF control. The contents of the

output register will again be available

on the output pins if FTF is released.

With both FTAB and FTF true (HIGH)

the L4C381 is functionally identical to

four cascaded 54S381-type devices.

OPERAND SELECTION

The two operand select lines, OSA and

OSB, control multiplexers that precede

the ALU inputs. These multiplexers

provide an operand force-to-zero

function as well as F register feedback

to the B input. Table 3 shows the

inputs to the ALU as a function of the

operand select inputs. Either the A or

B operands may be forced to zero.

TABLE 3. OPERAND SELECTION

OSB OSA OPERAND B OPERAND A

00 F A

01 0 A

10 B 0

11 B A

When both operand select lines are

low, the L4C381 is configured as a

chain calculation ALU. The registered

ALU output is passed back to the B

input to the ALU. This allows accumulation operations to be performed

by providing new operands via the A

input port. The accumulator can be

preloaded from the A input by setting

OSA true. By forcing the function

select lines to the CLEAR state (000),

the accumulator may be cleared. Note

that this feedback operation is not

affected by the state of the FTF

control. That is, the F outputs of the

L4C381 may be driven directly by the

ALU. The output register continues to

function, however, and provides the

ALU B operand source.

Arithmetic Logic Units

2

08/16/2000–LDS.381-P

DEVICES INCORPORATED

L4C381

16-bit Cascadable ALU

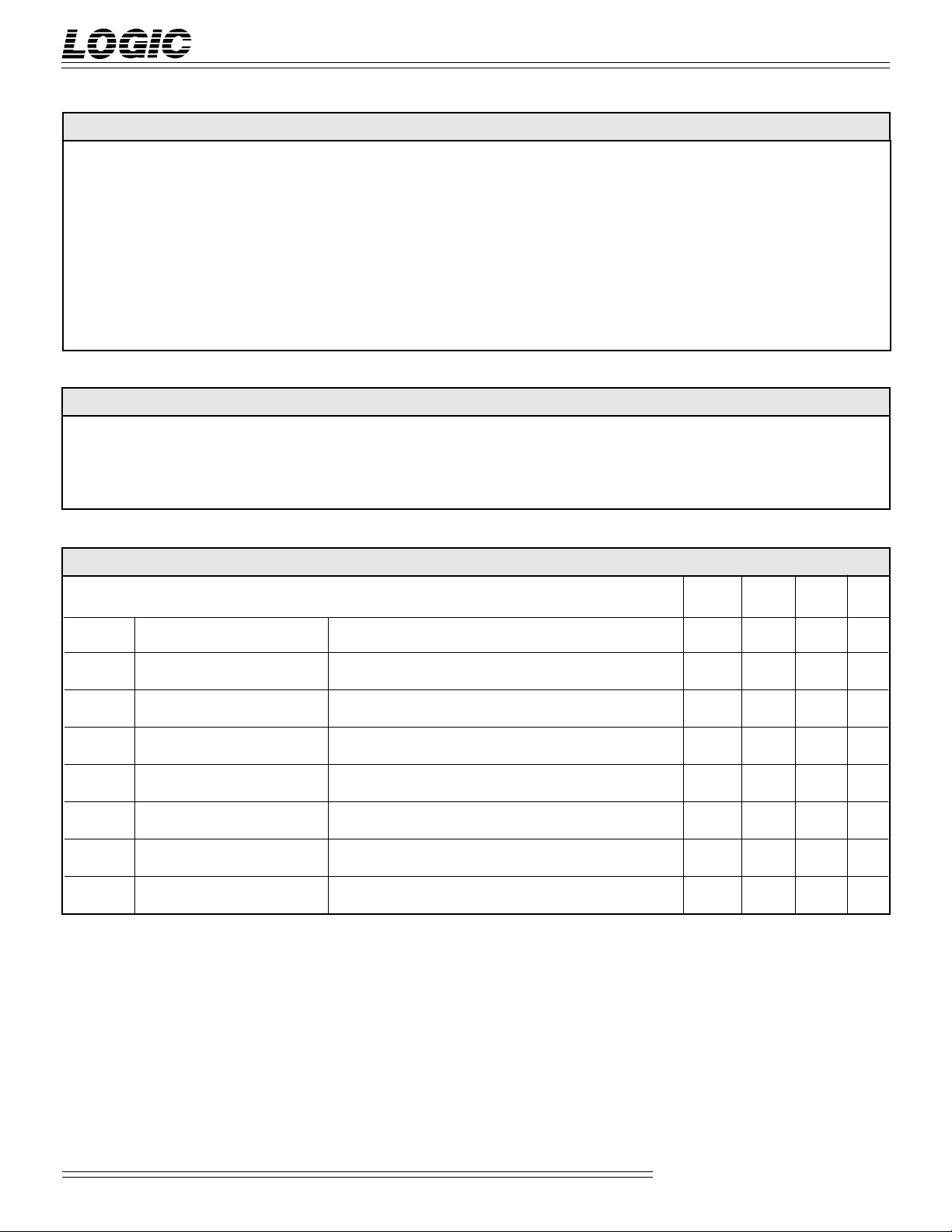

MAXIMUM RATINGS

Storage temperature ........................................................................................................... –65°C to +150°C

Operating ambient temperature........................................................................................... –55°C to +125°C

VCC supply voltage with respect to ground............................................................................ –0.5 V to +7.0V

Input signal with respect to ground ........................................................................................ –3.0 V to +7.0 V

Signal applied to high impedance output ............................................................................... –3.0 V to +7.0 V

Output current into low outputs............................................................................................................. 25 mA

Latchup current ............................................................................................................................... > 400 mA

OPERATING CONDITIONS

Active Operation, Commercial 0°C to +70°C 4.75 V ≤ VCC ≤ 5.25 V

Active Operation, Military –55°C to +125°C 4.50 V ≤ VCC ≤ 5.50 V

ELECTRICAL CHARACTERISTICS

Above which useful life may be impaired (Notes 1, 2, 3, 8)

To meet specified electrical and switching characteristics

Mode Temperature Range (Ambient) Supply Voltage

Over Operating Conditions (Note 4)

Symbol Parameter Test Condition Min Typ Max Unit

VOH Output High Voltage VCC = Min., IOH = –2.0 mA 2.4 V

VOL Output Low Voltage VCC = Min., IOL = 8.0 mA 0.5 V

VIH Input High Voltage 2.0 VCC V

VIL Input Low Voltage (Note 3) 0.0 0.8 V

IIX Input Current Ground ≤ VIN ≤ VCC (Note 12) ±20 µA

IOZ Output Leakage Current Ground ≤ VOUT ≤ VCC (Note 12) ±20 µA

ICC1 VCC Current, Dynamic (Notes 5, 6) 15 30 mA

ICC2 VCC Current, Quiescent (Note 7) 1.5 mA

Arithmetic Logic Units

3

08/16/2000–LDS.381-P

DEVICES INCORPORATED

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

6

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

16-bit Cascadable ALU

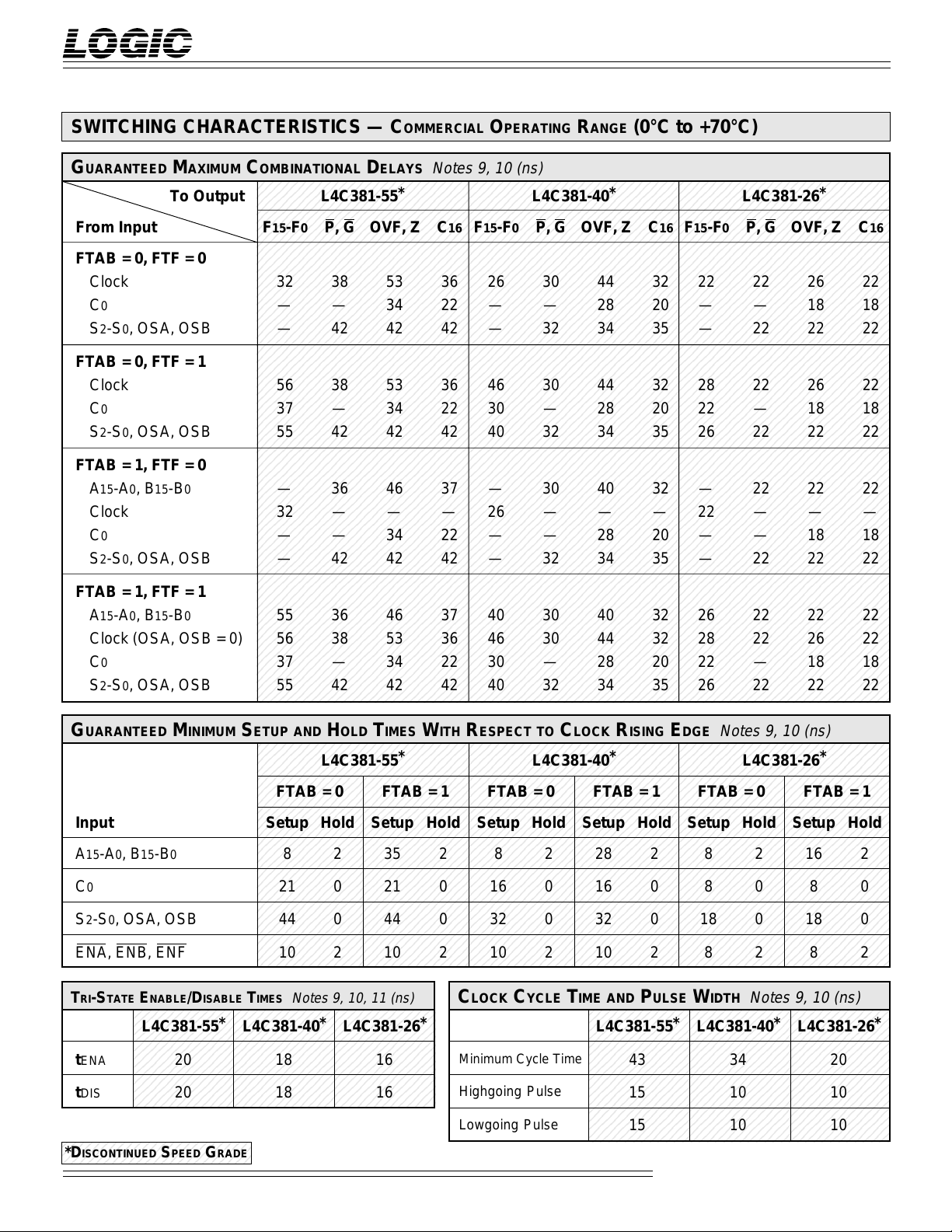

SWITCHING CHARACTERISTICS — COMMERCIAL OPERATING RANGE (0°C to +70°C)

L4C381

GUARANTEED MAXIMUM COMBINATIONAL DELAYS

To Output

From Input

FTAB = 0, FTF = 0

Clock

C0

S2-S0, OSA, OSB

FTAB = 0, FTF = 1

Clock

C0

S2-S0, OSA, OSB

FTAB = 1, FTF = 0

A15-A0, B15-B0

Clock

C0

S2-S0, OSA, OSB

FTAB = 1, FTF = 1

A15-A0, B15-B0

Clock (OSA, OSB = 0)

C0

S2-S0, OSA, OSB

GUARANTEED MINIMUM SETUP AND HOLD TIMES WITH RESPECT TO CLOCK RISING EDGE

Input

A15-A0, B15-B0

C0

S2-S0, OSA, OSB

ENA, ENB, ENF

TRI-STATE ENABLE/DISABLE TIMES

tENA

tDIS

2345678901234567890123

*DISCONTINUED SPEED GRADE

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

L4C381-55*L4C381-40*L4C381-26

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

20 18 16

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

20 18 16

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

F15-F0 P, G OVF, Z C16

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

Setup Hold Setup Hold

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

2345678901234567890123456789012123456789012345678901234567890121234567890123

L4C381-55

32 38 53 36

— — 34 22

—424242

56 38 53 36

37 — 34 22

55 42 42 42

—364637

32———

— — 34 22

—424242

55 36 46 37

56 38 53 36

37 — 34 22

55 42 42 42

L4C381-55

FTAB = 0 FTAB = 1

82352

21 0 21 0

44 0 44 0

10 2 10 2

Notes 9, 10, 11 (ns)

Notes 9, 10 (ns)

*

F15-F0 P, G OVF, Z C16

*

Setup Hold Setup Hold

CLOCK CYCLE TIME AND PULSE WIDTH

*

Minimum Cycle Time

Highgoing Pulse

Lowgoing Pulse

4

L4C381-40

*

F15-F0 P, G OVF, Z C16

26 30 44 32

— — 28 20

—323435

46 30 44 32

30 — 28 20

40 32 34 35

—304032

26———

— — 28 20

—323435

40 30 40 32

46 30 44 32

30 — 28 20

40 32 34 35

L4C381-40

FTAB = 0 FTAB = 1

82282

16 0 16 0

32 0 32 0

10 2 10 2

*

234567890123456789012345678901212345

234567890123456789012345678901212345

L4C381-55*L4C381-40*L4C381-26

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

43 34 20

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

15 10 10

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

234567890123456789012345678901212345

15 10 10

234567890123456789012345678901212345

Setup Hold Setup Hold

Arithmetic Logic Units

L4C381-26

*

22 22 26 22

— — 18 18

—222222

28 22 26 22

22 — 18 18

26 22 22 22

—222222

22———

— — 18 18

—222222

26 22 22 22

28 22 26 22

22 — 18 18

26 22 22 22

Notes 9, 10 (ns)

L4C381-26

*

FTAB = 0 FTAB = 1

82162

80 80

18 0 18 0

82 82

Notes 9, 10 (ns)

*

08/16/2000–LDS.381-P

Loading...

Loading...