LOGIC L29C521PC22, L29C520PC22, L29C520JC22 Datasheet

DEVICES INCORPORATED

L29C520/521

4 x 8-bit Multilevel Pipeline Register

Pipeline Registers

08/02/2000–LDS.520/1-P

1

❑❑

❑❑

❑ Four 8-bit Registers

❑❑

❑❑

❑ Implements Double 2-Stage Pipeline

or Single 4-Stage Pipeline Register

❑❑

❑❑

❑ Hold, Shift, and Load Instructions

❑❑

❑❑

❑ Separate Data In and Data Out Pins

❑❑

❑❑

❑ High-Speed, Low Power CMOS

Technology

❑❑

❑❑

❑ Three-State Outputs

❑❑

❑❑

❑ Replaces IDT29FCT520/IDT29FCT521

and AMD Am29520/Am29521

❑❑

❑❑

❑ Package Styles Available:

• 24-pin PDIP

• 28-pin PLCC, J-Lead

FEATURES DESCRIPTION

L29C520/521

4 x 8-bit Multilevel Pipeline Register

DEVICES INCORPORATED

The L29C520 and L29C521 are pin-

for-pin compatible with the

IDT29FCT520/IDT29FCT521 and

AMD Am29520/Am29521, implemented in low power CMOS.

The L29C520 and L29C521 contain

four registers which can be configured

as two independent, 2-level pipelines

or as one 4-level pipeline.

The Instruction pins, I1-0, control the

loading of the registers. For either

device, the registers may be configured as a four-stage delay line, with

data loaded into R1 and shifted

sequentially through R2, R3, and R4.

Also, for the L29C520, data may be

loaded from the inputs into either R1

or R3 with only R2 or R4 shifting. The

L29C521 differs from the L29C520 in

that R2 and R4 remain unchanged

during this type of data load, as

shown in Tables 1 and 2. Finally, I1-0

may be set to prevent any register

from changing.

The S1-0 select lines control a 4-to-1

multiplexer which routes the contents

of any of the registers to the Y output

pins. The independence of the I and S

controls allows simultaneous write

and read operations on different

registers.

S1 S0 Register Selected

L L Register 4

L H Register 3

H L Register 2

H H Register 1

TABLE 3. OUTPUT SELECT

I1 I0 Description

LLD➞R1 R1➞R2 R2➞R3 R3➞R4

L H HOLD HOLD D➞R3 HOLD

HLD➞R1 HOLD HOLD HOLD

H H ALL REGISTERS ON HOLD

TABLE 2.

L29C521 INSTRUCTION TABLE

I1 I0 Description

LLD➞R1 R1➞R2 R2➞R3 R3➞R4

L H HOLD HOLD D➞R3 R3➞R4

HLD➞R1 R1➞R2 HOLD HOLD

H H ALL REGISTERS ON HOLD

TABLE 1.

L29C520 INSTRUCTION TABLE

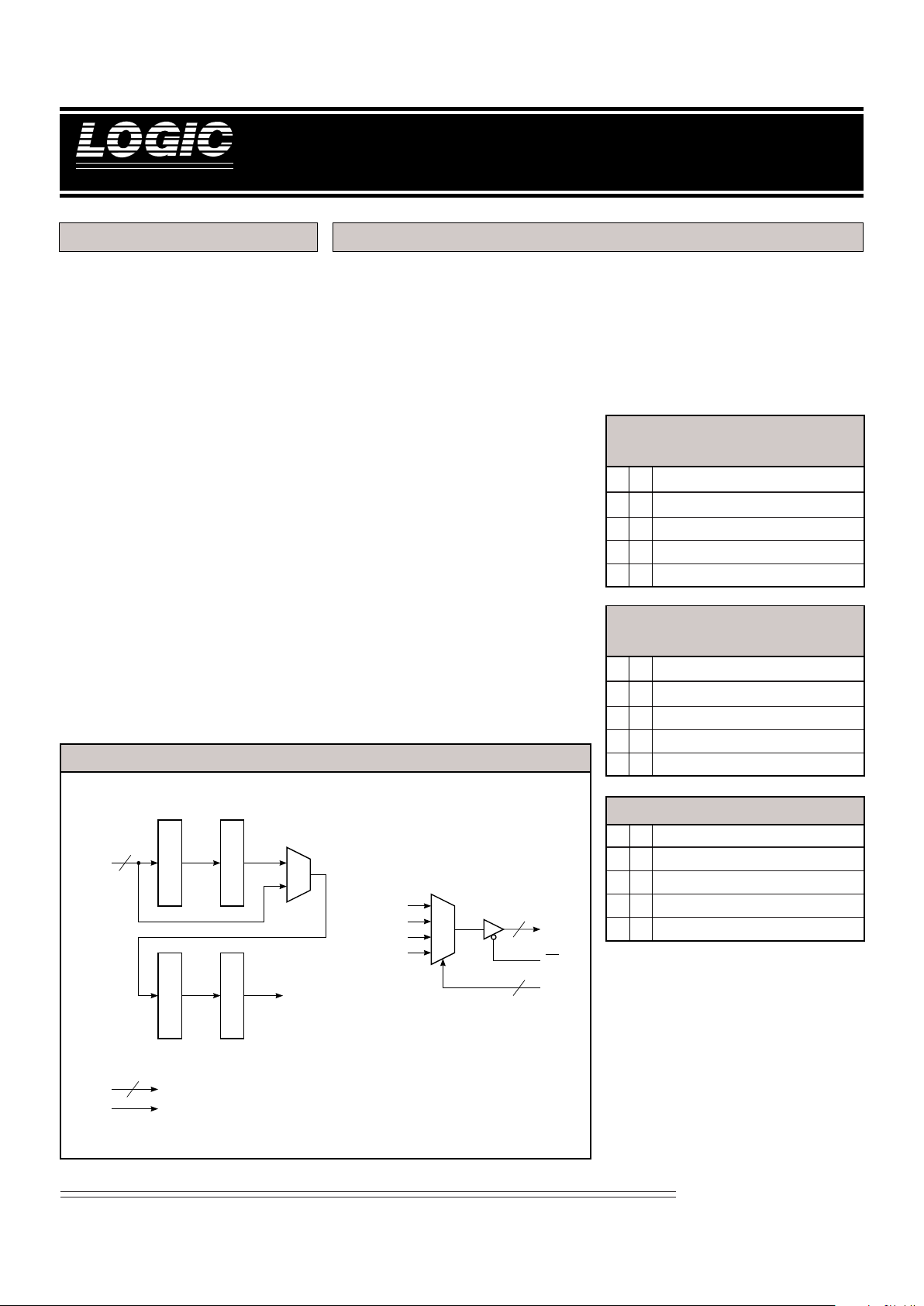

L29C520/521 BLOCK DIAGRAM

MUX

REG 1

REG 2

REG 3

REG 4

REGISTER 1

REGISTER 2

REGISTER 3

REGISTER 4

MUX

D

8-0

8

8

OE

Y

7-0

S

1-0

I

1-0

CLK

2

2

DEVICES INCORPORATED

L29C520/521

4 x 8-bit Multilevel Pipeline Register

Pipeline Registers

08/02/2000–LDS.520/1-P

2

Storage temperature ........................................................................................................... –65°C to +150°C

Operating ambient temperature........................................................................................... –55°C to +125°C

VCC supply voltage with respect to ground............................................................................ –0.5 V to +7.0V

Input signal with respect to ground ........................................................................................ –3.0 V to +7.0 V

Signal applied to high impedance output ............................................................................... –3.0 V to +7.0 V

Output current into low outputs............................................................................................................. 25 mA

Latchup current ............................................................................................................................... > 400 mA

MAXIMUM RATINGS

Above which useful life may be impaired (Notes 1, 2, 3, 8)

Symbol Parameter Test Condition Min Typ Max Unit

VOH Output High Voltage VCC = Min., IOH = –15.0 mA 2.4 V

VOL Output Low Voltage VCC = Min., IOL = 24.0 mA 0.5 V

VIH Input High Voltage 2.0 VCC V

V IL Input Low Voltage (Note 3) 0.0 0.8 V

IIX Input Current Ground ≤ VIN ≤ VCC (Note 12) ±20 µA

IOZ Output Leakage Current Ground ≤ VOUT ≤ VCC (Note 12) ±20 µA

ICC1 VCC Current, Dynamic (Notes 5, 6) 30 mA

ICC2 VCC Current, Quiescent (Note 7) 1.5 mA

ELECTRICAL CHARACTERISTICS

Over Operating Conditions (Note 4)

OPERATING CONDITIONS

To meet specified electrical and switching characteristics

Mode Temperature Range (Ambient) Supply Voltage

Active Operation, Commercial 0°C to +70°C 4.75 V ≤ VCC ≤ 5.25 V

Active Operation, Military –55°C to +125°C 4.50 V ≤ VCC ≤ 5.50 V

DEVICES INCORPORATED

L29C520/521

4 x 8-bit Multilevel Pipeline Register

Pipeline Registers

08/02/2000–LDS.520/1-P

3

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

23456789012345

6

1234567890123456789012345678901212345678901234

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1

23456789012345678901234567890121234567890123

4

1234567890123456789012345678901212345678901234

L29C520/521–

22 14*

Symbol Parameter Min M ax Min M ax

tPD Clock to Output Delay 22 14

tSEL Select to Output Delay 20 13

tPW Clock Pulse Width 10 7

tSI Instruction Setup Time 10 5

tHI Instruction Hold Time 3 1

tSD Data Setup Time 10 5

tHD Data Hold Time 3 1

tENA Three-State Output Enable Delay (Note 11) 21 15

tDIS Three-State Output Disable Delay (Note 11) 15 12

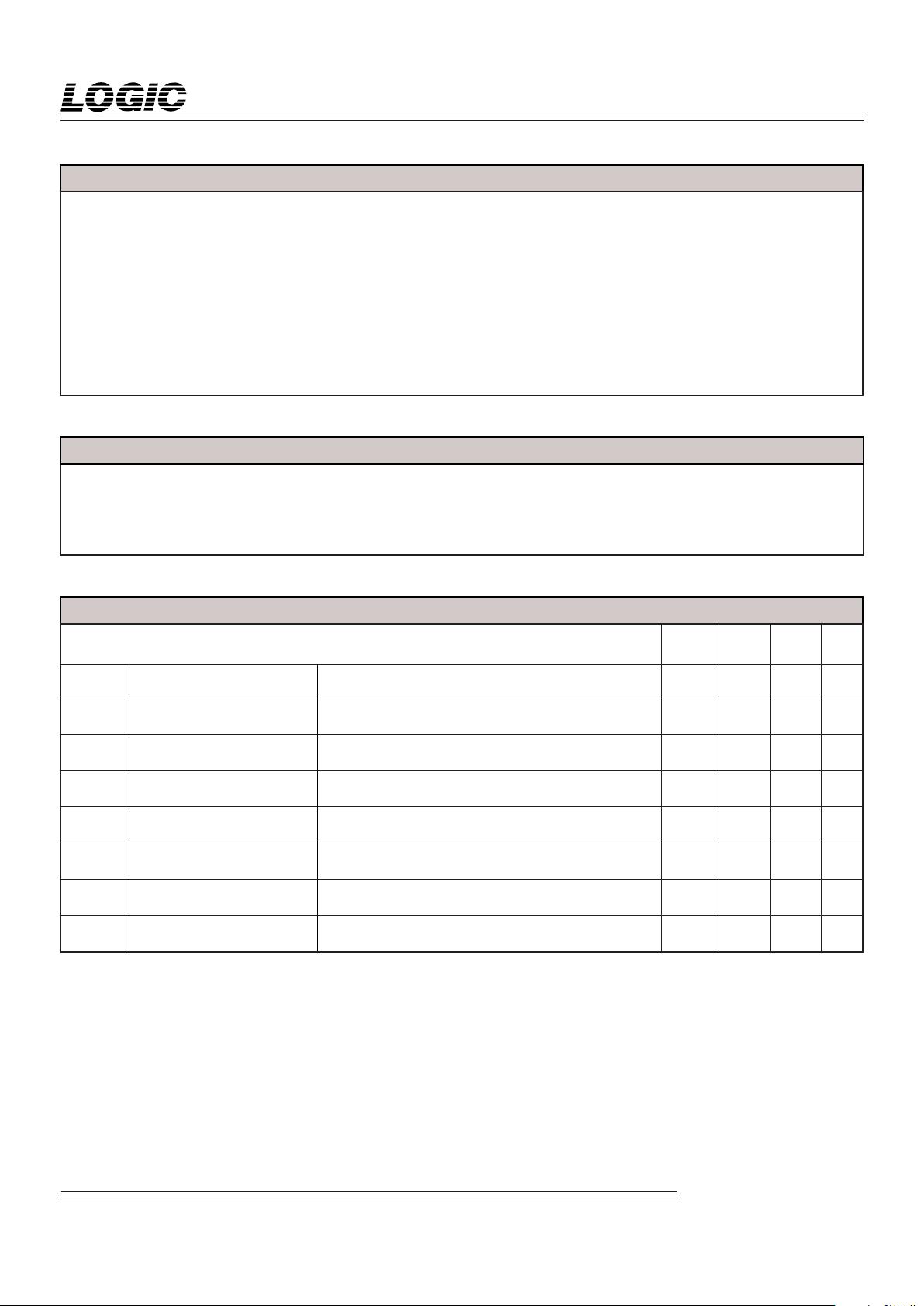

COMMERCIAL OPERATING RANGE (0°C to +70°C)

Notes 9, 10 (ns)

SWITCHING CHARACTERISTICS

L29C520/521–

30

*

24

*

16

*

Symbol Parameter Min Max Min Max Min Max

tPD Clock to Output Delay 30 24 16

tSEL Select to Output Delay 30 22 15

tPW Clock Pulse Width 15 10 8

tSI Instruction Setup Time 15 1 0 6

tHI Instruction Hold Time 5 3 2

tSD Data Setup Time 15 1 0 6

tHD Data Hold Time 5 3 2

tENA Three-State Output Enable Delay (Note 11) 25 22 16

tDIS Three-State Output Disable Delay (Note 11) 20 16 13

MILITARY OPERATING RANGE (–55°C to +125°C)

Notes 9, 10 (ns)

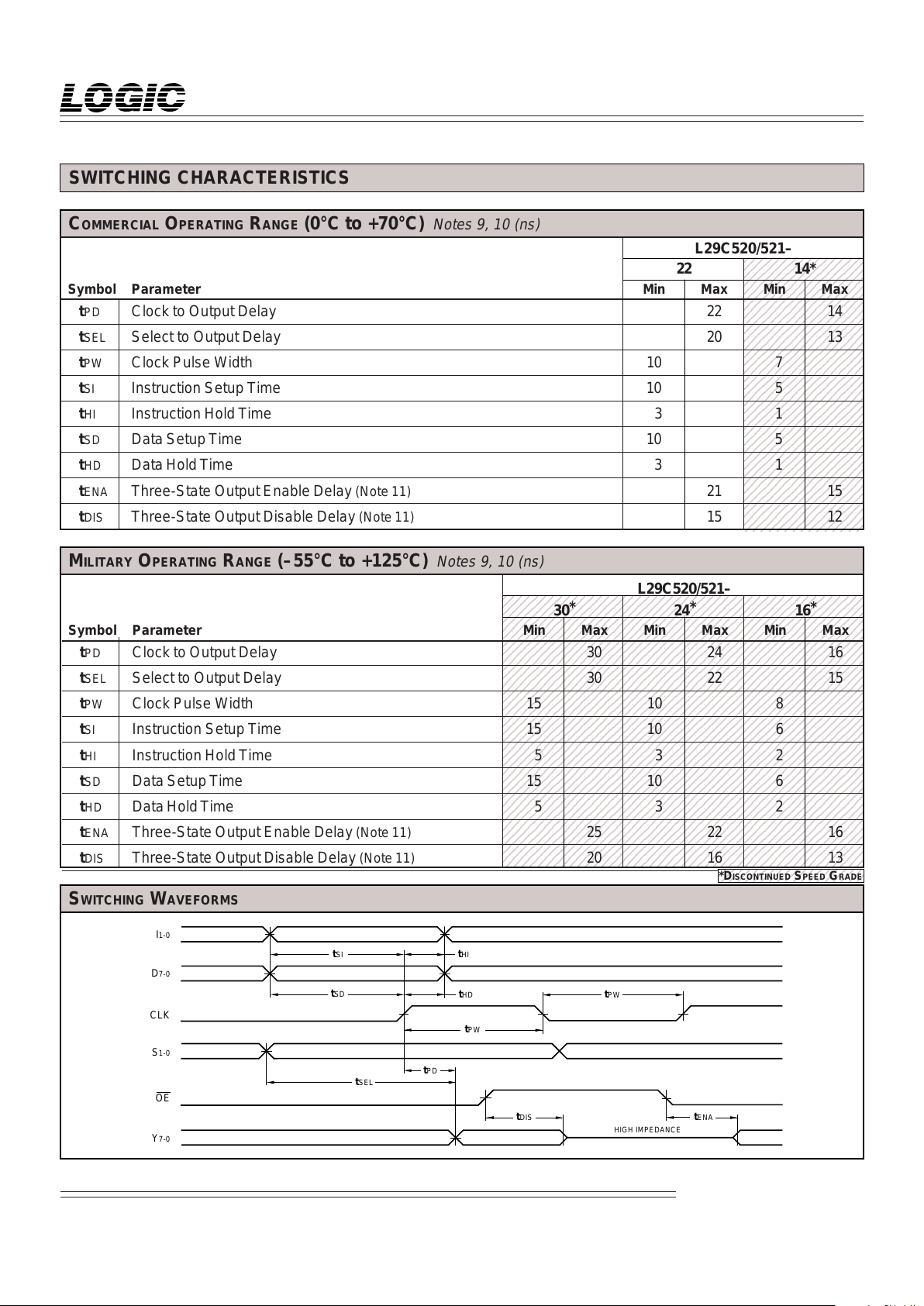

SWITCHING WAVEFORMS

HIGH IMPEDANCE

t

ENA

t

DIS

t

PW

t

SI

t

SD

D

7-0

CLK

OE

t

PD

t

HD

t

HI

t

PW

t

SEL

I

1-0

S

1-0

Y

7-0

*DISCONTINUED SPEED GRADE

Loading...

Loading...