Page 1

TVS Diode Arrays (SPA

, etc.)

®

Diodes)

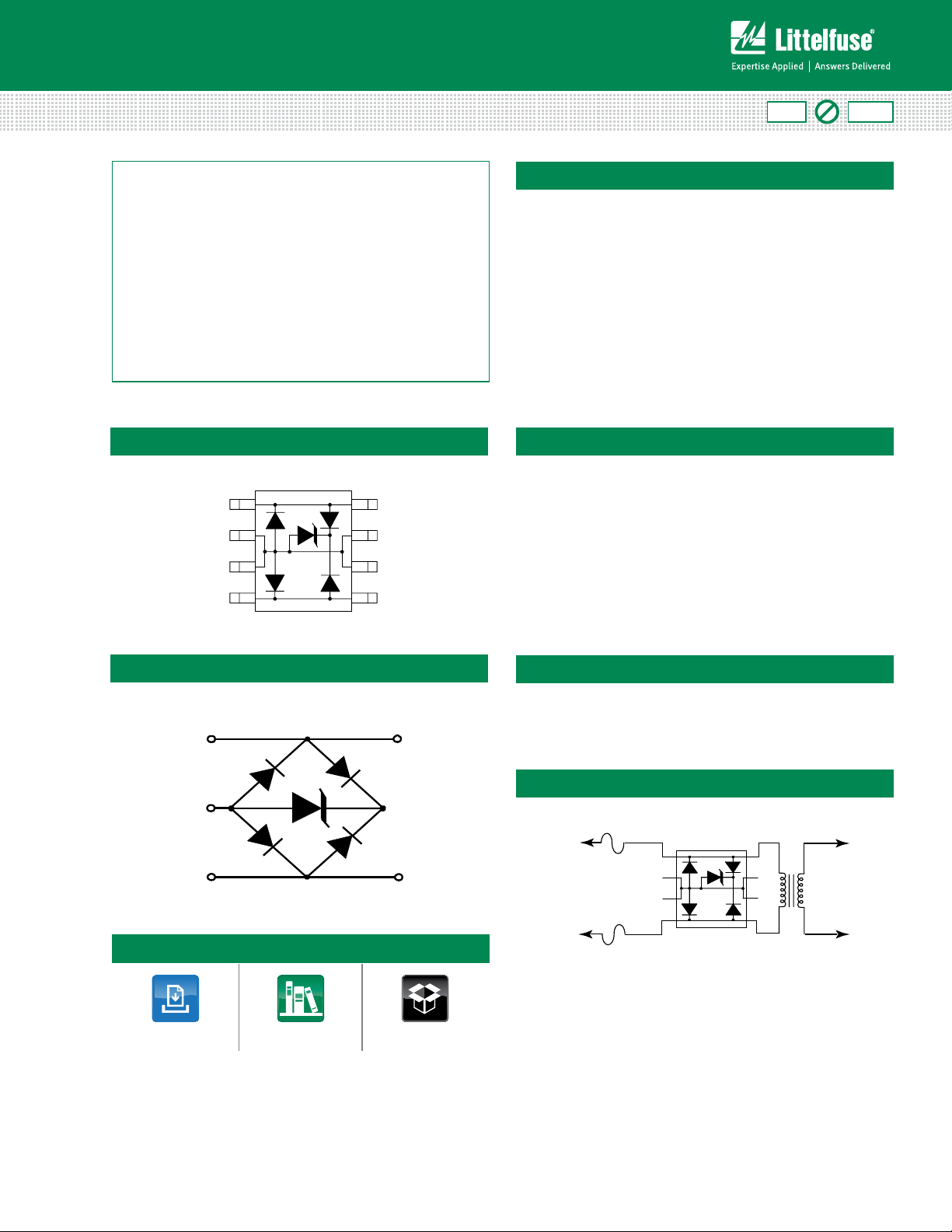

Lightning Surge Protection - LC03-3.3 Series

LC03-3.3 Series 3.3V 150A Diode Array

Pinout

1

2

3

SOIC-8 (Top View)

8

7

6

54

RoHS

Pb

GREEN

Description

This LC03-3.3 series provides overvoltage protection for

applications such as 10/100/1000 BaseT Ethernet, and

T3/E3 interfaces. This new protector combines the TVS

diode element with a diode rectifier bridge to provide both

longitudinal and differential protection in one package.

This design results in a capacitive loading characteristic

that is log-linear with respect to the signal voltage across

the device. This reduces intermodulation (IM) distortion

caused by a typical solid-state protection solution. The

application schematic provides the connection information

and the LC03-3.3 is rated for GR-1089, intra-building

transient immunity requirements for telecommunication

installations.

Features

• Lightning Protection,

IEC61000-4-5, 150A

(t

p

=8/20µs)

• EFT, IEC61000-4-4, 40A

(t

p

=5/50ns)

• Low insertion loss, loglinear capacitance

• Low clamping voltage

• SOIC-8 surface mount

package (JEDEC MS-012)

• Combined longitudinal

and metallic protection

• Clamping speed of

nanoseconds

• UL 94V-0 epoxy molding

• RoHS compliant

Functional Block Diagram

Line in

Pin 2, 3, 6,

and 7

Line in

Pin 1 and 8

Pin 4 and 5

Line out

Line out

Additional Information

Datasheet

Life Support Note:

Not Intended for Use in Life Support or Life Saving Applications

The products shown herein are not designed for use in life sustaining or life saving

applications unless otherwise expressly indicated.

© 2013 Littelfuse, Inc.

Specifications are subject to change without notice.

Revised: 04/24/13

Resources

Samples

Applications

• T1/E1 Line cards

• T3/E3 and DS3 Interfaces

• 10/100/1000 BaseT

Ethernet

• STS-1 Interfaces

Application Example

TeleLink (0461 1.25) LC03-3.3BTG

1

2

3

4

8

7

6

5

to chipset

(Ethernet PHY,

T3/E3 PHY

This schematic shows a high-speed data interface

protection solution. The LC03-3.3BTG is compatible with

the intra-building surge requirements of Telcordia’s GR1089-CORE, and the Basic Level Recommendations of

ITU K.20 and K.21. The TeleLink fuse provides overcurrent

protection for the long term 50/60 Hz power fault events.

Page 2

TVS Diode Arrays (SPA

®

Diodes)

Lightning Surge Protection - LC03-3.3 Series

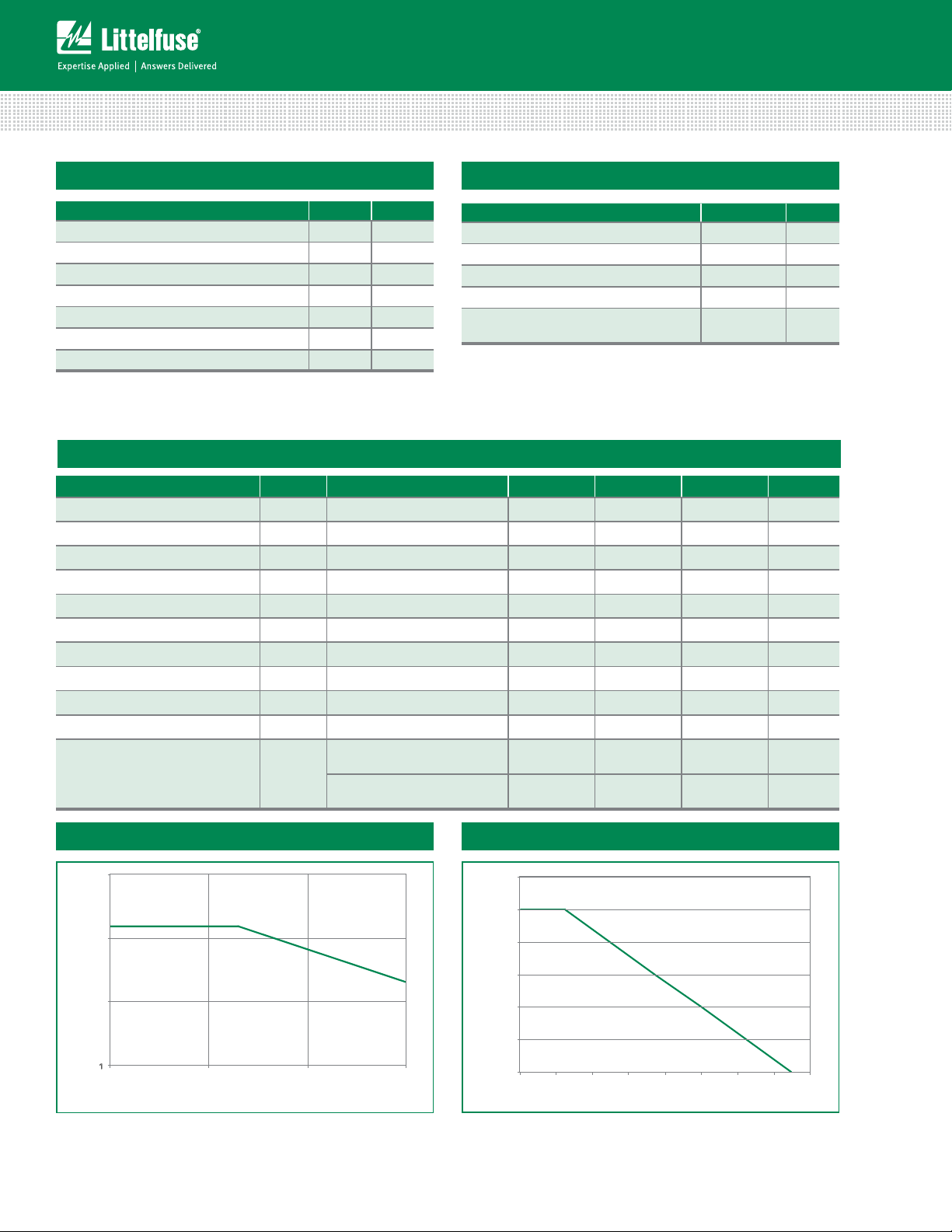

Absolute Maximum Ratings

Parameter Rating Units

Peak Pulse Current (8/20µs) 150 A

Peak Pulse Power (8/20µs) 3300 W

IEC 61000-4-2, Direct Discharge, (Level 4) 30 kV

IEC 61000-4-2, Air Discharge, (Level 4) 30 kV

IEC 61000-4-5 (8/20µs) 150 A

Telcordia GR 1089 (Intra-Building) (2/10µs) 100 A

ITU K.20 (5/310µs) 40 A

CAUTION: Stresses above those listed in “Absolute Maximum Ratings” may cause

permanent damage to the device. This is a stress only rating and operation of the device

at these or any other conditions above those indicated in the operational sections of this

specification is not implied.

Electrical Characteristics (TOP = 25°C)

Parameter Symbol Test Conditions Min Typ Max Units

Reverse Stand-Off Voltage V

Reverse Breakdown Voltage V

Snap Back Voltage V

Reverse Leakage Current I

Clamping Voltage, Line-Ground V

Clamping Voltage, Line-Ground V

Dynamic Resistance, Line-Ground R

Clamping Voltage, Line-Line V

Clamping Voltage, Line-Line V

Dynamic Resistance , Line-Line R

Junction Capacitance C

RWM

BR

SB

R

C

C

DYN

C

C

DYN

Between I/O Pins and Ground

j

IT≤1µA - - 3.3 V

IT= 2µA 3.3 - - V

IT= 50mA 3.3 - - V

V

= 3.3V, T= 25°C - - 1 µA

RWM

IPP= 50A, tp=8/20 µs - - 13 V

IPP= 100A, tp=8/20 µs - - 17 V

(VC2-VC1)/(I

IPP= 50A, tp=8/20 µs - - 15 V

IPP= 100A, tp=8/20 µs - - 20 V

(VC2-VC1)/(I

VR=0V, f= 1MHz

Between I/O Pins

=0V, f= 1MHz

V

R

Thermal Information

Parameter Rating Units

SOIC Package 170 °C/W

Operating Temperature Range –40 to 125 °C

Storage Temperature Range –55 to 150 °C

Maximum Junction Temperature 150 °C

Maximum Lead Temperature (Soldering

20-40s) (SOIC - Lead Tips Only)

) - 0.15 -

PP2-IPP1

) - 0.25 -

PP2-IPP1

- 9 12 pF

- 4.5 6 pF

260 °C

SP03a-3.3

W

W

Figure 1: Non-repetitive Peak Pulse Current vs. Pulse Time

1000

100

10

Peak Pulse Current (A)

1

110100 10 00

Pulse decay time (µs)

Figure 2: Current Derating Curve

120

)

P

100

80

60

40

20

Percentage of Rated Current (%I

0

020406080100 120140 160

Ambient Temperature (C)

Specifications are subject to change without notice.

© 2013 Littelfuse, Inc.

Revised: 04/24/13

Page 3

TVS Diode Arrays (SPA

Line to Ground

Line to Line

0

1

2

3

4

5

6

7

8

9

10

0.00.5 1.01.5 2.02.5 3.0

Capacitance (pF)

Bias Voltage (V)

Line to Line

Line to Ground

0

2

4

6

8

10

12

14

16

18

0102030405060708090 100

Clamp Voltage-V

C

(V)

Peak Pulse Current-IPP(A)

t

R

R

o

C

e

T

T

®

Diodes)

Lightning Surge Protection - LC03-3.3 Series

Figure 3: Pulse Waveform

110%

100%

90%

80%

70%

PP

60%

50%

Percent of I

40%

30%

20%

10%

0%

0.0 5.0 10.0 15.0 20.0 25.0 30.0

Figure 5: Capacitance vs. Reverse Voltage

Figure 4: Clamping Voltage vs. Peak Pulse Current

Figure 6: Forward Voltage vs. Forward Current

7

6

5

4

3

Ground-to-Line

Soldering Parameters

Reflow Condition Pb – Free assembly

- Temperature Min (T

Pre Heat

Average ramp up rate (Liquidus) Temp

(T

) to peak

L

T

S(max)

Reflow

Peak Temperature (TP) 260

Time within 5°C of actual peak

Temperature (t

Ramp-down Rate 6°C/second max

Time 25°C to peak Temperature (T

Do not exceed 260°C

© 2013 Littelfuse, Inc.

Specifications are subject to change without notice.

Revised: 04/24/13

- Temperature Max (T

- Time (min to max) (ts) 60 – 180 secs

to TL - Ramp-up Rate 3°C/second max

- Temperature (TL) (Liquidus) 217°C

- Temperature (tL) 60 – 150 seconds

)

p

) 150°C

s(min)

) 200°C

s(max)

3°C/second max

+0/-5

°C

20 – 40 seconds

) 8 minutes Max.

P

2

Forward Voltage (V)

1

0

0102030405060708090 100

Forward Current (A)

t

T

P

Ramp-up

t

amp-up

PreheatPrehea

S

T

L

T

S(max)

Temperature

T

S(min)

25

time to peak temperature

P

t

L

Ramp-down

Time

Critical Zone

ritical Zon

L to TP

to

T

amp-d

Page 4

TVS Diode Arrays (SPA

LC03

3.3

B T

G

®

Diodes)

Lightning Surge Protection - LC03-3.3 Series

Package Dimensions — Mechanical Drawings and Recommended Solder Pad Outline

Package SOIC-8

Pins 8

JEDEC MS-012

Millimetres Inches

L

o

F

Recommended

Soldering Pad Outline

(Reference Only)

A 1.35 1.75 0.053 0.069

A1 0.10 0.25 0.004 0. 010

A2 1.25 1.65 0.050 0.065

B 0.31 0.51 0.012 0.020

c 0.17 0.25 0.007 0.010

D 4.80 5.00 0.189 0.197

E 5.80

E1 3.80 4.00 0.150 0.157

e 1.27 BSC 0.050 BSC

L 0.40

Min Max Min Max

6.20

1.27

0.228

0.016

SP03a-3.3

0.244

0.050

Embossed Carrier Tape & Reel Specification — SOIC Package

Part Numbering System

–

G= Green

T= Tape & Reel

Series

Working

Voltage

Package

B = SOIC

Part Marking System

F

LC03-3.3

L

XXXXXXXX

First Line: Part number

Second Line: Date code

Ordering Information

Part Number Package Marking Min. Order Qty.

LC03-3.3BTG SOIC-8 LC03-3.3 2500

Millimetres Inches

Min Max Min Max

E 1.65 1.85 0.065 0.073

F 5.4 5.6 0.213 0.22

P2 1.95 2.05 0.077 0.081

D 1. 5 1. 6 0.059 0.063

D1 1.50 Min 0.059 Min

P0 3.9 4.1 0.154 0.161

10P0 40.0 ± 0.20 1.574 ± 0.008

W 11. 9 12.1 0.468 0.476

P 7. 9 8.1 0.311 0.319

A0 6.3 6.5 0.248 0.256

B0 5.1 5.3 0.2 0.209

K0 2 2.2 0.079 0.087

t 0.30 ± 0.05 0.012 ± 0.002

Product Characteristics

Lead Plating Matte Tin

Lead Material Copper Alloy

Lead Coplanarity 0.004 inches (0.102mm)

Substitute Material Silicon

Body Material Molded Epoxy

Flammability UL 94 V-0

Notes :

1. All dimensions are in millimeters

2. Dimensions include solder plating.

3. Dimensions are exclusive of mold flash & metal burr.

4. Blo is facing up for mold and facing down for trim/form, i.e. reverse trim/form.

5. Package surface matte finish VDI 11-13.

Specifications are subject to change without notice.

© 2013 Littelfuse, Inc.

Revised: 04/24/13

Loading...

Loading...