Page 1

advertisement

y

Pass HDMI Compliance Tests with Ease – Design Note 394

Bill Martin

Introduction

The high defi nition multimedia interface (HDMI) is fast

becoming the de facto standard for passing digital

audio and video data in home entertainment systems.

2

This standard includes an I

C type bus called a display

data channel (DDC) that is used to pass extended digital

interface data (EDID) from the sink device (such as a

digital TV) to the source device (such as a digital A/V

receiver). EDID includes vital information on the digital

data formats that the sink device can accept. The HDMI

specifi cation requires that devices have less than 50pF

of input capacitance on their DDC bus lines, which can

®

be very diffi cult to meet. The LTC

4300A’s capacitance

buffering feature allows devices to pass the HDMI DDC

input capacitance compliance test with ease.

LTC4300A-1 Bus Buffer

The LTC4300A-1 is a 2-wire bus buffer that includes

capacitance buffering between input and output, an enable pin for input-to-output connection control through

hardware and rise time accelerators to provide for swift

bus transitions through the bus logic thresholds. Due

to the sub-10pF input capacitance of the LTC4300A-1,

the capacitance buffering right at the HDMI connector

interface allows the component to easily pass the DDC

input capacitance test limit of 50pF even if the internal

capacitance of the channel is substantially higher. The

HDMI cable connector must see the OUT side of the

LTC4300A-1 for the input capacit ance compliance testing

to be accurate.

In HDMI, the sink pulls the hot plug detect (HPD) signal

h ig h to t el l t h e s ou r ce th a t i t i s r e ad y t o a c ce pt co m ma nd s

through the DDC. This signal can be controlled by the

READY pin of the LTC4300A-1 to prevent the possibility

of erroneous attempts by the source to contact the sink

before the sink is ready to return EDID. The READY pin

only goes high after 5V is applied and the LTC4300A-1

ENABLE pin is pulled high by the HDMI receiver IC, a

controller in the sink, or the 5V line itself.

The rise time accelerators in the LTC4300A-1 compress

transition times on rising signal edges, minimizing the

chance of interrupted data transfer due to noise and al-

2

lowing the DDC to meet I

C timing requirements. That

is, HDMI specifi cation allows for 800pF of load; enough

that the DDC cannot be guaranteed to meet the required

2

100kHz I

C 1µs rise time specifi cation with the allowed

DDC pullup resist ance values. Rise time acceler ators allow

this timing requirement to be met even with capacitances

well above 800pF.

, LT, LTC, LTM and Burst Mode are registered trademarks of Linear Technolog

Corporation. All other trademarks are the property of their respective owners.

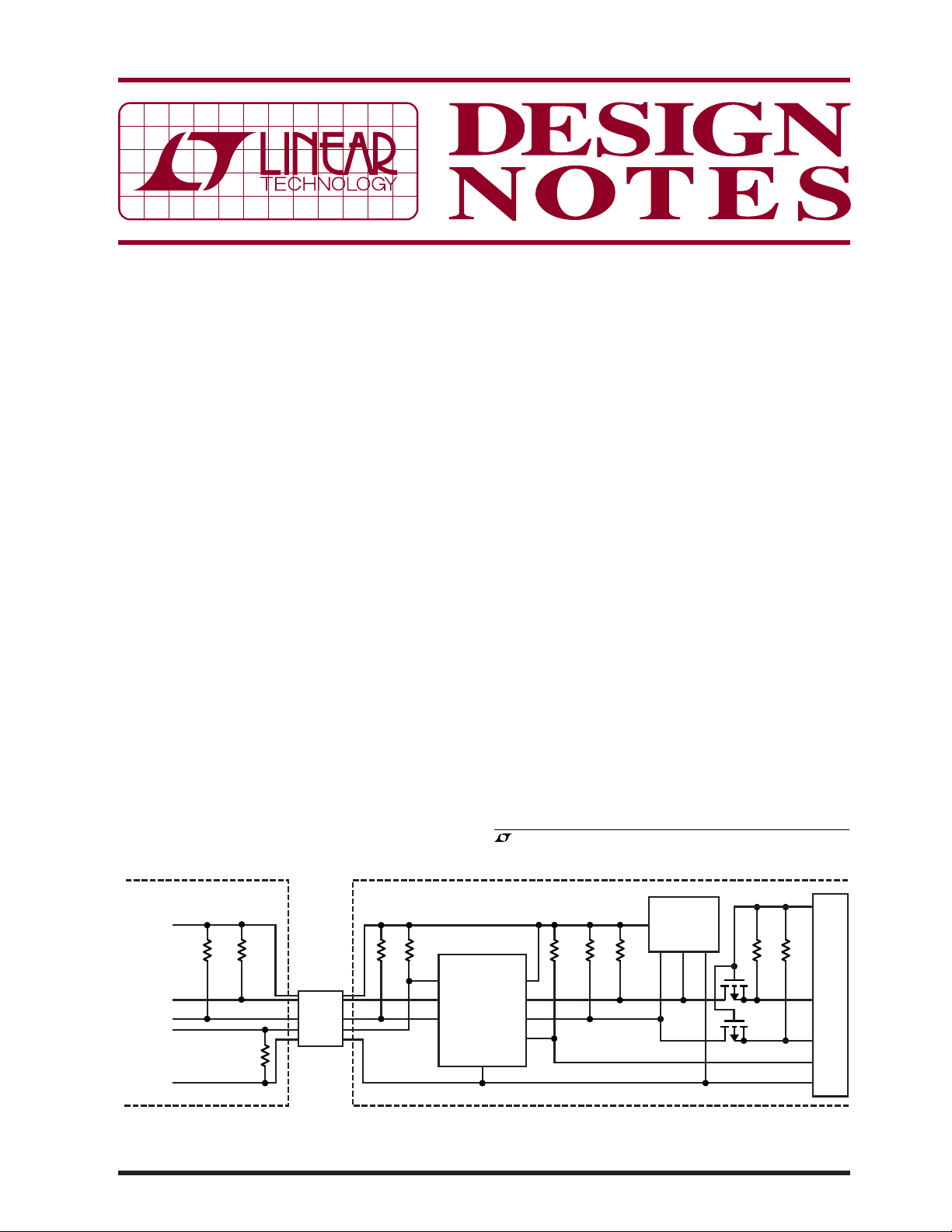

5V

SDA

TO

HDMI

SCL

TX IC

HPD

DDC/CEC GROUND

HDMI SOURCE (DVD PLAYER)

08/06/394

100k

EEPROM

V

CC

SCL SDA

HDMI

CABLE

5V

5

7

2

DDC

HDMI SINK (DIGITAL TV)

LTC4300A-1

READY

SDAOUT

SCLOUT

GND

V

SDAIN

SCLIN

ENABLE

4

100k 10k 10k

8

CC

6

3

1

Figure 1. LTC4300A-1 in HDMI Capacitance Buffering Application

GND

3.3V

10k 10k1.8k 47k1.8k 1k

DN394 F01

HDMI

RX IC

Page 2

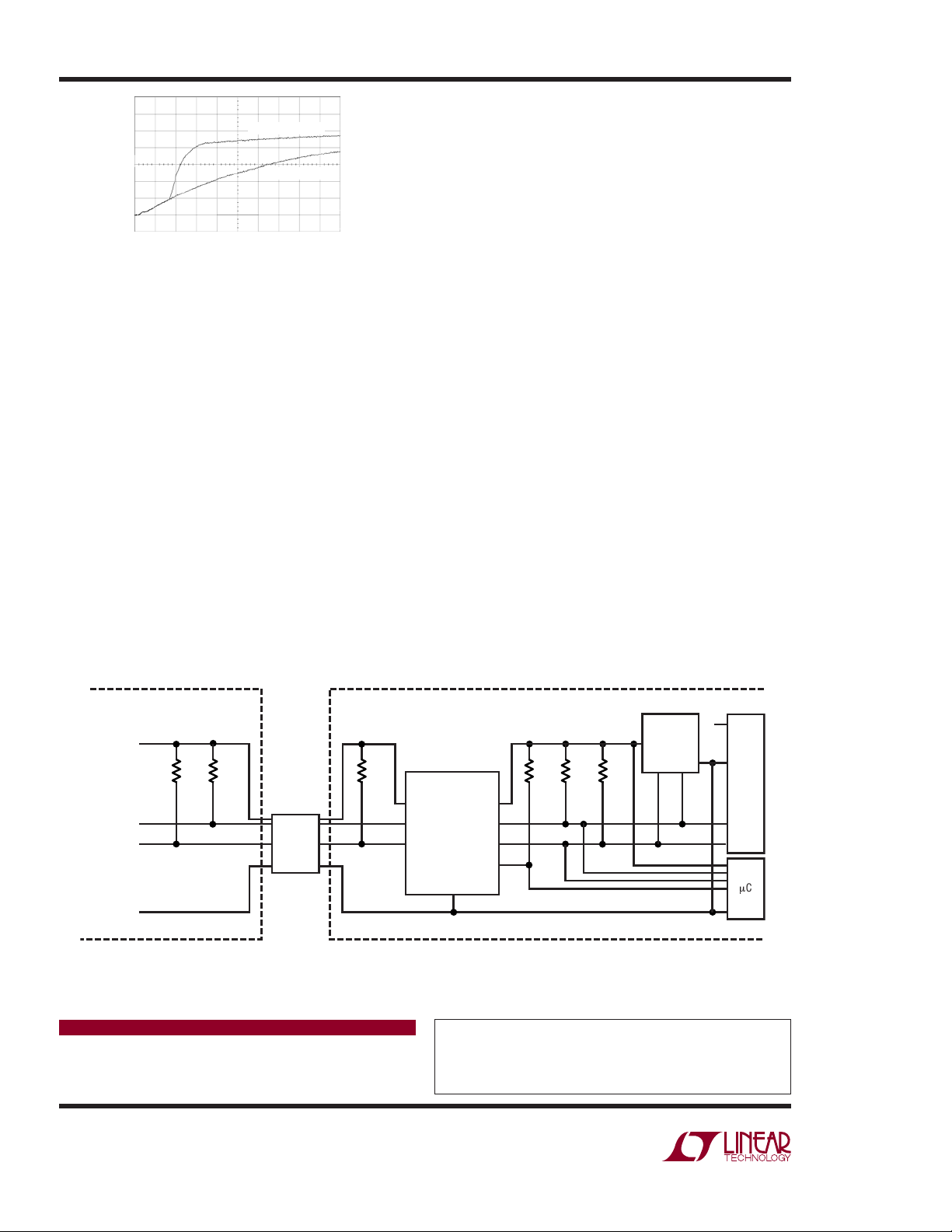

WITH LTC4300A

1V/DIV

200ns/DIV

NO BUFFER

DN394 F02

Figure 2. The LTC4300A Provides Capacitance Buffering for

the DDC while Improving Bus Timing

LTC4300A-3 Level Shifting Buffer

The LTC4300A-3 level shifting I2C buffer is also a

good solution for this application. Figure 3 shows the

LTC4300A-3 being used for capacitance bu ffering and 5V

to 3.3V level shifting. In this application, the EEPROM is

powered by a backup 3.3V supply that is available when

the component is turned off. The EDID in the EEPROM

should be available for reading even when a component’s

power is off. The level shifting between the 5V and 3.3V

b u s s e g m e n t s i s a c c o m p l i s h e d b y h a v i n g s e p a r a t e s u p p l y

pins for the two segments.

If the 5V supply for the DDC is changed to 3.3V in future

versions of the HDMI specifi cation, the LTC4300A-1 can

remain in the design as is, for it can work with supply

voltages from 2.7V to 5.5V. The LTC4300A-1 will transparently support new and legacy equipment in the case

of an HDMI specifi cation change.

Figure 2 shows how the LTC4300A-1 provides capacitance buffering at the cable interface while improving

the rise time of the heavily loaded 5V bus (750pF in this

example). Without the LTC4300A-1, the signal is failing

2

C 1µs rise time specifi cation (measured between

the I

and 0.7VCC). In the DDC capacitance test, only

0.3V

CC

the capacitance of the connector, the traces to the

LTC4300A-1 and the less than 10pF input capacitance of

the LTC4300A-1 will be measured.

5V

SDA

TO

HDMI

SCL

TX IC

DDC/CEC GROUND

HDMI SOURCE (DVD PLAYER)

1.8k 47k1.8k

HDMI

CABLE

5V

DDC

HDMI REPEATER (DIGITAL RECEIVER)

Having two supply pins also allows the LTC4300A-3 to

provide rising edge acceleration on the 3.3V and 5V bus

segments. This is a useful feature for the bus segment

that is inside the component, but cable capacitance values

of well over the 700pF HDMI spec will be encountered in

the up to 30m HDMI cables that are being used for home

theaters, so rise time acceleration is a most valuable

feature on the cable side bus segment.

Although the applications shown are for HDMI receive

channels, the LTC4300A-1 and LTC4300A-3 can also be

used in HDMI transmit channels with equal success.

Conclusion

The LTC4300A-1 and LTC4300A-3 solve the DDC capacitance testing problem in HDMI while also substantially improving the timing performance of the bus and

providing a high level of ESD protection.

SWITCHED

3.3V

HDMI

RX IC

DN394 F03

LTC4300A-3

V

CC2

SDAOUT

SCLOUT

GND

V

SDAIN

SCLIN

ENABLE

BACKUP 3.3V

100k 10k 10k

CC

EEPROM

V

CC

SCL SDA

m

C

Figure 3. LTC4300A-3 in a Level Shifting and Capacitance Buffering HDMI Application with Backup 3.3V

Data Sheet Download

http://www.linear.com

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900

●

FAX: (408) 434-0507 ● www.linear.com

For applications help,

call (408) 432-1900, Ext. 2759

dn394f LT 0806 409K • PRINTED IN THE USA

© LINEAR TECHNOLOGY CORPORATION 2006

Loading...

Loading...