FEATURES

LTC3831

High Power Synchronous

Switching Regulator Controller

for DDR Memory Termination

U

DESCRIPTIO

■

High Power Switching Regulator Controller

for DDR Memory Termination

■

V

Tracks 1/2 of VIN or External V

OUT

■

No Current Sense Resistor Required

■

Low Input Supply Voltage Range: 3V to 8V

■

Maximum Duty Cycle >91% Over Temperature

■

Drives All N-Channel External MOSFETs

■

High Efficiency: Over 95% Possible

■

Programmable Fixed Frequency Operation:

REF

100kHz to 500kHz

■

External Clock Synchronization Operation

■

Programmable Soft-Start

■

Low Shutdown Current: <10µA

■

Overtemperature Protection

■

Available in 16-Pin Narrow SSOP Package

U

APPLICATIO S

■

DDR SDRAM Termination

■

SSTL_2 Interface

■

SSTL_3 Interface

The LTC®3831 is a high power, high efficiency switching

regulator controller designed for DDR memory termination. The LTC3831 generates an output voltage equal to

1/2 of an external supply or reference voltage. The LTC3831

uses a synchronous switching architecture with N-channel MOSFETs. Additionally, the chip senses output current through the drain-source resistance of the upper

N-channel FET, providing an adjustable current limit

without a current sense resistor.

The LTC3831 operates with input supply voltage as low as

3V and with a maximum duty cycle of >91%. It includes a

fixed frequency PWM oscillator for low output ripple

operation. The 200kHz free-running clock frequency can

be externally adjusted or synchronized with an external

signal from 100kHz to above 500kHz. In shutdown mode,

the LTC3831 supply current drops to <10µA.

, LTC and LT are registered trademarks of Linear Technology Corporation.

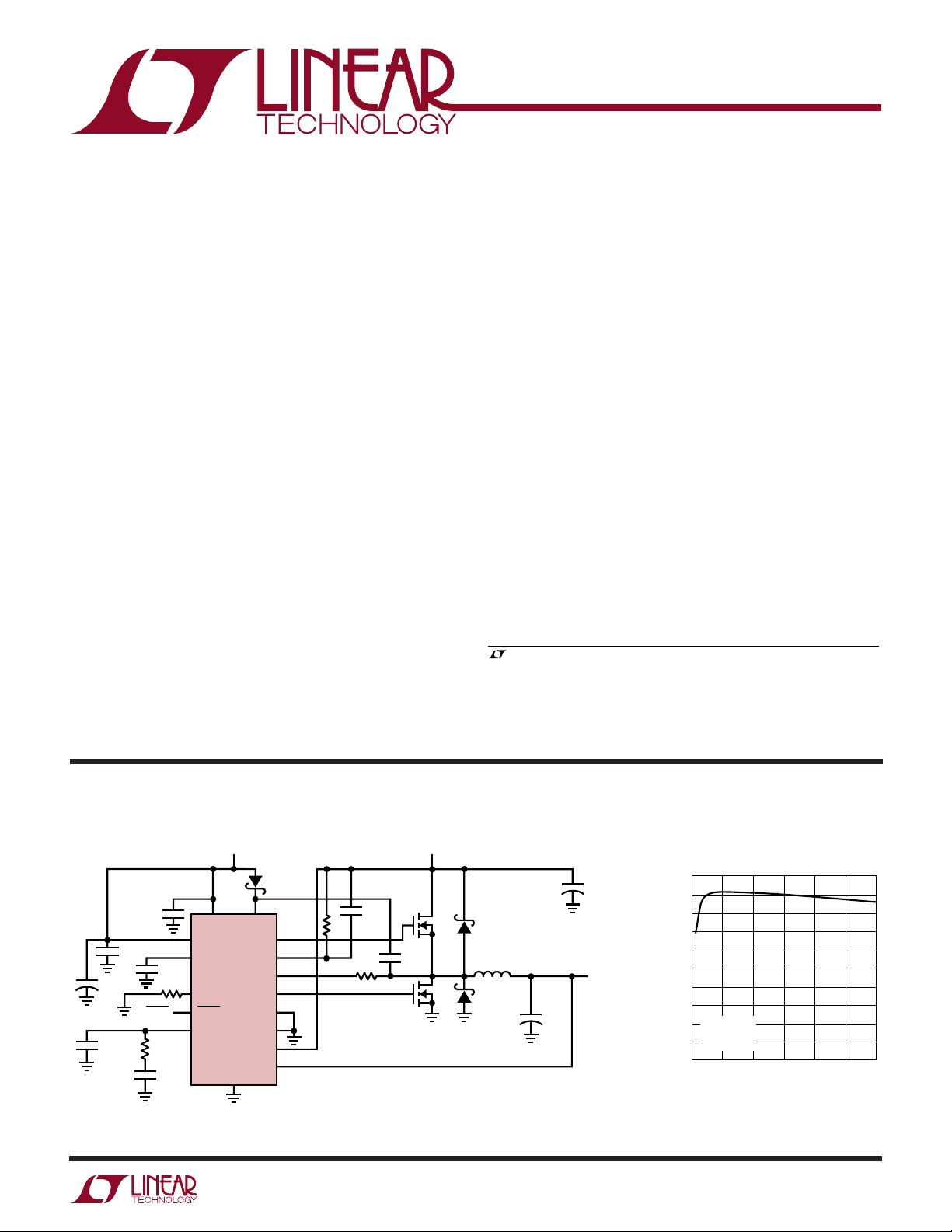

TYPICAL APPLICATIO

5V

MBR0530T1

1µF

0.1µF

+

4.7µF

SHDN

C1

33pF

R

15k

PV

PV

CC2

CC1

0.01µF

130k

C

C

C

1500pF

V

CC

SS

FREQSET

SHDN

COMP

LTC3831

–

R

I

MAX

PGND

GND

TG

I

FB

BG

+

R

FB

Figure 1. Typical DDR Memory Termination Application

U

0.1µF

10k

1k

C

: SANYO POSCAP 6TPB330M

IN

: SANYO POSCAP 4TPB470M

C

OUT

Q1, Q2: SILICONIX Si4410DY

V

DDQ

2.5V

Q1 MBRS340T3

0.1µF

Q2

L

O

1.2µH

MBRS340T3

Efficiency vs Load Current

+

C

IN

330µF

×2

V

TT

1.25V

±6A

+

C

OUT

470µF

×3

3831 F01

100

90

80

70

60

50

40

EFFICIENCY (%)

30

TA = 25°C

20

= 2.5V

V

IN

10

V

OUT

0

0

= 1.25V

1

2

LOAD CURRENT (A)

34

5

6

2831 G01

3831f

1

LTC3831

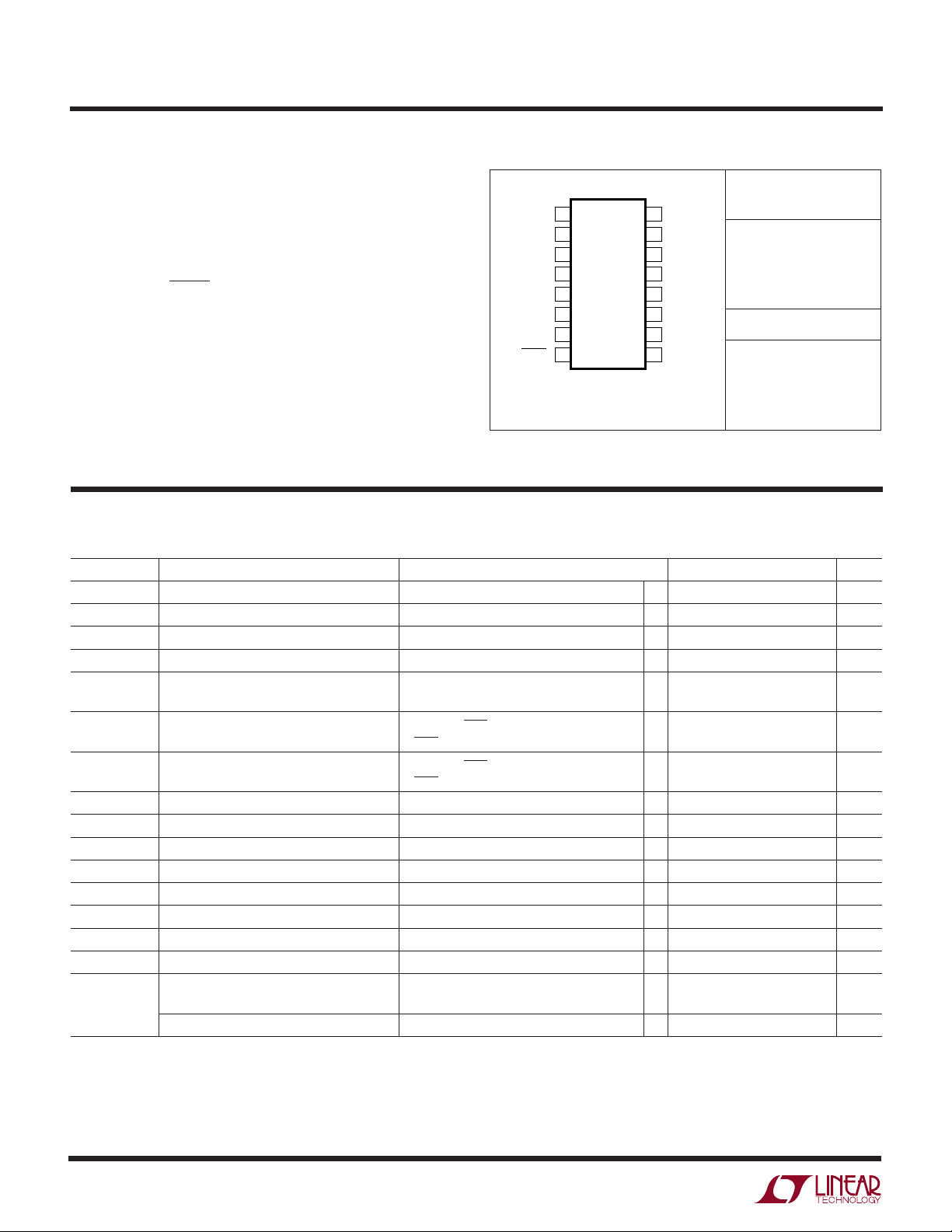

GN PACKAGE

16-LEAD PLASTIC SSOP

1

2

3

4

5

6

7

8

TOP VIEW

16

15

14

13

12

11

10

9

TG

PV

CC1

PGND

GND

R

–

FB

R

+

SHDN

BG

PV

CC2

V

CC

I

FB

I

MAX

FREQSET

COMP

SS

WWWU

ABSOLUTE AXI U RATI GS

PACKAGE/ORDER I FOR ATIO

UU

W

(Note 1)

Supply Voltage

VCC....................................................................... 9V

PV

................................................................ 14V

CC1,2

Input Voltage

IFB, I

............................................... –0.3V to 14V

MAX

ORDER PART

NUMBER

LTC3831EGN

R+, R–, FB, SHDN, FREQSET ..... –0.3V to VCC + 0.3V

Junction Temperature (Note 9)............................. 125°C

Operating Temperature Range (Note 4) .. – 40°C to 85°C

Storage Temperature Range ................. –65°C to 150°C

GN PART MARKING

3831

Lead Temperature (Soldering, 10 sec)..................300°C

T

= 125°C, θJA = 130°C/W

JMAX

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ELECTRICAL CHARACTERISTICS

range, otherwise specifications are at TA = 25°C. VCC, PV

The ● denotes specifications that apply over the full operating temperature

, PV

CC1

= 5V, VR+ = 2.5V, VR– = GND, unless otherwise noted. (Note 2)

CC2

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

CC

PV

CC

V

UVLO

V

FB

∆V

OUT

I

VCC

I

PVCC

∆f

OSC

V

SAWL

V

SAWH

V

COMPMAX

∆f

OSC

A

V

g

m

I

COMP

I

MAX

/∆I

FREQSET

Supply Voltage ● 358 V

PV

, PV

CC1

Voltage (Note 7) ● 3 13.2 V

CC2

Undervoltage Lockout Voltage 2.4 2.9 V

Feedback Voltage VR+ = 2.5V, VR– = 0V, V

Output Load Regulation I

Output Line Regulation V

Supply Current Figure 2, V

PVCC Supply Current Figure 2, V

= 0A to 10A (Note 6) 2 mV

OUT

= 4.75V to 5.25V 0.1 mV

CC

= V

SHDN

V

= 0V ● 110 µA

SHDN

V

= 0V ● 0.1 10 µA

SHDN

CC

= VCC (Note 3) ● 14 20 mA

SHDN

= 1.25V ● 1.231 1.25 1.269 V

COMP

● 0.7 1.6 mA

Internal Oscillator Frequency FREQSET Floating ● 160 200 240 kHz

V

at Minimum Duty Cycle 1.2 V

COMP

V

at Maximum Duty Cycle 2.2 V

COMP

Maximum V

COMP

VFB = 0V, PV

= 8V 2.85 V

CC1

Frequency Adjustment 10 kHz/µA

Error Amplifier Open-Loop DC Gain ● 46 55 dB

Error Amplifier Transconductance ● 520 650 780 µmho

Error Amplifier Output Sink/Source Current 100 µA

I

Sink Current V

MAX

I

Sink Current Tempco V

MAX

= V

IMAX

CC

= VCC (Note 6) 3300 ppm/°C

IMAX

91215 µA

● 41220 µA

3831f

2

LTC3831

ELECTRICAL CHARACTERISTICS

range, otherwise specifications are at TA = 25°C. VCC, PV

The ● denotes specifications that apply over the full operating temperature

, PV

CC1

= 5V, VR+ = 2.5V, VR– = GND, unless otherwise noted. (Note 2)

CC2

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

IH

V

IL

I

IN

I

SS

I

SSIL

+

R

tr, t

f

t

NOV

DC

MAX

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are referenced to ground unless otherwise

specified.

Note 3: Supply current in normal operation is dominated by the current

needed to charge and discharge the external FET gates. This will vary with

the LTC3831 operating frequency, operating voltage and the external FETs

used.

Note 4: The LTC3831EGN is guaranteed to meet performance

specifications from 0°C to 70°C. Specifications over the –40°C to 85°C

operating temperature range are assured by design, characterization and

correlation with statistical process controls.

SHDN Input High Voltage ● 2.4 V

SHDN Input Low Voltage ● 0.8 V

SHDN Input Current V

Soft-Start Source Current VSS = 0V, V

Maximum Soft-Start Sink Current V

Undercurrent Limit PV

SHDN

IMAX

CC1

= V

CC

IMAX

= VCC, V

= 8V

● 0.1 1 µA

= 0V, V

= 0V, VSS = VCC (Note 8), 1.6 mA

IFB

IFB

= V

CC

● –8 –12 –16 µA

R+ Input Resistance 49.5 kΩ

Driver Rise/Fall Time Figure 2, PV

Driver Nonoverlap Time Figure 2, PV

Maximum TG Duty Cycle Figure 2, VFB = 0V (Note 5), PV

CC1

CC1

= PV

= 5V (Note 5) ● 80 250 ns

CC2

= PV

= 5V (Note 5) ● 25 120 250 ns

CC2

= 8V ● 91 95 %

CC1

Note 5: Rise and fall times are measured using 10% and 90% levels. Duty

cycle and nonoverlap times are measured using 50% levels.

Note 6: Guaranteed by design, not subject to test.

Note 7: PV

must be higher than VCC by at least 2.5V for TG to operate

CC1

at 95% maximum duty cycle and for the current limit protection circuit to

be active.

Note 8: The current limiting amplifier can sink but cannot source current.

Under normal (not current limited) operation, the output current will be

zero.

Note 9: This IC includes overtemperature protection that is intended to protect

the device during momentary overload conditions. Junction temperature will

exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair

device reliability.

3831f

3

LTC3831

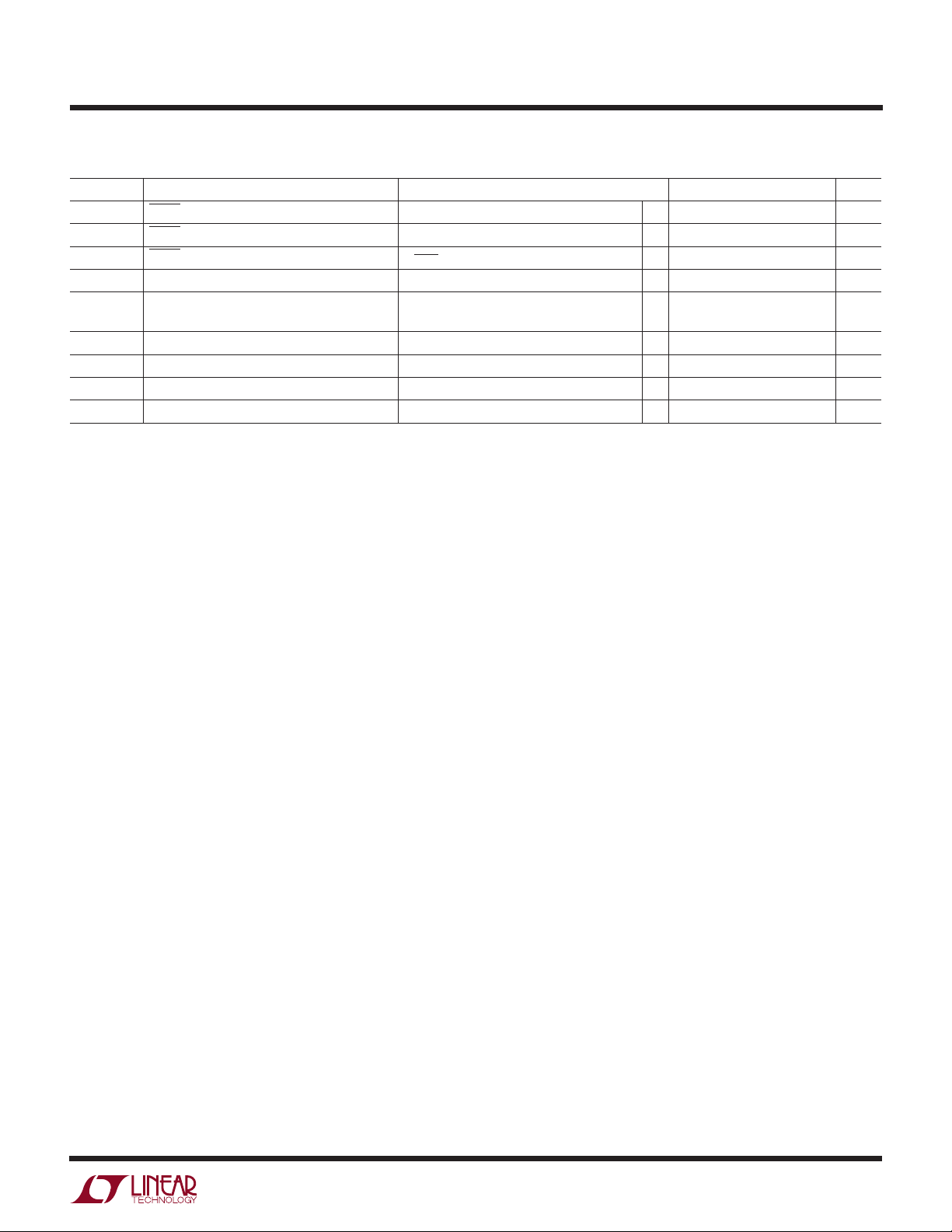

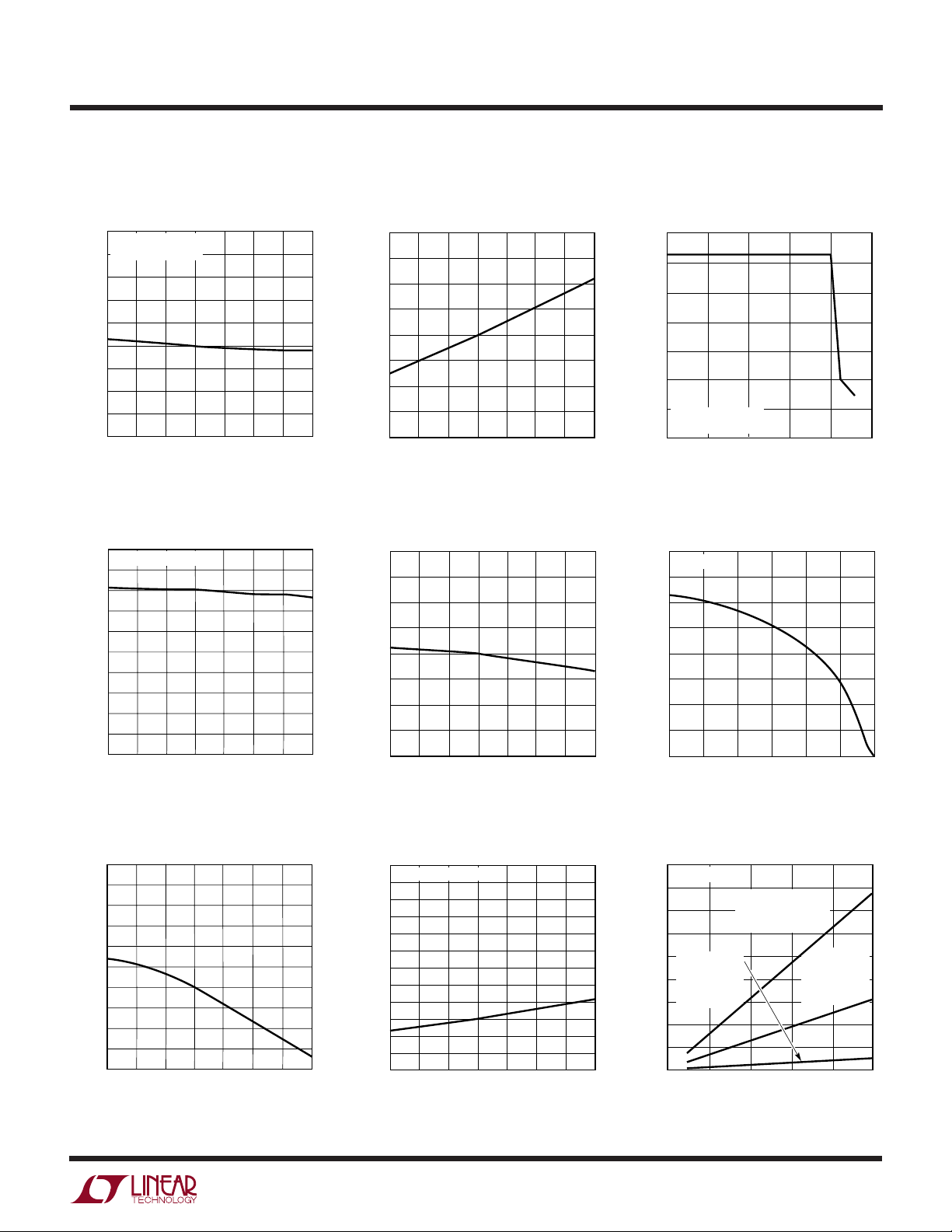

TEMPERATURE (˚C)

–50

ERROR AMPLIFIER TRANSCONDUCTANCE (µmho)

700

750

800

25 75

3831 G05

650

600

–25 0

50 100 125

550

500

TEMPERATURE (°C)

–50

40

ERROR AMPLIFIER OPEN-LOOP GAIN (dB)

45

50

55

60

–25 0 25 50

3831 G07

75 100 125

EXTERNAL SYNC FREQUENCY (kHz)

100

0.5

V

SAWH

– V

SAWL

(V)

0.6

0.8

0.9

1.0

1.5

1.2

200

300

3831 G10

0.7

1.3

1.4

1.1

400

500

TA = 25°C

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Load Regulation Line Regulation

1.270

TA = 25°C

REFER TO FIGURE 1

1.265

NEGATIVE OUTPUT CURRENT

INDICATES CURRENT SINKING

1.260

1.255

(V)

1.250

OUT

V

1.245

1.240

1.235

1.230

–4 –2 2

–6

0

OUTPUT CURRENT (A)

46

3831 G02

1.260

1.258

1.256

1.254

1.252

(V)

1.250

FB

V

1.248

1.246

1.244

1.242

1.240

TA = 25°C

3

4

5

SUPPLY VOLTAGE (V)

6

7

3831 G03

Error Amplifier Transconductance

vs Temperature

10

8

6

4

∆V

2

FB

(mV)

0

–2

–4

–6

–8

–10

8

Output Temperature Drift

1.270

REFER TO FIGURE 1

OUTPUT = NO LOAD

1.265

1.260

1.255

(V)

1.250

OUT

V

1.245

1.240

1.235

1.230

–25 0 50

–50

TEMPERATURE (°C)

Oscillator Frequency

vs Temperature

250

FREQSET FLOATING

240

230

220

210

200

190

180

OSCILLATOR FREQUENCY (kHz)

170

160

–50

4

0

–25

TEMPERATURE (°C)

25

25 125

50

75 100

3831 G04

75 100

3831 G08

Error Amplifier Sink/Source

Current vs Temperature

∆V

OUT

(mV)

200

180

160

140

120

100

80

60

40

ERROR AMPLIFIER SINK/SOURCE CURRENT (µA)

–50

20

15

10

5

0

–5

–10

–15

–20

Oscillator Frequency

vs FREQSET Input Current

600

500

400

300

200

OSCILLATOR FREQUENCY (kHz)

100

0

–40

–25 0 50

–30

FREQSET INPUT CURRENT (µA)

25

TEMPERATURE (°C)

–20 –10 0

75 100 125

3831 G06

TA = 25°C

10 20

3831 G09

Error Amplifier Open-Loop Gain

vs Temperature

Oscillator (V

SAWH

– V

SAWL

)

vs External Sync Frequency

3831f

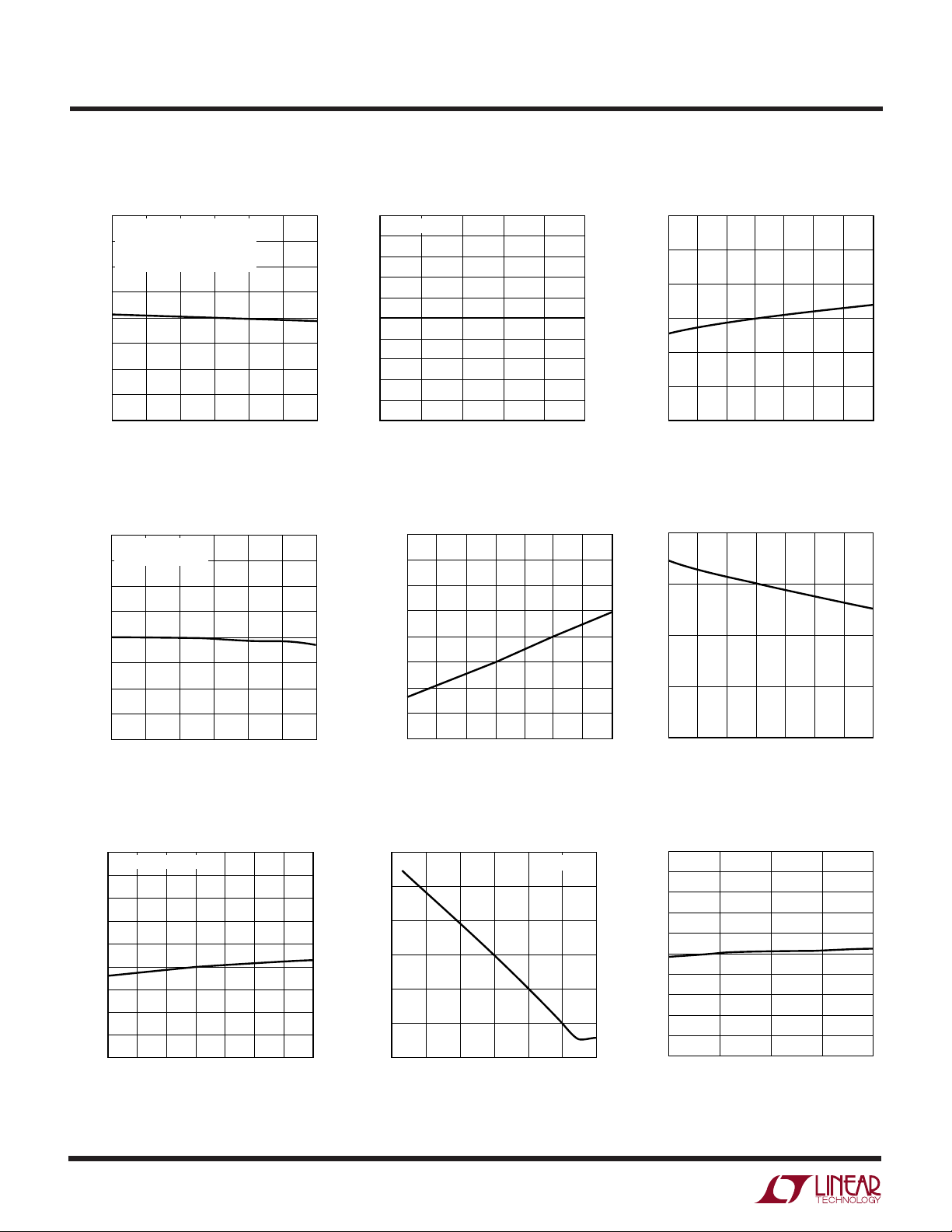

UW

OUTPUT CURRENT (A)

0

1.4

1.2

1.0

0.8

0.6

0.4

0.2

0

610

3831 G13

24

8

OUTPUT VOLTAGE (V)

TA = 25°C

REFER TO FIGURE 1

TYPICAL PERFOR A CE CHARACTERISTICS

LTC3831

Maximum TG Duty Cycle

vs Temperature

100

VFB = 0V

REFER TO FIGURE 3

99

98

97

96

95

94

93

MAXIMUM G1 DUTY CYCLE (%)

92

91

–50

0

–25

TEMPERATURE (°C)

25 125

50

Output Current Limit Threshold

vs Temperature

10

REFER TO FIGURE 1

9

8

7

6

5

4

3

OUTPUT CURRENT LIMIT (A)

2

1

0

–50

–25

0

TEMPERATURE (°C)

50

25

75 100

75

100

3831 G11

3831 G14

125

I

Sink Current

MAX

vs Temperature Output Overcurrent Protection

20

18

16

14

12

10

SINK CURRENT (µA)

MAX

8

I

6

4

–25 0 50

–50

25

TEMPERATURE (°C)

Soft-Start Source Current

vs Temperature

–8

–9

–10

–11

–12

–13

–14

–15

SOFT-START SOURCE CURRENT (µA)

–16

–25 0 50

–50

25

TEMPERATURE (°C)

75 100 125

3831 G12

75 100 125

3831 G15

Soft-Start Sink Current

vs (V

– V

IFB

2.00

TA = 25°C

1.75

1.50

1.25

1.00

0.75

0.50

SOFT-START SINK CURRENT (mA)

0.25

0

–125 –100 –50

–150

IMAX

V

IFB

– V

)

–75

IMAX

(mV)

–25

0

3831 G16

3.0

2.9

2.8

2.7

2.6

2.5

2.4

2.3

2.2

2.1

2.0

–50

UNDERVOLTAGE LOCKOUT THRESHOLD VOLTAGE (V)

Undervoltage Lockout Threshold

Voltage vs Temperature

50

25

0

–25

TEMPERATURE (°C)

75

100

3831 G17

125

VCC Operating Supply Current

vs Temperature

1.6

FREQSET FLOATING

1.5

1.4

1.3

1.2

1.1

1.0

0.9

0.8

0.7

0.6

OPERATING SUPPLY CURRENT (mA)

CC

0.5

V

0.4

–50

0

–25

TEMPERATURE (°C)

50

25

PVCC Supply Current

vs Oscillator Frequency

90

TA = 25°C

80

70

60

50

TG AND BG

40

WITH 1000pF,

PV

30

SUPPLY CURRENT (mA)

CC

20

PV

10

100

125

3831 G18

75

0

0

TG AND BG LOADED

WITH 6800pF,

= 12V

PV

CC1,2

TG AND BG

LOADED

= 5V

CC1,2

100 300

200

OSCILLATOR FREQUENCY (kHz)

LOADED

WITH 6800pF,

PV

CC1,2

400

= 5V

500

3831 G19

3831f

5

LTC3831

UW

TYPICAL PERFOR A CE CHARACTERISTICS

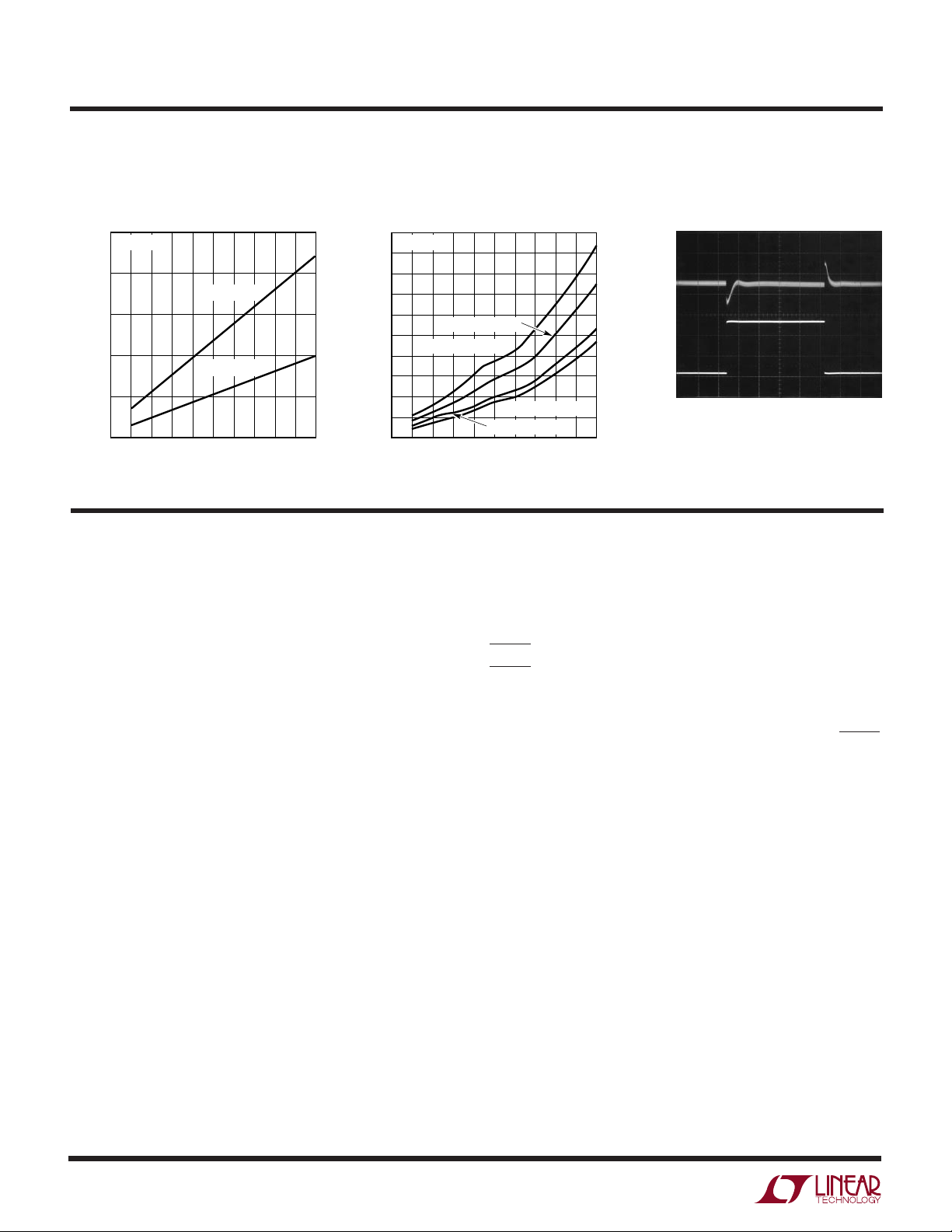

PVCC Supply Current

vs Gate Capacitance

50

TA = 25°C

40

30

20

SUPPLY CURRENT (mA)

CC

10

PV

0

123

0

GATE CAPACITANCE AT TG AND BG (nF)

45

U

PV

= 12V

CC1,2

PV

= 5V

CC1,2

67 9

8

3831 G20

UU

10

TG Rise/Fall Time

vs Gate Capacitance Transient Response

200

TA = 25°C

180

160

140

120

100

80

60

TG RISE/FALL TIME (ns)

40

20

0

0

tf AT PV

AT PV

t

r

CC1,2

21

GATE CAPACITANCE AT TG AND BG (nF)

PI FU CTIO S

TG ( Pin 1): Top Driver Output. Connect this pin to the gate

of the upper N-channel MOSFET, Q1. This output swings

from PGND to PV

shutdown mode.

PV

(Pin 2): Power Supply Input for TG. Connect this pin

CC1

to a potential of at least VIN + V

can be generated using an external supply or a simple

charge pump connected to the switching node between

the upper MOSFET and the lower MOSFET.

PGND (Pin 3): Power Ground. Both drivers return to this

pin. Connect this pin to a low impedance ground in close

proximity to the source of Q2. Refer to the Layout Consideration section for more details on PCB layout techniques.

GND (Pin 4): Signal Ground. All low power internal circuitry returns to this pin. To minimize regulation errors

due to ground currents, connect GND to PGND right at the

LTC3831.

R–, R+ (Pins 5, 7): These two pins connect to the internal

resistor divider that generate the internal ratiometric reference for the error amplifier. The reference voltage is set

at 0.5 • (VR+ – VR–).

FB (Pin 6): Feedback Voltage. FB senses the regulated

output voltage either directly or through an external resistor divider. The FB pin is servoed to the ratiometric

. It remains low if BG is high or during

CC1

GS(ON)(Q1)

. This potential

V

OUT

50mV/DIV

= 5V

43

CC1,2

= 5V

AT PV

t

r

5

tf AT PV

67 9

CC1,2

CC1,2

= 12V

= 12V

8

10

3831 G21

I

LOAD

2A/DIV

50µs/DIV

3831 G22.tif

reference under closed-loop conditions. The LTC3831 can

operate with a minimum VFB of 1.1V and maximum VFB of

(VCC – 1.75V).

SHDN (Pin 8): Shutdown. A TTL compatible low level at

SHDN for longer than 100µs puts the LTC3831 into

shutdown mode. In shutdown, TG and BG go low, all

internal circuits are disabled and the quiescent current

drops to 10µA max. A TTL compatible high level at SHDN

allows the part to operate normally. This pin also double as

an external clock input to synchronize the internal oscillator with an external clock.

SS (Pin 9): Soft-Start. Connect this pin to an external

capacitor, CSS, to implement a soft-start function. If the

LTC3831 goes into current limit, CSS is discharged to

reduce the duty cycle. CSS must be selected such that

during power-up, the current through Q1 will not exceed

the current limit level.

COMP (Pin 10): External Compensation. This pin internally connects to the output of the error amplifier and input

of the PWM comparator. Use a RC + C network at this pin

to compensate the feedback loop to provide optimum

transient response.

3831f

6

LTC3831

U

UU

PI FU CTIO S

FREQSET (Pin 11): Frequency Set. Use this pin to adjust

the free-running frequency of the internal oscillator. With

the pin floating, the oscillator runs at about 200kHz. A

resistor from FREQSET to ground speeds up the oscillator;

a resistor to VCC slows it down.

I

(Pin 12): Current Limit Threshold Set. I

MAX

threshold for the internal current limit comparator. If I

drops below I

current limit. I

Connect this pin to the main V

with TG on, the LTC3831 goes into

MAX

has an internal 12µA pull-down to GND.

MAX

supply at the drain of Q1,

IN

through an external resistor to set the current limit threshold. Connect a 0.1µF decoupling capacitor across this

resistor to filter switching noise.

IFB (Pin 13): Current Limit Sense. Connect this pin to the

switching node at the source of Q1 and the drain of Q2

through a 1k resistor. The 1k resistor is required to prevent

MAX

sets the

FB

voltage transients from damaging IFB.This pin is used for

sensing the voltage drop across the upper N-channel

MOSFET, Q1.

VCC (Pin 14): Power Supply Input. All low power internal

circuits draw their supply from this pin. This pin requires

a 4.7µF bypass capacitor to GND.

PV

(Pin 15): Power Supply Input for BG. Connect this

CC2

pin to the main high power supply.

BG (Pin 16): Bottom Driver Output . Connect this pin to the

gate of the lower N-channel MOSFET, Q2. This output

swings from PGND to PV

. It remains low when TG is

CC2

high or during shutdown mode. To prevent output undershoot during a soft-start cycle, BG is held low until TG first

goes high (FFBG in the Block Diagram).

BLOCK DIAGRA

SHDN

FREQSET

COMP

12µA

SS

Q

C

W

100µs DELAY

INTERNAL

OSCILLATOR

QSS

+

V

REF

2.2V

1.2V

LOGIC AND

THERMAL SHUTDOWN

–

PWM

+

–

CC

DISABLE

I

LIM

POWER DOWN

–

V

– 3% V

REF

–

+

+

12µA

DISABLE GATE DRIVE

MAXMINERR

–

+ 3%

REF

I

FB

I

MAX

+

V

–

POR

+

PV

CC1

V

+ 2.5V

CC1

S

Q

R

Q

FFBG

S ENABLE

Q

R

BG

V

CC

PV

CC1

TG

PV

CC2

BG

PGND

FB

+

R

24k

V

+ 3%

REF

750Ω

V

REF

750Ω

V

– 3%

REF

24k

3830 BD

R

GND

–

3831f

7

LTC3831

TEST CIRCUITS

PV

CC

V

SHDNVCC

CC

I

LTC3831

MAX

PV

CC2PVCC1

GND

Figure 2

V

COMP

NC

NC

V

2.5V

SHDN V

SS

FREQSET

FB

FB

COMP

+

R

–

R

WUUU

APPLICATIO S I FOR ATIO

OVERVIEW

The LTC3831 is a voltage mode feedback, synchronous

switching regulator controller (see Block Diagram) designed for use in high to medium power, DDR memory

termination. It includes an onboard PWM generator, a

ratiometric reference, two high power MOSFET gate drivers and all necessary feedback and control circuitry to

form a complete switching regulator circuit. The PWM

loop nominally runs at 200kHz.

The LTC3831 is designed to generate an output voltage that

tracks at 1/2 of the external voltage connected between the

R+ and R– pins. The LTC3831 can be used to generate the

termination voltage, VTT, for interface like the SSTL_2 where

VTT is a ratio of the interface supply voltage, V

requirement in the SSTL_2 interface standard for VTT to

track the interface supply voltage to improve noise immunity. Using the LTC3831 to supply the interface termination voltage allows large current sourcing and sinking

through the termination resistors during bus transitions.

DDQ

. It is a

I

FB

PGND

+

10µF

TG

6800pF

BG

6800pF

3831 F02

0.1µF

TG RISE/FALL

BG RISE/FALL

THEORY OF OPERATION

Primary Feedback Loop

The LTC3831 senses the output voltage of the circuit

through the FB pin and feeds this voltage back to the

internal transconductance error amplifier, ERR. The error

amplifier compares the output voltage to the internal

ratiometric reference, V

the PWM comparator. V

, and outputs an error signal to

REF

is set to 0.5 multiplied by the

REF

voltage difference between the R+ and R– pins, using an

internal resistor divider.

This error signal is compared with a fixed frequency ramp

waveform, from the internal oscillator, to generate a pulse

width modulated signal. This PWM signal drives the

external MOSFETs through the TG and BG pins. The

resulting chopped waveform is filtered by LO and C

OUT

which closes the loop. Loop compensation is achieved

with an external compensation network at the COMP pin,

the output node of the error amplifier.

The LTC3831 includes a current limit sensing circuit that

uses the topside external N-channel power MOSFET as a

current sensing element, eliminating the need for an

external sense resistor. Also included is an internal softstart feature that requires only a single external capacitor

to operate. In addition, the part features an adjustable

oscillator which can free run or synchronize to an external

signal with frequencies from 100kHz to 500kHz, allowing

added flexibility in external component selection.

8

MIN, MAX Feedback Loops

Two additional comparators in the feedback loop provide

high speed output voltage correction in situations where

the error amplifier may not respond quickly enough. MIN

compares the feedback signal to a voltage 3% below V

REF

.

If the signal is below the comparator threshold, the MIN

comparator overrides the error amplifier and forces the

loop to maximum duty cycle, >91%. Similarly, the MAX

3831f

WUUU

=

()()

()

()()

VV V

fLV

IN OUT OUT

OSC O IN

–

APPLICATIO S I FOR ATIO

LTC3831

comparator forces the output to 0% duty cycle if the

feedback signal is greater than 3% above V

. To prevent

REF

these two comparators from triggering due to noise, the

MIN and MAX comparators’ response times are deliberately delayed by two to three microseconds. These two

comparators help prevent extreme output perturbations

with fast output load current transients, while allowing the

main feedback loop to be optimally compensated for

stability.

Thermal Shutdown

The LTC3831 has a thermal protection circuit that disables

both gate drivers if activated. If the chip junction temperature reaches 150°C, both TG and BG are pulled low. TG and

BG remain low until the junction temperature drops below

125°C, after which, the chip resumes normal operation.

Soft-Start and Current Limit

The LTC3831 includes a soft-start circuit that is used for

start-up and current limit operation. The SS pin requires

an external capacitor, CSS, to GND with the value determined by the required soft-start time. An internal 12µA

current source is included to charge CSS. During powerup, the COMP pin is clamped to a diode drop (B-E junction

of QSS in the Block Diagram) above the voltage at the SS

pin. This prevents the error amplifier from forcing the loop

to maximum duty cycle. The LTC3831 operates at low duty

cycle as the SS pin rises above 0.6V (V

≈ 1.2V). As SS

COMP

continues to rise, QSS turns off and the error amplifier

takes over to regulate the output. The MIN comparator is

disabled during soft-start to prevent it from overriding the

soft-start function.

The LTC3831 includes yet another feedback loop to control operation in current limit. Just before every falling

edge of TG, the current comparator, CC, samples and

holds the voltage drop measured across the external

upper MOSFET, Q1, at the IFB pin. CC compares the voltage

at IFB to the voltage at the I

pin. As the peak current

MAX

rises, the measured voltage across Q1 increases due to the

drop across the R

drops below I

MAX

, indicating that Q1’s drain current has

of Q1. When the voltage at I

DS(ON)

FB

exceeded the maximum level, CC starts to pull current out

of CSS, cutting the duty cycle and controlling the output

current level. The CC comparator pulls current out of the

SS pin in proportion to the voltage difference between I

and I

. Under minor overload conditions, the SS pin

MAX

FB

falls gradually, creating a time delay before current limit

takes effect. Very short, mild overloads may not affect the

output voltage at all. More significant overload conditions

allow the SS pin to reach a steady state, and the output

remains at a reduced voltage until the overload is removed. Serious overloads generate a large overdrive at

CC, allowing it to pull SS down quickly and preventing

damage to the output components. By using the R

DS(ON)

of Q1 to measure the output current, the current limiting

circuit eliminates an expensive discrete sense resistor that

would otherwise be required. This helps minimize the

number of components in the high current path.

The current limit threshold can be set by connecting an

external resistor R

supply at the drain of Q1. The value of R

IMAX

from the I

pin to the main V

MAX

is determined

IMAX

IN

by:

R

IMAX

= (I

LMAX

)(R

DS(ON)Q1

)/I

IMAX

where:

I

= I

LMAX

I

= Maximum load current

LOAD

I

RIPPLE

LOAD

+ (I

RIPPLE

/2)

= Inductor ripple current

f

= LTC3831 oscillator frequency = 200kHz

OSC

LO = Inductor value

R

I

IMAX

The R

DS(ON)Q1

DS(ON)

= On-resistance of Q1 at I

= Internal 12µA sink current at I

LMAX

MAX

of Q1 usually increases with temperature. To

keep the current limit threshold constant, the internal

12µA sink current at I

is designed with a positive

MAX

temperature coefficient to provide first order correction

for the temperature coefficient of R

DS(ON)Q1

.

In order for the current limit circuit to operate properly and

to obtain a reasonably accurate current limit threshold, the

3831f

9

LTC3831

WUUU

APPLICATIO S I FOR ATIO

I

and I

IMAX

source pins. In addition, connect a 0.1µF decoupling

capacitor across R

wise, noise spikes or ringing at Q1’s source can cause the

actual current limit to be greater than the desired current

limit set point. Due to switching noise and variation of

R

DS(ON)

accurate. The current limiting circuitry is primarily meant

to prevent damage to the power supply circuitry during

fault conditions. The exact current level where the limiting

circuit begins to take effect will vary from unit to unit as the

R

DS(ON)

±40% and with ±25% variation on the LTC3831’s I

current, this can give a ±65% variation on the current limit

threshold.

The R

DS(ON)

low. This occurs during power up, when PV

up. To prevent the high R

limit, the LTC3831 disables the current limit circuit if

PV

CC1

operation of the current limit circuit, PV

least 2.5V above VCC when TG is high. PV

when TG is low, allowing the use of an external charge

pump to power PV

LTC3831

Oscillator Frequency

The LTC3831 includes an onboard current controlled

oscillator that typically free-runs at 200kHz. The oscillator

frequency can be adjusted by forcing current into or out of

the FREQSET pin. With the pin floating, the oscillator runs

at about 200kHz. Every additional 1µA of current into/out

of the FREQSET pin decreases/increases the frequency by

pins must be Kelvin sensed at Q1’s drain and

FB

to filter switching noise. Other-

IMAX

, the actual current limit trip point is not highly

of Q1 varies. Typically, R

varies as much as

DS(ON)

MAX

is high if the VGS applied to the MOSFET is

is ramping

CC1

from activating the current

DS(ON)

is less than 2.5V above VCC. To ensure proper

must be at

CC1

can go low

CC1

.

CC1

V

IN

R

IMAX

+

CC

–

12µA

Figure 3. Current Limit Setting

I

12

MAX

I

FB

13

0.1µF

TG

1k

BG

Q1

Q2

+

C

IN

L

O

V

OUT

+

C

OUT

3831 F03

10kHz. The pin is internally servoed to 1.265V, connecting

a 50k resistor from FREQSET to ground forces 25µA out of

the pin, causing the internal oscillator to run at approximately 450kHz. Forcing an external 10µA current into

FREQSET cuts the internal frequency to 100kHz. An internal clamp prevents the oscillator from running slower than

about 50kHz. Tying FREQSET to VCC forces the chip to run

at this minimum speed.

Shutdown

The LTC3831 includes a low power shutdown mode,

controlled by the logic at the SHDN pin. A high at SHDN

allows the part to operate normally. A low level at SHDN for

more than 100µs forces the LTC3831 into shutdown

mode. In this mode, all internal switching stops, the COMP

and SS pins pull to ground and Q1 and Q2 turn off. The

LTC3831 supply current drops to <10µA, although off-

state leakage in the external MOSFETs may cause the total

VIN current to be somewhat higher, especially at elevated

temperatures. If SHDN returns high, the LTC3831 reruns

a soft-start cycle and resumes normal operation.

External Clock Synchronization

The LTC3831 SHDN pin doubles as an external clock input

for applications that require a synchronized clock. An

internal circuit forces the LTC3831 into external synchronization mode if a negative transition at the SHDN pin is

detected. In this mode, every negative transition on the

SHDN pin resets the internal oscillator and pulls the ramp

signal low. This forces the LTC3831 internal oscillator to

lock to the external clock frequency.

The LTC3831 internal oscillator can be externally synchronized from 100kHz to 500kHz. Frequencies above 300kHz

can cause a decrease in the maximum obtainable duty

cycle as rise/fall time and propagation delay take up a

larger percentage of the switch cycle. The low period of

this clock signal must not be >100µs or else the LTC3831

enters into the shutdown mode.

Figure 4 describes the operation of the external synchronization function. A negative transition at the SHDN pin

forces the internal ramp signal low to restart a new PWM

cycle. Notice that the ramp amplitude is lowered as the

external clock frequency goes higher. The effect of this

3831f

10

WUUU

APPLICATIO S I FOR ATIO

SHDN

TRADITIONAL

SYNC METHOD

WITH EARLY

RAMP

TERMINATION

RAMP AMPLITUDE

LTC3831

KEEPS RAMP

AMPLITUDE

CONSTANT

UNDER SYNC

200kHz

FREE RUNNING

RAMP SIGNAL

ADJUSTED

RAMP SIGNAL

WITH EXT SYNC

3831 F04

LTC3831

Gate drive for the top N-channel MOSFET Q1 is supplied

from PV

power supply input) by at least one power MOSFET

V

GS(ON)

allows PV

to 14V maximum. This higher voltage can be supplied with

a separate supply, or it can be generated using a charge

pump.

Gate drive for the bottom MOSFET Q2 is provided through

PV

CC2

MOSFET V

driven from the same supply/charge pump for the PV

or it can be connected to a lower supply to improve

efficiency.

Figure 6 shows a doubling charge pump circuit that can be

used to provide 2VIN gate drive for Q1. The charge pump

consists of a Schottky diode from VIN to PV

capacitor from PV

. This supply must be above VIN (the main

CC1

for efficient operation. An internal level shifter

to operate at voltages above V

CC1

and VIN, up

CC

. This supply only need to be above the power

for efficient operation. PV

GS(ON)

to the switching node at the drain of

CC1

can also be

CC2

and a 0.1µF

CC1

CC1

,

Figure 4. External Synchronization Operation

decrease in ramp amplitude increases the open-loop gain

of the controller feedback loop. As a result, the loop

crossover frequency increases and it may cause the feedback loop to be unstable if the phase margin is insufficient.

To overcome this problem, the LTC3831 monitors the

peak voltage of the ramp signal and adjust the oscillator

charging current to maintain a constant ramp peak.

Input Supply Considerations/Charge Pump

The LTC3831 requires four supply voltages to operate: V

for the main power input, PV

CC1

and PV

for MOSFET

CC2

IN

gate drive and a clean, low ripple VCC for the LTC3831

internal circuitry (Figure 5).

In many applications, V

can be powered from V

CC

IN

through an RC filter. This supply can be as low as 3V. The

low quiescent current (typically 800µA) allows the use of

relatively large filter resistors and correspondingly small

filter capacitors. 100Ω and 4.7µF usually provide ad-

equate filtering for VCC. For best performance, connect the

4.7µF bypass capacitor as close to the LTC3831 VCC pin as

possible.

INTERNAL

CIRCUITRY

LTC3831

OPTIONAL

USE FOR V

D

Z

12V

1N5242

V

CC

PV

CC2

PV

CC1

Figure 5. Supplies Input

≥ 7V

IN

CC2

PV

CC1

TG

BG

PV

LTC3831

Figure 6. Doubling Charge Pump

V

TG

BG

MBR0530T1

0.1µF

IN

Q1

L

O

Q2

V

IN

Q1

L

O

Q2 C

V

OUT

+

C

OUT

3831 F05

V

OUT

+

OUT

3831 F06a

3831f

11

LTC3831

WUUU

APPLICATIO S I FOR ATIO

Q2. This circuit provides 2VIN – VF to PV

while Q1 is ON

CC1

and VIN – VF while Q1 is OFF where VF is the forward voltage

of the Schottky diode. Ringing at the drain of Q2 can cause

transients above 2VIN at PV

12V zener diode should be included from PV

to prevent transients from damaging the circuitry at PV

; if VIN is higher than 7V, a

CC1

to PGND

CC1

CC1

or the gate of Q1.

For applications with a lower VIN supply, a tripling charge

pump circuit shown in Figure 7 can be used to provide 2V

IN

and 3VIN gate drive for the external top and bottom

MOSFETs respectively. This circuit provides 3VIN – 3VF to

PV

while Q1 is ON and 2VIN – 2VF to PV

CC1

where VF is

CC2

the forward voltage of the Schottky diode. The circuit

requires the use of Schottky diodes to minimize forward

drop across the diodes at start-up. The tripling charge

pump circuit can rectify any ringing at the drain of Q2 and

provide more than 3VIN at PV

be included from PV

to PGND to prevent transients

CC1

from damaging the circuitry at PV

The charge pump capacitors for PV

; a 12V zener diode should

CC1

or the gate of Q1.

CC1

refresh when the

CC1

BG pin goes high and the switch node is pulled low by Q2.

The BG on time becomes narrow when the LTC3831

operates at maximum duty cycle (95% typical) which can

occur if the input supply rises more slowly than the softstart capacitor or the input voltage droops during load

transients. If the BG on time gets so narrow that the switch

node fails to pull completely to ground, the charge pump

voltage may collapse or fail to start causing excessive

dissipation in external MOSFET Q1. This is most likely with

low VCC voltages and high switching frequencies, coupled

with large external MOSFETs that slow the BG and switch

node slew rates.

The LTC3831 overcomes this problem by sensing the

PV

voltage when TG is high. If PV

CC1

is less than 2.5V

CC1

above VCC, the maximum TG duty cycle is reduced to 70%

by clamping the COMP pin at 1.8V (QC in the Block

Diagram). This increases the BG on time and allows the

charge pump capacitors to be refreshed.

D

12V

1N5242

10µF

For applications using an external supply to power PV

Z

LTC3831

1N5817

1N5817

PV

PV

CC2

CC1

TG

BG

Figure 7. Tripling Charge Pump

1N5817

0.1µF

0.1µF

V

IN

Q1

L

O

Q2 C

V

OUT

+

OUT

3831 F07

,

CC1

this supply must also be higher than VCC by at least 2.5V

to ensure normal operation.

Connecting the Ratiometric Reference Input

The LTC3831 derives its ratiometric reference, V

REF

,

using an internal resistor divider. The top and bottom of

the resistor divider is connected to the R+ and R– pins

respectively. This permits the output voltage to track at a

ratio of the differential voltage at R+ and R–.

The LTC3831 can operate with a minimum VFB of 1.1V and

maximum VFB of (VCC – 1.75V). With R– connected to

GND, this gives a V

3.5V). If V

+

is higher than the permitted input voltage,

R

+

input range of 2.2V to (2 • VCC –

R

increase the VCC voltage to raise the input range.

In a typical DDR memory termination application as shown

in Figure 1, R+ is connected to V

the interface, and R– to GND. The output voltage V

connected to the FB pin, so V

, the supply voltage of

DDQ

= 0.5 • V

TT

DDQ

.

TT

is

If a ratio greater than 0.5 is desired, it can be achieved

using an external resistor divider connected to VTT and FB

pin. Figure 8 shows an application that generates a VTT of

0.6 • V

DDQ

.

12

3831f

WUUU

APPLICATIO S I FOR ATIO

5V

1µF

0.01µF

130k

C

C

C

1500pF

V

SS

FREQSET

SHDN

COMP

0.1µF

+

4.7µF

SHDN

C1

33pF

R

15k

PV

CC

CC2

LTC3831

R

PV

CC1

TG

I

MAX

I

FB

BG

PGND

GND

R

FB

–

MBR0530T1

+

10k

C

C

Q1, Q2: SILICONIX Si4410DY

0.1µF

1k

: SANYO POSCAP 6TPB330M

IN

: SANYO POSCAP 4TPB470M

OUT

V

DDQ

2.5V

Q1 MBRS340T3

0.1µF

Q2

L

O

1.2µH

MBRS340T3

LTC3831

+

C

IN

330µF

×2

V

TT

1.5V

±6A

+

C

OUT

470µF

×3

2k

1%

10k

1%

3831 F08

Figure 8. Typical Application with VTT = 0.6 • V

Power MOSFETs

Two N-channel power MOSFETs are required for most

LTC3831 circuits. These should be selected based primarily on threshold voltage and on-resistance considerations.

Thermal dissipation is often a secondary concern in high

efficiency designs. The required MOSFET threshold should

be determined based on the available power supply voltages and/or the complexity of the gate drive charge pump

scheme. In 3.3V input designs where an auxiliary 12V

supply is available to power PV

MOSFETs with R

specified at VGS = 5V or 6V can be

DS(ON)

CC1

and PV

, standard

CC2

used with good results. The current drawn from this supply varies with the MOSFETs used and the LTC3831’s

operating frequency, but is generally less than 50mA.

LTC3831 applications that use 5V or lower VIN voltage and

doubling/tripling charge pumps to generate PV

PV

, do not provide enough gate drive voltage to fully

CC2

CC1

and

enhance standard power MOSFETs. Under this condition,

the effective MOSFET R

may be quite high, raising

DS(ON)

the dissipation in the FETs and reducing efficiency. Logiclevel FETs are the recommended choice for 5V or lower

voltage systems. Logic-level FETs can be fully enhanced

with a doubler/tripling charge pump and will operate at

maximum efficiency.

DDQ

After the MOSFET threshold voltage is selected, choose

the R

based on the input voltage, the output voltage,

DS(ON)

allowable power dissipation and maximum output current. In a typical LTC3831 circuit operating in continuous

mode, the average inductor current is equal to the output

load current. This current flows through either Q1 or Q2

with the power dissipation split up according to the duty

cycle:

V

DC Q

DC Q

The R

()

() –

DS(ON)

OUT

1

=

V

IN

V

21

==

OUTININ OUT

V

VV

–

V

IN

required for a given conduction loss can now

be calculated by rearranging the relation P = I2R.

P

MAX Q

() ()

R

DS ON Q

==

()

1

DC Q I

()•( )

P

R

DS ON Q

P

MAX

()

==

2

DC Q I

()•( )•(– )•( )

should be calculated based primarily on required

1

1

LOAD

MAX Q

() ()

2

2

LOAD

VP

•

IN MAX Q

2

VI

•( )

OUT LOAD

VP

IN MAX Q

2

VV I

IN OUT LOAD

1

2

2

2

efficiency or allowable thermal dissipation. A typical high

3831f

13

LTC3831

WUUU

APPLICATIO S I FOR ATIO

efficiency circuit designed for 2.5V input and 1.25V at 5A

output might allow no more than 3% efficiency loss at full

load for each MOSFET. Assuming roughly 90% efficiency

at this current level, this gives a P

MAX

value of:

(1.25V)(5A/0.9)(0.03) = 0.21W per FET

and a required R

(. )•(. )

R

DS ON Q

R

DS ON Q

==Ω

()

1

()

==Ω

2

( . – . )( )

Note that while the required R

of:

DS(ON)

25 021

VW

( . )( )

125 5

VA

(. )•(. )

25 021

VW

25 125 5

VVA

2

DS(ON)

.

0 017

.

0 017

2

values suggest large

MOSFETs, the power dissipation numbers are only 0.21W

per device or less; large TO-220 packages and heat sinks

are not necessarily required in high efficiency applications.

Siliconix Si4410DY or International Rectifier IRF7413 (both

in SO-8) or Siliconix SUD50N03-10 (TO-252) or ON Semiconductor MTD20N03HDL (DPAK) are small footprint

surface mount devices with R

values below 0.03Ω at

DS(ON)

5V of VGS that work well in LTC3831 circuits. Using a

higher P

value in the R

MAX

calculations generally

DS(ON)

decreases the MOSFET cost and the circuit efficiency and

increases the MOSFET heat sink requirements.

Table 1 highlights a variety of power MOSFETs that are for

use in LTC3831 applications.

Inductor Selection

The inductor is often the largest component in an LTC3831

design and must be chosen carefully. Choose the inductor

value and type based on output slew rate requirements. The

maximum rate of rise of inductor current is set by the

inductor’s value, the input-to-output voltage differential and

the LTC3831’s maximum duty cycle. In a typical 2.5V input

1.25V output application, the maximum rise time will be:

DC V V

•( – ) .

MAX IN OUT

LL

OO

=

1 138

A

s

µ

where LO is the inductor value in µH. With proper fre-

quency compensation, the combination of the inductor

and output capacitor values determine the transient recovery time. In general, a smaller value inductor improves

transient response at the expense of ripple and inductor

core saturation rating. A 2µH inductor has a 0.57A/µs rise

Table 1. Recommended MOSFETs for LTC3831 Applications

TYPICAL INPUT

R

PARTS AT 25°C (mΩ) RATED CURRENT (A) C

Siliconix SUD50N03-10 19 15 at 25°C 3200 1.8 175

TO-252 10 at 100°C

Siliconix Si4410DY 20 10 at 25°C 2700 150

SO-8 8 at 70°C

ON Semiconductor MTD20N03HDL 35 20 at 25°C 880 1.67 150

D PAK 16 at 100°C

Fairchild FDS6670A 8 13 at 25°C 3200 25 150

S0-8

Fairchild FDS6680 10 11.5 at 25°C 2070 25 150

SO-8

ON Semiconductor MTB75N03HDL 9 75 at 25°C 4025 1 150

DD PAK 59 at 100°C

IR IRL3103S 19 64 at 25°C 1600 1.4 175

DD PAK 45 at 100°C

IR IRLZ44 28 50 at 25°C 3300 1 175

TO-220 36 at 100°C

Fuji 2SK1388 37 35 at 25°C 1750 2.08 150

TO-220

Note: Please refer to the manufacturer’s data sheet for testing conditions and detailed information.

DS(ON)

CAPACITANCE

(pF) θJC (°C/W) T

ISS

JMAX

(°C)

3831f

14

WUUU

APPLICATIO S I FOR ATIO

LTC3831

time in this application, resulting in a 8.8µs delay in

responding to a 5A load current step. During this 8.8µs,

the difference between the inductor current and the output

current is made up by the output capacitor. This action

causes a temporary voltage droop at the output. To

minimize this effect, the inductor value should usually be

in the 1µH to 5µH range for most LTC3831 circuits. To

optimize performance, different combinations of input

and output voltages and expected loads may require

different inductor values.

Once the required value is known, the inductor core type

can be chosen based on peak current and efficiency

requirements. Peak current in the inductor will be equal to

the maximum output load current plus half of the peak-topeak inductor ripple current. Ripple current is set by the

inductor value, the input and output voltage and the

operating frequency. The ripple current is approximately

equal to:

VV V

−()•()

I

RIPPLE

IN OUT OUT

=

fLV

••

OSC O IN

Input and Output Capacitors

A typical LTC3831 design places significant demands on

both the input and the output capacitors. During normal

steady load operation, a buck converter like the LTC3831

draws square waves of current from the input supply at the

switching frequency. The peak current value is equal to the

output load current plus 1/2 the peak-to-peak ripple current. Most of this current is supplied by the input bypass

capacitor. The resulting RMS current flow in the input

capacitor heats it and causes premature capacitor failure

in extreme cases. Maximum RMS current occurs with

50% PWM duty cycle, giving an RMS current value equal

to I

ripple current rating must be used to ensure reliable

operation. Note that capacitor manufacturers’ ripple current ratings are often based on only 2000 hours (3 months)

lifetime at rated temperature. Further derating of the input

capacitor ripple current beyond the manufacturer’s specification is recommended to extend the useful life of the

circuit. Lower operating temperature has the largest effect

on capacitor longevity.

/2. A low ESR input capacitor with an adequate

OUT

f

= LTC3831 oscillator frequency = 200kHz

OSC

LO = Inductor value

Solving this equation with our typical 2.5V to 1.25V

application with 2µH inductor, we get:

(. – . )• .

25 125 125

VVV

200 2 2 5

Peak inductor current at 5A load:

5A + (1.56A/2) = 5.78A

The ripple current should generally be between 10% and

40% of the output current. The inductor must be able to

withstand this peak current without saturating, and the

copper resistance in the winding should be kept as low as

possible to minimize resistive power loss. Note that in

circuits not employing the current limit function, the

current in the inductor may rise above this maximum

under short circuit or fault conditions; the inductor should

be sized accordingly to withstand this additional current.

Inductors with gradual saturation characteristics are often

the best choice.

••.

kHz H V

µ

=

.

156

A

P

-P

The output capacitor in a buck converter under steadystate conditions sees much less ripple current than the

input capacitor. Peak-to-peak current is equal to inductor

ripple current, usually 10% to 40% of the total load

current. Output capacitor duty places a premium not on

power dissipation but on ESR. During an output load

transient, the output capacitor must supply all of the

additional load current demanded by the load until the

LTC3831 adjusts the inductor current to the new value.

ESR in the output capacitor results in a step in the output

voltage equal to the ESR value multiplied by the change in

load current. A 5A load step with a 0.05Ω ESR output

capacitor results in a 250mV output voltage shift; this is

20% of the output voltage for a 1.25V supply! Because of

the strong relationship between output capacitor ESR and

output load transient response, choose the output capacitor for ESR, not for capacitance value. A capacitor with

suitable ESR will usually have a larger capacitance value

than is needed to control steady-state output ripple.

Electrolytic capacitors, such as the Sanyo MV-WX series,

rated for use in switching power supplies with specified

ripple current ratings and ESR, can be used effectively in

3831f

15

LTC3831

LOOP GAIN

3830 F10b

f

Z

f

LC

f

ESR

f

CO

f

P

FREQUENCY

20dB/DECADE

f

SW

= LTC3831 SWITCHING

FREQUENCY

f

CO

= CLOSED-LOOP CROSSOVER

FREQUENCY

WUUU

APPLICATIO S I FOR ATIO

LTC3831 applications. OS-CON electrolytic capacitors

from Sanyo and other manufacturers give excellent performance and have a very high performance/size ratio for

electrolytic capacitors. Surface mount applications can

use either electrolytic or dry tantalum capacitors. Tantalum capacitors must be surge tested and specified for use

in switching power supplies. Low cost, generic tantalums

are known to have very short lives followed by explosive

deaths in switching power supply applications. Other

capacitor series that can be used include Sanyo POSCAPs

and the Panasonic SP line.

A common way to lower ESR and raise ripple current

capability is to parallel several capacitors. A typical LTC3831

application might exhibit 5A input ripple current. Sanyo

OS-CON capacitors, part number 10SA220M (220µF/10V),

feature 2.3A allowable ripple current at 85°C; three in

parallel at the input (to withstand the input ripple current)

meet the above requirements. Similarly, Sanyo POSCAP

4TPB470M (470µF/4V) capacitors have a maximum rated

ESR of 0.04Ω, three in parallel lower the net output

capacitor ESR to 0.013Ω.

Feedback Loop Compensation

The LTC3831 voltage feedback loop is compensated at the

COMP pin, which is the output node of the error amplifier.

The feedback loop is generally compensated with an RC +

C network from COMP to GND as shown in Figure 9a.

frequency for the overall open-loop transfer function. The

zero and pole from the compensation network are:

fZ = 1/[2π(RC)(CC)] and

fP = 1/[2π(RC)(C1)] respectively.

Figure 9b shows the Bode plot of the overall transfer

function.

Although a mathematical approach to frequency compensation can be used, the added complication of input and/or

output filters, unknown capacitor ESR, and gross operating point changes with input voltage, load current variations, all suggest a more practical empirical method. This

can be done by injecting a transient current at the load and

using an RC network box to iterate toward the final values,

or by obtaining the optimum loop response using a

network analyzer to find the actual loop poles and zeros.

LTC3831

ERR

–

+

V

COMP

10

R

C

C

Figure 9a. Compensation Pin Hook-Up

C1

C

REF

V

3831 F09a

FB

V

6

TT

Loop stability is affected by the values of the inductor, the

output capacitor, the output capacitor ESR, the error

amplifier transconductance and the error amplifier compensation network. The inductor and the output capacitor

create a double pole at the frequency:

fLC

=π

12/ ( )( )

LC O OUT

[]

The ESR of the output capacitor and the output capacitor

value form a zero at the frequency:

f ESR C

=π

12/ ( )( )

ESR OUT

[]

The compensation network used with the error amplifier

must provide enough phase margin at the 0dB crossover

16

Figure 9b. Bode Plot of the LTC3831 Overall Transfer Function

3831f

WUUU

APPLICATIO S I FOR ATIO

LTC3831

Table 2 shows the suggested compensation component

value for 2.5V to 1.25V applications based on the 470µF

Sanyo POSCAP 4TPB470M output capacitors.

Table 3 shows the suggested compensation component

values for 2.5V to 1.25V applications based on 1500µF

Sanyo MV-WX output capacitors.

Table 2. Recommended Compensation Network for 2.5V to

1.25V Applications Using Multiple Paralleled 470µF Sanyo

POSCAP 4TPB470M Output Capacitors

L1 (µH) C

1.2 1410 6.8 3.3 33

1.2 2820 15 3.3 33

1.2 4700 22 1.5 33

2.4 1410 15 10 33

2.4 2820 36 3.3 10

2.4 4700 47 4.7 10

4.7 1410 33 10 10

4.7 2820 68 22 10

4.7 4700 120 10 10

(µF) RC (kΩ)C

OUT

(nF) C1 (pF)

C

LAYOUT CONSIDERATIONS

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation of the

LTC3831. These items are also illustrated graphically in

the layout diagram of Figure 10. The thicker lines show the

high current paths. Note that at 5A current levels or above,

Table 3. Recommended Compensation Network for 2.5V to

1.25V Applications Using Multiple Paralleled 1500µF Sanyo

MV-WX Output Capacitors

L1 (µH) C

1.2 4500 20 1.5 120

1.2 6000 27 1 82

1.2 9000 43 0.47 56

2.4 4500 51 1 56

2.4 6000 62 1 33

2.4 9000 82 0.47 27

4.7 4500 82 3.3 33

4.7 6000 100 1 15

4.7 9000 150 1 15

(µF) RC (kΩ)C

OUT

(nF) C1 (pF)

C

4.7µF

C1

C

PV

CC

100Ω

10k

PGND

1µF

0.1µF

1k

+

V

PV

1µF

GND

NC

R

C

C

C

SS

CC

FREQSET

SHDN

COMP

SS

GND PGND

GND

LTC3831

CC2

PV

CC1

TG

I

MAX

I

FB

+

R

BG

FB

–

R

V

IN

+

C

OPTIONAL

Q1

MBRS340T3

MBRS340T3

Q2

IN

L

O

V

OUT

+

C

OUT

PGND

3830 F11

Figure 10. Typical Schematic Showing Layout Considerations

3831f

17

LTC3831

WUUU

APPLICATIO S I FOR ATIO

current density in the PC board itself is a serious concern.

Traces carrying high current should be as wide as possible. For example, a PCB fabricated with

requires a minimum trace width of

1. In general, layout should begin with the location of the

power devices. Be sure to orient the power circuitry so that

a clean power flow path is achieved. Conductor widths

should be maximized and lengths minimized. After you are

satisfied with the power path, the control circuitry should

be laid out. It is much easier to find routes for the relatively

small traces in the control circuits than it is to find

circuitous routes for high current paths.

2.

The GND and PGND pins should be shorted directly at

the LTC3831

turbances in the LTC3831 and prevents differences in

ground potential from disrupting internal circuit operation.

This connection should then tie into the ground plane

a single point, preferably at a fairly quiet point in the circuit

such as

practical, however, due to physical constraints. Another

reasonably good point to make this connection is between

the output capacitors and the source connection of the

bottom MOSFET Q2. Do not tie this single point ground in

the trace run between the Q2 source and the input capacitor ground, as this area of the ground plane will be very

noisy.

. This helps to minimize internal ground dis-

close to the output capacitors

0.15" to carry 5A

. This is not always

2oz copper

.

at

3. The small-signal resistors and capacitors for frequency

compensation and soft-start should be located very close

to their respective pins and the ground ends connected to

the signal ground pin through a separate trace. Do not

connect these parts to the ground plane!

4. The VCC, PV

be as close to the LTC3831 as possible. The 4.7µF and 1µF

bypass capacitors shown at VCC, PV

provide optimum regulation performance.

5. The (+) plate of CIN should be connected as close as

possible to the drain of the upper MOSFET, Q1. An additional 1µF ceramic capacitor between VIN and power ground

is recommended.

6. The VFB pin is very sensitive to pickup from the switching node. Care should be taken to isolate VFB from possible

capacitive coupling to the inductor switching signal.

7. In a typical SSTL application, if the R+ pin is to be connected to V

the switching regulator, do not connect R+ along the high

current flow path; it should be connected to the SSTL interface supply output. R– should be connected to the interface supply GND.

8. Kelvin sense I

and PV

CC1

, which is also the main supply voltage for

DDQ

and IFB at Q1’s drain and source pins.

MAX

decoupling capacitors should

CC2

CC1

and PV

will help

CC2

18

3831f

PACKAGE DESCRIPTIO

LTC3831

U

GN Package

16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

.045 ±.005

.254 MIN

RECOMMENDED SOLDER PAD LAYOUT

.007 – .0098

(0.178 – 0.249)

.016 – .050

NOTE:

1. CONTROLLING DIMENSION: INCHES

2. DIMENSIONS ARE IN

3. DRAWING NOT TO SCALE

*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

**DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

(0.406 – 1.270)

INCHES

(MILLIMETERS)

.150 – .165

.0250 TYP.0165 ±.0015

.015

(0.38 ± 0.10)

0° – 8° TYP

± .004

× 45°

.229 – .244

(5.817 – 6.198)

.053 – .068

(1.351 – 1.727)

.008 – .012

(0.203 – 0.305)

16

15

12

.189 – .196*

(4.801 – 4.978)

14

12 11 10

13

5

4

3

678

.0250

(0.635)

BSC

.009

(0.229)

9

(0.102 – 0.249)

REF

.150 – .157**

(3.810 – 3.988)

.004 – .0098

GN16 (SSOP) 0502

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

3831f

19

LTC3831

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LTC1530 High Power Synchronous Switching Regulator Controller SO-8 with Current Limit. No R

LTC1628 Family Dual High Efficiency 2-Phase Synchronous Step-Down Controllers Constant Frequency, Standby 5V and 3.3V LDOs, 3.5V ≤ VIN ≤ 36V

LTC1702 Dual High Efficiency 2-Phase Synchronous Step-Down Controller 550kHz, 25MHz GBW Voltage Mode, VIN ≤ 7V, No R

LTC1703 Dual 550kHz Synchronous 2-Phase Switching Regulator LTC1702 with Mobile VID for Portable Systems

Controller with Mobile VID

LTC1705 Dual 550kHz Synchronous 2-Phase Switching Regulator Provides Core, I/O and CLK Supplies for Portable Systems

Controller with 5-Bit VID Plus LDO

LTC1709 Family 2-Phase, 5-Bit Desktop VID Synchronous Step-Down Controllers Current Mode, VIN to 36V, I

LTC1736 Synchronous Step-Down Controller with 5-Bit Mobile VID Control Fault Protection, Power Good, 3.5V to 36V Input, Current Mode

LTC1753 5-Bit Desktop VID Programmable Synchronous 1.3V to 3.5V Programmable Output Using Internal 5-Bit DAC

Switching Regulator

LTC1778 Wide Operating Range/Step-Down Controller, No R

SENSE

VIN Up to 36V, Current Mode, Power Good

LTC1873 Dual Synchronous Switching Regulator with 5-Bit Desktop VID 1.3V to 3.5V Programmable Core Output Plus I/O Output

LTC1929 2-Phase, Synchronous High Efficiency Converter Current Mode Ensures Accurate Current Sensing VIN Up to 36V,

with Mobile VID I

LTC3413 3A, Monolithic Synchronous Regulator for DDR/QDR Low R

Memory Termination (Sink and Source), V

LTC3713 Low Input Voltage, High Power, No R

, Step-Down Minimum VIN: 1.5V, Uses Standard Logic-Level N-Channel

SENSE

Up to 40A

OUT

Internal Switch: 85mΩ, ±3A Output Current

DS(ON)

OUT

= V

Synchronous Controller MOSFETs

LTC3778 Wide Operating Range, No R

LTC3717 Wide VIN Step-Down Controller for DDR Memory Termination Current Mode Operation, V

, Step-Down Controller VIN Up to 36V, Current Mode, Power Good, Stable with

SENSE

Ceramic C

Tracks V

OUT

(V

), No R

IN

DDQ

OUT

SENSE

Output Current Limit

LTC3718 Bus termination Supply for Low Votlage V

IN

LTC3832 High Power Synchronous Switching Regulator Controller V

No R

is a trademark of Linear Technology Corporation.

SENSE

1.5V ≤ VIN, Generates 5V Gate Drive for Standard N-Ch MOSFETs,

2A ≤ I

≤ 25A

OUT

as low as 0.6V

OUT

TM

required

SENSE

SENSE

Up to 42A, Various VID Tables

OUT

/2

REF

= 1/2 VIN, V

OUT

(VTT)

, Symmetrical Sink and Source

20

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

3831f

LT/TP 0503 1K • PRINTED IN USA

LINEAR TECHNOLOG Y CORPORATION 2001

Loading...

Loading...