Programmable Up/Down Tracking

FEATURES

■

Wide VIN Range: 3V to 30V Operation with Line

Feedforward Compensation

■

Leading Edge Modulation Architecture for

Extremely Low Duty Cycle Operation

■

Phase-Lockable Fixed Frequency: 330kHz to 750kHz

■

Two 180° Out-of-Phase Controllers

■

Fast Programmable Power-Up/-Down Tracking

■

Programmable Current Limit Without External

Current Sense Resistor

■

Optional Burst Mode® Operation at Light Load

■

±1% 0.6V Voltage Reference

■

External N-Channel MOSFET Architecture

■

Low Shutdown Current: <100µA

■

Overvoltage Protection and PGOOD Flag

■

Small 28-Lead SSOP and 32-Lead QFN Packages

U

APPLICATIO S

■

Notebook and Palmtop Computers

■

Portable Instruments

■

Battery-Operated Digital Devices

■

DC Power Distribution Systems

LTC3802

Dual 550kHz Synchronous

2-Phase DC/DC Controller with

U

DESCRIPTIO

The LTC®3802 is a dual switching regulator controller

optimized for high efficiency step-down conversion from

input voltages between 3V to 30V. The controller uses a

leading edge modulation scheme to allow extremely low

duty cycle operation. The constant frequency voltage mode

controller allows a phase-lockable frequency between

330kHz and 750kHz. Power loss and noise due to the ESR

of the input capacitors are minimized by operating the two

controller output stages 180° out of phase. The synchronous buck architecture automatically shifts to Burst Mode

operation as the output load decreases, ensuring maximum efficiency over a wide range of load currents.

The LTC3802 features an onboard, trimmed 0.6V reference and provides better than 1% regulation at the converter outputs. A separate output sense provides real time

overvoltage protection and PGOOD sensing. An FBT pin

programs the power-up/-down tracking between the two

channels to meet various sequencing requirements. A

RUN/SS pin provides soft-start and externally programmable current limit protection functions.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode is a registered trademark of Linear Technology Corporation.

U.S. Patent Nos 5481178, 5846544, 6304066, 6580258, 5055767, 6307356

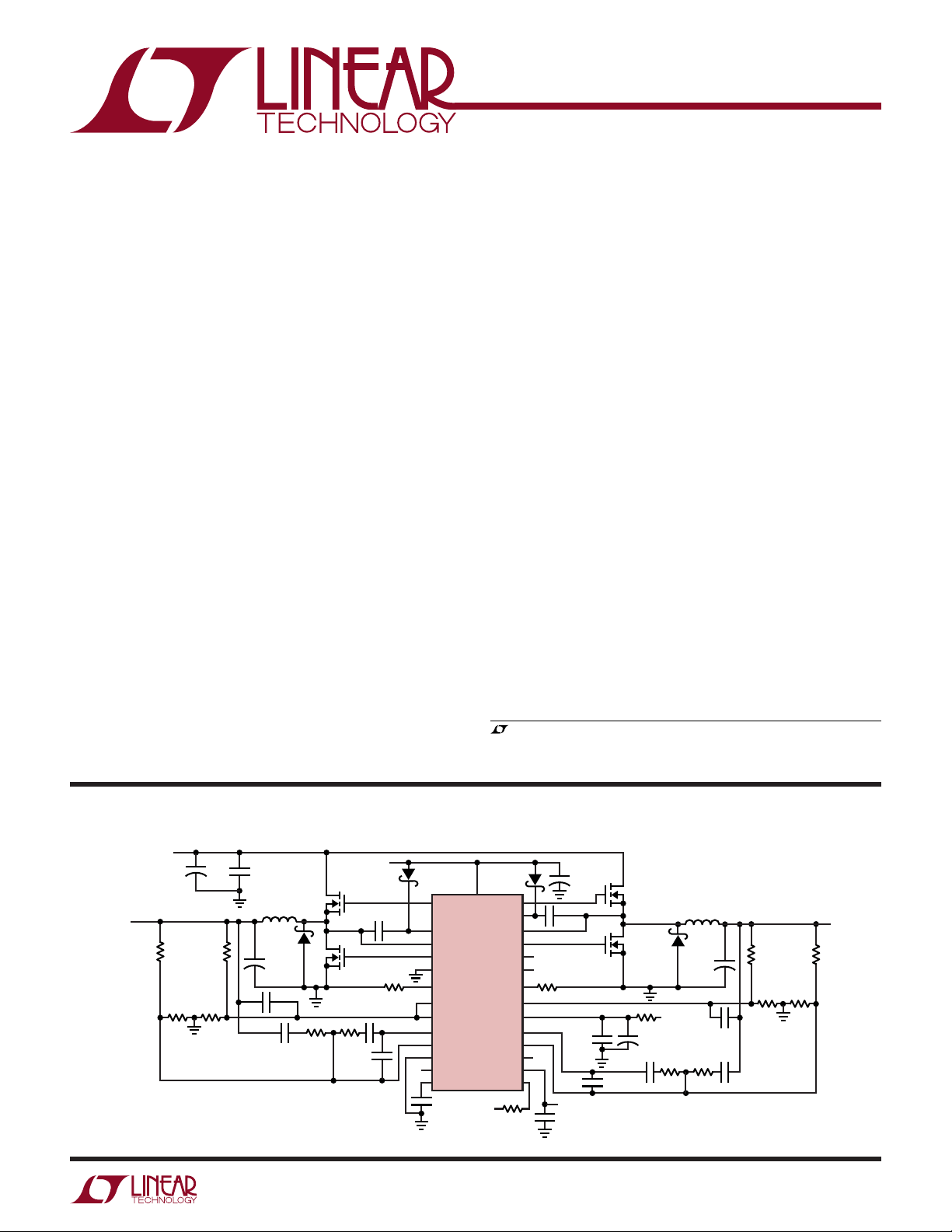

TYPICAL APPLICATIO

V

IN

V

OUT1

3.3V

15A

5V TO 22V

10k

56µF

+

2.21k2.21k

10k

25V

×2

4.7µF

25V

×8

+

1500pF

1µH

B340B

330µF

4V

×3

560pF

390Ω

U

CMDSH-3

Si7860DP

×2

Si7440DP

×2

15k

330pF

5V

0.1µF

2200pF

TG1

BOOST1

SW1

BG1

PGND

I

MAX1

FBT

CMPIN1

COMP1

FB1

SGND

FCB

RUN/SS

0.1µF

PV

CC

LTC3802

CMDSH-3

TG2

BOOST2

SW2

BG2

PLLIN

PLLLPF

I

MAX2

CMPIN2

V

COMP2

FB2

PHASEMD

V

INFF

PGOOD

10k

5V

+

10µF

0.1µF

47k47k

CC

0.1µF

V

IN

0.47µF

330pF

Si7860DP

×2

Si7440DP

×2

+

10Ω

10µF

1µH

B340B

330µF

4V

×3

5V

390Ω15k

+

560pF

1500pF2200pF

10k

3.16k 3.16k

10k

3802 TA01

V

2.5V

15A

OUT2

3802f

1

LTC3802

WW

W

U

ABSOLUTE AXI U RATI GS

Supply Voltage

VCC, PVCC............................................................. 7V

BOOSTn.............................................................. 37V

BOOSTn – SWn.................................................... 7V

SWn........................................................ –1V to 30V

Input Voltage

V

.................................................................... 30V

INFF

FBn, CMPINn, FBT, PLLIN, FCB,

RUN/SS, PGOOD, PLLLPF, PHASEMD,

EXTREF, I

n

.......................... –0.3V to VCC + 0.3V

MAX

UUW

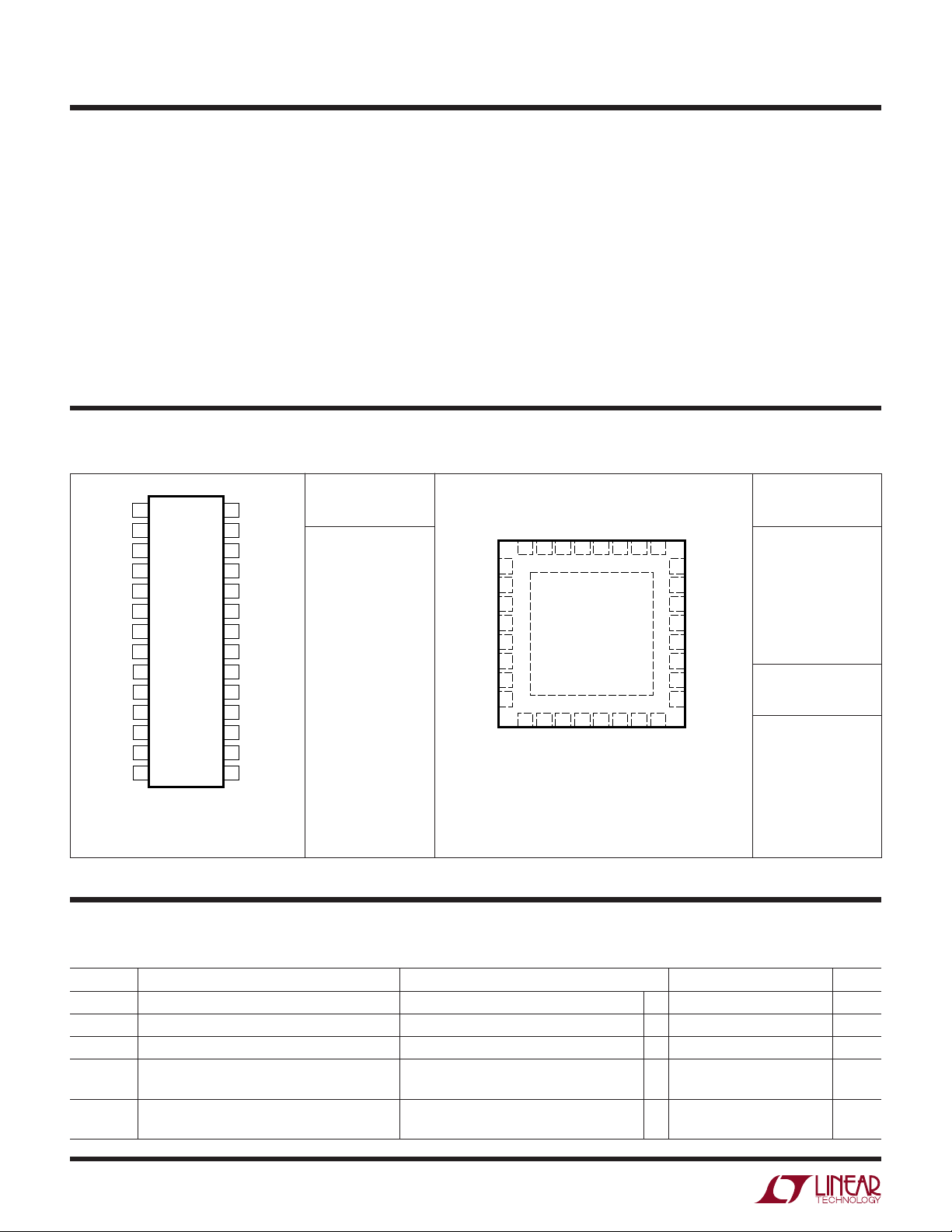

PACKAGE/ORDER I FOR ATIO

PV

CC

BG1

BOOST1

TG1

SW1

PGND

I

MAX1

FBT

CMPIN1

10

COMP1

11

FB1

12

SGND

13

FCB

14

RUN/SS

28-LEAD PLASTIC SSOP

T

JMAX

TOP VIEW

1

2

3

4

5

6

7

8

9

GN PACKAGE

= 125°C, θJA = 110°C/W

28

27

26

25

24

23

22

21

20

19

18

17

16

15

BG2

BOOST2

TG2

SW2

PLLIN

PLLLPF

I

MAX2

CMPIN2

V

CC

COMP2

FB2

PHASEMD

V

INFF

PGOOD

ORDER PART

NUMBER

LTC3802EGN

(Note 1)

PGND

PGND

I

MAX1

FBT

CMPIN1

COMP1

FB1

Extended Commercial

Operating Temperature Range (Note 2) .. –40°C to 85°C

Storage Temperature Range

LTC3802EGN ................................... –65°C to 150°C

LTC3802EUH ................................... –65°C to 125°C

Lead Temperature (Soldering, 10 sec)

LTC3802EGN Only........................................... 300°C

TOP VIEW

ORDER PART

NUMBER

TG1

BOOST1

BG1

PVCCBG2

BOOST2

TG2

32 31 30 29 28 27 26 25

1SW1

2

3

4

5

6

7

8

9 10 11 12

SGND

32-LEAD (5mm × 5mm) PLASTIC QFN

T

JMAX

EXPOSED PAD (PIN 33) IS GND

MUST BE SOLDERED TO PCB

33

13 14 15 16

FCB

PGOOD

EXTREF

RUN/SS

UH PACKAGE

= 125°C, θJA = 34°C/W

V

INFF

PHASEMD

SW2

FB2

24

23

22

21

20

19

18

17

PGND

PGND

PLLIN

PLLLPF

I

MAX2

CMPIN2

V

CC

COMP2

LTC3802EUH

UH PART

MARKING

3802

Consult LTC Marketing for parts specified with wider operating temperature ranges.

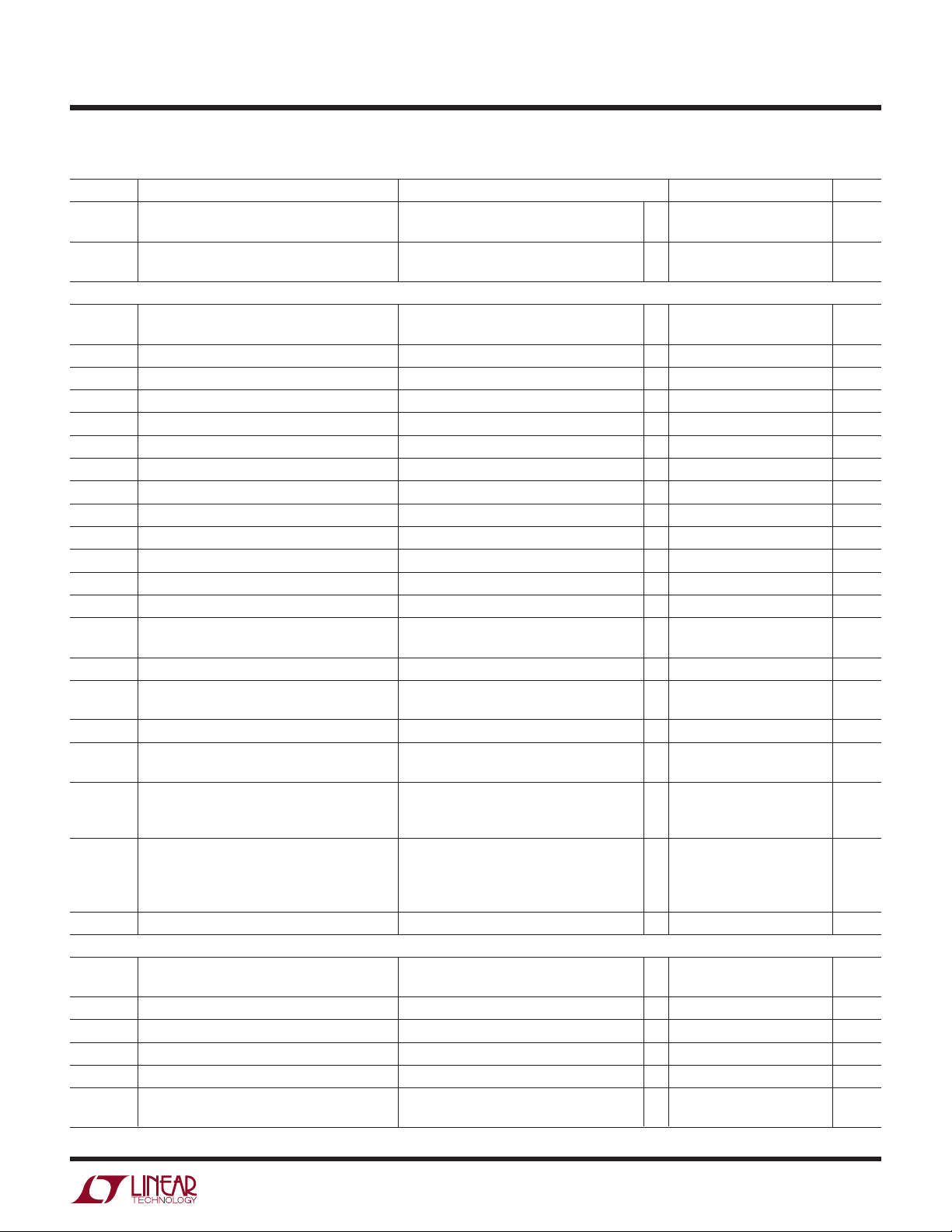

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range. (Note 3) VCC = PVCC = BOOST = 5V, unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

PV

BV

V

I

VCC

CC

CC

CC

UVLO

VCC Supply Voltage ● 356 V

PVCC Supply Voltage (Note 4) ● 56 V

BOOST Pin Voltage V

Positive Undervoltage Lockout Measured at V

VCC Supply Current VFB = V

– VSW (Note 4) ● 56 V

BOOST

Measured at V

V

RUN/SS

CC

INFF

COMP

= 0V, PLLIN Floating ● 100 150 µA

2.2 2.5 2.8 V

2.2 2.5 2.8 V

● 6.5 9 mA

3802f

2

LTC3802

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range. (Note 3) VCC = PVCC = BOOST = 5V, unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

I

PVCC

I

BOOST

Switcher Control Loop

V

FB

∆V

FB

∆V

OUT

A

ERR

GBW Error AMP Gain Bandwidth Product f = 100kHz (Note 7) 10 MHz

I

COMP

I

FB

I

CMPIN

I

FBT

I

EXTREF

V

EXTREF

A

LFF

R

VINFF

V

PGOOD

V

OVP

V

BURRS

V

SAW

I

IMAX

I

LIM(TH)

I

SS

V

SHDN

LOGIC and PGOOD

I

PHASEMD

V

IH

V

IL

I

PGOOD

V

OLPG

t

PGOOD

PVCC Supply Current VFB = V

V

RUN/SS

BOOST Pin Current VFB = V

V

RUN/SS

Feedback Voltage V

EXTREF

V

EXTREF

= 0V, No Load 2 mA

CMPIN

= 0V (Notes 5, 6) 1 10 µA

= 0V, No Load 1 mA

CMPIN

= 0V (Notes 5, 6) 1 10 µA

= 5V, 0°C ≤ T ≤ 70°C 0.594 0.600 0.606 V

= 5V ● 0.591 0.600 0.609 V

Feedback Voltage VCC Line Regulation VCC = 4.5V to 6V ±0.01 %/V

Output Voltage Load Regulation (Note 7) 0.1 ±0.2 %

Error AMP DC Gain No Load, V

Error AMP Output Sink/Source Current V

RUN/SS

= V

EXTREF

CC

= V

RUN/SS

= V

CC

● 70 80 dB

±12 mA

Voltage Feedback Input Current VFB = 0V to 1V ● ±1 µA

Comparators Input Current V

FBT Input Current V

EXTREF Input Current V

External Reference Not to Affect V

∆ Drop in Duty Cycle/∆ V

V

Input Resistance 1MΩ

INFF

FB

INFF

= 0V to 1V ● ±1 µA

CMPIN

= 0V to 1V ● ±1 µA

FBT

= 0V to 5V ● ±1 µA

EXTREF

● 1V

V

= 5V to 30V 2.3 %/V

VINFF

Positive Power Good Threshold With Respect to 0.6V ● 5 10 15 %

Negative Power Good Threshold With Respect to 0.6V

Overvoltage Threshold With Respect to V

(V

– VFB) to Reset 15 mV

CMPIN

FB

● –5 –10 –15 %

359 %

Burst Mode Operation –12 mV

SAW Before Line Compensation 1.2 V

I

Source Current V

MAX

I

Comparator Offset ● –15 0 15 mV

LIM

V

Hard I

Threshold 5V/V

IMAX/ILIM

Threshold V

LIM/ILIM

RUN/SS Source Current V

RUN/SS Sink/Source Current Ratio V

RUN/SS Sink Current, I

RUN/SS Sink Current, Hard I

LIM

LIM

= 1V –9.0 –10 –11.0 µA

IMAX

= 0V 1.5 V/V

CMPIN

= V

CMPIN

CMPIN

V

CMPIN

V

CMPIN

= 0.6V, V

FBT

= V

= 0.6V, V

FBT

= V

= 0.6V 100 µA

FBT

= V

= 0V ● 1mA

FBT

= V

PHASEMD

PHASEMD

CC

= 0V 1.5 2 2.5 µA/µA

● –8.5 –10 –11.5 µA

–5 –7 –9 µA

RUN/SS Shutdown Threshold RUN/SS↑ ● 0.4 0.8 1.2 V

PHASEMD Pull-Up Current V

PHASEMD Pull-Down Current V

= 0V –7 µA

PHASEMD

= 5V 2 µA

PHASEMD

PLLIN, FCB High Level Input Voltage ● 2.4 V

PLLIN, FCB Low Level Input Voltage ● 0.8 V

V

Leakage Current Power Good ±1 µA

PGOOD

V

Output Low Voltage I

PGOOD

V

Falling Edge Delay (Note 8) ● 100 150 µs

PGOOD

V

Rising Edge Delay (Note 8) 10 µs

PGOOD

= 1mA ● 0.1 0.3 V

PGOOD

3802f

3

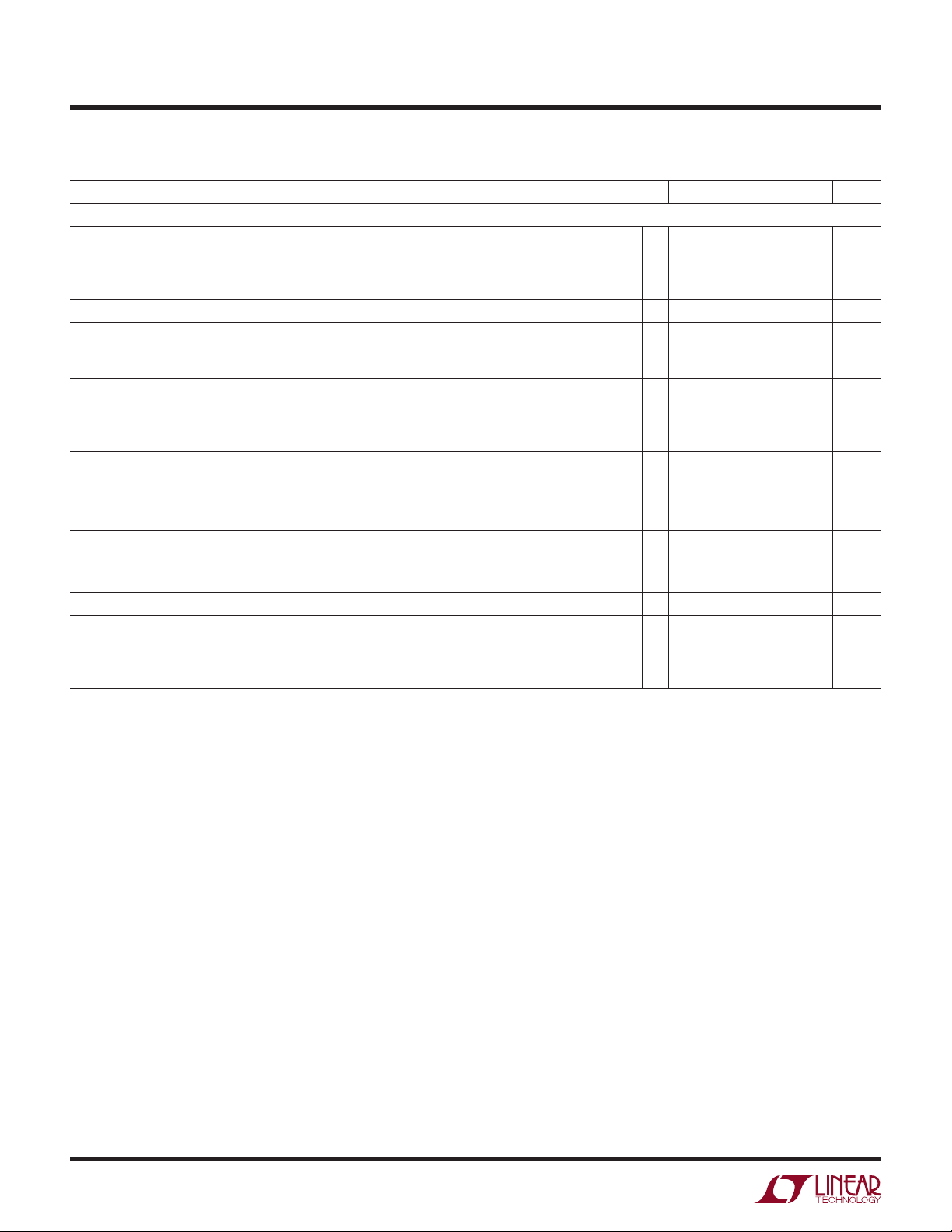

LTC3802

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating

temperature range. (Note 3) VCC = PVCC = BOOST = 5V, unless otherwise specified.

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

Switcher Switching Characteristics

f

OSC

R

PLLIN

I

PLLLPF

Phase TG1↓ vs PLLIN↓ PHASEMD Floats 0 Deg

V

PHASEMD

DC

MIN

DC

MAX

t

ON(MIN)

t

NOV

R

DS(ON)

Oscillator Frequency PLLIN Open or V

V

= 1.2V 550 kHz

PLLLPF

V

= 0V 250 330 400 kHz

PLLLPF

V

= 2.4V 650 750 850 kHz

PLLLPF

= 0V 490 550 610 kHz

PLLIN

PLLIN Pull-Down Current Source 5 µA

Phase Detector Output Current

Sourcing Capability f

Sinking Capability f

TG1↓ vs PLLIN↓ V

> f

PLLIN

< f

PLLIN

PHASEMD

OSC

OSC

–15 µA

15 µA

= 5V 90 Deg

TG2↓ vs PLLIN↓ PHASEMD Floats 180 Deg

TG2↓ vs PLLIN↓ V

= 5V 270 Deg

PHASEMD

Shutdown Threshold ● 1.2 1.7 V

Floating 2.0 V

90° Phase Threshold ● 3.5 4.0 4.5 V

Minimum TG Duty Cycle V

Maximum TG Duty Cycle V

= 0V ● 0%

PLLIN

PLLIN

= 0V, V

= 0.6V (Note 9) ● 86 89 92 %

CMPIN

TG Minimum Pulse Width (Notes 7, 10) 50 ns

BG Minimum Pulse Width V

= 0V (Note 9) 400 ns

CMPIN

Driver Nonoverlap No Load 10 30 80 ns

TG High R

TG Low R

BG High R

BG Low R

DS(ON)

DS(ON)

DS(ON)

DS(ON)

I

= 100mA (Note 7) 1.6 2.20 Ω

OUT

1.3 1.80 Ω

1.8 2.50 Ω

0.7 1.00 Ω

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The LTC3802 is guaranteed to meet performance specifications

from 0°C to 70°C. Specifications over the –40°C to 85°C operating

temperature range are assured by design, characterization and correlation

with statistical process controls.

Note 3: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are referenced to ground unless otherwise

specified.

Note 4: To ensure proper operation, PV

be greater than V

of the external MOSFETs.

GS(ON)

and BVCC (V

CC

BOOST

– VSW) must

Note 5: Supply current in normal operation is dominated by the current

needed to charge and discharge the external MOSFET gates. This current

will vary with supply voltage and the external MOSFETs used.

Note 6: Supply current in shutdown is dominated by external MOSFET

leakage and may be significantly higher than the quiescent current drawn

by the LTC3802, especially at elevated temperature.

Note 7: Guaranteed by design, not subject to test.

Note 8: Rise and fall times are measured using 10% and 90% levels. Delay

and nonoverlap times are measured using 50% levels.

Note 9: If V

is less than 90% of its nominal value, BG minimum

CMPIN

pulse width is limited to 400ns.

Note 10: The LTC3802 leading edge modulation architecture does not

have a minimum TG pulse width requirement. The TG minimum pulse

width is limited by the rise and fall times.

3802f

4

UW

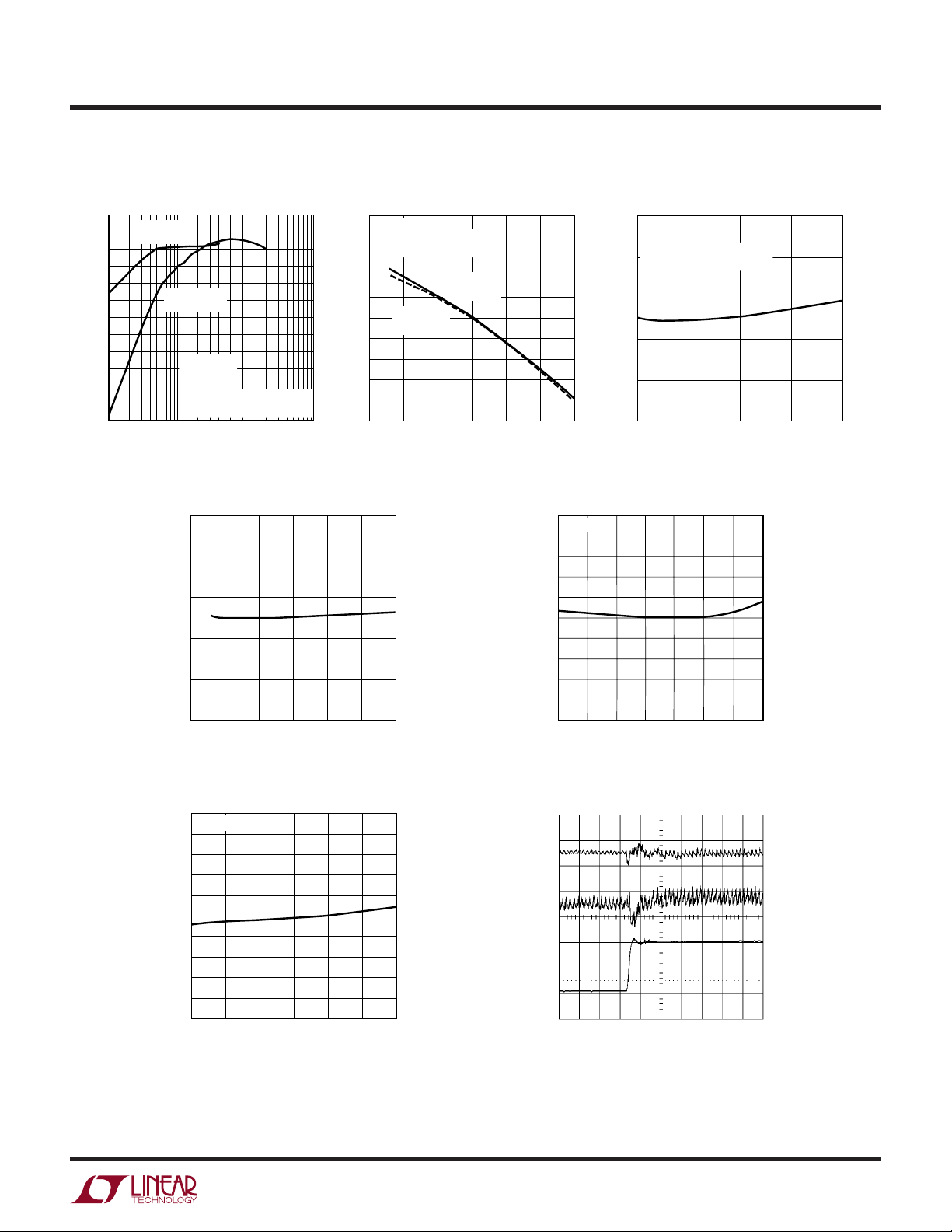

TYPICAL PERFOR A CE CHARACTERISTICS

LTC3802

Efficiency vs I

100

EFFICIENCY (%)

Burst Mode

95

OPERATION

90

85

80

75

70

65

60

55

50

45

40

0.1

OUT

CONTINUOUS

MODE

VIN = 12V

V

= 3.3V

OUT

T

= 25°C

A

CIRCUIT ON THE FIRST PAGE

OF THIS DATA SHEET

1 10 100

I

(A)

OUT

Line Regulation

2.5125

VCC = 5V

= 5A

I

OUT

= 25°C

T

2.5075

2.5025

(V)

OUT

V

2.4975

2.4925

2.4875

A

0

10 15 20

5

3802 G01

VIN (V)

Efficiency vs V

100

TA = 25°C

98

CIRCUIT ON THE FIRST PAGE

OF THIS DATA SHEET

96

94

92

V

= 2.5V

0

25 30

3802 G04

OUT

I

OUT

5

0.5

0.4

0.3

0.2

0.1

0

–0.1

–0.2

–0.3

–0.4

–0.5

= 10A

∆V

OUT

(%)

90

88

EFFICIENCY (%)

86

84

82

80

IN

V

= 2.5V

OUT

I

= 5A

OUT

15 20

10

VIN (V)

30

25

3802 G02

Load Regulation

2.5125

VIN = 12V

= 25°C

T

A

CIRCUIT ON THE FIRST PAGE

2.5075

OF THIS DATA SHEET

2.5025

(V)

OUT

V

2.4975

2.4925

2.4875

0

0.5

0.4

0.3

0.2

∆V

0.1

OUT

0

(%)

–0.1

–0.2

–0.3

–0.4

3802 G03

–0.5

20

I

OUT

10

15

(A)

5

VFB vs Temperature

100

125

1.0

0.8

0.6

0.4

0.2

0

–0.2

–0.4

–0.6

–0.8

–1.0

∆V

FB

(%)

606.0

604.8

603.6

602.4

601.2

600.0

(mV)

FB

V

598.8

597.6

596.4

595.2

594.0

VCC = 5V

–50

0

–25

TEMPERATURE (°C)

50

25

75

LTC1323 • TPC05

VFB vs VCC Supply Voltage Line Feedforward Transient

3802 G06

0.5

0.4

0.3

0.2

∆V

0.1

FB

(%)

0

–0.1

–0.2

–0.3

–0.4

–0.5

6

V

OUT

2.5V

(NO LOAD)

AC 50mV/DIV

V

COMP

AC 50mV/DIV

V

5V TO 15V

STEP

5V/DIV

IN

: 1µF/50V ×6

C

IN

SANYO 35CV220AX

10µs/DIV

603.0

602.4

601.8

601.2

600.6

600.0

(mV)

FB

V

599.4

598.8

598.2

597.6

597.0

TA = 25°C

3

4.5

4

3.5

VCC SUPPLY VOLTAGE (V)

5

5.5

3802 G07

3802f

5

LTC3802

TEMPERATURE (°C)

–50 –25

–10

I

LIM(TH)

OFFSET (mV)

–2

10

0

50

75

3802 G13

–6

6

2

25

100

125

VCC = 5V

V

IMAX

= 500mV

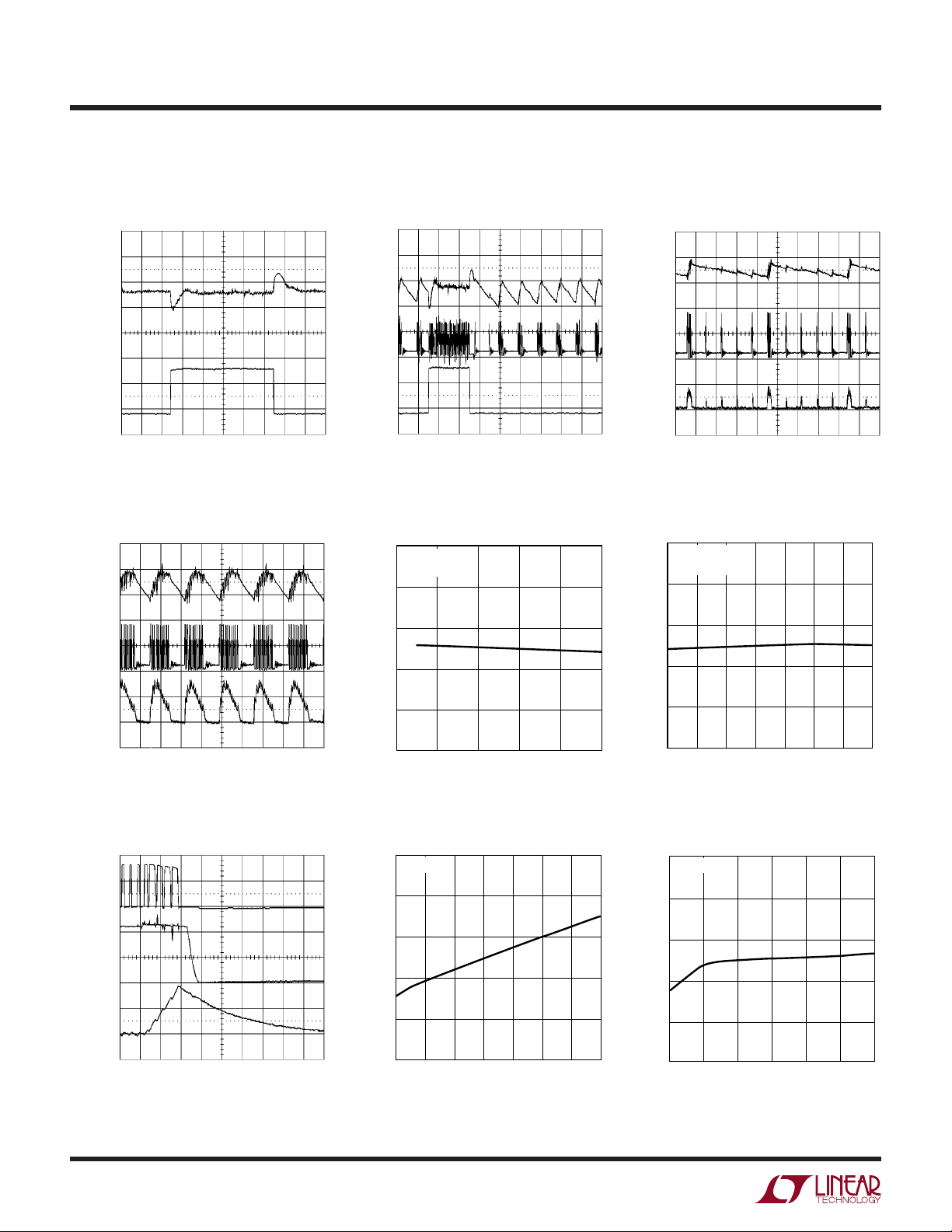

UW

TYPICAL PERFOR A CE CHARACTERISTICS

V

OUT

1.2V

50mV/DIV

Load Step in Continuous Mode

50mV/DIV

Load Step in Burst Mode Operation

V

OUT

1.2V

V

SW

10V/DIV

V

OUT

1.2V

50mV/DIV

V

SW

10V/DIV

Burst Mode Waveform

with 0.2A Load

I

OUT

1A TO 10A

STEP

5A/DIV

V

OUT

1.2V

50mV/DIV

V

10V/DIV

INDUCTOR

CURRENT

5A/DIV

10V/DIV

= 12V

IN

CIRCUIT ON

FIRST PAGE OF THIS DATA SHEET

20µs/DIVV

Burst Mode Waveform

with 3A Load

SW

= 12V

IN

CIRCUIT ON

FIRST PAGE OF THIS DATA SHEET

20µs/DIVV

Short-Circuit Test

TG

3802 G08

3802 G11

I

OUT

1A TO 10A

STEP

5A/DIV

10

OFFSET (mV)

LIM(TH)

I

–6

–10

600

580

= 12V

IN

CIRCUIT ON

FIRST PAGE OF THIS DATA SHEET

I

LIM(TH)

TA = 25°C

= 5V

V

CC

6

2

–2

200

0

50µs/DIVV

Offset vs V

400

V

IMAX

Switching Frequency

vs Temperature

VCC = 5V

IMAX

600

(mV)

800

3802 G09

3802 G12

1000

INDUCTOR

CURRENT

5A/DIV

= 12V

IN

CIRCUIT ON

FIRST PAGE OF THIS DATA SHEET

I

LIM(TH)

Switching Frequency

vs VCC Supply Voltage

600

TA = 25°C

580

50µs/DIVV

Offset vs Temperature

3802 G10

RUN/SS

2V/DIV

INDUCTOR

CURRENT

20A/DIV

6

CIRCUIT ON

FIRST PAGE OF THIS DATA SHEET

= 12V, V

V

IN

= 47k, L = 1µH (TOKO-FDA1254-1ROM)

R

I(MAX)

5µs/DIV

= 3.3V, CSS = 0.01µF,

OUT

3802 G14

560

540

520

SWITCHING FREQUENCY (kHz)

500

–50 –25

25

0

TEMPERATURE (°C)

560

540

SWITCHING FREQUENCY (kHz)

520

50

75

100

125

3802 G15

500

3

4 4.5 5

3.5

VCC SUPPLY VOLTAGE (V)

5.5 6

3802 G16

3802f

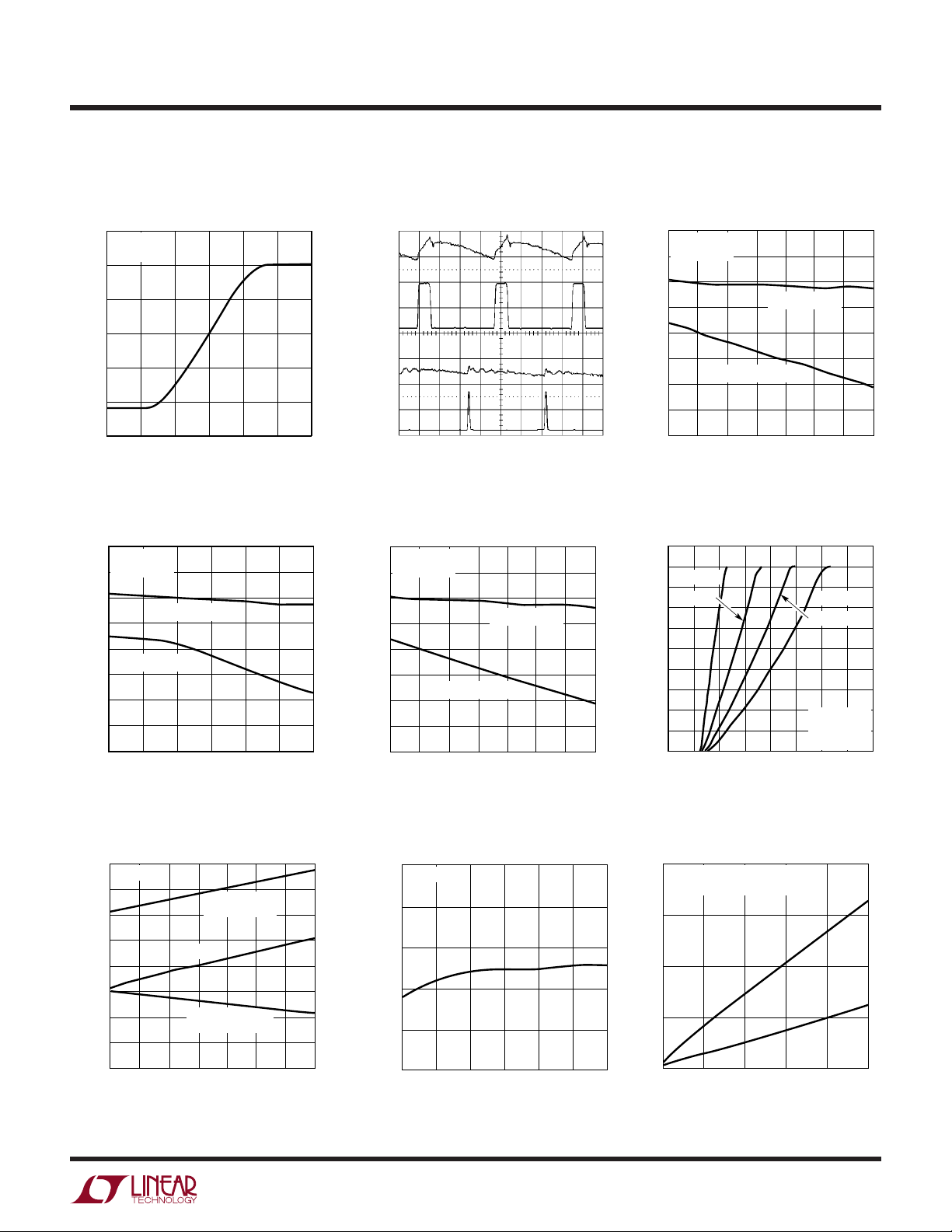

UW

TEMPERATURE (°C)

–50

MAXIMUM DUTY CYCLE (%)

95

25

3802 G19

80

70

–25 0 50

65

60

100

90

85

75

75 100 125

VCC = 5V

f

SW

= 550kHz

V

CMPIN

> 0.54V

V

CMPIN

< 0.54V

TYPICAL PERFOR A CE CHARACTERISTICS

Switching Frequency vs V

850

TA = 25°C

= 5V

V

CC

750

PLLLPF

AC 20mV/DIV

Continuous Mode Operation

V

OUT1

5V

LTC3802

Maximum Duty Cycle

vs Temperature

650

550

450

SWITCHING FREQUENCY (kHz)

350

250

0

0.8 1.2 1.6

0.4

V

PLLLPF

Maximum Duty Cycle

vs VCC Supply Voltage

100

TA = 25°C

= 550kHz

f

SW

95

90

85

80

75

70

MAXIMUM DUTY CYCLE (%)

65

0

3

V

CMPIN

V

< 0.54V

CMPIN

3.5 4 5

VCC SUPPLY VOLTAGE (V)

(V)

> 0.54V

4.5

2 2.4

3802 G17

5.5

3802 G20

6

TG1

20V/DIV

V

OUT2

TG2

20V/DIV

1V

= 30V

IN

AC 20mV/DIV

Maximum Duty Cycle

vs Switching Frequency Duty Cycle vs V

100

TA = 25°C

= 5V

V

CC

95

90

85

80

75

70

MAXIMUM DUTY CYCLE (%)

65

60

390 450 570

330

0.5µs/DIVV

V

> 0.54V

CMPIN

V

< 0.54V

CMPIN

510

SWITCHING FREQUENCY (kHz)

630 690 750

3802 G18

3802 G21

100

90

VIN = 5V

80

VIN = 12V

70

60

50

40

DUTY CYCLE (%)

30

20

10

0

0.8

1 1.4

1.2

V

COMP

1.6

COMP

(V)

1.8

VIN = 30V

VIN = 20V

TA = 25°C

= 5V

V

CC

V

CMPIN

2

= V

2.2

FB

2.4

3802 G22

I

IMAX

vs Temperature

12.0

VCC = 5V

11.5

11.0

10.5

(µA)

10.0

IMAX

I

9.5

9.0

8.5

8.0

–50

–25 0 50

and I

RUN/SS

TEMPERATURE (°C)

I

RUN/SS

SINK CURRENT

I

IMAX

I

RUN/SS

SOURCE CURRENT

25

75 100 125

3802 G23

20

15

10

5

0

–5

–10

–15

–20

I

RUN/SS

(µA)

(µA)

IMAX

I

11.5

10.9

10.3

9.7

9.1

8.5

I

vs VCC Supply Voltage

IMAX

TA = 25°C

3

4 4.5 5

3.5

VCC SUPPLY VOLTAGE (V)

5.5 6

3802 G24

Driver Supply Current vs Load

80

TA = 25°C

= V

PV

CC

60

40

20

DRIVER SUPPLY CURRENT (mA)

0

0

– VSW = 5V

BOOST

2000

4000

CTG, CBG LOAD (pF)

6000

I

PVCC

I

BOOST1

I

BOOST2

8000

10000

3802 G25

3802f

7

LTC3802

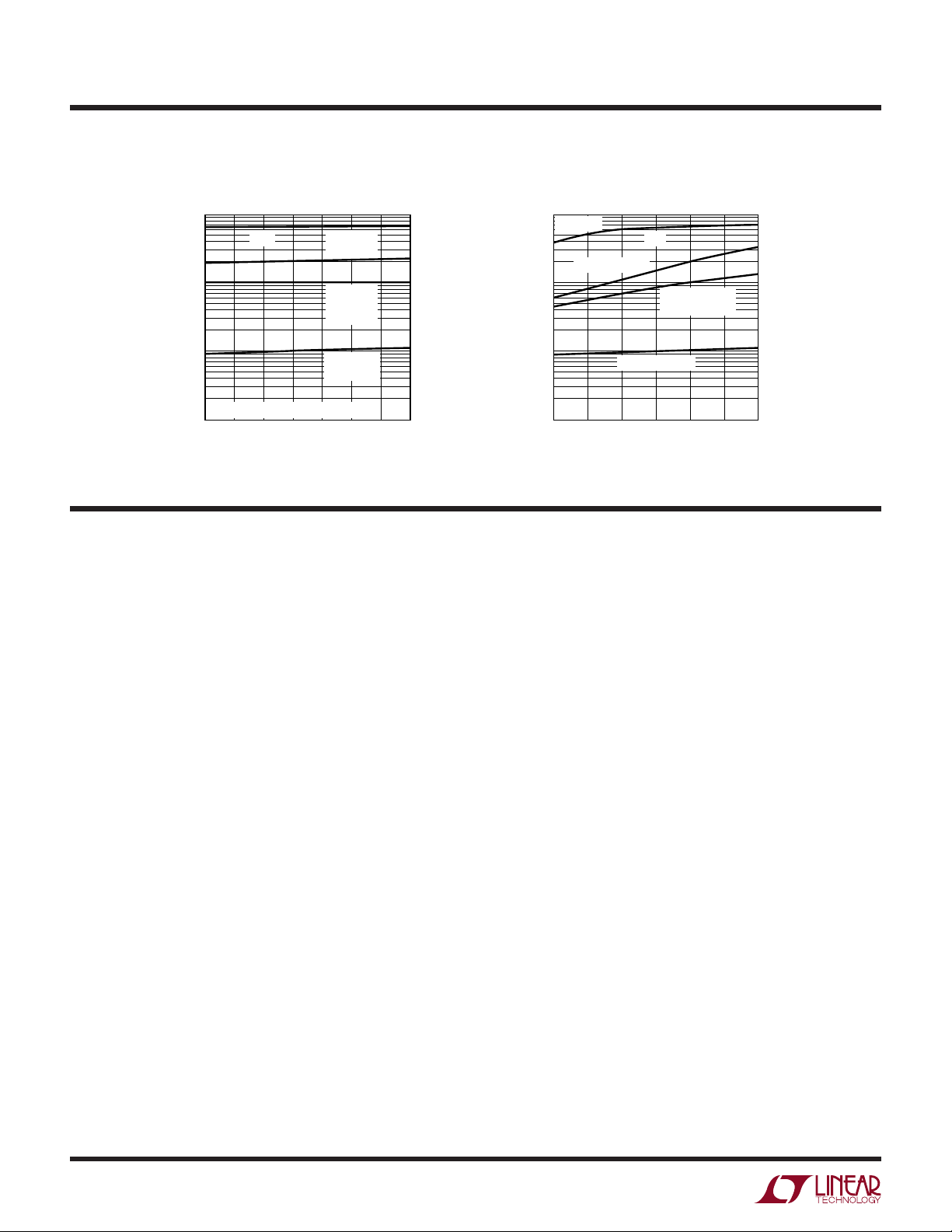

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Supply Current vs Temperature Supply Current vs Supply Voltage

10

I

VCC

1

I

PVCC

(NO LOAD)

I

BOOST1

I

BOOST2

(NO LOAD)

10

1

TA = 25°C

I

PVCC

(NO LOAD)

I

VCC

I

BOOST1, IBOOST2

(NO LOAD)

0.1

SUPPLY CURRENT (mA)

0.01

VCC = V

–50 –25

= V

PVCC

0 25 50 75 100 125

TEMPERATURE (°C)

BOOST

I

SHUTDOWN

– VSW = 5V

VCC

3802 G26

UUU

PI FU CTIO S

PVCC (Pin 1/Pin 29): Driver Power Supply Input. PV

provides power to the two BG drivers and must be connected to an external voltage high enough to fully turn on

the external MOSFETs, QB1 and QB2. PVCC requires at

least a 10µF bypass capacitor directly to PGND.

BG1 (Pin 2/Pin 30): Channel 1 Controller Bottom Gate

Drive. The BG1 pin drives the gate of the bottom N-channel

synchronous switch MOSFET, QB1. BG1 is designed to

drive typically up to 10,000pF of gate capacitance.

BOOST1 (Pin 3/Pin 31): Channel 1 Controller Top Gate

Driver Supply. BOOST1 should be bootstrapped to SW1

with a 0.1µF capacitor. An external Schottky diode from

PVCC to BOOST1 creates a complete floating chargepumped supply at BOOST1. No other external supplies are

required.

TG1 (Pin 4/Pin 32): Channel 1 Controller Top Gate Drive.

The TG1 pin drives the top N-channel MOSFET with a

voltage swing equal to PVCC superimposed on the switch

node voltage SW1. TG1 is designed to drive typically up to

6000pF of gate capacitance.

(28-Pin SSOP/32-Pin QFN Package)

CC

0.1

SUPPLY CURRENT (mA)

0.01

3

I

SHUTDOWN

VCC

453.5 4.5 5.5 6

SUPPLY VOLTAGE (V)

3802 G27

SW1 (Pin 5/Pin 1): Channel 1 Controller Switching Node.

Connect SW1 to the switching node of the channel 1

converter. When the bottom MOSFET QB1 turns on, the

current limit comparator and the burst comparator

monitor the voltage at SW1. If the voltage drop across

MOSFET QB1 is too large, the controller enters current

limit; if it is too small, the switcher enters Burst Mode

operation. See Current Limit and Burst Mode Applications Information.

PGND (Pin 6/Pins 2, 3, 23, 24): Power Ground. The BG

drivers return to this pin. Connect PGND to a high current

ground node in close proximity to the sources of external

MOSFETs QB1 and QB2 and the VIN, PVCC and V

OUT

bypass capacitors.

I

(Pin 7/Pin 4): Channel 1 Controller Current Limit

MAX1

Set. The I

pin has an internal 10µA current source

MAX1

pull-up, allowing the current limit and burst comparator

threshold to be programmed by a single external resistor

to SGND. See Current Limit and Burst Mode Applications

Information.

8

3802f

UUU

PI FU CTIO S

LTC3802

(28-Pin SSOP/32-Pin QFN Package)

FBT (Pin 8/Pin 5): Feedback Tracking Input. FBT should be

connected through a resistive divider network to V

set the channel 1 output slew rate. Upon power-up/-down,

the LTC3802 servos FBT and CMPIN2 to the same potential to control the output power-up/-down slew rate. To

program both outputs to have the same slew rate, duplicate the CMPIN2 resistive divider at FBT. To have a

ratiometric slew rate, short FBT to CMPIN1. To disable the

tracking function, short FBT to CMPIN2.

CMPIN1 (Pin 9/Pin 6): Channel 1 Controller Comparators

Input. CMPIN1 should be connected through a resistive

divider network to V

voltage. To improve transient response, a feedforward

capacitor can be added to the resistive divider. The power

good comparators, overvoltage comparator and Burst

reset comparators monitor this node directly. CMPIN1 is

a sensitive pin, avoid coupling noise into this pin.

COMP1 (Pin 10/Pin 7): Channel 1 Controller Error Amplifier Output. The COMP1 pin is connected directly to the

channel 1 error amplifier output and the input of the line

feedforward circuit. Use an RC network between the

COMP1 pin and the FB1 pin to compensate the feedback

loop for optimum transient response. Under start-up

conditions, the potential at RUN/SS controls the slew rate

at COMP1.

FB1 (Pin 11/Pin 8): Channel 1 Controller Error Amplifier

Input. FB1 should be connected through a resistive divider

network to V

voltage. Also, connect the channel 1 switcher loop compensation network to FB1.

SGND (Pin 12/Pin 9): Signal Ground. All the internal low

power circuitry returns to the SGND pin. Connect to a low

impedance ground, separated from the PGND node. All

feedback, compensation and soft-start connections should

return to SGND. SGND and PGND should be connected

only at a single point, near the PGND pin and the negative

terminal of the VIN bypass capacitor.

to set the channel 1 switcher output

OUT1

to monitor its real time output

OUT1

OUT1

to

FCB (Pin 13/Pin 10): Force Continuous Bar. Internally

pulled high. When FCB is shorted to GND, the controller

forces both converters to maintain continuous synchronous operation regardless of load current.

EXTREF (Pin 11, QFN Package Only): External Reference.

The EXTREF pin and the internal bandgap voltage are used

as the switcher control loop’s reference in a diode OR

manner. If the potential at the EXTREF pin is less than 0.6V,

it overrides the internal reference and lowers the switcher

output voltages. If EXTREF potential is more than 1V, the

internal bandgap voltage controls both channel output

voltages. EXTREF has no effect on the PGOOD threshold.

EXTREF is internally connected to the RUN/SS pin in the

GN28 package.

RUN/SS (Pin 14/Pin 12): Run Control and Soft-Start

Input. An internal 7µA current source pull-up and an

external capacitor to ground at this pin sets the start-up

delaly (approximately 300ms/µF), the output ramp rate

and the time delay for soft current limit. Forcing this pin

below 0.8V with an open-drain/collector transistor shuts

down the device. Pulling RUN/SS high with a current

greater than 10µA can result in malfunctioning of tracking

during start-up. Pulling RUN/SS high with currents higher

than 50µA can interfere with current limit protection.

PGOOD (Pin 15/Pin 13): Open-Drain Power Good Output.

PGOOD is pulled to ground under shutdown condition or

when any switcher output voltage is not within ±10% of its

set point .

V

(Pin 16/Pin 14): Line Feedforward Compensation

INFF

Input. Connects to the VIN power supply to provide line

feedforward compensation. A change in VIN immediately

modulates the input to the PWM comparator and changes

the pulse width in an inversely proportional manner, thus

bypassing the feedback loop and providing excellent transient line regulation. V

lowpass filter can be added to this pin to prevent noisy

signals from affecting the loop gain.

is a sensitive pin, an external

INFF

3802f

9

LTC3802

UUU

PI FU CTIO S

(28-Pin SSOP/32-Pin QFN Package)

PHASEMD (Pin 17/Pin 15): Phase Selector Input. This pin

determines the phase relationships between controller␣ 1,

controller 2 and the PLLIN signal. When PHASEMD is

floating, its value is around 2V, and the internal phaselocked loop synchronizes the falling edge of TG1 to the

falling edge of the PLLIN signal. When PHASEMD is forced

high, PLLIN leads TG1 by 90°. TG1 and TG2 remain at 180°

out of phase independent of the PHASEMD input. When

PHASEMD is forced low, an internal current source discharges the RUN/SS slowly to provide power down tracking. Avoid coupling noise into this sensitive pin.

FB2 (Pin 18/Pin 16): Channel 2 Controller Error Amplifier

Input. See FB1.

COMP2 (Pin 19/Pin 17): Channel 2 Controller Error Amplifier Output. See COMP1.

VCC (Pin 20/Pin 18): Power Supply Input. All the internal

circuits except the switcher output drivers are powered

from this pin. VCC should be connected to a low noise 5V

supply and should be bypassed to SGND with at least a

10µF capacitor in close proximity to the LTC3802.

CMPIN2 (Pin 21/Pin 19): Channel 2 Controller Comparators Input. See CMPIN1.

I

(Pin 22/Pin 20): Channel 2 Controller Current Limit

MAX2

Set. See I

PLLLPF (Pin 23/Pin 21): Phase-Locked Loop Lowpass

Filter. The phase-locked loop’s lowpass filter is tied to this

pin. Alternatively, this pin can be driven with an AC or DC

voltage source to vary the frequency of the internal

oscillator.

PLLIN (Pin 24/Pin 22): Phase-Locked Loop Input/External Synchronization Input to the Phase Detector. The

falling edge of this signal is used for frequency synchronization. When PLLIN floats or shorts to ground, the

controllers free run at 550kHz.

SW2 (Pin 25/Pin 25): Channel 2 Controller Switching

Node. See SW1.

TG2 (Pin 26/Pin 26): Channel 2 Controller Top Gate Drive.

See TG1.

BOOST2 (Pin 27/Pin 27): Channel 2 Controller Top Gate

Driver Supply. See BOOST1.

BG2 (Pin 28/Pin 28): Channel 2 Controller Bottom Gate

Drive. See BG1.

Exposed Pad (Pin 33, QFN Package Only): Exposed Pad

is PGND, must be soldered to PCB.

MAX1

.

10

3802f

BLOCK DIAGRA

PLLIN

PLLLPF

PHASEMD

V

INFF

W

TO CH2

PLL AND OSC

–

+

LINE

FEEDFORWARD

COMPENSATION

PWM

DISABLE Burst Mode

OPERATION

STOP TOP GATE

V

BURST

+

LTC3802

CHANNEL 1

CC

LOGIC

–

FCB

I

LIM

–

SUBCIRCUIT

DUPLICATE FOR

SECOND CONTROLLER

CHANNEL

–1

+

BOOST1, 2

TG1, 2

SW1, 2

PV

CC

BG1, 2

PGND

SGND

COMP1, 2

EXTREF

(QFN PACKAGE

ONLY)

V

REF

0.6V

FB1, 2

PGOOD

MPG

ERR

–

+

100µs

DELAY

FROM CH2 PGOOD

COMPARATORS

REF

POS

RESET

–

+ 15mV

÷ 5÷ 100

SOFT-

POWER DOWN

NEG

RESET

–

REF

+

– 12mVV

+

START

MAX

+

V

REF

–

+ 5%V

10µA

TRACK

7µA

I

MAX1,2

RUN/SS

–

+

FBT

CMPIN2

CMPIN1, 2

–

NPG

+

V

– 10%

REF

–

V

+ 10%

REF

PPG

+

PGOOD COMPARATORS

3802 BD

3802f

11

LTC3802

VV

R

R

OUT REF

B

=+

•1

1

WUUU

APPLICATIO S I FOR ATIO

Switching Architecture

The LTC3802 includes two step-down (buck) voltage

mode feedback switching regulator controllers. These two

controllers act independently of each other except at startup and current limit. For proper power-up sequencing,

channel 1 is designated to be the higher output voltage

channel (see Start-Up Tracking).

Each channel uses two external sychronous N-channel

MOSFETs. A floating topside driver and a simple external

charge pump provide full gate drive to each upper MOSFET.

The controller uses leading edge modulation architecture

to allow extremely low duty cycle and fast load recovery

operation. In a typical LTC3802 switching cycle, the PWM

comparator turns on the top MOSFET and charges up the

output capacitor. Some time later, an internal clock resets

the top MOSFET, turns on the bottom MOSFET and reduces the output charging current. The top gate duty cycle

is controlled by the feedback amplifier, which compares

the divided output voltage with an internal reference. This

switching cycle repeats itself at a fixed 550kHz frequency

or in synchronization with an external oscillator.

The internal master clock runs at 550kHz, turning off the

top gate once every 1.8µs. Thus, feedback loop compo-

nents and output inductors and capacitors can be scaled

to a particular operating frequency. Noise generated by the

circuit will always be in a known frequency band, with the

550kHz frequency designed to leave the 455kHz IF band

free of interference. Subharmonic oscillation and slope

compensation, common headaches with constant frequency current mode switchers, are absent in voltage

mode designs like the LTC3802. Two LTC3802 channels

run from a common clock, with the phasing chosen to be

180° from channel 1 to channel 2. This has the effect of

doubling the frequency of the switching pulses seen by the

input bypass capacitor, significantly lowering its RMS

current and reducing the capacitance required.

Feedback Control

Each LTC3802 channel senses the output voltage at V

with an internal feedback op amp (see Block Diagram).

This is a real op amp with a low impedance output, 80dB

open-loop gain and 10MHz gain-bandwidth product. The

positive input is connected to a level-shifted internal

OUT

600mV reference, while the negative input is connected to

the level-shifted FB pin. The output is connected to COMP,

which is in turn connected to the line feedforward circuit

and from there to the PWM generator. To speed up the

overshoot recovery time, the maximum potential at the

COMP pin is internally clamped at a level corresponding to

the maximum top gate duty cycle. Under start-up conditions, RUN/SS controls the COMP pin slew rate.

At steady state, as shown in Figure 1, the output of the

switching regulator is given the following equation

Unlike many regulators that use a transconductance (gm)

amplifier, the LTC3802 is designed to use an inverting summing amplifier topology with the FB pin configured as a

virtual ground. This allows the feedback gain to be tightly

controlled by external components, which is not possible

with a simple gm amplifier. In addition, the voltage feedback amplifier allows flexibility in choosing pole and zero

locations. In particular, it allows the use of “Type 3” compensation, which provides a phase boost at the LC pole

frequency and significantly improves the control loop phase

margin.

In a typical LTC3802 circuit, the feedback loop consists of

the line feedforward circuit, the modulator, the external

inductor, the output capacitor and the feedback amplifier

with its compensation network. All these components

affect loop behavior and need to be accounted for in the

loop compensation. The modulator consists of the PWM

generator, the output MOSFET drivers and the external

MOSFETs themselves. The modulator gain varies linearily

with the input voltage. The line feedforward circuit compensates for this change in gain, and provides a constant

gain from the error amplifier output to the inductor input

regardless of input voltage. From a feedback loop point of

view, the combination of the line feedforward circuit and

the modulator looks like a linear voltage transfer function

from COMP to the inductor input and has a gain roughly

equal to 22V/V. It has fairly benign AC behavior at typical

loop compensation frequencies with significant phase

shift appearing at half the switching frequency.

3802f

12

WUUU

APPLICATIO S I FOR ATIO

LTC3802

The external inductor/output capacitor combination makes

a more significant contribution to loop behavior. These

components cause a second order LC roll-off at the output

with 180° phase shift. This roll-off is what filters the PWM

waveform, resulting in the desired DC output voltage, but

this phase shift causes stability issues in the feedback loop

and must be frequency compensated. At higher frequencies, the reactance of the output capacitor will approach its

ESR, and the roll-off due to the capacitor will stop, leaving

–20dB/decade and 90° of phase shift.

Figure 1 shows a Type 3 amplifier. The transfer function of

this amplifier is given by the following equation:

+

V

COMP

V

OUT

sC R s R R C

–()

1121 133

=

()

sR C C s C C R sC R

+

11 21 1 2 21 33

()

[]

++

[]

+

(//)

+

()

The RC network across the error amplifier and the

feedforward components R3 and C3 introduce two polezero pairs to obtain a phase boost at the system unity gain

frequency, fC. In theory, the zeros and poles are placed

symmetrically around fC, and the spread between the

zeros and the poles is adjusted to give the desired phase

boost at fC. However, in practice, if the crossover frequency is much higher than the LC double-pole frequency,

this method of frequency compensation normally generates a phase dip within the unity bandwidth and creates

some concern regarding conditional stability.

If conditional stability is a concern, move the error

amplifier’s zero to a lower frequency to avoid excessive

phase dip. The following equations can be used to compute the feedback compensation components value:

choose:

f

f Crossover frequency

==

C

ff

ZERR LC

f

ZRES

ff

P ERR ESR

ff

P RES C

1

()

2

()

1

()

2

()

==

f

C

==

512133

==

==

5

1

221

RC

π

RRC

π+

()

π

221 2

RC C

1

π

233

RC

SW

10

1

(//)

Required error amplifier gain at frequency fC:

22

f

40 1 20 1 20

≈+

log – log – log

20

log •

R

≈

R

where A

MOD

C

f

LC

11

2

1

f

LC

+

f

C

f

C

++

1

f

ESRLCESR LC

++

is the modulator and line feedforward gain

f

C

+

f

ESR

f

() () ()

222

P RESCP RES Z RES

f

ff

ff

f

Z RES

f

–

112+

2

f

P RESC()

A

()

MOD

–

()

f

and is equal to:

VDC

A

MOD

IN MAX MAX

≈=≈

•

()

V

SAW

•.

30 0 89

.

12

22

VV

/

Once the value of resistor R1, poles and zeros location

have been decided, the value of R2, C1, C2, R3 and C3 can

be obtained from the above equations.

f Switching frequency

=

SW

f

LC

f

ESR

=

π

2

=

π

2

1

LC

OUT

1

RC

ESR OUT

V

OUT

C3

R1 R3

R

B

V

REF

C2

C1

R2

–

FB

+

Figure 1. Type 3 Amplifier Compensation

COMP

GAIN (dB)

GAIN

0

PHASE

–1

BOOST

–1+1

FREQ

–90

–180

–270

–380

3802 F01

3802f

13

PHASE (DEG)

LTC3802

WUUU

APPLICATIO S I FOR ATIO

Compensating a switching power supply feedback loop is

a complex task. The applications shown in this data sheet

show typical values, optimized for the power components

shown. Though similar power components should suffice, substantially changing even one major power component may degrade performance significantly. Stability

also may depend on circuit board layout. To verify the

calculated component values, all new circuit designs

should be prototyped and tested for stability.

Overvoltage Protection and Power Good Flag

Notice that the FB pin is the feedback amplifier’s virtual

ground node (offset by V

pensation network does not include local DC feedback

around the amplifier, the DC level at FB will be an accurate

replica of the output voltage, divided down by the resistive

divider. However, the compensation capacitors will tend

to attenuate AC signals at FB, especially during quick

transients. Because of this delay in the servo loop, the duty

cycle is not able to adjust immediately to shifts in the

output voltage. This problem is most apparent at high

input and low output voltages. Under transient conditions,

a slow reaction in the duty cycle could cause a large step

in the output voltage. The LTC3802 avoids this voltage

instability through the use of an additional comparator

input pin, CMPIN, which provides real time measurement

of the output voltage. A duplicate FB divider, R1 and R

should be connected to this pin. A small feedforward

capacitor can be added across the top resistor to speed up

the comparators.

The MAX comparator monitors the output voltage through

the CMPIN pin. If the output moves 5% above its nominal

value, the comparator immediately turns the top MOSFET

(QT) off and the bottom MOSFET (QB) on and maintains

this state until the output falls back within 5% of its nominal value. This pulls the output down as fast as possible,

preventing damage to the (often expensive) load. If CMPIN

rises because the output is shorted to a higher supply, QB

will stay on until the short goes away, the higher supply

current limits or QB dies trying to save the load. This behavior provides maximum protection against overvoltage

fault at the output, while allowing the circuit to resume

normal operation when the fault is removed.

). Because the typical com-

REF

B

CMPIN is also used as the input for the positive power good

comparator PPG and the negative power good comparator

NPG. The PPG comparator goes high if the potential at

CMPIN is 10% above the nominal value. The NPG comparator fires if CMPIN potential is 10% lower than the nominal

value. The output of PPG and NPG is connected to the

PGOOD pin through the transistor MPG (see Block Diagram). PGOOD is an open-drain output and requires an

external pull-up resistor. If channel 1 and 2 regulator output voltages are within ±10% of their nominal values, the

transistor MPG shuts off and PGOOD is pulled high by the

external pull-up resistor. If any of the two outputs is outside the 10% window for more than 100µs, PGOOD pulls

low indicating that at least one output is out of regulation.

For PGOOD to go high, both switcher outputs must be in

regulation. PGOOD remains active during soft-start and current limit. Upon power-up, PGOOD is forced low. As soon

as the RUN/SS pin rises above the shutdown threshold, the

power good comparators take over and control the transistor MPG directly. The 100µs delay ensures that short out-

put transient glitches that are successfully “caught” by the

power good comparators don’t cause momentary glitches

at the PGOOD pin.

Current Limit Protection

The LTC3802 includes an onboard current limit circuit that

limits the maximum output current to a user-programmed

level. It works by sensing the voltage drop across QB when

QB is on and comparing that voltage to a user-programmed voltage at I

10µA pull-up, enabling the user to set the voltage at I

with a single resistor, R

comparator reference input is equal to V

(see Block Diagram).

Any time QB is on and the current flowing to the output is

reasonably large, the SW node at the drain of QB will be

somewhat negative with respect to PGND. Since QB looks

like a low value resistor during its on-time, the voltage

drop across it is proportional to the current flowing in it.

The LTC3802 senses this voltage, inverts it and compares

it to the current comparator reference. The current comparator begins limiting the output current when the magnitude of the negative voltage is larger than its reference.

MAX

. The I

IMAX

pin includes a trimmed

MAX

, to ground. The current

divided by 5

IMAX

MAX

14

3802f

WUUU

APPLICATIO S I FOR ATIO

LTC3802

The current limit detector is connected to an internal

100µA current source. Once current limit occurs, this

current begins to discharge the soft-start capacitor at

RUN/SS, reducing the duty cycle and controlling the

output voltage until the current drops below the limit. The

soft-start capacitor needs to move a fair amount before it

has any effect on the duty cycle, adding a delay until the

current limit takes effect. This allows the LTC3802 to

experience brief overload conditions without affecting the

output voltage regulation. The delay also acts as a pole in

the current limit loop to enhance loop stability.

Under severe short-circuit conditions, if the load current is

1.5 times larger than the programmed current limit threshold, the LTC3802 shuts off the top MOSFET immediately.

This stops the increase in the inductor current. At this

moment, if CMPIN is 10% lower than its nominal value, the

LTC3802 hard current limit latches and discharges the

RUN/SS capacitor with a current source of more than 1mA

until RUN/SS hits its shutdown threshold. Once RUN/SS

is completely discharged, the LTC3802 cycles its softstart again.

Programming the current limit on the LTC3802 is straightforward. To set the current limit, calculate the expected

voltage drop across QB at the maximum desired current:

V

= (I

PROG

I

should be set much higher than the expected oper-

LIMIT

ating current, to allow for MOSFET R

temperature. Power MOSFET R

LIMIT

)(R

DS(ON)

)

changes with

DS(ON)

varies from MOSFET

DS(ON)

to MOSFET, limiting the accuracy obtainable from the

LTC3802 current limit loop. Setting I

to 150% of the

LIMIT

maximum normal operating current is usually safe and will

adequately protect the power components if they are

chosen properly. Note that ringing on the switch node can

cause an error for the current limit threshold. This factor

will change depending on the layout. The SW node should

have minimum routing from the MOSFETs to the LTC3802

to reduce parasitic inductor and hence ringing. V

then programmed at the I

pin using the internal 10µA

MAX

PROG

is

pull-up current and an external resistor:

V

•

R

IMAX

=

PROG

A

µ510

The resulting value of R

should be checked in an

IMAX

actual circuit to ensure that the current circuit kicks in as

expected. Circuits that use very low values for R

IMAX

(<25k) should be checked carefully, since small changes

in R

can cause large I

IMAX

changes when the switch

LIMIT

node ringing makes up a large percentage of the total

V

PROG

value. If V

is set too low, the LTC3802 may fail

PROG

to start up. The LTC3802 current limit is designed primarily as a disaster preventing, “no blow up” circuit, and is

not useful as a precision current regulator.

The LTC3802 bottom MOSFET VDS current sensing architecture not only eliminates the external current sense

resistors and the corresponding power losses in the high

current paths, it allows a wide range of output voltage

setting, including extremely low duty cycle operation. On

the other hand, for high input voltage with small output

inductance applications, care must be taken to avoid

inductor saturation during dead-short conditions. As soon

as the output short circuits, the controller instantaneously

enters maximum duty cycle operation.

During the top MOSFET on interval, the current comparator is not monitoring the current and there is no current

limit action until the bottom MOSFET turns on and the

inductor current exceeds its hard current limit threshold.

Typically, the top MOSFET and the inductor need to

withstand one clock period of transient high current operation until the hard current limit operation engages.

Peak currents can exceed 6 times the maximum DC output

current during this period. Most MOSFETs allow 10µs of

high current and this short duration of current should not

damage the MOSFET. Nevertheless, it is a good idea to

reduce the peak inductor current. This can be achieved by

having a larger inductance to limit the short-circuit current

slew rate, or an inductor with a saturation current that is

higher than the hard current limit threshold. Alternatively,

an inductor core material with a softer saturation characteristic such as iron powder can be used.

Shutdown/Soft-Start

The RUN/SS pin performs two functions: when pulled to

ground it shuts down the LTC3802, and it acts as a

conventional soft-start pin, enforcing a maximum duty

cycle limit proportional to the voltage at RUN/SS. An

3802f

15

LTC3802

WUUU

APPLICATIO S I FOR ATIO

internal 7µA current source pull-up is connected to the

RUN/SS pin, allowing a soft-start ramp to be generated

with a single external capacitor to ground. The 7µA current

source is active even when the LTC3802 is shut down,

ensuring the device will start when the external pull-down

at RUN/SS is released. Under shutdown conditions, the

LTC3802 goes into a micropower sleep mode, and the

quiescent current drops to 100µA.

The RUN/SS pin shuts down the LTC3802 when it falls

below 0.8V (Figure 2). Between about 0.8V and 2V, the

LTC3802 wakes up and the duty cycle is kept to a miminum.

As the potential at RUN/SS goes higher, the duty cycle

increases linearly between 2V and 3.2V, reaching its final

value of 89% when RUN/SS exceeds 3.2V. Prior to this

point, the feedback amplifier will assume control of the

loop and the output will come into regulation. Note that the

RUN/SS linear range varies with the potential at V

INFF

; for

5V input voltage, the RUN/SS active range reduces to

2V-2.25V.

The value of the soft-start capacitor, CSS, may depend on

the input and output voltages, inductor value, output

capacitance and load current. The inductor’s start-up

current (from V

= 0V), can be much higher than its

OUT

steady-state current. The difference depends on the input

power supply slew rate, the input and output voltages, the

LTC3802 soft-start slew rate, and the inductor and output

capacitor values.

values. These values establish the transient load recovery

time. In general, a low value inductor combined with a high

value capacitor yields a short transient load recovery time

at the expense of higher inductor ripple and start-up

current. These components, together with a small softstart capacitor, can also cause high inrash current. This

triggers the LTC3802 current limit comparator and forces

the LTC3802 to repeat the soft-start cycle, never allowing

the supply to start.

Start-up problems can also occur when a small soft-start

capacitor is used with a small output inductor and

capacitor. High input voltages generate high inrash currents, charging the output capacitor quickly and causing

the output to overshoot. The LTC3802 OVP comparator

turns off the top MOSFET once the output is 5% higher

than its nominal value. However, the residual energy in

the inductor will continue to charge the output capacitor,

forcing the output voltage to increase further until the

inductor energy is depleted. This overshoot at the output

causes the feedback loop to operate nonlinearly; the

output tends to ring for several cycles until the loop

mechanism is restored.

Therefore, select CSS with start-up in mind. Choosing C

SS

to ensure that there is no output overshoot and the inrush

current is not able to trigger the current comparator. A

minimum recommended soft-start capacitor of

CSS = 0.1µF will be sufficient for most applications.

For a given application, the known input and output

requirements determine the output inductor and capacitor

V

OUT

0V

START-UP

5V

RUN/SS

3.2V

2V

MINIMUM DUTY CYCLE

0.8V

0V

POWER DOWN MODE

LTC3802 ENABLE

Figure 2. Soft-Start Operation in Start-Up and Current Limit

NORMAL OPERATION

CURRENT LIMIT

COMP CONTROLS DUTY CYCLE

RUN/SS CONTROLS DUTY CYCLE

3802 F02

16

Undervoltage Lockout

The LTC3802 is designed for wide VIN operation. The

internal UVLO circuit monitors the VCC and V

potential

INFF

and starts operation as long as they are above their 2.5V

UVLO thresholds. For high VIN supply operation, the low

UVLO threshold should not cause any problem under

typical application conditions. Upon power-up, once the

VIN potential is higher than the UVLO threshold, the

LTC3802 releases the RUN/SS node and allows the startup current to charge the soft-start capacitor. The time

interval for the RUN/SS potential to ramp from 0.8V to 2V

allows the VIN supply to slew to its steady-state potential.

A 0.1µF soft-start capacitor creates a 17ms time delay

before the driver starts switching. Most power supplies

have a start-up time well within this time interval. For some

3802f

WUUU

APPLICATIO S I FOR ATIO

LTC3802

special power supplies with a slow start-up slew rate, the

LTC3802 drivers might start switching before the input

supply reaches its steady-state value. The high inrush

current through the input power cable might cause the V

IN

supply to dip below the UVLO threshold and cause startup problems. Figure␣ 3 shows a simple circuit to fix this

problem. The selection of the zener voltage allows the V

IN

UVLO trip point to be programmed externally.

V

> V

IN

Z

1N4699

V

Z

100k

10k

100k

= 12V

Q1

2N3904

Figure 3. External UVLO Setting

Q2

2N3904

3802 F03

LTC3802

RUN/SS

C

SS

Start-Up Tracking

Many DSP chips, microprocessors, FPGAs and ASICs

require multiple power supplies for the core and I/O

sections. Internally, the core and I/O blocks are isolated by

structures which may become forward biased if the supply

voltages are not at specified levels. During power-up and

power-down operations, differences in the starting point

and ramp rates of the two supplies may cause current to

flow between the isolation structures which, when prolonged and excessive, can reduce the useable life of the

semiconductor device. These currents can also trigger

latch-up in devices, leading to device failure.

Of greater concern than internal isolation of core and I/O

structures are system-level concerns, such as bus

contention between the I/O pins of the DSP and external

peripheral devices. Power supply sequencing between the

core and I/O may be required to prevent bidirectional I/O

pins of the DSP and a peripheral device from opposing

each other. Since the bus control logic originates in the

core section, powering the I/O prior to the core may cause

the DSP and peripheral pins to be configured

simulatneously as outputs. If the data values on each side

are opposing, then the output drivers contend for control,

causing excessive current flow and eventually device

failure.

The LTC3802 can be configured to give two different

power-up/power-down slew rates to meet different application requirements: ratiometric and coincident tracking

configurations (Figure 4). With a ratiometric configuration, the LTC3802 produces two different output slew

rates (with V

OUT1

> V

). Because each channel’s slew

OUT2

rate is proportional to its corresponding output voltage,

the two output voltages reach their steady-state value at

about the same time. The coincident configuration produces the same slew rate at both outputs, so that the lower

output voltage channel reaches its steady state first.

Figure 4 shows the simplified schematic to realize this

power-up function. During power-up, the tracking amplifier TRACK servos the tracking feedback loop and forces

FBT to be at the same potential as CMPIN2.

For ratiometric start-up, set:

RT5 = R51

or remove resistors RT4 and RT5 and short FBT to CMPIN1.

At power-up, if the channel 2 output voltage slew rate is

too fast, or CMPIN2 is higher than FBT, the tracking

amplifier will force a smaller channel 2 duty cycle.

Channel␣ 1’s duty cycle is controlled by the RUN/SS pin and

is not affected by the tracking amplifier.

For coincident start-up, set:

RT5 = R52

During power-up, if the channel 1 output voltage is higher

than that of channel 2, or if FBT is higher than CMPIN2, the

tracking amplifier TRACK starts to discharge the C

SS

capacitor and forces both channels to have the same duty

cycle and output voltage. The tracking amplifier stops

discharging once channel 2 reaches its negative power

good threshold.

To have the proper power-down sequence, ground the

PHASEMD pin. This turns on an internal current source

which slowly discharges the soft-start capacitor. Once the

RUN/SS potential is low enough to control the duty cycle,

the tracking amplifier takes control and servos the feedback loop to produce the selected output ramp. The

LTC3802 tracking function can be easily disabled by

disconnecting the FBT resistive divider and shorting FBT

to CMPIN2.

3802f

17

LTC3802

WUUU

APPLICATIO S I FOR ATIO

V

OUT1

R

R12

EXTREF

REF

RB2R52

V

OUT2

R42

3802 F04

L2L1

+

C

OUT2

+

–

CMPIN2

V

WITH

OUT1

10Ω LOAD

V

WITH

OUT2

10Ω LOAD

LFF

AND

PWM

LFF

R41

T4

EXTREF

REF

C

OUT1

+

R11R

AND

PWM

+

–

R51

R

CMPIN1

B1

0.5V/DIV

FBT

RATIOMETRIC TRACKING

= R51

R

T5

C

= 1µF

SS

T5

SAW1

CH1

DUTY CYCLE

CONTROL

V

MUST BE HIGHER THAN V

OUT1

R11 = R41 = RT4 = R12 = R42

R

= R51, RB2 = R52

B1

V

WITH

OUT1

10Ω LOAD

V

WITH

OUT2

10Ω LOAD

1.7V

+

PHASEMD

POWER-UP/-DOWN OUTPUTS

–

OUT2

TRACK

SAW2

C

SS

7µA

CH2

DUTY CYCLE

CONTROL

RUN/SS

14µA

+–

COINCIDENT TRACKING

= R52

R

T5

C

= 1µF

SS

0.5V/DIV

10ms/DIV

Figure 4. Simplified Power-Up/Power-Down Output Tracking Schematic

The QFN version of the LTC3802 provides an additional

reference pin for external ratiometric start-up. If the potential at the EXTREF pin is less than 0.6V, it overrides the

internal reference. This pin can be connected to an external

ramp to control the output slew rate. If external tracking is

not required, connect EXTREF to a potential somewhat

larger than 0.6V or short EXTREF to the RUN/SS pin. The

EXTREF pin should never be allowed to float. In the GN28

package, EXTREF is internally shorted to the RUN/SS pin.

Burst Mode Operation

The LTC3802 switcher supply has two modes of operation. Under heavy loads, it operates as a fully synchronous, continuous conduction switching regulator. In this

mode of operation (continuous mode), the current in the

inductor flows in the positive direction (towards the output) during the entire switching cycle, constantly supplying current to the load. In this mode, the synchronous

10ms/DIV

switch (QB) is on whenever QT is off, so the current always

flows through a low impedance switch, minimizing voltage drop and power loss. This is the most efficient mode

of operation at heavy loads, where the resistive losses in

the power devices are the dominant loss term.

Continuous mode works efficiently when the load current

is greater than half of the ripple current in the inductor. In

a buck converter like the LTC3802, the average current in

the inductor (averaged over one switching cycle) is equal

to the load current. The ripple current is the difference

between the maximum and the minimum current during

a switching cycle (see Figure 5a). The ripple current

depends on inductor value, clock frequency and output

voltage, but is constant regardless of load as long as the

LTC3802 remains in continuous mode. See the Inductor

Selection section for a detailed description of ripple

current.

3802f

18

WUUU

APPLICATIO S I FOR ATIO

LTC3802

As the output load current decreases in continuous mode,

the average current in the inductor will reach a point where

it drops below half the ripple current. At this point, the

current in the inductor will reverse during a portion of the

switching cycle, or begin to flow from the output back to

the input. This does not adversely affect regulation, but

does cause additional losses as a portion of the inductor

current flows back and forth through the resistive power

switches, giving away a little more power each time and

lowering the efficiency. There are some benefits to allowing this reverse current flow: the circuit will maintain

regulation even if the load current drops to zero and the

output ripple voltage and frequency remain constant at all

loads, easing filtering requirements. However, continuous

mode at low output current does cause losses in efficiency. A portion of the inductor current flows back and

forth through the resistive power switches, causing I2R

losses. The drivers continue to switch QT and QB on and

off once a cycle. Each time an external MOSFET is turned

on, the internal driver must charge its gate to a potential

above the MOSFET’s source voltage; when the MOSFET is

turned off, that charge is lost to ground or SW. At the high

switching frequencies, the lost gate charges can add up to

tens of millicoulombs. As the load current continues to

drop, these charges quickly become the dominant power

loss term, reducing efficiency once again.

I

AVERAGE

I

RIPPLE

INDUCTOR CURRENT

TIME

Figure 5a. Continuous Mode

3802 F05a

To minimize the switching loss and reverse current flow at

light loads, the LTC3802 switches to a second mode of

operation: Burst Mode operation (Figure 5b). In Burst

Mode operation, at the end of the QB cycle, if the inductor

current approaches zero or goes negative, the LTC3802

turns off both drivers. The actual cutoff threshold is

proportional to the I

V

IMAX

––

3

mV

setting and is equal to:

MAX

100

The –3mV built-in offset overcomes the random mismatch in the burst compararator trip point and allows

Burst Mode operation at no load.

Once both MOSFETs shut off, the voltage at the SW pin will

float around V

, and the inductor current and the voltage

OUT

across the inductor will be close to zero. This prevents

current from flowing backwards in QB, eliminating that

power loss term.

The moment the LTC3802 enters Burst Mode operation,

both drivers skip a number of switching cycles until the

internal 36µs timeout forces the switcher to return to

continuous operation. This timeout eliminates the audible

noise from certain types of inductors when they are lightly

loaded. After the 36µs timeout, the LTC3802 forces one

continuous mode cycle and checks the inductor current at

the end of the period. If it is still too small, it enters Burst

Mode operation again. This pattern repeats until the output is loaded. The LTC3802 returns to continuous mode

operation if it detects that CMPIN potential is 12mV below

or 15mV above its nominal bandgap voltage. Immediately

after returning to continuous mode operation, the regulator output might continue to droop slightly until the feedback loop responds and requests an increase in duty cycle.

During sudden transient steps, the regulator output ripple

is limited by the feedback loop transient response and is

independent of the mode of operation.

I

RIPPLE

INDUCTOR CURRENT

Figure 5b. Burst Mode Operation

TIME

3802 F05b

I

AVERAGE

The small 15mV and –12mV offset at the POS and NEG

RESET comparators ensure that after a transient load step,

the LTC3802 returns to continuous mode quickly. This

minimizes the output ripple under Burst Mode operation.

For proper Burst Mode operation, the LTC3802 requires

very precise CMPIN and FB sensing. To realize this,

CMPIN and FB must use the same resistive divider values

3802f

19

LTC3802

V

CC

LTC3802

PLLLPF

R

LP

C

LP

3806 F06

VCO

INTERNAL MASTER CLOCK

÷12

PHASEMD

PLLIN

PHASE DETECTOR

WUUU

APPLICATIO S I FOR ATIO

and all resistors should have better than 1% tolerance. If

this is not possible and Burst Mode operation is required,

the potential at CMPIN can be set slightly higher than FB

by using a slightly bigger resistor from CMPIN to ground.

This removes the requirement of having expensive resistors at the FB and CMPIN pins, at the expense of having a

higher Burst Mode ripple and slightly different overvoltage and power good thresholds. To ensure clean Burst

Mode operation, the CMPIN and FB resistive divider requires good layout technique. Both resistive dividers must

be connected to the same nodes and away from high

current paths.

Low load current efficiency depends strongly on proper

Burst Mode operation. In an ideal system, the gate drive is

the dominant loss term at low load currents. Burst Mode

operation turns off all output switching for several clock

cycles in a row, significantly cutting gate drive losses. As

the load current in Burst Mode operation falls toward zero,

the current drawn by the LTC3802 falls to a quiescent

level—about 6.5mA. To maximize low load efficiency,

make sure the LTC3802 is allowed to enter Burst Mode

operation as cleanly as possible.

The phase detector used is an edge sensitive digital circuit

which provides zero degree phase shift between the external and internal oscillators. This type of phase detector will

not lock up on an input frequency close to the harmonics

of the VCO center frequency. The output of the phase

detector is a complementary pair of current sources

charging or discharging the external filter network on the

PLLLPF pin. A simplified block diagram is shown in

Figure␣ 6.

If the external frequency, f

lator frequency, f

, current is sourced continuously,

OSC

pulling up the PLLLPF pin. When f

, is greater than the oscil-

PLLIN

is less than f

PLLIN

OSC

,

current is sunk continuously, pulling down the PLLLPF

pin. If f

PLLIN

and f

are the same but exhibit a phase

OSC

difference, the current sources turn on for a period corresponding to the phase difference. Thus the voltage on the

PLLLPF pin is adjusted until the phase and frequency of

the external and internal oscillators are identical. At this

stable operating point the phase comparator output is

open and the filter capacitor, CLP, holds the voltage. When

locked, the PLL aligns the turn off of the top MOSFET to the

falling edge of the synchronizing signal.

Operating Frequency/Frequency Synchronization

The LTC3802 controller uses a constant frequency, phaselockable internal oscillator with its frequency determined

by an internal capacitor. This capacitor is charged by a

fixed current plus an additional current that is proportional

to the voltage applied to the PLLLPF pin. When the PLLIN

pin is not used, an internal pull-down current source

forces PLLIN to ground and the controller runs at a fixed

550kHz switching frequency.

The phase-locked loop allows the internal oscillator to be

synchronized to an external source via the PLLIN pin. The

phase-locked loop consists of an internal voltage controlled oscillator, a divide by 12 frequency divider and a

phase detector. The voltage controlled oscillator monitors

the output of the phase detector at the PLLLPF pin. It

provides a linear relationship between the PLLLPF potential and the master oscillator frequency. A DC voltage input

from 0.5V to 1.9V corresponds to a 330kHz to 750kHz

master switching frequency.

20

The loop filter components, CLP and RLP, smooth out the

current pulses from the phase detector and provide a

stable input to the voltage controlled oscillator. The filter

components, CLP and RLP, determine how fast the loop

acquires lock. Typically RLP = 10k and CLP is between

0.01µF and 0.1µF.

The PHASMD pin determines the relative phases between

the TG1, TG2 and the PLLIN signals. When PHASEMD is

Figure 6. Phase-Locked Loop Block Diagram

3802f

WUUU

APPLICATIO S I FOR ATIO

LTC3802

floating, it sits at around 2V and the internal phase-locked

loop synchronizes TG1’s falling edge to the falling edge of

the PLLIN signal. When PHASEMD is high, these two

signals are 90° out of phase. TG1 and TG2 remains 180°

out of phase independent of PHASEMD input.

The PHASEMD signal together with the PLL circuit can be

used to synchronize an additional LTC3802 power supply

circuit to provide a 4-phase, 4-output solution. Compared

to an in-phase multiple controller solution, the LTC3802’s

4-phase design reduces the input capacitor ripple current

requirements and efficiency losses because the peak

current drawn from the input capacitor is spaced out

within the switching cycle.

EXTERNAL COMPONENTS SELECTION

VCC and PVCC Power Supplies

Power for the top and bottom MOSFET drivers is derived

from the PVCC pin; the internal controller circuitry is derived from the VCC pin. Under typical operating conditions,

the total current consumption at these two pins should be

well below 100mA. Hence, PVCC and VCC can be connected

to an external auxiliary 5V power supply. If an auxiliary

supply is not available, a simple zener diode and a darlington

NPN buffer can be used to power up these two pins as

shown in Figure 7. To prevent switching noise from coupling to the sensitive analog control circuitry, VCC should

V

R

Z

2k

100Ω

V

5.6V

Q1: ZETEX FZT603

V

: MM5Z6V2ST1

Z

+

Q1

Z

Figure 7. LTC3802 Power Supply Inputs

C

IN

DCP

C

QT

V

OUT

C

OUT

10Ω

L

+

D1

10µF

+

10µF

CP

QB

+

0.1µF

0.1µF

BOOST

TG

SW

BG

PV

CC

PGND

V

CC

V

LTC3802

SGND

IN

INFF

3802 F07

have a 10µF bypassed capacitor close to the device. The

BiCMOS process that allows the LTC3802 to include large

on-chip MOSFET drivers also limits the maximum PV

CC

and VCC voltage to 7V. This limits the practical maximum

auxiliary supply to a loosely regulated 7V rail. If VCC drops

below 2.5V or PVCC drops below VCC by more than 1V, the

LTC3802 goes into undervoltage lockout and prevents the

power switches from turning on.

Top MOSFET Driver Supply

An external bootstrap capacitor, CCP, connected to the

BOOST pin supplies the gate drive voltage for the topside

MOSFET. This capacitor is charged through diode DCP

from PVCC when the switch node is low. When the top

MOSFET turns on, the switch node rises to VIN and the

BOOST pin rises to approximately VIN + PVCC. The boost