Linear Technology LTC1344 Datasheet

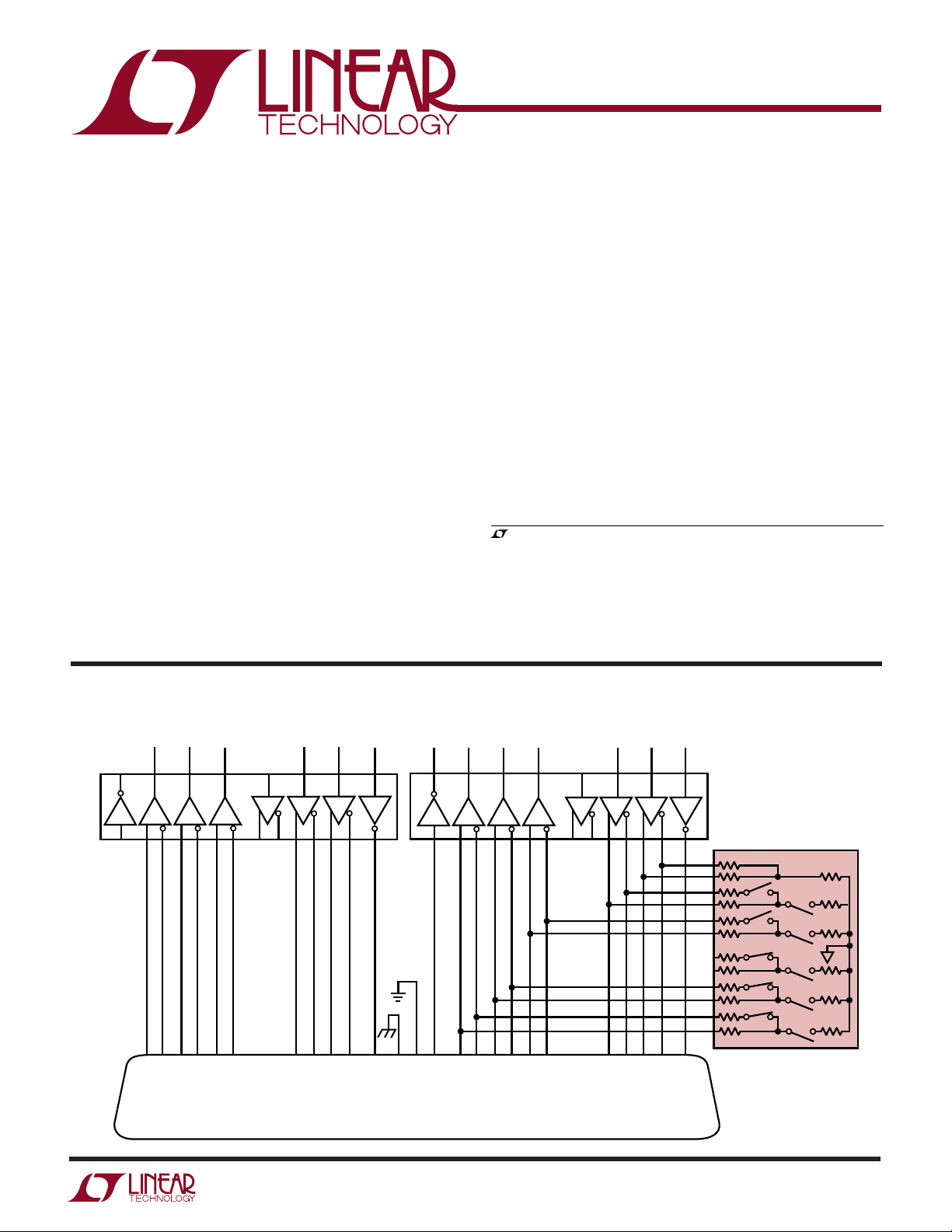

D2

LTC1343

RTSDTRDSR DCDCTS RL

D1

D3D4

R1

R3R4R2

D2

LTC1343

LL

TXDSCTETXCRXCRXDTM

LL A (141)

TXD A (103)

TXD B

SCTE A (113)

SCTE B

RXC A (115)

RXC B

RXD A (104)

RXD B

RTS A (105)

RTS B

DTR A (108)

DTR B

CTS A (106)

CTS B

TM A (142)

SGND (102)

SHIELD (101)

18

21424111512179314192023622 810513 21 7 1625

1344 TA01

DB-25 CONNECTOR

LTC1344

D1

D3D4

R1

R3R4R2

TXC A (114)

TXC B

RL A (140)

DCD A (109)

DCD B

DSR A (107)

DSR B

FEATURES

■

Software-Selectable Cable Termination for:

RS232 (V.28)

RS423 (V.10)

RS422 (V.11)

RS485

RS449

EIA530

EIA530-A

V.35

V.36

X.21

■

Outputs Won’t Load the Line with Power Off

U

APPLICATIO S

LTC1344

Software-Selectable

Cable Terminator

U

DESCRIPTIO

The LTC®1344 features six software-selectable

multiprotocol cable terminators. Each terminator can be

configured as an RS422 (V.11) 100Ω minimum differen-

tial load, V.35 T-network load or an open circuit for use

with RS232 (V.28) or RS423 (V.10) transceivers that

provide their own termination. When combined with the

LTC1343, the LTC1344 forms a complete software-selectable multiprotocol serial port. A data bus latch feature

allows sharing of the select lines between multiple interface ports.

The LTC1344 is available in a 24-lead SSOP.

, LTC and LT are registered trademarks of Linear Technology Corporation.

■

Data Networking

■

CSU and DSU

■

Data Routers

TYPICAL APPLICATION

Daisy-Chained Control Outputs

U

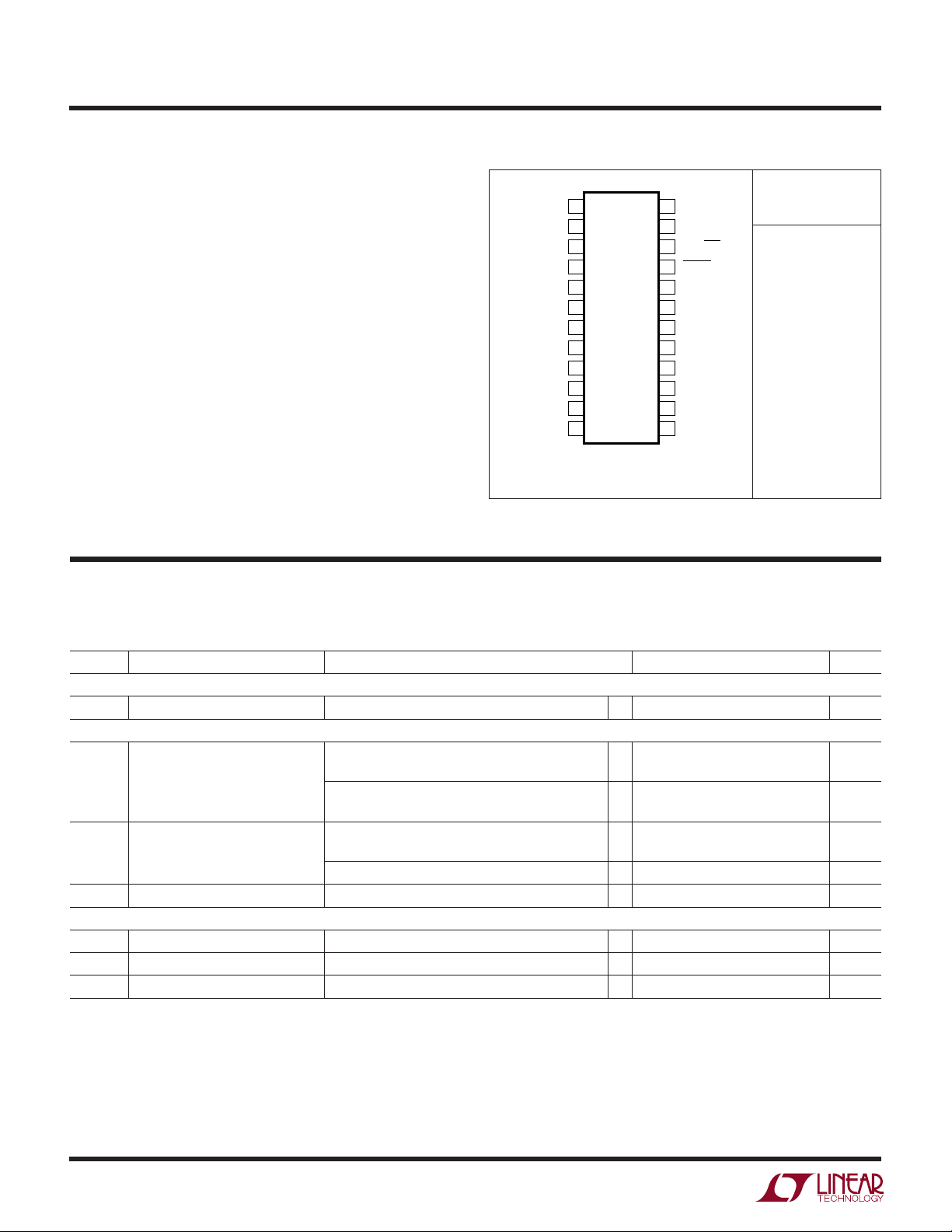

1

LTC1344

1

2

3

4

5

6

7

8

9

10

11

12

TOP VIEW

G PACKAGE

24-LEAD PLASTIC SSOP

24

23

22

21

20

19

18

17

16

15

14

13

M0

V

EE

R1C

R1B

R1A

R2A

R2B

R2C

R3A

R3B

R3C

GND

M1

M2

DCE/DTE

LATCH

R6B

R6A

R5A

R5B

R4A

R4B

V

CC

GND

WW

W

U

ABSOLUTE MAXIMUM RATINGS

(Note 1)

Positive Supply Voltage (VCC)................................... 7V

Negative Supply Voltage (VEE) ........................... –13.2V

Input Voltage (Logic Inputs) .... VEE – 0.3V to VCC + 0.3V

Input Voltage (Load Inputs) .................................. ±18V

Operating Temperature Range

LTC1344C ............................................... 0°C to 70°C

LTC1344I........................................... –40°C to 85°C

Storage Temperature Range ................ –65°C to 150°C

Lead Temperature (Soldering, 10 sec)................. 300°C

/

PACKAGE

T

JMAX

Consult factory for Military grade parts.

O

RDER I FOR ATIO

= 150°C, θJA = 100°C/W

WU

ORDER PART

NUMBER

LTC1344CG

LTC1344IG

U

ELECTRICAL CHARACTERISTICS

The ● denotes the specifications which apply over the full operating temperature range, otherwise specifications are at TA = 25°.

V

= 5V ±5%, VEE = –5V ±5%, T

CC

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

Supplies

I

CC

Terminator Pins

R

V.35

R

V.11

I

LEAK

Logic Inputs

V

IH

V

IL

I

IN

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: All currents into device pins are positive; all currents out of device

pins are negative. All voltages are reference to ground unless otherwise

specified.

Supply Current All Digital Pins = GND or V

Differential Mode Impedance All Loads (Figure 1), – 2V ≤ VCM ≤ 2V (Commercial) ● 90 103 110 Ω

Common Mode Impedance All Loads (Figure 2), – 2V ≤ V

Differential Mode Impedance All Loads (Figure 1), – 7V ≤ VCM ≤ 7V (Commercial) 100 104 Ω

High Impedance Leakage Current All Loads, –7V ≤ VCM ≤ 7V (Commercial) ● ±1 ±50 µA

Input High Voltage All Logic Input Pins ● 2V

Input Low Voltage All Logic Input Pins ● 0.8 V

Input Current All Logic Input Pins ● ±10 µA

A

= T

MIN

to T

(Notes 2, 3) unless otherwise noted.

MAX

CC

≤ 2V (Commercial) ● 135 153 165 Ω

CM

All Loads (Figure 1), – 2V ≤ VCM ≤ 2V (Industrial) ● 90 104 125 Ω

All Loads (Figure 2), – 2V ≤ V

All Loads (Figure 1), V

All Loads (Figure 1), V

CM

CM

≤ 2V (Industrial) ● 130 153 170 Ω

CM

= 0V (Commercial) ● 100 104 110 Ω

= 0V (Industrial) ● 95 104 125 Ω

Note 3: All typicals are given at VCC = 5V, VEE = –5V, T

● 200 700 µA

= 25°C.

A

2

W

VCC VOLTAGE (V)

103

DIFFERENTIAL MODE IMPEDANCE (Ω)

104

105

1344 G03

4.6 4.8 5.0 5.2 5.4

U

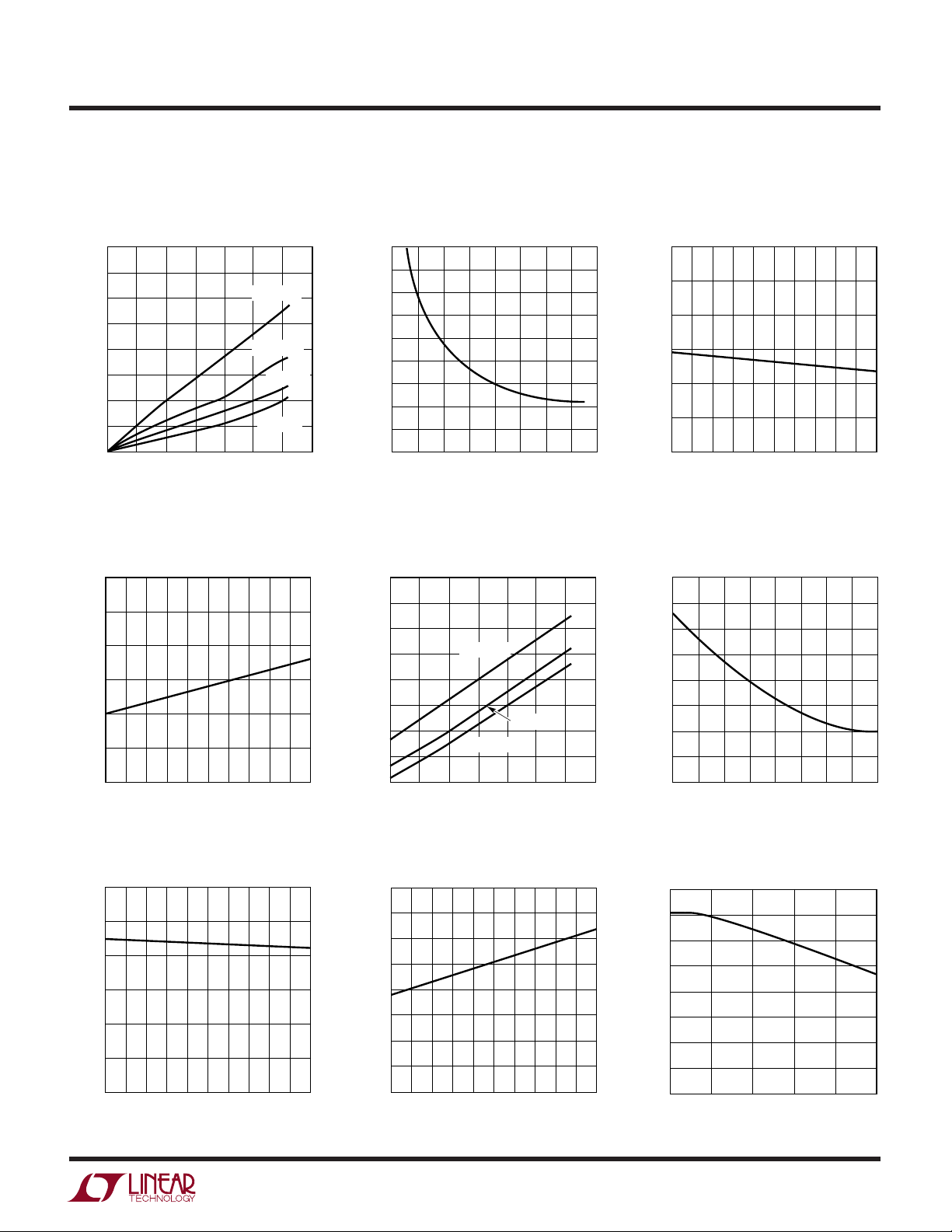

TYPICAL PERFORMANCE CHARACTERISTICS

LTC1344

V.11 or V.35 Differential Mode

Impedance vs Temperature

120

115

110

105

DIFFERENTIAL MODE IMPEDANCE (Ω)

100

–40

–20 0 40

20

TEMPERATURE (°C)

V.11 or V.35 Differential Mode

Impedance vs Negative Supply

Voltage (VEE)

105

VCM = –7V

= –2V

V

CM

VCM = 0V

V

= 7V

CM

60 80 100

1344 G01

V.11 or V.35 Differential Mode

Impedance vs Common Mode

Voltage

108

106

104

102

DIFFERENTIAL MODE IMPEDANCE (Ω)

100

–8

–6 –4 –2 0 2 4 8

COMMON MODE VOLTAGE (V)

V.35 Common Mode Impedance

vs Temperature

165

160

VCM = –2V

V.11 or V.35 Differential Mode

Impedance vs Supply Voltage

(VCC)

6

1344 G02

V.35 Common Mode Impedance

vs Common Mode Voltage

158

156

104

DIFFERENTIAL MODE IMPEDANCE (Ω)

103

–5.4 – 5.2 –5.0 –4.8 – 4.6

V.35 Common Mode Impedance

vs Supply Voltage (VCC)

153

152

COMMON MODE IMPEDANCE (Ω)

151

4.6 4.8 5.0 5.2 5.4

VEE VOLTAGE (V)

VCC VOLTAGE (V)

1344 G04

1344 G07

155

150

COMMON MODE IMPEDANCE (Ω)

145

–20 0 40

–40

TEMPERATURE (°C)

VCM = 0V

VCM = 2V

20

V.35 Common Mode Inpedance

vs Negative Supply Voltage (VEE)

154

153

152

151

COMMON MODE IMPEDANCE (Ω)

150

–5.4

–5.2

–5.0

VEE VOLTAGE (V)

60 80 100

1344 G05

–4.8

–4.6

1344 G08

154

152

COMMON MODE IMPEDANCE (Ω)

150

–2

–1

COMMON MODE VOLTAGE (V)

0

Supply Current vs Temperature

310

290

270

250

230

210

SUPPLY CURRENT (µA)

190

170

150

–20 10 40 70 100

–50

TEMPERATURE (°C)

1

2

1344 G06

1344 G09

3

LTC1344

PIN FUNCTIONS

UUU

M0 (Pin 1): TTL Level Mode Select Input. The data on M0

is latched when LATCH is high.

VEE (Pin 2): Negative Supply Voltage Input. Can connect

directly to the LTC1343 VEE pin.

R1C (Pin 3): Load 1 Center Tap.

R1B (Pin 4): Load 1 Node B.

R1A (Pin 5): Load 1 Node A.

R2A (Pin 6): Load 2 Node A.

R2B (Pin 7): Load 2 Node B.

R2C (Pin 8): Load 2 Center Tap.

R3A (Pin 9): Load 3 Node A.

R2B (Pin 10): Load 2 Node B.

R3C (Pin 11): Load 3 Center Tap.

GND (Pin 12): Ground Connection for Load 1 to Load 3.

GND (Pin 13): Ground Connection for Load 4 to Load 6.

V

(Pin 14): Positive Supply Input. 4.75V ≤ VCC ≤ 5.25V.

CC

R4B (Pin 15): Load 4 Node B.

R4A (Pin 16): Load 4 Node A.

R5B (Pin 17): Load 5 Node B.

R5A (Pin 18): Load 5 Node A.

R6A (Pin 19): Load 6 Node A.

R6B (Pin 20): Load 6 Node B.

LATCH (Pin 21): TTL Level Logic Signal Latch Input. When

it is low the input buffers on M0, M1, M2 and DCE/DTE are

transparent. When it is high the logic pins are latched into

their respective input buffers. The data latch allows the

select lines to be shared between multiple I/O ports.

DCE/DTE (Pin 22): TTL Level Mode Select Input. The DCE

mode is selected when it is high and DTE mode when low.

The data on DCE/DTE is latched when LATCH is high.

M2 (Pin 23): TTL Level Mode Select Input 1. The data on

M2 is latched when LATCH is high.

M1 (Pin 24): TTL Level Mode Select Input 2. The data on

M1 is latched when LATCH is high.

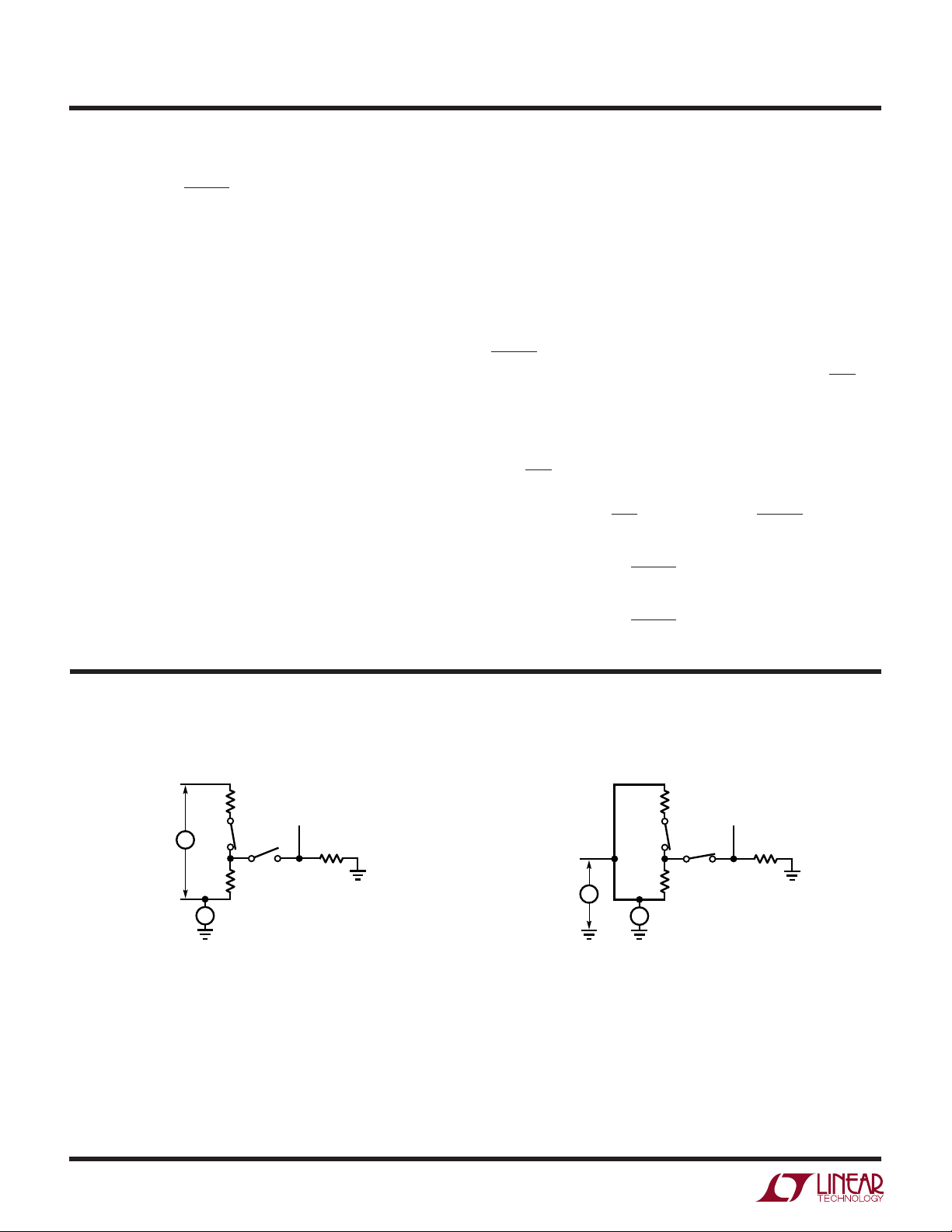

TEST CIRCUITS

A

Ω

B

Figure 1. Differential V.11 or V.35 Impedance Measurement Figure 2. V.35 Common Mode Impedance Measurement

S1

ON

±7V OR ±2V

V

R1

51.5Ω

R2

51.5Ω

S2

OFF

R1

C

R3

124Ω

1344 F01

A, B

Ω

51.5Ω

S1

ON

R2

51.5Ω

±2V

V

S2

ON

C

R3

124Ω

1344 F02

4

Loading...

Loading...