20V/µs, Low Power, Rail-to-Rail Input

FEATURES

■

Gain Bandwidth Product: 60MHz

■

Input Common Mode Range Includes Both Rails

■

Output Swings Rail-to-Rail

■

Low Quiescent Current: 1mA Max

■

Input Offset Voltage: 350

■

Input Bias Current: 150nA Max

■

Wide Supply Range: 2.2V to 12.6V

■

Large Output Current: 50mA Typ

■

Low Voltage Noise: 10nV√Hz Typ

■

Slew Rate: 20V/µs Typ

■

Common Mode Rejection: 102dB Typ

■

Power Supply Rejection: 105dB Typ

■

Open-Loop Gain: 100V/mV Typ

■

Operating Temperature Range: – 40°C to 85°C

■

Single in the 8-Pin SO and 5-Pin Low Profile

µµ

µV Max

µµ

(1mm) ThinSOTTM Packages

■

Dual in the 8-Pin SO and (3mm x 3mm) DFN

Packages

■

Quad in the 16-Pin SSOP Package

U

APPLICATIO S

■

Low Voltage, High Frequency Signal Processing

■

Driving A/D Converters

■

Rail-to-Rail Buffer Amplifiers

■

Active Filters

■

Video Amplifiers

■

Fast Current Sensing Amplifiers

LT6220/LT6221/LT6222

Single/Dual/Quad 60MHz,

and Output Precision Op Amps

U

DESCRIPTIO

The LT®6220/LT6221/LT6222 are single/dual/quad, low

power, high speed rail-to-rail input and output operational

amplifiers with excellent DC performance. The LT6220/

LT6221/LT6222 feature reduced supply current, lower

input offset voltage, lower input bias current and higher

DC gain than other devices with comparable bandwidth.

Typically, the LT6220/LT6221/LT6222 have an input offset voltage of less than 100µV, an input bias current of less

than 15nA and an open-loop gain of 100V/mV. The parts

have an input range that includes both supply rails and an

output that swings within 10mV of either supply rail to maximize the signal dynamic range in low supply applications.

The LT6220/LT6221/LT6222 maintain performance for

supplies from 2.2V to 12.6V and are specified at 3V, 5V

and ±5V supplies. The inputs can be driven beyond the

supplies without damage or phase reversal of the output.

The LT6220 is housed in the 8-pin SO package with the

standard op amp pinout as well as the 5-pin SOT-23

package. The LT6221 is available in 8-pin SO and DFN

(3mm × 3mm low profile dual fine pitch leadless) packages with the standard op amp pinout. The LT6222 features the standard quad op amp configuration and is

available in the 16-Pin SSOP package. The LT6220/ LT6221/

LT6222 can be used as plug-in replacements for many op

amps to improve input/output range and performance.

, LTC and LT are registered trademarks of Linear Technology Corporation.

ThinSOT is a trademark of Linear Technology Corporation.

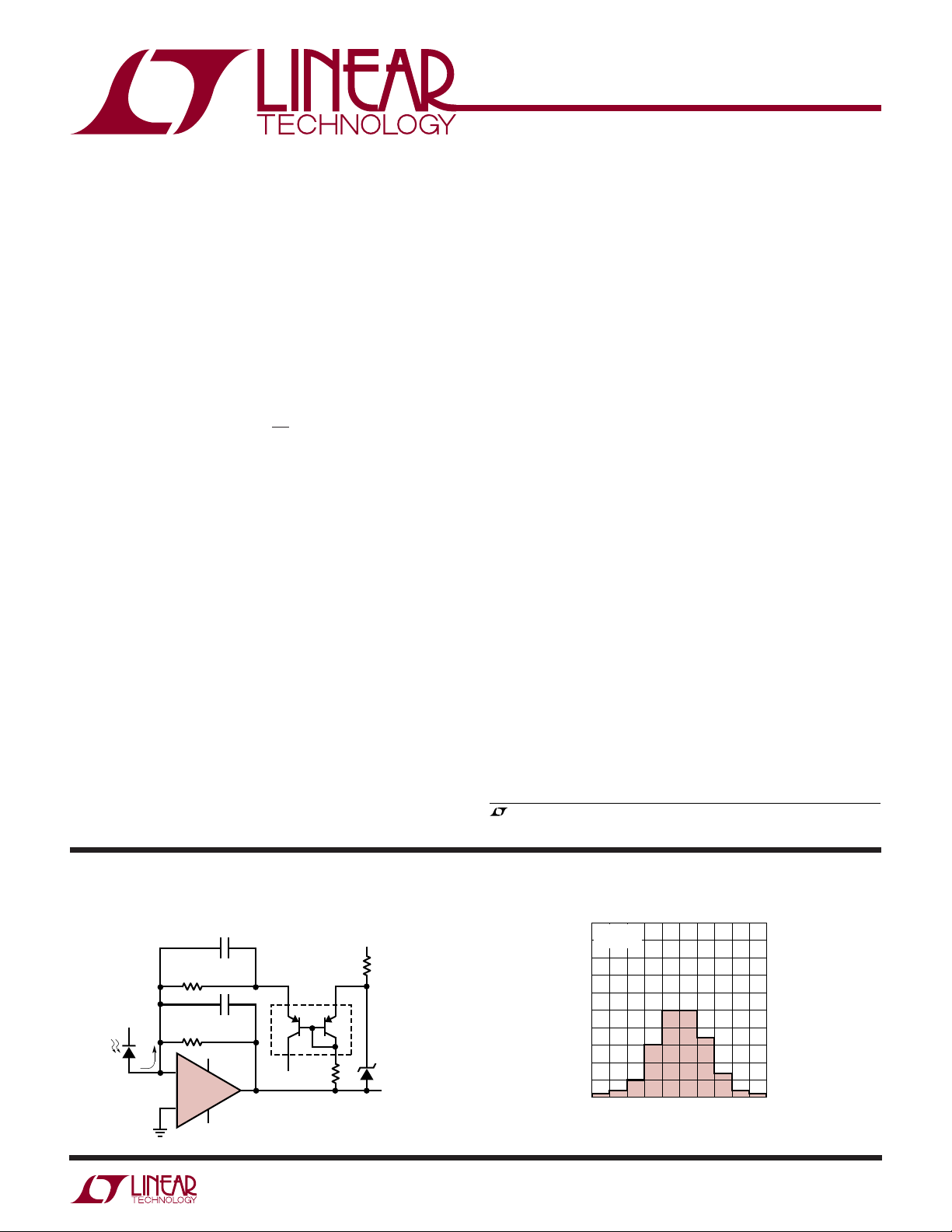

TYPICAL APPLICATIO

Stepped-Gain Photodiode Amplifier

30pF

3.24k

+

V

S

I

PD

PHOTODIODE

~4pF

100k

–

+

V

LT6220

V

1pF

+

S

V

S

–

S

VS = ±1.5V TO ±5V

U

VOS Distribution, VCM = 0V

(S8, PNP Stage)

50

+

V

S

10k

LT1634-1.25

–

33k

V

OUT

622012 TA01

VS = 5V, 0V

= 0V

V

45

CM

40

35

30

25

20

15

PERCENT OF UNITS (%)

10

5

0

–150

–250

INPUT OFFSET VOLTAGE (µV)

–50 0

50

150

250

622012 G01

622012fa

1

LT6220/LT6221/LT6222

TOP VIEW

GN PACKAGE

16-LEAD NARROW PLASTIC SSOP

1

2

3

4

5

6

7

8

16

15

14

13

12

11

10

9

OUT A

–IN A

+IN A

V

S

+

+IN B

–IN B

OUT B

NC

OUT D

–IN D

+IN D

V

S

–

+IN C

–IN C

OUT C

NC

A

B

C

D

WW

W

ABSOLUTE AXI U RATI GS

Total Supply Voltage (V

–

S

to V

+

) ......................... 12.6V

S

U

(Note 1)

Input Voltage (Note 2) ..............................................±V

Input Current (Note 2) ........................................ ±10mA

Output Short Circuit Duration (Note 3) ............ Indefinite

Operating Temperature Range (Note 4) ...–40°C to 85°C

Specified Temperature Range (Note 5) .... –40°C to 85°C

UUW

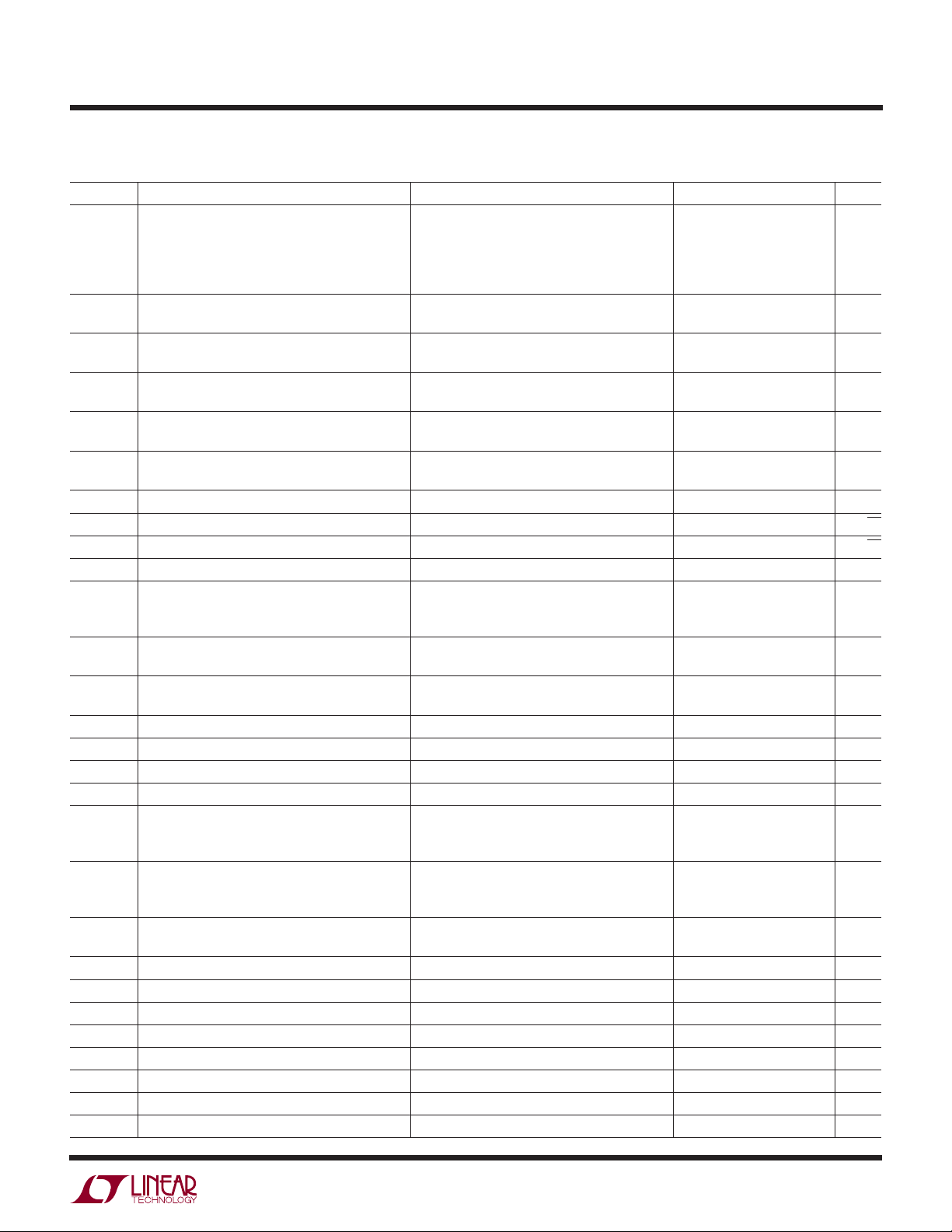

PACKAGE/ORDER I FOR ATIO

ORDER PART

TOP VIEW

V

1

OUT

–

V

2

S

+IN 3

5-LEAD PLASTIC TSOT-23

T

= 150°C, θJA = 250°C/W (NOTE 10)

JMAX

+

–

S5 PACKAGE

5 V

4 –IN

+

S

NUMBER

LT6220CS5

LT6220IS5

S5 PART*

MARKING

LTAFP

Maximum Junction Temperature .......................... 150°C

S

(DD Package) ................................................... 125°C

Storage Temperature .............................–65°C to 150°C

(DD Package) ....................................–65°C to 125°C

Lead Temperature (Soldering, 10 sec.)................. 300°C

ORDER PART

NC

1

–IN

2

+IN

3

–

V

4

S

S8 PACKAGE

8-LEAD PLASTIC SO

T

= 150°C, θJA = 190°C/W

JMAX

TOP VIEW

–

+

NC

8

+

V

7

S

V

6

OUT

NC

5

NUMBER

LT6220CS8

LT6220IS8

S8 PART

MARKING

6220

6220I

–IN A

+IN A

T

EXPOSED PAD INTERNALLY CONNECTED TO V

ORDER PART

NUMBER

LT6221CDD

LT6221IDD

Consult LTC Marketing for parts specified with wider operating temperature ranges.

*The temperature grades are identified by a label on the shipping container.

2

TOP VIEW

1OUT A

2

A

3

–

V

4

S

8-LEAD (3mm × 3mm) PLASTIC DFN

JMAX

DD PACKAGE

= 125°C, θJA = 160°C/W (NOTE 10)

(PCB CONNECTION OPTIONAL)

8

V

S

OUT B

7

–IN B

6

B

+IN B

5

DD PART*

MARKING

LADZ 6222

+

–

S

OUT A

–IN A

+IN A

V

ORDER PART

NUMBER

LT6221CS8

LT6221IS8

TOP VIEW

1

2

A

3

–

4

S

S8 PACKAGE

8-LEAD PLASTIC SO

= 150°C, θJA = 190°C/W

T

JMAX

+

V

8

S

OUT B

7

–IN B

6

B

+IN B

5

S8 PART

MARKING

6221

6221I

T

= 150°C, θJA = 135°C/W

JMAX

ORDER PART

NUMBER

LT6222CGN

LT6222IGN

SSOP PART

MARKING

6222I

622012fa

LT6220/LT6221/LT6222

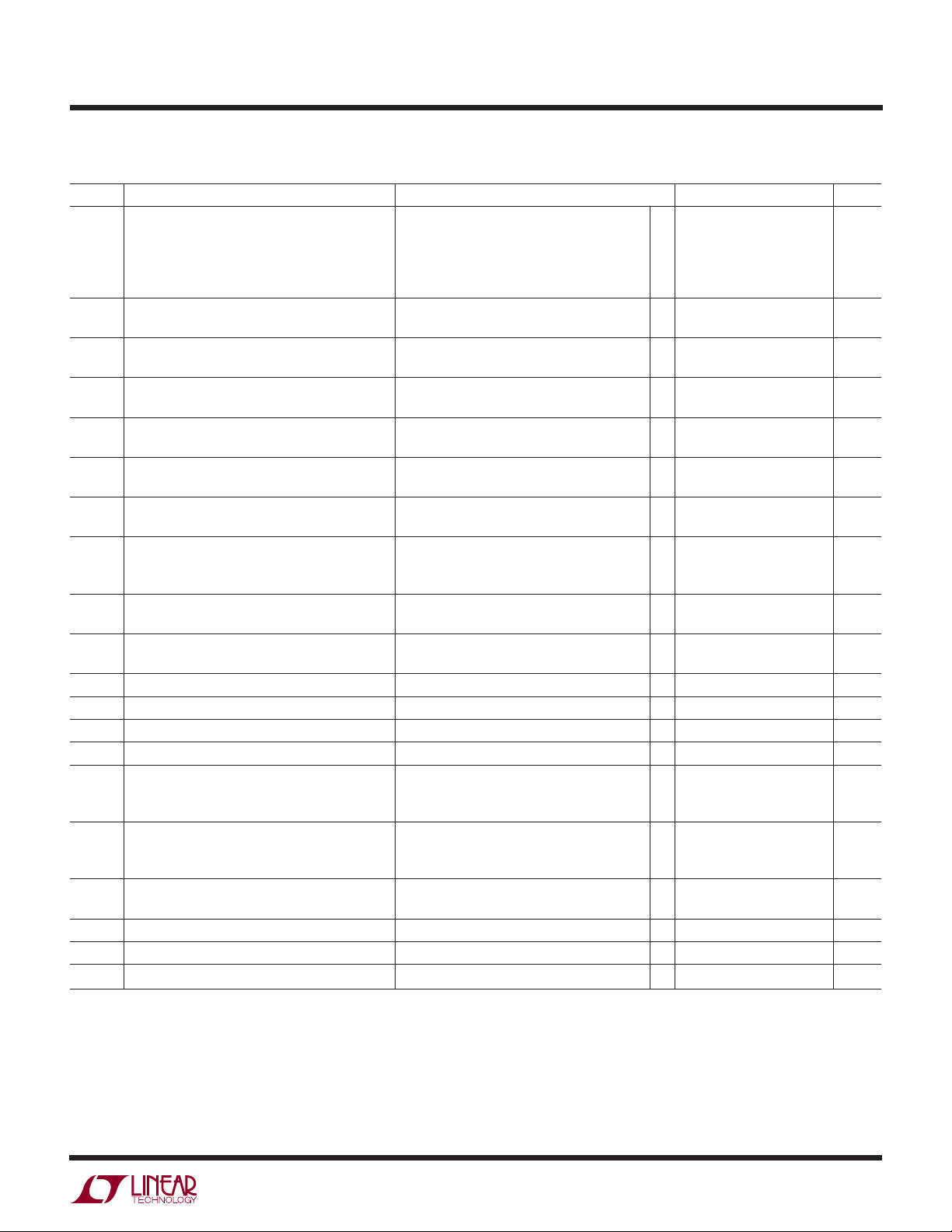

ELECTRICAL CHARACTERISTICS

TA = 25°C, VS = 5V, 0V; VS = 3V, 0V; VCM = V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆V

OS

I

B

I

OS

e

n

i

n

C

IN

A

VOL

CMRR Common Mode Rejection Ratio VS = 5V, V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, V

V

OL

V

OH

I

SC

I

S

GBW Gain-Bandwidth Product VS = 5V, Frequency = 1MHz 35 60 MHz

SR Slew Rate VS = 5V, AV = –1, RL= 1k, VO = 4V 10 20 V/µs

FPBW Full Power Bandwidth VS = 5V, AV = 1, VO = 4V

HD Harmonic Distortion VS = 5V, AV = 1, RL= 1k, VO = 2V

t

S

∆G Differential Gain (NTSC) VS = 5V, AV = 2, RL= 1k 0.3 %

∆θ Differential Phase (NTSC) VS = 5V, AV = 2, RL= 1k 0.3 Deg

Input Offset Voltage VCM = 0V 70 350 µV

Input Offset Voltage Shift VS = 5V, VCM = 0V to 3.5V 30 195 µV

Input Offset Voltage Match (Channel-to-Channel) VCM = 0V 100 600 µV

(Note 9) V

Input Bias Current VCM = 1V 15 150 nA

Input Bias Current Match (Channel-to-Channel) VCM = 1V 15 175 nA

(Note 9) V

Input Offset Current VCM = 1V 15 100 nA

Input Noise Voltage 0.1Hz to 10Hz 0.5 µV

Input Noise Voltage Density f = 10kHz 10 nV/√Hz

Input Noise Current Density f = 10kHz 0.8 pA/√Hz

Input Capacitance 2pF

Large Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k at VS/2 35 100 V/mV

CMRR Match (Channel-to-Channel) (Note 9) VS = 5V, V

Input Common Mode Range 0 V

PSRR Match (Channel-to-Channel) (Note 9) 79 105 dB

Minimum Supply Voltage (Note 6) 2.2 2.5 V

Output Voltage Swing LOW (Note 7) No Load 5 40 mV

Output Voltage Swing HIGH (Note 7) No Load 5 40 mV

Short-Circuit Current VS = 5V 20 45 mA

Supply Current Per Amplifier 0.9 1 mA

Settling Time 0.01%, VS = 5V, V

= half supply, unless otherwise noted

OUT

= 0V (DD Package) 150 700 µV

V

CM

= 0V (S5 Package) 200 850 µV

V

CM

= V

V

CM

S

VCM = VS (S5 Package) 0.5 3 mV

= 3V, VCM = 0V to 1.5V 15 120 µV

V

S

= 0V (DD Package) 150 1100 µV

CM

= V

V

CM

S

= V

CM

S

= V

V

CM

S

= 5V, VO = 1V to 4V, RL = 100Ω at VS/2 3.5 10 V/mV

V

S

= 3V, VO = 0.5V to 2.5V, RL = 1k at VS/2 30 90 V/mV

V

S

= 0V to 3.5V 85 102 dB

VS = 3V, V

V

S

I

SINK

I

SINK

I

SOURCE

I

SOURCE

CM

= 0V to 1.5V 82 102 dB

CM

= 0V to 3.5V 79 100 dB

CM

= 3V, V

= 0V to 1.5V 76 100 dB

CM

= 0V 84 105 dB

CM

= 5mA 100 200 mV

= 20mA 325 650 mV

= 5mA 130 250 mV

= 20mA 475 900 mV

VS = 3V 20 35 mA

p-p

= 2V, AV = 1, RL= 1k 300 ns

STEP

0.5 2.5 mV

250 600 nA

20 250 nA

15 100 nA

S

1.6 MHz

, fC = 500kHz –77.5 dBc

P-P

P-P

622012fa

V

3

LT6220/LT6221/LT6222

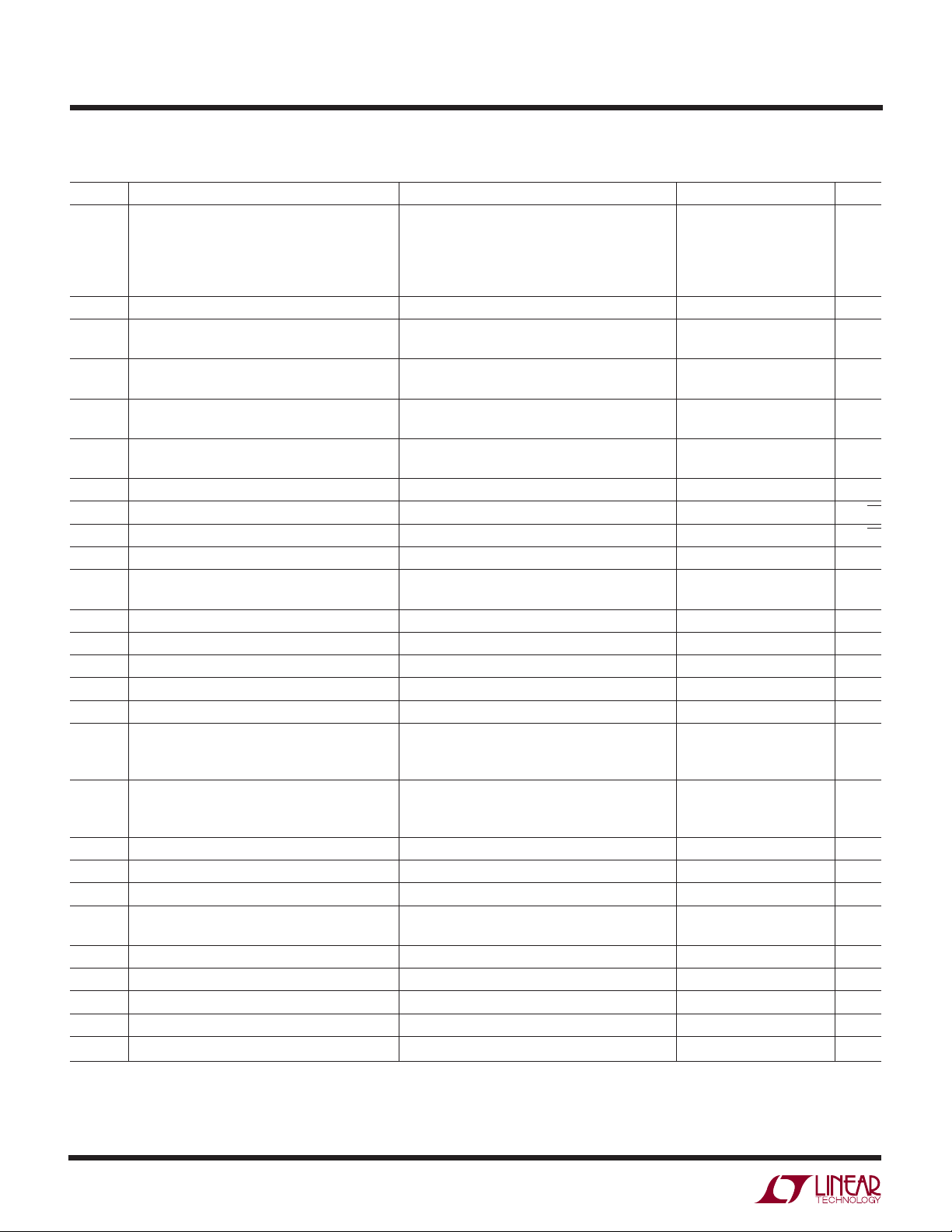

ELECTRICAL CHARACTERISTICS

temperature range. V

= 5V, 0V; VS = 3V, 0V; VCM = V

S

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C

= half supply, unless otherwise noted.

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

∆V

OS

OS

Input Offset Voltage VCM = 0V ● 90 500 µV

= 0V (DD Package) ● 180 850 µV

V

CM

V

= 0V (S5 Package) ● 230 1250 µV

CM

= V

V

CM

S

= VS (S5 Package) ● 0.5 3.5 mV

V

CM

● 0.5 3 mV

Input Offset Voltage Shift VS = 5V, VCM = 0V to 3.5V ● 30 280 µV

= 3V, VCM = 0V to 1.5V ● 15 190 µV

V

S

Input Offset Voltage Match (Channel-to-Channel) VCM = 0V ● 110 850 µV

(Note 9) V

= 0V (DD Package) ● 180 1400 µV

CM

VOS TC Input Offset Voltage Drift (Note 8) ● 1.5 5 µV/°C

(S5 Package)

I

B

Input Bias Current VCM = 1V ● 20 175 nA

= VS – 0.2V ● 275 800 nA

V

CM

● 3.5 10 µV/°C

Input Bias Current Match (Channel-to-Channel) VCM = 1V ● 15 200 nA

(Note 9) V

I

OS

A

VOL

Input Offset Current VCM = 1V ● 15 125 nA

Large Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k at VS/2 ● 30 90 V/mV

CMRR Common Mode Rejection Ratio VS = 5V, V

CMRR Match (Channel-to-Channel) (Note 9) VS = 5V, V

Input Common Mode Range ● 0V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, V

= VS – 0.2V ● 20 300 nA

CM

V

= VS – 0.2V ● 15 125 nA

CM

= 5V, VO = 1V to 4V, RL = 100Ω at VS/2 ● 3 9 V/mV

V

S

= 3V, VO = 0.5V to 2.5V, RL = 1k at VS/2 ● 25 80 V/mV

V

S

= 0V to 3.5V ● 82 100 dB

= 3V, V

= 3V, V

CM

= 0V to 1.5V ● 78 100 dB

CM

= 0V to 3.5V ● 77 100 dB

CM

= 0V to 1.5V ● 73 100 dB

CM

S

= 0V ● 81 104 dB

CM

V

S

V

S

PSRR Match (Channel-to-Channel) (Note 9) ● 76 104 dB

Minimum Supply Voltage (Note 6) ● 2.2 2.5 V

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 850 mV

I

= 5mA ● 110 220 mV

SINK

= 20mA ● 375 750 mV

I

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 850 mV

= 5mA ● 150 300 mV

I

SOURCE

I

= 20mA ● 600 1100 mV

SOURCE

Short-Circuit Current VS = 5V ● 20 40 mA

= 3V ● 20 30 mA

V

S

Supply Current Per Amplifier ● 1 1.4 mA

GBW Gain-Bandwidth Product VS = 5V, Frequency = 1MHz ● 30 60 MHz

SR Slew Rate VS = 5V, AV = –1, RL = 1k, VO = 4V

P-P

● 918 V/µs

V

4

622012fa

LT6220/LT6221/LT6222

ELECTRICAL CHARACTERISTICS

temperature range. V

= 5V, 0V; VS = 3V, 0V; VCM = V

S

The ● denotes the specifications which apply over the –40°C ≤ TA ≤ 85°C

= half supply unless otherwise noted. (Note 5)

OUT

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

∆V

OS

Input Offset Voltage VCM = 0V ● 125 700 µV

= 0V (DD Package) ● 300 1300 µV

V

CM

V

= 0V (S5 Package) ● 350 2000 µV

CM

= V

V

CM

S

= VS (S5 Package) ● 1 4.5 mV

V

CM

Input Offset Voltage Shift VS = 5V, VCM = 0V to 3.5V ● 30 300 µV

OS

= 3V, VCM = 0V to 1.5V ● 30 210 µV

V

S

● 0.75 3.5 mV

Input Offset Voltage Match (Channel-to-Channel) VCM = 0V ● 175 1200 µV

(Note 9) V

= 0V (DD Package) ● 300 2200 µV

CM

VOS TC Input Offset Voltage Drift (Note 8) ● 1.5 7.5 µV/°C

(S5 Package)

I

B

Input Bias Current VCM = 1V ● 25 200 nA

= VS – 0.2V ● 300 900 nA

V

CM

● 3.5 15 µV/°C

Input Bias Current Match (Channel-to-Channel) VCM = 1V ● 15 250 nA

(Note 9) V

I

OS

A

VOL

Input Offset Current VCM = 1V ● 20 150 nA

Large Signal Voltage Gain VS = 5V, VO = 0.5V to 4.5V, RL = 1k at VS/2 ● 25 70 V/mV

CMRR Common Mode Rejection Ratio VS = 5V, V

CMRR Match (Channel-to-Channel) (Note 9) VS = 5V, V

Input Common Mode Range ● 0V

PSRR Power Supply Rejection Ratio VS = 2.5V to 10V, V

= VS – 0.2V ● 20 350 nA

CM

V

= VS – 0.2V ● 20 150 nA

CM

= 5V, VO = 1.5V to 3.5V, RL = 100Ω at VS/2 ● 2.5 8 V/mV

V

S

= 3V, VO = 0.5V to 2.5V, RL= 1k at VS/2 ● 20 60 V/mV

V

S

= 0V to 3.5V ● 81 100 dB

= 3V, V

= 3V, V

CM

= 0V to 1.5V ● 77 100 dB

CM

= 0V to 3.5V ● 76 100 dB

CM

= 0V to 1.5V ● 72 100 dB

CM

S

= 0V ● 79 104 dB

CM

V

S

V

S

PSRR Match (Channel-to-Channel) (Note 9) ● 74 104 dB

Minimum Supply Voltage (Note 6) ● 2.2 2.5 V

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 10 60 mV

I

= 5mA ● 120 240 mV

SINK

= 10mA ● 220 450 mV

I

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 10 60 mV

= 5mA ● 160 325 mV

I

SOURCE

I

= 10mA ● 325 650 mV

SOURCE

Short-Circuit Current VS = 5V ● 12.5 30 mA

= 3V ● 12.5 25 mA

V

S

Supply Current Per Amplifier ● 1.1 1.5 mA

GBW Gain-Bandwidth Product VS = 5V, Frequency = 1MHz ● 25 50 MHz

SR Slew Rate VS = 5V, AV = –1, RL = 1k, VO = 4V ● 815 V/µs

V

622012fa

5

LT6220/LT6221/LT6222

ELECTRICAL CHARACTERISTICS

TA = 25°C, VS = ±5V, VCM = 0V, V

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

∆V

OS

I

B

I

OS

e

n

i

n

C

IN

A

VOL

CMRR Common Mode Rejection Ratio V

PSRR Power Supply Rejection Ratio V

V

OL

V

OH

I

SC

I

S

GBW Gain-Bandwidth Product Frequency = 1MHz 60 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, 20 V/µs

FPBW Full Power Bandwidth VO = 8V

HD Harmonic Distortion AV = 1, RL= 1k, VO = 2V

t

S

∆G Differential Gain (NTSC) AV = 2, RL = 1k 0.15 %

∆θ Differential Phase (NTSC) AV = 2, RL = 1k 0.6 Deg

Input Offset Voltage VCM = –5V 80 500 µV

Input Offset Voltage Shift VCM = –5V to 3.5V 70 675 µV

Input Offset Voltage Match (Channel-to-Channel) VCM = –5V 100 850 µV

Input Bias Current VCM = –4V 20 150 nA

Input Bias Current Match (Channel-to-Channel) VCM = –4V 15 175 nA

Input Offset Current VCM = –4V 15 100 nA

Input Noise Voltage 0.1Hz to 10Hz 0.5 µV

Input Noise Voltage Density f = 10kHz 10 nV/√Hz

Input Noise Current Density f = 10kHz 0.8 pA/√Hz

Input Capacitance f = 100kHz 2 pF

Large Signal Voltage Gain VO = – 4V to 4V, RL = 1k 35 95 V/mV

CMRR Match (Channel-to-Channel) 77 100 dB

Input Common Mode Range V

PSRR Match (Channel-to-Channel) 79 105 dB

Output Voltage Swing LOW (Note 7) No Load 5 40 mV

Output Voltage Swing HIGH (Note 7) No Load 5 40 mV

Short-Circuit Current 25 50 mA

Supply Current Per Amplifier 1 1.5 mA

Settling Time 0.01%, V

= 0V, unless otherwise noted.

OUT

V

= –5V (DD Package) 150 750 µV

CM

= –5V (S5 Package) 200 900 µV

V

CM

= 5V 0.7 2.5 mV

V

CM

V

= 5V (S5 Package) 0.7 3 mV

CM

V

= –5V (DD Package) 150 1300 µV

CM

= 5V 250 700 nA

V

CM

= 5V 20 250 nA

V

CM

= 5V 15 100 nA

V

CM

= –2V to 2V, RL = 100Ω 3.5 10 V/mV

V

O

= –5V to 3.5V 82 102 dB

CM

+

= 2.5V to 10V, V

S

= 5mA 100 200 mV

I

SINK

I

= 20mA 325 650 mV

SINK

I

SOURCE

I

SOURCE

Measure at V

P-P

–

–

= 0V, VCM = 0V 84 105 dB

S

S

+

V

S

= 5mA 130 250 mV

= 20mA 475 900 mV

= ±2V

O

P-P

, fc = 500kHz –77.5 dBc

p-p

= 5V, AV = 1, RL = 1k 375 ns

STEP

0.8 MHz

V

6

622012fa

LT6220/LT6221/LT6222

ELECTRICAL CHARACTERISTICS

temperature range. V

= ±5V, VCM = 0V, V

S

= 0V, unless otherwise noted.

OUT

The ● denotes the specifications which apply over the 0°C ≤ TA ≤ 70°C

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

∆V

OS

OS

Input Offset Voltage VCM = –5V ● 100 650 µV

V

= –5V (DD Package) ● 180 900 µV

CM

= –5V (S5 Package) ● 230 1300 µV

V

CM

= 5V ● 0.75 3 mV

V

CM

V

= 5V (S5 Package) ● 0.75 3.5 mV

CM

Input Offset Voltage Shift VCM = –5V to 3.5V ● 90 850 µV

Input Offset Voltage Match (Channel-to-Channel) VCM = –5V ● 90 1100 µV

(Note 9) V

= –5V (DD Package) ● 180 1500 µV

CM

VOS TC Input Offset Voltage Drift (Note 8) ● 1.5 5 µV/°C

(S5 Package)

I

B

Input Bias Current VCM = –4V ● 20 175 nA

= 4.8V ● 275 800 nA

V

CM

● 3.5 10 µV/°C

Input Bias Current Match (Channel-to-Channel) VCM = –4V ● 15 200 nA

(Note 9) V

I

OS

A

VOL

Input Offset Current VCM = –4V ● 15 125 nA

Large Signal Voltage Gain VO = – 4V to 4V, RL = 1k ● 30 90 V/mV

CMRR Common Mode Rejection Ratio V

= 4.8V ● 20 300 nA

CM

V

= 4.8V ● 15 125 nA

CM

= –2V to 2V, RL =100Ω ● 3 9 V/mV

V

O

= –5V to 3.5V ● 80 100 dB

CM

CMRR Match (Channel-to-Channel) (Note 9) ● 75 100 dB

Input Common Mode Range ● V

PSRR Power Supply Rejection Ratio

+

= 2.5V to 10V, V

VS

–

–

= 0V, VCM = 0V ● 81 104 dB

S

S

+

V

S

PSRR Match (Channel-to-Channel) (Note 9) ● 76 104 dB

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 850 mV

= 5mA ● 110 220 mV

I

SINK

= 20mA ● 375 750 mV

I

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 850 mV

I

= 5mA ● 150 300 mV

SOURCE

= 20mA ● 600 1100 mV

I

SOURCE

Short-Circuit Current ● 20 40 mA

Supply Current Per Amplifier ● 1.2 2 mA

GBW Gain-Bandwidth Product Frequency = 1MHz ● 60 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, ● 18 V/µs

Measure at VO = ±2V

V

622012fa

7

LT6220/LT6221/LT6222

ELECTRICAL CHARACTERISTICS

temperature range. V

= ±5V, VCM = 0V, V

S

= 0V, unless otherwise noted. (Note 5)

OUT

The ● denotes the specifications which apply over the –40°C ≤ TA ≤ 85°C

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

OS

Input Offset Voltage VCM = –5V ● 150 800 µV

V

= –5V (DD Package) ● 300 1300 µV

CM

= –5V (S5 Package) ● 350 2000 µV

V

CM

= 5V ● 0.75 3.5 mV

V

CM

VCM = 5V (S5 Package) ● 1 4.5 mV

∆V

OS

Input Offset Voltage Shift VCM = – 5V to 3.5V ● 90 950 µV

Input Offset Voltage Match (Channel-to-Channel) VCM = –5V ● 175 1350 µV

(Note 9) VCM = –5V (DD Package) ● 300 2200 µV

VOS TC Input Offset Voltage Drift (Note 8) ● 1.5 7.5 µV/°C

(S5 Package)

I

B

Input Bias Current VCM = –4V ● 25 200 nA

● 3.5 15 µV/°C

VCM = 4.8V ● 300 900 nA

Input Bias Current Match (Channel-to-Channel) VCM = –4V ● 15 250 nA

(Note 9) V

I

OS

Input Offset Current VCM = –4V ● 20 150 nA

= 4.8V ● 20 350 nA

CM

VCM = 4.8V ● 20 150 nA

A

VOL

Large Signal Voltage Gain VO = –4V to 4V, RL = 1k ● 25 70 V/mV

VO = –1V to 1V, RL = 100Ω ● 2.5 8 V/mV

CMRR Common Mode Rejection Ratio VCM = –5V to 3.5V ● 79 100 dB

CMRR Match (Channel-to-Channel) (Note 9) ● 74 100 dB

Input Common Mode Range ● –5 5 V

PSRR Power Supply Rejection Ratio V

= 2.5V to 10V, V

S+

–

= 0V, VCM = 0V ● 79 104 dB

S

PSRR Match (Channel-to-Channel) (Note 9) ● 74 104 dB

V

OL

V

OH

I

SC

I

S

Output Voltage Swing LOW (Note 7) No Load ● 10 60 mV

I

= 5mA ● 120 240 mV

SINK

I

= 10mA ● 220 450 mV

SINK

Output Voltage Swing HIGH (Note 7) No Load ● 10 60 mV

I

= 5mA ● 160 325 mV

SOURCE

I

= 10mA ● 325 650 mV

SOURCE

Short-Circuit Current ● 12.5 30 mA

Supply Current ● 1.4 2.25 mA

GBW Gain-Bandwidth Product Frequency = 1MHz ● 50 MHz

SR Slew Rate AV = –1, RL = 1k, VO = ±4V, ● 15 V/µs

Measure at VO = ±2V

Note 1: Absolute Maximum Ratings are those values beyond which the life

of a device may be impaired.

Note 2: The inputs are protected by back-to-back diodes. If the differential

input voltage exceeds 1.4V, the input current should be limited to less than

10mA.

Note 3: A heat sink may be required to keep the junction temperature

below the absolute maximum rating when the output is shorted

indefinitely.

Note 4: The LT6220C/LT6221C/LT6222C and LT6220I/LT6221I/LT6222I

are guaranteed functional over the temperature range of –40°C and 85°C.

Note 5: The LT6220C/LT6221C/LT6222C are guaranteed to meet specified

performance from 0°C to 70°C. The LT6220C/LT6221C/LT6222C are

designed, characterized and expected to meet specified performance from

–40°C to 85°C but is not tested or QA sampled at these temperatures. The

LT6220I/LT6221I/LT6222I are guaranteed to meet specified performance

from –40°C to 85°C.

Note 6: Minimum supply voltage is guaranteed by power supply rejection

ratio test.

Note 7: Output voltage swings are measured between the output and

power supply rails.

Note 8: This parameter is not 100% tested.

Note 9: Matching parameters are the difference between amplifiers A and

D and between B and C on the LT6222; between the two amplifiers on the

LT6221.

Note 10: Thermal resistance (θJA) varies with the amount of PC board

metal connected to the package. The specified values are for short traces

connected to the leads. If desired, the thermal resistance can be

substantially reduced by connecting Pin 2 of the LT6220CS5/LT6220IS5 or

the underside metal of DD packages to a larger metal area (V

–

trace).

S

622012fa

8

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LT6220/LT6221/LT6222

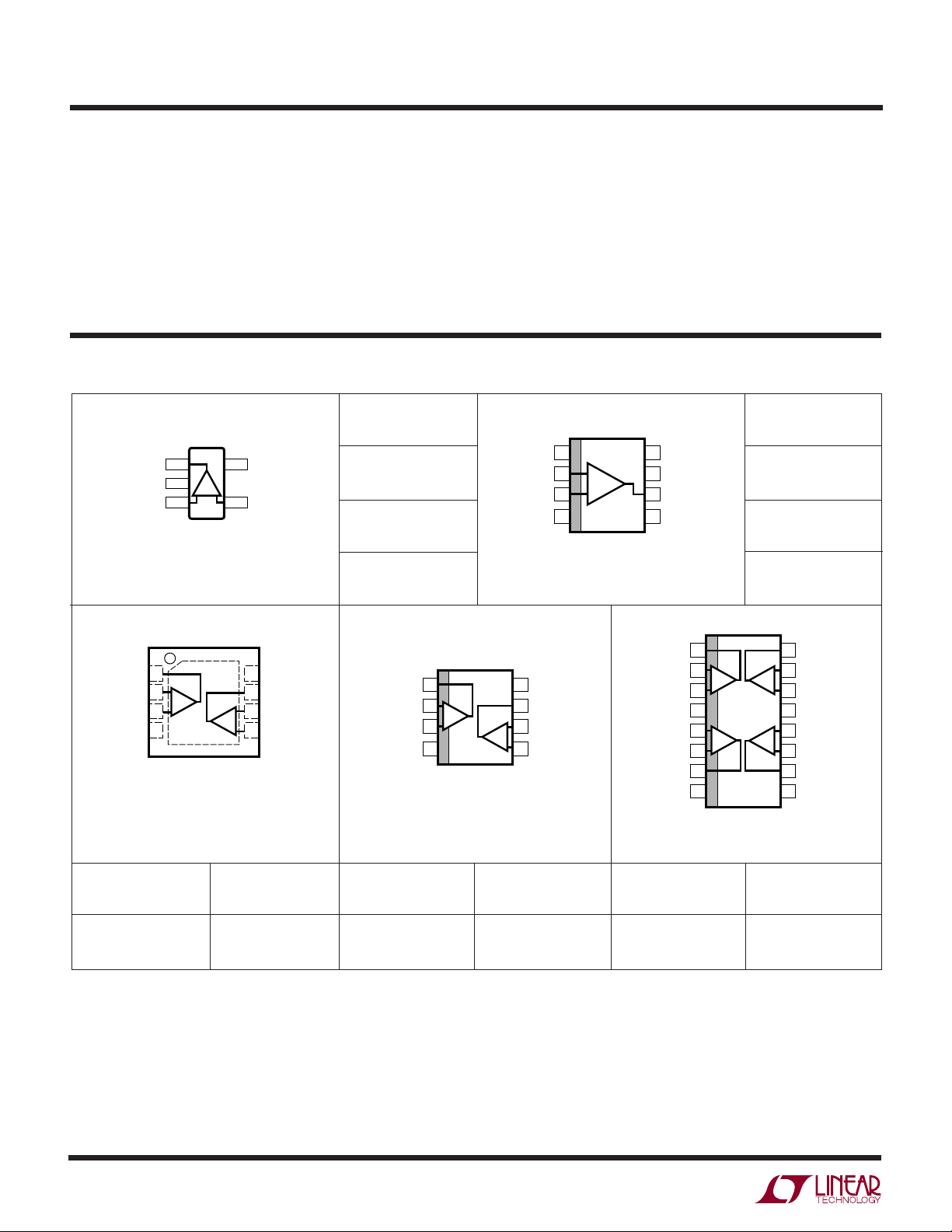

VOS Distribution, VCM = 0V

(S8, PNP Stage)

50

VS = 5V, 0V

= 0V

V

45

CM

40

35

30

25

20

15

PERCENT OF UNITS (%)

10

5

0

–150

–250

–50 0

INPUT OFFSET VOLTAGE (µV)

50

150

250

622012 G01

VOS Distribution, VCM = 0V

(SOT5, PNP Stage)

50

VS = 5V, 0V

= 0V

V

45

CM

40

35

30

25

20

15

PERCENT OF UNITS (%)

10

5

0

–600

–1000

–200

INPUT OFFSET VOLTAGE (µV)

0

200

VOS Distribution, VCM = 5V

(SOT5, NPN Stage) Supply Current vs Supply Voltage

50

VS = 5V, 0V

= 5V

V

45

CM

40

35

30

25

20

15

PERCENT OF UNITS (%)

10

5

0

–1800

–3000

INPUT OFFSET VOLTAGE (µV)

–600 0

600

1800

3000

622012 G04

3

2

1

SUPPLY CURRENT PER AMPLIFIER (mA)

0

0

3

2

TOTAL SUPPLY VOLTAGE (V)

TA = 125°C

TA = –55°C

5 7 9 11 12

468

600

622012 G02

TA = 25°C

101

622012 G05

1000

VOS Distribution, VCM = 5V

(S8, NPN Stage)

50

VS = 5V, 0V

= 5V

V

45

CM

40

35

30

25

20

15

PERCENT OF UNITS (%)

10

5

0

–2000

–1200

INPUT OFFSET VOLTAGE (µV)

–400

4000

Offset Voltage

vs Input Common Mode Voltage

700

VS = 5V, 0V

TYPICAL PART

500

–100

–300

OFFSET VOLTAGE (µV)

–500

–700

300

100

0

INPUT COMMON MODE VOLTAGE (V)

TA = –55°C

TA = 25°C

TA = 125°C

1

3

2

1200

4

2000

622012 G03

5

622012 G06

Input Bias Current

vs Common Mode Voltage

400

VS = 5V, 0V

300

200

100

0

–100

–200

–300

INPUT BIAS CURRENT (nA)

–400

–500

–600

1

0

COMMON MODE VOLTAGE (V)

TA = 25°C

TA = –55°C

2

Input Bias Current

vs Temperature

0.6

VS = 5V, 0V

0.5

0.4

TA = 125°C

3

4

5

622012 G07

6

INPUT BIAS CURRENT (µA)

0.3

0.2

0.1

–0.1

–0.2

0

–55

–25 5

NPN ACTIVE

= 5V

V

CM

PNP ACTIVE

= 1V

V

CM

35

65 95

TEMPERATURE (°C)

125

622012 G08

Output Saturation Voltage

vs Load Current (Output Low)

10

VS = 5V, 0V

1

0.1

TA = 25°C

0.01

OUTPUT SATURATION VOLTAGE (V)

0.001

0.01

TA = 125°C

TA = –55°C

1100.1 100

LOAD CURRENT (mA)

622012 G09

622012fa

9

LT6220/LT6221/LT6222

OUTPUT VOLTAGE (V)

–5

CHANGE IN OFFSET VOLTAGE (µV)

200

600

1000

3

622012 G15

–200

–600

0

400

800

–400

–800

–1000

–3–4

–1–2

12 4

0

5

RL = 1k

VS = ±5V

R

L

TO GND

RL = 100Ω

FREQUENCY (kHz)

10

NOISE VOLTAGE (nV/√Hz)

20

25

35

40

0.01 1 10 100

622012 G18

0

0.1

30

15

5

VS = 5V, 0V

NPN ACTIVE

V

CM

= 4.25V

PNP ACTIVE

V

CM

= 2.5V

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Output Saturation Voltage

vs Load Current (Output High) Minimum Supply Voltage

10

VS = 5V, 0V

1

0.1

TA = 25°C

0.01

OUTPUT SATURATION VOLTAGE (V)

0.001

0.01

TA = 125°C

TA = –55°C

1100.1 100

LOAD CURRENT (mA)

622012 G10

0.6

0.4

0.2

0

–0.2

–0.4

CHANGE IN OFFSET VOLTAGE (mV)

–0.6

TA = –55°C

TA = 25°C

TA = 125°C

1.5 2.5 3.5 4.5

TOTAL SUPPLY VOLTAGE (V)

Open-Loop Gain Open-Loop Gain

1000

800

600

400

200

–200

–400

–600

CHANGE IN OFFSET VOLTAGE (µV)

–800

–1000

VS = 3V, 0V

TO GND

R

L

0

0.5

0

RL = 1k

RL = 100Ω

1.5 2

1

OUTPUT VOLTAGE (V)

2.5

622012 G13

1000

800

600

400

200

0

–200

–400

–600

CHANGE IN OFFSET VOLTAGE (µV)

–800

–1000

3

10.5

0

RL = 1k

21.5

OUTPUT VOLTAGE (V)

RL = 100Ω

3 3.5 4.5

2.5

622012 G11

VS = 5V, 0V

TO GND

R

L

4

622012 G14

5.5102345

6

Output Short-Circuit Current

vs Power Supply Voltage

70

TA = 25°C

60

50

40

30

20

10

0

–10

–20

–30

–40

–50

OUTPUT SHORT-CIRCUIT CURRENT (mA)

–60

–70

1.5

TA = 125°C

TA = –55°C

TA = –55°C

TA = 25°C

2.5

2

POWER SUPPLY VOLTAGE (±V)

TA = 125°C

3.5 5

3

SOURCING

Open-Loop Gain

SINKING

4

4.5

622012 G12

Offset Voltage vs Output Current Warm-Up Drift vs Time Input Noise Voltage vs Frequency

2.0

VS = ±5V

1.5

1.0

0.5

0

–0.5

–1.0

CHANGE IN OFFSET VOLTAGE (mV)

–1.5

–2.0

–75

10

TA = –55°C

TA = 125°C

–45 –15 15 7530–60 –30 0 60

OUTPUT CURRENT (mA)

TA = 25°C

45

622012 G16

10

8

6

4

2

0

–2

–4

–6

CHANGE IN OFFSET VOLTAGE (µV)

–8

–10

LT6222

GN16

= ±2.5V

V

S

LT6222

GN16

= ±5V

V

S

105

0

TIME AFTER POWER-UP (SECONDS)

LT6220

SOT5

= ±2.5V

V

S

LT6220

SOT5

= ±5V

V

S

2015

25

LT6221

S8

= ±2.5V

V

S

LT6221

S8

= ±5V

V

S

30 35 45

40

622012 G17

50

622012fa

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Input Current Noise vs Frequency 0.1Hz to 10Hz Output Voltage Noise

3.0

VS = 5V, 0V

2.5

2.0

1.5

PNP ACTIVE

= 2.5V

V

1.0

NOISE CURRENT (pA/√Hz)

0.5

0

0.01 1 10 100

0.1

FREQUENCY (kHz)

CM

NPN ACTIVE

= 4.25V

V

CM

Gain Bandwidth and Phase

Margin vs Temperature

90

80

GAIN BANDWIDTH PRODUCT

70

60

50

PHASE MARGIN

GAIN BANDWIDTH (MHz)

–25

–55

5

TEMPERATURE (°C)

VS = ±2.5V

VS = ±5V

VS = ±5V

VS = ±2.5V

35

65

95

622012 G19

125

622012 G22

800

VS = 5V, 0V

600

400

200

0

–200

–400

OUTPUT NOISE VOLTAGE (nV)

–600

–800

0

Gain and Phase vs Frequency Slew Rate vs Temperature

80

70

60

PHASE MARGIN (DEG)

50

40

70

60

50

40

30

20

30

GAIN (dB)

20

10

0

–10

–20

10k

246 107135 9

TIME (SECONDS)

PHASE

GAIN

VS = ±5V

100k 1M 10M 100M

FREQUENCY (Hz)

8

622012 G20

VS = ±5V

VS = ±2.5V

VS = ±2.5V

622012 G23

LT6220/LT6221/LT6222

Gain Bandwidth and Phase

Margin vs Supply Voltage

90

TA = 25°C

80

70

60

50

GAIN BANDWIDTH (MHz)

0

120

100

80

60

40

20

0

–20

–40

–60

–80

30

PHASE (DEG)

25

20

SLEW RATE (V/µs)

15

–55

GAIN BANDWIDTH PRODUCT

PHASE MARGIN

21

TOTAL SUPPLY VOLTAGE (V)

AV = –1

= RG = 1k

R

F

= 1k

R

L

–25

67 9

43

5

VS = ±5V

53565

TEMPERATURE (°C)

8

622012 G21

VS = ±2.5V

70

60

50

40

30

20

10

95 125

622012 G24

PHASE MARGIN (DEG)

Gain vs Frequency (AV = 1) Output Impedance vs Frequency

15

AV = 1

12

= 10pF

C

L

= 1k

R

L

9

6

3

0

GAIN (dB)

–3

–6

–9

–12

–15

0.1

1 10 100

FREQUENCY (MHz)

VS = ±2.5V

VS = ±5V

622012 G25

Gain vs Frequency (AV = 2)

15

12

9

6

3

0

GAIN (dB)

–3

–6

AV = 2

= RG = 1k

R

F

–9

= 20pF

C

F

= 10pF

C

L

–12

= 1k

R

L

–15

0.1

1 10 100

FREQUENCY (MHz)

VS = ±5V

VS = ±2.5V

622012 G26

1000

VS = ±2.5V

100

10

1

0.1

OUTPUT IMPEDACNE (Ω)

0.01

0.001

0.1 1 10

AV = 10

AV = 1

FREQUENCY (MHz)

AV = 2

100

620012 G27

622012fa

11

LT6220/LT6221/LT6222

FREQUENCY (MHz)

0.01

–70

DISTORTION (dBc)

–50

–30

0.1 1 10

622012 G34

–90

–80

–60

–40

–100

–110

VS = 5V, 0V

A

V

= 2

V

OUT

= 2V

P-P

RL = 150Ω,

3RD

RL = 150Ω,

2ND

RL = 1k,

3RD

RL = 1k,

2ND

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Common Mode Rejection Ratio

vs Frequency

120

VS = 5V, 0V

100

80

60

40

20

COMMON MODE REJECTION RATIO (dB)

0

0.01 1 10 100

0.1

FREQUENCY (MHz)

Series Output Resistor

vs Capacitive Load

50

VS = 5V, 0V

45

= 2

A

V

= ∞, UNLESS NOTED

R

L

40

35

30

25

20

OVERSHOOT (%)

15

10

5

0

10

ROS = 20Ω

ROS = RL = 50Ω

100 1000 10000

CAPACITIVE LOAD (pF)

ROS = 10Ω

622012 G28

622012 G32

Power Supply Rejection Ratio

vs Frequency

120

VS = 5V, 0V

100

80

60

40

20

POWER SUPPLY REJECTION RATIO (dB)

NEGATIVE

0

0.01

0.001 0.1 1 10 100

POSITIVE

SUPPLY

SUPPLY

FREQUENCY (MHz)

622012 G29

Series Output Resistor

vs Capacitive Load

50

VS = 5V, 0V

45

= 1

A

V

= ∞, UNLESS NOTED

R

L

40

35

30

25

20

OVERSHOOT (%)

ROS = RL = 50Ω

15

10

5

0

10

ROS = 20Ω

100 1000 10000

CAPACITIVE LOAD (pF)

Distortion vs Frequency Distortion vs Frequency

–30

VS = 5V, 0V

= 1

A

V

–40

–50

–60

–70

–80

DISTORTION (dBc)

–90

–100

–110

0.01

V

OUT

RL = 150Ω,

= 2V

P-P

RL = 150Ω,

2ND

3RD

RL = 1k,

3RD

0.1 1 10

FREQUENCY (MHz)

RL = 1k,

2ND

622012 G33

ROS = 10Ω

622012 G31

)

P-P

OUTPUT VOLTAGE SWING (V

12

Maximum Undistorted Output

Signal vs Frequency 5V Large-Signal Response

5.0

4.5

4.0

3.5

3.0

2.5

2.0

1.5

VS = 5V, 0V

= 1k

R

L

1.0

0 0.1 1 10

0.01

FREQUENCY (MHz)

AV = –1 AV = 2

622012 G35

1V/DIV

0V

= 5V, 0V 100ns/DIV 622012 G36

V

S

AV = 1

= 1k

R

L

50mV/DIV

2.5V

5V Small-Signal Response

V

= 5V, 0V 50ns/DIV 622012 G37

S

AV = 1

R

= 1k

L

622012fa

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LT6220/LT6221/LT6222

±5V Large-Signal Response

2V/DIV

0V

= ±5V 200ns/DIV 622012 G38

V

S

AV = 1

= 1k

R

L

±5V Small-Signal Response Output Overdriven Recovery

50mV/DIV

0V

= ±5V 50ns/DIV 622012 G39

V

S

AV = 1

= 1k

R

L

WUUU

APPLICATIO S I FOR ATIO

Circuit Description

The LT6220/LT6221/LT6222 have an input and output

signal range that covers from the negative power supply to

the positive power supply. Figure 1 depicts a simplified

schematic of the amplifier. The input stage comprises two

differential amplifiers, a PNP stage, Q1/Q2, and an NPN

stage, Q3/Q4, that are active over different ranges of

common mode input voltage. The PNP stage is active

between the negative supply to approximately 1.2V below

the positive supply. As the input voltage moves closer

toward the positive supply, the transistor Q5 will steer the

V

IN

1V/DIV

0V

V

OUT

2V/DIV

0V

V

= 5V, 0V 200ns/DIV 622012 G40

S

AV = 2

= 1k

R

L

tail current, I1, to the current mirror, Q6/Q7, activating the

NPN differential pair and the PNP pair becomes inactive

for the rest of the input common mode range up to the

positive supply. Also, at the input stage, devices Q17 to

Q19 act to cancel the bias current of the PNP input pair.

When Q1/Q2 are active, the current in Q16 is controlled to

be the same as the current Q1/Q2. Thus, the base current

of Q16 is nominally equal to the base current of the input

devices. The base current of Q16 is then mirrored by

devices Q17-Q19 to cancel the base current of the input

devices Q1/Q2.

+

V

–

+

V

V

BIAS

+

I

1

Q2

Q1

D3

D4

Q10

+

I

2

+IN

–IN

Q16

Q18Q17

–

V

ESDD2ESDD1

D6D7D8

D5

ESDD3ESDD4

–

V+V

Q19

D1

D2

Q4

Q7

Q5 V

Q3

Q6

R3 R4 R5

Q12

Q11

Q9

Q8

R2R1

C

C

Q13

+

I

3

–

V

BUFFER

OUTPUT BIAS

Q15

C2

OUT

AND

C1

Q14

622012 F01

Figure 1. LT6220/LT6221/LT6222 Simplified Schematic Diagram

622012fa

13

LT6220/LT6221/LT6222

WUUU

APPLICATIO S I FOR ATIO

A pair of complementary common emitter stages Q14/Q15

that enable the output to swing from rail-to-rail construct

the output stage. The capacitors C2 and C3 form the local

feedback loops that lower the output impedance at high

frequency. These devices are fabricated by Linear

Technology’s proprietary high speed complementary bipolar process.

Power Dissipation

The LT6222, with four amplifiers, is housed in a small

16-lead SSOP package and typically has a thermal resistance (θJA) of 135°C/W. It is necessary to ensure that the

die’s junction temperature does not exceed 150°C. The

junction temperature, TJ, is calculated from the ambient

temperature, TA, power dissipation, PD, and thermal resistance, θJA:

TJ = TA + (PD • θJA)

The power dissipation in the IC is the function of the supply

voltage, output voltage and the load resistance. For a given

supply voltage, the worst-case power dissipation P

occurs when the maximum supply current and the output

voltage is at half of either supply voltage for a given load

resistance. P

PVI

D MAX S S MAX

Example: For an LT6222 in a 16-lead SSOP package

operating on ±5V supplies and driving a 100Ω load, the

worst-case power dissipation is given by:

P Amp mA

DMAX()

If all four amplifiers are loaded simultaneously, then the

total power dissipation is 322mW.

The maximum ambient temperature at which the part is

allowed to operate is:

TA = TJ – (P

= 150°C – (0.322W • 135°C/W) = 106.5°C

/•../

is given by:

D(MAX)

2

V

⎛

⎞

S

•/=

()

=

10 1 8 2 5 100

()

.. .

=+ =

0 018 0 0625 80 5

D(MAX)

+

⎜

⎝

• 135°C/W)

R

⎟

⎠

2

+

()

L() ()

2

mW

D(MAX)

Input Offset Voltage

The offset voltage will change depending upon which input

stage is active. The PNP input stage is active from the

negative supply rail to 1.2V below the positive supply rail,

then the NPN input stage is activated for the remaining

input range up to the positive supply rail during which the

PNP stage remains inactive. The offset voltage is typically

less than 70µV in the range that the PNP input stage is

active.

Input Bias Current

The LT6220/LT6221/LT6222 employ a patent pending

technique to trim the input bias current to less than 150nA

for the input common mode voltage of 0.2V above the

negative supply rail to 1.2V below the positive rail. The low

input offset voltage and low input bias current of the

LT6220/LT6221/LT6222 provide precision performance

especially for high source impedance applications.

Output

The LT6220/LT6221/LT6222 can deliver a large output

current, so the short-circuit current limit is set around

50mA to prevent damage to the device. Attention must be

paid to keep the junction temperature of the IC below the

absolute maximum rating of 150°C (refer to the Power

Dissipation section) when the output is in continuous

short circuit. The output of the amplifier has reversebiased diodes connected to each supply. If the output is

forced beyond either supply, unlimited current will flow

through these diodes. If the current is transient and limited

to several hundred milliamperes, no damage will occur to

the device.

Overdrive Protection

When the input voltage exceeds the power supplies, two

pair of crossing diodes, D1 to D4, will prevent the output

from reversing polarity. If the input voltage exceeds either

power supply by 700mV, diode D1/D2 or D3/D4 will turn

on to keep the output at the proper polarity. For the phase

reversal protection to perform properly, the input current

must be limited to less than 5mA. If the amplifier is

14

622012fa

WUUU

–

+

I

PD

PHOTODIODE

~4pF

V

S

+

V

S

+

V

S

+

V

S

–

V

S

–

LT6220

R1

100k

R2

3.24k

R3

33k

R4

10k

C1

1pF

C2

30pF

Q1 Q2

12

34

PHILIPS

BCV62

LT1634-1.25

V

OUT

VS = ±1.5V TO ±5V

622012 F02

APPLICATIO S I FOR ATIO

LT6220/LT6221/LT6222

severely overdriven, an external resistor should be used to

limit the overdriven current.

The LT6220/LT6221/LT6222’s input stages are also protected against a large differential input voltage of 1.4V or

higher by a pair of back-to-back diodes, D5/D8, to prevent

the emitter-base breakdown of the input transistors. The

current in these diodes should be limited to less than

10mA when they are active. The worse-case differential

input voltage usually occurs when the input is driven while

the output is shorted to ground in a unity-gain configuration. In addition, the amplifier is protected against ESD

strikes up to 3kV on all pins by a pair of protection diodes

on each pin that are connected to the power supplies as

shown in Figure 1.

Capacitive Load

The LT6220/LT6221/LT6222 are optimized for high bandwidth, low power and precision applications. They can

drive a capacitive load up to 100pF in a unity-gain configuration and more for higher gain. When driving a larger

capacitive load, a resistor of 10Ω to 50Ω should be

connected between the output and the capacitive load to

avoid ringing or oscillation. The feedback should still be

taken from the output so that the resistor will isolate the

capacitive load to ensure stability. Graphs on capacitive

loads show the transient response of the amplifier when

driving capacitive load with specified series resistors.

Feedback Components

When feedback resistors are used to set up gain, care must

be taken to ensure that the pole formed by the feedback

resistors and the total capacitance at the inverting input

does not degrade stability. For instance, the LT6220/

LT6221/LT6222, set up with a noninverting gain of 2, two

5k resistors and a capacitance of 5pF (part plus PC board),

will probably oscillate. The pole is formed at 12.7MHz that

will reduce phase margin by 52 degrees when the crossover frequency of the amplifier is around 10MHz. A capacitor of 10pF or higher connecting across the feedback

resistor will eliminate any ringing or oscillation.

U

TYPICAL APPLICATIO S

Stepped-Gain Photodiode Amplifier

The circuit of Figure 2 is a stepped gain transimpedance

photodiode amplifier. At low signal levels, the circuit has

a high 100kΩ gain, but at high signal levels the circuit

automatically and smoothly changes to a low 3.2kΩ gain.

The benefit of a stepped gain approach is that it maximizes

dynamic range, which is very useful on limited supplies.

Put another way, in order to get 100kΩ sensitivity and still

handle a 1mA signal level without resorting to gain reduction, the circuit would need a 100V negative voltage

supply.

The operation of the circuit is quite simple. At low photodiode currents (below 10µA) the output and inverting

input of the op amp will be no more than 1V below ground.

The LT1634 in parallel with R3 and Q2 keep a constant

current though Q2 of about 20µA. R4 maintains quiescent

current through the LT1634 and pulls Q2’s emitter above

ground, so Q1 is reverse biased and no current flows

through R2. So for small signals, the only feedback path

is R1 (and C1) and the circuit is a simple transimpedance

amplifier with 100kΩ gain.

Figure 2. Stepped-Gain Photodiode Amplifier

622012fa

15

LT6220/LT6221/LT6222

U

PACKAGE DESCRIPTIO

As the signal level increases though, the output of the op

amp goes more negative. At 12.5µA of photodiode cur-

rent, the 100kΩ gain dictates that the LT6220 output will

be about 1.25V below ground. However, at that point the

emitter of Q2 will be at ground, and the base of Q1 will be

1V below ground. Thus, Q1 turns on and photodiode

current starts to flow through R2. The transimpedance

gain is therefore now reduced to R1||R2, or about 3.1kΩ.

The circuit response is shown in Figure 3. Note the smooth

transition between the two operating gains, as well as the

linearity.

PHOTO

CURRENT

100µA/DIV

V

OUT

0.5V/DIV

5µs/DIV

622012 F03

Figure 3. Stepped-Gain Photodiode Amplifier Response

Single 3V Supply, 1MHz, 4th Order Butterworth Filter

The circuit shown in Figure 4 makes use of the low voltage

operation and the wide bandwidth of the LT6221 to create

a DC accurate 1MHz 4th order lowpass filter powered from

a 3V supply. The amplifiers are configured in the inverting

mode for the lowest distortion and the output can swing

rail-to-rail for maximum dynamic range. Figure 5 displays

the frequency response of the filter. Stopband attenuation

is greater than 100dB at 50MHz.

20

0

–20

–40

–60

GAIN (dB)

–80

–100

–120

1k 100k 1M 10M 100M

10k

FREQUENCY (Hz)

622012 F05

Figure 5. Frequency Response of Filter

Differential-In/Differential-Out Amplifier

The circuit of Figure 6 shows the LT6222 applied as a

buffered differential-in differential-out amplifier with a

gain of 2. Op amps A and B are configured as simple unitygain buffers, offering high input impedance to upstream

circuitry. Resistors R1 and R2 perform an averaging

function on the common mode input voltage and R3

attenuates it by a factor of 2/3 and references it to the

voltage source V

V

, is placed at the noninverting inputs of op amps C and

ICM

. The resultant voltage, V

OCM

MID

= 2/3 •

D. The other four resistors set gains of +3 from the

noninverting input and –2 through the inverting path. Thus

the output voltage of the upper path is:

–OUT = 3 • (2/3 • V

• (V

+ V

ICM

= 2V

= V

ICM

OCM

+ V

– V

ICM

DIFF

OCM

DIFF

+ 1/3 • V

/2)

– 2V

ICM

OCM

– V

) – 2

DIFF

16

V

VS/2

909Ω

909Ω

IN

2.67k

220pF

47pF

–

1/2 LT6221

+

1.1k

1.1k

2.21k

470pF

22pF

–

1/2 LT6221

+

3V

622012 F04

V

OUT

Figure 4. 3V, 1MHz, 4th Order Butterworth Filter

622012fa

PACKAGE DESCRIPTIO

LT6220/LT6221/LT6222

U

and the output of the lower path is:

+OUT = 3 • (2/3 • V

– V

• (V

ICM

= 2V

= V

ICM

OCM

+ V

+ V

DIFF

DIFF

ICM

/2)

OCM

+ 1/3 • V

– 2V

ICM

OCM

+ V

) – 2

DIFF

Note that the input common mode voltage does not appear

in the output as either a common mode or a difference

mode term. However the voltage V

does appear in the

OCM

output terms, and with the same polarity, so it sets up the

output DC level. Also, the differential input voltage V

DIFF

appears fully at both outputs with opposite polarity, giving

U

PACKAGE DESCRIPTIO

DD Package

8-Lead Plastic DFN (3mm × 3mm)

(Reference LTC DWG # 05-08-1698)

0.675 ±0.05

rise to the effective differential gain of 2. Calculations show

that using 1% resistors gives worst-case input common

mode feedthrough better than –31dB, whether looking at

the output common mode or difference mode. Considering the 6dB of gain, worst-case common mode rejection

ratio is 37dB. (Remember this is assuming 1% resistors.

Of course, this can be improved with more precise resistors.) Results achieved on the bench with typical 1%

resistors showed 67dB of CMRR at low frequency and

40dB CMRR at 1MHz. Gains other than 2 can be achieved

by setting R3 = α • (R1||R2), R5 = α • R4 and R7 = α • R6

where gain = α.

R = 0.115

TYP

0.38 ± 0.10

85

3.5 ±0.05

1.65 ±0.05

(2 SIDES)2.15 ±0.05

PACKAGE

OUTLINE

0.25 ± 0.05

RECOMMENDED SOLDER PAD PITCH AND DIMENSIONS

2.38 ±0.05

(2 SIDES)

0.50

BSC

3.00 ±0.10

PIN 1

TOP MARK

(NOTE 6)

0.200 REF

NOTE:

1. DRAWING TO BE MADE A JEDEC PACKAGE OUTLINE M0-229 VARIATION OF (WEED-1)

2. DRAWING NOT TO SCALE

3. ALL DIMENSIONS ARE IN MILLIMETERS

4. DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE

MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE

5. EXPOSED PAD SHALL BE SOLDER PLATED

6. SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION

ON TOP AND BOTTOM OF PACKAGE

(4 SIDES)

0.75 ±0.05

1.65 ± 0.10

0.00 – 0.05

(2 SIDES)

0.25 ± 0.05

BOTTOM VIEW—EXPOSED PAD

2.38 ±0.10

(2 SIDES)

14

0.50 BSC

(DD8) DFN 1203

622012fa

17

LT6220/LT6221/LT6222

U

PACKAGE DESCRIPTIO

0.62

MAX

0.95

REF

S5 Package

5-Lead Plastic TSOT-23

(Reference LTC DWG # 05-08-1635)

2.90 BSC

(NOTE 4)

1.22 REF

3.85 MAX

2.62 REF

RECOMMENDED SOLDER PAD LAYOUT

PER IPC CALCULATOR

0.20 BSC

DATUM ‘A’

0.30 – 0.50 REF

NOTE:

1. DIMENSIONS ARE IN MILLIMETERS

2. DRAWING NOT TO SCALE

3. DIMENSIONS ARE INCLUSIVE OF PLATING

1.4 MIN

0.09 – 0.20

(NOTE 3)

4. DIMENSIONS ARE EXCLUSIVE OF MOLD FLASH AND METAL BURR

5. MOLD FLASH SHALL NOT EXCEED 0.254mm

6. JEDEC PACKAGE REFERENCE IS MO-193

2.80 BSC

1.50 – 1.75

(NOTE 4)

PIN ONE

0.95 BSC

0.80 – 0.90

1.00 MAX

0.30 – 0.45 TYP

5 PLCS (NOTE 3)

0.01 – 0.10

1.90 BSC

S5 TSOT-23 0302

18

622012fa

PACKAGE DESCRIPTIO

.050 BSC

LT6220/LT6221/LT6222

U

S8 Package

8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

.189 – .197

.045 ±.005

(4.801 – 5.004)

8

NOTE 3

7

6

5

.245

MIN

.030 ±.005

TYP

RECOMMENDED SOLDER PAD LAYOUT

.010 – .020

(0.254 – 0.508)

.008 – .010

(0.203 – 0.254)

.016 – .050

NOTE:

1. DIMENSIONS IN

2. DRAWING NOT TO SCALE

3. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

(0.406 – 1.270)

INCHES

(MILLIMETERS)

× 45°

.160 ±.005

0°– 8° TYP

.228 – .244

(5.791 – 6.197)

GN Package

16-Lead Plastic SSOP (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1641)

.045 ±.005

.053 – .069

(1.346 – 1.752)

.014 – .019

(0.355 – 0.483)

TYP

.150 – .157

(3.810 – 3.988)

NOTE 3

1

2

16

15

3

4

.189 – .196*

(4.801 – 4.978)

12 11 10

14

13

.004 – .010

(0.101 – 0.254)

.050

(1.270)

BSC

9

SO8 0303

.009

(0.229)

REF

.254 MIN

RECOMMENDED SOLDER PAD LAYOUT

.007 – .0098

(0.178 – 0.249)

.016 – .050

NOTE:

1. CONTROLLING DIMENSION: INCHES

2. DIMENSIONS ARE IN

3. DRAWING NOT TO SCALE

*DIMENSION DOES NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.006" (0.152mm) PER SIDE

**DIMENSION DOES NOT INCLUDE INTERLEAD FLASH. INTERLEAD

FLASH SHALL NOT EXCEED 0.010" (0.254mm) PER SIDE

(0.406 – 1.270)

(MILLIMETERS)

INCHES

.150 – .165

.0250 BSC.0165 ± .0015

.015

(0.38 ± 0.10)

0° – 8° TYP

± .004

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

× 45°

.229 – .244

(5.817 – 6.198)

.0532 – .0688

(1.35 – 1.75)

.008 – .012

(0.203 – 0.305)

TYP

12

.150 – .157**

(3.810 – 3.988)

5

4

678

3

.004 – .0098

(0.102 – 0.249)

.0250

(0.635)

BSC

GN16 (SSOP) 0204

622012fa

19

LT6220/LT6221/LT6222

U

TYPICAL APPLICATIO

RELATED PARTS

5.6pF

+ V

+IN

– V

–IN

DIFF

DIFF

/2

/2

+

A

1/4 LT6222

–

+

B

1/4 LT6222

R4

1k

–

1/4 LT6222

R1

2k

V

R2

2k

R6

1k

+

MID

+

1/4 LT6222

–

V

ICM

V

ICM

–

5.6pF

= ±1.3V TO ±6V

V

S

BW ≅ 11MHz

R5

2k

+

V

S

D

R3

2k

C

R7

–

V

2k

S

622012 F06

–OUT

V

OCM

+OUT

Figure 6. Buffered Gain of 2 Differential-In/Differential-Out Amplifier

PART NUMBER DESCRIPTION COMMENTS

LT1498/LT1499 Dual/Quad 10MHz, 6V/µs Rail-to-Rail Input/ High DC Accuracy, 475µV V

Output C

LT1800/LT1801/LT1802 Single/Dual/Quad 80MHz, 25V/µs, 350µV V

Op Amps Wide Supply Range, 2.2V to 30V

LOAD

, 250nA I

OS(MAX)

BIAS(MAX)

Max Supply Current 2.2mA/Amp,

OS(MAX)

, Max Supply Current 2mA/Amp

Low Power Rail-to-Rail Input/Output Precision Op Amps

LT1803/LT1804/LT1805 Single/Dual/Quad 85MHz, 100V/µs 2mV V

, Max Supply Current 3mA/Amp

OS(MAX)

Rail-to-Rail Input/Output Op Amps

LT1806/LT1807 Single/Dual 325MHz, 140V/µs Rail-to-Rail Input/ High DC Accuracy, 550µV V

Max Low Noise 3.5nV/√Hz

OS(MAX)

Output Op Amps Low Distortion –80dBc at 5MHz, Power Down (LT1806)

LT1809/LT1810 Single/Dual 180MHz, Rail-to-Rail Input/Output Op Amps 350V/µs Slew Rate, Low Distortion –90dBc at 5MHz,

Power Down (LT1809)

20

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507 ● www.linear.com

622012fa

LT/TP 0204 1K • PRINTED IN USA

© LINEAR TECHNOLOGY CORPORATION 2003

Loading...

Loading...