Page 1

FEATURES

■

Wide Input Range: 4V to 60V

■

Output Voltages up to 36V (Step-Down)

■

Burst Mode® Operation: <100µA Supply Current

■

10µA Shutdown Supply Current

■

±1.3% Reference Accuracy

■

200kHz Fixed Frequency

■

Drives N-Channel MOSFET

■

Programmable Soft-Start

■

Programmable Undervoltage Lockout

■

Internal High Voltage Regulator for Gate Drive

■

Thermal Shutdown

■

Current Limit Unaffected by Duty Cycle

■

16-Pin Thermally Enhanced TSSOP Package

U

APPLICATIO S

■

Industrial Power Distribution

■

12V and 42V Automotive and Heavy Equipment

■

High Voltage Single Board Systems

■

Distributed Power Systems

■

Avionics

■

Telecom Power

LT3724

High Voltage, Current Mode

Switching Regulator Controller

U

DESCRIPTIO

The LT®3724 is a DC/DC controller used for medium

power, low part count, low cost, high efficiency supplies.

It offers a wide 4V-60V input range (7.5V minimum startup

voltage) and can implement step-down, step-up, inverting

and SEPIC topologies.

The LT3724 includes Burst Mode operation, which reduces quiescent current below 100µA and maintains high

efficiency at light loads. An internal high voltage bias

regulator allows for simple biasing and can be back driven

to increase efficiency.

Additional features include fixed frequency current mode

control for fast line and load transient response; a gate

driver capable of driving large N-channel MOSFETs; a

precision undervoltage lockout function; 10µA shutdown

current; short-circuit protection; and a programmable

soft-start function that directly controls output voltage

slew rates at startup which limits inrush current, minimizes overshoot and facilitates supply sequencing.

The LT3724 is available in a 16-lead thermally enhanced

TSSOP package.

, LTC and LT are registered trademarks of Linear Technology Corporation.

Burst Mode is a registered trademark of Linear Technology Corporation.

All other trademarks are the property of their respective owners.

Protected by U.S. Patents including 5731694, 6498466, 6611131.

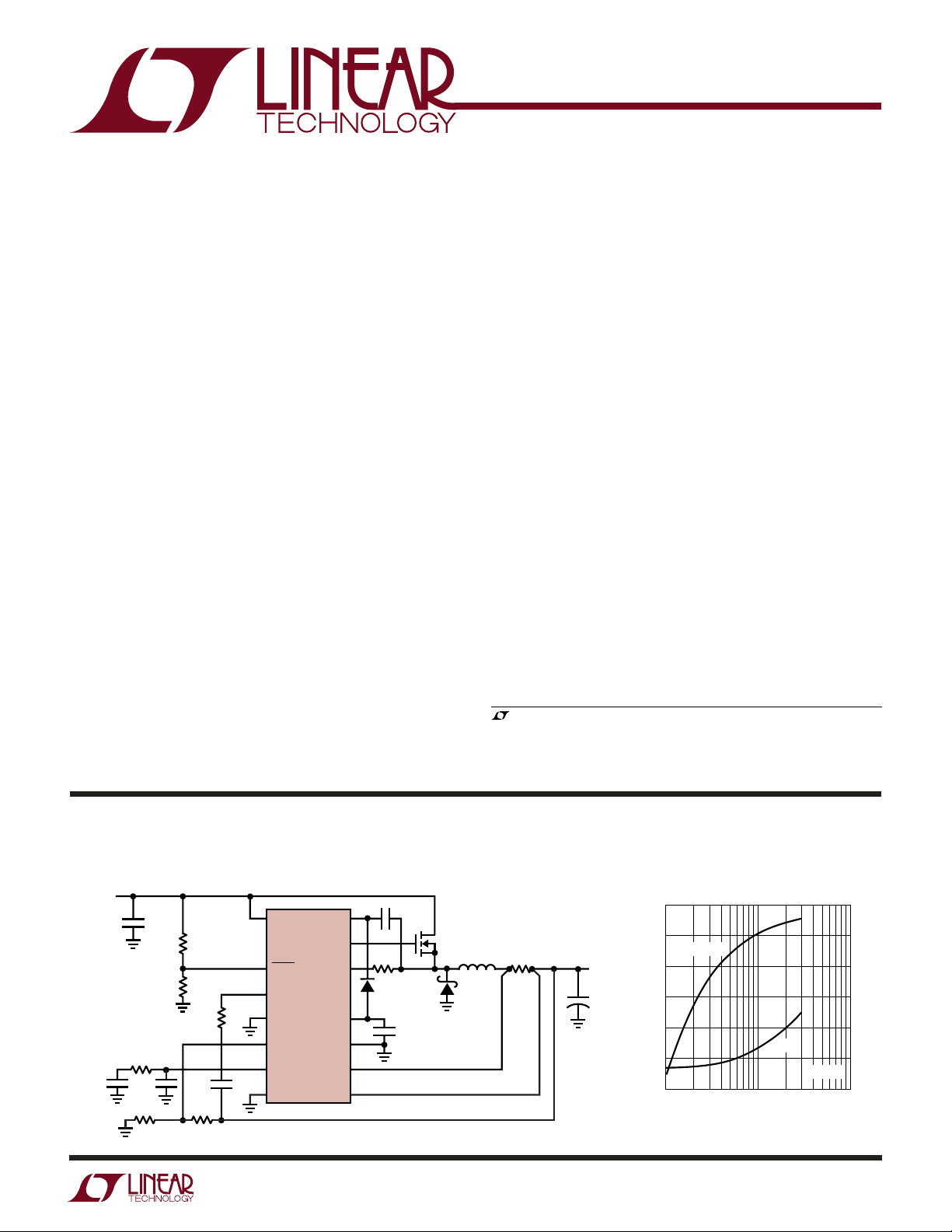

TYPICAL APPLICATIO

V

30V TO

60V

68µF

IN

C

IN

40.2k

120pF680pF

4.99k 93.1k

1M

68.1k

200k

High Voltage Step-Down Regulator

V

IN

SHDN

C

SS

Burst_EN

V

FB

V

C

1000pF

SGND

LT3724

U

BOOST

PGND

SENSE

SENSE

Efficiency and Power Loss

vs Load Current

95

0.22µF

TG

10Ω

SW

V

CC

+

–

1µF

SS3H9

Si7852

47µH

0.025Ω

3724 TA01a

V

OUT

24V

75W

+

C

OUT

330µF

90

EFFICIENCY

85

80

EFFICIENCY (%)

75

70

65

0.1

LOSS

VIN = 48V

110

LOAD CURRENT (A)

3724 TA01b

12

10

POWER LOSS (W)

8

6

4

2

0

3724fa

1

Page 2

LT3724

WW

W

U

ABSOLUTE AXI U RATI GS

(Note 1)

Input Supply Voltage (VIN)......................... 65V to –0.3V

Boosted Supply Voltage (BOOST).............. 80V to – 0.3V

Switch Voltage (SW)(Note 8) ....................... 65V to –1V

Differential Boost Voltage

(BOOST to SW) ..................................... 24V to –0.3V

Bias Supply Voltage (V

SENSE

+

and SENSE– Voltages ................... 40V to – 0.3V

Differential Sense Voltage

+

(SENSE

to SENSE–) .................................. 1V to – 1V

BURST_EN Voltage.................................... 24V to – 0.3V

, VFB, CSS, and SHDN Voltages ................5V to –0.3V

V

C

C

and SHDN Pin Currents ................................... 1mA

SS

Operating Junction Temperature Range (Note 2)

LT3724E (Note 3) ..............................–40°C to 125°C

LT3724I .............................................–40°C to 125°C

Storage Temperature .............................–65°C to 150°C

Lead Temperature (Soldering, 10 sec).................. 300°C

) .........................24V to –0.3V

CC

UUW

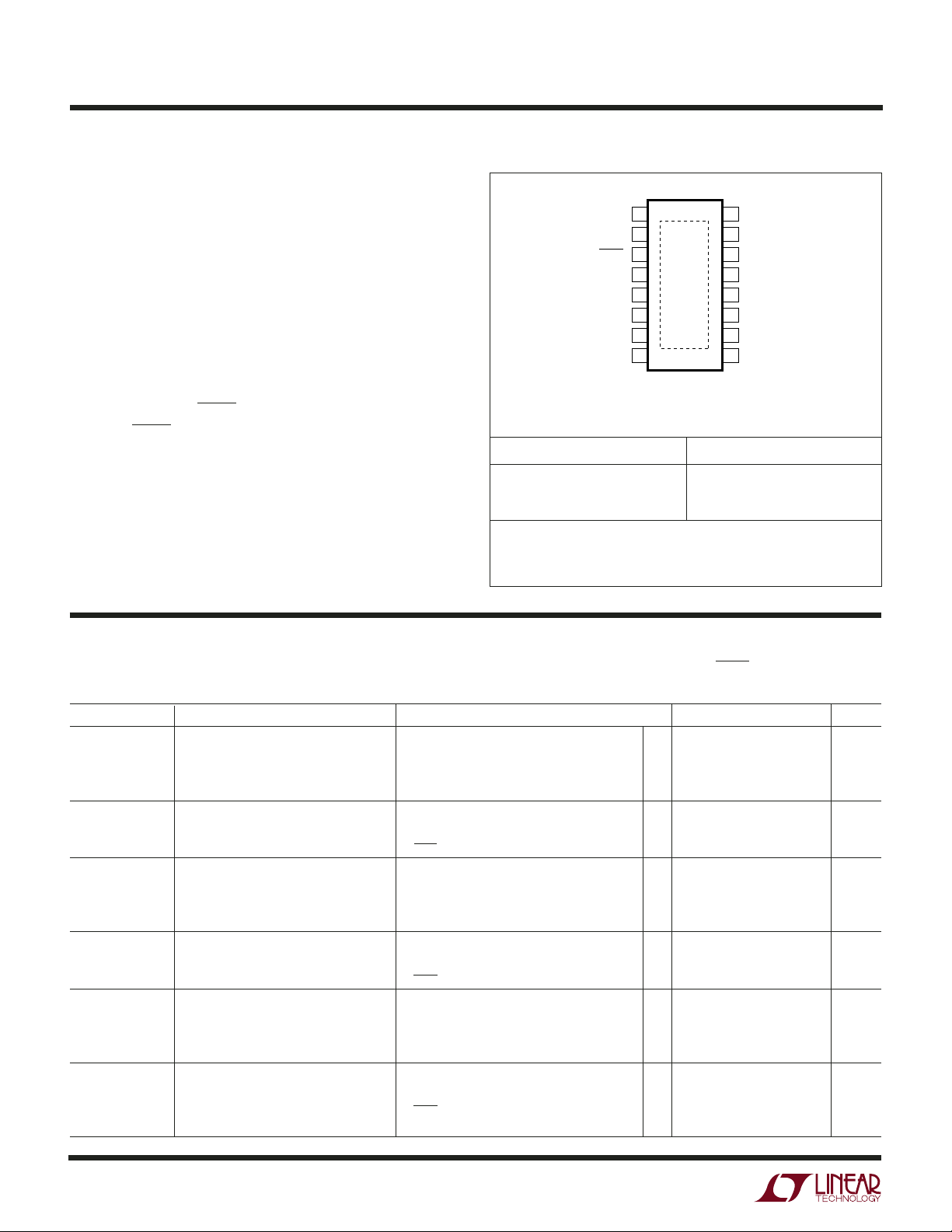

PACKAGE/ORDER I FOR ATIO

TOP VIEW

1

V

IN

2

NC

3

SHDN

4

C

SS

BURST_EN

V

FB

V

C

SGND

16-LEAD PLASTIC TSSOP

T

= 125°C, θJA = 40°C/W, θJC = 10°C/W

JMAX

EXPOSED PAD IS SGND (PIN 17) MUST BE SOLDERED TO PCB

5

6

7

8

FE PACKAGE

17

ORDER PART NUMBER

LT3724EFE

LT3724IFE

Order Options Tape and Reel: Add #TR

Lead Free: Add #PBF Lead Free Tape and Reel: Add #TRPBF

Lead Free Part Marking: http://www.linear.com/leadfree/

Consult LTC Marketing for parts specified with wider operating temperature ranges.

BOOST

16

TG

15

SW

14

NC

13

V

12

CC

PGND

11

10

9

SENSE

SENSE

+

–

FE PART MARKING

3724EFE

3724IFE

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

–

SENSE

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

I

V

I

V

I

= SENSE+ = 10V, SGND = PGND = SW = 0V, unless otherwise noted.

IN

VIN

BOOST

BOOST

CC

VCC

Operating Voltage Range (Note 4)

Minimum Start Voltage

UVLO Threshold (Falling)

UVLO Threshold Hysteresis 670 mV

VIN Supply Current V

V

Burst Mode Current V

IN

Shutdown Current V

V

IN

Operating Voltage Range

Operating Voltage Range (Note 5) V

UVLO Threshold (Rising) V

UVLO Threshold Hysteresis V

BOOST Supply Current (Note 6) 1.4 mA

BOOST Burst Mode Current V

BOOST Shutdown Current V

Operating Voltage Range (Note 5)

Output Voltage Over Full Line and Load Range

UVLO Threshold (Rising) 6.25 V

UVLO Threshold Hysteresis 500 mV

VCC Supply Current (Note 6)

V

Burst Mode Current V

CC

Shutdown Current V

V

CC

Short-Circuit Current

The ● denotes the specifications which apply over the full operating

= 25°C. VIN = 20V, VCC = BOOST = BURST_EN = 10V, SHDN = 2V,

A

●

460V

●

7.5 V

●

3.65 3.8 3.95 V

> 9V 20 µA

CC

BURST_EN

SHDN

BOOST

BOOST

BOOST

BURST_EN

SHDN

BURST_EN

SHDN

= 0V, VFB = 1.35V 20 µA

= 0V

- V

SW

- V

SW

- V

SW

= 0V 0.1 µA

= 0V 0.1 µA

= 0V 80 µA

= 0V 20 µA

●

●

●

●

●

●

●

–30 –55 mA

10 15 µA

5V

400 mV

8 8.3 V

1.7 2.1 mA

75 V

20 V

20 V

3724fa

2

Page 3

LT3724

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

–

SENSE

= SENSE+ = 10V, SGND = PGND = SW = 0V, unless otherwise noted.

The ● denotes the specifications which apply over the full operating

= 25°C. VIN = 20V, VCC = BOOST = BURST_EN = 10V, SHDN = 2V,

A

SYMBOL PARAMETER CONDITIONS MIN TYP MAX UNITS

V

I

FB

V

FB

SHDN

Error Amp Reference Voltage Measured at VFB Pin 1.224 1.231 1.238 V

●

1.215 1.245 V

Feedback Input Current 25 nA

Enable Threshold (Rising)

●

1.3 1.35 1.4 V

Threshold Hysteresis 120 mV

V

SENSE

I

SENSE

f

SW

V

FB(SS)

Common Mode Range

Current Limit Sense Voltage V

Input Current V

(I

SENSE

+

+ I

–

) 2V < V

SENSE

SENSE

SENSE(CM)

V

SENSE(CM)

+

– V

SENSE

–

= 0V 400 µA

SENSE(CM)

< 3.5V 2 µA

> 4V –150 µA

●

036V

●

140 150 175 mV

Operating Frequency 190 200 210 kHz

●

175 220 kHz

Soft-Start Disable Voltage VFB Rising 1.185 V

Soft-Start Disable Hysteresis 300 mV

I

SS

g

m

A

V

V

C

I

VC

V

TG

t

TG

t

TG(OFF)

t

TG(ON)

I

SW

Soft-Start Capacitor Control Current 2 µA

Error Amp Transconductance ●275 340 400 µmhos

Error Amp DC Voltage Gain 62 dB

Error Amp Output Range Zero Current to Current Limit 1.2 V

Error Amp Sink/Source Current ±30 µA

Gate Drive Output On Voltage (Note 7) C

Gate Drive Output Off Voltage C

Gate Drive Rise/Fall Time 10% to 90% or 90% to 10%, C

= 3300pF 9.8 V

LOAD

= 3300pF 0.1 V

LOAD

= 3300pF 60 ns

LOAD

Minimum Switch Off Time 350 ns

Minimum Switch On Time

●

300 500 ns

SW Pin Sink Current VSW = 2V 300 mA

Note 1: Stresses beyond those listed under Absolute Maximum Ratings

may cause permanent damage to the device. Exposure to any Absolute

Maximum Rating condition for extended periods may affect device

reliability and lifetime.

Note 2: The LT3724 includes overtemperature protection that is intended

to protect the device during momentary overload conditions. Junction

temperature will exceed 125°C when overtemperature protection is active.

Continuous operation above the specified maximum operating junction

temperature may impair device reliability.

Note 3: The LT3724E is guaranteed to meet performance specifications

from 0°C to 125°C junction temperature. Specifications over the –40°C to

125°C operating junction temperature range are assured by design,

characterization and correlation with statistical process controls. The

LT3724I is guaranteed over the full –40°C to 125°C operating junction

temperature range.

Note 4: VIN voltages below the start-up threshold (7.5V) are only

supported when the V

Note 5: Operating range is dictated by MOSFET absolute maximum V

is externally driven above 6.5V.

CC

GS

.

Note 6: Supply current specification does not include switch drive

currents. Actual supply currents will be higher.

Note 7: DC measurement of gate drive output “ON” voltage is typically

8.6V. Internal dynamic bootstrap operation yields typical gate “ON”

voltages of 9.8V during standard switching operation. Standard operation

gate “ON” voltage is not tested but guaranteed by design.

Note 8: The –1V absolute maximum on the SW pin is a transient

condition. It is guaranteed by design and not subject to test.

3724fa

3

Page 4

LT3724

UW

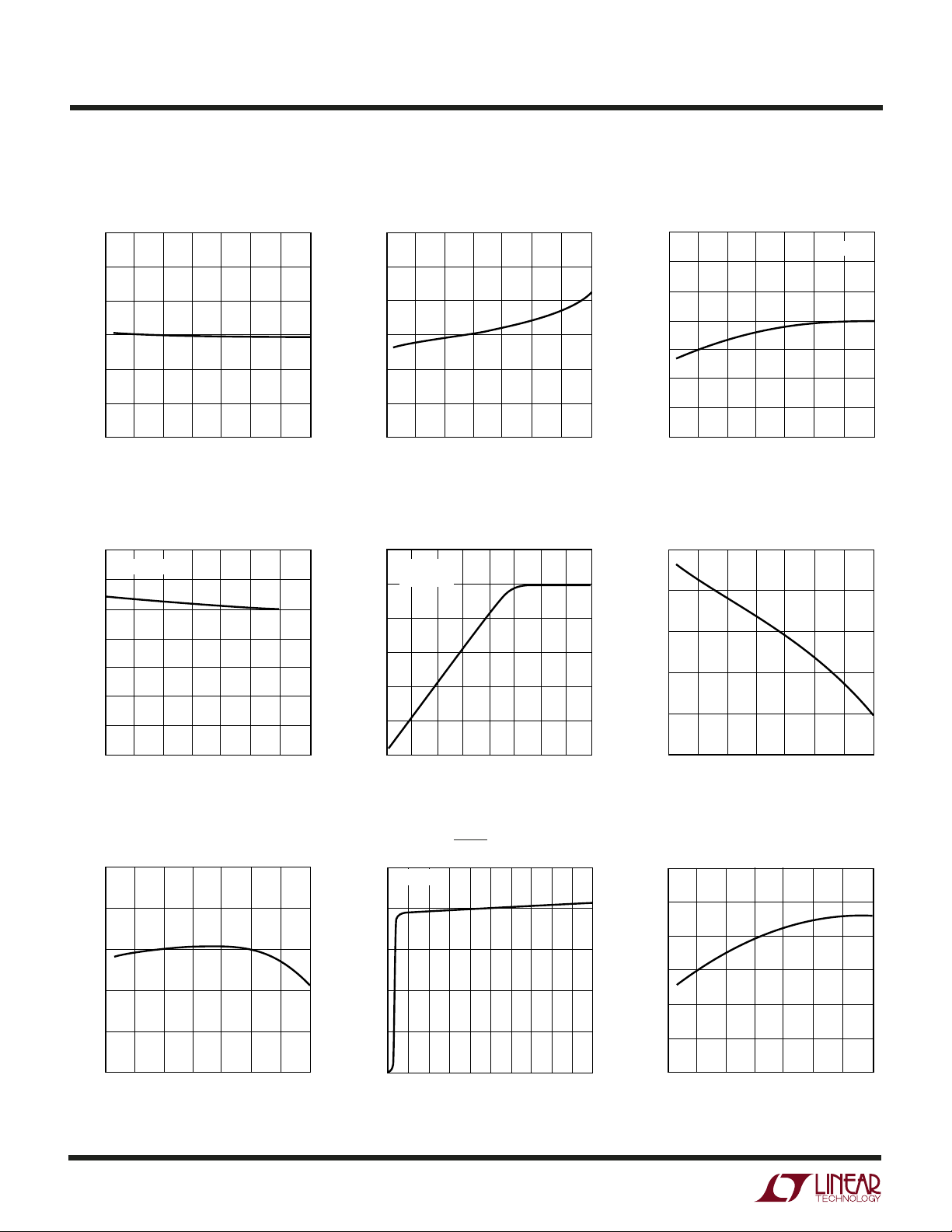

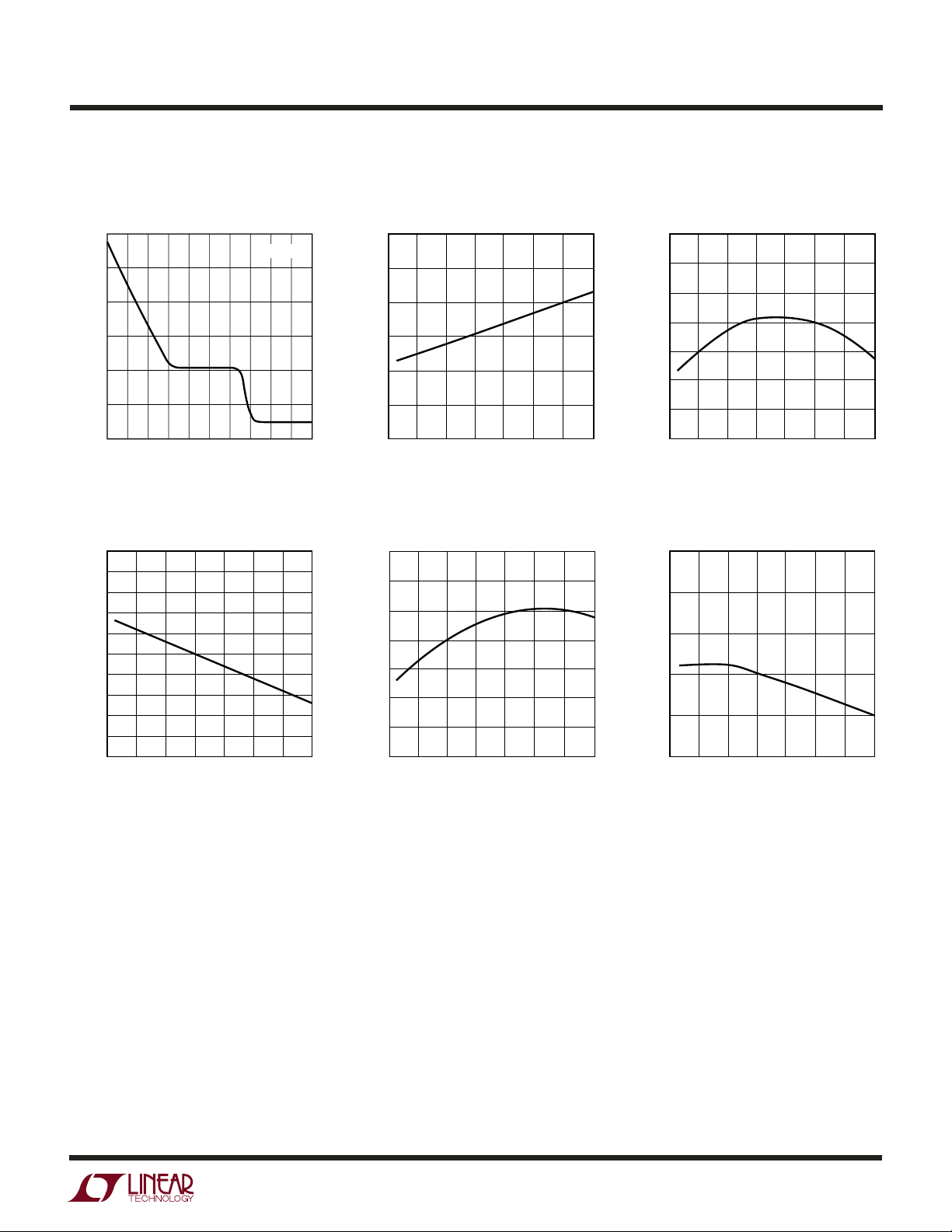

TYPICAL PERFOR A CE CHARACTERISTICS

Shutdown Threshold (Rising)

vs Temperature

1.38

1.37

1.36

1.35

1.34

1.33

SHUTDOWN THRESHOLD, RISING (V)

1.32

–50 25 75

–25 0 50 100 125

TEMPERATURE (°C)

V

vs I

CC

CC(LOAD)

8.2

TA = 25°C ICC = 20mA

8.1

8.0

7.9

(V)

CC

V

7.8

7.7

7.6

3724 G01

Shutdown Threshold (Falling)

vs Temperature V

1.26

1.25

1.24

1.23

1.22

1.21

SHUTDOWN THRESHOLD, FALLING (V)

1.20

–25 0 50 100 125

(V)

CC

V

–50

VCC vs V

9

T

A

8

7

6

5

4

= 25°C

25 75

TEMPERATURE (°C)

3724 G02

IN

vs Temperature

CC

8.2

8.1

8.0

7.9

(V)

CC

V

7.8

7.7

7.6

7.5

–50 25 75–25 0 50 100 125

TEMPERATURE (°C)

I

Current Limit vs Temperature

CC

70

60

50

40

CURRENT LIMIT (mA)

CC

I

30

ICC = 20mA

3724 G03

7.5

0

510

20 30 35

15 25

I

(mA)

CC (LOAD)

VCC UVLO Threshold (Rising)

vs Temperature

6.5

6.4

6.3

6.2

UVLO THRESHOLD, RISING (V)

6.1

CC

V

6.0

–50 25 75–25 0 50 100 125

TEMPERATURE (°C)

4

3724 G04

3724 G07

3

4

57

vs VCC (SHDN = 0V)

CC

25

TA = 25°C

20

15

(µA)

CC

I

10

5

0

246

0

11

6

8

VIN (V)

10

9

12

3724 G05

20

–50 25 75–25 0 50 100 125

TEMPERATURE (°C)

3724 G06

Error Amp Transconductance

vs TemperatureI

350

345

340

335

330

325

ERROR AMP TRANSCONDUCTANCE (µMhos)

810

VCC (V)

12 14 18

16

3724 G08

320

–50

20

–25 0

TEMPERATURE (°C)

50 100 125

25 75

3724 G09

3724fa

Page 5

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LT3724

I

(SENSE+ + SENSE–)

V

SENSE (CM)

400

300

200

(µA)

)

–

100

+ SENSE

+

0

(SENSE

I

–100

–200

0

0.5

1.0 1.5 2.0

V

SENSE (CM)

vs

2.5 4.53.5 5.04.03.0

Maximum Current Sense

Threshold vs Temperature

160

158

156

154

152

150

148

146

144

CURRENT SENSE THRESHOLD (mV)

142

140

–50 25 75

–25 0

TEMPERATURE (°C)

50 100 125

(V)

Operating Frequency

vs Temperature

TA = 25°C

3724 G10

230

220

210

200

190

OPERATING FREQUENCY (kHz)

180

170

–50

–25 0

V

UVLO Threshold (Rising)

IN

25 75

TEMPERATURE (°C)

50 100 125

3724 G11

vs Temperature

4.54

4.52

4.50

4.48

4.46

4.44

UVLO THRESHOLD, RISING (V)

IN

4.42

V

4.40

–50 25 75

–25 0

TEMPERATURE (°C)

3724 G13 3724 G14 3724 G15

50 100 125

Error Amp Reference

vs Temperature

1.234

1.233

1.232

1.231

1.230

1.229

ERROR AMP REFERENCE (V)

1.228

1.227

–50 25 75

–25 0

TEMPERATURE (°C)

V

UVLO Threshold (Falling)

IN

vs Temperature

3.86

3.84

3.82

3.80

3.78

UVLO THRESHOLD, FALLING (V)

IN

V

3.76

–50 25 75

–25 0

TEMPERATURE (°C)

50 100 125

50 100 125

3724 G12

3724fa

5

Page 6

LT3724

U

UU

PI FU CTIO S

VIN (Pin 1): The VIN pin is the main supply pin and should

be decoupled to SGND with a low ESR capacitor located

close to the pin.

NC (Pin 2): No Connection.

SHDN (Pin 3): The SHDN pin has a precision IC enable

threshold of 1.35V (rising) with 120mV of hysteresis. It is

used to implement an undervoltage lockout (UVLO) circuit. See Application Information section for implementing a UVLO function. When the SHDN pin is pulled below

a transistor V

entered, all internal circuitry is disabled and the V

current is reduced to approximately 10µA. Typical pin

input bias current is <10µA and the pin is internally

clamped to 6V.

C

(Pin 4): The soft-start pin is used to program the

SS

supply soft-start function. The pin is connected to V

a ceramic capacitor (CSS) and 200kΩ series resistor.

During start-up, the supply output voltage slew rate is

controlled to produce a 2µA average current through the

soft-start coupling capacitor. Use the following formula to

calculate C

C

= 2µA(tSS/V

SS

See the application section for more information on setting the rise time of the output voltage during start-up.

Shorting this pin to SGND disables the soft-start function.

BURST_EN (Pin 5): The BURST_EN pin is used to enable

or disable Burst Mode operation. Connect the BURST_EN

pin to ground to enable the burst mode function. Connect

the pin to V

(0.7V), a low current shutdown mode is

BE

for a given output voltage slew rate:

SS

)

OUT

to disable the burst mode function.

CC

supply

IN

OUT

via

optimize transient response. Connecting a 100pF or greater

high frequency bypass capacitor from this pin to ground

is recommended. When Burst Mode operation is enabled

(see Pin 5 description), an internal low impedance clamp

on the V

pin is set at 100mV below the burst threshold,

C

which limits the negative excursion of the pin voltage.

Therefore, this pin cannot be pulled low with a low impedance source. If the V

pin must be externally manipulated,

C

do so through a 1kΩ series resistance.

SGND (Pin 8, 17): The SGND pin is the low noise ground

reference. It should be connected to the –V

side of the

OUT

output capacitors. Careful layout of the PCB is necessary

to keep high currents away from this SGND connection.

See the Application Information section for helpful hints

on PCB layout of grounds.

SENSE

the current sense amplifier and is connected to the V

–

(Pin 9): The SENSE– pin is the negative input for

OUT

side of the sense resistor for step-down applications. The

sensed inductor current limit is set to 150mV across the

SENSE inputs.

SENSE

+

(Pin 10): The SENSE+ pin is the positive input for

the current sense amplifier and is connected to the inductor side of the sense resistor for step-down applications.

The sensed inductor current limit is set to 150mV across

the SENSE inputs.

PGND (Pin 11): The PGND pin is the high-current ground

reference for internal low side switch and the V

regulator

CC

circuit. Connect the pin directly to the negative terminal of

the V

decoupling capacitor. See the Application Infor-

CC

mation section for helpful hints on PCB layout of grounds.

(Pin 6): The output voltage feedback pin, VFB, is

V

FB

externally connected to the supply output voltage via a

resistive divider. The VFB pin is internally connected to the

inverting input of the error amplifier. In regulation, V

FB

is

1.231V.

V

(Pin 7): The VC pin is the output of the error amplifier

C

whose voltage corresponds to the maximum (peak) switch

current per oscillator cycle. The error amplifier is typically

configured as an integrator circuit by connecting an RC

network from the V

pin to SGND. This circuit creates the

C

dominant pole for the converter regulation control loop.

Specific integrator characteristics can be configured to

6

VCC (Pin 12): The VCC pin is the internal bias supply

decoupling node. Use low ESR 1µF ceramic capacitor to

decouple this node to PGND. Most internal IC functions

are powered from this bias supply. An external diode

connected from V

to the BOOST pin charges the

CC

bootstrapped capacitor during the off-time of the main

power switch. Back driving the VCC pin from an external DC

voltage source, such as the V

output of the buck

OUT

regulator supply, increases overall efficiency and reduces

power dissipation in the IC. In shutdown mode this pin

sinks 20µA until the pin voltage is discharged to 0V.

NC (Pin 13): No Connection.

3724fa

Page 7

LT3724

U

UU

PI FU CTIO S

SW (Pin 14): In step-down applications the SW pin is

connected to the cathode of an external clamping Schottky

diode, the drain of the power MOSFET and the inductor.

The SW node voltage swing is from V

of the power MOSFET, to a Schottky voltage drop below

ground during the off-time of the power MOSFET. In startup and in operating modes where there is insufficient

inductor current to freewheel the Schottky diode, an

internal switch is turned on to pull the SW pin to ground

so that the BOOST pin capacitor can be charged. Give

careful consideration in choosing the Schottky diode to

limit the negative voltage swing on the SW pin.

TG (Pin 15): The TG pin is the bootstrapped gate drive for

the top N-Channel MOSFET. Since very fast high currents

are driven from this pin, connect it to the gate of the power

during the on-time

IN

MOSFET with a short and wide, typically 0.02” width, PCB

trace to minimize inductance.

BOOST (Pin 16): The BOOST pin is the supply for the

bootstrapped gate drive and is externally connected to a

low ESR ceramic boost capacitor referenced to SW pin.

The recommended value of the BOOST capacitor,C

is 50 times greater that the total input capacitance of the

topside MOSFET. In most applications 0.1µF is adequate.

The maximum voltage that this pin sees is VIN + VCC,

ground referred, and is limited to 75V.

Exposed Pad (SGND) (Pin 17): The exposed leadframe is

internally connected to the SGND pin. Solder the exposed

pad to the PCB ground for electrical contact and optimal

thermal performance.

BOOST

,

3724fa

7

Page 8

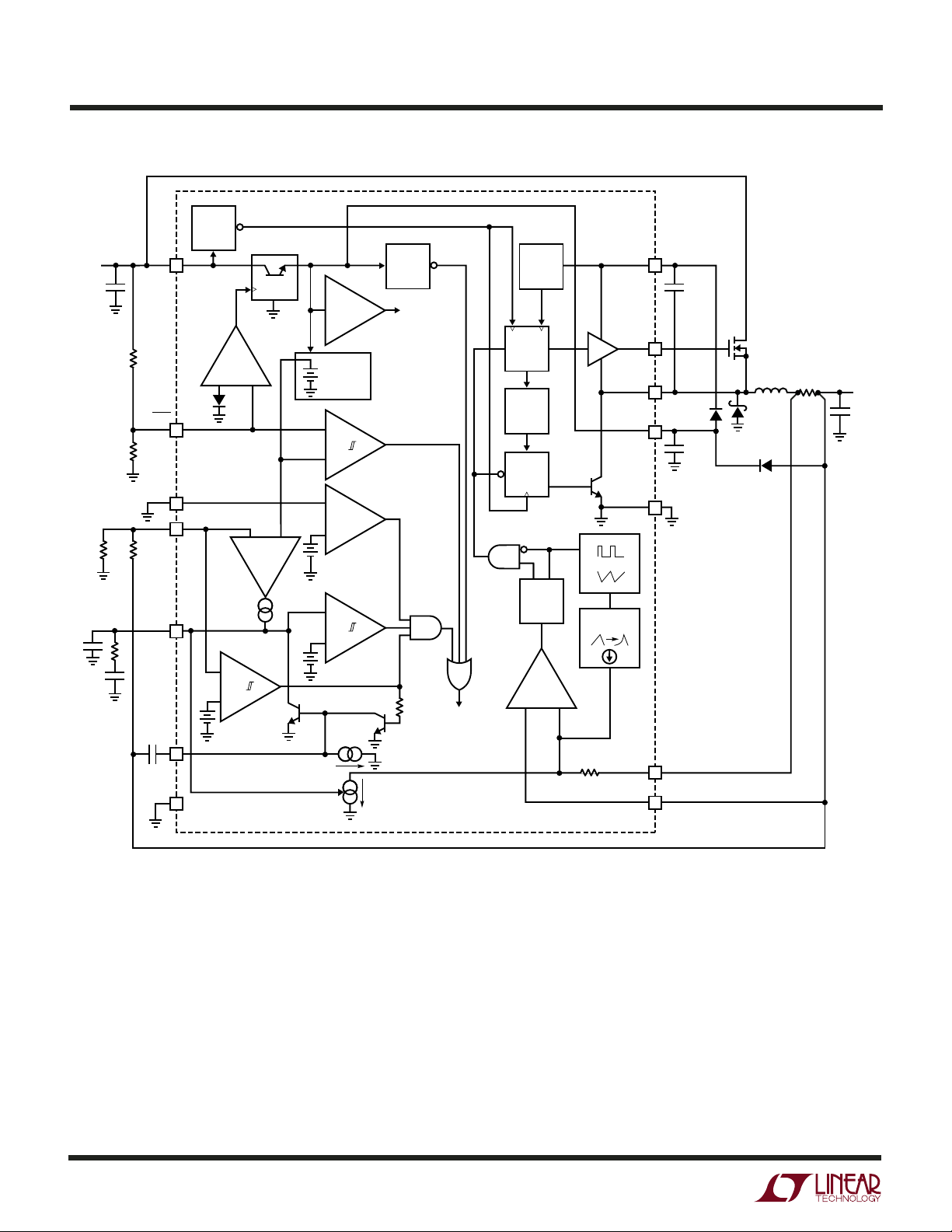

LT3724

U

U

W

FU CTIO AL DIAGRA

V

IN

UVLO

(<4V)

V

IN

RA

SHDN

RB

BURST_EN

V

R2

C

C

SS

SGND

1

3

5

FB

6

V

C

7

SS

1.185V

4

8

V

IN

C

IN

R1

C

C2

R

C

C

C1

–

–

g

m

ERROR

AMP

SOFT-START

DISABLE/BURST

ENABLE

+

–

8V V

CC

REGULATOR

+

+

1.231V

0.5V

~1V

3.8V

REGULATOR

FEEDBACK

REFERENCE

+

–

–

+

–

+

2µA

V

CC

UVLO

(<6V)

INTERNAL

SUPPLY RAIL

BURST MODE

OPERATION

DRIVE

CONTROL

SWITCH

LOGIC

DRIVE

CONTROL

CURRENT

SENSE

COMPARATOR

NOL

–

BST

UVLO

BOOST

16

C

BOOST

BOOSTED

SWITCH

DRIVER

OSCILLATOR

SQ

R

SLOPE COMP

GENERATOR

15

14

12

11

TG

SW

V

CC

PGND

M1

L1

R

SENSE

D2

C

VCC

D1

D3

(OPTIONAL)

V

OUT

C

OUT

+

+

+

–

10

9

SENSE

SENSE

–

8

3724 FD

3724fa

Page 9

OPERATIO

LT3724

U

(Refer to Functional Diagram)

The LT3724 is a PWM controller with a constant frequency, current mode control architecture. It is designed

for low to medium power, switching regulator applications. Its high operating voltage capability allows it to stepup or down input voltages up to 60V without the need for

a transformer. The LT3724 is used in nonsynchronous

applications, meaning that a freewheeling rectifier diode

(D1 of Function Diagram) is used instead of a bottom side

MOSFET. For circuit operation, please refer to the Functional Diagram of the IC and Typical Application on the

front page of the data sheet. The LT3800 is a similar part

that uses synchronous rectification, replacing the diode

with a MOSFET in a step-down application.

Main Control Loop

During normal operation, the external N-channel MOSFET

switch is turned on at the beginning of each cycle. The

switch stays on until the current in the inductor exceeds a

current threshold set by the DC control voltage, V

, which

C

is the output of the voltage control loop. The voltage

control loop monitors the output voltage, via the V

FB

pin

voltage, and compares it to an internal 1.231V reference.

It increases the current threshold when the V

voltage is

FB

below the reference voltage and decreases the current

threshold when the V

voltage is above the reference

FB

voltage. For instance, when an increase in the load current

occurs, the output voltage drops causing the V

voltage

FB

to drop relative to the 1.231V reference. The voltage

control loop senses the drop and increases the current

threshold. The peak inductor current is increased until the

average inductor current equals the new load current and

the output voltage returns to regulation.

Current Limit/Short-Circuit

The inductor current is measured with a series sense

resistor (see the Typical Application on the front page).

When the voltage across the sense resistor reaches the

maximum current sense threshold, typically 150mV, the

TG MOSFET driver is disabled for the remainder of that

cycle. If the maximum current sense threshold is still

exceeded at the beginning of the next cycle, the entire cycle

is skipped. Cycle skipping keeps the inductor currents to

a reasonable value during a short-circuit, particularly

when V

is high. Setting the sense resistor value is

IN

discussed in the “Application Information” section.

/Boosted Supply

V

CC

An internal V

regulator provides VIN derived gate-drive

CC

power for start-up under all operating conditions with

MOSFET gate charge loads up to 90nC. The regulator can

operate continuously in applications with V

to 60V, provided the V

voltage and/or MOSFET gate

IN

voltages up

IN

charge currents do not create excessive power dissipation

in the IC. Safe operating conditions for continuous regulator use are shown in Figure 1. In applications where

these conditions are exceeded, V

must be derived from

CC

an external source after start-up. The LT3724 regulator

can, however, be used for “full time” use in applications

where short-duration V

transients exceed allowable con-

IN

tinuous voltages.

70

60

50

(V)

40

IN

V

30

SAFE

20

10

Figure 1. V

OPERATING

AREA

0

20 40 60 80

MOSFET TOTAL GATE CHARGE (nC)

Regulator Continuous Operating Conditions

CC

100

3724 F01

For higher converter efficiency and less power dissipation

in the IC, V

can also be supplied from an external supply

CC

such as the converter output. When an external supply

back drives the internal V

diode and the V

voltage is pulled to a diode above its

CC

regulator through an external

CC

regulation voltage, the internal regulator is disabled and

goes into a low current mode. V

is the bias supply for

CC

most of the internal IC functions and is also used to charge

the bootstrapped capacitor (C

) via an external diode.

BOOST

The external MOSFET switch is biased from the

bootstrapped capacitor. While the external MOSFET switch

is off, an internal BJT switch, whose collector is connected

to the SW pin and emitter is connected to the PGND pin,

is turned on to pull the SW node to PGND and recharge the

bootstrap capacitor. The switch stays on until either the

3724fa

9

Page 10

LT3724

OPERATIO

U

(Refer to Functional Diagram)

start of the next cycle or until the bootstrapped capacitor

is fully charged.

MOSFET Driver

The LT3724 contains a high speed boosted driver to turn

on and off an external N-channel MOSFET switch. The

MOSFET driver derives its power from the boost capacitor

which is referenced to the SW pin and the source of the

MOSFET. The driver provides a large pulse of current to

turn on the MOSFET fast to minimize transition times.

Multiple MOSFETs can be paralleled for higher current

operation.

To eliminate the possibility of shoot through between the

MOSFET and the internal SW pull-down switch, an adaptive nonoverlap circuit ensures that the internal pull-down

switch does not turn on until the gate of the MOSFET is

below its turn on threshold.

Low Current Operation (Burst Mode Operation)

To increase low current load efficiency, the LT3724 is

capable of operating in Linear Technology’s proprietary

Burst Mode operation where the external MOSFET operates intermittently based on load current demand. The

Burst Mode function is disabled by connecting the

BURST_EN pin to V

and enabled by connecting the pin

CC

to SGND.

When the required switch current, sensed via the V

C

pin

voltage, is below 15% of maximum, Burst Mode operation

is employed and that level of sense current is latched onto

the IC control path. If the output load requires less than

this latched current level, the converter will overdrive the

output slightly during each switch cycle. This overdrive

condition is sensed internally and forces the voltage on the

pin to continue to drop. When the voltage on VC drops

V

C

150mV below the 15% load level, switching is disabled,

and the LT3724 shuts down most of its internal circuitry,

reducing total quiescent current to 100µA. When the

converter output begins to fall, the V

pin voltage begins

C

to climb. When the voltage on the VC pin climbs back to the

15% load level, the IC returns to normal operation and

switching resumes. An internal clamp on the VC pin is set

at 100mV below the output disable threshold, which limits

the negative excursion of the pin voltage, minimizing the

converter output ripple during Burst Mode operation.

During Burst Mode operation, the V

and the V

is provided for V

pin, giving a total VIN current of 100µA. Burst current

V

IN

can be reduced further when V

derived source, as the V

current is reduced to 80µA. If no external drive

CC

, all VCC bias currents originate from the

CC

CC

component of VIN current is

CC

pin current is 20µA

IN

is driven using an output

then reduced by the converter duty cycle ratio.

Start-Up

The following section describes the start-up of the supply

and operation down to 4V once the step-down supply is up

and running. For the protection of the LT3724 and the

switching supply, there are internal undervoltage lockout

(UVLO) circuits with hysteresis on VIN, VCC and V

BOOST

, as

shown in the Electrical Characteristics table. Start-up and

continuous operation require that all three of these

undervoltage lockout conditions be satisfied because the

TG MOSFET driver is disabled during any UVLO fault

condition. In startup, for most applications, V

ered from V

the LT3724. This requires V

the V

CC

, in turn, has to be high enough to charge the BOOST

V

CC

through the high voltage linear regulator of

IN

to be high enough to drive

IN

voltage above its undervoltage lockout threshold.

is pow-

CC

capacitor through an external diode so that the BOOST

voltage is above its undervoltage lockout threshold. There

is an NPN switch that pulls the SW node to ground each

cycle during the TG power MOSFET off-time, ensuring the

BOOST capacitor is kept fully charged. Once the supply is

up and running, the output voltage of the supply can

backdrive V

disables the high voltage regulator to conserve V

through an external diode. Internal circuitry

CC

supply

IN

current. Output voltages that are too low or too high to

backdrive V

doubler or linear regulator. Once V

supply other than V

require additional circuitry such as a voltage

CC

is backdriven from a

CC

, VIN can be reduced to 4V with

IN

normal operation maintained.

10

3724fa

Page 11

OPERATIO

LT3724

U

(Refer to Functional Diagram)

Soft-Start

The soft-start function controls the slew rate of the power

supply output voltage during start-up. A controlled output

voltage ramp minimizes output voltage overshoot, reduces inrush current from the V

supply sequencing. A capacitor, C

of the supply and the CSS pin of the IC, programs the

V

OUT

slew rate. The capacitor provides a current to the C

which is proportional to the dV/dt of the output voltage.

The soft-start circuit overrides the control loop and adjusts the inductor current until the output voltage slew rate

yields a 2µA current through the soft-start capacitor. If the

current is greater than 2µA, then the current threshold set

by the DC control voltage, V

inductor current is lowered. This in turn lowers the output

current and the output voltage slew rate is decreased. If the

current is less than 2µA, then the current threshold set by

the DC control voltage, V

current is raised. This in turn increases the output current

and the output voltage slew rate is increased. Once the

output voltage is within 5% of its regulation voltage, the

soft-start circuit is disabled and the main control regulates

the output. The soft-start circuit is reactivated when the

output voltage drops below 70% of its regulation voltage.

Slope/Antislope Compensation

The IC incorporates slope compensation to eliminate

potential subharmonic oscillations in the current control

loop. The IC’s slope compensation circuit imposes an

, is increased and the inductor

C

supply, and facilitates

IN

, connected between

SS

pin

SS

, is decreased and the

C

artificial ramp on the sensed current to increase the rising

slope as duty cycle increases.

Unfortunately, this additional ramp typically affects the

sensed current value, thereby reducing the achievable

current limit value by the same amount as the added ramp

represents. As such, the current limit is typically reduced

as the duty cycle increases. The LT3724, however, contains antislope compensation circuitry to eliminate the

current limit reduction associated with slope compensation. As the slope compensation ramp is added to the

sensed current, a similar ramp is added to the current limit

threshold. The end result is that the current limit is not

compromised so the LT3724 can provide full power regardless of required duty cycle.

Shutdown

The LT3724 includes a shutdown mode where all the

internal IC functions are disabled and the V

reduced to less than 10µA. The shutdown pin can be used

for undervoltage lockout with hysteresis, micropower

shutdown or as a general purpose on/off control of the

converter output. The shutdown function has two thresholds. The first threshold, a precision 1.23V threshold with

120mV of hysteresis, disables the converter from switching. The second threshold, approximately a 0.7V referenced to SGND, completely disables all internal circuitry

and reduces the V

Application Information section for more information.

current to less than 10µA. See the

IN

current is

IN

3724fa

11

Page 12

LT3724

(–)•

•

()

()

VVV

Vf

IN MAX OUT OUT

IN MAX SW

WUUU

APPLICATIO S I FOR ATIO

The basic LT3724 step-down (buck) application, shown in

the Typical Application on the front page, converts a larger

positive input voltage to a lower positive or negative

output voltage. This Application Information section assists selection of external components for the requirements of the power supply.

R

The current sense resistor, R

SENSE

Selection

, monitors the inductor

SENSE

current of the supply (See Typical Application on front

page). Its value is chosen based on the maximum required

output load current. The LT3724 current sense amplifier

has a maximum voltage threshold of, typically, 150mV.

Therefore, the peak inductor current is 150mV/R

The maximum output load current, I

OUT(MAX)

, is the peak

SENSE

.

inductor current minus half the peak-to-peak ripple current, ∆I

.

L

Allowing adequate margin for ripple current and external

component tolerances, R

can be calculated as

SENSE

follows:

mV

R

SENSE

Typical values for R

100

=

I

OUT MAX

()

SENSE

are in the range of 0.005Ω

to 0.05Ω.

Inductor Selection

compensation circuit is ineffective and current mode

instability may occur at duty cycles greater than 50%.

Lower values of ∆I

netics. A value of ∆I

of I

OUT(MAX)

ripple current around the DC output current of

require larger and more costly mag-

L

= 0.3 • I

L

OUT(MAX)

produces a ±15%

the supply.

Some magnetics vendors specify a volt-second product in

their datasheet. If they do not, consult the magnetics

vendor to make sure the specification is not being exceeded by your design. The volt-second product is calculated as follows:

Volt-second (µsec) =

The magnetics vendors specify either the saturation current, the RMS current or both. When selecting an inductor

based on inductor saturation current, use the peak current

through the inductor, I

OUT(MAX)

+ ∆IL/2. The inductor

saturation current specification is the current at which the

inductance, measured at zero current, decreases by a

specified amount, typically 30%.

When selecting an inductor based on RMS current rating,

use the average current through the inductor, I

OUT(MAX)

.

The RMS current specification is the RMS current at which

the part has a specific temperature rise, typically 40°C,

above 25°C ambient.

The critical parameters for selection of an inductor are

minimum inductance value, volt-second product, saturation current and/or RMS current.

The minimum inductance value is calculated as follows:

VV

LV

≥

OUT

IN MAX OUT

•

fV I

SW IN MAX L

fSW is the switch frequency (200kHz).

The typical range of values for ∆IL is (0.2 • I

(0.5 • I

OUT(MAX)

), where I

current of the supply. Using ∆I

good design compromise between inductor performance

versus inductor size and cost. Higher values of ∆IL will

increase the peak currents, requiring more filtering on the

input and output of the supply. If ∆IL is too high, the slope

12

–

()

••

()

∆

OUT(MAX)

= 0.3 • I

L

is the maximum load

OUT(MAX)

OUT(MAX)

) to

yields a

After calculating the minimum inductance value, the voltsecond product, the saturation current and the RMS

current for your design, select an off-the-shelf inductor. A

list of magnetics vendors can be found at www.linear.com,

or contact the Linear Technology Application Department.

For more detailed information on selecting an inductor,

please see the “Inductor Selection” section of Linear

Technology Application Note 44.

Step-Down Converter: MOSFET Selection

The selection criteria of the external N-channel standard

level power MOSFET include on resistance(R

verse transfer capacitance (C

voltage (V

), total gate charge (QG), and maximum

DSS

), maximum drain source

RSS

DS(ON)

), re-

continuous drain current.

3724fa

Page 13

WUUU

APPLICATIO S I FOR ATIO

LT3724

For maximum efficiency, minimize R

R

minimizes conduction losses while low C

DS(ON)

minimizes transition losses. The problem is that R

is inversely related to C

. Balancing the transition losses

RSS

DS(ON)

and C

RSS

. Low

RSS

DS(ON)

with the conduction losses is a good idea in sizing the

MOSFET. Select the MOSFET to balance the two losses.

Calculate the maximum conduction losses of the MOSFET:

PI

COND OUT MAX

Note that R

()()

=

DS(ON)

⎛

2

() ()

⎜

⎝

has a large positive temperature depen-

V

OUT

V

IN

⎞

⎟

⎠

R

DS ON

dence. The MOSFET manufacturer’s data sheet contains a

curve, R

vs Temperature.

DS(ON)

Calculate the maximum transition losses:

P

= (k)(VIN)2 (I

TRAN

OUT(MAX)

)(C

RSS

)(fSW)

where k is a constant inversely related to the gate driver

current, approximated by k = 2 for LT3724 applications.

The total maximum power dissipation of the MOSFET is

the sum of these two loss terms:

P

FET(TOTAL)

= P

To achieve high supply efficiency, keep the P

COND

+ P

TRAN

FET(TOTAL)

to

less than 3% of the total output power. Also, complete a

thermal analysis to ensure that the MOSFET junction

temperature is not exceeded.

TJ = TA + P

FET(TOTAL)

• θ

JA

where θJA is the package thermal resistance and TA is the

ambient temperature. Keep the calculated T

below the

J

maximum specified junction temperature, typically 150°C.

Note that when V

dominate. A MOSFET with higher R

is high, the transition losses may

IN

and lower C

DS(ON)

RSS

may provide higher efficiency. MOSFETs with higher voltage V

lower C

specification usually have higher R

DSS

.

RSS

DS(ON)

and

The internal V

maximum total MOSFET gate charge, Q

regulator operating range limits the

CC

, to 90nC. The Q

G

G

vs VGS specification is typically provided in the MOSFET

data sheet. Use Q

at VGS of 8V. If VCC is back driven from

G

an external supply, the MOSFET drive current is not

sourced from the internal regulator of the LT3724 and the

QG of the MOSFET is not limited by the IC. However, note

that the MOSFET drive current is supplied by the internal

regulator when the external supply back driving V

CC

is not

available such as during startup or short-circuit.

The manufacturer’s maximum continuous drain current

specification should exceed the peak switch current,

I

OUT(MAX)

+ ∆IL/2.

During the supply startup, the gate drive levels are set by

the V

Once the supply is up and running, the V

driven by an auxiliary supply such as V

not to exceed the manufacturer’s maximum V

voltage regulator, which is approximately 8V.

CC

can be back

CC

. It is important

OUT

specifica-

GS

tion. A standard level threshold MOSFET typically has a

maximum of 20V.

V

GS

Step-Down Converter: Rectifier Selection

The rectifier diode (D1 on the Functional Diagram) in a

buck converter generates a current path for the inductor

current when the main power switch is turned off. The

rectifier is selected based upon the forward voltage, reverse voltage and maximum current. A Schottky diode is

recommended. Its low forward voltage yields the lowest

power loss and highest efficiency. The maximum reverse

voltage that the diode will see is V

IN(MAX)

.

In continuous mode operation, the average diode current

is calculated at maximum output load current and maximum VIN:

VV

II

DIODE AVG OUT MAX

=

() ( )

IN MAX OUT

−

()

V

()

IN MAX

Choose the MOSFET V

specification to exceed the

DSS

maximum voltage across the drain to the source of the

MOSFET, which is V

IN(MAX)

plus any additional ringing on

the switch node. Ringing on the switch node can be greatly

reduced with good PCB layout and, if necessary, an RC

snubber.

To improve efficiency and to provide adequate margin

for short-circuit operation, a diode rated at 1.5 to 2 times

the maximum average diode current, I

DIODE(AVG)

, is

recommended.

3724fa

13

Page 14

LT3724

WUUU

APPLICATIO S I FOR ATIO

Step-Down Converter: Input Capacitor Selection

A local input bypass capacitor is required for buck converters because the input current is pulsed with fast rise

and fall times. The input capacitor selection criteria are

based on the bulk capacitance and RMS current capability.

The bulk capacitance will determine the supply input ripple

voltage. The RMS current capability is used to keep from

overheating the capacitor.

The bulk capacitance is calculated based on maximum

input ripple, ∆VIN:

C

()

IN BULK

IV

OUT MAX OUT

=

Vf V

∆

IN SW IN MIN

•

()

••

()

∆VIN is typically chosen at a level acceptable to the user.

100mV-200mV is a good starting point. Aluminum electrolytic capacitors are a good choice for high voltage, bulk

capacitance due to their high capacitance per unit area.

The capacitor’s RMS current is:

(– )

VVV

II

CIN RMS OUT

=

()

OUT IN OUT

2

()

V

IN

Step-Down Converter: Output Capacitor Selection

The output capacitance, C

design’s output voltage ripple, ∆V

requirements. ∆V

is a function of ∆IL and the C

OUT

, selection is based on the

OUT

, and transient load

OUT

OUT

ESR. It is calculated by:

∆ = ∆ +

V I ESR

OUT L

⎛

•

⎜

⎝

(• • )

8

fC

SW OUT

1

The maximum ESR required to meet a ∆V

⎞

⎟

⎠

design

OUT

requirement can be calculated by:

VLf

()()()

∆

ESR MAX

()

Worst-case ∆V

=

OUT

OUT SW

V

OUT

⎛

1

•–

⎜

V

⎝

V

IN MAX

⎞

OUT

⎟

⎠

()

occurs at highest input voltage. Use

paralleled multiple capacitors to meet the ESR requirements. Increasing the inductance is an option to lower the

ESR requirements. For extremely low ∆V

, an additional

OUT

LC filter stage can be added to the output of the supply.

Application Note 44 has some good tips on sizing an

additional output filter.

If applicable, calculate it at the worst case condition, VIN =

. The RMS current rating of the capacitor is specified

2V

OUT

by the manufacturer and should exceed the calculated

I

CIN(RMS)

. Due to their low ESR (Equivalent Series Resistance), ceramic capacitors are a good choice for high

voltage, high RMS current handling. Note that the ripple

current ratings from aluminum electrolytic capacitor manufacturers are based on 2000 hours of life. This makes it

advisable to further derate the capacitor or to choose a

capacitor rated at a higher temperature than required.

The combination of aluminum electrolytic capacitors and

ceramic capacitors is an economical approach to meeting

the input capacitor requirements. The capacitor voltage

rating must be rated greater than V

IN(MAX)

. Multiple capacitors may also be paralleled to meet size or height

requirements in the design. Locate the capacitor very

close to the MOSFET switch and use short, wide PCB

traces to minimize parasitic inductance.

Output Voltage Programming

A resistive divider sets the DC output voltage according to

the following formula:

V

RR

⎛

21

⎜

⎝

OUT

1 231

.

⎞

1=

–

⎟

⎠

V

The external resistor divider is connected to the output of

the converter as shown in Figure 2. Tolerance of the

feedback resistors will add additional error to the output

voltage.

Example: V

Rk

= 12V; R1 = 10kΩ

OUT

V

12

⎛

⎜

⎝

1 231

.

V

⎞

1 8748 866 1= Ω−

⎟

⎠

= Ω− Ω

k use k210

..%

3724fa

14

Page 15

WUUU

APPLICATIO S I FOR ATIO

LT3724

L1

R2

VFB PIN

R1

Figure 2. Output Voltage Feedback Divider

C

OUT

3724 F02

V

OUT

The VFB pin input bias current is typically 25nA, so use of

extremely high value feedback resistors could cause a

converter output that is slightly higher than expected. Bias

current error at the output can be estimated as:

∆V

OUT(BIAS)

= 25nA • R2

Supply UVLO and Shutdown

The SHDN pin has a precision voltage threshold with

hysteresis which can be used as an undervoltage lockout

threshold (UVLO) for the power supply. Undervoltage

lockout keeps the LT3724 in shutdown until the supply

input voltage is above a certain voltage programmed by

the user. The hysteresis voltage prevents noise from

falsely tripping UVLO.

Resistors are chosen by first selecting RB. Then

RA RB

=

V

SUPPLY(ON)

⎛

SUPPLY ON

•

⎜

⎝

.

135

()

V

is the input voltage at which the undervoltage

⎞

–

1

⎟

⎠

V

lockout is disabled and the supply turns on.

Example: Select RB = 49.9kΩ, V

SUPPLY(ON)

= 14.5V

(based on a 15V minimum input voltage)

RA k

= Ω

49 9

⎛

⎜

⎝

135

.

⎞

1.•

–

⎟

⎠

V

V

14 5

.

= 486.1kΩ (499kΩ resistor is selected)

V

SUPPLY

RA

SHDN PIN

RB

3724 F03

Figure 3. Undervoltage Lockout Circuit

If additional hysteresis is desired for the enable function,

an external positive feedback resistor can be used from the

LT3724 regulator output.

The shutdown function can be disabled by connecting the

SHDN pin to the VIN through a large value pull-up resistor.

This pin contains a low impedance clamp at 6V, so the

SHDN pin will sink current from the pull-up resistor(R

VV

–6

I

SHDN

IN

=

R

PU

PU

):

Because this arrangement will clamp the SHDN pin to the

6V, it will violate the 5V absolute maximum voltage rating

of the pin. This is permitted, however, as long as the

absolute maximum input current rating of 1mA is not

exceeded. Input SHDN pin currents of <100µA are recom-

mended: a 1MΩ or greater pull-up resistor is typically

used for this configuration.

Soft-Start

The soft-start function forces the programmed slew rate

while the converter output rises to 95% of regulation,

which corresponds to 1.185V on the V

pin. Once 95%

FB

regulation is achieved, the soft-start circuit is disabled.

The soft-start circuit will re-enable when the VFB pin drops

below 70% of regulation, which corresponds to 300mV of

control hysteresis on the V

pin. This allows for a con-

FB

trolled recovery from a “brown-out” condition.

If low supply current in standby mode is required, select

a higher value of RB.

The supply turn off voltage is 9% below turn on. In the

example the V

SUPPLY(OFF)

would be 13.2V.

C

SS1

R

SS

V

OUT

Figure 4.Soft-Start Circuit

A

LT3724

C

SS

3724 F04

3724fa

15

Page 16

LT3724

WUUU

APPLICATIO S I FOR ATIO

The desired soft-start rise time (tSS) is programmed via a

programming capacitor C

, using a value that corre-

SS1

sponds to 2µA average current during the soft-start inter-

val. This capacitor value follows the relation:

6

–

210

••

=

C

1

SS

V

OUT

t

SS

RSS is typically set to 200k for most applications.

Considerations for Low-Voltage Output Applications

The LT3724 C

pin biases to 220mV during the soft-start

SS

cycle, and this voltage is increased at Figure 4 node “A” by

the 2µA signal current through RSS, so the output has to

reach this value before the soft-start function is engaged.

The value of this output soft-start startup voltage offset

V

OUT(SS)

) follows the relation:

= 220mV + R

• 2 • 10

SS

–6

(V

OUT(SS)

Which is typically 0.64V for RSS = 200k.

In some low voltage output applications, it may be desirable to reduce the value of this soft-start startup voltage

offset. This is possible by reducing the value of RSS. With

reduced values of R

, the signal component caused by

SS

voltage ripple on the output must be minimized for proper

soft-start operation.

Peak-to-peak output voltage ripple (∆V

posed on node “A” through the capacitor C

can be set using the following equation:

of R

SS

V

∆

R

=

SS

OUT

13 10

.•

6

–

) will be im-

OUT

. The value

SS1

It is important to use low ESR output capacitors for

LT3724 voltage converter designs to minimize this ripple

voltage component. A design with an excessive ripple

component can be evidenced by observing the VC pin

during the start cycle.

The soft-start cycle should be evaluated to verify that the

reduced R

value allows operation without excessive

SS

modulation of the VC pin before finalizing the design.

If VC pin has an excessive ripple component during

the soft-start cycle, converter output ripple should be

V

OUT

V

OUT(SS)

)

V(V

C

TIME, 250µs/DIV

3724F05

Figure 5. Soft-Start Characteristic

Showing Excessive Ripple Component

V

OUT

V

OUT(SS)

V(VC)

TIME, 250ms/DIV

3724F06

Figure 6. Desirable Soft-Start Characteristic

reduced. This is typically accomplished by increasing

output capacitance and/or reducing output capacitor ESR.

External Current Limit Foldback Circuit

An additional startup voltage offset can occur during the

period before the LT3724 soft-start circuit becomes active. Before the soft-start circuit throttles back the V

pin

C

in response to the rising output voltage, current as high as

the peak programmed current limit (I

) can flow in the

MAX

switched inductor. Switching will stop once the soft-start

circuit takes hold and reduces the voltage on the V

pin,

C

but the output voltage will continue to increase as the

stored energy in the inductor is transferred to the output

capacitor. With I

edge rise on V

in the inductor, the resulting leading-

MAX

due to energy stored in the inductor

OUT

follows the relation:

L

OUT

/12

⎞

⎟

⎠

3724fa

∆VI

=

OUT MAX

•

⎛

⎜

⎝

C

16

Page 17

WUUU

APPLICATIO S I FOR ATIO

LT3724

Inductor current typically doesn’t reach I

in the few

MAX

cycles that occur before soft-start becomes active, but can

with high input voltages or small inductors, so the above

relation is useful as a worst-case scenario.

This energy transfer increase in output voltage is typically

small, but for some low voltage applications with relatively

small output capacitors, it can become significant. The

voltage rise can be reduced by increasing output capacitance, which puts additional limitations on C

for these

OUT

low voltage supplies. Another approach is to add an

external current limit foldback circuit which reduces the

value of I

during start-up.

MAX

An external current limit foldback circuit can be easily

incorporated into an LT3724 DC/DC converter application

by placing a 1N4148 diode and a 47kΩ resistor from the

converter output (V

the peak current to 0.25 • I

) to the LT3724’s VC pin. This limits

OUT

MAX

when V

= 0V. A current

OUT

limit foldback circuit also has the added advantage of

providing reduced output current in the DC/DC converter

during short-circuit fault conditions, so a foldback circuit

may be useful even if the soft-start function is disabled.

If the soft-start circuit is disabled by shorting the C

SS

pin

to ground, the external current limit foldback circuit must

be modified by adding an additional diode and resistor.

The 2-diode, 2-resistor network shown also provides 0.25

• I

MAX

when V

= 0V.

OUT

V

C

1N4148

47k

V

OUT

Figure 7. Current Limit Foldback Circuit

for Applications that use Soft-Start

3724 F03

V

C

1N4148

1N4148

39k

27k

V

OUT

3724 F07

Figure 8. Current Limit Foldback Circuit for Applications

that have Soft-Start Disabled (C

Pin Shorted to SGND)

SS

Efficiency Considerations

The efficiency of a switching regulator is equal to the

output power divided by the input power times 100%.

Express percent efficiency as:

% Efficiency = 100% - (L1 + L2 + L3 + ...)

where L1, L2, etc. are individual loss terms as a percentage

of input power.

Although all dissipative elements in the circuit produce

losses, four main contributors usually account for most of

the losses in LT3724 circuits:

1. LT3724 V

2

2. I

R conduction losses

and VCC current loss

IN

3. MOSFET transition loss

4. Schottky diode conduction loss

1. The V

and VCC currents are the sum of the quiescent

IN

currents of the LT3724 and the MOSFET drive currents.

The quiescent currents are in the LT3724 Electrical Characteristics table. The MOSFET drive current is a result of

charging the gate capacitance of the power MOSFET each

cycle with a packet of charge, Q

. QG is found in the

G

MOSFET data sheet. The average charging current is

calculated as Q

currents can be reduced by backdriving V

voltage than V

• fSW. The power loss term due to these

G

with a lower

CC

such as V

IN

OUT

.

3724fa

17

Page 18

LT3724

WUUU

APPLICATIO S I FOR ATIO

2. I2R losses are calculated from the DC resistances of the

MOSFET, the inductor, the sense resistor, and the input

and output capacitors. In continuous conduction mode

the average output current flows through the inductor and

R

Schottky diode. The resistances of the MOSFET (R

and the R

with the resistances of the inductor and R

but is chopped between the MOSFET and the

SENSE

multiplied by the duty cycle can be summed

SENSE

SENSE

DS(ON)

to obtain

)

the total series resistance of the circuit. The total conduction power loss is proportional to this resistance and

usually accounts for between 2% to 5% loss in efficiency.

3. Transition losses of the MOSFET can be substantial with

input voltages greater than 20V. See MOSFET Selection

section.

4. The Schottky diode can be a major contributor of power

loss especially at high input to output voltage ratios (low

duty cycles) where the diode conducts for the majority of

the switch period. Lower V

reduces the losses. Note that

f

oversizing the diode does not always help because as the

diode heats up the V

is reduced and the diode loss term

f

is decreased.

2

I

R losses and the Schottky diode loss dominate at high

load currents. Other losses including C

IN

and C

OUT

ESR

dissipative losses and inductor core losses generally

account for less than 2% total additional loss in efficiency.

input capacitor, and the ground return of the V

capaci-

CC

tor. This ground has very fast high currents and is considered the noisy ground. The two grounds are connected to

each other only at the (–) terminal of V

OUT

.

2. Use short wide traces in the loop formed by the

MOSFET, the Schottky diode and the input capacitor to

minimize high frequency noise and voltage stress from

parasitic inductance. Surface mount components are preferred.

3. Connect the VFB pin directly to the feedback resistors

–

independent of any other nodes, such as the SENSE

pin.

Connect the feedback resistors between the (+) and (–)

terminals of C

. Locate the feedback resistors in close

OUT

proximity to the LT3724 to keep the high impedance node,

, as short as possible.

V

FB

4. Route the SENSE

–

and SENSE+ traces together and keep

as short as possible.

5. Locate the V

and BOOST capacitors in close proximity

CC

to the IC. These capacitors carry the MOSFET driver’s high

peak currents. Place the small signal components away

from high frequency switching nodes (BOOST, SW, and

TG). In the layout shown in Figure 9, place all the small

signal components on one side of the IC and all the power

components on the other. This helps to keep the signal and

power grounds separate.

PCB Layout Checklist

When laying out the printed circuit board, the following

checklist should be used to ensure proper operation.

These items are illustrated graphically in the layout diagram of Figure 9.

1. Keep the signal and power grounds separate. The signal

ground consists of the LT3724 SGND pin, the exposed pad

on the backside of the LT3724 IC and the (–) terminal of

V

. The signal ground is the quiet ground and does not

OUT

contain any high, fast currents. The power ground consists of the Schottky diode anode, the (–) terminal of the

18

6. A small decoupling capacitor (100pF) is sometimes

useful for filtering high frequency noise on the feedback

and sense nodes. If used, locate as close to the IC as

possible.

7. The LT3724 packaging will efficiently remove heat from

the IC through the exposed pad on the backside of the part.

The exposed pad is soldered to a copper footprint on the

PCB. Make this footprint as large as possible to improve

the thermal resistance of the IC case to ambient air. This

helps to keep the LT3724 at a lower temperature.

8. Make the trace connecting the gate of MOSFET M1 to the

TG pin of the LT3724 short and wide.

3724fa

Page 19

WUUU

APPLICATIO S I FOR ATIO

LT3724

+

V

IN

R

A

1

V

IN

R

B

R

C

SS

R2

CSS

R

C

C

C1

R1

C

C2

3

SHDN

4

C

SS

5

BURST_EN

6

V

FB

7

V

C

8

SGND

LT3724

17

BOOST

PGND

SENSE

SENSE

V

TG

SW

16

15

14

12

CC

+

–

C

VCC

11

10

9

Figure 9. LT3724 Layout Diagram (See PCB Layout Checklist).

Minimum On-Time Considerations

(Step-Down Converters)

Minimum on-time (t

) is the least amount of time that

TG(ON)

the LT3724 is capable of turning the MOSFET on and then

off again. It is determined by internal timing delays and the

gate charge of the MOSFET. Applications with high input

to output differential voltages operate at low duty cycles

and may approach this minimum on-time, typically 300nS.

The LT3724 switching frequency is internally set to 200kHz,

C

BOOST

D2

D3

M1

C

IN

–

V

IN

L1

R

SENSE

C

OUT

D1

+

V

OUT

–

3724 F06

therefore, the minimum duty cycle of the MOSFET switch

is 6%. When the duty cycle needs to be less than 6% the

output will stay regulated, but cycle skipping may occur.

Cycle skipping results in an increase in inductor ripple

current. If it is important that cycle skipping does not

occur, follow this guideline which takes into account

worst case fSW and t

V

IN(MAX)

≤ 9 • V

OUT

This is only an issue for supplies with V

TG(ON)

:

< 7V.

OUT

3724fa

19

Page 20

LT3724

TYPICAL APPLICATIO S

U

12V to 24V/50W Boost (Step-Up) Converter

V

8V TO16V

IN

R2

187k

R1

10k

C

IN

33µF ×2

25V

1500pF

D1

BAV99

1

V

IN

0.1µF

25V

C1

C2

120pF

R

CSS

200k

R6

40.2k

C3

4700pF

R3

4.7M

3

SHDN

4

C

SS

5

BURST_EN

6

V

FB

7

V

C

8

SGND

LT3724

BOOST

PGND

SENSE

SENSE

SW

V

16

15

TG

14

12

CC

11

10

+

9

–

C4

1µF

25V

R

SENSE

0.015Ω

L1

10µH

D2

SBM540

M1

3724 TA02

C

OUT1

330µF

35V

= SANYO, 25SVP33M

C

IN

L1 = VISHAY, IHLP-5050FD-011

M1 = SILICONIX, Si7370DP

= SANYO, 35CV330AXA

C

OUT1

= TDK, C4532X7R1H225K

C

OUT2

D2 = DIODESINC., SBM540

R

SENSE

V

OUT

24V AT 50W

C

OUT2

2.2µF x3

50V

= IRC LRF2512-01-R0I5-F

Efficiency and Power Loss vs Load Current

100

LOSS

= 12V

V

98

96

94

IN

VIN = 16V

VIN = 12V

3.0

2.5

POWER LOSS (W)

2.0

1.5

20

EFFICIENCY (%)

92

90

88

0.1

VIN = 8V

110

LOAD CURRENT (A)

1.0

0.5

0

3724 F08

3724fa

Page 21

TYPICAL APPLICATIO S

LT3724

U

High Voltage LED Driver with Dimmer Control

V

IN

8V TO 60V

R1

100pF

C1

M2

2N7002

4.7M

OPTIONAL

DIMMER

CONTROL

1kHz

C1 = OPTIONAL TO REDUCE LED RIPPLE CURRENT

= TDK, C4532X7R2A225K

C

IN

D1 = DIODESINC., B170

M1 = ZETEX, ZXMN10A07F

= VISHAY, WSL2010R0150FEA

R

SENSE

L1 = COILTRONICS, CTX300-4

1

V

3

SHDN

4

C

5

BURST_EN

6

V

7

V

8

SGND

LED

C1

(OPTIONAL)

16

BOOST

IN

LT3724

SS

FB

C

PGND

SENSE

SENSE

15

TG

14

SW

12

V

CC

11

10

+

9

–

C

1µF

16V

300µH

VCC

3724 TA03

D1

B170

L1

4.5V to 20V Input to 12V at 25W Output SEPIC Converter with 60V Input Transient Capability

V

IN

4.5V TO 20V

TO 60V

TRANSIENT

R2

130k

R1

14.7k

390pF

R4

47k

D3

D1N4148

C

IN1

22µF

2x

25V

C1

49.9k

C2

120pF

C

IN2

25V

RA

1µF

RB

100k

R5

40.2k

C3

680pF

R3

200k

1

V

3

SHDN

4

C

5

BURST_EN

6

V

7

V

8

SGND

IN

LT3724

SS

FB

C

BOOST

PGND

SENSE

SENSE

16

15

TG

14

SW

12

V

CC

11

10

+

9

–

D1B

GSD2004

C7

0.1µF

C4

1µF

25V

D1A

GSD2004

C5, C

C

OUT1

D2 = ON SEMI, MBRD660

L1 = COILCRAFT VERSAPAC VP5-D83

M1 = VISHAY, Si7852DP

•

L1

20µH

C5

22µF

M1

10Ω

C6

56pF

10Ω

, C

IN1

= SANYO, OS-CON 16SVP330M

3x

25V

R6

20µH

R

SENSE

R7

0.010Ω

= TDKC453X7R1E226M

OUT2

D2

L1

•

12V AT 25W

C

OUT1

330µF

16V

C

OUT2

22µF

25V

3724 TA07a

V

OUT

M1

ZXMN10A07F

:

ADJUST I

LED

0.15V

=

I

LED

R

SENSE

R

SENSE

0.5Ω

Efficiency and Power Loss

vs Load Current

92

91

90

89

88

EFFICIENCY (%)

87

86

85

0.1

LOAD CURRENT (A)

3724 TA07b

3.5

3.0

2.5

POWER LOSS (W)

2.0

1.5

1.0

0.5

0

VIN = 20V

VIN = 15V

VIN = 10V

LOSS

= 15V

V

IN

110

3724fa

21

Page 22

LT3724

TYPICAL APPLICATIO S

V

IN

15V TO 60V

C

100µF

100V

R4

130k

R5

14.7k

+

IN

C1

3300pF

C2

120pF

2.2µF x2

100V

R3

49.9k

R

200k

CSS

U

from V

R2

499k

R6

15k

C3

680pF

12V Step-Down with VCC Back Driven

and Ceramic Capacitor in Output Filter

OUT

1

V

3

SHDN

4

C

5

BURST_EN

6

V

7

V

8

SGND

IN

LT3724

SS

FB

C

BOOST

PGND

SENSE

SENSE

V

SW

16

R7

15

TG

14

12

CC

11

10

+

9

–

20Ω

D2A

BAV99

C4

1µF

D2B

16V

BAV99

C

IN

C

OUT

D1: DIODESINC., PDS5100H

L1: COEV DU1971-470M

M1: VISHAY Si7852DP

C6

0.1µF

16V

M1

Si7852DP

L1

47µH

D1

: TDK, C4532X7R2A225MT

: TDK, C4532X7R1C336MT

R

SENSE

0.020Ω

3724 TA04

V

OUT

12V AT 50W

C

OUT

33µF x3

16V

22

3724fa

Page 23

PACKAGE DESCRIPTIO

3.58

(.141)

U

FE Package

16-Lead Plastic TSSOP (4.4mm)

(Reference LTC DWG # 05-08-1663)

Exposed Pad Variation BC

4.90 – 5.10*

(.193 – .201)

3.58

(.141)

16 1514 13 12 11

LT3724

10 9

6.60 ±0.10

4.50 ±0.10

RECOMMENDED SOLDER PAD LAYOUT

0.09 – 0.20

(.0035 – .0079)

NOTE:

1. CONTROLLING DIMENSION: MILLIMETERS

2. DIMENSIONS ARE IN

3. DRAWING NOT TO SCALE

SEE NOTE 4

0.65 BSC

4.30 – 4.50*

(.169 – .177)

0.50 – 0.75

(.020 – .030)

MILLIMETERS

(INCHES)

(.116)

0.45 ±0.05

2.94

1.05 ±0.10

1345678

2

0.25

REF

0° – 8°

0.65

(.0256)

BSC

0.195 – 0.30

(.0077 – .0118)

TYP

4. RECOMMENDED MINIMUM PCB METAL SIZE

FOR EXPOSED PAD ATTACHMENT

*DIMENSIONS DO NOT INCLUDE MOLD FLASH. MOLD FLASH

SHALL NOT EXCEED 0.150mm (.006") PER SIDE

2.94

(.116)

1.10

(.0433)

MAX

0.05 – 0.15

(.002 – .006)

FE16 (BC) TSSOP 0204

6.40

(.252)

BSC

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

3724fa

23

Page 24

LT3724

TYPICAL APPLICATIO S

U

V

IN

18V TO 36V

C

SS

1000pF

R1

88.7k

R2

C

10.2k

D1 = BAV99

D2 = ON SEMI, MBRD350

L1 = COEV, DU1311-470M

M1 = VISHAY, Si7370DP

= SANYO, 50CV220KX

C

IN1

C

OUT1

C2

680pF

= SANYO, 16SVP330M

R3

2M

0.1µF

R

CSS

200k

R6, 40.2k

C

120pF

1

V

IN

LT3724

3

SHDN

4

C

SS

6

V

FB

7

V

C1

C

8

GND

BOOST

PGND

SENSE

SENSE

V

TG

SW

16

15

14

D1A

12

CC

11

10

+

9

–

1µF

16V

0.1µF

16V

D1B

M1

L1

47µH

D2

R

SENSE

0.040Ω

3724 TA05

+

C

IN1

220µF

50V

V

OUT

–12V

1.5A

C

OUT1

330µF

+

16V

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

Inverting –12V 1.5A Converter

LT1339 High Power Synchronous DC/DC Controller VIN up to 60V, Drivers 10000pF Gate Capacitance, I

LTC1624 Switching Controller Buck, Boost, SEPIC, 3.5V ≤ V

LTC1702A Dual 2-Phase Synchronous DC/DC Controller 550kHz Operation, No R

LTC1735 Synchronous Step-Down DC/DC Controller 3.5V = <V

LTC1778 No R

Synchronous DC/DC Controller 4V = <VIN= <36V, Fast Transient Response, Current Mode, I

SENSE

LT3010 50mA, 3V to 80V Linear Regulator 1.275V = <V

= <36V, 0.8V = <V

IN

= <60V, No Protection Diode Required,

OUT

≤ 36V; 8-Lead SO Package

IN

, 3V = <VIN = <7V, I

SENSE

= <6V, Current Mode, I

OUT

8-Lead MSOP Package

LT3430/LT3431 Monolithic 3A, 200kHz/500kHz Step-Down Regulator 5.5V = <VIN = <60V, 0.1Ω Saturation Switch, 16-Lead SSOP Package

LTC3703/LTC3703-5 100V Synchronous Switching Regulator Controllers No R

LT3800 High Voltage Synchronous Regulator Controller VIN up to 60V, I

, Voltage Mode Control, GN16 Package

SENSE

= <20A, Current Mode,

OUT

16-Lead TSSOP FE Package

OUT

OUT

= <20A

= <20A

OUT

= <20A

OUT

= <20A

24

Linear Technology Corporation

1630 McCarthy Blvd., Milpitas, CA 95035-7417