Page 1

FEATURES

LT1678/LT1679

Dual/Quad Low Noise,

Rail-to-Rail, Precision Op Amps

U

DESCRIPTIO

■

Rail-to-Rail Input and Output

■

100% Tested Low Voltage Noise:

3.9nV/√Hz Typ at 1kHz

5.5nV/√Hz Max at 1kHz

■

Single Supply Operation from 2.7V to 36V

■

Offset Voltage: 100µV Max

■

Low Input Bias Current: 20nA Max

■

High A

■

High CMRR: 100dB Min

■

High PSRR: 106dB Min

■

Gain Bandwidth Product: 20MHz

■

Operating Temperature Range: –40°C to 85°C

■

Matching Specifications

■

No Phase Inversion

■

8-Lead SO and 14-Lead SO Packages

: 3V/µV Min, RL = 10k

VOL

U

APPLICATIO S

■

Strain Gauge Amplifiers

■

Portable Microphones

■

Battery-Powered Rail-to-Rail Instrumentation

■

Low Noise Signal Processing

■

Microvolt Accuracy Threshold Detection

■

Infrared Detectors

®

The LT

1678/LT1679 are dual/quad rail-to-rail op amps

offering both low noise and precision: 3.9nV/√Hz wideband

noise, 1/f corner frequency of 4Hz and 90nV peak-to-peak

0.1Hz to 10Hz noise are combined with outstanding

precision: 100µV maximum offset voltage, greater than

100dB common mode and power supply rejection and

20MHz gain bandwidth product. The LT1678/LT1679 bring

precision as well as low noise to single supply applications as

low as 3V. The input range exceeds the power supply by

100mV with no phase inversion while the output can swing

to within 170mV of either rail.

The LT1678/LT1679 are offered in the SO-8 and SO-14

packages. A full set of matching specifications are also

provided, facilitating their use in matching dependent applications such as a two op amp instrumentation amplifier

design. The LT1678/LT1679 are specified for supply voltages of ±15V, single 5V as well as single 3V. For a single

amplifier with similiar performance, see the LT1677 data

sheet.

, LTC and LT are registered trademarks of Linear Technology Corporation.

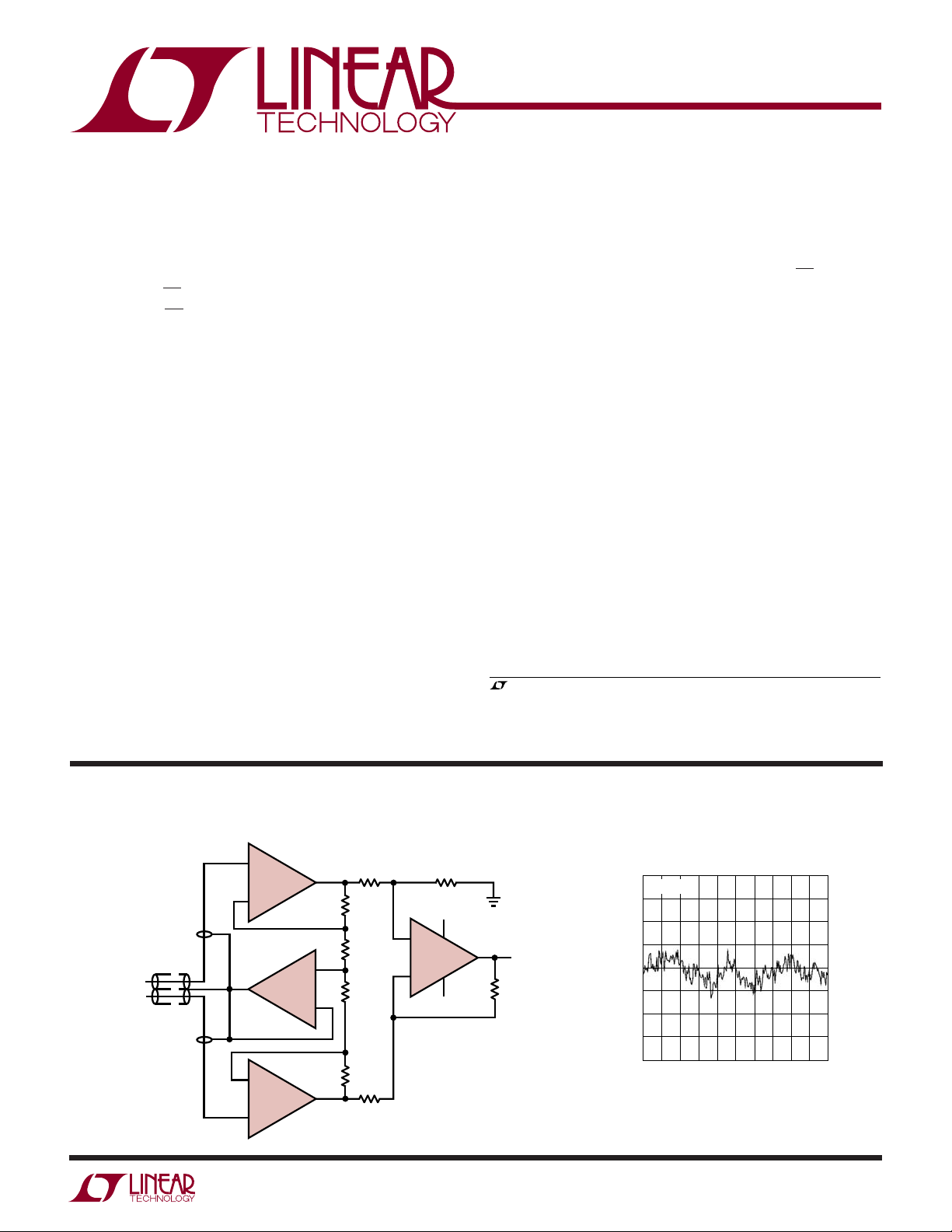

TYPICAL APPLICATIO

Instrumentation Amplifier with Shield Driver

3

+

1/4

LT1679

2

–

GUARD

INPUT

+

–

GUARD

8

1/4

LT1679

13

–

1/4

LT1679

12

+

U

0.1Hz to 10Hz Voltage Noise

VS = ±2.5V

VOLTAGE NOISE (50nV/DIV)

4681002

TIME (sec)

16789 TA01b

sn16789 16789fs

5

+

6

–

16789 TA01

30k1k

15V

4

1/4

LT1679

11

–15V

GAIN = 1000

7

OUTPUT

30k

1

R

F

3.4k

R

G

100Ω

10

+

R

G

100Ω

9

–

R

F

3.4k

14

1k

1

Page 2

LT1678/LT1679

TOP VIEW

S PACKAGE

14-LEAD PLASTIC SO

1

2

3

4

5

6

7

14

13

12

11

10

9

8

OUT A

–IN A

+IN A

V

+

+IN B

–IN B

OUT B

OUT D

–IN D

+IN D

V

–

+IN C

–IN C

OUT C

AD

CB

WWWU

ABSOLUTE AXI U RATI GS

(Note 1)

Supply Voltage ...................................................... ±18V

Input Voltages (Note 2) ............ 0.3V Beyond Either Rail

Differential Input Current (Note 2) ..................... ± 25mA

Output Short-Circuit Duration (Note 3) ............ Indefinite

Storage Temperature Range ................. – 65°C to 150°C

Lead Temperature (Soldering, 10 sec.)................. 300°C

Operating Temperature Range

(Note 4)............................................. – 40°C to 85°C

Specified Temperature Range

(Note 5)............................................. – 40°C to 85°C

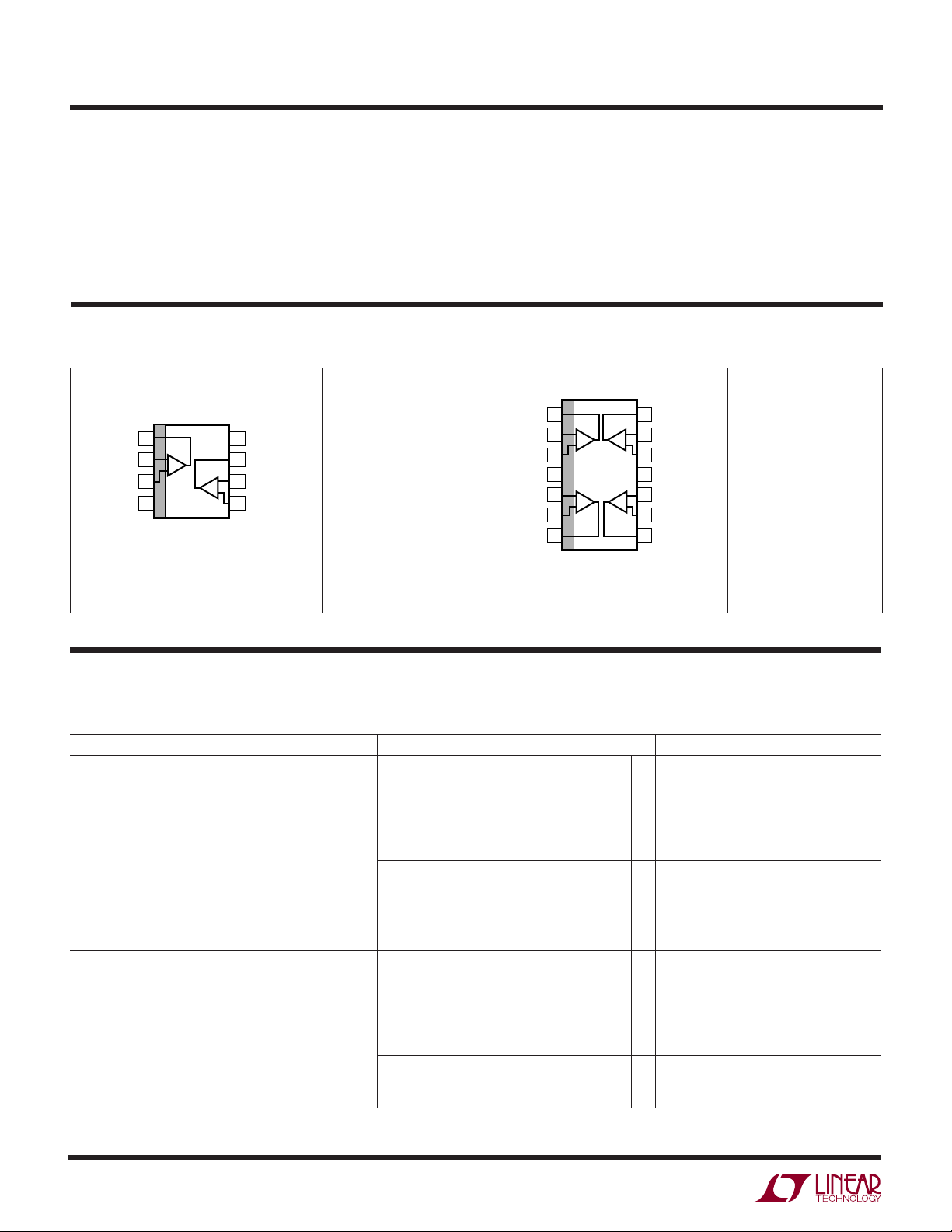

UU

W

PACKAGE/ORDER I FOR ATIO

ORDER PART

TOP VIEW

1

OUT A

2

–IN A

3

+IN A

–

4

V

8-LEAD PLASTIC SO

T

= 150°C, θJA = 190°C/ W

JMAX

A

B

S8 PACKAGE

+

8

V

7

OUT B

6

–IN B

+IN B

5

Consult LTC Marketing for parts specified with wider operating temperature ranges.

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at TA = 25°C. VS = 3V, VCM = VO = 1.7V; VS = 5V, VCM = VO = 2.5V unless

otherwise noted.

SYMBOL PARAMETER CONDITIONS (Note 6) MIN TYP MAX UNITS

V

OS

∆V

OS

∆Temp

I

B

2

Input Offset Voltage (Note 11) 35 100 µV

Average Input Offset Drift (Note 10) ● 0.40 3 µV/°C

Input Bias Current (Note 11) ±2 ±20 nA

NUMBER

LT1678CS8

LT1678IS8

S8 PART MARKING

1678

1678I

The ● denotes the specifications which apply over the full operating

≤ 70°C ● 55 270 µV

0°C ≤ T

A

–40°C ≤ T

VS =5V, VCM = VS + 0.1V 150 550 µV

=5V, VCM = VS – 0.3V, 0°C ≤ TA ≤ 70°C ● 180 750 µV

V

S

=5V, VCM = VS – 0.3V, –40°C ≤ TA ≤ 85°C ● 200 1000 µV

V

S

VS =5V, VCM = –0.1V 1.5 30 mV

=5V, VCM = 0V, 0°C ≤ TA ≤ 70°C ● 1.8 45 mV

V

S

=5V, VCM = 0V, –40°C ≤ TA ≤ 85°C ● 2.0 50 mV

V

S

0°C ≤ T

–40°C ≤ T

VS = 5V, VCM = VS + 0.1V 0.19 0.40 µA

= 5V, VCM = VS – 0.3V, 0°C ≤ TA ≤ 70°C ● 0.19 0.60 µA

V

S

= 5V, VCM = VS – 0.3V, –40°C ≤ TA ≤ 85°C ● 0.25 0.75 µA

V

S

VS = 5V, VCM = –0.1V –5 –0.41 µA

= 5V, VCM = 0V, 0°C ≤ TA ≤ 70°C ● –8.4 – 0.45 µA

V

S

= 5V, VCM = 0V, –40°C ≤ TA ≤ 85°C ● –10 – 0.47 µA

V

S

≤ 85°C ● 75 350 µV

A

≤ 70°C ● ± 3 ±35 nA

A

≤ 85°C ● ± 7 ±50 nA

A

T

= 150°C, θJA = 160°C/ W

JMAX

ORDER PART

NUMBER

LT1679CS

LT1679IS

sn16789 16789fs

Page 3

LT1678/LT1679

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

The ● denotes the specifications which apply over the full operating

= 25°C. VS = 3V, VCM = VO = 1.7V; VS = 5V, VCM = VO = 2.5V unless

A

otherwise noted.

SYMBOL PARAMETER CONDITIONS (Note 6) MIN TYP MAX UNITS

I

OS

e

n

i

n

V

CM

R

IN

C

IN

CMRR Common Mode Rejection Ratio VS = 5V, VCM = 1.9V to 3.9V 98 120 dB

PSRR Power Supply Rejection Ratio VS = 2.7V to 36V, VCM = VO = 1.7V 100 125 dB

A

VOL

V

OL

Input Offset Current (Note 11) 4 25 nA

0°C ≤ TA ≤ 70°C ● 535 nA

–40°C ≤ T

≤ 85°C ● 855 nA

A

VS = 5V, VCM = VS + 0.1V 6 30 nA

V

= 5V, VCM = VS – 0.3V, 0°C ≤ TA ≤ 70°C ● 10 40 nA

S

V

= 5V, VCM = VS – 0.3V, –40°C ≤ TA ≤ 85°C ● 15 65 nA

S

VS = 5V, VCM = –0.1V 0.1 1.6 µA

V

= 5V, VCM = 0V, 0°C ≤ TA ≤ 70°C ● 0.1 2.0 µA

S

VS = 5V, VCM = 0V, –40°C ≤ TA ≤ 85°C ● 0.15 2.4 µA

Input Noise Voltage 0.1Hz to 10Hz (Note 7) 90 nV

VCM = V

S

180 nV

VCM = 0V 1600 nV

P-P

P-P

P-P

Input Noise Voltage Density (Note 8) fO = 10Hz 4.4 nV/√Hz

VCM = VS, fO = 10Hz 6.6 nV/√Hz

V

= 0V, fO = 10Hz 19 nV/√Hz

CM

fO = 1kHz 3.9 5.5 nV/√Hz

VCM = VS, fO = 1kHz 5.3 nV/√Hz

V

= 0V, fO = 1kHz 9 nV/√Hz

CM

Input Noise Current Density fO = 10Hz 1.2 pA/√Hz

fO = 1kHz 0.3 pA/√Hz

Input Voltage Range –0.1 VS + 0.1V V

● 0V

– 0.3V V

S

Input Resistance Common Mode 2 GΩ

Input Capacitance 4.2 pF

VS = 5V, VCM = 1.9V to 3.9V ● 92 120 dB

V

= 3.1V to 36V, VCM = VO = 1.7V ● 98 120 dB

S

Large-Signal Voltage Gain VS = 3V, RL = 10k, VO = 2.5V to 0.7V 0.6 3 V/µV

● 0.3 2 V/µV

VS = 3V, RL = 2k, VO = 2.2V to 0.7V 0.5 3 V/µV

0°C ≤ TA ≤ 70°C ● 0.4 0.9 V/µV

–40°C ≤ T

≤ 85°C ● 0.4 0.8 V/µV

A

VS = 3V, RL = 600Ω, VO = 2.2V to 0.7V 0.20 0.43 V/µV

0°C ≤ TA ≤ 70°C ● 0.15 0.40 V/µV

–40°C ≤ T

≤ 85°C ● 0.10 0.35 V/µV

A

VS = 5V, RL = 10k, VO = 4.5V to 0.7V 1 3.8 V/µV

O°C < T

< 70°C ● 0.6 2 V/µV

A

–40 < TA < 85°C ● 0.3 2 V/µV

VS = 5V, RL = 2k, VO = 4.2V to 0.7V 0.7 3.5 V/µV

0°C ≤ T

≤ 70°C ● 0.6 3.2 V/µV

A

–40°C ≤ TA ≤ 85°C ● 0.5 3.0 V/µV

VS = 5V, RL = 600Ω, VO = 4.2V to 0.7V 0.6 3.0 V/µV

0°C ≤ T

≤ 70°C ● 0.5 2.8 V/µV

A

–40°C ≤ TA ≤ 85°C ● 0.4 2.5 V/µV

Output Voltage Swing Low (Note 11) Above GND

I

= 0.1mA 80 170 mV

SINK

0°C ≤ T

≤ 70°C ● 125 200 mV

A

– 40°C ≤ TA ≤ 85°C ● 130 250 mV

sn16789 16789fs

3

Page 4

LT1678/LT1679

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

The ● denotes the specifications which apply over the full operating

= 25°C. VS = 3V, VCM = VO = 1.7V; VS = 5V, VCM = VO = 2.5V unless

A

otherwise noted.

SYMBOL PARAMETER CONDITIONS (Note 6) MIN TYP MAX UNITS

V

OL

V

OH

I

SC

SR Slew Rate (Note 13) AV = – 1, RL = 10k 4 6 V/µs

GBW Gain Bandwidth Product (Note 11) fO = 100kHz 13 20 MHz

t

S

R

O

I

S

∆V

OS

∆IB+ Noninverting Bias Current Match ±2 ±30 nA

∆CMRR Common Mode Rejection Match VS = 5V, VCM = 1.9V to 3.9V 94 110 dB

∆PSRR Power Supply Rejection Match VS = 2.7V to 36V, VCM = VO = 1.7V 96 120 dB

Output Voltage Swing Low (Note 11) Above GND

I

= 2.5mA 170 250 mV

SINK

0°C ≤ T

– 40°C ≤ T

≤ 70°C ● 195 320 mV

A

≤ 85°C ● 205 350 mV

A

Above GND

I

= 10mA 370 600 mV

SINK

0°C ≤ T

– 40°C ≤ T

Output Voltage Swing High (Note 11) Below V

I

0°C ≤ T

– 40°C ≤ T

Below V

I

0°C ≤ T

– 40°C ≤ T

Below V

I

0°C ≤ T

– 40°C ≤ T

≤ 70°C ● 440 720 mV

A

≤ 85°C ● 465 770 mV

A

S

= 0.1mA 75 150 mV

SOURCE

≤ 70°C ● 85 200 mV

A

≤ 85°C ● 93 250 mV

A

S

= 2.5mA 110 250 mV

SOURCE

≤ 70°C ● 195 350 mV

A

≤ 85°C ● 205 375 mV

A

S

= 10mA 170 400 mV

SOURCE

≤ 70°C ● 200 500 mV

A

≤ 85°C ● 230 550 mV

A

Output Short-Circuit Current (Note 3) VS = 3V 15 22 mA

● 13 19 mA

VS = 5V 18 29 mA

● 14 25 mA

= 10k, 0°C ≤ TA ≤ 70°C ● 3.5 5.8 V/µs

R

L

= 10k, –40°C ≤ TA ≤ 85°C ● 3 5.5 V/µs

R

L

= 100kHz ● 12.5 19 MHz

f

O

Settling Time 2V Step 0.1%, AV = +1 1.4 µs

Open-Loop Output Resistance I

Closed-Loop Output Resistance A

2V Step 0.01%, A

= 0 100 Ω

OUT

= 100, f = 10kHz 1 Ω

V

= +1 2.4 µs

V

Supply Current per Amplifier (Note 12) 2 3.4 mA

● 2.5 3.8 mA

Offset Voltage Match 35 150 µV

(Notes 11, 15) 0°C ≤ T

(Notes 11, 15) 0°C ≤ T

(Notes 11, 14, 15)

(Notes 11, 14, 15) V

≤ 70°C ● 55 400 µV

A

–40°C ≤ T

–40°C ≤ T

S

≤ 85°C ● 75 525 µV

A

≤ 70°C ● ±3 ±55 nA

A

≤ 85°C ● ±7 ±75 nA

A

● 88 110 dB

= 3.1V to 36V, VCM = VO = 1.7V ● 94 120 dB

4

sn16789 16789fs

Page 5

LT1678/LT1679

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

The ● denotes the specifications which apply over the full operating

= 25°C. VS = ±15V, VCM = VO = 0V unless otherwise noted.

A

SYMBOL PARAMETER CONDITIONS (Note 6) MIN TYP MAX UNITS

V

∆V

OS

OS

Input Offset Voltage 20 150 µV

0°C ≤ T

≤ 70°C ● 30 350 µV

A

–40°C ≤ T

≤ 85°C ● 45 420 µV

A

Average Input Offset Drift (Note 10) ● 0.40 3 µV/°C

∆Temp

I

B

I

OS

e

n

Input Bias Current ±2 ±20 nA

0°C ≤ T

≤ 70°C ● ±3 ±35 nA

A

–40°C ≤ T

≤ 85°C ● ±7 ±50 nA

A

Input Offset Current 325 nA

≤ 70°C ● 535 nA

0°C ≤ T

A

–40°C ≤ T

Input Noise Voltage 0.1Hz to 10Hz (Note 7) 90 nV

≤ 85°C ● 855 nA

A

VCM = 15V 180 nV

VCM = –15V 1600 nV

P-P

P-P

P-P

Input Noise Voltage Density fO = 10Hz 4.4 nV/√Hz

= 15V, fO = 10Hz 6.6 nV/√Hz

V

CM

V

= –15V, fO = 10Hz 19 nV/√Hz

CM

fO = 1kHz 3.9 5.5 nV/√Hz

= 15V, fO = 1kHz 5.3 nV/√Hz

V

CM

= –15V, fO = 1kHz 9 nV/√Hz

V

CM

i

n

V

CM

R

IN

C

IN

Input Noise Current Density fO = 10Hz 1.2 pA/√Hz

f

= 1kHz 0.3 pA/√Hz

O

Input Voltage Range (Note 16) ● – 13.3 14 V

Input Resistance Common Mode 2 GΩ

Input Capacitance 4.2 pF

CMRR Common Mode Rejection Ratio VCM = –13.3V to 14V 100 130 dB

● 96 124 dB

PSRR Power Supply Rejection Ratio VS = ±1.7V to ±18V 106 130 dB

● 100 125 dB

A

VOL

Large-Signal Voltage Gain RL = 10k, VO = ±14V 3 7 V/µV

≤ 70°C ● 26 V/µV

0°C ≤ T

A

–40°C ≤ T

≤ 85°C ● 14 V/µV

A

RL = 2k, VO = ±13.5V 0.8 1.7 V/µV

0°C ≤ T

≤ 70°C ● 0.5 1.4 V/µV

A

–40°C ≤ T

≤ 85°C ● 0.4 1.1 V/µV

A

sn16789 16789fs

5

Page 6

LT1678/LT1679

ELECTRICAL CHARACTERISTICS

temperature range, otherwise specifications are at T

The ● denotes the specifications which apply over the full operating

= 25°C. VS = ±15V, VCM = VO = 0V unless otherwise noted.

A

SYMBOL PARAMETER CONDITIONS (Note 6) MIN TYP MAX UNITS

V

OL

Output Voltage Swing Low Above –V

I

= 0.1mA 110 200 mV

SINK

0°C ≤ T

– 40°C ≤ T

Above –V

I

= 2.5mA 170 280 mV

SINK

0°C ≤ T

S

≤ 70°C ● 125 230 mV

A

≤ 85°C ● 130 260 mV

A

S

≤ 70°C ● 195 350 mV

A

– 40°C ≤ TA ≤ 85°C ● 205 380 mV

Above –V

I

0°C ≤ T

– 40°C ≤ T

V

OH

Output Voltage Swing High Below +V

I

0°C ≤ T

– 40°C ≤ T

Below +V

I

S

= 10mA 370 600 mV

SINK

≤ 70°C ● 440 700 mV

A

≤ 85°C ● 450 750 mV

A

S

= 0.1mA 80 150 mV

SOURCE

≤ 70°C ● 90 200 mV

A

≤ 85°C ● 100 250 mV

A

S

= 2.5mA 110 200 mV

SOURCE

0°C ≤ TA ≤ 70°C ● 120 300 mV

– 40°C ≤ T

Below +V

I

SOURCE

0°C ≤ T

– 40°C ≤ T

I

SC

Output Short-Circuit Current (Note 3) 20 35 mA

≤ 85°C ● 120 350 mV

A

S

= 10mA 200 450 mV

≤ 70°C ● 250 500 mV

A

≤ 85°C ● 250 550 mV

A

● 15 28 mA

SR Slew Rate RL = 10k (Note 9) 4 6 V/µs

= 10k (Note 9) 0°C ≤ TA ≤ 70°C ● 3.5 5.8 V/µs

R

L

= 10k (Note 9) –40°C ≤ TA ≤ 85°C ● 3 5.5 V/µs

R

L

GBW Gain Bandwidth Product fO = 100kHz 13 20 MHz

= 100kHz ● 12.5 19 MHz

f

O

THD Total Harmonic Distortion RL = 2k, AV = 1, fO = 1kHz, VO = 20V

t

S

Settling Time 10V Step 0.1%, AV = +1 2.7 µs

P-P

0.00025 %

10V Step 0.01%, AV = +1 3.9 µs

R

O

I

S

Open-Loop Output Resistance I

Closed-Loop Output Resistance A

= 0 100 Ω

OUT

= 100, f = 10kHz 1 Ω

V

Supply Current per Amplifier 2.5 3.5 mA

● 3 4.5 mA

Channel Separation f = 10Hz, VO = ±10V, RL = 10k 132 dB

∆V

OS

Offset Voltage Match 5 225 µV

(Note 15) 0°C ≤ T

≤ 70°C ● 30 525 µV

A

–40°C ≤ T

≤ 85°C ● 45 630 µV

A

∆IB+ Noninverting Bias Current Match ±2 ±30 nA

(Note 15) 0°C ≤ TA ≤ 70°C ● ±3 ±55 nA

–40°C ≤ T

≤ 85°C ● ±7 ±75 nA

A

∆CMRR Common Mode Rejection Match VCM = –13.3V to 14V 96 120 dB

(Notes 14, 15)

● 92 115 dB

∆PSRR Power Supply Rejection Match VS = ±1.7V to ±18V 100 123 dB

(Notes 14, 15) ● 96 120 dB

6

sn16789 16789fs

Page 7

ELECTRICAL CHARACTERISTICS

LT1678/LT1679

Note 1: Absolute Maximum Ratings are those values beyond which the life

of the device may be impaired.

Note 2: The inputs are protected by back-to-back diodes. Current limiting

resistors are not used in order to achieve low noise. If differential input

voltage exceeds ±1.4V, the input current should be limited to 25mA. If the

common mode range exceeds either rail, the input current should be

limited to 10mA.

Note 3: A heat sink may be required to keep the junction temperature

below absolute maximum.

Note 4: The LT1678C/LT1679C and LT1678I/LT1679I are guaranteed

functional over the Operating Temperature Range of –40°C to 85°C.

Note 5: The LT1678C/LT1679C are guaranteed to meet specified

performance from 0°C to 70°C. The LT1678C/LT1679C are designed,

characterized and expected to meet specified performance from – 40°C to

85°C but is not tested or QA sampled at these temperatures. The LT1678I/

LT1679I are guaranteed to meet specified performance from – 40°C to

85°C.

Note 6: Typical parameters are defined as the 60% yield of parameter

distributions of individual amplifier; i.e., out of 100 LT1678/LT1679s,

Note 8: Noise is 100% tested at ±15V supplies.

Note 9: Slew rate is measured in A

measured at ±5V.

Note 10: This parameter is not 100% tested.

Note 11: V

= ±15V tests.

V

S

= 5V limits are guaranteed by correlation to VS = 3V and

S

Note 12: VS = 3V limits are guaranteed by correlation to VS = 5V and

= ±15V tests.

V

S

Note 13: Guaranteed by correlation to slew rate at VS = ±15V and GBW at

= 3V and VS = ±15V tests.

V

S

Note 14: ∆CMRR and ∆PSRR are defined as follows:

1. CMRR and PSRR are measured in µV/V on the individual amplifiers.

2. The difference is calculated between the matching sides in µV/V.

3. The result is converted to dB.

Note 15: Matching parameters are the difference between amplifiers A and

B on the LT1678 and between amplifiers A and D and B and C in the

LT1679.

Note 16: Input range guaranteed by the common mode rejection ratio test.

typically 60 op amps will be better than the indicated specification.

Note 7: See the test circuit and frequency response curve for 0.1Hz to10Hz

tester in the Applications Information section.

UW

TYPICAL PERFOR A CE CHARACTERISTICS

= – 1; input signal is ±10V, output

V

Voltage Noise vs Frequency

100

VS = ±15V

= 25°C

T

A

10

NOISE VOLTAGE (nV/√Hz)

1

0.1

1 100

10 1000

FREQUENCY (Hz)

VCM = 14.5V

VCM = 0V

16789 G01

0.1Hz to 10Hz Voltage Noise

VS = 5V, 0V

VOLTAGE NOISE (50nV/DIV)

4681002

TIME (sec)

16789 G02

0.01Hz to 1Hz Voltage Noise

VS = 5V, 0V

VOLTAGE NOISE (50nV/DIV)

40 60 80 100020

TIME (sec)

16789 G03

sn16789 16789fs

7

Page 8

LT1678/LT1679

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Voltage Noise vs Temperature

6

VS = ±15V

= 0V

V

CM

5

–25

0

10Hz

1kHz

50

25

TEMPERATURE (°C)

RMS VOLTAGE NOISE DENSITY (nV/√Hz)

4

3

2

1

–50

Input Bias Current vs Temperature

1400

VS = ±15V

1200

1000

800

600

400

INPUT BIAS CURRENT (nA)

200

0

–25 25 100 125

–50 0 50 75

VCM = –14V

CURRENT OUT OF DUT

VCM = 14.7V

CURRENT INTO DUT

TEMPERATURE (°C)

Current Noise vs Frequency

10

VS = ±15V

= 25°C

T

A

1

NOISE VOLTAGE (pA/√Hz)

100

125

16789 G04

75

0.1

0.01

VCM = 0V

VCM = 14.5V

0.1 1 10

FREQUENCY (kHz)

16789 G05

Input Bias Current Over the

Common Mode Range

900

VS = ±15V

700

= 25°C

T

A

500

0

VCM = 14.5V

VCM = 14.1V

8

12

16789 G08

–1

–2

OFFSET VOLTAGE (mV)

–3

–4

–5

16789 G07

300

VCM = –13.5V

100

–100

–300

INPUT BIAS CURRENT (nA)

–500

–700

–900

–16 16

INPUT BIAS CURRENT

VCM = –15.2V

–12 –4 4

–8

COMMON MODE INPUT VOLTAGE (V)

Input Bias Current vs Temperature

16

VS = ±15V

14

= 0V

V

CM

12

10

8

6

4

2

0

INPUT BIAS CURRENT (nA)

–2

–4

–6

–50 25 75

–25 0

TEMPERATURE (°C)

50 100 125

Offset Voltage Shift vs

Common Mode

5

4

3

2

1

0

–1.0

VOS IS REFERRED TO

V

CM

–

1.0

V

2.0

= 0V

VS = ±1.5V TO ±15V

= 25°C

T

A

5 TYPICAL PARTS

–0.8 –0.4 V

– V+ (V)VCM – V– (V)

V

CM

+

0.4

16789 G09

16789 G06

500

400

300

200

100

0

–100

–200

–300

–400

–500

OFFSET VOLTAGE (µV)

Warm-Up Drift vs Time

10

VS = ±15V

= 25°C

T

A

8

6

4

2

CHANGE IN OFFSET VOLTAGE (µV)

0

0

1

8

SO PACKAGE

2

TIME (min)

V

Distribution of Input Offset

Voltage Drift (SO-8)

30

VS = 5V, 0V

= –40°C TO 85°C

T

A

111 PARTS (2 LOTS)

25

20

15

10

PERCENT OF UNITS (%)

5

0

3

4

16789 G10

–3.0 3.0

–1.0 1.0

–2.0 2.0

INPUT OFFSET VOLTAGE DRIFT (µV/°C)

0

16789 G11

–100

VOLTAGE OFFSET (µV)

–200

–300

vs Temperature of

OS

Representive Units

200

VS = 5V, 0V

= 0V

V

CM

100

0

–35 5

–55

–15

TEMPERATURE (°C)

85

45 125

65

25

sn16789 16789fs

105

16789 G12

Page 9

UW

TYPICAL PERFOR A CE CHARACTERISTICS

LT1678/LT1679

Common Mode Range vs

Temperature

5

4

3

2

25°C

1

125°C

0

–1

–2

OFFSET VOLTAGE (mV)

–3

–4

–5

–1.0

–

V

VOS IS REFERRED TO

V

CM

1.0

–

(V)

S

–55°C

= 0V

2.0

–0.8 –0.4 V

VS = ±2.5V TO ±15V

25°C

125°C

V

– V

CM

Power Supply Rejection Ratio

vs Frequency

160

VS = ±15V

= 25°C

T

A

140

120

100

80

60

40

20

POWER SUPPLY REJECTION RATIO (dB)

0

0.001 0.01

NEGATIVE SUPPLY

POSITIVE SUPPLY

0.1 101

FREQUENCY (kHz)

S

–55°C

–

+

(V)VCM – V

100

0.4

16789 G09

16789 G16

1000

500

400

300

200

100

0

–100

–200

–300

–400

–500

Supply Current vs Supply Voltage

4.0

3.5

OFFSET VOLTAGE (µV)

3.0

T

= 125°C

2.5

2.0

1.5

SUPPLY CURRENT PER AMPLIFIER (mA)

1.0

0

A

±5 ±10 ±15 ±20

SUPPLY VOLTAGE (V)

Voltage Gain vs Supply Voltage

10

RL = 10k

1

OPEN LOOP VOLTAGE GAIN (V/µV)

0.1

0

10

SUPPLY VOLTAGE (V)

RL = 2k

T

= 25°C

A

TA = 25°C

TO GND

R

L

= VO = VS/2

V

CM

20

= –55°C

T

A

16789 G17

16789 G14

30

Common Mode Rejection Ratio

vs Frequency

160

VS = ±15V

= 25°C

T

140

A

= 0V

V

CM

120

100

80

60

40

20

COMMON MODE REJECTION RATIO (dB)

0

10k

100k 1M 10M

FREQUENCY (Hz)

% Overshoot vs Capacitive Load

60

VS = ±15V

= 2k TO 10k

R

L

= 1

A

50

V

= 25°C

T

A

40

30

OVERSHOOT (%)

20

10

0

RISING EDGE

FALLING EDGE

10

100 1000

CAPACITIVE LOAD (pF)

16789 G15

16789 G18

Phase Margin, Gain Bandwidth

Product and Slew Rate vs

Temperature

90

80

PHASE MARGIN

70

60

50

PHASE MARGIN (DEG)

40

8

6

SLEW RATE (V/µs)

4

–35 5

–55 –15

GAIN BANDWIDTH PRODUCT

+SR

–SR

25

TEMPERATURE (°C)

45 125

65

VS = ±15V

= 15pF

C

L

= –1

A

V

= RG = 1k

R

F

85

105

16789 G19

Large Signal

GAIN BANDWIDTH PRODUCT, f

30

25

20

15

O

= 100kHz (MHz)

10

Transient Response

10V

–10V

= –1

A

VCL

= ±15V

V

S

5µs/DIV

16789 G20

Small Signal

Transient Response

50mV

0V

–50mV

= 1

A

VCL

= ±15V

V

S

= 15pF

C

L

0.5µs/DIV

16789 G21

sn16789 16789fs

9

Page 10

LT1678/LT1679

UW

TYPICAL PERFOR A CE CHARACTERISTICS

Settling Time vs Output

Step (Inverting)

6

VS = ±15V

= –1

A

V

5

= 25°C

T

A

4

0.01% OF

3

FULL SCALE

2

SETTLING TIME (µs)

0.1% OF

FULL SCALE

1

0

–10 –8 –4 0 4 8

–6 –2 2 6

5k

V

IN

OUTPUT STEP (V)

Gain, Phase Shift vs Frequency

50

40

TA = –55°C

30

20

10

VOLTAGE GAIN (dB)

0

–10

0.1

PHASE

TA = 125°C

TA = 25°C

TA = 125°C

TA = –55°C

GAIN

1 10 100

FREQUENCY (MHz)

5k

–

+

0.01% OF

FULL SCALE

0.1% OF

FULL SCALE

VS = ±15V

= 14.7V

V

CM

= 10pF

C

L

TA = 25°C

V

OUT

16789 G22

16789 G25

SETTLING TIME (µs)

10

100

80

PHASE SHIFT (DEG)

60

40

20

0

–20

Settling Time vs Output

Step (Noninverting)

6

VS = ±15V

= 1

A

V

5

= 25°C

T

A

4

0.01% OF

FULL SCALE

3

2

0.1% OF

1

FULL SCALE

0

–10 –8 –4 0 4 8–6 –2 2 6 10

V

IN

OUTPUT STEP (V)

–

2k

+

0.01% OF

FULL SCALE

2k

RL = 1k

0.1% OF

FULL SCALE

16789 G23

Gain, Phase Shift vs Frequency

50

40

30

20

10

VOLTAGE GAIN (dB)

TA = 25°C

0

TA = –55°C

–10

0.1

GAIN

1 10 100

FREQUENCY (MHz)

PHASE

VS = ±15V

= –14V

V

CM

= 10pF

C

L

TA = –55°C

TA = 125°C

TA = 25°C

V

OUT

16789 G26

Gain, Phase Shift vs Frequency

50

40

30

20

TA = 125°C

10

VOLTAGE GAIN (dB)

0

–10

0.1

100

+V

S

0

80

60

40

20

0

–20

–0.1

–0.2

PHASE SHIFT (DEG)

–0.3

0.8

0.7

0.6

0.5

0.4

0.3

OUTPUT VOLTAGE SWING (V)

0.2

0.1

–V

0

S

–10

VS = ±15V

V

PHASE

TA = –55°C

TA = 25°C

1 10 100

FREQUENCY (MHz)

GAIN

TA = –55°C

CM

= 10pF

C

L

TA = 25°C

TA = 125°C

Output Voltage Swing vs

Load Current

VS = ±15V

TA = 125°C

TA = 25°C

TA = 125°C

TA = 25°C

TA = –55°C

–8 –4

–6

–2

OUTPUT CURRENT (mA)

4

0810

2

100

= 0V

80

PHASE SHIFT (DEG)

60

40

20

0

–20

16789 G24

TA = –55°C

6

16789 G27

Closed-Loop Output

Impedance vs Frequency

100

VS = ±15V

10

1

0.1

OUTPUT IMPEDANCE (Ω)

0.01

0.001

100

10

FREQUENCY (Hz)

10

AV = 100

1k

10k

Total Harmonic Distortion and

Noise vs Frequency for

Noninverting Gain

0.1

ZL = 2k/15pF

= ±15V

V

S

= 20V

V

O

P-P

AV = 1, 10, 100

MEASUREMENT BANDWIDTH

0.01

= 10Hz TO 80kHz

AV = 100

= 1

A

V

100k

1M

16789 G28

0.001

AV = 10

AV = 1

TOTAL HARMONIC DISTORTION + NOISE (%)

0.0001

20 1k 10k 50k

100

FREQUENCY (Hz)

16789 G29

Total Harmonic Distortion and

Noise vs Frequency for

Noninverting Gain

0.1

ZL = 2k/15pF

= ±15V

V

S

= 20V

V

O

P-P

AV = –1, –10, –100

MEASUREMENT BANDWIDTH

0.01

= 10Hz TO 80kHz

AV = –100

0.001

AV = –10

AV = –1

TOTAL HARMONIC DISTORTION + NOISE (%)

0.0001

20 1k 10k 50k

100

FREQUENCY (Hz)

sn16789 16789fs

16789 G30

Page 11

WUUU

APPLICATIO S I FOR ATIO

LT1678/LT1679

Rail-to-Rail Operation

To take full advantage of an input range that can exceed

the supply, the LT1678/LT1679 are designed to eliminate

phase reversal. Referring to the photographs shown in

Figure 1, the LT1678/LT1679 are operating in the follower mode (A

= +1) at a single 3V supply. The output

V

of the LT1678/LT1679 clips cleanly and recovers with no

phase reversal. This has the benefit of preventing lock-up

in servo systems and minimizing distortion components.

Input = –0.5V to 3.5V

3

2

1

INPUT VOLTAGE (V)

0

–0.5

50µs/DIV

LT1678 Output

3

2

16789 F01a

input and a current, limited only by the output short-circuit

protection, will be drawn by the signal generator. With

R

≥ 500Ω, the output is capable of handling the current

F

requirements (I

≤ 20mA at 10V) and the amplifier stays

L

in its active mode and a smooth transition will occur.

As with all operational amplifiers when R

be created with R

and the amplifier’s input capacitance,

F

> 2k, a pole will

F

creating additional phase shift and reducing the phase

margin. A small capacitor (20pF to 50pF) in parallel with R

F

will eliminate this problem.

R

F

–

OUTPUT

+

LT1678

Figure 2. Pulsed Operation

6V/µs

16789 F02

Noise Testing

The 0.1Hz to 10Hz peak-to-peak noise of the

LT1679

are measured in the test circuit shown (Figure 3).

LT1678/

The frequency response of this noise tester (Figure 4)

indicates that the 0.1Hz corner is defined by only one zero.

The test time to measure 0.1Hz to 10Hz noise should not

exceed ten seconds, as this time limit acts as an additional

zero to eliminate noise contributions from the frequency

band below 0.1Hz.

1

OUTPUT VOLTAGE (V)

0

–0.5

50µs/DIV

Figure 1. Voltage Follower with Input Exceeding the Supply

Voltage (VS = 3V)

16789 F01b

Unity-Gain Buffer Application

When RF ≤ 100Ω and the input is driven with a fast, large-

signal pulse (>1V), the output waveform will look as

shown in the pulsed operation diagram (Figure 2).

During the fast feedthrough-like portion of the output, the

input protection diodes effectively short the output to the

Measuring the typical 90nV peak-to-peak noise performance of the

LT1678/LT1679

requires special test pre-

cautions:

1. The device should be warmed up for at least five

minutes. As the op amp warms up, its offset voltage

changes typically 3µV due to its chip temperature

increasing 10°C to 20°C from the moment the power

supplies are turned on. In the ten-second measurement

interval these temperature-induced effects can easily

exceed tens of nanovolts.

2. For similar reasons, the device must be well shielded

from air currents to eliminate the possibility of

thermoelectric effects in excess of a few nanovolts,

which would invalidate the measurements.

sn16789 16789fs

11

Page 12

LT1678/LT1679

(i) RS ≤ 400Ω. Voltage noise dominates

(ii) 400Ω ≤ R

S

≤ 50k at 1kHz

400Ω ≤ R

S

≤ 8k at 10Hz

(iii) R

S

> 50k at 1kHz

R

S

> 8k at 10Hz

Resistor Noise

Dominates

Current Noise

Dominates

WUUU

APPLICATIO S I FOR ATIO

0.1µF

100k

10Ω

*DEVICE UNDER TEST

NOTE: ALL CAPACITOR VALUES ARE FOR

NONPOLARIZED CAPACITORS ONLY

–

*

LT1678

+

VOLTAGE GAIN

= 50,000

2k

4.7µF

+

–

24.3k

LT1001

100k

0.1µF

4.3k

22µF

2.2µF

Figure 3. 0.1Hz to 10Hz Noise Test Circuit

3. Sudden motion in the vicinity of the device can also

“feedthrough” to increase the observed noise.

Current noise is measured in the circuit shown in Figure 5

and calculated by the following formula:

12

/

⎡

e

⎢

()

no

⎣

i

=

n

2

−

130

nV

()

Ω

1 101

M

()()

•

101

2

⎤

⎥

⎦

100

90

80

70

60

GAIN (dB)

50

40

30

0.01 1 10 100

0.1

FREQUENCY (Hz)

16789 F04

110k

SCOPE

× 1

= 1M

R

IN

16789 F03

Figure 4. 0.1Hz to 10Hz Peak-to-Peak

Noise Tester Frequency Response

Total Noise = [(op amp voltage noise)2 + (resistor noise)

+ (current noise RS)2]

1/2

2

Three regions can be identified as a function of source

resistance:

100k

100Ω

500k

500k

–

LT1678

+

Figure 5.

The

LT1678/LT1679

achieve their low noise, in part, by

operating the input stage at 100µA versus the typical 10µA

of most other op amps. Voltage noise is inversely proportional while current noise is directly proportional to the

square root of the input stage current. Therefore, the

LT1678/LT1679

’s current noise will be relatively high. At

low frequencies, the low 1/f current noise corner frequency (≈200Hz) minimizes current noise to some extent.

In most practical applications, however, current noise will

not limit system performance. This is illustrated in the

Total Noise vs Source Resistance plot (Figure 6) where:

12

16789 F05

Clearly the

e

no

(iii), where total system noise is at least six times higher

than the voltage noise of the op amp, i.e., the low voltage

LT1678/LT1679

should not be used in region

noise specification is completely wasted. In this region the

LT1113 or LT1169 are better choices.

1000

100

TOTAL NOISE DENSITY (nV/√Hz)

Figure 6. Total Noise vs Source Resistance

R

R

SOURCE RESISTANCE = 2R

10

1

0.1

VS = ±15V

T

AT 1kHz

AT 10Hz

RESISTOR

NOISE ONLY

1 10 100

SOURCE RESISTANCE (kΩ)

= 25°C

A

16789 F06

sn16789 16789fs

Page 13

WUUU

APPLICATIO S I FOR ATIO

LT1678/LT1679

Rail-to-Rail Input

The input common mode range for the

LT1678/LT1679

can exceed the supplies by at least 100mV. As the

common mode voltage approaches the positive rail (+V

S

– 0.7V), the tail current for the input pair (Q1, Q2) is

reduced, which prevents the input pair from saturating

(refer to the Simplified Schematic). The voltage drop

across the load resistors RC1, RC2 is reduced to less than

200mV, degrading the slew rate, bandwidth, voltage

noise, offset voltage and input bias current (the cancellation is shut off).

When the input common mode range goes below 1.5V

above the negative rail, the NPN input pair (Q1, Q2) shuts

off and the PNP input pair (Q8, Q9) turns on. The offset

voltage, input bias current, voltage noise and bandwidth

are also degraded. The graph of Offset Voltage Shift vs

Common Mode shows where the knees occur by displaying the change in offset voltage. The change-over points

are temperature dependent; see the graph Common Mode

Range vs Temperature.

Rail-to-Rail Output

The rail-to-rail output swing is achieved by using transistor collectors (Q28, Q29 referring to the Simplified Schematic) instead of customary class A-B emitter followers for

the output stage. The output NPN transistor (Q29) sinks the

current necessary to move the output in the negative direction. The change in Q29’s base emitter voltage is reflected

directly to the gain node (collectors of Q20 and Q16). For

large sinking currents, the delta V

of Q29 can dominate

BE

the gain. Figure 7 shows the change in input voltage for a

change in output voltage for different load resistors connected between the supplies. The gain is much higher for

output voltages above ground (Q28 sources current) since

the change in base emitter voltage of Q28 is attenuated by

the gain in the PNP portion of the output stage. Therefore,

for positive output swings (output sourcing current) there

is hardly any change in input voltage for any load resistance.

Highest gain and best linearity are achieved when the output

is sourcing current, which is the case in single supply operation when the load is ground referenced. Figure 8 shows

gains for both sinking and sourcing load currents for a

worst-case load of 600Ω.

INPUT VOLTAGE

(50µV/DIV)

VOLTAGE GAIN SINGLE SUPPLY

= 5V

V

S

= 600Ω

R

RL = 600Ω

RL = 1k

RL = 10k

TA = 25°C

= ±15V

V

S

CONNECTED TO 0V

R

L

MEASURED ON

TEKTRONIX 577

CURVE TRACER

–15 –10 –5 0 5 10 15

OUTPUT VOLTAGE (V)

Figure 7. Voltage Gain Split Supply Figure 8. Voltage Gain Single Supply

16789 F07

INPUT VOLTAGE

(10µV/DIV)

RL TO 0V

RL TO 5V

120354

L

MEASURED ON TEKTRONIX 577

CURVE TRACER

OUTPUT VOLTAGE (V)

16789 F08

sn16789 16789fs

13

Page 14

LT1678/LT1679

R8

200Ω

R21

100Ω

R13

100Ω

R24

100Ω

R9

200Ω

Q1A

Q10

Q12

Q5

Q6

Q4 Q7

C10

81pF

R

C2

6k

R

C1

6k

Q11

Q3

IB

D4

D3

D1

D2

IC

ID

50µA

IA, IB = 0µA V

CM

> 1.5V ABOVE –V

S

200µA V

CM

< 1.5V ABOVE –V

S

IC = 200µA V

CM

< 0.7V BELOW +V

S

50µA V

CM

> 0.7V BELOW +V

S

ID = 100µA V

CM

< 0.7V BELOW +V

S

0µA V

CM

> 0.7V BELOW +V

S

IA

Q8 Q9

Q21

Q13

×2

Q2B

Q17

Q18

R15

1k

Q24

+

+IN

–IN

50µA

Q15

Q14 Q16

Q25

Q22

100µA

R14

1k

R16

1k

R25

1k

R30

2k

R26

100Ω

R29

10Ω

R23B

10k

R23A

10k

100µA

160µA

Q19

Q20

R20

2k

R2

50Ω

R19

2k

200µA

Q38

Q23

C2

80pF

+

R32

1.5k

Q32

R34

2k

R54

100Ω

R3

100Ω

C3

40pF

C4

20pF

Q29

16789 SS

Q26

Q30

Q31

+

R1

500Ω

C1

40pF

+

+

Q27

Q35

Q34

Q28

OUT

–V

S

+V

S

Q1B Q2A

WW

SI PLIFIED SCHE ATIC

14

sn16789 16789fs

Page 15

PACKAGE DESCRIPTIO

.050 BSC

U

S8 Package

8-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

.189 – .197

.045 ±.005

(4.801 – 5.004)

8

NOTE 3

7

6

LT1678/LT1679

5

.245

MIN

.030 ±.005

TYP

RECOMMENDED SOLDER PAD LAYOUT

.010 – .020

(0.254 – 0.508)

.008 – .010

(0.203 – 0.254)

.016 – .050

NOTE:

1. DIMENSIONS IN

2. DRAWING NOT TO SCALE

3. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

(0.406 – 1.270)

INCHES

(MILLIMETERS)

× 45°

.160 ±.005

0°– 8° TYP

.228 – .244

(5.791 – 6.197)

S Package

14-Lead Plastic Small Outline (Narrow .150 Inch)

(Reference LTC DWG # 05-08-1610)

.050 BSC

N

.045 ±.005

.053 – .069

(1.346 – 1.752)

.014 – .019

(0.355 – 0.483)

TYP

13

14

1

.337 – .344

(8.560 – 8.738)

12

2

NOTE 3

11

.150 – .157

(3.810 – 3.988)

NOTE 3

3

4

.004 – .010

(0.101 – 0.254)

.050

(1.270)

BSC

SO8 0303

10

8

9

.245

MIN

1 2 3 N/2

.030 ±.005

TYP

RECOMMENDED SOLDER PAD LAYOUT

.010 – .020

(0.254 – 0.508)

.008 – .010

(0.203 – 0.254)

NOTE:

1. DIMENSIONS IN

2. DRAWING NOT TO SCALE

3. THESE DIMENSIONS DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS.

MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED .006" (0.15mm)

× 45°

.016 – .050

(0.406 – 1.270)

INCHES

(MILLIMETERS)

.160 ±.005

(5.791 – 6.197)

0° – 8° TYP

Information furnished by Linear Technology Corporation is believed to be accurate and reliable.

However, no responsibility is assumed for its use. Linear Technology Corporation makes no representation that the interconnection of its circuits as described herein will not infringe on existing patent rights.

.228 – .244

.053 – .069

(1.346 – 1.752)

.014 – .019

(0.355 – 0.483)

TYP

N

.150 – .157

(3.810 – 3.988)

N/2

1

3

2

4

.050

(1.270)

BSC

5

7

6

NOTE 3

.004 – .010

(0.101 – 0.254)

S14 0502

sn16789 16789fs

15

Page 16

LT1678/LT1679

TYPICAL APPLICATIO

Bridge Reversal Eliminates 1/f Noise and Offset Drift of a Low Noise, Non-autozeroed, Bipolar Amplifier.

Circuit Gives 14nV Noise Level or 19 Effective Bits Over a 10mV Span

V

REF

3

350Ω

350Ω

5,6,7,8

5,6,7,8

V

1

3

1

350Ω

REF

4

2

100k

350Ω

100k

4

2

φ1

2X

SILICONIX

Si9801

φ2

U

100Ω

0.1%

5V

+

1/2 LT1678

–

–

1/2 LT1678

+

0.047µF

0.047µF

7V

10Ω

1k

0.1%

1k

0.1%

10Ω

LT1461-5

φ1

φ2

1µF

1µF

≈2s

10µF

100Ω

100Ω

0.1µF

+

IN

–

IN

V

REF

REF

LTC2440

–

REF

16789 TA02

+

RELATED PARTS

PART NUMBER DESCRIPTION COMMENTS

LT1028/LT1128 Ultralow Noise Precision Op Amps Lowest Noise 0.85nV/√Hz

LT1115 Ultralow Noise, Low distortion Audio Op Amp 0.002% THD, Max Noise 1.2nV/√Hz

LT1124/LT1125 Dual/Quad Low Noise, High Speed Precision Op Amps Similar to LT1007

LT1126/LT1127 Dual/Quad Decompensated Low Noise, High Speed Precision Op Amps Similar to LT1037

LT1226 Low Noise, Very High Speed Op Amp 1GHz, 2.6nV/√Hz, Gain of 25 Stable

LT1498/LT1499 10MHz, 5V/µs, Dual/Quad Rail-to-Rail Input and Output Op Amps Precision C-LoadTM Stable

LT1677 Single Version of LT1678/LT1679 Rail-to-Rail 3.2nV/√Hz

LT1792 Low Noise, Precision JFET Input Op Amp 4.2nV/√Hz, 10fA/√Hz

LT1793 Low Noise, Picoampere Bias Current Op Amp 6nV/√Hz, 1fA/√Hz, IB = 10pA Max

LT1806 Low Noise, 325MHz Rail-to-Rail Input and Output Op Amp 3.5nV/√Hz

LT1881/LT1882 Dual/Quad Rail-to-Rail Output Picoamp Input Precision Op Amps C

LT1884/LT1885 Dual/Quad Rail-to-Rail Output Picoamp Input Precision Op Amps 2.2MHz Bandwidth, 1.2V/µs SR

C-Load is a trademark of Linear Technology Corporation.

Linear Technology Corporation

16

1630 McCarthy Blvd., Milpitas, CA 95035-7417

(408) 432-1900 ● FAX: (408) 434-0507

●

www.linear.com

to 1000pF, IB = 200pA Max

LOAD

© LINEAR TECHNOLOGY CORPORATION 2003

LT/TP 0104 1K • PRINTED IN USA

sn16789 16789fs

Loading...

Loading...