Linear LTC2345 Demo Manual

Description

DEMO MANUAL DC2326A

LTC2345

16-/18-Bit, Octal 200ksps, SAR ADC

Demonstration circuit 2326A shows the proper way to drive

®

the LTC

2345 ADC. The LTC2345 is a low noise, high speed,

simultaneous sampling 16-/18-bit successive approximation

register (SAR) ADC. The LTC2345 has a flexible SoftSpan

interface that allows conversion-by-conversion control of

the input voltage span on a per-channel basis. An internal

2.048V reference and 2× buffer simplify basic operation

while an external reference can be used to increase the

input range and the SNR of the ADC.

The DC2326A demonstrates the DC and AC performance of

the LTC2345 in conjunction with the DC590/DC2026 and

DC890 data collection boards. Use the DC590/DC2026 to

demonstrate DC performance such as peak-to-peak noise

and DC linearity. Use the DC890 if precise sampling rates

are required or to demonstrate AC performance such as

™

SNR, THD, SINAD and SFDR. The DC2326A is intended

to demonstrate recommended grounding, component

placement and selection, routing and bypassing for this

ADC. A suggested driver circuit for the analog inputs is

also presented.

Design files for this circuit board including the schematic,

layout and BOM are available at

http://www.linear.com/demo/DC2326A

L, LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks and PScope,

QuikEval and SoftSpan are trademarks of Linear Technology Corporation. All other trademarks

are the property of their respective owners.

assembly options

Assembly

Version U1 Part Number

DC2326A-A

DC2326A-B LTC2345-16 200ksps 8 16 60MHz 300

LTC2345-18 200ksps 8 18 60MHz 300

Max Conversion

Rate

Number of

Channels

Number of

Bits

Max CLK IN

Frequency

CLK IN/fs

Ratio

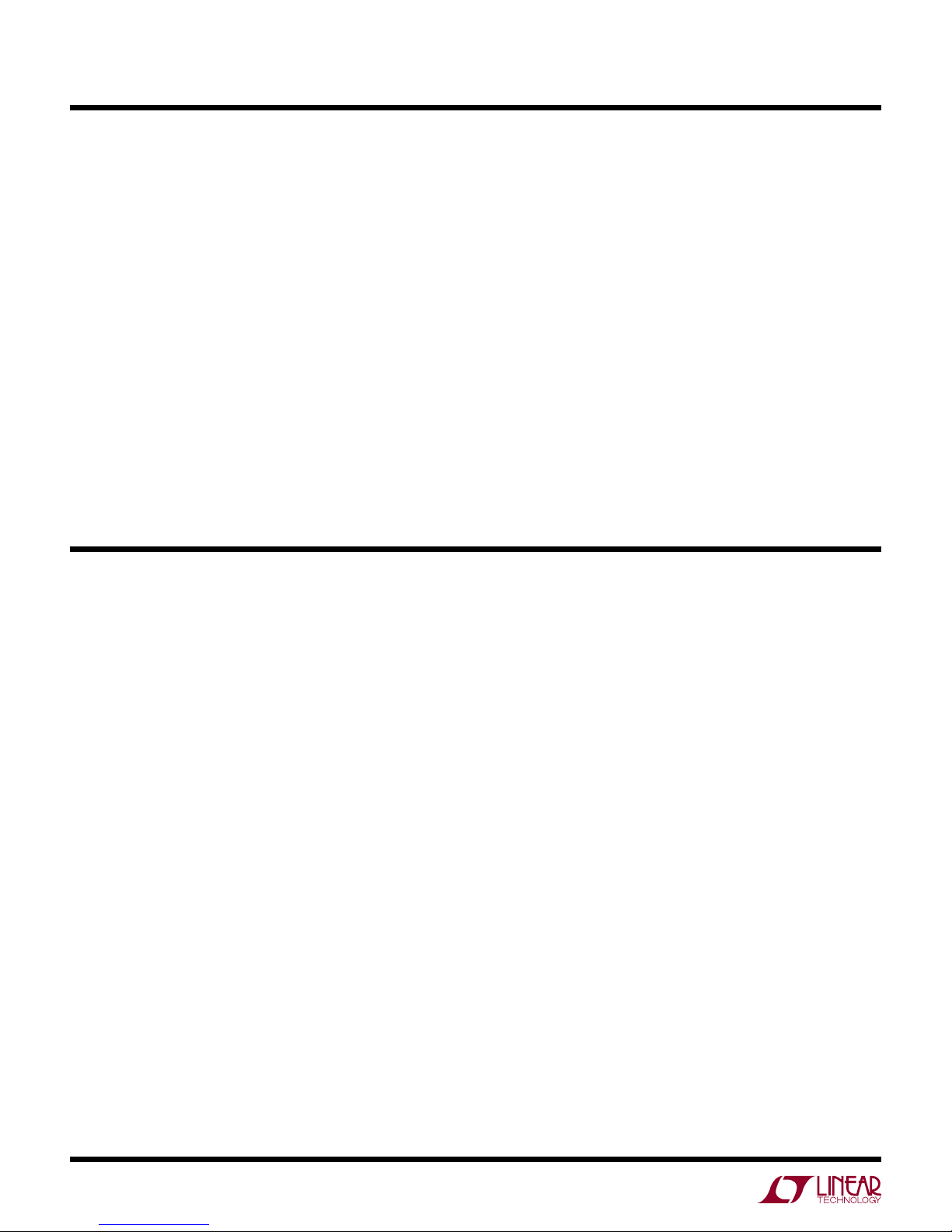

boarD photo

0V to 4.096V

0V to 4.096V

+9V

GND

–9V

V

IN2

DC890

V

IN1

CLK

100MHz MAX

2.5V

P-P

Figure 1. DC2326A Connection Diagram

DC590 OR DC2026

dc2326af

1

DEMO MANUAL DC2326A

Dc890 Quick start proceDure

Check to make sure that all jumpers are set to their default

settings as described in the DC2326A Jumpers section of

this manual. The default connections configure the ADC to

use the onboard reference and regulators to generate all

the required bias voltages. The analog inputs by default are

DC coupled. Connect the DC2326A to a DC890 USB High

Speed Data Collection Board using connector P1. Then,

connect the DC890 to a host PC with a standard USB A/B

cable. Apply ±9V to the indicated terminals. Then apply

a low jitter signal source to J5 and J6. Use J7 to route

the signal sources of J5 and J6 to the desired AIN0-AIN7

inputs. Observe the recommended input voltage range

for each analog input. Connect a low jitter 2.5V

wave or square wave to connector J1. See the Assembly

Options table for the appropriate clock frequency. Note

that J1 has a 50Ω termination resistor to ground.

P-P

sine

™

Run the PScope

later) which can be downloaded from www.linear.com/

designtools/software.

Complete software documentation is available from the

Help menu. Updates can be downloaded from the

menu.

may be added.

The PScope software should recognize the DC2326A and

configure itself automatically.

Click the Collect button (See Figure 3) to begin acquiring

data. The Collect button then changes to Pause, which

can be clicked to stop data acquisition.

Check for updates periodically as new features

software (Pscope.exe version K82 or

Tools

Dc590/Dc2026 Quick start proceDure

IMPORTANT! To avoid damage to the DC2326A, make

sure that VCCIO (JP6 of the DC590, JP3 of the DC2026)

of the DC590/DC2026 is set to 3.3V before connecting

the DC590/DC2026 to the DC2326A.

To use the DC590/DC2026 with the DC2326A, it is necessary

to apply ±9V and ground to the ±9V and GND terminals of

the DC2326A. Connect the DC590/DC2026 to a host PC

with a standard USB A/B cable. Connect the DC2326A to

a DC590/DC2026 USB serial controller using the supplied

14-conductor ribbon cable. Apply a signal source to J5

and J6. Use J7 to route the signal sources of J5 and J6

to the desired AIN0-AIN7 inputs. No Clock is required on

J1 when using the DC590/DC2026. The clock signal is

provided by the DC590/DC2026.

Run the QuikEval software (quikeval.exe version K103 or

later) which is available from www.linear.com/designtools/

software. The correct control panel will be loaded auto

matically. Click

reading the ADC.

-

the COLLECT button (Figure 6) to begin

2

dc2326af

Dc2326a setup

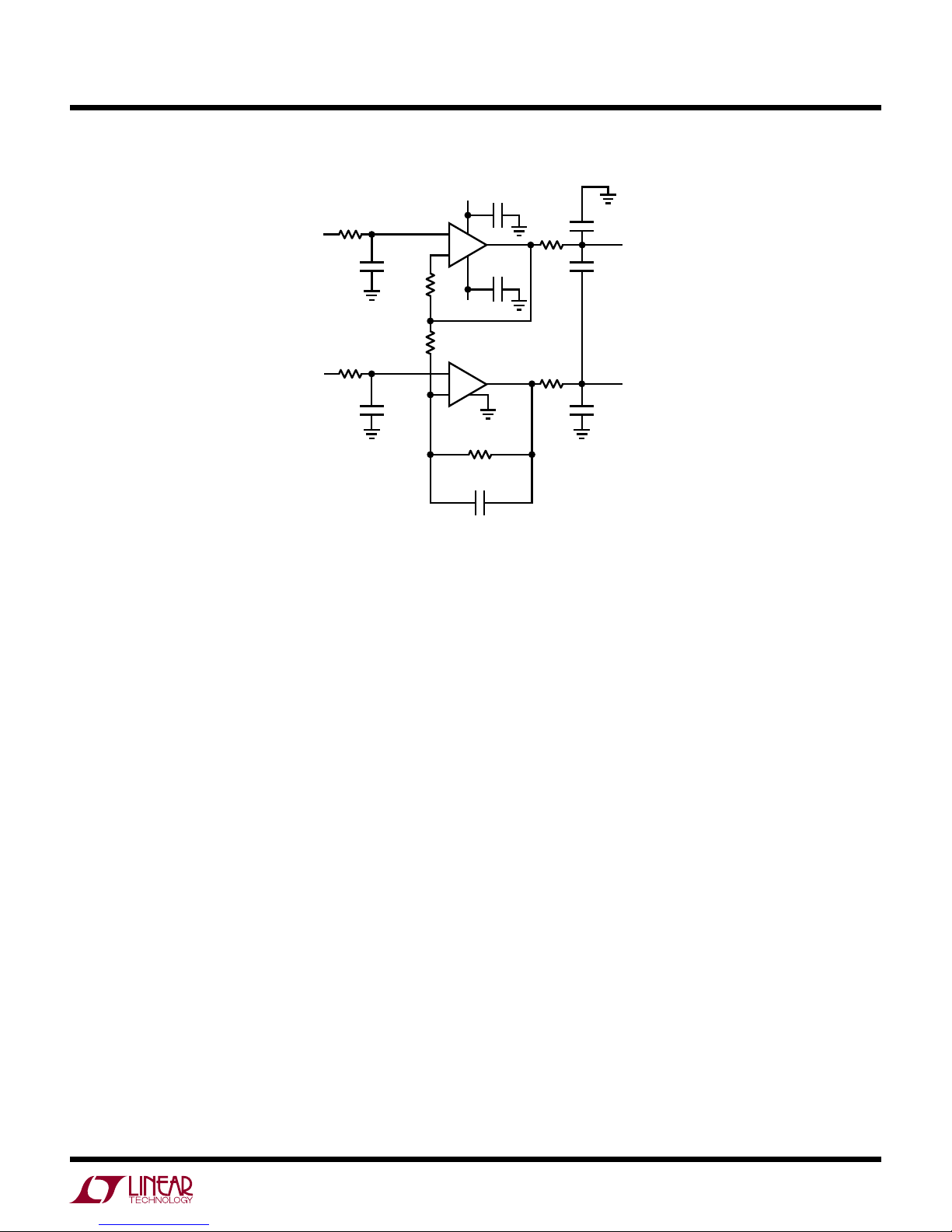

IN0

R107

0Ω

C100

OPT

U25B

LT6237IDD

R113

0Ω

DEMO MANUAL DC2326A

C96

V

CC

0.1µF

R108

+

C104

–

0.1µF

V

EE

49.9Ω

C94

1000pF

C98

OPT

IN0

+

R124

0Ω

V

CM

C112

OPT

R119

1k

+

–

Figure 2. 0V–4.096V Single-Ended to Fully Differential DC Coupled Driver

DC Power

The DC2326A requires ±9VDC and draws +145mA/–65mA.

Most of the supply current is consumed by the FPGA,

opamps, regulators and discrete logic on the board. The

±9VDC input voltage powers the ADC through LT1763

regulators which provide protection against accidental

reverse bias. Additional regulators provide power for the

FPGA and opamps.

U25A

LT6237IDD

EN

R129

1k

C116

OPT

dc2326 F02

R123

49.9Ω

C102

1000pF

IN0

–

conversion rate is shown in the Assembly Options table. If

the clock input is to be driven with logic, it is recommended

that the 49.9Ω termination resistor (R4) be removed.

Driving R4 with discrete logic may result in slow rising

edges. These slow rising edges may compromise the SNR

the converter

of

in the presence of high-amplitude higher

frequency input signals.

Data Output

Clock Source

You must provide a low jitter 2.5V

P-P

to the clock input, J1. The clock input is AC coupled so the

DC level of the clock signal is not important. A generator

such as the Rohde & Schwarz SMB100A high speed clock

source is recommended to drive the clock input. Even a

good generator can start to produce noticeable jitter at

low frequencies. Therefore it is recommended for lower

sample rates to divide down a higher frequency clock to

the desired sample rate. The ratio of clock frequency to

sine or square wave

Parallel data output from this board (0V to 2.5V default),

if not connected to the DC890, can be acquired by a logic

analyzer, and subsequently imported into a spreadsheet, or

mathematical package depending on what form of digital

signal processing is desired. Alternatively, the data can

be fed directly into an application circuit. Use pin 50 of

P1 to latch the data. The data should be latched using the

negative edge of this signal. The data output signal levels

at P1 can also be increased to 0V-3.3V if the application

circuit requires a higher voltage. This is accomplished by

moving JP2 to the 3.3V position.

dc2326af

3

Loading...

Loading...