User Guide for the LTD-BK1000

Product: LTE_WCDMA Wireless Modem

Model name: LTD-BK1000

Table of Contents

1. Overview

2. Major features

3. Interface

4. Electrical specifications

5. RF specifications

6. Mechanical specifications

7. General specifications

8. Connectors

9. RFx information

10. Approbation FCC

Copyright ⓒ. 2017. All Rights Reserved.

1. Overview

The LTD-BK1000 is a personal mobile communication device that incorporates

the latest compact radio technology, including smaller and lighter components

and support for WCDMA(850/1900MHz) bands and LTE(700/850/1700/1900

MHz). This device acts as the vehicle’s telematics system and connects to

WCDMA (HSPA+) and LTE wireless networks and wireless modules to allow

voice and data communication. Furthermore, this device can operate on land

and water as well as other similar areas.

In LTE mode, the device provides uplink speeds of up to 50 Mbps and

downlink speeds of up to 150 Mbps for seamless transfer of data such as

movies and video calls. The device also supports the transfer of large amounts

of data.

The device communicates with the host system via a standard RS-232 or USB

port, and AT commands and control commands can be used to send data. Voice

calls are also possible.

Copyright ⓒ. 2017. All Rights Reserved.

34 x 40 x 3.5 mm

(Tolerance

Technology

2. Major features

Dimensions

Weight

Mechanical

Interface

Temperature*

Main chipset

Memory

Standard

TBD g (max)

USB, general purpose I/O pins

Operation: -20 ℃ - +70 ℃

Storage: -40 ℃ - +85 ℃

MDM9628

4Gb(NAND) / 1Gb(SDRAM)

WCDMA (HSPA+)

LTE

– width, length : TBD)

- DL Speed : 14.4 Mbps

- UL Speed : 5.76 Mbps

- DL Speed : 150 Mbps

(L x W x T)

ETC

Band

Power

DC power

Functions

- UL Speed : 50 Mbps

WCDMA B2, B5

LTE B2, B4, B5, B17

WCDMA : Typ. 24dBm (Power Class 3)

LTE : Typ. 23dBm (Power Class 3)

4 V

Voice, data, SMS

Copyright ⓒ. 2017. All Rights Reserved.

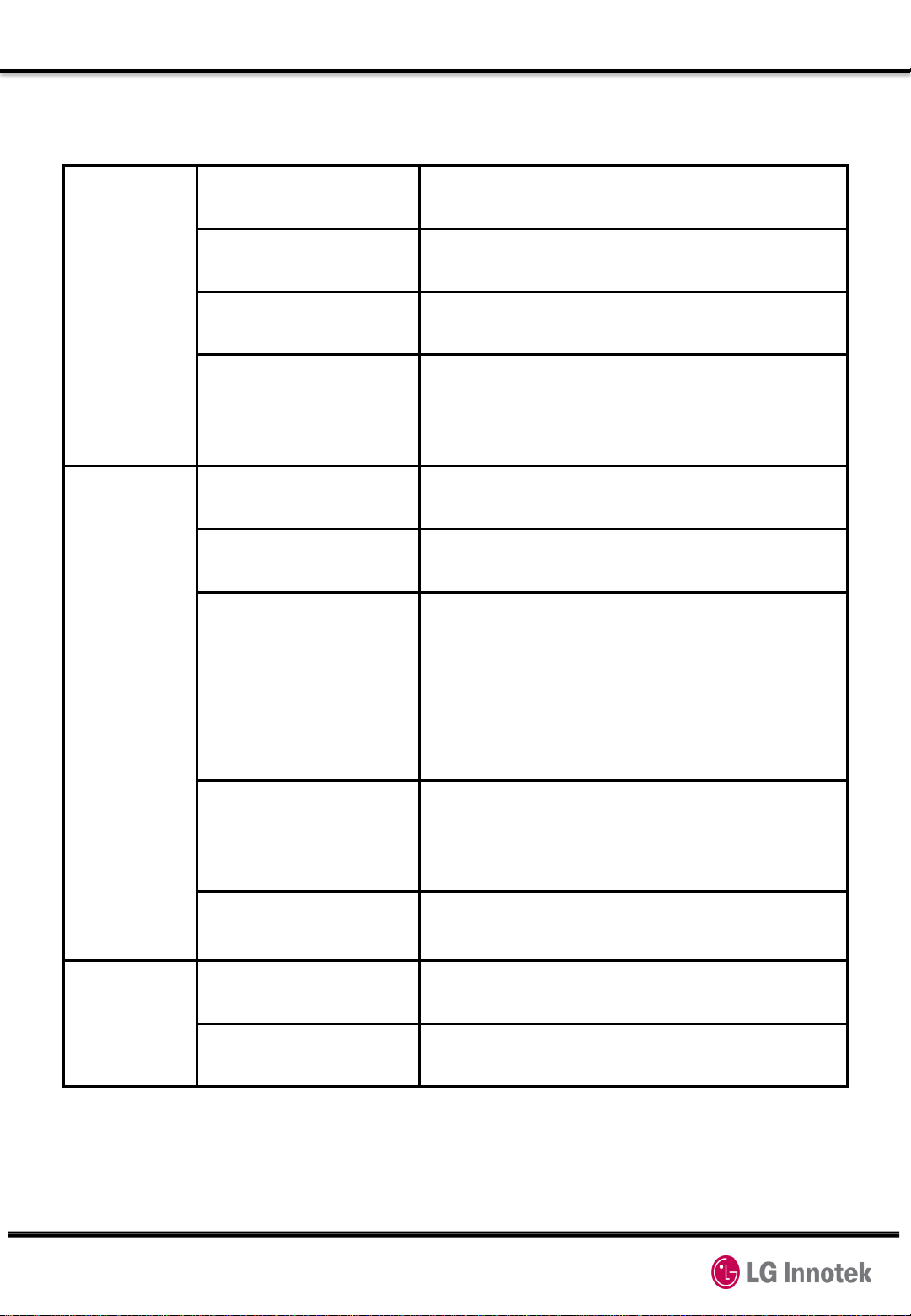

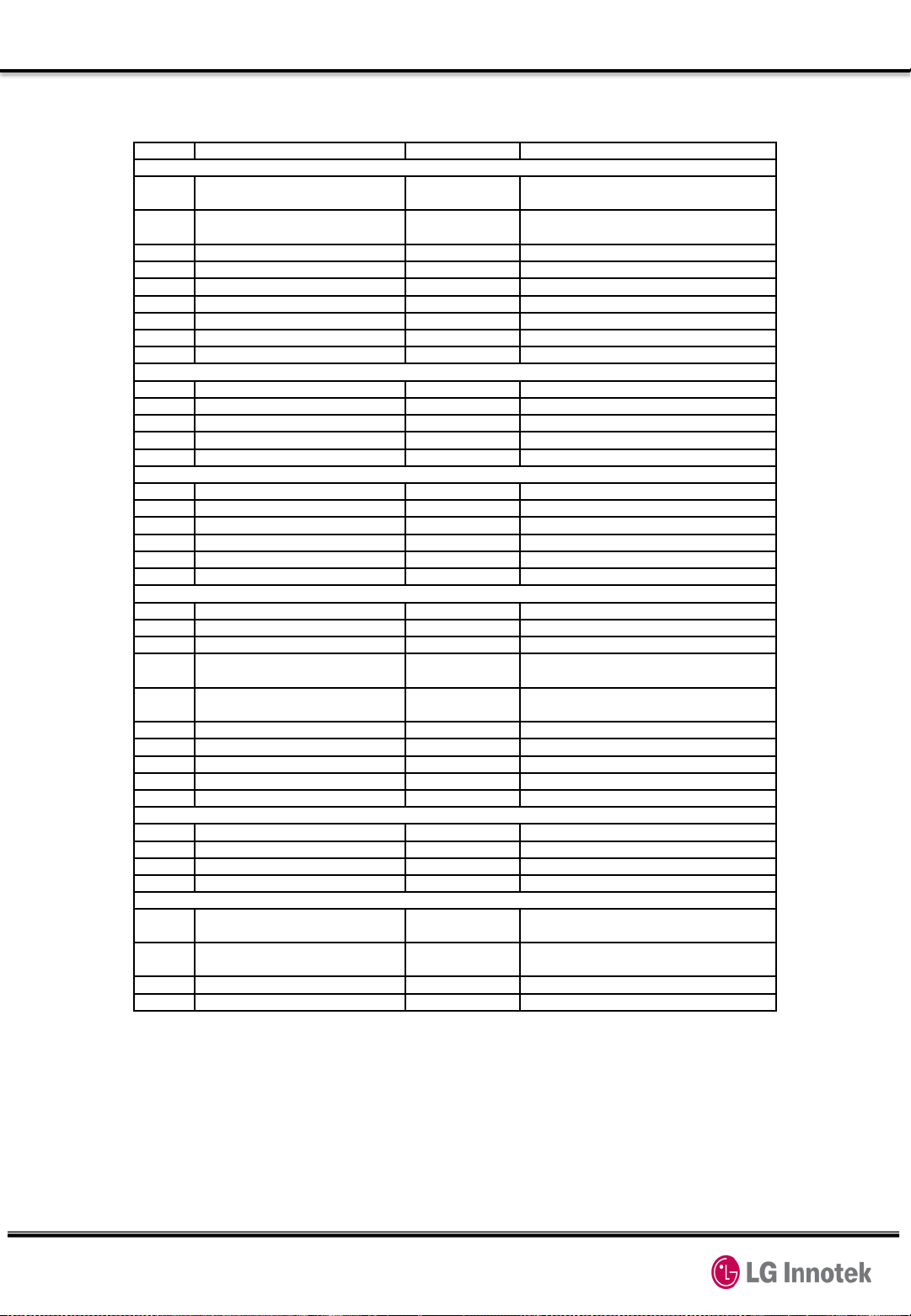

3. Interface

GND12 GND10 GND6 GND5

GND GND GND GND

GND GND

GND11 GND4

21 A21 C21 E21 G21 I21 K 21 M21 O21 Q21 S21 U21 W21 Y21 AA21 AC21 AE21

GND MAIN_ANT GND GND G ND GND GND GND G ND GND GND G ND GND GND ANT_DIV GND

20 B20 D20 F20 H20 J20 L20 N20 P20 R20 T20 V20 X20 Z20 AB20 A D20

GND GND M AIN_ANT_DTC_EN GND GND G ND GND GND GND GND GND GND DIV_ANT_DTC_EN GND GND

19 A19 C19 E19 G19 I19 K 19 M19 O19 Q19 S19 U19 W19 Y19 AA19 AC19 AE19

GND GND ADC 1 GND GND GND GND GND G ND GND GND GND GND ADC2 GND GND

18 B18 D18 F18 H18 J18 L18 N18 P18 R18 T18 V18 X18 Z18 AB18 A D18

GND GND GND GND GND G ND GND GND GND GND GND G ND G ND GND GND

17 A17 C17 E17 G17 I17 K 17 M17 O17 Q17 S17 U17 W17 Y17 AA17 AC17 AE17

VPH_PWR GND GND GND GND GND GND G ND G ND GND GND GND GND GND G ND GND

16 B16 D16 F16 H16 J16 L16 N16 P16 R16 T16 V16 X16 Z16 AB16 A D16

VPH_PWR GND GND GND GND GND GND G ND G ND GND GND GND GND GND G ND

15 A15 C15 E15 G15 I15 W15 Y15 AA15 AC15 AE15

VPH_PWR GND GND GND GND GND GND GND GND GND

14 B14 D14 F14 H14 N14 P14 R14 X14 Z14 AB14 A D14

VPH_PWR GND GND GND GND GND GND GND GND GND G ND

13 A13 C13 E13 G13 I13 M13 O13 Q13 S13 W13 Y13 AA13 AC13 AE13

GND GND GND GND GND GND GND GND GND GND GND GND GND GND

12 B12 D12 F12 H12 N12 P12 R12 X12 Z12 AB12 A D12

NC G ND GND GND GND GND GND GND G ND GND GND

11 A11 C11 E11 G11 I11 M11 O11 Q11 S11 W11 Y11 AA11 AC11 AE11

GND GND GND GND GND GND GND GND GND SGMII_RX_M SGMII_TX_P EPHY_RST_N SGM II_CLK EPHY_INT_N

10 B10 D10 F10 H10 N10 P10 R10 X10 Z10 AB10 A D10

GND GND GND GND GND GND GND SGMII_RX_P SGMII_TX_M SGMII_DATA GND

9 A9 C9 E9 G9 I9 M9 O9 Q9 S9 W9 Y9 AA9 A C9 AE9

VPH_PWR VREG_L11_1P8 GND NC NC GND GND G ND GND GND G ND GND GND MDM _JTAG_SRST_N

8 B8 D8 F8 H8 N8 P8 R8 X8 Z8 AB8 AD8

VPH_PWR VREG_L11_1P8 GND GND GND GND G ND MDM2AP_INT_N AP2MDM_INT_N MDM_JTAG_TCK MDM_JTAG_PS_HOLD

7 A7 C7 E7 G7 I7 W7 Y7 AA7 AC7 AE7

VPH_PWR VPH_PWR GND NC SPI_LEVEL_SHIFT_EN GND COEX_UART_RX GND MDM_JTAG_TMS MDM_JTAG_TRST_N

6 B6 D6 F6 H6 J6 L6 N6 P6 R6 T6 V6 X6 Z6 AB6 AD 6

GND GND GP IO ACC_PWR_ON G ND G PIO GPIO GND SPI_CS_N SPI_CLK GND DSRC_SLP_CLK COEX_UART_TX MDM_JTAG_TDO MDM_JTAG_TDI

5 A5 C5 E5 G5 I5 K5 M5 O5 Q5 S5 U5 W5 Y5 AA5 AC5 AE5

GND NC GPIO GND BOOT_OK UART1_TX UART2_TX UART3_TX SPI_INTERRUPT SPI_MOSI SPI_MISO GND

WLAN_3V_EN_DSRC

GND GND GND

4 B4 D4 F4 H4 J4 L4 N4 P4 R4 T4 V4 X4 Z4 AB4 AD4

MDM_RESOUT_N NC G ND MGS GND UART1_RX UART2_RX UA RT3_RX GND GND GND RFCLK2_QCA DSRC_PP S GND Ehernet_DC-DC_EN

3 A3 C3 E3 G3 I3 K3 M3 O3 Q3 S3 U3 W3 Y3 AA3 AC3 AE3

PHONE_ON_N LGA_RESIN_N GND 96H_END UIM1_PRESENT GND GND GND SDC_DATA3 SDC_DATA2 GND P CM_EN PCM_DIN WLAN_EN_DSRC GND VREG_L5_UIM2

2 B2 D2 F2 H2 J2 L2 N2 P2 R2 T2 V2 X2 Z2 AB2 AD2

GND GND VREG _L6_UIM1 UIM1_CLK GND USB_ID USB_HS_DM GND SDC _DATA1 SDC_DATA0 G ND PCM _CLK GND HSIC_DATA NC

1 A1 C1 E1 G1 I1 K1 M1 O1 Q1 S1 U1 W1 Y1 AA1 AC1 AE1

GND GND UIM 1_RESET UIM1_DATA GND U SB_VBUS USB_HS_DP GND SDC_CMD SDC_CLK GND PCM_SYNC PCM_DOU T GND HSIC_STB NC

GND9 A B C D E F G H I J K L M N O P Q R S T U V W X Y Z AA AB AC AD AE GND2

GND GND

GND GND GND GND

GND8 GND7 GND3 GND1

3.1 LGA Pad Layout (Top View)

Copyright ⓒ. 2017. All Rights Reserved.

Figure 1. LGA Pin map

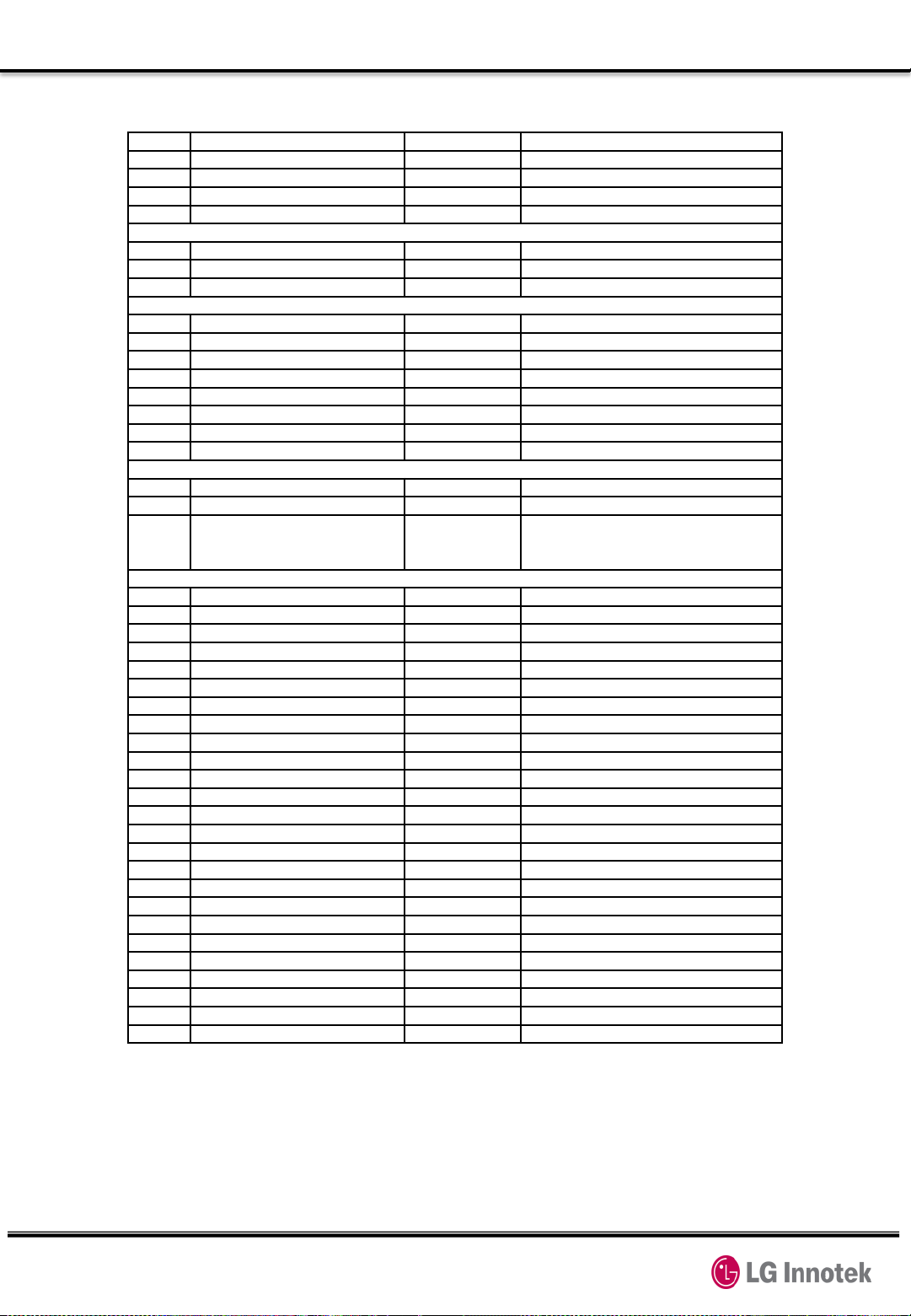

3. Interface

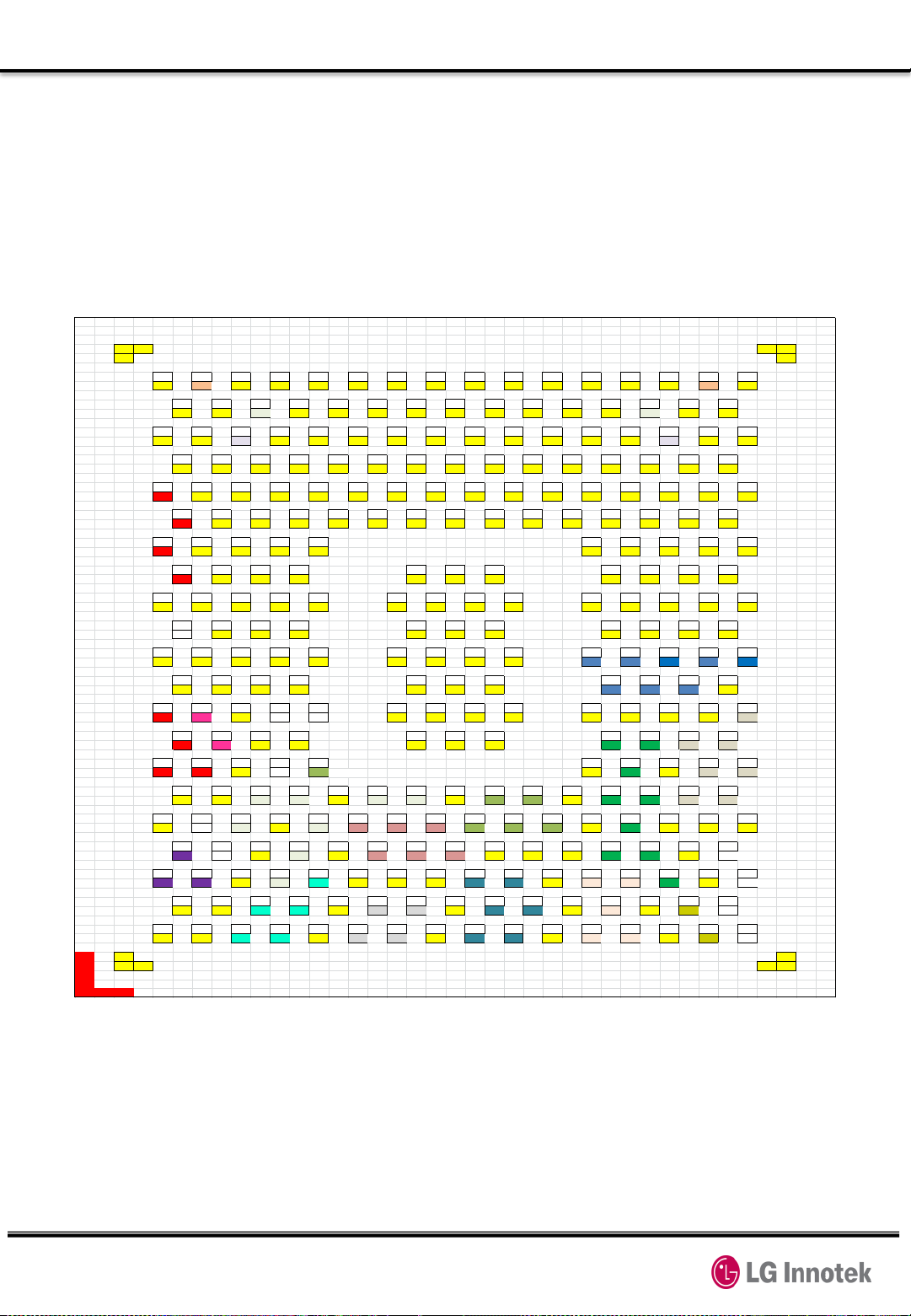

PAD. NAME

DIRECTION

DESCRIPTION

Antenna Interface Pads

MAIN_ANT

RF Main Antenna

DIV_ANT

RF Diversity Antenna

User Interface Pads

ACC_PWR_ON

ACC_PWR_ON

BOOT_OK

BOOT_OK

MSG

MSG

96H_END

96H_END

MAIN_ANT_DTC_EN

Main ANT Detect Enable

DIV_ANT_DTC_EN

Diversity ANT Detect Enable

SPI_LEVEL_SHIFT_EN

SPI LEVEL SHIFT Enable

ETHERNET_DCDC_ENABLE

Ethernet power enable

GPIO1

General purpose I/O

GPIO2

General purpose I/O

GPIO3

Input/Output (Not

support INTERR

UPT)

General purpose I/O

GPIO4

General purpose I/O

ADC Interface Pads

ADC1

ADC Convertor input for main

antenna detect

ADC2

ADC Convertor input for diversity

antenna detect

PCM Interface Pads

PCM_EN

PCM 3.3 Level Shifter Enable

PCM_CLK

PCM Clock

PCM_SYNC

PCM Frame Sync

PCM_DIN

PCM Data In

PCM_DOUT

PCM Data Out

JTAG Pin Description

MDM_JTAG_TMS

JTAG mode select input

MDM_JTAG_PS_HOLD

JTAG PS HOLD detect

MDM_JTAG_TDI

JTAG data input

MDM_JTAG_TRST_N

JTAG reset for debug

MDM_JTAG_TDO

JTAG debugging

MDM_JTAG_TCK

JTAG clock input

MDM_JTAG_SRST_N

JTAG reset

USB Interface Pads

USB_HS_DM

USB high speed data (minus)

USB_HS_DP

USB high speed data (plus)

USB_VBUS

USB power

USB_ID

USB ID

SDIO Interface Pads

SDC_CLK

Secure digital controller clock

SDC_CMD

Secure digital controller command

SDC_DATA0

Secure digital controller data bit 0

SDC_DATA1

Secure digital controller data bit 1

SDC_DATA2

Secure digital controller data bit 2

3.2 Pin description

C21

AC21

H6

I5

H4

G3

F20

Z20

I7

AD4

F6

E5

L6

N6

E19

AA19

W3

X2

W1

Y3

Y1

AC7

AD8

AD6

AE7

AB6

AB8

AE9

N2

M1

K1

L2

S1

Q1

T2

R2

S3

Input/Output

Input/Output

Input

Output

Output

Output

Output

Output

Output

Output

Input

Input

Output

Input

Input

Input

Output

Input/Output

input

Input

Input

Output

Input

Input

Input/Output

Input/Output

Input

Input

Output

Output

Input/Output

Input/Output

Input/Output

Input/Output

(Do not use

with External

PU)

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

SDC_DATA3

Secure digital controller data bit 3

SGMMI Interface Pads

EPHY_RST_N or UIM2_RESET

Ethernet PHY reset

EPHY_INT_N or UIM2_DETECT

Ethernet PHY interrupt

SGMII_DATA or UIM2_CLK

SGMII input Output data

GND

Ground

SGMII_RX_P

SGMII receive

SGMII_RX_M

SGMII receive

SGMII_TX_M

SGMII transmit

SGMII_TX_P

SGMII transmit

SGMII_CLK or UIM2_DATA

SGMII clock

SPI Interface Pads

SPI_MOSI

SPI Serial Output

SPI_CLK

SPI Serial Clock

SPI_CS_N

SPI Chip Select

SPI_MISO

SPI Serial input

SPI_INTERRUPT

MICOM → LGA SPI interrupt

UART Interface Pads

UART2_TX

UART2 Transmit data

UART2_RX

UART2 Receive data

UART1_TX

Debug UART5 Transmit Data

UART1_RX

Debug UART5 Receive Data

UART3_TX

UART6 Transmit data

UART3_RX

UART6 Receive data

USIM Interface Pads

UIM1_PRESENT

Detection of an external UIM card

UIM1_CLK

Clock Output to an external UIM card

UIM1_RESET

Reset Output to an external UIM card

UIM1_DATA

Data connection with an external UIM

card

VREG_L6_UIM1

Supply Output for an external UIM card

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

HSIC Pin Description

HSIC_DATA

HSIC data

HSIC_STB

HSIC Strobe signal

NC

No Connect

NC

No Connect

DSRC Pin Description

COEX_UART_RX

LTE receiver sync for coexistence with

UART

COEX_UART_TX

LTE transmitter sync for coexistence

with UART

RFCLK2_QCA

Low noise RF clock Output

WLAN_EN_DSRC

WLAN Enable

Q3

AA11

AE11

AB10

AD10

X10

W11

Z10

Y11

AC11

S5

T6

R6

U5

Q5

M5

N4

K5

L4

O5

P4

I3

H2

E1

G1

F2

E3

D2

A1

C1

B2

AB2

AC1

AD2

AE1

Y7

Z6

X4

AA3

Input/Output

Input/Output

Input

Input

Output

Output

Output

Output

Output

Output

Input

Input

Output

Input

Output

Input

Output

Input

Input

Output

Output

Input/Output

Output

Input/Output

Input/Output

Input

Output

Output

Output

Output

Input

- plus

-minus

- plus

-minus

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

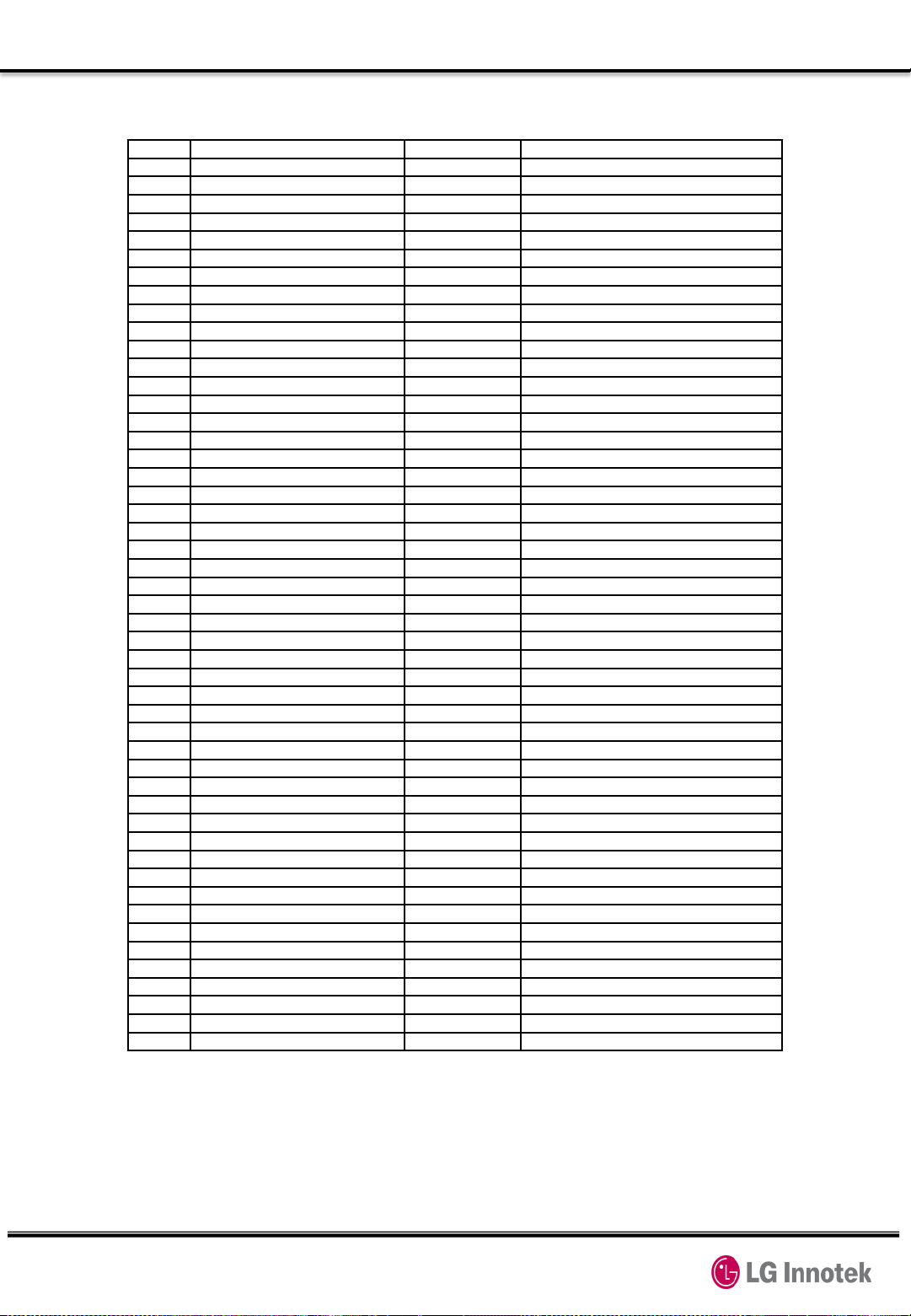

3. Interface

DSRC_SLP_CLK

DSRC sleep clock

WLAN_3V_EN_DSRC

Used for WLAN enable

DSRC_PPS

Pulse Per Second

MDM2AP_INT_N

MDM to AP interrupt, PCM_LDO_EN

AP2MDM_INT_N

AP to MDM interrupt

Control Pads

LGA_PHONE_ON

ON/OFF Control

MDM_RESOUT_N

Reset Output

LGA_RESIN_N

External Reset Input

Power Supply Pads

VPH_PWR for PAM

power supply (4.0V)

VPH_PWR for PAM

power

VPH_PWR for PAM

power

VPH_PWR for PAM

power

VPH_PWR for PMIC

power

VPH_PWR for PMIC

power

VPH_PWR for PMIC

power

VPH_PWR for PMIC

power

Voltage Reference Pad

VREG_L11_1P8

LDO out for 1.8V pull up

VREG_L11_1P8

LDO out for 1.8V pull up

Voltage Reference for SGMII

(VREG_L5_UIM2) – Ethernet

IO

Ethernet I/O voltage

NC Pads

NC

No Connect

NC

No Connect

NC

No Connect

NC

No Connect

NC

No Connect

NC

No Connect

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

X6

Y5

Z4

X8

Z8

A3

B4

C3

A17

B16

A15

B14

A9

B8

A7

C7

C9

D8

AE3

G9

B12

I9

G7

C5

D4

A21

E21

G21

I21

K21

M21

O21

Q21

S21

U21

W21

Y21

AA21

AE21

B20

D20

H20

J20

Output

Output

Input/Output

Output

Input

Input

Output

Input

Input

Input

Input

Input

Input

Input

Input

Input

Output

Output

전압 level

Output

supply (4.0V)

supply (4.0V)

supply (4.0V)

supply (4.0V)

supply (4.0V)

supply (4.0V)

supply (4.0V)

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

L20

N20

P20

R20

T20

V20

X20

AB20

AD20

A19

C19

G19

I19

K19

M19

O19

Q19

S19

U19

W19

Y19

AC19

AE19

B18

D18

F18

H18

J18

L18

N18

P18

R18

T18

V18

X18

Z18

AB18

AD18

C17

E17

G17

I17

K17

M17

O17

Q17

S17

U17

W17

Y17

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

AA17

AC17

AE17

D16

F16

H16

J16

L16

N16

P16

R16

T16

V16

X16

Z16

AB16

AD16

C15

E15

G15

I15

W15

Y15

AA15

AC15

AE15

D14

F14

H14

X14

Z14

AB14

AD14

A13

C13

E13

G13

I13

W13

Y13

AA13

AC13

AE13

D12

F12

H12

X12

Z12

AB12

AD12

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

A11

C11

E11

G11

I11

B10

D10

F10

H10

E9

W9

Y9

AA9

AC9

F8

H8

E7

W7

AA7

B6

D6

J6

P6

V6

A5

W5

AA5

AC5

AE5

F4

J4

R4

T4

V4

AB4

K3

M3

O3

U3

AC3

J2

P2

V2

Z2

I1

O1

U1

AA1

GND1

GND2

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND11

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND

Ground

GND3

GND4

GND5

GND6

GND7

GND8

GND9

GND1

0

GND1

2

N14

P14

R14

M13

O13

Q13

S13

N12

P12

R12

M11

O11

Q11

S11

N10

P10

R10

M9

O9

Q9

S9

N8

P8

R8

G5

Copyright ⓒ. 2017. All Rights Reserved.

Table 1. Pin descriptions

3. Interface

3.3 USB

This device supports universal serial bus (USB) connections for high-speed

data communication. The relevant hardware satisfies the USB 2.0

specifications and supports maximum communications speeds of 480 Mbps

Pin NO. Signal Name

M1

N2

K1

USB_D+

USB_D-

USB_VBUS

Pin I/O

(Modem host)

IO

IO

I

Function Description

USB Differential data line (+)

USB Differential data line (-)

Table 2. USB Pin descriptions

USB Power Supply

Copyright ⓒ. 2017. All Rights Reserved.

3. Interface

No.

3.4 Audio

This module includes a PCM interface. The pull-up and pull-down resistors

attached to these pin must provide more than 50 Kohm of resistance.

Pin NO.

W1 PCM_SYNC

X2 PCM_CLK

Y1 PCM_TXD

Y3

PCM_RXD I PCM Interface digital audio data in

Signal Name

3.5 User interface

Pin

Signal Name Direction

Pin I/O

(Modem host)

I

I

O

PCM Interface sync

PCM Interface clock

PCM Interface digital audio data out

Table 3. PCM Pin descriptions

Function Description

Function

I5

BOOT_OK

C3 RESET_IN I

H4 MSG O

G3 96H_END O

H6 ACC_ON_SLEEP

A3 Phone_ON I

Table 4. User interface Pin descriptions

O

I

Indicates that the Modem boot is complete.

Control line to unconditionally restart the

module.

Indicates that the Modem receive Urgent

message.

Indicates that the 96hr sleep mode is end.

Control line to power on or 96hr sleep mode.

Control line to power on / off

Copyright ⓒ. 2017. All Rights Reserved.

4. Electrical specifications

A7,C7,B8,A9,

B14,A15,B16,

4.1 Power supply specifications

The host system provides the power supply (V_BATT)DC 4 V, 2.5 A to the

device. The internal power supply module manages the power supplied to the

integral circuits and maintains constant voltages. This module also controls

each power block to minimize power consumption.

In particular, the PAM (power amplifier module) consumes a lot of power, so it

receives a direct power supply of 4 V from the V_BATT. Therefore the

V_BATT signal inputs only the supply power of the PAM, even when the

absolute rating is higher. In addition, the entire power input module blocks and

protects against high surges and ESD in the NAD module.

Pin No. Signal Name Direction

V_BATT I 3.9 V 4 V 4.1 V

A17

Table 5. Power supply specifications

MIN TYP MAX

Copyright ⓒ. 2017. All Rights Reserved.

4. Electrical specifications

ACC_ON_SLEEP

4.2 Logic level specifications

4.2.1 Digital logic level specifications

Signal Name Type

BOOT_OK O 0 0.45 1.35 1.8

RESET_IN I -0.3 0.63 1.17 1.8

MSG O 0 0.45 1.35 1.8

96H_END O 0 0.45 1.35 1.8

I 0 0.63 1.17 1.8

Low High

Min Max Min Max

Table 6. Digital logic level specifications

Unit

V

Copyright ⓒ. 2017. All Rights Reserved.

5. RF specifications

5.1 WCDMA

5.1.1 Receiver

.- Bandwidth : 5MHz

.- Frequency : 869MHz – 894MHz (B5), 1930MHz – 1990MHz (B2)

.- RF to Baseband Direct conversion (Zero IF)

.- Modulation method : QPSK, 16QAM

.- Sensitivity : ≤-104dBm (BER = Under 0.1%)

5.1.2 Transmitter

.- Frequency: 824MHz – 849MHz (B5), 1850MHz – 1910MHz (B2)

.- Maximum RF Output : Power class3 , 20.3dBm ~ 25.7dBm

.- Modulation method : QPSK

.- Baseband to RF Direct conversion (Zero IF)

5.2 LTE

5.2.1 Receiver

.- Bandwidth :

B2/B4(5 MHz, 10 MHz, 15 MHz, 20 MHz), B5/B17(5 MHz, 10 MHz)

.- Frequency :

B2 (1930 MHz – 1990 MHz), B4 (2110 MHz – 2155 MHz), B5 (869 MHz

– 894 MHz), B17 (734 MHz – 746 MHz)

.- RF to Baseband Direct conversion (Zero IF)

.- Modulation method : QPSK, 16QAM and 64QAM

.- Sensitivity :

B2 (≤-94.3dBm @QPSK, BW:10 MHz), B4 (≤-96.3dBm @QPSK, BW:10

MHz), B5 (≤-94.3dBm @QPSK, BW:10 MHz), B17 (≤-93.3dBm

@QPSK, BW:10 MHz)

Copyright ⓒ. 2017. All Rights Reserved.

5. RF specifications

5.2.2 Transmitter

.- Frequency:

B2 (1850 MHz – 1910 MHz), B4 (1710 MHz – 1755 MHz),B5 (824 MHz

– 849 MHz), B17 (704 MHz – 716MHz)

.- Maximum RF Output : Power class3 , 20.3dBm ~ 25.7dBm

.- Modulation method : QPSK and 16QAM

.- Baseband to RF Direct conversion (Zero IF)

Copyright ⓒ. 2017. All Rights Reserved.

6. Mechanical specifications

6.1 Environment specifications

.- Storage temp.: -40 ℃ - +85 ℃

.- Operating temp.: -20 ℃ - +70 ℃

(-20 ℃ - +70 ℃ : 3GPP specifications are satisfied

-30 ℃ - -20 ℃, +70 ℃ - +80 ℃ : May cause performance degradation)

.- Operating humidity: 80% (60℃) relative humidity

Copyright ⓒ. 2017. All Rights Reserved.

6. Mechanical specifications

6.1 Mechanical dimensions

Dimensions

Weight TBD grams(max.)

Modem interface connector 12709HS-H40 (Manufacture vendor : YUNHO)

Modem antenna Connector (Plug)

34 x 40.0 x 3.5 mm (L x W x T)

(Tolerance – width, length : TBD)

KR15005-DD , KR15005-DG

(Manufacture vendor : KET)

Table 7. Mechanical specification

Figure 2. Mechanical dimension

Copyright ⓒ. 2017. All Rights Reserved.

7. General specifications

Ref Sense Go/No Go

7.1 WCDMA B5 electrical specifications

1 Maximum Output Power 20.3~25.7dBm

2 Frequency Error -195 ~ +195Hz

3

4 Minimum Output Power -49dBm ↓

5 Occupied Bandwidth (OBW) 5MHz ↓ Normal

6

7

Inner Loop Power Control in the Uplin

Spectrum emis

sion mask

Adjacent Chan

nel Leakage Po

wer Ratio (ACL

TEST ITEM Spec. Test Temperature

Normal, Temp L, Te

Normal, Temp L, Te

PASS Normal Mid - PASS

Normal, Temp L, Te

-48.5dBc ↓

-37.5dBc ↓ PASS PASS PASS

-47.5dBc ↓ PASS PASS PASS

-47.5dBc ↓ PASS PASS PASS

-32.2dBc ↓

-42.2dBc ↓

Normal, Temp L, Te

Normal, Temp L, Te

R)

k

SEM Band1 Offset2.

5-3.5MHz (at Freq+3.

5MHz)

SEM Band1 Offset3.

5-7.5MHz (at Freq+7.

5MHz)

SEM Band1 Offset7.

5-8.5MHz (at Freq+8.

5MHz)

SEM Band1 Offset8.

5-12.5MHz

ACLR Offset +5/-5M

Hz Rel

ACLR Offset +10/-10

MHz Rel

mp H

mp H

mp H

Normal

mp H

mp H

Test Freq

uency

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

CHANNEL

4357 4400 4458

PASS PASS PASS

PASS PASS PASS

-

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

8

9

10

11

12

Error Vector M

agnitude(EVM)

Peak code do

main error

Phase Disconti

nuity

Reference Sen

sitivity Level

Maximum Inpu

t Level

EVM at Tx output po

wer 24dBm /-18dBm

PCDE at Tx output p

ower 24dBm/-18dBm

Phase Discontinuity

max EVM

Phase Discontinuity

max Frequency Error

Phase Discontinuity

max 1500Hz

I^or=-104dBm/3.84M

Hz

Max Input Go/No Go

I^or=-25.7dBm/3.84M

Hz

17.5% ↓ Normal

-14dB ↓ Normal

17.5% ↓

-195~195Hz - PASS

36 degrees ↓ - PASS

BER 0.1% ↓

BER 0.1% ↓ Normal Mid - PASS

Normal Mid

Normal, Temp L, Te

mp H

Low, Mid,

Low, Mid,

Low, Mid,

Table 8. WCDMA B5 RF specification

High

High

High

PASS PASS PASS

PASS PASS PASS

- PASS

PASS PASS PASS

-

-

-

-

Copyright ⓒ. 2017. All Rights Reserved.

7. General specifications

Ref Sense Go/No Go

7.2 WCDMA B2 electrical specifications

1 Maximum Output Power 20.3~25.7dBm

2 Frequency Error -195 ~ +195Hz

3

4 Minimum Output Power -49dBm ↓

5 Occupied Bandwidth (OBW) 5MHz ↓ Normal

6

7

Inner Loop Power Control in the Uplin

Spectrum emis

sion mask

Adjacent Chan

nel Leakage Po

wer Ratio (ACL

TEST ITEM Spec. Test Temperature

Normal, Temp L, Te

Normal, Temp L, Te

PASS Normal Mid - PASS

Normal, Temp L, Te

-48.5dBc ↓

-37.5dBc ↓ PASS PASS PASS

-47.5dBc ↓ PASS PASS PASS

-47.5dBc ↓ PASS PASS PASS

-32.2dBc ↓

-42.2dBc ↓

Normal, Temp L, Te

Normal, Temp L, Te

R)

k

SEM Band1 Offset2.

5-3.5MHz (at Freq+3.

5MHz)

SEM Band1 Offset3.

5-7.5MHz (at Freq+7.

5MHz)

SEM Band1 Offset7.

5-8.5MHz (at Freq+8.

5MHz)

SEM Band1 Offset8.

5-12.5MHz

ACLR Offset +5/-5M

Hz Rel

ACLR Offset +10/-10

MHz Rel

mp H

mp H

mp H

Normal

mp H

mp H

Test Freq

uency

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

Low, Mid,

High

CHANNEL

9662 9800 9938

PASS PASS PASS

PASS PASS PASS

-

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

PASS PASS PASS

8

9

10

11

12

Error Vector M

agnitude(EVM)

Peak code do

main error

Phase Disconti

nuity

Reference Sen

sitivity Level

Maximum Inpu

t Level

EVM at Tx output po

wer 24dBm /-18dBm

PCDE at Tx output p

ower 24dBm/-18dBm

Phase Discontinuity

max EVM

Phase Discontinuity

max Frequency Error

Phase Discontinuity

max 1500Hz

I^or=-104dBm/3.84M

Hz

Max Input Go/No Go

I^or=-25.7dBm/3.84M

Hz

17.5% ↓ Normal

-14dB ↓ Normal

17.5% ↓

-195~195Hz - PASS

36 degrees ↓ - PASS

BER 0.1% ↓

BER 0.1% ↓ Normal Mid - PASS

Normal Mid

Normal, Temp L, Te

mp H

Low, Mid,

Low, Mid,

Low, Mid,

Table 9. WCDMA B2 RF specification

High

High

High

PASS PASS PASS

PASS PASS PASS

- PASS

PASS PASS PASS

-

-

-

-

Copyright ⓒ. 2017. All Rights Reserved.

7. General specifications

12.5%↓(16QAM,

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Reference Sensitivity

7.3 LTE B2 electrical specifications

1 Maximum Output Power(class 3) 20.3~25.7dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

2 Minimum Output Power -39dBm ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

3 Frequency Error ±0.1ppm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

시험 항목 Spec. Test Temperature Frequency

TX Channel

18650 18900 19150

4 Error Vector Magnitude(EVM)

5

6 In-band emission

7

8

9

Relative Carrier

Leakage Power

EVM equalizer

spectrum flatness

Spectrum emission

mask

Adjacent Channel

Leakage Power Ratio

Carrier Leakage

(3.2dBm ± 3.2dB)

In-band emission

(3.2dBm ± 3.2dB)

EVM equalizer spectrum

flatness Range1

upper/lower Area 1

upper/lower Area 2

upper/lower Area 3

upper/lower Area 4

ACLR E-UTRA ± -29.2dB ↓

ACLR UTRA Offset 1 ± -32.2dB ↓ PASS PASS PASS

ACLR UTRA Offset 2 ± -35.2dB ↓ PASS PASS PASS

50RB)

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

5.4 dB ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-16.5 dBm ↓

-8.5 dBm ↓ PASS PASS PASS

-11.5 dBm ↓ PASS PASS PASS

-23.5 dBm ↓ PASS PASS PASS

Normal Low, Mid, High PASS PASS PASS

PASS PASS PASS

Normal Low, Mid, High

PASS PASS PASS

Normal, Temp L, Temp H Low, Mid, High

10

Level @ 10MHz

Ref Sense throughput

Table 10. LTE B2 RF specification

Copyright ⓒ. 2017. All Rights Reserved.

shall be ≥ 95%

-94.3 dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

7. General specifications

12.5%↓(16QAM,

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Reference Sensitivity

7.4 LTE B4 electrical specifications

1 Maximum Output Power(class 3) 20.3~25.7dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

2 Minimum Output Power -39dBm ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

3 Frequency Error ±0.1ppm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

시험 항목 Spec. Test Temperature Frequency

TX Channel

20000 20175 20350

4 Error Vector Magnitude(EVM)

5

6 In-band emission

7

8

9

Relative Carrier

Leakage Power

EVM equalizer

spectrum flatness

Spectrum emission

mask

Adjacent Channel

Leakage Power Ratio

Carrier Leakage

(3.2dBm ± 3.2dB)

In-band emission

(3.2dBm ± 3.2dB)

EVM equalizer spectrum

flatness Range1

upper/lower Area 1

upper/lower Area 2

upper/lower Area 3

upper/lower Area 4

ACLR E-UTRA ± -29.2dB ↓

ACLR UTRA Offset 1 ± -32.2dB ↓ PASS PASS PASS

ACLR UTRA Offset 2 ± -35.2dB ↓ PASS PASS PASS

50RB)

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

5.4 dB ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-16.5 dBm ↓

-8.5 dBm ↓ PASS PASS PASS

-11.5 dBm ↓ PASS PASS PASS

-23.5 dBm ↓ PASS PASS PASS

Normal Low, Mid, High PASS PASS PASS

PASS PASS PASS

Normal Low, Mid, High

PASS PASS PASS

Normal, Temp L, Temp H Low, Mid, High

10

Level @ 10MHz

Ref Sense throughput

Table 11. LTE B4 RF specification

Copyright ⓒ. 2017. All Rights Reserved.

shall be ≥ 95%

-96.3 dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

7. General specifications

12.5%↓(16QAM,

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Reference Sensitivity

7.5 LTE B5 electrical specifications

1 Maximum Output Power(class 3) 20.3~25.7dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

2 Minimum Output Power -39dBm ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

3 Frequency Error ±0.1ppm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

시험 항목 Spec. Test Temperature Frequency

TX Channel

20450 20525 20600

4 Error Vector Magnitude(EVM)

5

6 In-band emission

7

8

9

Relative Carrier

Leakage Power

EVM equalizer

spectrum flatness

Spectrum emission

mask

Adjacent Channel

Leakage Power Ratio

Carrier Leakage

(3.2dBm ± 3.2dB)

In-band emission

(3.2dBm ± 3.2dB)

EVM equalizer spectrum

flatness Range1

upper/lower Area 1

upper/lower Area 2

upper/lower Area 3

upper/lower Area 4

ACLR E-UTRA ± -29.2dB ↓

ACLR UTRA Offset 1 ± -32.2dB ↓ PASS PASS PASS

ACLR UTRA Offset 2 ± -35.2dB ↓ PASS PASS PASS

50RB)

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

5.4 dB ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-16.5 dBm ↓

-8.5 dBm ↓ PASS PASS PASS

-11.5 dBm ↓ PASS PASS PASS

-23.5 dBm ↓ PASS PASS PASS

Normal Low, Mid, High PASS PASS PASS

PASS PASS PASS

Normal Low, Mid, High

PASS PASS PASS

Normal, Temp L, Temp H Low, Mid, High

10

Level @ 10MHz

Ref Sense throughput

Table 12. LTE B5 RF specification

Copyright ⓒ. 2017. All Rights Reserved.

shall be ≥ 95%

-94.3 dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

7. General specifications

12.5%↓(16QAM,

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Spectrum Emission Mask

Reference Sensitivity

7.17 LTE B17 electrical specifications

1 Maximum Output Power(class 3) 20.3~25.7dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

2 Minimum Output Power -39dBm ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

3 Frequency Error ±0.1ppm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

시험 항목 Spec. Test Temperature Frequency

TX Channel

23780 23790 23800

4 Error Vector Magnitude(EVM)

5

6 In-band emission

7

8

9

Relative Carrier

Leakage Power

EVM equalizer

spectrum flatness

Spectrum emission

mask

Adjacent Channel

Leakage Power Ratio

Carrier Leakage

(3.2dBm ± 3.2dB)

In-band emission

(3.2dBm ± 3.2dB)

EVM equalizer spectrum

flatness Range1

upper/lower Area 1

upper/lower Area 2

upper/lower Area 3

upper/lower Area 4

ACLR E-UTRA ± -29.2dB ↓

ACLR UTRA Offset 1 ± -32.2dB ↓ PASS PASS PASS

ACLR UTRA Offset 2 ± -35.2dB ↓ PASS PASS PASS

50RB)

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-24.2 dBc Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

5.4 dB ↓ Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

-16.5 dBm ↓

-8.5 dBm ↓ PASS PASS PASS

-11.5 dBm ↓ PASS PASS PASS

-23.5 dBm ↓ PASS PASS PASS

Normal Low, Mid, High PASS PASS PASS

PASS PASS PASS

Normal Low, Mid, High

PASS PASS PASS

Normal, Temp L, Temp H Low, Mid, High

10

Level @ 10MHz

Ref Sense throughput

Table 13. LTE B17 RF specification

Copyright ⓒ. 2017. All Rights Reserved.

shall be ≥ 95%

-93.3 dBm Normal, Temp L, Temp H Low, Mid, High PASS PASS PASS

8. RFx information

The strength of the RF field produced by the wireless module or modules

embedded in the TCU is well within all international RF exposure limits known

at this time. Because the wireless modules embedded in the TCU emit less than

the maximum amount of energy permitted in radio frequency safety standards

and recommendations, the manufacturer believes these modules are safe for

use.

Regardless of the power levels, care should be taken to minimize human

contact during normal operation. This module should be remain more than 20

cm (8 inches) from the body when wireless devices are on and transmitting.

This transmitter must not be collocated or operated in conjunction with any

other antenna or transmitter. Operation is subject to the following two conditions:

(1) this module does not cause interference , (2) this module accepts any

interference that may cause undesired operation.

8.1 Information for the integrator

The integrator must not provide information to the end user regarding how to

install or remove this RF module in the user manual of the end product. The user

manual that is provided by the integrator for end users must include the following

information in a prominent location. To comply with FCC RF exposure

requirements, the antenna used for this transmitter must be installed to provide a

separation distance of at least 20 cm from all persons and must not be

collocated or operated in conjunction with any other antenna or transmitter. The

label for the end product must include FCC ID: YZP-BK1000 or A RF transmitter

inside, IC ID: 7414C-BK1000

Copyright ⓒ. 2017. All Rights Reserved.

9. Approbation FCC

This module complies with FCC/IC rules.

FCC : Part 22, Part 24, Part 27

IC : RSS-130, RSS-132, RSS-133, RSS-139

Furthermore, this device complies with FCC/IC radiation exposure limits set forth for uncontrolled

environments.

This module must be installed and operated with minimum distance of 20 cm between the radiating element

and the user.

This module must not be co-located with any other transmitters or antennas

Cet module est conforme à l'exposition de FCC et IC rayonnements limites é-tablies pour un environnement

non contrôlé. Cet module doit être installé et utilisé avec une distance minimale de 20 cm entre le radiateur et

votre corps. Ce module ne doit pas être même endroit avec d'autres émetteur ou antennes.

To comply with FCC/IC regulations limiting both the maximum RF output power and human exposure to RF

radiation, the maximum antenna gain including cable loss in a mobile-only exposure condition must not

exceed the values listed in the following table.

Band Frequency Range

[MHz]

Maximum Antenna

Gain[dBi]

WCDMA(B5) 826.40~846.6 4.5

WCDMA(B2) 1852.4~1907.6 2.0

LTE(B2) 1850~1910 2.0

LTE(B4) 1710~1755 2.0

LTE(B5) 824~849 4.5

LTE(B17) 704~716 4.5

To satisfy the FCC’s exterior labeling requirements, the following text must appear on the

exterior of the end product.

Contains transmitter module FCC ID: YZP-BK1000

Contains transmitter module IC ID: 7414C-BK1000

Changes or modifications to this equipment may cause harmful interference unless the

modifications are expressly approved in the instruction manual. Users may lose the authority

to operate this equipment if an unauthorized change or codification is made.

Note: If this module is intended for use in a portable device, additional testing will be required

to satisfy the RF exposure and SAR requirements of FCC Part 2.1093 and RSS-102.

Copyright ⓒ. 2017. All Rights Reserved.

Loading...

Loading...